(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-12914

(P2006-12914A)

(43) 公開日 平成18年1月12日(2006.1.12)

| (51) Int.C1.       |                              | F 1         | テーマコード (参考)                                |

|--------------------|------------------------------|-------------|--------------------------------------------|

| <b>HO1L 21/301</b> | <b>(2006.01)</b>             | HO1L 21/78  | Q                                          |

| <b>HO1L 21/02</b>  | <b>(2006.01)</b>             | HO1L 21/02  | C                                          |

| <b>HO1L 21/304</b> | <b>(2006.01)</b>             | HO1L 21/304 | 621B                                       |

|                    |                              | HO1L 21/304 | 622J                                       |

|                    |                              | HO1L 21/78  | M                                          |

| 審査請求               | 未請求                          | 請求項の数 23    | O L (全 11 頁) 最終頁に続く                        |

| (21) 出願番号          | 特願2004-183961 (P2004-183961) | (71) 出願人    | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日           | 平成16年6月22日 (2004.6.22)       | (74) 代理人    | 100076428<br>弁理士 大塚 康徳                     |

|                    |                              | (74) 代理人    | 100112508<br>弁理士 高柳 司郎                     |

|                    |                              | (74) 代理人    | 100115071<br>弁理士 大塚 康弘                     |

|                    |                              | (74) 代理人    | 100116894<br>弁理士 木村 秀二                     |

|                    |                              | (72) 発明者    | 桃井 一隆<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社内   |

最終頁に続く

(54) 【発明の名称】集積回路チップの製造方法及び半導体装置

## (57) 【要約】

【課題】集積回路が形成された半導体領域の薄化に伴うチップ化又はパッケージングの困難性を緩和する。

【解決手段】集積回路チップの製造方法は、第1面及び第2面を有し、第1面側に集積回路を含む半導体領域120を有する半導体基板の前記第1面に第1支持部材150を結合させる第1結合工程と、第1支持部材150に結合された半導体基板の第2面側の部分を半導体領域120が残るように除去して半導体基板を薄化する薄化工程と、薄化後の半導体基板の第2面側に第2支持部材170を結合させる第2結合工程と、半導体領域120を切断してチップ化するチップ化工程とを含む。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

集積回路チップの製造方法であって、

第1面及び第2面を有し、前記第1面側に集積回路を含む半導体領域を有する半導体基板の前記第1面に第1支持部材を結合させる第1結合工程と、

前記第1支持部材に結合された前記半導体基板の前記第2面側の部分を前記半導体領域が残るように除去して前記半導体基板を薄化する薄化工程と、

薄化後の前記半導体基板の前記第2面側に第2支持部材を結合させる第2結合工程と、

前記半導体領域を切断してチップ化するチップ化工程と、

を含むことを特徴とする集積回路チップの製造方法。

10

**【請求項 2】**

前記チップ化工程を前記第2結合工程の後に実施することを特徴とする請求項1に記載の集積回路チップの製造方法。

**【請求項 3】**

前記チップ化工程の後に、チップ化された前記半導体領域から前記第1支持部材を剥離する剥離工程を更に含むことを特徴とする請求項2に記載の集積回路チップの製造方法。

**【請求項 4】**

前記チップ化工程では、前記半導体領域を前記第2支持部材と共に切断してチップ化することを特徴とする請求項3に記載の集積回路チップの製造方法。

**【請求項 5】**

前記チップ化工程では、前記半導体領域を前記第1支持部材及び前記第2支持部材と共に切断してチップ化することを特徴とする請求項3に記載の集積回路チップの製造方法。

**【請求項 6】**

前記第2結合工程の後であって前記チップ化工程の前に、前記第1支持部材、前記半導体領域及び前記第2支持部材が結合された結合体から前記第1支持部材を剥離する工程を更に含むことを特徴とする請求項2に記載の集積回路チップの製造方法。

**【請求項 7】**

前記チップ化工程では、前記半導体領域を前記第2支持部材と共に切断してチップ化することを特徴とする請求項6に記載の集積回路チップの製造方法。

**【請求項 8】**

前記チップ化工程を前記薄化工程の後であって前記第2結合工程の前に実施することを特徴とする請求項1に記載の集積回路チップの製造方法。

**【請求項 9】**

前記結合工程の後に、チップ化された前記半導体領域から前記第1支持部材を剥離する剥離工程を更に含むことを特徴とする請求項8に記載の集積回路チップの製造方法。

**【請求項 10】**

前記半導体基板は、前記半導体領域の下に分離層を有し、

前記薄化工程では、前記第1支持部材に結合された前記半導体基板を前記分離層を利用して分割することにより前記半導体基板の前記第2面側の部分を除去する、

ことを特徴とする請求項1乃至請求項9のいずれか1項に記載の集積回路チップの製造方法。

**【請求項 11】**

前記分離層は、陽極化成又はイオン注入によって形成されることを特徴とする請求項10に記載の集積回路チップの製造方法。

**【請求項 12】**

前記薄化工程で除去された部分を前記半導体基板の材料として再使用することを特徴とする請求項10又は請求項11に記載の集積回路チップの製造方法。

**【請求項 13】**

チップ化された半導体領域をパッケージングする工程を更に含むことを特徴とする請求項1乃至請求項12のいずれか1項に記載の集積回路チップの製造方法。

20

30

40

50

**【請求項 1 4】**

前記第1支持部材は、プラスチック、ガラス、セラミック、金属、半導体からなるグループから選択されるいすれかの材料で構成されていることを特徴とする請求項1乃至請求項13のいすれか1項に記載の集積回路チップの製造方法。

**【請求項 1 5】**

前記第2支持部材は、前記半導体基板よりも高い熱伝導率有する部材で構成されていることを特徴とする請求項1乃至請求項14のいすれか1項に記載の集積回路チップの製造方法。

**【請求項 1 6】**

前記第2結合工程では、薄化後の前記半導体領域と前記第2支持部材とを導電性を有する部材によって結合することを特徴とする請求項1乃至請求項15のいすれか1項に記載の集積回路チップの製造方法。

10

**【請求項 1 7】**

前記半導体領域は、シリコン、ゲルマニウム、化合物半導体からなるグループから選択されるいすれかの材料で構成されていることを特徴とする請求項1乃至請求項16のいすれか1項に記載の集積回路チップの製造方法。

**【請求項 1 8】**

前記第2支持部材は、光透過性部材であることを特徴とする請求項1乃至請求項14及び請求項17のいすれか1項に記載の集積回路チップの製造方法。

20

**【請求項 1 9】**

前記第2結合工程では、薄化後の前記半導体領域と前記第2支持部材とを光透過性を有する部材によって結合することを特徴とする請求項1乃至請求項18のいすれか1項に記載の集積回路チップの製造方法

**【請求項 2 0】**

半導体装置であって、

集積回路チップと、

前記集積回路の1つの面に結合された支持部材と、

をパッケージングして構成され、前記集積回路チップと前記支持部材とが略同一の大きさを有する、

ことを特徴とする半導体装置。

30

**【請求項 2 1】**

前記支持部材は、前記集積回路チップの基板よりも熱伝導率が高い部材であることを特徴とする請求項20に記載の半導体装置。

**【請求項 2 2】**

前記支持部材は、光透過性部材であることを特徴とする請求項20に記載の半導体装置。

**【請求項 2 3】**

前記集積回路チップ及び前記支持部材は、複数の集積回路チップを有する半導体基板と前記半導体基板に結合された支持部材とを共に切断して得られたものであることを特徴とする請求項20乃至請求項22のいすれか1項に記載の半導体装置。

40

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、集積回路チップの製造方法及び半導体装置に関する。

**【背景技術】****【0 0 0 2】**

近年、半導体デバイスを薄化する技術が注目されている。特許文献1には、第1基板に保護膜、保護絶縁層及び薄膜デバイス層を順に形成し、その薄膜デバイス層に接着剤を使って第2基板を貼り付けた後に第1基板をエッチングによって除去し、更に保護膜を除去して保護絶縁層を露出させ、その保護絶縁層に接着剤を使って保護基板を貼り付け、その

50

後、薄膜デバイス層の電極部分にフレキシブルケーブルに接続してアクティブマトリックス型有機エレクトロルミネッセンスディスプレイを製造することが開示されている。しかしながら、特許文献1は、ディスプレイとして使用される大面積の薄膜デバイス層を製造することを意図したものであり、保護基板を貼り付けて得られたパネルをチップ化することを意図したものではない。

特許文献2には、半絶縁性GaN基板上に分子線エピタキシャル法により半導体素子が形成された基板からエピタキシャルリフトオフ法によって半導体素子を分離し、その半導体素子を熱伝導率のよいダイヤモンド基板上に被着させる技術が開示されている。しかしながら、特許文献2は、ダイヤモンド基板上に被着させた半導体素子をチップ化することについては開示していない。

特許文献3には、半導体素子を備えた半導体膜を分離層上に形成した基板を支持部材に貼り合わせた後に、このようにして得られた部材を分離層を利用して分割し、その後に、半導体膜をチップ化する技術を開示している。

【特許文献1】特開2003-323132号公報

【特許文献2】特開2000-58562号公報

【特許文献3】特開2002-231909号公報

【発明の開示】

【発明が解決しようとする課題】

【0003】

柔軟性を向上させ、積層を可能にし、放熱性を高める観点において、半導体デバイスの薄膜化に対する要求が高まっている。しかしながら、一方で、半導体デバイスの薄化は、ダイシング時における半導体デバイスの破損をもたらし得るほか、ダイボンディング時におけるチップの保持を困難にし得る。

【0004】

本発明は、上記の課題認識を基礎としてなされたものであり、集積回路が形成された半導体領域の薄化に伴うチップ化又はパッケージングの困難性を緩和すること、より具体的には、例えば、ダイシングやダイボンディング等を容易化することを目的とする。

【課題を解決するための手段】

【0005】

本発明の第1の側面は、集積回路チップの製造方法に係り、前記製造方法が、第1面及び第2面を有し、前記第1面側に集積回路を含む半導体領域を有する半導体基板の前記第1面に第1支持部材を結合させる第1結合工程と、前記第1支持部材に結合された前記半導体基板の前記第2面側の部分を前記半導体領域が残るように除去して前記半導体基板を薄化する薄化工程と、薄化後の前記半導体基板の前記第2面側に第2支持部材を結合させる第2結合工程と、前記半導体領域を切断してチップ化するチップ化工程とを含むことを特徴とする。

【0006】

本発明の好適な実施形態によれば、前記チップ化工程は、前記第2結合工程の後に実施されうる。

ここで、前記製造方法は、前記チップ化工程の後に、チップ化された前記半導体領域から前記第1支持部材を剥離する剥離工程を更に含むことが好ましい。前記チップ化工程では、前記半導体領域を前記第2支持部材と共に切断してチップ化してもよいし、前記半導体領域を前記第1支持部材及び前記第2支持部材と共に切断してチップ化してもよい。

或いは、前記製造方法は、前記第2結合工程の後であって前記チップ化工程の前に、前記第1支持部材、前記半導体領域及び前記第2支持部材が結合された結合体から前記第1支持部材を剥離する工程を更に含んでもよい。ここで、前記チップ化工程では、前記半導体領域を前記第2支持部材と共に切断してチップ化することができる。

本発明の他の好適な実施形態によれば、前記チップ化工程は、前記薄化工程の後であって前記第2結合工程の前に実施されうる。ここで、前記製造方法は、前記結合工程の後に、チップ化された前記半導体領域から前記第1支持部材を剥離する剥離工程を更に含むこ

とが好ましい。

#### 【0007】

本発明の好適な実施形態によれば、前記半導体基板は、前記半導体領域の下に分離層を有し、前記薄化工程では、前記第1支持部材に結合された前記半導体基板を前記分離層を利用して分割することにより前記半導体基板の前記第2面側の部分を除去することが好ましい。ここで、前記分離層は、陽極化成又はイオン注入によって形成されることが好ましい。前記薄化工程で除去された部分は、前記半導体基板の材料として再使用することができる。

本発明の好適な実施形態によれば、前記製造方法は、チップ化された半導体領域をパッケージングする工程を更に含みうる。

10

#### 【0008】

本発明の好適な実施形態によれば、前記第1支持部材は、プラスチック、ガラス、セラミック、金属、半導体からなるグループから選択されるいづれかの材料で構成されることが好ましい。

本発明の好適な実施形態によれば、前記第2支持部材は、前記半導体基板よりも高い熱伝導率有する部材で構成されることが好ましい。

#### 【0009】

本発明の好適な実施形態によれば、前記第2結合工程では、薄化後の前記半導体領域と前記第2支持部材とを導電性を有する部材（例えば、半田）によって結合することが好ましい。

20

#### 【0010】

本発明の好適な実施形態によれば、前記半導体領域は、シリコン、ゲルマニウム、化合物半導体からなるグループから選択されるいづれかの材料で構成されることが好ましい。

本発明の好適な実施形態によれば、前記第2支持部材は、光透過性部材であってもよい。ここで、光という用語は、可視光に限定されるものではなく、赤外光や紫外光も含まれる。

#### 【0011】

本発明の好適な実施形態によれば、薄化後の前記半導体領域と前記第2支持部材とを光透過性を有する部材によって結合してもよい。

30

本発明の第2の側面は、半導体装置に係り、前記半導体装置が、集積回路チップと、前記集積回路の1つの面に結合された支持部材とをパッケージングして構成され、前記集積回路チップと前記支持部材とが略同一の大きさを有することを特徴とする。

#### 【0012】

本発明の好適な実施形態によれば、前記支持部材は、前記集積回路チップの基板よりも熱伝導率が高い部材であることが好ましい。

#### 【0013】

本発明の好適な実施形態によれば、前記支持部材は、光透過性部材であってもよい。ここで、光という用語は、可視光に限定されるものではなく、赤外光や紫外光も含まれる。

#### 【0014】

本発明の好適な実施形態によれば、前記集積回路チップ及び前記支持部材は、複数の集積回路チップを有する半導体基板と前記半導体基板に結合された支持部材とを共に切断して得られたものであることが好ましい。

40

#### 【発明の効果】

#### 【0015】

本発明によれば、集積回路が形成された半導体領域の薄化に伴うチップ化又はパッケージングの困難性を緩和すること、より具体的には、例えば、ダイシングやダイボンディング等を容易化することができる。

#### 【発明を実施するための最良の形態】

#### 【0016】

以下、添付図面を参照しながら本発明の好適な実施形態を説明する。

50

## 【0017】

半導体デバイスの高集積化及び高速化に伴って半導体デバイスからの発熱が非常に大きくなっている。発熱による半導体デバイスの高温化は、デバイス特性に著しい悪影響を与えるため、放熱性能の向上が求められる。放熱性能の向上は、半導体デバイスの薄化によって達成されるものの、半導体デバイスを単純に薄化するのみでは、ダイシング時において半導体デバイス又はチップが破損し得る他、ダイボンディング時においてチップの保持を困難にし得る。

## 【0018】

そこで、この実施形態では、半導体デバイスが形成された半導体層或いは半導体領域を第1支持部材で支持した状態で薄化することにより放熱特性を改善するとともに、該薄化された半導体層或いは半導体領域を第2支持部材で支持した状態で切断(分割)してチップ化することにより、半導体層或いは半導体領域の破損を防止する。更に、第2支持部材として熱放熱性に優れた部材を採用することにより、熱放熱性をより向上させることができる。第1支持部材は、半導体層或いは半導体領域の切断の前に剥離されてもよいし、切断の後に剥離されてもよい。

更に、半導体層或いは半導体領域の切断(分割)は、それが第1支持部材によってのみ支持された状態(すなわち、第2支持部材で支持される前の状態)でなされてもよく、この場合は、切断の後、第1支持部材が剥離される前に、切断によりチップ化された半導体層或いは半導体領域に貼り付けられ得る。

## [第1実施形態]

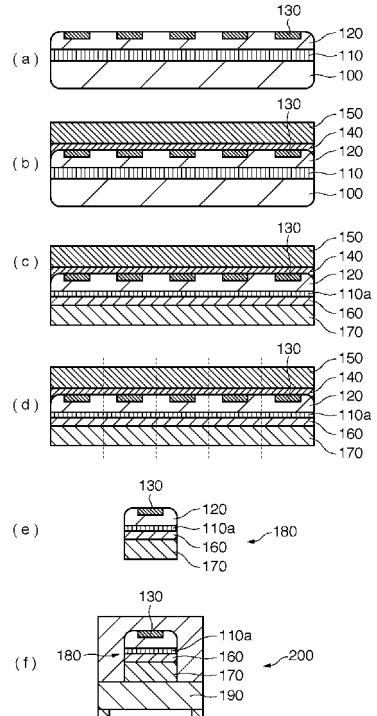

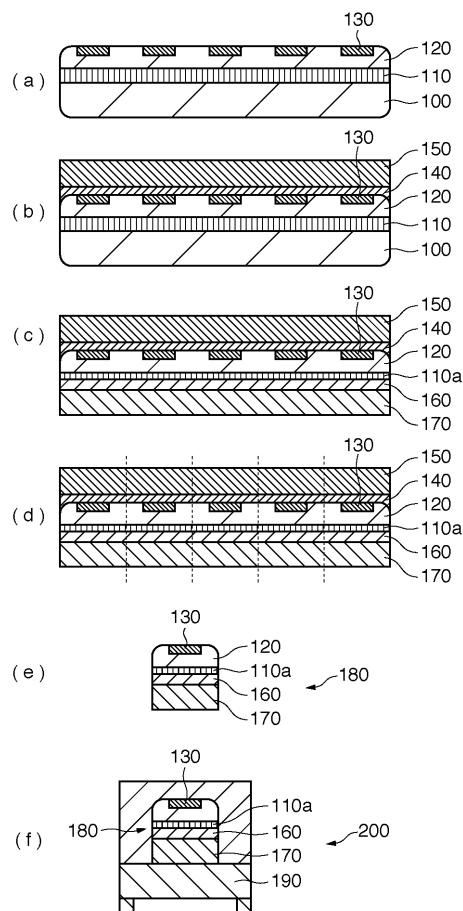

図1を参照しながら本発明の第1実施形態を説明する。

## 【0019】

まず、図1(a)に示す工程において、シード基板としての半導体基板100に分離層110及び半導体層(半導体領域)120を形成し、更に、半導体層120に半導体デバイスを含む集積回路130を形成する。

## 【0020】

具体的には、例えば、シード基板としてのシリコン基板(半導体基板)100に、分離層として多孔度の異なる2層からなる多孔質層110を陽極化成法により形成する。陽極化成の条件(例えば、電流条件)を変更することにより、多孔度の異なる2層の多孔質層110を形成することができる。多孔度の異なる2層構造の多孔質層110を形成することにより、2層の界面を後の分離工程における分離面として利用することができる。

陽極化成条件は、例えば、次のように決定することができる。

## 【0021】

半導体基板: P-基板、比抵抗 = 1.6 m · cm

陽極化成液: HF:IPA = 4.2.5:9.2 (wt. %)

電流条件(第1層の多孔質層): 5.12 A、150秒

電流条件(第2層の多孔質層): 9.2 A、60秒

ここで、半導体基板の比抵抗と不純物に制限はなく、分離層となる多孔質層を形成できる条件であれば、任意に設定することができる。ただし、次の工程でエピタキシャル成長法を適用する場合、良質なエピタキシャル成長層(半導体層)を形成するために、比抵抗が6~20 m · cmのP型基板を採用することが好ましく、比抵抗が1.4~1.7 m · cmのP型基板を採用することが更に好ましい。

## 【0022】

なお、多孔質層は、必ずしも2層構造とする必要はなく、単一層でもよいし、3層以上の多層構造でもよい。

更に、分離層としての多孔質層110が形成されたシリコン基板100を酸素雰囲気中で酸化処理し(例えば、400、1時間)、孔壁を熱酸化膜で覆うことが好ましい。続いて、多孔質層110の表面に希フッ酸(HF)水溶液を接触させ、孔の内壁の酸化膜を残して、多孔質層110の表面の酸化膜を除去することが好ましい。なお、この処理は、多孔質層の表面の酸化膜のみを除去できる方法であれば十分であり、例えば、希フッ酸水

10

20

30

40

50

溶液に変えてフッ酸（HF）蒸気を用いてもよい。

【0023】

続いて、水素含有雰囲気中でシリコン基板100をベークすることによって、多孔質層110の表面の孔を封止することが好ましい。

【0024】

続いて、多孔質層110上に単結晶シリコン層（半導体相）120をエピタキシャル成長させる。例えば、2μm厚の単結晶シリコン層120は、次の条件で成長させることができる。

【0025】

ソースガス：SiH<sub>2</sub>Cl<sub>2</sub> / H<sub>2</sub>

ガス流量：0.5 / 180 l/min

ガス圧力：80 Torr

温度：950

10

なお、エピタキシャル成長法としては、気相成長法のみならず、液相成長法を適用してもよい。また、半導体層120として、シリコン層に代えて、ゲルマニウム等の他の半導体層、又は、SiGe等の化合物半導体層を成長させてもよい。

【0026】

続いて、半導体層120に、リソグラフィー技術によって、マイクロプロセッサー、ロジックIC、メモリ等の集積回路130を形成する。集積回路を形成する工程は、バルク基板に集積回路を形成する工程と同様である。以上の工程により、図1(a)に模式的に示す基板が得られる。ここで、図1(a)に示す基板の半導体層120側の面を第1面、その反対側の面を第2面と呼ぶことにする。

20

【0027】

次いで、図1(b)に示す工程では、半導体層120に集積回路130が形成された半導体基板（図1(a)）を半導体層120側（第1面側）が内側になるようにして第1支持部材150と結合させる。この結合には、例えば、エポキシ接着剤等の接着剤140を用いることができる。

30

【0028】

第1支持部材150としては、例えば、プラスチック、ガラス、セラミック、金属、半導体等を採用することができ、要求される接着強度、使用可能な接着剤の種類、第1支持部材に要求される強度等に応じて適宜選択することができる。ここで、後の分離工程において、多孔質層中の分離面よりも先に接着面が剥れない方法が選択されるべきである。

30

【0029】

次いで、図1(c)に示す工程では、図1(b)に示す基板から多孔質層110中の分離面（多孔度の異なる2層の多孔質層の界面）を境（分離面）としてシード基板としてのシリコン基板100（第2面側の部分）を分離（除去）し、分離後の2枚の基板のうち半導体層120を有する基板の半導体層120側に第2支持部材170を貼り合わせる。

【0030】

シリコン基板100の分離（除去）には、流体を適用した分離方法が好適である。具体的には、多孔質層110中の分離面又はその近傍に水、アルコール等の液体、又は、空気、窒素等の気体を吹き付ける方法が好ましい。

40

【0031】

ここで、必要に応じて、集積回路130が形成された半導体層120に残存している多孔質層110aを除去しても良い。残存する多孔質層110aの除去方法としては、シリコンを酸化する薬液（例えば、過酸化水素水、硝酸とフッ酸との混合液）を使う方法や、機械的な研削方法が好適である。

【0032】

分離層としての多孔質層120を利用したシリコン基板100の除去方法は、シリコン基板100を材料基板として本製造方法において再使用が可能である点、シリコン基板100の除去を短時間で行うことができる点、半導体層120に対するダメージが小さい点

50

で優れている。再使用は、分離後のシリコン基板 110 を必要に応じて処理した後に、図 1 (a) を参照して説明して工程に提供することによりなされる。

分離後の 2 枚の基板のうち半導体層 120 を有する基板の半導体層 120 側 ( 第 2 面側 ) に第 2 支持部材 170 を結合させることにより、第 2 支持部材 170 / ( 残存多孔質層 110a ; 除去されない場合のみ ) / 半導体層 120 / 接着剤 140 / 第 1 支持部材 150 となる。

第 2 支持部材 170 は、高い熱伝導率を有する熱伝導部材 ( 例えば、シード基板としての半導体基板よりも高い熱伝導率を有する部材 ) であることが好ましい。また、貼り合わせにおいては、熱伝導性の良い接着剤 160 や、半田 ( 導電性部材 ) を用いてもよい。また、残存多孔質層 110a の孔壁に銅などをメッキし、高熱伝導板と貼り合わせることも好適である。

#### 【 0033 】

第 2 支持部材 170 に代えて LSI 用ヒートシンク等のヒートシンクを用いることも有用である。また、第 2 支持部材 170 にヒートシンクを結合することも有用である。高熱伝導板とヒートシンクを組み合わせて使用する場合、高熱伝導板は、半導体層 120 又は残存多孔質層 110a とヒートシンク ( 例えば、Cu 、 Al ) の両方と接着剤や半田 ( 導電性部材 ) を介して結合可能な材質が好ましく、金属、特に銅や金など、集積回路を構成する半導体材料よりも熱伝導率の高い材料であることが好ましい。

#### 【 0034 】

図 1 (c) に示す工程に次いで、図 1 (d) に示す工程では、第 2 支持部材 170 によって支持された半導体層 120 をダイシング ( 切断 ) して、図 1 (e) に模式的に示すような集積回路チップ 180 を得る。ここで、半導体層 120 の切断は、第 2 支持部材 170 と共になされてもよいし、第 1 支持部材 150 及び第 2 支持部材の双方と共になされてもよい。或いは、第 2 支持部材 170 として、半導体層 120 のチップサイズに応じてチップ化 ( 切断又は分離 ) された複数の部材を使用する場合には、半導体層 120 の切断の際は、半導体層 120 のみが切断されてもよいし、半導体層 120 及び第 1 支持部材 150 のみが切断されてもよい。

集積回路チップ 180 は、チップ化された半導体層 120 と、該チップ化された半導体層 120 と略同一直径にチップ化された第 2 支持部材 170 を含む。

#### 【 0035 】

従来は、半導体層がエピタキシャル成長分の厚み程度しかなく非常に薄かった。このために、ダイシング時に半導体層が破損してしまう問題や、ダイボンディングの際にチップを保持することが難しいという問題があった。一方、この実施形態によれば、ダイシングに先立って高熱伝導板等の第 2 支持部材 170 によって半導体層 120 を支持するために、ダイシングに対しても充分な強度を有し、かつ、ダイボンディング時のチップの保持が容易である。

#### 【 0036 】

次いで、図 1 (f) に示す工程では、集積回路チップ 180 をパッケージングする。ここで、パッケージングにおいては、第 2 支持部材 170 としての高熱伝導板とパッケージ台 190 とを接着し、更に集積回路 130 とパッケージ台 190 のリードフレームとをワイヤーボンディングする。

#### 【 0037 】

典型的には、パッケージングに先立ってチップ 180 又は半導体層 120 から第 1 支持部材 150 が除去され得る。チップ 180 又は半導体層 120 からの第 1 支持部材 150 の除去は、半導体層 120 に第 2 支持部材 170 を結合させた後であれば、ダイシング ( 切断 ) の前でも後でもよいが、ダイシングの後の方が好ましい。ダイシング後にチップ 180 から第 1 支持部材 150 を除去する方法によれば、接着面積が小さいため、小さい力でチップ 180 から第 1 支持部材 150 を剥がすことができる。

チップ 180 又は半導体層 120 から第 1 支持部材 150 を剥がす方法は、チップ又は基板全体を接着剤の剥離液 ( 有機溶剤 ) の中に浸漬する方法が好適であるが、第 1 支持部材 150 の剥離は、剥離液に半導体層 120 の接着剤が付着する場合、剥離液による半導体層 120 の剥離による半導体層 120 の損傷を防ぐため、剥離液の濃度を適度に設定する。

10

20

30

40

50

材を機械的に研削する方法や、熱応力の違いを利用して第1支持部材を剥がす方法でもよい。

#### 【0038】

以上の工程によって得られる図1(f)に模式的に示す集積回路チップ180は、従来のバルクシリコン基板を用いた集積回路チップと比較して厚さが数百分の一であるため、放熱特性が格段に優れている。また、半導体層を第2支持部材で支持した状態で半導体層をチップ化(分割)することにより、ダイシング等の処理時における半導体層の破損を防止することができ、更に、第2支持部材として熱放熱性に優れた部材を採用することにより、熱放熱性をより向上させることができる。更に、チップ化された半導体層をチップ化された第2支持部材が支持されることにより、ダイボンディング時における集積回路チップの保持が容易になる。

上記の実施形態では、半導体層120に第2支持部材を結合させた後に半導体層120の切断を実施するが、これに代えて、第1支持部材150に結合させた半導体層120を切断してチップ化した後に、チップ化された半導体層120に第2支持部材170を結合させて、その後に、チップ化された半導体層120から第1支持部材150を剥離してもよい。このような方法においては、半導体層120は、半導体層120が第1支持部材150によって支持された状態で切断されるので、切断の際に半導体層120に与えられるダメージを低減することができる。また、チップ化された半導体層120から第1支持部材150が剥離される前に半導体層120に第2支持部材170が結合されるので、チップ化された半導体層120を衝撃等から保護することができ、例えば、ダイボンディング時におけるチップ化された半導体層120の保持を容易にすることができます。

チップ化された半導体層120への第2支持部材170の結合に際にしては、チップサイズに切断された第2支持部材170をチップ化された半導体層120の各チップに結合させてもよいし、切断されていない第2支持部材170をチップ化された半導体層120に結合させた後に第2支持部材170をチップサイズに切断してもよい。

#### 【0039】

また、半導体層120のチップ化の際は、半導体層120と共に第1支持部材150も切断してもよいが、第1支持部材150を切断することなく半導体層120のみを切断してもよい。

#### 【0040】

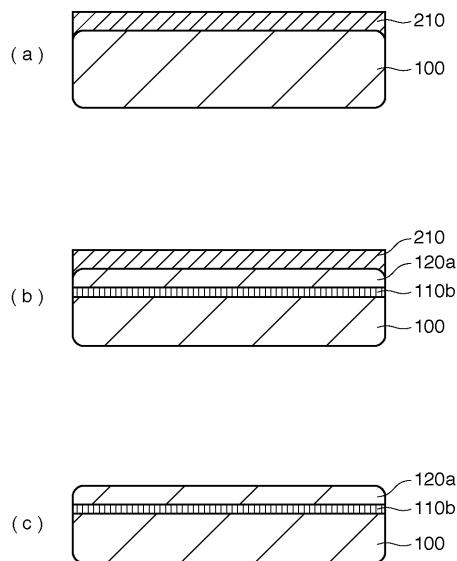

##### [第2実施形態]

この実施形態は、第1の実施形態における分離層の形成方法を変更するものである。

まず、図2(a)に示す工程において、シード基板としてのシリコン基板(半導体基板)100に保護膜210として絶縁層(例えば、 $SiO_2$ 層)等を形成し、図2(b)に示す工程において、シリコン基板100に水素イオン等のイオンを注入することにより、シリコン基板100の表面から所定深さの領域に分離層(イオン注入層)110bとしてのイオン注入層を形成する。水素イオンの注入量は、例えば、 $10^{16} \sim 10^{17}$ (atoms/cm<sup>2</sup>)のオーダーとすることができます。

その後、図2(c)に示す工程において、保護膜210を除去する。これにより、分離層110b上に半導体層120aを有する基板を形成することができる。このようにして得られる基板を図1(b)～(f)に示す工程に提供することにより、第1実施形態と同様に、薄化された半導体層を有する集積回路チップを形成することができる。

なお、イオン注入に先立って実施される保護膜の形成工程は必須ではなく、シード基板(半導体基板)100に保護膜を形成することなくイオンを注入して分離層を形成してもよい。

#### 【0041】

##### [第3実施形態]

この実施形態は、分離層を利用することなくシード基板を除去する方法とともに光カーボの製造方法を提供する。

#### 【0042】

10

20

30

40

50

まず、シード基板としてのシリコン基板上に、例えば受光素子及び增幅回路を含む集積回路を形成し、その後、そのシリコン基板に対して集積回路側（第1面側）が内側になるように第1支持部材を結合させる。

【0043】

次いで、集積回路を含む領域として所定厚さ（例えば、50 μm）の半導体層（半導体領域）が残るように、グラインダーによる研削と研磨により、シリコン基板を裏面（第2面側）から薄化する。

次いで、得られた基板の集積回路側（第2面側）に第2支持部材としての光透過性基板（石英基板）を結合させる。この際、熱処理（例えば、400℃、1時間）を施すことによって結合強度を高めることが好ましい。

【0044】

ここで、光透過性基板は、石英に限定されるものではなく、光透過性を有する基板であれば、その材料は特に限定されず、例えば、ガラス等であってもよい。光透過性基板としては、例えば、シード基板としての半導体基板よりも光透過性が高い基板を採用し得る。

【0045】

次いで、基板をダイシングし、配線した後に、プラスチックを用いてパッケージングを行うことで、透明な光カード（光透過部を有するカード）を得ることができる。

また、第1実施形態においても、第2支持部材として光透過性の部材を採用するとともに光透過部を有するカード又はパッケージを製造することができる。

【図面の簡単な説明】

【0046】

【図1】半導体チップを製造する方法を模式的に説明する図である。

【図2】分離層の形成方法の他の例を説明する図である。

【図1】

【図2】

## フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 01 L 21/78

P

(72)発明者 佐藤 信彦

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内