(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-526748

(P2016-526748A)

(43) 公表日 平成28年9月5日(2016.9.5)

(51) Int.Cl.

G 11 C 11/406 (2006.01)

F 1

G 11 C 11/34

3 6 3 G

テーマコード(参考)

5MO24

審査請求 未請求 予備審査請求 未請求 (全 19 頁)

(21) 出願番号 特願2016-521410 (P2016-521410)

(86) (22) 出願日 平成26年5月5日 (2014.5.5)

(85) 翻訳文提出日 平成27年12月17日 (2015.12.17)

(86) 國際出願番号 PCT/US2014/036858

(87) 國際公開番号 WO2014/209498

(87) 國際公開日 平成26年12月31日 (2014.12.31)

(31) 優先権主張番号 61/838,435

(32) 優先日 平成25年6月24日 (2013.6.24)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 14/242,769

(32) 優先日 平成26年4月1日 (2014.4.1)

(33) 優先権主張国 米国(US)

(71) 出願人 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サン デイエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ジュン・ピル・キム

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】弱保持時間有するメモリセルのためのリフレッシュ方式

## (57) 【要約】

メモリコントローラ内のメモリリフレッシュ方法は、第1のメモリアドレスに対応する第1の保持状態と、第2のメモリアドレスに対応する第2の保持状態とを検査するステップを含む。メモリリフレッシュ方法はまた、第2の保持状態が弱保持状態を示すとき、第2のメモリアドレスに対応する行に対してリフレッシュ動作を実行するステップを含む。第1のメモリアドレスは、リフレッシュカウンタアドレスに対応し、第2のメモリアドレスは、リフレッシュカウンタアドレスの相補アドレスに対応する。

FIG. 5

**【特許請求の範囲】****【請求項 1】**

メモリコントローラ内のメモリリフレッシュ方法であって、

第1のメモリアドレスに対応する第1の保持状態と、第2のメモリアドレスに対応する第2の保持状態とを検査するステップと、

前記第2の保持状態が弱保持状態を示すとき、前記第2のメモリアドレスに対応する行に対してリフレッシュ動作を実行するステップであって、前記第1のメモリアドレスが、リフレッシュカウンタアドレスに対応し、前記第2のメモリアドレスが、前記リフレッシュカウンタアドレスの相補アドレスに対応する、ステップと

を含む、メモリリフレッシュ方法。

10

**【請求項 2】**

前記第2のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行するステップの後に、前記第1のメモリアドレスに対応する行に対してリフレッシュ動作を実行するステップと、

前記第2のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行するステップの前に、前記第1のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行するステップと

をさらに含む、請求項1に記載のメモリリフレッシュ方法。

**【請求項 3】**

前記第1の保持状態を検査するステップが、ワンタイムプログラマブルメモリから前記第1のメモリアドレスの前記第1の保持状態と前記第2のメモリアドレスの前記第2の保持状態とを読み取るステップを含む、請求項1に記載のメモリリフレッシュ方法。

20

**【請求項 4】**

前記ワンタイムプログラマブルメモリが、各メモリアドレスとそれぞれの各メモリアドレスに対応する保持状態とを含む、請求項3に記載のメモリリフレッシュ方法。

**【請求項 5】**

前記ワンタイムプログラマブルメモリが、前記弱保持状態を有する各メモリアドレスを含む、請求項3に記載のメモリリフレッシュ方法。

**【請求項 6】**

前記第1の保持状態を検査するステップが、弱行表から前記第1のメモリアドレスをもつヒットが検出されたのか、または前記第2のメモリアドレスをもつヒットが検出されたのかを決定するステップを含む、請求項1に記載のメモリリフレッシュ方法。

30

**【請求項 7】**

前記第2のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行するステップと同時に、前記第1のメモリアドレスに対応する行に対して前記リフレッシュ動作を実行するステップをさらに含む、請求項1に記載のメモリリフレッシュ方法。

**【請求項 8】**

前記第2のメモリアドレスに対応する第2の複数の内部行からの内部弱行に対して前記リフレッシュ動作を実行するステップと同時に、前記第1のメモリアドレスに対応する第1の複数の内部行に対して前記リフレッシュ動作を実行するステップをさらに含み、前記内部弱行が、前記第2の保持状態によって識別される、請求項1に記載のメモリリフレッシュ方法。

40

**【請求項 9】**

前記第1のメモリアドレスが、前記リフレッシュカウンタアドレスに対応し、前記第2のメモリアドレスが、相補最上位ビットをもつ前記リフレッシュカウンタアドレスに対応する、請求項1に記載のメモリリフレッシュ方法。

**【請求項 10】**

前記メモリリフレッシュ方法が、行アドレスストア(RAS)リフレッシュサイクル中に実行される、請求項1に記載のメモリリフレッシュ方法。

**【請求項 11】**

50

前記メモリコントローラが、携帯電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニットおよび/または固定ロケーションデータユニット中に組み込まれる、請求項1に記載のメモリリフレッシュ方法。

【請求項12】

ダイナミックメモリと、

前記ダイナミックメモリに結合されたリフレッシュ制御ブロックとを含むメモリコントローラであって、前記リフレッシュ制御ブロックが、リフレッシュカウンタと、保持状態表と、制御論理手段とを含み、前記制御論理手段が、

前記保持状態表からの第1のメモリアドレスに対応する第1の保持状態と、前記保持状態表からの第2のメモリアドレスに対応する第2の保持状態とを検査することと、

前記第2の保持状態が弱保持状態を示すとき、リフレッシュ動作を挿入することであって、前記第1のメモリアドレスが、リフレッシュカウンタアドレスに対応し、前記第2のメモリアドレスが、前記リフレッシュカウンタアドレスの相補アドレスに対応する、挿入することと

を行うように動作可能である、メモリコントローラ。

【請求項13】

前記保持状態表が、各メモリアドレスとそれぞれの各メモリアドレスに対応する保持状態とを含むワンタイムプログラマブルメモリを含む、請求項12に記載のメモリコントローラ。

【請求項14】

前記保持状態表が、前記弱保持状態を有する各メモリアドレスを含むワンタイムプログラマブルメモリを含む、請求項12に記載のメモリコントローラ。

【請求項15】

前記制御論理手段が、

前記第2のメモリアドレスに対応する前記行に対する前記リフレッシュ動作の後に、前記第1のメモリアドレスに対応する行に対してリフレッシュ動作を実行することと、

前記第2のメモリアドレスに対応する前記行に対する前記リフレッシュ動作の前に、前記第1のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行することと、

前記第2のメモリアドレスに対応する前記行に対する前記リフレッシュ動作と同時に、前記第1のメモリアドレスに対応する行に対して前記リフレッシュ動作を実行することと

を行うようにさらに動作可能である、請求項12に記載のメモリコントローラ。

【請求項16】

前記制御論理手段が、前記第2のメモリアドレスに対応する第2の複数の内部行からの内部弱行に対して前記リフレッシュ動作を実行することと同時に、前記第1のメモリアドレスに対応する第1の複数の内部行に対して前記リフレッシュ動作を実行するようにさらに動作可能であり、前記内部弱行が、前記第2の保持状態によって識別される、請求項12に記載のメモリコントローラ。

【請求項17】

前記第1のメモリアドレスが、前記リフレッシュカウンタアドレスに対応し、前記第2のメモリアドレスが、相補最上位ビットをもつ前記リフレッシュカウンタアドレスに対応する、請求項12に記載のメモリコントローラ。

【請求項18】

前記メモリコントローラが、携帯電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニットおよび/または固定ロケーションデータユニット中に組み込まれる、請求項12に記載のメモリコントローラ。

10

20

30

40

50

**【請求項 19】**

ダイナミックメモリと、

前記ダイナミックメモリに結合されたリフレッシュ制御ブロックとを含むメモリコントローラであって、前記リフレッシュ制御ブロックが、リフレッシュカウンタと、保持状態表と、制御論理手段とを含み、前記リフレッシュ制御ブロックが、

前記リフレッシュカウンタからの第1のメモリアドレスに対応する第1の保持状態と、前記保持状態表からの第2のメモリアドレスに対応する第2の保持状態とを検査するための手段と、

前記第2の保持状態が弱保持状態を示すとき、前記第2のメモリアドレスに対応する行に対してリフレッシュ動作を実行するための手段と

を含む、メモリコントローラ。

**【請求項 20】**

前記メモリコントローラが、

前記第2のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行した後に、前記第1のメモリアドレスに対応する行に対してリフレッシュ動作を実行するための手段と、

前記第2のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行する前に、前記第1のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行するための手段と

をさらに含む、請求項19に記載のメモリコントローラ。

**【請求項 21】**

前記メモリコントローラが、前記第2のメモリアドレスに対応する前記行に対して前記リフレッシュ動作を実行するための手段と同時に、前記第1のメモリアドレスに対応する行に対して前記リフレッシュ動作を実行するための手段をさらに含む、請求項19に記載のメモリコントローラ。

**【請求項 22】**

前記メモリコントローラが、前記第2のメモリアドレスに対応する第2の複数の内部行からの内部弱行に対して前記リフレッシュ動作を実行するための手段と同時に、前記第1のメモリアドレスに対応する第1の複数の内部行に対して前記リフレッシュ動作を実行するための手段をさらに含み、前記内部弱行が、前記第2の保持状態によって識別される、請求項19に記載のメモリコントローラ。

**【請求項 23】**

前記保持状態表が、各メモリアドレスとそれぞれの各メモリアドレスに対応する保持状態とを含むワンタイムプログラマブルメモリを含む、請求項19に記載のメモリコントローラ。

**【請求項 24】**

前記保持状態表が、前記弱保持状態を有する各メモリアドレスを含むワンタイムプログラマブルメモリを含む、請求項19に記載のメモリコントローラ。

**【請求項 25】**

前記第1のメモリアドレスが、リフレッシュカウンタアドレスに対応し、前記第2のメモリアドレスが、相補最上位ビットをもつ前記リフレッシュカウンタアドレスに対応する、請求項19に記載のメモリコントローラ。

**【請求項 26】**

前記メモリコントローラが、携帯電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニットおよび/または固定ロケーションデータユニット中に組み込まれる、請求項19に記載のメモリコントローラ。

**【請求項 27】**

メモリコントローラ内のメモリリフレッシュ方法であって、

10

20

30

40

50

第1のメモリアドレスに対応する第1の保持状態と、第2のメモリアドレスに対応する第2の保持状態とをテストするステップと、

前記第2の保持状態が弱保持状態を示すとき、前記第2のメモリアドレスに対応する行に対してリフレッシュ動作を実行するステップと

を含む、メモリリフレッシュ方法。

#### 【請求項 28】

前記メモリコントローラが、携帯電話、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、エンターテインメントユニット、ナビゲーションデバイス、コンピュータ、ハンドヘルドパーソナル通信システム(PCS)ユニット、ポータブルデータユニットおよび/または固定ロケーションデータユニット中に組み込まれる、請求項27に記載のメモリリフレッシュ方法。

10

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

#### 関連出願の相互参照

本出願は、Jung Pill Kimらの名義で2013年6月24日に出願された、米国仮特許出願第61/838,435号の利益を主張し、上記の仮出願の開示は、参照により全体が本明細書に明示的に組み込まれる。

#### 【0002】

本開示は、電子メモリ動作に関し、より詳細には、弱保持時間(weak retention time)を有するメモリセルのためのリフレッシュ方式に関する。

20

#### 【背景技術】

#### 【0003】

半導体メモリデバイスは、たとえば、スタティックランダムアクセスメモリ(SRAM)および動的ランダムアクセスメモリ(DRAM)を含む。DRAMメモリセルは概して、1つのトランジスタと1つのキャパシタとを含み、これにより、高度な統合が可能になる。キャパシタは、対応するビット値(たとえば、「0」または「1」)として情報を記憶するために荷電されるか、あるいは放電され得る。キャパシタは電荷を漏電するので、記憶された情報は、キャパシタ電荷が周期的にリフレッシュされない限り、最終的に減衰する。リフレッシュ要件により、DRAMは、SRAMおよび他のスタティックメモリとは対照的にダイナミックメモリと呼ばれる。DRAMの連続的なリフレッシュは、概して、その使用をコンピュータメインメモリに限定する。

30

#### 【0004】

DRAMスケーリングは、DRAMチップごとのビット総数を増加させ続け、セルの値を可読に保つプロセスであるDRAMリフレッシュの仕様に直接影響を及ぼす。DRAMリフレッシュの仕様は、リフレッシュコマンドが各DRAMに送られる間隔(tREFI)と、リフレッシュコマンドがDRAMインターフェースを占有する時間量(tRFC)とを含む。残念ながら、DRAMスケーリングは、弱保持セル(たとえば、保持時間が低減されたセル)の数を増加させる。そのようなセルは、記憶された情報を維持するために追加のリフレッシュサイクルを伴う。チップまたは他の同様のコンピューターアーキテクチャ上のシステムにおけるリフレッシュサイクルの増加により、顕著なパフォーマンスおよび電力消費量影響が生じる。そうでない場合、リフレッシュサイクルの増加なしに潜在的なDRAMチップ歩留まり損失が生じる。

40

#### 【発明の概要】

#### 【課題を解決するための手段】

#### 【0005】

本開示の一態様によれば、メモリコントローラ内のメモリリフレッシュ方法は、第1のメモリアドレスに対応する第1の保持状態と、第2のメモリアドレスに対応する第2の保持状態と検査するステップを含む。本方法はまた、第2の保持状態が弱保持状態を示すとき、第2のメモリアドレスに対応する行に対してリフレッシュ動作を実行するステップを含む。第1のメモリアドレスは、リフレッシュカウンタドレスに対応し、第2のメモリアド

50

レスは、リフレッシュカウンタアドレスの相補アドレスに対応する。

【0006】

本開示の別の態様によれば、メモリコントローラは、ダイナミックメモリとダイナミックメモリに結合されたリフレッシュ制御ブロックとを含む。リフレッシュ制御ブロックは、リフレッシュカウンタと、保持状態表と、制御論理とを含む。制御論理は、保持状態表からの第1のメモリアドレスに対応する第1の保持状態と、保持状態表からの第2のメモリアドレスに対応する第2の保持状態とを検査する。制御論理はまた、第2の保持状態が弱保持状態を示すとき、リフレッシュ動作を挿入する。第1のメモリアドレスは、リフレッシュカウンタアドレスに対応し、第2のメモリアドレスは、リフレッシュカウンタアドレスの相補アドレスに対応する。

10

【0007】

本開示の別の態様によれば、メモリコントローラは、ダイナミックメモリとダイナミックメモリに結合されたリフレッシュ制御ブロックとを含む。リフレッシュ制御ブロックは、リフレッシュカウンタと、保持状態表と、制御論理とを含む。制御論理は、リフレッシュカウンタからの第1のメモリアドレスに対応する第1の保持状態と、保持状態表からの第2のメモリアドレスに対応する第2の保持状態とを検査するための手段を含む。制御論理はまた、第2の保持状態が弱保持状態を示すとき、第2のメモリアドレスに対応する行に対してリフレッシュ動作を実行するための手段を含む。

20

【0008】

上記は、続く詳細な説明がより良く理解され得るように、本開示の特徴および技術的な利点を、かなり広く概説したものである。本開示のさらなる特徴および利点について以下で説明する。本開示と同じ目的を実行するための他の構造を修正または設計するための基礎として、本開示が容易に利用され得ることを当業者は諒解されたい。そのような均等な構成は、添付の特許請求の範囲に記載される本開示の教示から逸脱しないことも当業者は認識されたい。本開示の特色をなすと思われる新規の特徴は、その組成と動作方法の両方について、さらなる目的および利点とともに、後続の記述を添付の図との関連で考慮したときによりよく理解されるであろう。しかしながら、図の各々は、例示および説明のみを目的として提供され、本開示の限定を定義するものとして意図されないことを明白に理解されたい。

30

【0009】

本開示のより完全な理解のために、ここで、添付の図面と併せて以下の説明を参照する。

【図面の簡単な説明】

【0010】

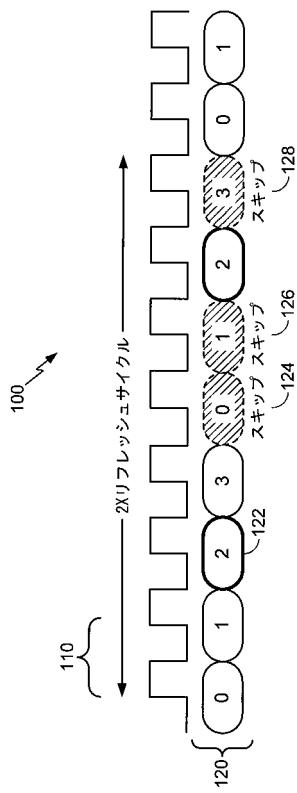

【図1A】本開示の態様による、他のメモリセルのためのリフレッシュ頻度を維持しながら、弱保持状態をもつメモリセルのリフレッシュ頻度を増加させるための技法を示す回路タイミング図である。

40

【図1B】本開示の態様による、他のメモリセルのためのリフレッシュ頻度を維持しながら、弱保持状態をもつメモリセルのリフレッシュ頻度を増加させるための技法を示す回路タイミング図である。

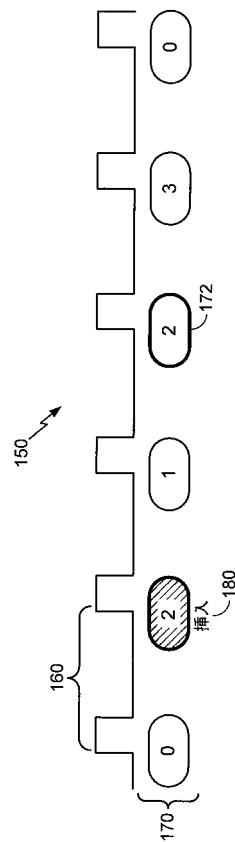

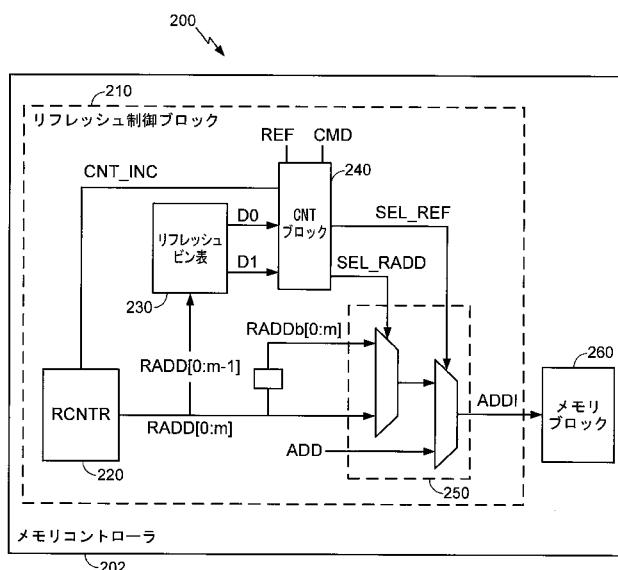

【図2A】本開示の一態様による、リフレッシュ制御ブロックを含むメモリコントローラを示すブロック図である。

【図2B】本開示の一態様による、それぞれの各メモリアドレスに対応する保持状態を与えるためのリフレッシュ表である。

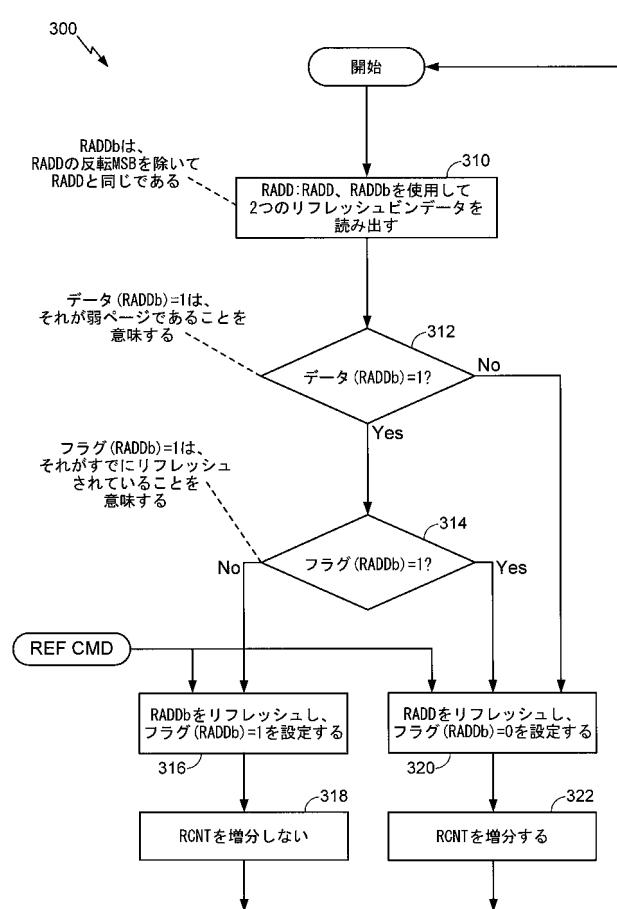

【図3】本開示の一態様による、弱保持状態をもつメモリセルのためのリフレッシュ方式を示すフローチャートである。

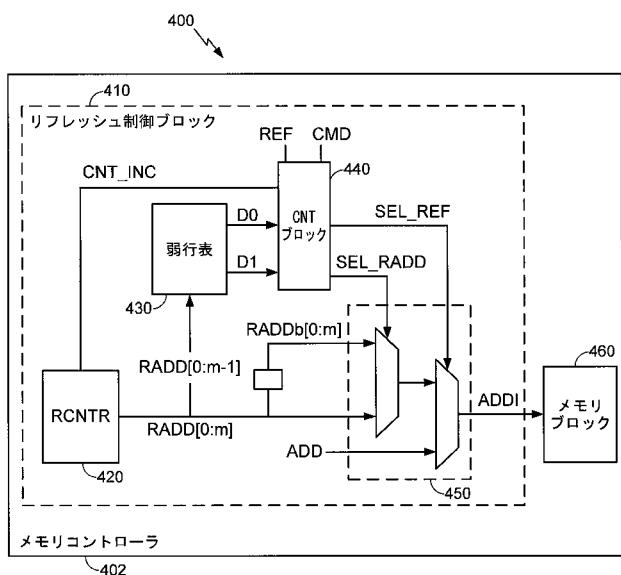

【図4A】本開示の別の態様による、リフレッシュ制御ブロックを含むメモリコントローラを示すブロック図である。

50

【図4B】本開示の一態様による、弱保持状態を有するメモリアドレスを与えるためのリフレッシュ表である。

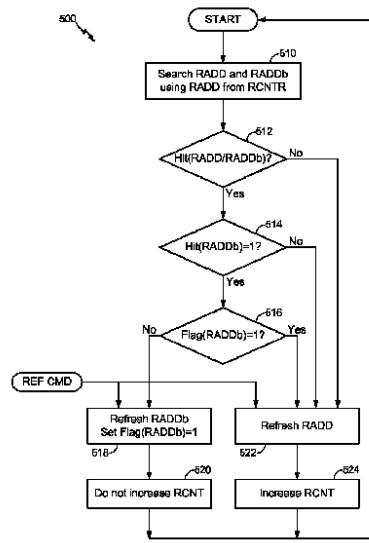

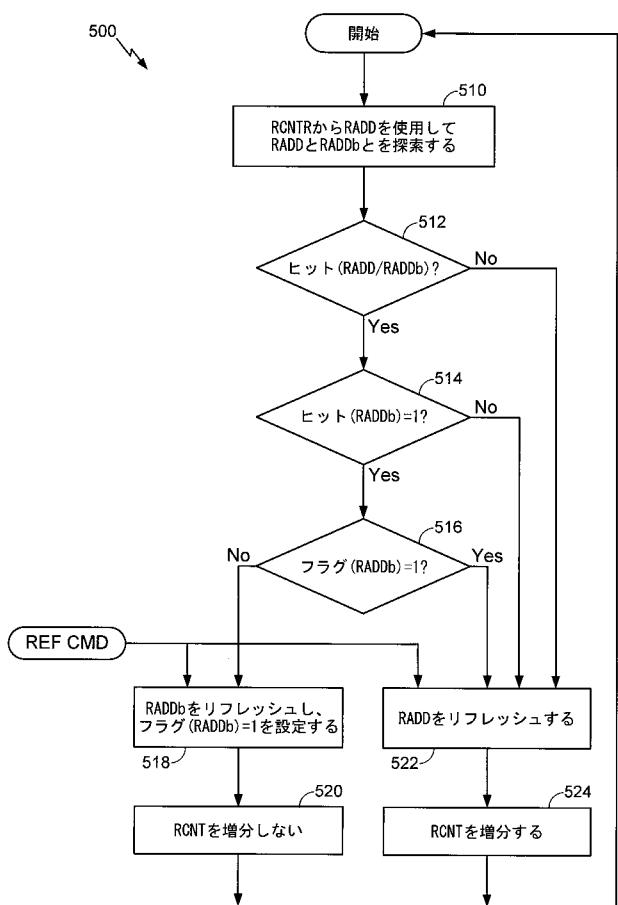

【図5】本開示の別の態様による、弱保持状態をもつメモリセルのためのリフレッシュ方式を示すフローチャートである。

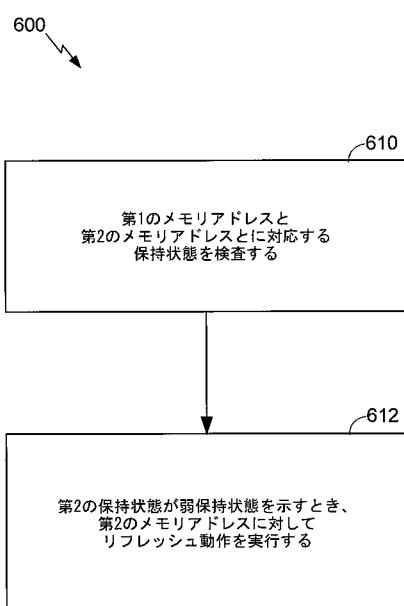

【図6】本開示の一態様による、弱保持状態をもつメモリセルをリフレッシュするための方法を示すフローチャートである。

【図7A】本開示の態様による、他のメモリセルのためのリフレッシュ頻度を維持しながら、弱保持状態をもつメモリセルのリフレッシュ頻度を増加させるための技法を示す回路タイミング図である。

【図7B】本開示の一態様による、リフレッシュ表である。

【図8】本開示の一態様による、それぞれの各メモリアドレスに対応する保持状態を与えるためのリフレッシュ表である。

【図9】本開示の態様を有利に用いることができる例示的なワイヤレス通信システムを示すブロック図である。

【発明を実施するための形態】

【0011】

添付の図面に関して下記に記載される発明を実施するための形態は、様々な構成の説明として意図されており、本明細書に記載される概念が実践され得る唯一の構成を表すことは意図されていない。詳細な説明は、様々な概念の完全な理解を与えるための具体的な詳細を含む。しかしながら、これらの概念はこれらの具体的な詳細がなくても実行され得ることが、当業者には明らかであろう。場合によっては、そのような概念を曖昧にするのを回避するために、よく知られている構造および構成要素がブロック図の形式で示されている。本明細書の説明では、「および/または」という用語の使用は、「包含的論理和」を表すことを意図し、「または」という用語の使用は、「排他的論理和」を表すことを意図する。

【0012】

ダイナミックランダムアクセスメモリ(DRAM)スケーリングは、DRAMチップ当たりのビット総数を増加させ続けている。容量のこの増加は、ビットセルの値が可読に保たれるプロセスであるDRAMリフレッシュの仕様に直接影響を及ぼす。DRAMリフレッシュの仕様は、リフレッシュコマンドが各DRAMに送られる間隔( $t_{REFI}$ )と、リフレッシュコマンドがDRAMインターフェースを占有する時間量( $t_{RFC}$ )とを含む。残念ながら、DRAMスケーリングはまた、弱保持セル(たとえば、保持時間が低減されたセル)の数を増加させる。そのようなセルは、記憶された情報を維持するために増加されたリフレッシュサイクルを伴う。パフォーマンスおよび電力消費量は、チップ(SoC)または他の同様のコンピューターアーキテクチャ上のシステムにおけるDRAM上のリフレッシュサイクルの増加により顕著な影響を及ぼされる。弱保持セルの数の増加からの潜在的なDRAMチップ歩留まり損失がリフレッシュサイクルの増加なしに生じる。

【0013】

本開示の一態様は、リフレッシュ期間(たとえば、リフレッシュ間隔 $t_{REFI}$ )の名目増加に伴って、弱保持状態をもつセルのためのリフレッシュサイクルを挿入する。一構成では、リフレッシュ制御ブロックは、第1のメモリアドレスに対応する第1の保持状態と、第2のメモリアドレスに対応する第2の保持状態とをテストする。この構成では、第1のメモリアドレスは、リフレッシュカウンタアドレスに対応し、第2のメモリアドレスは、リフレッシュカウンタアドレスの相補アドレス(たとえば、反転最上位ビット(MSB)をもつリフレッシュカウンタアドレス)である。動作中、第2のメモリアドレスの保持状態が弱保持状態を示すとき、第2のメモリアドレスに対してリフレッシュ動作が実行される。第2のメモリアドレスに対するリフレッシュ動作は、第1のメモリアドレスに対するリフレッシュ動作の前に、その後に、またはそれと同時に実行され得る。

【0014】

図1Aおよび図1Bに、本開示の態様による、他のメモリセルのためのリフレッシュ頻度を維持しながら、弱保持状態をもつメモリセル(たとえば、行)のリフレッシュ頻度を増加させるための技法を示す回路タイミング図を示す。図1Aに、リフレッシュアドレス120に対

10

20

30

40

50

してリフレッシュ動作を実行するためのダブルリフレッシュサイクル110をもつタイミング図100を示す。ダブルリフレッシュサイクル110は、たとえば、32マイクロ秒(μs)のリフレッシュ仕様の場合、16マイクロ秒(μs)になり得る。この例では、弱保持状態を有するリフレッシュアドレス122をもつ4行のメモリがある。典型的に、リフレッシュアドレス0、1、2および3に対してリフレッシュ動作が実行される。ただし、この例では、後続のバス中でリフレッシュアドレス124と、リフレッシュアドレス126と、リフレッシュアドレス128とに対するリフレッシュ動作がスキップされる。図1Aに示すように、通常保持状態をもつリフレッシュアドレスのためのリフレッシュサイクルをスキップしながら、弱保持状態を有するリフレッシュアドレス122のためのリフレッシュサイクルが倍化される。

【0015】

10

図1Bに、リフレッシュアドレス170に対してリフレッシュ動作を実行するためにシングルリフレッシュサイクル160を用いるタイミング図150を示す。シングルリフレッシュサイクル160は、たとえば、32マイクロ秒(μs)になり得る。この例では、同じく、弱保持状態を有するリフレッシュアドレス172をもつ4行のメモリがある。典型的に、弱保持状態をもつリフレッシュアドレス172に対して挿入リフレッシュ動作180が実行される。この例では、弱行リフレッシュサイクルが挿入される。図1Bに示すように、通常保持状態をもつリフレッシュアドレスのためのリフレッシュサイクルの名目増加のみに伴って、弱保持状態をもつリフレッシュアドレス172ためだけのリフレッシュサイクルが倍化される。

【0016】

20

図2Aは、本開示の一態様による、リフレッシュ制御ブロック210を含むメモリコントローラ202を示すブロック図200である。この構成では、リフレッシュ制御ブロック210は、リフレッシュカウンタ220と、リフレッシュビン表230と、カウンタブロック240と、リフレッシュ制御論理250とを含む。一構成では、リフレッシュビン表230は、各メモリアドレスに対応する保持状態を記憶するために使用される。この構成では、リフレッシュビン表230は、シングルリフレッシュカウンタアドレス(RADD)と相補リフレッシュカウンタアドレス(RADD<sub>b</sub>)とを使用して2つのリフレッシュビンテーブルエントリへのアクセスを可能にする。この例では、相補リフレッシュカウンタアドレスRADD<sub>b</sub>は、反転最上位ビット(MSB)をもつリフレッシュカウンタアドレスRADDに対応する。相補リフレッシュカウンタアドレスRADD<sub>b</sub>に対応する保持状態が弱保持状態を示すとき、リフレッシュ制御論理250は、メモリブロック260内の相補リフレッシュカウンタアドレスRADD<sub>b</sub>に対応する行に対してリフレッシュ動作を実行する。

30

【0017】

図2Bに、本開示の一態様による、それぞれの各メモリアドレスに対応する保持状態を与えるためのリフレッシュ表270を示す。リフレッシュ表270中のエントリは、図2Aのリフレッシュビン表230をポピュレートするために使用され得る。この例では、相補リフレッシュカウンタアドレス274は弱保持状態を有する(たとえば、「1」が弱保持状態に対応する)。動作中、リフレッシュカウンタアドレス272(たとえば、RADDが「010」である)と相補リフレッシュカウンタアドレス274(たとえば、RADD<sub>b</sub>が2進数「110」である)とのための保持状態が決定され得る。相補リフレッシュカウンタアドレス274が弱保持状態を有するので、図3にさらに示すように、図2Aのリフレッシュ制御論理250は、リフレッシュカウンタアドレス272に対するリフレッシュ動作より前にリフレッシュ動作を挿入する。

40

【0018】

図3は、本開示の一態様による、弱保持状態をもつメモリセルのためのリフレッシュ方式を示すフローチャート300である。ブロック310において、2つの保持状態が、シングルリフレッシュカウンタアドレスRADDを使用して読み取られる。たとえば、図2Aに示すように、リフレッシュビン表は、リフレッシュカウンタアドレスRADDと相補リフレッシュカウンタアドレスRADD<sub>b</sub>に対応する保持状態を出力する。ブロック312において、相補リフレッシュカウンタアドレスRADD<sub>b</sub>に対応する保持状態が弱保持状態にあるかどうかが決定される。相補リフレッシュカウンタアドレスRADD<sub>b</sub>の保持状態が通常であるとき、ブロック320において、リフレッシュカウンタアドレスRADDのためのリフレッシュ動作が実行される

50

。 ブロック322において、リフレッシュカウンタ値(RCNT)が増分される。そうでない場合、ブロック314において、相補リフレッシュカウンタアドレスRADDbに対してリフレッシュ動作が実行されているかどうかが決定される。リフレッシュ動作が実行されていないとき、ブロック316において、相補リフレッシュカウンタアドレスRADDbのためのリフレッシュ動作が実行される。ブロック318において、リフレッシュカウンタRCNTが増分されず、したがって、その後、リフレッシュカウンタアドレスRADDに対してリフレッシュ動作が実行される。

【 0 0 1 9 】

図4Aは、本開示の別の態様による、リフレッシュ制御ブロック410を含むメモリコントローラ402を示すブロック図400である。この構成では、リフレッシュ制御ブロック410は、リフレッシュカウンタ420と、弱行表(weak row table)430と、カウンタブロック440と、リフレッシュ制御論理450とを含む。本開示の本態様では、リフレッシュ制御ブロック410の構成は、図2Aに示すリフレッシュ制御ブロック210の構成と同様であるが、弱行表430が、図2Aのリフレッシュビン表230と置き換わる。この構成では、図4Bにさらに示す弱行表470は、対応する弱保持状態をもつメモリアドレスのみを含む。対照的に、図2Bのリフレッシュビン表230は、各メモリアドレス、ならびに、たとえば、メモリブロック260内の各メモリアドレスの対応する保持状態を含む。

10

【 0 0 2 0 】

図5は、本開示の別の態様による、弱保持状態をもつメモリセルのためのリフレッシュ方式を示すフローチャート500である。ブロック510において、弱行表を探索するためにリフレッシュカウンタアドレスRADDと相補リフレッシュカウンタアドレスRADDbとが使用される。たとえば、図4Aおよび図4Bに示すように、弱行表430/470を探索するためにリフレッシュカウンタアドレスRADDと相補リフレッシュカウンタアドレスRADDbとが使用される。ブロック512において、弱行表中でヒットが検出されるかどうかが決定される。ブロック514において、相補リフレッシュカウンタアドレスRADDbからヒットが検出されると、ブロック516において、相補リフレッシュカウンタアドレスRADDbのためのリフレッシュ動作が実行されたかどうかが決定される。リフレッシュ動作が実行されていないとき、ブロック518において、相補リフレッシュカウンタアドレスRADDbに対するリフレッシュ動作が実行される。ブロック520において、リフレッシュカウントRCNTが増分されず、したがって、ブロック522において、リフレッシュカウンタアドレスRADDに対してリフレッシュ動作が実行される。ブロック524において、リフレッシュカウンタ値(RCNT)が増分される。

20

【 0 0 2 1 】

図6は、本開示の一態様による、弱保持状態をもつメモリセルをリフレッシュするための方法600を示すフローチャートである。ブロック610において、第1のメモリアドレスに対応する第1の保持状態が検査され、第2のメモリアドレスに対応する第2の保持状態が検査される。たとえば、図2Aに示すように、リフレッシュビン表は、リフレッシュアドレスRADDと相補リフレッシュアドレスRADDbとに対応する保持状態を出力する。代替的に、図4Aおよび図4Bに示すように、弱行表430/470を探索するためにリフレッシュアドレスRADDと相補リフレッシュアドレスRADDbとが使用される。ブロック612において、第2の保持状態が弱保持状態を示すとき、第2のメモリアドレスに対応する行に対してリフレッシュ動作が実行される。たとえば、図2Aに示すように、相補リフレッシュカウンタアドレスRADDbに対応する保持状態が弱保持状態を示すとき、リフレッシュ制御論理250は、メモリブロック260内の相補リフレッシュカウンタアドレスRADDbに対応する行に対してリフレッシュ動作を実行する。相補リフレッシュカウンタアドレスRADDbのためのリフレッシュ動作は、リフレッシュカウンタアドレスRADDのためのリフレッシュ動作の前に、その後に、またはそれと同時に実行され得る。

30

【 0 0 2 2 】

図7Aに、本開示の態様による、他のメモリセルのためのリフレッシュ頻度を維持しながら、弱保持状態をもつメモリセル(たとえば、行)のリフレッシュ頻度を増加させるための技法を示す回路タイミング図を示す。タイミング図100は、リフレッシュアドレス120に対

40

50

してリフレッシュ動作を実行するためのダブルリフレッシュサイクル110を有する。ダブルリフレッシュサイクル110は、32マイクロ秒(μs)のリフレッシュが指定されるとき、たとえば、16マイクロ秒(μs)になり得る。この例では、弱保持状態を有するリフレッシュアドレス122をもつ8行のメモリがある。典型的に、リフレッシュアドレス0、1、2、3、4、5、6および7に対してリフレッシュ動作が実行される。ただし、この例では、後続のバス中でリフレッシュアドレス124と、リフレッシュアドレス126と、リフレッシュアドレス128と、リフレッシュアドレス130と、リフレッシュアドレス132と、リフレッシュアドレス134と、リフレッシュアドレス136とに対するリフレッシュ動作がスキップされる。タイミング図100に示すように、通常保持状態をもつリフレッシュアドレスのためのリフレッシュサイクルをスキップしながら、弱保持状態を有するリフレッシュアドレス122のためのリフレッシュサイクルが倍化される。

10

## 【0023】

タイミング図150に、リフレッシュアドレス170に対してリフレッシュ動作を実行するためのシングルリフレッシュサイクル160を示す。シングルリフレッシュサイクル160は、たとえば、32マイクロ秒(μs)になり得る。この例では、同じく、弱保持状態を有するリフレッシュアドレス172をもつ8行のメモリがある。典型的に、弱保持状態をもつリフレッシュアドレス172に対して挿入リフレッシュ動作180が実行される。この例では、弱行リフレッシュサイクルが挿入される。タイミング図150に示すように、通常保持状態をもつリフレッシュアドレスのためのリフレッシュサイクルを維持しながら、弱保持状態をもつリフレッシュアドレス172のためだけのリフレッシュサイクルが倍化される。

20

## 【0024】

タイミング図150に示す挿入方式では、1Xリフレッシュサイクルは、挿入弱行(たとえば、リフレッシュアドレス172)の割合(%)だけ増加する。この例では、たとえば、8Kサイクル/32msの同じリフレッシュサイクル保持仕様を保つために、リフレッシュサイクル保持仕様は、次のように変更され得る。

(8K+弱行の%)サイクル/32ms (1)

たとえば、弱行の割合が5%に等しい場合、リフレッシュサイクル保持仕様として8.4Kサイクル/32msまたは8Kサイクル/30.4msが指定され得る。

## 【0025】

タイミング図700に、本開示の態様による、リフレッシュサイクル保持仕様を維持しながら、弱保持状態をもつメモリセル(たとえば、行)のリフレッシュ頻度を増加させるためのダブルアクティブ化方式を示す。リフレッシュアドレス720に対してリフレッシュ動作を実行するためのシングルリフレッシュサイクル710をもつタイミング図700が示されている。シングルリフレッシュサイクル710は、たとえば、32マイクロ秒(μs)になり得る。この例では、同じく、弱保持状態を有するリフレッシュカウンタアドレス722をもつ8行のメモリがある。典型的に、弱保持状態をもつリフレッシュアドレス722に対して挿入リフレッシュ動作730が実行される。ただし、この例では、挿入リフレッシュ動作730は、リフレッシュアドレス724のためのリフレッシュ動作と同時に実行される。タイミング図700に示すように、リフレッシュサイクル保持状態(たとえば、8Kサイクル/32ms)を維持しながら、弱保持状態をもつリフレッシュアドレス722のためだけのリフレッシュサイクルが倍化される。

30

40

## 【0026】

図7Bに、本開示の一態様による、それぞれの各メモリアドレスに対応する保持状態を与えるためのリフレッシュ表770を示す。リフレッシュ表770中のエントリはリフレッシュ表(たとえば、図2Aのリフレッシュビン表230または図4Aの弱行表430)をポピュレートし得る。この例では、相補リフレッシュカウンタアドレス774は弱保持状態を有する(たとえば、「10100」が弱保持状態に対応する)。ただし、この例では、弱保持状態はまた、相補リフレッシュカウンタアドレス774に対応する内部行(たとえば、32)のグループから弱内部行(weak internal row)を識別する。

## 【0027】

50

動作中、リフレッシュカウンタアドレス272(たとえば、RADDが「010」である)と相補リフレッシュカウンタアドレス274(たとえば、RADDbが2進数「110」である)とのための保持状態が決定され得る。相補リフレッシュカウンタアドレス774が弱保持状態を有するので、図8にさらに示すように、リフレッシュカウンタアドレス772に対応する内部行のグループのためのリフレッシュ動作と同時に、対応する弱内部行のためのリフレッシュ動作が実行され得る。この構成では、相補リフレッシュカウンタアドレス774に対応する内部行のグループから弱内部行のみに同時リフレッシュ動作を限定することによって、(リフレッシュカウンタアドレス772と相補リフレッシュカウンタアドレス774とに対応する64個の内部行の各々に対して同時リフレッシュ動作を実行するのとは対照的に)電力雑音が低減される。

10

#### 【0028】

図8は、本開示の別の態様による、弱保持状態をもつメモリセルのためのリフレッシュ方式を示すフローチャート800である。ブロック810において、リフレッシュカウンタアドレスRADDと相補リフレッシュカウンタアドレスRADDbとがリフレッシュ表から読み取られる。ブロック812において、相補リフレッシュカウンタアドレスRADDbに対応する保持状態が弱保持状態にあるかどうかが決定される。相補リフレッシュカウンタアドレスRADDbの保持状態が通常であるとき、ブロック820において、リフレッシュカウンタアドレスRADDのためのリフレッシュ動作が実行される。ブロック822において、リフレッシュカウンタ値(RCNT)が増分される。そうでない場合、ブロック814において、相補リフレッシュカウンタアドレスRADDbのためのリフレッシュ動作が、リフレッシュカウンタアドレスRADDのためのリフレッシュ動作とともに実行される。一構成では、弱保持状態は、相補リフレッシュカウンタアドレスRADDbに対応する内部行(たとえば、32)のグループから弱内部行を識別する。この構成では、同時リフレッシュ動作は、相補リフレッシュカウンタアドレスRADDbに対応する内部行のグループから弱内部行に対してのみ実行される。

20

#### 【0029】

一構成では、弱行についての情報は、DRAMからチップ(SoC)上のシステムに与えられるべきである。したがって、SoCは、リフレッシュサイクルを調整することができる。1つのそのような実装形態は、弱行%情報とともにDRAM中に読み取り専用モードレジスタセット(MRS)モードを有することである。SoCは、情報を読み取り、リフレッシュサイクルを調整することができる。

30

#### 【0030】

一構成では、メモリコントローラは、リフレッシュ制御ブロックを含む。リフレッシュ制御ブロックは、リフレッシュカウンタと、リフレッシュビン表と、カウンタブロックとを含む。リフレッシュ制御ブロックは、リフレッシュカウンタからの第1のメモリアドレスに対応する第1の保持状態と、保持状態表からの第2のメモリアドレスに対応する第2の保持状態とを検査するための手段を含む。本開示の一態様では、チェック手段は、チェック手段によって具陳された機能を実行するように構成されたリフレッシュ制御論理250/450であり得る。この構成では、リフレッシュ制御ブロックはまた、第2の保持状態が弱保持状態を示すとき、第2のメモリアドレスに対応する行に対してリフレッシュ動作を実行するための手段を含む。本開示の一態様では、実行手段は、実行手段によって具陳された機能を実行するように構成されたリフレッシュ制御論理250/450であり得る。別の態様では、前述の手段は、前述の手段によって具陳された機能を実行するように構成された任意のモジュールまたは任意の装置であり得る。

40

#### 【0031】

図9に、本開示の一態様を有利に用いることができる例示的なワイヤレス通信システム900を示す。説明のために、図9に、3つのリモートユニット920、930、および950と2つの基地局940とを示す。一般的なワイヤレス通信システムは、これよりも多くのリモートユニットと基地局とを有し得ることが認識されよう。リモートユニット920、930、および950は、以下でさらに説明する本開示の態様であるメモリコントローラ回路925A、925B、および925Cをそれぞれ含む。図9に、基地局940からリモートユニット920、930、および950へ

50

の順方向リンク信号980と、リモートユニット920、930、および950から基地局940への逆方向リンク信号990とを示す。

【0032】

図9では、ワイヤレスローカルループシステムにおいて、リモートユニット920は携帯電話として示されており、リモートユニット930はポータブルコンピュータとして示されており、リモートユニット950は固定ロケーションリモートユニットとして示されている。たとえば、リモートユニットは、セルフオン、ハンドヘルドパーソナル通信システム(PCS)ユニット、携帯情報端末などのポータブルデータユニット、またはメータ読み取り機器などの固定ロケーションデータユニットであり得る。図9に、本開示の教示によるメモリコントローラ回路を示すが、本開示は、これらの例示的な図示のユニットに限定されない。たとえば、本開示の態様によるメモリコントローラ回路は、任意のデバイスにおいて最適に用いられ得る。

10

【0033】

特定の回路について説明してきたが、本開示を実施するために、開示された回路のすべてが必要とされるわけではないことが当業者には理解されよう。さらに、本開示に対する焦点を維持するために、いくつかのよく知られている回路について記載していない。同様に、説明はある位置における論理「0」および論理「1」に言及しているが、本開示の動作に影響を与えるに論理値を切り替え、それに応じて回路の残りの部分を調整し得ることが当業者には理解されよう。

20

【0034】

本開示およびその利点について詳しく説明したが、添付の特許請求の範囲によって規定される本開示の趣旨および範囲から逸脱することなく、本明細書において様々な変更、代用および改変が行われることを理解されたい。さらに、本出願の範囲は、本明細書で説明したプロセス、機械、製造、組成物、手段、方法、およびステップの特定の構成に限定されるものではない。当業者が本開示から容易に諒解するように、本明細書で説明した対応する構成と実質的に同じ機能を実行するか、または実質的に同じ結果を実現する、現存するまたは今後開発されるプロセス、機械、製造、組成物、手段、方法、またはステップが、本開示に従って利用され得る。したがって、添付の特許請求の範囲は、そのようなプロセス、機械、製造、組成物、手段、方法、またはステップをそれらの範囲内に含むものとする。

30

【0035】

本開示の前述の説明は、いかなる当業者も本開示を作成または使用することができるようにするために与えたものである。本開示への様々な修正が当業者には容易に明らかになり、本明細書で定義される一般原理は、本開示の趣旨および範囲を逸脱することなく他の変形形態に適用され得る。したがって、本開示は、本明細書で説明する例および設計に限定されるものではなく、本明細書で開示する原理および新規の特徴に合致する最も広い範囲を与えられるべきである。

【符号の説明】

【0036】

- 100 タイミング図

- 110 ダブルリフレッシュサイクル

- 120 リフレッシュアドレス

- 122 リフレッシュアドレス

- 124 リフレッシュアドレス

- 126 リフレッシュアドレス

- 128 リフレッシュアドレス

- 130 リフレッシュアドレス

- 132 リフレッシュアドレス

- 134 リフレッシュアドレス

- 136 リフレッシュアドレス

40

50

|      |                  |    |

|------|------------------|----|

| 150  | タイミング図           |    |

| 160  | シングルリフレッシュサイクル   |    |

| 170  | リフレッシュアドレス       |    |

| 172  | リフレッシュアドレス       |    |

| 180  | 挿入リフレッシュ動作       |    |

| 200  | ロック図             |    |

| 202  | メモリコントローラ        |    |

| 210  | リフレッシュ制御ロック      |    |

| 220  | リフレッシュカウンタ       |    |

| 230  | リフレッシュビン表        | 10 |

| 240  | カウンタロック          |    |

| 250  | リフレッシュ制御論理       |    |

| 260  | メモリロック           |    |

| 270  | リフレッシュ表          |    |

| 272  | リフレッシュカウンタアドレス   |    |

| 274  | 相補リフレッシュカウンタアドレス |    |

| 400  | ロック図             |    |

| 402  | メモリコントローラ        |    |

| 410  | リフレッシュ制御ロック      |    |

| 420  | リフレッシュカウンタ       | 20 |

| 430  | 弱行表              |    |

| 440  | カウンタロック          |    |

| 450  | リフレッシュ制御論理       |    |

| 470  | 弱行表              |    |

| 700  | タイミング図           |    |

| 710  | シングルリフレッシュサイクル   |    |

| 720  | リフレッシュアドレス       |    |

| 722  | リフレッシュカウンタアドレス   |    |

| 722  | リフレッシュアドレス       |    |

| 724  | リフレッシュアドレス       | 30 |

| 730  | 挿入リフレッシュ動作       |    |

| 770  | リフレッシュ表          |    |

| 772  | リフレッシュカウンタアドレス   |    |

| 774  | 相補リフレッシュカウンタアドレス |    |

| 900  | ワイヤレス通信システム      |    |

| 920  | リモートユニット         |    |

| 925A | メモリコントローラ回路      |    |

| 925B | メモリコントローラ回路      |    |

| 925C | メモリコントローラ回路      |    |

| 930  | リモートユニット         | 40 |

| 940  | 基地局              |    |

| 950  | リモートユニット         |    |

| 980  | 順方向リンク信号         |    |

| 990  | 逆方向リンク信号         |    |

【図 1 A】

【図 1 B】

【図 2 A】

【図 2 B】

| 追加 | リフレッシュ |

|----|--------|

| 0  | 0      |

| 1  | 0      |

| 2  | 0      |

| 3  | 0      |

| 4  | 0      |

| 5  | 0      |

| 6  | 1      |

| 7  | 0      |

【図 3】

【図4A】

【図4B】

|       |

|-------|

| 追加    |

| 12345 |

| 103   |

| 45    |

| 334   |

| 67    |

| 590   |

| 6412  |

| 7     |

【図5】

【図6】

【図 7 A】

【図 7 B】

| 追加 | リフレッシュ |

|----|--------|

| 0  | 0      |

| 1  | 0      |

| 2  | 0      |

| 3  | 0      |

| 4  | 0      |

| 5  | 0      |

| 6  | 10100  |

| 7  | 0      |

【図 8】

【図 9】

FIG. 9

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2014/036858

A. CLASSIFICATION OF SUBJECT MATTER

INV. G11C11/406

ADD.

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G11C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

EPO-Internal, WPI Data, COMPENDEX, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                  | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| A         | US 2007/033339 A1 (BEST SCOTT C [US] ET AL) 8 February 2007 (2007-02-08)<br>paragraph [0029] - paragraph [0061];<br>figures 1,2A,2B,3<br>-----<br>US 2005/099868 A1 (OH JONG-HOON [US])<br>12 May 2005 (2005-05-12)<br>paragraph [0035] - paragraph [0043];<br>figures 3-6<br>----- | 1-27                  |

| A         |                                                                                                                                                                                                                                                                                     | 1-27                  |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier application or patent but published on or after the international filing date

- "L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

25 September 2014

09/10/2014

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040,

Fax: (+31-70) 340-3016

Authorized officer

Lecoutre, Renaud

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2014/036858

| Patent document cited in search report | Publication date | Patent family member(s) |               | Publication date |

|----------------------------------------|------------------|-------------------------|---------------|------------------|

| US 2007033339                          | A1 08-02-2007    | US 2007033339           | A1 08-02-2007 |                  |

|                                        |                  | US 2009282189           | A1 12-11-2009 |                  |

| US 2005099868                          | A1 12-05-2005    | CN 1879173              | A 13-12-2006  |                  |

|                                        |                  | DE 602004007545         | T2 13-03-2008 |                  |

|                                        |                  | EP 1685570              | A1 02-08-2006 |                  |

|                                        |                  | JP 2007510254           | A 19-04-2007  |                  |

|                                        |                  | US 2005099868           | A1 12-05-2005 |                  |

|                                        |                  | WO 2005045845           | A1 19-05-2005 |                  |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LR,LS,MW,MZ,NA,RW,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,RU,TJ,TM),EP(AL,AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,R,S,SE,SI,SK,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,KM,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BN,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,H,R,HU,ID,IL,IN,IR,IS,JP,KE,KG,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PA,PE,PG,PH,PL,PT,QA,RO,RS,RU,RW,SA,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TH,TJ,TM,TN,TR,TT,TZ,UA,UG,US

(72)発明者 シアンユ・ドン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

(72)発明者 ジュンウォン・スー

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライヴ・5775

F ターム(参考) 5M024 AA40 BB22 BB39 EE30 PP02 PP07