(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7169751号

(P7169751)

(45)発行日 令和4年11月11日(2022.11.11)

(24)登録日 令和4年11月2日(2022.11.2)

(51)国際特許分類

|         |                 |         |          |

|---------|-----------------|---------|----------|

| H 0 4 N | 5/3745(2011.01) | H 0 4 N | 5/3745   |

| H 0 4 N | 5/341(2011.01)  | H 0 4 N | 5/341    |

| H 0 4 N | 5/378(2011.01)  | H 0 4 N | 5/378    |

| H 0 4 N | 5/374(2011.01)  | H 0 4 N | 5/374    |

| H 0 1 L | 27/146(2006.01) | H 0 1 L | 27/146 A |

請求項の数 20 (全27頁) 最終頁に続く

(21)出願番号 特願2018-48395(P2018-48395)

(22)出願日 平成30年3月15日(2018.3.15)

(65)公開番号 特開2019-161551(P2019-161551)

A)

(43)公開日 令和1年9月19日(2019.9.19)

審査請求日 令和3年3月11日(2021.3.11)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 110003281弁理士法人大塚国際特許事務所

宮本 佳昭

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

竹田 伸弘

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 田仲 祐士

東京都大田区下丸子3丁目30番2号

キヤノン株式会社内

(72)発明者 豊田 好一

審査官

最終頁に続く

(54)【発明の名称】 撮像素子およびそれを有する電子機器

## (57)【特許請求の範囲】

## 【請求項1】

単一フォトンの入射を検出可能な光電変換部を備える画素を複数有する撮像素子であつて、

複数の光電変換部の出力信号の論理和信号を生成するOR回路と、

前記論理和信号に含まれるパルスをカウントするカウンタと、

前記OR回路に入力する前記複数の光電変換部の出力信号の1つ以上を分周する分周器

であつて、出力信号によって分周比を異ならせることにより、出力信号に付与する重みを

異ならせる分周器と、を有し、

前記カウンタで、前記論理和信号の第1の期間に含まれるパルスをカウントすることにより、カウント値を、ローパスフィルタを適用した画素値として出力することを特徴とする撮像素子。

## 【請求項2】

前記カウンタに、1つの光電変換部の出力信号を供給するか、前記論理和信号を供給するかを切り替えるスイッチをさらに有し、

前記カウンタは、前記スイッチにより1つの光電変換部の出力信号が供給される場合には、該出力信号の前記第1の期間に含まれるパルスをカウントし、カウント値を、ローパスフィルタを適用しない画素値として出力することを特徴とする請求項1に記載の撮像素子。

## 【請求項3】

前記スイッチは、前記撮像素子の外部から供給される制御信号によって制御可能であることを特徴とする請求項2に記載の撮像素子。

【請求項4】

前記カウンタに、前記複数の光電変換部の出力信号を別個に供給するか、前記論理和信号を供給するかを切り替えるスイッチをさらに有し、

前記カウンタは、前記スイッチにより前記複数の光電変換部の出力信号が別個に供給される場合、前記複数の光電変換部の出力信号に含まれるパルスの数の差をカウントすることにより、ハイパスフィルタもしくはエッジ検出フィルタを適用した画素値を出力することを特徴とする請求項1に記載の撮像素子。

【請求項5】

前記スイッチは、前記撮像素子の外部から供給される制御信号によって制御可能であることを特徴とする請求項4に記載の撮像素子。

【請求項6】

前記カウンタは、前記カウンタは、前記スイッチにより1つの光電変換部の出力信号が供給される場合には、前記第1の期間に含まれるパルスの数と、第2の期間に含まれるパルスの数との差をカウントすることにより、カウント値を、時間方向にフィルタを適用した画素値として出力することを特徴とする請求項2に記載の撮像素子。

【請求項7】

前記第2の期間は前記第1の期間と同じ長さであることを特徴とする請求項6に記載の撮像素子。

10

【請求項8】

前記カウンタはアップダウンカウンタであり、前記第1の期間および前記第2の期間の一方でアップカウントし、他方でダウンカウントすることにより、前記差をカウントすることを特徴とする請求項6または請求項7に記載の撮像素子。

【請求項9】

前記撮像素子は複数の基板を有する積層構造を有し、前記光電変換部は第1の基板に、前記カウンタは第2の基板に設けられることを特徴とする請求項1から請求項8のいずれか1項に記載の撮像素子。

【請求項10】

前記第1の基板で複数の光電変換部の出力信号を多重化して前記第2の基板に転送することを特徴とする請求項9に記載の撮像素子。

20

【請求項11】

前記第2の基板では、前記多重化された出力信号を光電変換部ごとの出力信号に分離することを特徴とする請求項10に記載の撮像素子。

【請求項12】

前記第2の基板では、前記多重化された出力信号を分離しないことを特徴とする請求項10に記載の撮像素子。

【請求項13】

1つのマイクロレンズを水平方向に隣接する第1の光電変換部および第2の光電変換部が共有する構成である場合、

30

前記第1の光電変換部および前記第2の光電変換部の出力信号を多重化した第1の多重化信号と、

前記第1の光電変換部および前記第2の光電変換部と垂直方向に隣接し、かつ水平方向に隣接する第3の光電変換部および第4の光電変換部の出力信号を多重化した第2の多重化信号と、

前記第1の光電変換部および前記第3の光電変換部、もしくは前記第2の光電変換部および前記第4の光電変換部の出力信号を多重化した第3の多重化信号と、

を前記第1の基板から前記第2の基板に転送することを特徴とする請求項10から請求項12のいずれか1項に記載の撮像素子。

【請求項14】

40

50

1つのマイクロレンズを水平方向に隣接する第1の光電変換部および第2の光電変換部が共有する構成である場合、

前記第1の光電変換部および前記第2の光電変換部の出力信号を多重化した多重化信号と、

前記第1の光電変換部および前記第2の光電変換部の一方の出力信号と、

を前記第1の基板から前記第2の基板に転送することを特徴とする請求項1\_0から請求項1\_2のいずれか1項に記載の撮像素子。

【請求項15】

前記複数の光電変換部の出力信号のそれぞれは、他の出力信号とパルスの期間が重複しないことを特徴とする請求項1から請求項1\_4のいずれか1項に記載の撮像素子。

10

【請求項16】

前記複数の光電変換部のそれぞれが、單一フォトンの入射によって出力信号に電圧変化が発生する期間内で異なる期間にパルスを含んだ出力信号を生成することを特徴とする請求項1\_5に記載の撮像素子。

【請求項17】

前記出力信号の前記期間内に含まれるパルスの数を光電変換部によって異ならせることにより、光電変換部の出力信号に重み付けを行うことを特徴とする請求項1\_6に記載の撮像素子。

【請求項18】

前記光電変換部は、光電変換素子と、該光電変換素子の出力信号と比較信号とを比較して前記パルスを生成する比較回路とを有し、

20

前記比較信号が所定の周期で電圧が変化する信号であり、

前記パルスをカウントするカウンタが共通する複数の光電変換部のそれぞれが有する前記比較回路に入力される前記比較信号は、第1の電圧になる期間が重複しないように位相が異なることを特徴とする請求項1に記載の撮像素子。

【請求項19】

前記所定の周期が第1の期間と第2の期間とを有し、前記第1の期間において前記第1の電圧になる回数を2回以上とし、前記第2の期間において前記第1の電圧にならないように前記比較信号を構成することにより、該比較信号が入力される前記光電変換部に單一フォトンが入射した際に前記光電変換部の出力信号に含まれるパルスの数を2以上することを特徴とする請求項1\_8に記載の撮像素子。

30

【請求項20】

請求項1から請求項1\_9のいずれか1項に記載の撮像素子を有することを特徴とする電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、撮像素子およびそれを有する電子機器に関する。

【背景技術】

【0002】

アバランシェフォトダイオード(APD)は、降伏電圧(ブレークダウン電圧)以上の逆電圧を印加した状態(ガイガーモード)で動作させると、アバランシェ増倍が発生するという特性を有する。この性質を利用して、APDをガイガーモードで動作させて單一フォトンを検出可能とした受光素子がSPAD(Single Photon Avalanche Diode)である。

40

【0003】

特許文献1では、複数のSPADを2次元配置した光検出器を用い、光の飛行時間(TOF:Time Of Flight)に基づいて距離を計測するシステムが開示されている。特許文献1には、複数のSPADから出力された各パルス信号を単純加算することにより、フォトンの検出精度を高める構成が開示されている。

【先行技術文献】

50

## 【特許文献】

## 【0004】

【文献】特開2012-60012号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0005】

一般的にデジタルカメラでは、撮像素子とは別個の演算回路が用いて、ノイズ低減やエッジ検出などを目的としたフィルタを撮像画像に適用している。S P A Dを二次元配置した撮像素子を用いる場合にも、同様のフィルタを撮像画像に適用することが必要となる。しかし、特許文献1に記載された構成では、個々のパルス信号に重み付けをしたフィルタを適用することができない。また、加算によって得られるパルス信号にフィルタを適用する場合、フィルタを適用するための演算回路が必要となる。

10

## 【0006】

本発明は、簡単な構成でフィルタを適用した画像を生成可能な撮像素子の提供を目的の1つとする。

## 【課題を解決するための手段】

## 【0007】

上述の目的は、单一フォトンの入射を検出可能な光電変換部を備える画素を複数有する撮像素子であって、複数の光電変換部の出力信号の論理和信号を生成するOR回路と、論理和信号に含まれるパルスをカウントするカウンタと、OR回路に入力する複数の光電変換部の出力信号の1つ以上を分周する分周器であって、出力信号によって分周比を異ならせることにより、出力信号に付与する重みを異ならせる分周器と、を有し、カウンタで、論理和信号の第1の期間に含まれるパルスをカウントすることにより、カウント値を、一口パスフィルタを適用した画素値として出力することを特徴とする撮像素子によって達成される。

20

## 【発明の効果】

## 【0008】

本発明によれば、簡単な構成でフィルタを適用した画像を生成可能な撮像素子を提供することができる。

30

## 【図面の簡単な説明】

## 【0009】

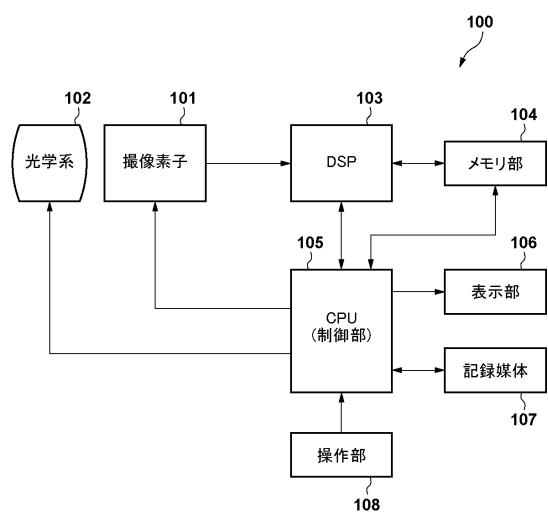

【図1】本発明の実施形態に係る撮像装置の例を示すブロック図

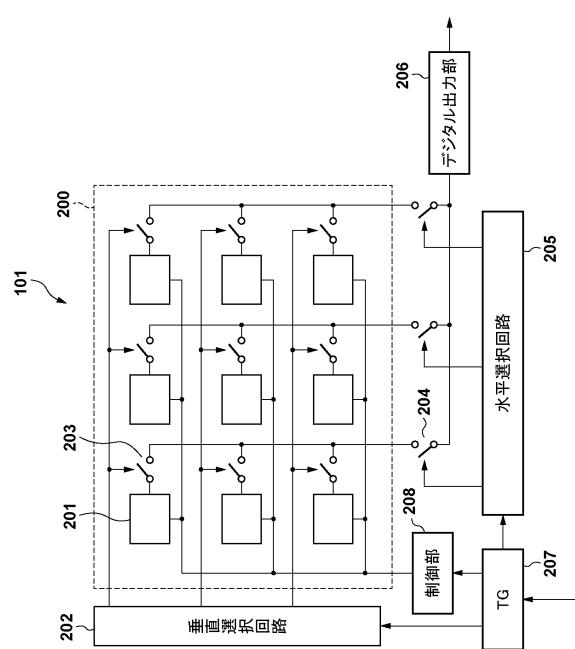

【図2】本発明の実施形態に係る撮像素子の構成例を示すブロック図

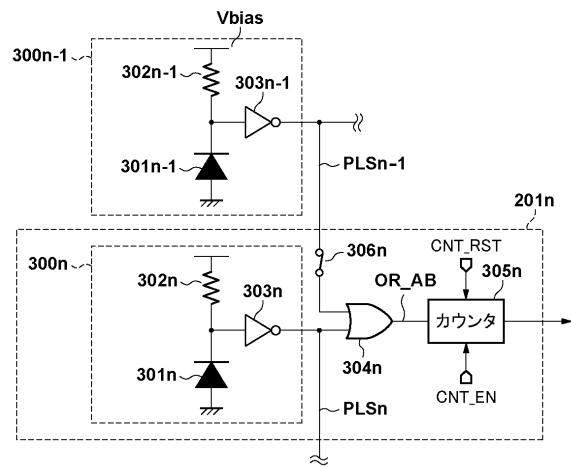

【図3】第1の実施形態に係る画素の等価回路図

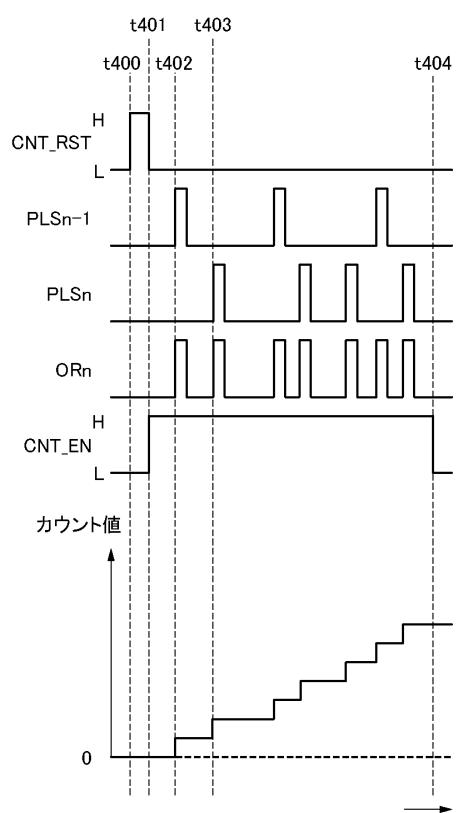

【図4】第1の実施形態に係るフォトンのカウント動作の一例を示すタイミングチャート

【図5】第2の実施形態に係る画素の等価回路図

【図6】第2の実施形態に係るフォトンのカウント動作の一例を示すタイミングチャート

【図7】第1および第2の実施形態に係る画素の等価回路図

【図8】第3の実施形態に係る画素の等価回路図

【図9】第3の実施形態に係るフォトンのカウント動作の一例を示すタイミングチャート

【図10】第4の実施形態に係る画素の等価回路図

【図11】第4の実施形態に係るフォトンのカウント動作の一例を示すタイミングチャート

【図12】第5の実施形態に係る画素の等価回路図

【図13】第5の実施形態に係る画素の動作を示すタイミングチャート

【図14】第5の実施形態に係る信号処理回路および撮像素子の構成図

【図15】第6の実施形態に係る画素の動作を示すタイミングチャート

【図16】第7の実施形態に係る画素の等価回路図

【図17】第7の実施形態に係る画素の動作を示すタイミングチャート

## 【発明を実施するための形態】

## 【0010】

40

50

以下、本発明の例示的な実施形態について、図面を参照しながら詳細に説明する。各図において、同一の部材については同一の参照符号を付し、重複する説明は省略する。なお、以下では本発明を撮像素子を有する電子機器の一例としてのデジタルカメラに適用した実施形態について説明するが、本発明は撮像素子を有しうる任意の電子機器に適用することができる。このような電子機器には撮像装置はもちろん、パーソナルコンピュータ、タブレット端末、携帯電話機、ゲーム機、ドライブレコーダ、ロボット、ドローンなどが含まれるが、これらに限定されない。

#### 【0011】

##### <第1の実施形態>

図1は、本発明の実施形態に係る撮像装置の一例としてのデジタルカメラ100の機能構成例を示すブロック図である。デジタルカメラ100は撮像素子101、光学系102、DSP103、メモリ部104、CPU105、表示部106、記録媒体107および操作部108から構成される。

10

#### 【0012】

光学系102はレンズ群および絞りを備え、被写体の光学像を撮像素子101の撮像面に形成する。また、光学系102は可動レンズや絞りを駆動する機構（例えばモータやアクチュエータ）を備える。絞りはメカニカルシャッタとして機能してもよい。

#### 【0013】

撮像素子101は、単一フォトンの入射を検出可能な光電変換部を備える画素を複数有し、光学系102が形成する光学像を、個々の光電変換部に入射したフォトンの数（デジタル値）に変換することができる。

20

#### 【0014】

DSP (Digital Signal Processor) 103は、撮像素子101が出力する画像データに対して様々な処理を適用する画像処理回路として機能するプロセッサである。主制御部として機能するCPU105は、デジタルカメラ100の各部の動作を制御する。なお、DSP103およびCPU105は、例えばメモリ部104に含まれる不揮発性メモリに記憶されているプログラムを、メモリ部104に含まれる揮発性メモリ（ワークメモリ）に読み込んで実行することにより、所定の動作を実現する。なお、CPU105によってもDSP103と同様の処理を実現できるが、DSP103は特定の信号処理に関してCPU105よりも高速に実行することができる。

30

#### 【0015】

表示部106は例えば液晶ディスプレイ（LCD）であり、撮影された画像、デジタルカメラ100の各種情報（撮影条件、各種設定値、バッテリー残量、残り記録枚数／時間など）、メニュー画面などのGUIを表示する。

#### 【0016】

記録媒体107はCPU105によって読み書きが可能であり、撮影で得られた画像データの記録先として用いられる。記録媒体107は例えば着脱可能なメモリカードであつてよい。

#### 【0017】

操作部108は、スイッチ、ボタン、ダイヤル、タッチパネルなど、デジタルカメラ100が有する複数の入力デバイスの総称である。操作部108に対するユーザ操作はCPU105が検出可能である。操作部108には例えば電源スイッチ、シャッターボタン、メニューボタン、方向キー、決定ボタンなどが含まれる。なお、操作部108にタッチパネルが含まれる場合、通常、表示部106の表示とタッチパネルとの組み合わせにより特定の機能を有する入力デバイスが実現される。

40

#### 【0018】

なお、DSP103は画像データから例えば自動露出制御（AE）や自動焦点検出（AF）に用いる評価値を生成することができる。CPU105はこれらの評価値に基づいて撮影条件（絞り値、シャッタースピード、撮影感度）を決定したり、光学系102が有するフォーカスレンズを駆動したりして、AEやAFを実現することができる。ホワイトバ

50

ランス調整、ガンマ補正、符号化および復号、被写体検出といった、一般的なデジタルカメラが備える機能については、特に説明しない限り、DSP103およびCPU105の少なくとも一方がプログラムを実行することによって実現可能である。

#### 【0019】

図2は、撮像素子101の構成例を模式的に示す図である。撮像素子101は、画素アレイ200、垂直選択回路202、スイッチ203、204、水平選択回路205、デジタル出力部206、タイミング発生回路(TG)207および制御部208を有する。

#### 【0020】

画素アレイ200は、2次元状に配置された複数の画素201を有する。図2では模式的に3行×3列分の画素201しか示していないが、実際には数十万から数千万の画素201が配列されている。垂直選択回路202は画素201ごとに設けられたスイッチ203のオン、オフを、画素の1行単位で制御する。画素201に対応するスイッチ203をオンにすることを、その画素201を選択するという。

#### 【0021】

水平選択回路205は、画素201の一列ごとに設けられた垂直信号線に接続されたスイッチ204のオン、オフを制御する。スイッチ203がオン状態の行に含まれる複数の画素201のうち、スイッチ204がオン状態の垂直信号線に接続されている1つの画素201から信号を読み出すことができる。読み出された信号は、デジタル出力部206によってA/D変換され、画素データとして撮像素子101の外部に出力される。

制御部208は、画素201に制御信号を供給する。

#### 【0022】

TG207はCPU105の制御に従い、垂直選択回路202、水平選択回路205および制御部208に制御信号を供給し、画素201の動作および、画素201からの信号読み出し動作を制御する。

#### 【0023】

以下、2次元状に配置された画素201のうち、n(nは1以上の整数)行目に配置された1つの画素201(画素201nと表記する)の動作制御について説明する。画素201nを構成する構成要素や、画素201nに関する信号についてもnを付記する。

#### 【0024】

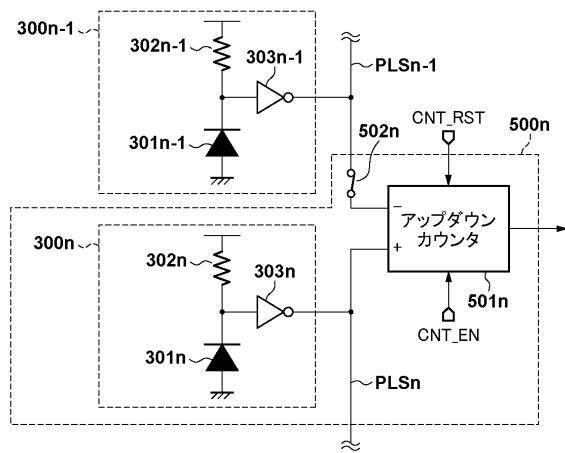

図3は、画素201nの等価回路図である。画素201nは、光電変換部である受光部300nと、OR回路304nと、カウンタ回路305nと、スイッチ306nとを備える。なお、図3では、便宜上、画素201nと同じ構成を有するn-1行目の画素201n-1の構成要素のうち、受光部300n-1も図示している。

#### 【0025】

受光部300nは、光電変換素子であるフォトダイオード301nと、クエンチ抵抗302nと、反転バッファ303nとを含んで構成される。本実施形態において、フォトダイオード301nはアバランシェフォトダイオード(APD)である。フォトダイオード301nにはクエンチ抵抗302nを介して降伏電圧以上のバイアス電圧Vbiasが印加されており、したがってフォトダイオード301nはガイガーモードで動作する。フォトダイオード301nにフォトンが入射すると、アバランシェ増倍によって大きな光電流が流れ、クエンチ抵抗302nで電圧降下が発生する。これにより、フォトダイオード301nに印加されるバイアス電圧Vbiasが低下し、バイアス電圧Vbiasが降伏電圧まで降下するとアバランシェ増倍は停止する。その結果、光電流が流れなくなり、フォトダイオード301nには再びバイアス電圧Vbiasが印加される状態に戻る。なお、クエンチ抵抗302nはフォトダイオード301nのアバランシェ増倍を停止するための抵抗素子である。ここで、クエンチ抵抗302nはトランジスタの抵抗成分を利用してよい。

#### 【0026】

反転バッファ303nは、クエンチ抵抗302nで発生した電圧変化をパルス信号として出力する。このようにして、フォトダイオード301nにフォトンが入射すると、反転

10

20

30

40

50

バッファ 3 0 3 n から 1 つのパルス信号を出力させることができる。ここで、受光部 3 0 0 n から出力されるパルス信号を P L S n 、受光部 3 0 0 n 1 から出力されるパルス信号を P L S n 1 とする。

【 0 0 2 7 】

OR 回路 3 0 4 n には受光部 3 0 0 n 、 3 0 0 n 1 から出力されるパルス信号が入力される。OR 回路 3 0 4 n は 2 つの入力信号の論理和信号を出力する。論理和信号はカウンタ回路 3 0 5 n に入力される。

【 0 0 2 8 】

カウンタ回路 3 0 5 n は OR 回路 3 0 4 n から出力される論理和信号が有するパルス数をカウントする。カウンタ回路 3 0 5 n でカウントした値（以降、カウント値）は、垂直信号線およびスイッチ 2 0 4 を通じてデジタル出力部 2 0 6 n に供給される。受光部 3 0 0 n 1 と OR 回路 3 0 4 との間に設けられるスイッチ 3 0 6 n は、制御部 2 0 8 の制御信号によってオン・オフが制御される。つまり、スイッチ 3 0 6 n は撮像素子 1 0 1 の外部から制御可能である。スイッチ 3 0 6 n がオフの場合、受光部 3 0 0 n 1 から出力されるパルス信号は OR 回路 3 0 4 に入力されない。

【 0 0 2 9 】

次に 2 つの受光部 3 0 0 n 、 3 0 0 n 1 から出力されるパルス信号 P L S n 、 P L S n 1 がどのようにカウンタ回路 3 0 5 n に入力されるかを説明する。まず、制御部 2 0 8 によりスイッチ 3 0 6 n がオンされる。これにより、2 つの受光部 3 0 0 n 、 3 0 0 n 1 から出力されるパルス信号 P L S n 、 P L S n 1 が OR 回路 3 0 4 n に入力される。

【 0 0 3 0 】

各画素 2 0 1 が有する受光部 3 0 0 が output するパルス信号は、自身が有する OR 回路 3 0 4 n と、同じ列の 1 つ下の行の画素が有する OR 回路 3 0 4 n (との間のスイッチ 3 0 6 ) とに出力される。

【 0 0 3 1 】

OR 回路 3 0 4 n は入力された 2 つのパルス信号 P L S n 、 P L S n 1 の論理和信号を生成し、カウンタ回路 3 0 5 n に出力する。そして、カウンタ回路 3 0 5 n は論理和信号に含まれるパルス数をカウントする。

【 0 0 3 2 】

このように、本実施形態では 2 つの受光部 3 0 0 n 、 3 0 0 n 1 から出力されるパルス信号 P L S n 、 P L S n 1 の論理和信号に含まれるパルスの数を 1 つのカウンタ回路 3 0 5 n でカウントする。よって、カウンタ回路 3 0 5 n のカウント値は、空間方向にフィルタを適用した画素値、より具体的には列方向（垂直方向）にローパスフィルタを適用した画素値に相当する。ここでは隣接する 2 つの画素について出力の論理和を得る構成について説明したが、隣接する 3 つ以上の画素について同様の構成としてもよい。論理和を得る出力（パルス信号）の数が増えるほどローパスフィルタの効果が強くなる。

【 0 0 3 3 】

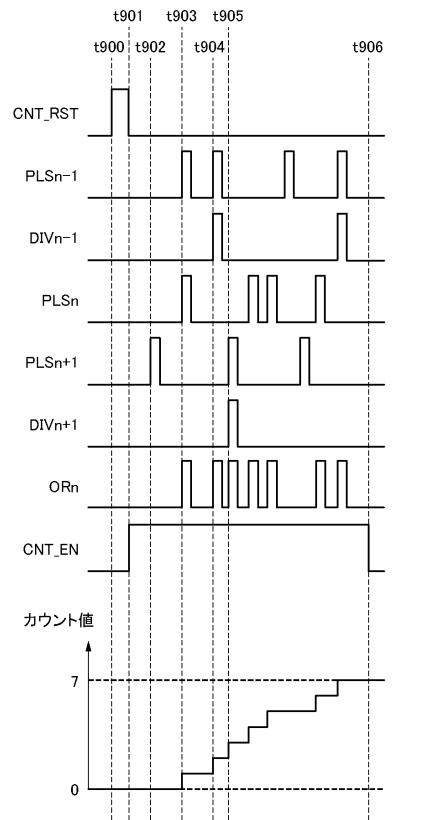

次に、図 3 に示した画素 2 0 1 n のフォトンのカウント動作について説明する。図 4 は、図 3 に示した画素 2 0 1 n のフォトンのカウント動作の一例を示すタイミングチャートである。説明のため、図 3 の OR 回路 3 0 4 n が output する論理和信号を OR n と表記する。ここで、 C N T \_ R S T と C N T \_ E N は制御部 2 0 8 から供給される、カウンタ回路 3 0 5 n の制御信号である。 C N T \_ R S T が H レベルとなるとカウンタ回路 3 0 5 n のカウント値がリセットされる。また、 C N T \_ E N が H レベルの期間のみ、カウンタ回路 3 0 5 n は論理和信号のパルスを計数する。すなわち、 C N T \_ E N は露光時間を制御する信号である。

【 0 0 3 4 】

C N T \_ R S T を時刻 t 4 0 0 で L レベルから H レベルにして、カウンタ回路 3 0 5 n のカウント値をリセットする。その後、時刻 t 4 0 1 で C N T \_ R S T を H レベルから L レベルとする。

【 0 0 3 5 】

10

20

30

40

50

また、時刻  $t_{401}$  で受光部  $300n$ 、 $300n-1$  にバイアス電圧  $V_{bias}$  が供給され、フォトダイオード  $301n$ 、 $301n-1$  には、降伏電圧以上のバイアス電圧が印加される。これにより、フォトダイオード  $301n$ 、 $301n-1$  はガイガーモードで動作し、フォトンが入射するごとに出力信号  $PLSn$ 、 $PLSn-1$  にパルスが発生する。また、時刻  $t_{401}$  で  $CNT\_EN$  が H レベルとなり、カウンタ回路  $305n$  はカウント動作を開始する。

#### 【0036】

時刻  $t_{402}$  において、受光部  $300n-1$  のフォトダイオード  $301n-1$  にフォトンが入射したことにより、受光部  $300n-1$  の出力信号  $PLSn-1$  に矩形状のパルスが発生する。これにより、OR 回路  $304n$  は出力信号  $PLSn-1$  由来のパルスを出力する。カウンタ回路  $305n$  はこのパルスをカウントし、カウント値が 0 から 1 になる。

10

#### 【0037】

時刻  $t_{403}$  において、受光部  $300n$  のフォトダイオード  $301n$  にフォトンが入射したことにより、受光部  $300n$  の出力信号  $PLSn$  に矩形状のパルスが発生する。これにより、OR 回路  $304n$  は出力信号  $PLSn$  由来のパルスを出力する。カウンタ回路  $305n$  はこのパルスをカウントし、カウント値が 1 から 2 になる。

#### 【0038】

時刻  $t_{403}$  以降、時刻  $t_{404}$  で  $CNT\_EN$  が L レベルになり撮影が終了するまで、受光部  $300n$ 、 $300n-1$  にフォトンが入射するごとに出力信号  $PLSn$ 、 $PLSn-1$  にパルスが発生する。個々のパルス信号は OR 回路  $304n$  を通じてカウンタ回路  $305n$  に供給され、パルス数がカウントされる。

20

#### 【0039】

時刻  $t_{404}$  で撮影が終了した後、カウンタ回路  $305n$  のカウント値は垂直選択回路  $202$  および水平選択回路  $205$  の制御によりデジタル出力部  $206$  に出力され、さらに撮像素子  $101$  の外部に出力される。

#### 【0040】

以上説明したように、本実施形態の撮像装置は、単一フォトンの検出が可能な画素（受光部）が複数配列された撮像素子を、複数の画素の出力の論理和を出力可能な構成とした。そして、複数の画素の出力の論理和を 1 つの画素の出力として用いることにより、簡単な構成でローパスフィルタを適用した画素出力を得ることができる。したがって、回路規模の増大を抑制しながら、ノイズを低減した画像を得ることができる。

30

#### 【0041】

なお、ローパスフィルタを適用しない場合には、論理和回路に入力する信号を 1 つにすればよい。具体的には、制御部  $208$  を通じて撮像素子  $101$  の外部からスイッチ  $306$  をオフすることで、カウンタ回路  $305$  は 1 つの受光部  $300$  から出力されるパルスをカウントする。このように、撮影された画像に対してローパスフィルタを適用するか否かを撮像素子の外部から動的に制御可能である。例えば  $CPU105$  は、撮影感度が予め定められた閾値を超える場合にローパスフィルタを適用するよう、制御部  $208$  を通じてスイッチ  $306$  のオン、オフを制御することができる。なお、論理和回路で 3 入力以上の論理和を出力可能な場合、撮影感度が上昇するにつれ、段階的に論理和回路に入力する信号の数を増やすように構成して、ローパスフィルタの効果を強くしてもよい。撮影感度は AE 処理で決定されてもよいし、ユーザの設定値であってもよい。

40

#### 【0042】

##### （第 2 の実施形態）

次に、本発明の第 2 の実施形態について説明する。第 1 の実施形態では複数の画素の出力の論理和を求めることでローパスフィルタの効果を実現する構成であった。本実施形態では、2 つの画素の出力の一方をアップダウンカウンタ回路のカウントアップ入力に、他方をカウントダウン入力に供給する構成により、ハイパス（微分）フィルタの効果を実現する。

#### 【0043】

50

本実施形態は撮像素子 1 0 1 の画素アレイ 2 0 0 の構成以外、第 1 の実施形態と共に通であってよい。そのため、以下では本実施形態における画素アレイ 2 0 0 の構成および動作について説明する。

#### 【0044】

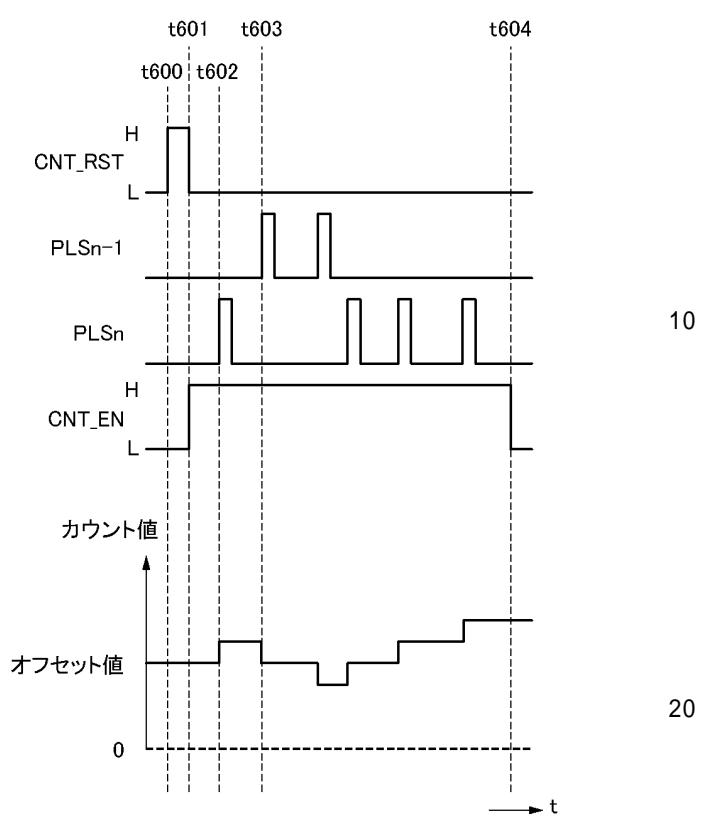

図 5 は、本実施形態における画素アレイ 2 0 0 に 2 次元配置される画素 2 0 1 に相当する画素 5 0 0 n の等価回路図である。第 1 の実施形態で説明した構成要素については図 3 と同じ参照数字を付し、重複する説明は省略する。第 1 の実施形態との構成上の違いは、OR 回路 3 0 4 n およびカウンタ回路 3 0 5 n の代わりに、アップダウンカウンタ回路 5 0 1 n が配置されている点である。なお、図 5 において、n 1 行の画素 5 0 0 n 1 については、第 1 の実施形態と同様に受光部 3 0 0 n 1 以外の構成を省略している。

10

#### 【0045】

アップダウンカウンタ回路 5 0 1 n は、アップカウント入力端子（以降、+ 端子）に入力されたパルス数をアップ方向にカウントし、ダウンカウント入力端子（以降、- 端子）に入力されたパルス数をダウン方向にカウントする。アップダウンカウンタ回路 5 0 1 n は対応する画素 5 0 0 n の受光部 3 0 0 n が出力するパルス数をアップカウントするよう構成される。スイッチ 5 0 2 n は画素 5 0 0 n と同じ水平位置で垂直方向に 1 行上の画素 5 0 0 n 1 の受光部 3 0 0 n 1 が出力するパルス信号をアップダウンカウンタ回路 5 0 1 n の - 端子へ入力するかしないかを切り替える。スイッチ 5 0 2 n がオフの場合、アップダウンカウンタ回路 5 0 1 n は画素 5 0 0 n の受光部 3 0 0 n が出力するパルスの数のアップカウントのみを行う。スイッチ 5 0 2 n のオン・オフは制御部 2 0 8 から供給される制御信号によって制御される。

20

#### 【0046】

次に、各受光部 3 0 0 n 、 3 0 0 n 1 から信号がどのようにアップダウンカウンタ回路 5 0 1 n に入力されるかを説明する。まず、制御部 2 0 8 によりスイッチ 5 0 2 n がオンされる。受光部 3 0 0 n 1 からの信号 P L S n 1 は、スイッチ 5 0 2 n を介してアップダウンカウンタ回路 5 0 1 n の - 端子に入力される。なお、信号 P L S n 1 は図示していないアップダウンカウンタ回路 5 0 1 n 1 の + 端子にも入力される。受光部 3 0 0 n からの信号 P L S n はアップダウンカウンタ回路 5 0 1 n の + 端子に入力される。また、信号 P L S n は図示していないスイッチ 5 0 2 n + 1 を介してアップダウンカウンタ回路 5 0 1 n + 1 の - 端子にも入力される。

30

#### 【0047】

アップダウンカウンタ回路 5 0 1 n は + 端子に入力されたパルス数をアップカウントし、- 端子に入力されたパルス数をダウンカウントする。従って、アップダウンカウンタ回路 5 0 1 n で得られるカウント値は、2 つの受光部 3 0 0 n 、 3 0 0 n 1 に入射したフォトン数の差である。これは、隣接する画素値の差を求めるハイパスフィルタを適用することに相当する。したがって、アップダウンカウンタ回路 5 0 1 n のカウント値は、受光部 3 0 0 n の画素信号に対して被写体のエッジを検出するフィルタ（ハイパスフィルタ）を適用した画素値に相当する。

#### 【0048】

次に、図 5 に示した画素 5 0 0 n のフォトンのカウント動作について説明する。図 6 は、図 5 に示した画素 5 0 0 n のフォトンのカウント動作の一例を示すタイミングチャートである。ここでも、C N T \_ R S T と C N T \_ E N は制御部 2 0 8 から供給される。本実施形態では、C N T \_ R S T が H レベルとなるとアップダウンカウンタ回路 5 0 1 n のカウント値が所定のオフセット値 ( $> 0$ ) にリセットされる。また、C N T \_ E N が H レベルの期間のみ、アップダウンカウンタ回路 5 0 1 n は入力パルスを計数する。すなわち、C N T \_ E N は露光時間を制御する信号である。

40

#### 【0049】

C N T \_ R S T を時刻  $t_{600}$  で L レベルから H レベルにして、アップダウンカウンタ回路 5 0 1 n のカウント値をリセットする。その後、時刻  $t_{601}$  で C N T \_ R S T を H レベルから L レベルとする。

50

**【0050】**

また、時刻  $t_{601}$  で受光部  $300n$ 、 $300n-1$  にバイアス電圧  $V_{bias}$  が供給され、フォトダイオード  $301n$ 、 $301n-1$  には、降伏電圧以上のバイアス電圧が印加される。これにより、フォトダイオード  $301n$ 、 $301n-1$  はガイガーモードで動作し、フォトンが入射するごとに出力信号  $PLSn$ 、 $PLSn-1$  にパルスが発生する。また、時刻  $t_{601}$  で  $CNT\_EN$  が H レベルとなり、アップダウンカウンタ回路  $501n$  はカウント動作を開始する。

**【0051】**

時刻  $t_{602}$  において、受光部  $300n$  のフォトダイオード  $301n$  にフォトンが入射したことにより、受光部  $300n$  の出力信号  $PLSn$  に矩形状のパルスが発生する。出力信号  $PLSn$  はアップダウンカウンタ回路  $501n$  の + 端子に入力されているため、アップダウンカウンタ回路  $501n$  はこのパルスをアップカウントし、カウント値がオフセット値 + 1 になる。

10

**【0052】**

時刻  $t_{603}$  において、受光部  $300n-1$  のフォトダイオード  $301n-1$  にフォトンが入射したことにより、受光部  $300n-1$  の出力信号  $PLSn-1$  に矩形状のパルスが発生する。これにより、アップダウンカウンタ回路  $501n$  はこのパルスをダウンカウントし、カウント値がオフセット値に戻る。

**【0053】**

時刻  $t_{603}$  以降、時刻  $t_{604}$  で  $CNT\_EN$  が L レベルになり撮影が終了するまで、受光部  $300n$ 、 $300n-1$  にフォトンが入射するごとに、出力信号  $PLSn$ 、 $PLSn-1$  にパルスが発生する。個々のパルスはアップダウンカウンタ回路  $501n$  に供給され、パルス数の差がカウントされる。

20

**【0054】**

時刻  $t_{604}$  で撮影が終了した後、アップダウンカウンタ回路  $501n$  のカウント値は、垂直選択回路  $202$  および水平選択回路  $205$  の制御によりデジタル出力部  $206$  に出力され、さらに撮像素子  $101$  の外部に出力される。

**【0055】**

以上説明したように、本実施形態の撮像装置は、單一フォトンの検出が可能な画素（受光部）が複数配列された撮像素子を、複数の画素の出力の差を出力可能な構成とした。そして、複数の画素の出力の差を 1 つの画素の出力として用いることにより、簡単な構成でエッジ検出フィルタ（ハイパスフィルタ）を適用した画素出力を得ることができる。

30

**【0056】**

なお、フィルタを適用しない場合には、アップダウンカウンタ回路  $501n$  に受光部  $300n$  の出力信号だけを入力すればよい。具体的には、制御部  $208$  を通じてスイッチ  $502$  をオフする。このように、撮影された画像に対してエッジ検出フィルタを適用するか否かを撮像素子の外部から動的に制御することができる。例えば、撮影画像を外観検査に用いる場合にエッジ検出フィルタを適用するよう、ユーザ設定によってスイッチ  $502$  のオン、オフを決定することができる。

**【0057】**

40

## &lt;変形例&gt;

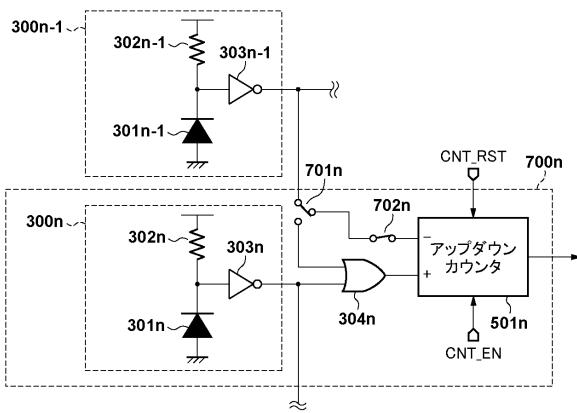

本実施形態は第 1 の実施形態と組み合わせて実施することもできる。図 7 はローパスフィルタとエッジ検出フィルタの 2 種類のフィルタを選択的に適用可能とした画素  $700n$  の等価回路図である。既に説明した構成要素については図 3 および図 5 と同じ参照番号を付してある。本実施形態では、アップダウンカウンタ回路  $501n$  の + 入力の前段に OR 回路  $304n$  を配置するとともに、スイッチ  $701n$ 、 $702n$  を有している。本実施形態の画素  $700n$  は図 2 の画素  $201$  に相当する。

**【0058】**

スイッチ  $701n$  は受光部  $300n-1$  の出力信号の供給先を、OR 回路  $304n$  またはスイッチ  $702n$  との間で切り替える。スイッチ  $702n$  はスイッチ  $701n$  を通じて

50

供給される信号をアップダウンカウンタ回路 501n の 端子へ入力するかしないかを切り替える。スイッチ 701n、702n はともに制御部 208 が供給する制御信号によって制御される。

#### 【0059】

画素 700n の信号にローパスフィルタを適用する場合、スイッチ 701n を、受光部 300n 1 の出力信号を OR 回路 304 に供給するように切り替える。これにより、図 3 に示した等価回路図と同様の構成を実現できる。したがって、ローパスフィルタが適用された画素 700n の画素値が、アップダウンカウンタ回路 501n のカウント値として得られる。この場合、スイッチ 702n はオンでもオフでもよい。

#### 【0060】

また、画素 700n の信号にエッジ検出フィルタを適用する場合、スイッチ 701n を、受光部 300n 1 の出力信号をスイッチ 702n に供給するように切り替える。また、スイッチ 702n をオンし、スイッチ 701n とアップダウンカウンタ回路 501n の 端子とを接続する。これにより、図 5 に示した等価回路図と同様の構成を実現できる。したがって、エッジ検出フィルタが適用された画素 700n の画素値が、アップダウンカウンタ回路 501n のカウント値として得られる。

10

#### 【0061】

なお、スイッチ 701n を、受光部 300n 1 の出力信号をスイッチ 702n に供給するように切り替え、スイッチ 702n をオフすることで、フィルタを適用しない画素 700n の画素値が、アップダウンカウンタ回路 501n のカウント値として得られる。

20

#### 【0062】

このように、本変形例によれば、簡便な構成により、外部からの制御により、フィルタを適用しない画素値、ローパスフィルタを適用した画素値、およびエッジ検出フィルタを適用した画素値を、選択的に得ることができる。

#### 【0063】

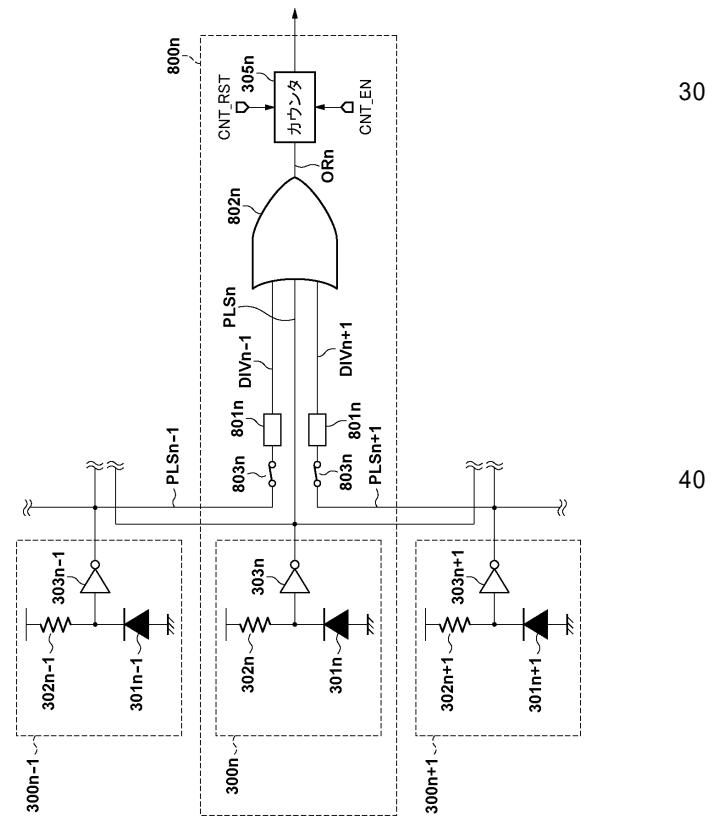

##### <第3の実施形態>

次に、本発明の第3の実施形態について説明する。本実施形態では、3つの受光部の出力信号に対して重み付け（分周）した後、パルス数をカウントすることにより、重み付けのフィルタを適用した画素値を取得可能とした。本実施形態は撮像素子 101 の画素アレイ 200 の構成以外、第1の実施形態と共通であってよい。そのため、以下では本実施形態における画素アレイ 200 の構成および動作について説明する。

30

#### 【0064】

図 8 は、本実施形態における画素アレイ 200 に2次元配置される画素 201 に相当する画素 800n の等価回路図である。第1の実施形態で説明した構成要素については図 3 と同じ参照数字を付し、重複する説明は省略する。本実施形態では、OR 回路 802n に 1 行下 (n + 1 行) の画素 800n + 1 の出力信号 PLSn + 1 がさらに入力される。また、画素 800n 1 および画素 800n + 1 の出力信号にそれぞれ重み付けを行う分周器 801n が設けられている。なお、図 8 において、n 1 行の画素 800n 1 および n + 1 行の画素 800n + 1 については、それぞれ、受光部 300n 1 および受光部 300n + 1 以外の構成を省略している。

40

#### 【0065】

2つの分周器 801n はそれぞれ、受光部 300n 1、300n + 1 の出力信号に含まれるHレベルのパルスを2分周（パルスの数を1/2に）し、分周したパルスを OR 回路 802n に入力する。なお、分周器 801n の分周比は2でなくてもよいし、出力信号ごとに異ならせててもよい。また、分周器 801n の分周比が可変であってもよい。

#### 【0066】

OR 回路 802n が有する3つの入力端子のうち2つには分周器 801n から、残り1つには受光部 300n からの信号が入力される。OR 回路 802n は3つの入力信号の論理和信号をカウンタ回路 305n に入力する。2つのスイッチ 803n は受光部 300n 1、300n + 1 の出力信号を分周器 801n へ入力するかしないかを切り替える。ス

50

イッチ 803n は制御部 208 からの制御信号によって制御される。

【0067】

次に、各受光部 300n\_1、300n、300n+1 の出力信号がどのように重み付けされ、カウンタ回路 305n に入力されるかを説明する。ここで、受光部 300n\_1 の出力信号 PLSn\_1 の分周出力を DIVn\_1、受光部 300n+1 の出力信号 PLSn+1 の分周出力を DIVn+1、OR 回路 802n の出力を ORn とする。

【0068】

まず、制御部 208 により 2 つのスイッチ 803n がオンされる。これにより、2 つの受光部 300n\_1、300n+1 の出力信号 PLSn\_1、PLSn+1 がそれぞれ対応する分周器 801n に入力される。分周器 801n は出力信号 PLSn\_1、PLSn+1 を 2 分周する。分周器 801n は、出力信号 PLSn\_1、PLSn+1 に含まれるパルスの数を 1/2 に削減した信号 DIVn\_1、DIVn+1 を出力する。

10

【0069】

したがって、スイッチ 803n がいずれもオンの場合、OR 回路 802n には、信号 DIVn\_1、DIVn+1 と、受光部 300n の出力信号 PLSn とが入力される。なお各画素の受光部 300 の出力信号は、上下に隣接する 2 つの画素の分周器（図 8 の例では画素 800n\_1、801n+1 が有する分周器）にも入力される。

【0070】

分周器 801n を用いることにより、OR 回路 802n の 3 つの入力信号のうち、受光部 300n\_1 および 300n+1 の出力信号 PLSn\_1 および PLSn+1 には、受光部 300n の出力信号 PLSn に対して 1/2 の重みが付与される。あるいは、出力信号 PLSn の重みは、出力信号 PLSn\_1 および PLSn+1 の重みの 2 倍となる。OR 回路 802n は 3 つの入力信号の論理和信号 ORn をカウンタ回路 305n に入力する。そして、カウンタ回路 305n は論理和信号 ORn のパルス数をカウントする。

20

【0071】

このように、分周器 801n を用いることで、受光部 300 の出力信号に重み付けすることができる。そのため、分周器 801n の分周比を調整することにより、画像に適用するローパスフィルタの効果を調整することができる。

【0072】

次に、図 8 に示した画素 800n のフォトンのカウント動作について説明する。図 9 は、図 8 に示した画素 800n のフォトンのカウント動作の一例を示すタイミングチャートである。ここで、CNT\_RST と CNT\_EN は第 1 の実施形態と同様の信号であり、制御部 208 から供給される。本実施形態では、CNT\_RST が H レベルとなるとアップダウンカウンタ回路 501n のカウント値が 0 にリセットされ、CNT\_EN が H レベルの期間のみ、カウンタ回路 305n は入力パルスを計数する。すなわち、CNT\_EN は露光時間を制御する信号である。

30

【0073】

CNT\_RST を時刻 t900 で L レベルから H レベルにして、アップダウンカウンタ回路 501n のカウント値をリセットする。その後、時刻 t901 で CNT\_RST を H レベルから L レベルとする。

40

【0074】

また、時刻 t901 で受光部 300n\_1、300n、300n+1 にバイアス電圧 Vbias が供給され、フォトダイオード 301n\_1、301n、301n+1 には、降伏電圧以上のバイアス電圧が印加される。これにより、フォトダイオード 301n\_1、301n、301n+1 はガイガーモードで動作し、フォトンが入射するごとに出力信号 PLSn+1、PLSn、PLSn\_1 にパルスが発生する。また、時刻 t901 で CNT\_EN が H レベルとなり、カウンタ回路 305n はカウント動作を開始する。

【0075】

時刻 t902 において、受光部 300n+1 のフォトダイオード 301n+1 にフォトンが入射したことにより、受光部 300n+1 の出力信号 PLSn+1 に矩形状のパルス

50

が発生する。出力信号  $P L S_{n+1}$  は分周器  $801_n$  に入力される。本実施形態の分周器  $801$  は、 $2m$  ( $m$  は 1 以上の整数) 番目のパルスを出力し、 $2m-1$  番目のパルスは出力しないことにより、分周比 2 の分周を行う。そのため、この時点では分周器  $801_n$  の出力信号  $D I V_{n+1}$  のレベルは L レベルを維持する。他の受光部  $300_n$  および  $300_{n-1}$  のフォトダイオード  $301_n$  および  $301_{n-1}$  にはフォトンが入射していないため、OR 回路  $802_n$  の入力信号は全て L レベルである。したがって、OR 回路  $802_n$  の出力信号  $O R_n$  も L レベルを維持し、カウンタ回路  $305_n$  のカウント値も初期値 (0) を維持する。

#### 【0076】

時刻  $t903$ において、受光部  $300_n$  および  $300_{n-1}$  のフォトダイオード  $301_n$  および  $301_{n-1}$  にフォトンが入射したことにより、受光部  $300_n$  および  $300_{n-1}$  の出力信号  $P L S_n$  および  $P L S_{n-1}$  に矩形状のパルスが発生する。受光部  $300_n$  の出力信号  $P L S_{n-1}$  は分周器  $801_n$  に入力されるが、1 番目のパルスであるため、出力信号  $D I V_{n-1}$  は L レベルを維持する。しかし、受光部  $300_n$  の出力信号  $P L S_n$  のパルスが OR 回路  $802_n$  の出力信号  $O R_n$  に反映されるため、カウンタ回路  $305_n$  のカウント値が +1 される。

#### 【0077】

時刻  $t904$ において、受光部  $300_{n-1}$  のフォトダイオード  $301_n$  にフォトンが入射し、受光部  $300_{n-1}$  の出力信号  $P L S_{n-1}$  に矩形状のパルスが発生する。これは、受光部  $300_{n-1}$  の出力信号  $P L S_{n-1}$  に発生した 2 番目のパルスであるため、分周器  $801_n$  は、出力信号  $D I V_n$  にパルスを発生させる。このパルスが OR 回路  $802_n$  の出力信号  $O R_n$  に反映され、カウンタ回路  $305_n$  のカウント値が +1 される。

#### 【0078】

時刻  $t905$ において、受光部  $300_n+1$  のフォトダイオード  $301_{n+1}$  にフォトンが入射し、受光部  $300_n+1$  の出力信号  $P L S_{n+1}$  に矩形状のパルスが発生する。これは、受光部  $300_n+1$  の出力信号  $P L S_{n+1}$  に発生した 2 番目のパルスであるため、分周器  $801_n$  は、出力信号  $D I V_{n+1}$  にパルスを発生させる。このパルスが OR 回路  $802_n$  の出力信号  $O R_n$  に反映され、カウンタ回路  $305_n$  のカウント値が +1 される。

#### 【0079】

時刻  $t905$  以降、時刻  $t906$  で  $C N T\_E N$  が L レベルになり撮影が終了するまで、受光部  $300_n$ 、 $300_{n-1}$ 、 $300_{n+1}$  にフォトンが入射するごとに、出力信号  $P L S_n$ 、 $P L S_{n-1}$ 、 $P L S_{n+1}$  にパルスが発生する。出力信号  $P L S_n$  および  $P L S_{n+1}$  のパルスは 2 個ごとに、出力信号  $P L S$  のパルスは 1 個ごとに論理和信号  $O R_n$  に反映され、カウンタ回路  $305_n$  でパルス数がカウントされる。

#### 【0080】

時刻  $t906$  で撮影が終了した後、カウンタ回路  $305_n$  のカウント値は、垂直選択回路  $202$  および水平選択回路  $205$  の制御によりデジタル出力部  $206$  に出力され、さらに撮像素子  $101$  の外部に出力される。

#### 【0081】

ここで、分周器  $801_n$  による重み付けを行った場合と行わない場合との違いについて述べる。重み付けを行った場合、時刻  $t906$  におけるカウンタ回路  $305_n$  のカウント値は図 9 に示すように 7 である。分周器  $801_n$  による重み付けを行わず、受光部  $300_n$  および  $300_{n+1}$  の出力信号  $P L S_n$  および  $P L S_{n+1}$  をそのまま OR 回路  $802_n$  に入力したとすると、時刻  $t906$  におけるカウント値は 10 となる。いずれの場合も受光部  $300_n$  の出力信号  $P L S$  には重み付けが行われず、時刻  $t901$  から  $t906$  の間で出力信号  $P L S_n$  に発生した 4 つのパルスはそのまま OR 回路  $802_n$  に入力される。図 9 の例では、3 つの受光部  $300_n$ 、 $300_{n-1}$ 、 $300_{n+1}$  にフォトンが同時に入射していない。したがって、カウント値のうち、受光部  $300_n$  の出力信号

10

20

30

40

50

P L S<sub>n</sub>のパルスに起因するカウント値は4である。つまり、カウント値に占める受光部300nの出力信号P L S<sub>n</sub>の割合は、重み付けを行った場合には4/7、重み付けを行わない場合には4/10となる。受光部300n-1および300n+1の出力信号P L S<sub>n-1</sub>およびP L S<sub>n+1</sub>に、受光部300nの出力信号P L S<sub>n</sub>より低い重みを付与することにより、重み付けを行った場合にはカウント値に占める出力信号P L S<sub>n</sub>の割合を高めることができる。

#### 【0082】

このように、本実施形態の撮像装置は、単一フォトンの検出が可能な画素（受光部）が複数配列された撮像素子を、複数の画素の出力の重み付け加算結果を出力可能な構成とした。そして、重み付け加算結果を1つの画素の出力として用いることにより、簡単な構成で、隣接画素値信号の重み付けを行ったローパスフィルタを適用した画素出力を得ることができる。重み付けにより被写体のエッジ情報を残しつつ、ノイズの影響を低減した良好な画質の画像信号（画像）を得ることができる。

なお、制御部208を通じてスイッチ803nをいずれもオフすることで、フィルタを適用しないようにすることも可能である。

#### 【0083】

##### <第4の実施形態>

次に、本発明の第4の実施形態について説明する。第1から第3の実施形態では、撮影前にスイッチのオン・オフを制御することにより、撮影された画像に対する空間フィルタの適用有無や適用するフィルタの種類を選択するものであった。本実施形態は、撮影中にスイッチのオン・オフを制御することにより、複数のフレームに跨がった（時間軸方向）のフィルタの適用に関する制御を実現する。

#### 【0084】

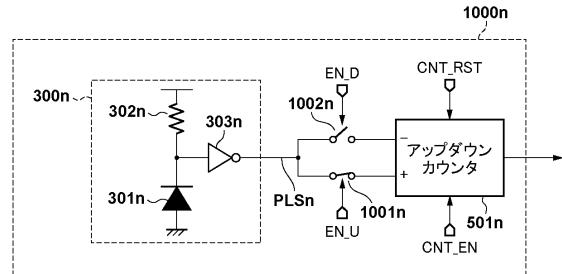

本実施形態は撮像素子101の画素アレイ200の構成以外、第1の実施形態と共にあってよい。そのため、以下では本実施形態における画素アレイ200の構成および動作について説明する。図10は、本実施形態における画素アレイ200に2次元配置される画素201に相当する画素1000nの等価回路図である。第1または第2の実施形態で説明した構成要素については図3または図5と同じ参照数字を付し、重複する説明は省略する。

#### 【0085】

スイッチ1001n、1002nは受光部300nの出力信号を、アップダウンカウンタ回路501nの+端子および-端子にどのように入力するか（あるいは入力しないか）を切り替える。スイッチ1001n、1002nは制御部208からの制御信号によって制御される。スイッチ1001n、1002nのオン、オフを撮影中に切り替えることにより、時間方向のフィルタを適用することができる。時間方向のフィルタを用いることにより、被写体の動きの有無を検出することができる。

#### 【0086】

次に、図10に示した画素1000nのフォトンのカウント動作について説明する。図11は、画素1000nのフォトンのカウント動作の一例を示すタイミングチャートである。なお、図11では、制御部208から供給される、スイッチ1001n、1002nのオン、オフを制御する信号をそれぞれE N\_U、E N\_Dとする。C N T\_R S TとC N T\_E Nは第1または第2の実施形態と同様の信号であり、制御部208から供給される。本実施形態では、C N T\_R S TがHレベルとなるとアップダウンカウンタ回路501nのカウント値が所定のオフセット値(>0)にリセットされ、C N T\_E NがHレベルの期間のみ、カウンタ回路305nは入力パルスを計数する。すなわち、C N T\_E Nは露光時間を制御する信号である。

#### 【0087】

C N T\_R S Tを時刻t1100でLレベルからHレベルにして、アップダウンカウンタ回路501nのカウント値をリセットし、オフセット値にする。その後、時刻t1101でC N T\_R S TをHレベルからLレベルとする。

## 【0088】

時刻  $t_{1101}$  で受光部 300n にバイアス電圧  $V_{bias}$  が供給される。フォトダイオード 301n には、降伏電圧以上のバイアス電圧が印加される。これにより、フォトダイオード 301n はガイガーモードで動作し、フォトンが入射することに出力信号  $PLS$  にパルスが発生する。また、時刻  $t_{1101}$  で  $CNT\_EN$  が H レベルとなり、アップダウンカウンタ回路 501n はカウント動作を開始する。

## 【0089】

時刻  $t_{1101}$  ではまた、 $EN\_U$  を H レベル ( $EN\_D$  は L レベルのまま) とし、スイッチ 1001n をオン、スイッチ 1002n をオフにする。これにより、受光部 300n の出力信号  $PLS$  は、アップダウンカウンタ回路 501n の + 端子だけに入力される。

10

## 【0090】

時刻  $t_{1102}$  において、受光部 300n のフォトダイオード 301n にフォトンが入射したことにより、出力信号  $PLS$  にパルスが発生する。このパルスはスイッチ 1001n を介してアップダウンカウンタ回路 501n の + 端子に入力され、アップダウンカウンタ回路 501n はカウント値を 1 増加 (+1) させる。

## 【0091】

時刻  $t_{1102}$  以降、時刻  $t_{1103}$  で  $EN\_U$  が L レベルになるまで、受光部 300n にフォトンが入射することに出力信号  $PLS$  にパルスが発生し、アップダウンカウンタ回路 501n のカウント値が増加する。ここで、 $EN\_U$  を H レベルにする期間 (時刻  $t_{1101}$  から時刻  $t_{1103}$  まで) を第 1 の撮像期間  $T_1$  とする。

20

## 【0092】

時刻  $t_{1103}$  で  $EN\_U$  を L レベルにしてスイッチ 1001n をオフする。これにより、受光部 300n の出力信号  $PLS$  がアップダウンカウンタ回路 501n の + 端子に入力されなくなる。この時点では、 $EN\_D$  も L レベルであるため、受光部 300n の出力信号  $PLS$  はアップダウンカウンタ回路 501n の - 端子にも入力されない。

## 【0093】

時刻  $t_{1104}$  において、 $EN\_D$  を H レベルにし、スイッチ 1002n をオンにする。これにより、受光部 300n の出力信号  $PLS$  がアップダウンカウンタ回路 501n の - 端子だけに入力されるようになる。

30

## 【0094】

時刻  $t_{1105}$  において、受光部 300n のフォトダイオード 301n にフォトンが入射したことにより、出力信号  $PLS$  にパルスが発生する。このパルスはスイッチ 1002n を介してアップダウンカウンタ回路 501n の - 端子に入力され、アップダウンカウンタ回路 501n はカウント値を 1 減少 (-1) させる。

## 【0095】

時刻  $t_{1105}$  以降、時刻  $t_{1106}$  で  $EN\_D$  が L レベルになるまで、受光部 300n にフォトンが入射することに出力信号  $PLS$  にパルスが発生し、アップダウンカウンタ回路 501n のカウント値が減少する。ここで、 $EN\_D$  を H レベルにする期間 (時刻  $t_{1104}$  から時刻  $t_{1106}$  まで) を第 2 の撮像期間  $T_2$  とする。なお、制御部 208 は、第 1 の撮像期間  $T_1$  と第 2 の撮像期間  $T_2$  とが等しく ( $T_1 = T_2$ ) なるように、 $EN\_U$  を H レベルにする期間  $T_1$  と  $EN\_D$  を H レベルにする期間  $T_2$  とを制御する。

40

## 【0096】

時刻  $t_{1106}$  で  $EN\_D$  を L レベルにするとスイッチ 1002n がオフされ、受光部 300n からの出力信号  $PLS$  がアップダウンカウンタ回路 501n の - 端子に入力されなくなる。また、 $CNT\_EN$  を L レベルとして、撮像を終了する。時刻  $t_{1106}$  で撮影が終了した後、画素 1000n のアップダウンカウンタ回路 501n のカウント値は、垂直選択回路 202 および水平選択回路 205 の制御によりデジタル出力部 206 に出力され、そして撮像素子 101 の外部に出力される。

## 【0097】

このように、2つの撮像期間におけるパルス数の差をカウントするように構成したので

50

、時間方向にフィルタを適用した画像信号を取得することができる。例えば、第1の撮像期間 $T_1$ と第2の撮像期間 $T_2$ を動画撮影中の連続するフレームの撮影期間とした場合、フレーム間で変化のない領域では画素値に変化がないため、第2の撮像期間 $T_2$ の終了時点におけるカウント値は初期値（オフセット値）となる。一方、フレーム間で変化があった領域については第2の撮像期間 $T_2$ の終了時点におけるカウント値がオフセット値とは異なる値となる。つまり、ある画素のカウント値がオフセット値であるか否かにより、その画素における被写体の変化（例えば動き）の有無を検出することができる。

#### 【0098】

このように、本実施形態の撮像装置は、單一フォトンの検出が可能な画素（受光部）が複数配列された像素子を、時間軸方向における画素値の差を出力可能な構成とした。そのため、簡単な構成で、画像間の変化の有無を検出する時間軸方向のフィルタを適用することができる。なお、制御部208を通じてスイッチ1002nを常にオフすることで、時間軸方向のフィルタを適用しないようにすることも可能である。したがって、例えば、監視カメラなどの常時稼働する機器に本実施形態の撮像装置を用いることで、容易に被写体の動きの有無を検出することが可能となる。

#### 【0099】

##### <第5の実施形態>

次に、本発明の第5の実施形態について説明する。第1から第4の実施形態においては、パルス数をカウントするカウンタを各画素に設けた構成について説明した。一方で、回路規模の増大を抑制する観点からは、カウンタを個々の画素に設けない方が良い。例えば、カウンタを像素子の周辺回路として画素外に配置し、画素（受光部）の出力信号をカウンタに転送する構成が考えられる。また、像素子を積層構造として、第1の基板に画素アレイを、第2の基板にカウンタを配置し、シリコン貫通電極（Through-Silicon Via : TSV）などを用いて第1の基板から第2の基板に画素（受光部）の出力信号を転送する構成も考えられる。しかし、前者の構成では、各画素から信号を転送する配線が必要となり、回路規模の増大や歩留まりの悪化などが想定される。

#### 【0100】

本実施形態は、第1から第4の実施形態に係る発明を実行可能で、かつ回路規模を抑制した構成の像素子を提供する。なお、本実施形態における「画素」は、第1から第4の実施形態における受光部に相当する。

#### 【0101】

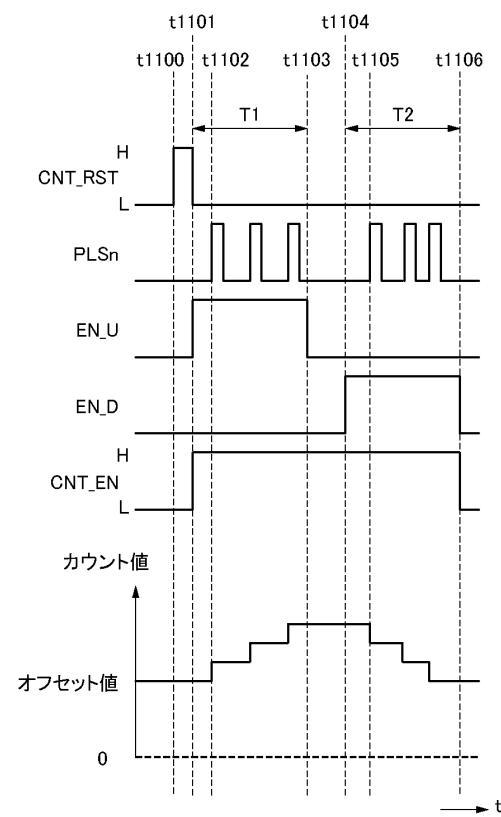

図12は、本発明の第5の実施形態に係る像素子101の画素アレイ200に含まれる画素1200を含む画素回路の構成を説明する。先の実施形態で説明した構成については同様の参照番号を付してある。

#### 【0102】

画素1200はアバランシェフォトダイオード（以下、単にフォトダイオードと呼ぶ）301、クエンチ抵抗302、比較回路1201を有する。図12では2つの画素を1200nと1200n+1と表記し、画素1200nの構成についてはnを、画素1200n+1の構成についてはn+1を付して区別する。なお、いずれの画素についても当てはまる事項については、添字をつけないで表記する。

#### 【0103】

比較回路1201は、フォトダイオード301の出力信号と、所定の比較信号 $V_{comp}$ とを比較し、比較結果を表す信号を出力する。なお、比較信号 $V_{comp}$ は後述する画素制御回路1221から供給される。本実施形態ではフォトダイオード301にフォトンが入射したことにより発生した電圧降下が閾値電圧 $V_{ref}$ を下回った際に、比較回路1201がHレベルを出力する。ここで閾値電圧 $V_{ref}$ は、フォトンがフォトダイオード301に入射した際に発生するパルス信号を検出可能であるとともに、VDDのノイズや隣接画素からのクロストークを誤検出しない電圧に設定する。また、フォトンがフォトダイオード301に入射した際に発生するパルス信号を検出しない電圧 $V_{dis}$ に比較信号 $V_{comp}$ を設定することにより、比較回路1201の出力を無効とすることが可能であ

10

20

30

40

50

る。

【0104】

図12に示す例では、2つの画素1200n 1および1200nが1つのOR回路1210に入力されている。OR回路1210は、画素1200n 1、1200nの出力信号のいずれかがHレベルの場合はHレベルを出力する。したがって、OR回路1210の出力信号は、画素1200n 1、1200nの出力信号の多重化信号と言うことができる。

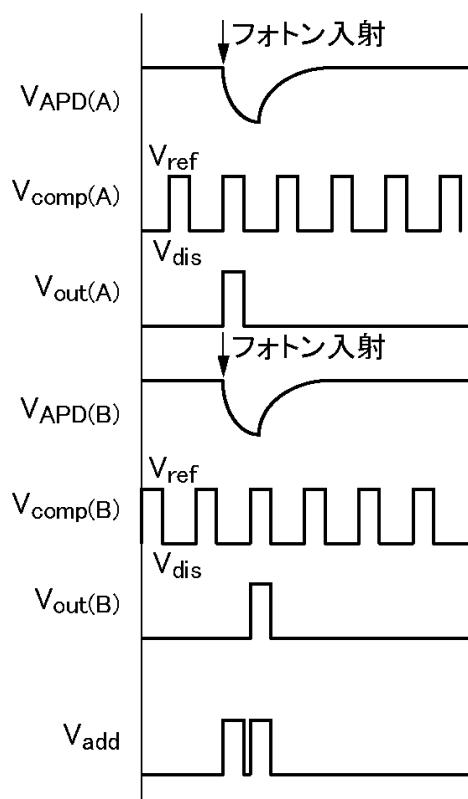

【0105】

次に、図13に示すタイミングチャートを用いて、図12に示した回路の動作について説明する。比較回路1201n 1に入力される比較信号Vcomp(A)は、周期t [s]で閾値電圧VrefとVdisが繰り返される矩形波である。Vcomp(A)が閾値電圧Vrefである期間に、フォトダイオード301aにフォトンが入射し、パルス電圧VAPD(A)が閾値電圧Vrefを下回ると、比較回路1201n 1の出力Vout(A)がHレベルとなる。すなわち、比較回路1201n 1のHレベル出力がOR回路1210に入力される期間は、Vcomp(A)が閾値電圧Vrefである期間に制限される。

10

【0106】

Vcomp(A)が電圧Vdisである期間は、フォトダイオード301の電圧VAPD(A)の値によらず比較回路1201n 1の出力はLレベルである。すなわちVcomp(A)が電圧Vdisである期間はパルスが出力されない。ここで、周期t [s]中、閾値電圧VrefとなるDuty比は50%以下である。より一般的には、1つのOR回路1210に入力される画素1200の数をN (Nは2以上の整数)とすると、Vcomp(A)が閾値電圧VrefとなるDuty比は1/N以下とする。また、フォトダイオード301にフォトンが入射した際に電圧VAPDに発生するパルス状の電圧変化が閾値電圧Vrefを下回る期間より周期t [s]を短い値に設定することで、フォトンの入射を取りこぼしなく検出することができる。

20

【0107】

図13では、フォトダイオード301n 1および301nに同時にフォトンが入射したときの動作を示している。本実施形態では1つのOR回路1210を共有する2つの比較回路1201n 1、1201nに入力する電圧Vcomp(A)、Vcomp(B)の位相をシフトしている。具体的にはVcomp(A)、Vcomp(B)が同時に閾値電圧Vrefにならないように位相をずらしている。

30

【0108】

換言すれば、周期t [s]の1周期の期間内において、共通のOR回路1210に接続される複数の画素1200について、比較回路1201からパルスが有効に出力される期間が重複しないようにVcompの位相を異なる。そうしないと、異なる画素1200のフォトダイオード301に同時にフォトンが入射した際、それぞれのフォトダイオード301の出力信号に発生するパルスがまとまった1つのパルスとしてカウントされてしまうからである。

40

【0109】

本実施形態の構成によれば、たとえフォトダイオード301n 1と301nとに同時にフォトンが入射した場合でも電圧VAPD(A)とVAPD(B)に発生するパルス状の電圧変化に基づくパルスが、異なる期間にOR回路1210に入力される。そのため、OR回路1210の出力信号Vaddには2個のパルスが含まれるようになり、実際に入射したフォトンの数が後段のカウンタ回路によって正しくカウントされる。

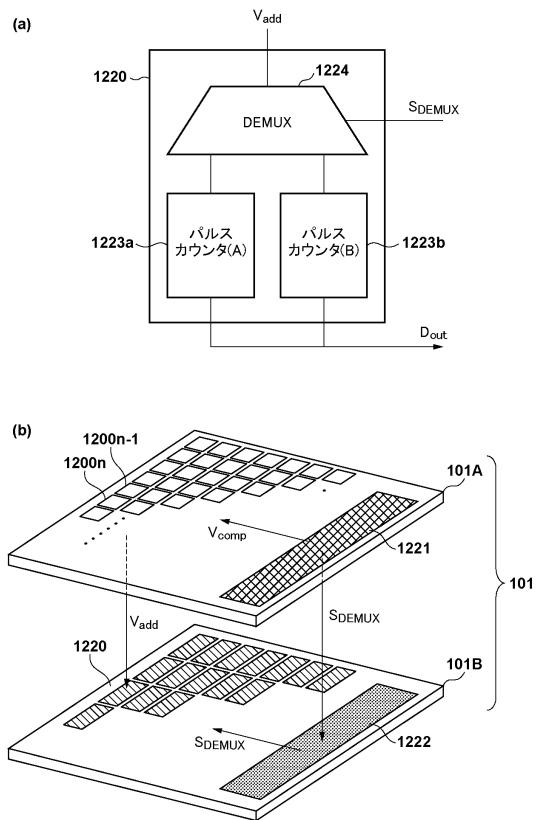

【0110】

次に図14(a)を用いて、本実施形態における信号処理回路の構成例について説明する。信号処理回路1220は後述するように、撮像素子101を構成する複数の基板のうち、画素アレイが設けられない基板に設けられる。信号処理回路1220は、デマルチプレクサ(DEMUX)1224と、パルスカウンタ1223a, 1223bとを有する。

50

デマルチプレクサ 1224 には OR 回路 1210 の出力信号 Vadd が入力され、制御信号 SDEMUX に従って、Vadd に含まれるパルスをパルスカウンタ 1223a, 1223b に振り分ける多重分離動作を行う。制御信号 SDEMUX は後述するデマルチプレクサ制御回路 1222 から供給される。

【0111】

制御信号 SDEMUX は、Vadd に含まれる、画素 1200n 1 由来のパルスと、画素 1200n 由来のパルスを分離し、前者をパルスカウンタ 1223a に、後者をパルスカウンタ 1223b に供給する。パルスカウンタ 1223a, 1223b は、デマルチプレクサ 1224 から供給される信号に含まれるパルスの数をカウントする。パルスカウンタ 1223a は画素 1200n 1 に入射したフォトンの数を、パルスカウンタ 1223b は画素 1200n に入射したフォトンの数をそれぞれカウントする。パルスカウンタ 1223a, 1223b は制御部 208 から供給されるパルスカウンタ制御信号に従ってカウント値を信号処理回路 1220 の外部に出力し、カウント値をリセットする。

【0112】

次に、図 14 (b) を用いて、本実施形態に係る撮像素子 101 の構成例について説明する。撮像素子 101 は第 1 基板 101A と第 2 基板 101B とが積層された構造を有する。第 1 基板 101A と第 2 基板 101B とは例えば TSV によって電気的に接続される。第 1 基板 101A には複数の画素 1200 が行列状に配列された画素アレイ 200 が形成される。

【0113】

ここで、OR 回路 1210、画素制御回路 1221 は第 1 基板 101A に含まれる。一方、第 2 基板 101B には、第 1 基板 101A に設けられた複数の OR 回路 1210 に対応して設けられ、OR 回路 1210 の出力信号 Vadd を受信する複数の信号処理回路 1220 と、デマルチプレクサ制御回路 1222 とを有する。

【0114】

デマルチプレクサ制御回路 1222 は第 1 基板 101A の画素制御回路 1221 から制御信号 SDEMUX を受信する。そして、デマルチプレクサ制御回路 1222 は、第 2 基板 101B に設けられている複数の信号処理回路 1220 が有するデマルチプレクサ 1224 に対し、制御信号 SDEMUX を供給する。これにより個々の信号処理回路 1220 に含まれるデマルチプレクサ 1224 は、OR 回路 1210 の出力信号 Vadd に含まれる、複数の画素 1200 由来のパルスを、画素ごとのパルスに分離する。

【0115】

本実施形態では、2つの画素 1200 の出力信号を OR 回路 1210 によって1系統の信号に多重化している。そのため、画素アレイ 200 が設けられる第 1 基板 101A と信号処理回路 1220 が設けられる第 2 基板 101B とを接続するためのビアや TSV といった電極の数を半減させることができるために、回路規模を抑制可能である。なお、ビアや TSV の数を半減させず、1つの画素を対応する信号処理回路 1220 と2つの経路で並列に接続することで、接続の信頼性を向上させてもよい。なお、撮像素子 101 を積層構造とすることは必須ではなく、信号処理回路 1220 やデマルチプレクサ制御回路 1222 を画素アレイの周辺回路として同じ基板上に設ける構成としてもよい。この場合も、OR 回路 1210 による多重化によって画素と信号処理回路 1220 との間の配線を半減させることができ、回路規模の抑制につながる。また、OR 回路 1210 が多重化する信号の数 (OR 回路 1210 を共用する画素 1200 の数) は 3 以上であってもよい。

【0116】

また、本実施形態では比較回路 1201 に対してフォトダイオード 301 の信号を入力する構成について説明した。しかし、フォトダイオード 301 の信号をカウンタに同期信号として入力する構成としてもよい。比較回路 1201 を制御する信号を同期信号として使用することで、カウンタ回路を同期カウンタで構成することも可能となる。

【0117】

< 第 6 の実施形態 >

10

20

30

40

50

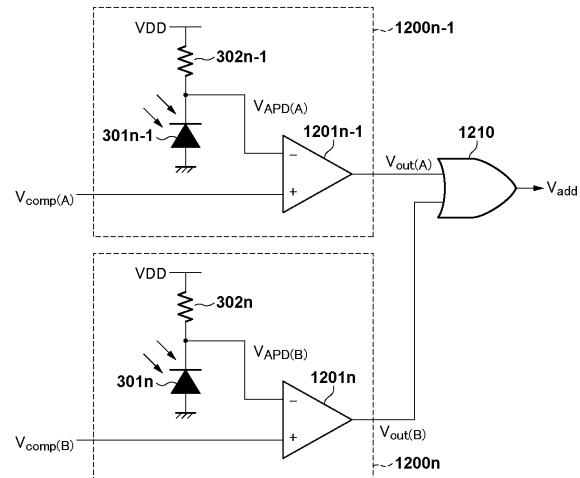

次に、本発明の第6の実施形態について説明する。第5の実施形態では、OR回路1210の出力信号をデマルチプレクサ1224で分離する構成であった。しかし、OR回路1210の出力をそのままパルスカウンタ1223に入力してパルス数をカウントする構成とすれば、OR回路1210を共有する画素1200の加算信号を得ることができる。この場合、デマルチプレクサ1224はOR回路1210の出力信号を分離せずにパルスカウンタ1223a, 1223bの一方に供給する。

#### 【0118】

従来、撮像素子の解像度（画素数）よりも低い解像度の画像を取得する方法として、加算読み出しありは画素混合と呼ばれる方法が知られている。また、画像の解像感を高めたり色重心ずれを補正するために、画素信号の加重加算を行う場合もある。これらの加算処理をアナログ画素信号について行う場合に専用のアナログ回路が必要となるため、回路規模が増大する。一方、画素信号をデジタル化して加算処理する場合、計算処理が必要となる。本実施形態では、専用回路も計算処理も必要とせずに画素信号の加重加算を実現する構成について説明する。

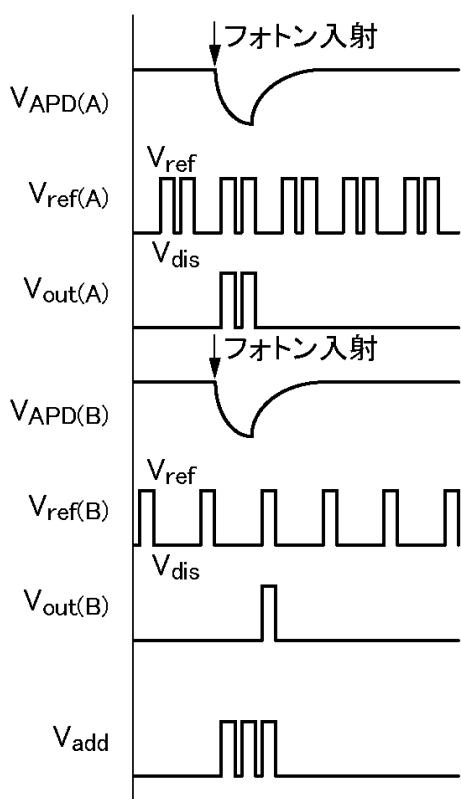

#### 【0119】

図15は、図12に示した構成の画素1200n 1, 1200nの信号を、2:1で加重加算して出力するためのタイミングチャートである。図13と同様、ここでも画素1200n 1, 1200nのフォトダイオード301n 1, 301nに同時にフォトンが入射した場合について示している。基本的な動作は第5の実施形態で図13に関して説明しているため、異なる点のみを説明する。本実施形態においても、「画素」は、第1から第4の実施形態における受光部に相当する。

#### 【0120】

本実施形態では、比較回路1201へ入力する電圧Vcompが閾値電圧Vrefとなる回数を画素ごとに異ならすことによって、画素信号に異なる重み付けを行う。ここでは、画素1200n 1の信号に画素1200nの信号の2倍の重みを付与するため、比較回路1201n 1に入力するVcomp(A)が閾値電圧Vrefとなる期間を1周期あたり2回としている。一方で比較回路1201nへ入力する電圧Vcomp(B)が閾値電圧Vrefである期間は、1周期の間に1回のままとする。

#### 【0121】

このように、フォトダイオード301で発生するパルス状の電圧変化を比較回路1201から出力可能な期間に、電圧Vcompが閾値電圧Vrefとなる回数を、付与する加重比率に応じて異ならせる。これにより、比較回路1201n 1の出力信号Vout(A)は、フォトダイオード301n 1に入射する1つのフォトンあたり2つのパルスを含むようになる。一方、比較回路1201nの出力信号Vout(B)は、フォトダイオード301nに入射する1つのフォトンあたり1つのパルスを含む。これら出力信号Vout(A)およびVout(B)をOR回路1210にそのまま入力することで、OR回路1210からは3つのパルスを含んだ出力信号ORnが得られる。

#### 【0122】

信号処理回路1220の構成は第5の実施形態の図14(a)で説明した通りでよく、信号処理回路1220の出力信号Vaddはデマルチプレクサ1224に入力される。デマルチプレクサ1224はデマルチプレクサ制御回路1222が出力する制御信号SDEMUXにより制御されるが、本実施形態では出力信号Vaddの多重分離を行わず、そのままパルスカウンタ1223aまたは1223bの一方に入力する。

#### 【0123】

これによりパルスカウンタ1223はVaddに含まれる全てのパルスをカウントするため、加重加算された画素値がカウント値として得られる。なお、デマルチプレクサ制御回路1222は制御信号SDEMUXを通して、デマルチプレクサ1224を動作させるモードと、動作をさせないモード（加算モード）を切り替えてよい。常に加算を行う場合にはデマルチプレクサ1224やデマルチプレクサ制御回路1222を省略してもよい。

#### 【0124】

10

20

30

40

50

本実施形態によれば、フォトン1つの入射によって生じるパルス状の電圧変化から重みに応じた数のパルスを生成するように制御することにより、専用の回路や計算処理を必要とせずに、加重加算した画素信号を得ることができる。

【0125】

<第7の実施形態>

次に、本発明の第7の実施形態について説明する。本実施形態に係る撮像素子は、複数のAPDで1つのマイクロレンズを共有する構成とすることで、撮像信号とともに位相差AF用の信号も得ることが可能な撮像素子である。N個（Nは2以上の整数）のAPDで1マイクロレンズを共有する構成では、通常の構成（1マイクロレンズあたり1つのAPD）に対し、必要なカウンタの数がN倍となる。本実施形態は、N個（Nは2以上の整数）のAPDで1マイクロレンズを共有する構成の撮像素子において、必要なカウンタの数をN倍よりも少なくするものである。

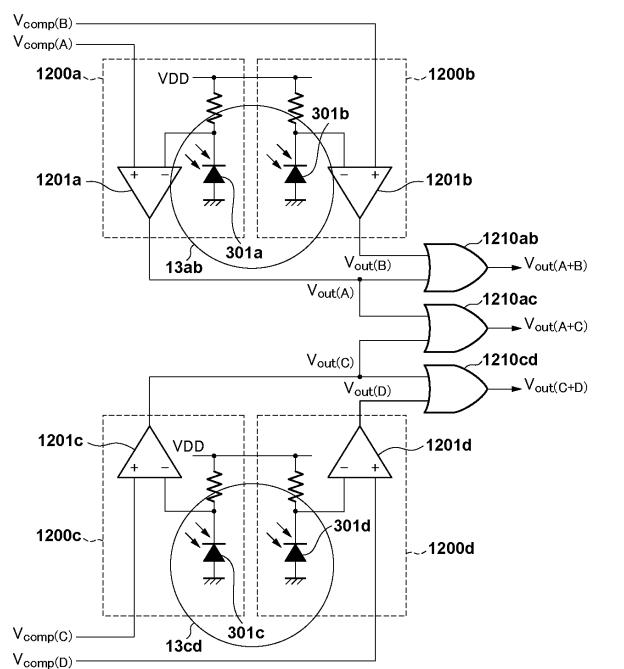

【0126】

図16は本実施形態に係る撮像素子の一例としての、1つのマイクロレンズを2つの画素で共有する構成の撮像素子の画素構成例を示す等価回路図である。画素1200の構成は第5の実施形態と同等であるが、画素1200a、1200bで1つのマイクロレンズ13abを共有するため、対応する射出瞳の領域が異なる。また、同様に、画素1200c、1200dで1つのマイクロレンズ13cdを共有している。本実施形態においても、「画素」は、第1から第4の実施形態における受光部に相当する。

【0127】

画素1200aと1200cは、対応する射出瞳の領域が等しい。また、画素1200b、1200dも、対応する射出瞳の領域が等しい。OR回路1210は、4つの画素の出力信号を加算する組み合わせに応じて3つ設けられている。OR回路1210abはマイクロレンズ13abを共有する画素1200a、1200bの出力信号の論理和信号を出力する。OR回路1210cdは、マイクロレンズ13cdを共有する画素1200c、1200dの出力信号の論理和信号を出力する。一方、OR回路1210acは、画素1200a、1200cの出力信号の論理和信号を出力する。

【0128】

次に、図17のタイミングチャートを用いて、図16に示した回路の動作について説明する。図17は、フォトダイオード301a、301b、301c、301dに同時にフォトンが入射したときの動作を示している。

【0129】

OR回路1210abを共有する比較回路1201a、1201bに入力する電圧Vc<sub>omp</sub>(A)、Vc<sub>omp</sub>(B)は、第5の実施形態で図13を用いて説明したように、同時に閾値電圧Vrefにならないように位相が制御されている。OR回路1210cdを共有する比較回路1201c、1201dに入力する電圧Vc<sub>omp</sub>(C)、Vc<sub>omp</sub>(D)についても同様に位相が制御されている。

【0130】

OR回路1210abからは、マイクロレンズ13abを共有する画素1200a、1200bの出力信号の論理和信号が、撮像信号Vout(A+B)として出力される。また、OR回路1210cdからは、マイクロレンズ13cdを共有する画素1200c、1200dの出力信号の論理和信号が、撮像信号Vout(C+D)として出力される。

【0131】

OR回路1210acを共有する比較回路1201a、1201cに入力する電圧Vc<sub>omp</sub>(A)、Vc<sub>omp</sub>(C)についても、同時に閾値電圧Vrefにならないように位相が制御されている。OR回路1210acからは、射出瞳内の同じ部分領域に対応する画素1200a、1200cの出力信号の論理和信号が、焦点検出用信号Vout(A+C)として出力される。

【0132】

OR回路1210ab、1210cd、1210acの出力信号は、それぞれ対応する

10

20

30

40

50

信号処理回路 1220 に転送され、分離されることなく 1 つのパルスカウンタでカウントされる。位相差 AF には画素 1200c と 1200d の出力信号の論理和信号である焦点検出用信号  $V_{out}(B + D)$  も必要である。本実施形態では  $V_{out}(A + B) + V_{out}(C + D) = V_{out}(B + D)$  という関係を用い、焦点検出用信号  $V_{out}(B + D)$  を演算によって求める。

#### 【0133】

なお、垂直方向に加算を行わない場合、画素 1200a, 1200b からは  $V_{out}(A + B)$  と、 $V_{out}(A)$  および  $V_{out}(B)$  の一方を出力するようにしてもよい。この場合、 $V_{out}(A)$  および  $V_{out}(B)$  の他方は、 $V_{out}(A + B)$  に含まれる第 1 のパルスの数と、 $V_{out}(A)$  および  $V_{out}(B)$  の一方に含まれる第 2 のパルスの数との差として演算により求めることができる。10

#### 【0134】

1 対の焦点検出用信号のずれ量を求めるための相關演算を行う際、水平方向の解像度は検出可能な空間周波数への影響が大きいのに対し、垂直方向の解像度は影響が小さい。そのため、本実施形態においては、水平方向に並んだ 2 つの画素 1200 で 1 つのマイクロレンズ 13 を共有する構成において、垂直方向に隣接する 2 つの画素 1200 の信号を加算して焦点検出用信号  $V_{out}(A + C)$  を求めている。加算によってノイズ低減効果が得られるため、低輝度な被写体に対しても精度よく焦点検出したい場合に特に有効である。なお、焦点検出用信号  $V_{out}(B + D)$  を演算によって求める処理は、例えば DSP 103 で実行することができる。20

#### 【0135】

この場合、DSP 103 は、撮像素子 101 からの出力  $D_{out}$  のうち、撮像信号  $V_{out}(A + B)$ ,  $V_{out}(C + D)$  と、焦点検出用信号  $V_{out}(A + C)$  を用いて焦点検出用信号  $V_{out}(B + D)$  を算出する。そして、DSP 103 は、1 対の焦点検出用信号  $V_{out}(A + C)$ ,  $V_{out}(B + D)$  のずれ量（位相差）を相關演算によって求め、CPU 105 に通知する。CPU 105 は、ずれ量を光学系 102 のデフォーカス量に変換し、デフォーカス量に基づいて光学系 102 が有するフォーカシングレンズを駆動することにより、位相差検出方式の自動焦点検出を行うことができる。

#### 【0136】

このように、本実施形態では、單一フォトンの検出が可能な画素（受光部）が複数配列された撮像素子において、複数の画素が 1 つのマイクロレンズを共有する構成とした場合に、画像信号、焦点検出用信号とも、複数の画素信号を加算して出力する構成とした。それにより、必要なカウンタの数を画素の数より少なくすることができる。30

#### 【0137】

##### （その他の実施形態）

本発明は、上述の実施形態の 1 以上の機能を実現するプログラムを、ネットワーク又は記憶媒体を介してシステム又は装置に供給し、そのシステム又は装置のコンピュータにおける 1 つ以上のプロセッサーがプログラムを読み出し実行する処理でも実現可能である。また、1 以上の機能を実現する回路（例えば、ASIC）によっても実現可能である。

#### 【符号の説明】

#### 【0138】

300…受光部、301…フォトダイオード、302…クエンチ抵抗、303…反転バッファ、304、802…OR 回路、305…カウンタ回路、306、502、803、1001、1002…スイッチ、501…アップダウンカウンタ回路、801…分周器

【図面】

【図 1】

【図 2】

10

20

【図 3】

【図 4】

30

40

50

【図 5】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

10

20

30

40

【図 11】

【図 12】

50

【図 1 3】

【図 1 4】

【図 1 5】

【図 1 6】

10

20

30

40

50

【図 1 7】

## フロントページの続き

(51)国際特許分類

|        |        |   |

|--------|--------|---|

| F I    |        |   |

| H 01 L | 27/146 | F |

| H 01 L | 27/146 | D |

(56)参考文献

特開2016-223952 (JP, A)

国際公開第2017/132600 (WO, A1)

特開2006-033452 (JP, A)

特開2011-071958 (JP, A)

米国特許出願公開第2013/0300838 (US, A1)

(58)調査した分野 (Int.Cl., DB名)

H 04 N 5 / 30 - 378

H 01 L 27 / 14 - 148