(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3640175号

(P3640175)

(45) 発行日 平成17年4月20日(2005.4.20)

(24) 登録日 平成17年1月28日(2005.1.28)

(51) Int.C1.<sup>7</sup>

F 1

|         |         |         |       |         |

|---------|---------|---------|-------|---------|

| G 1 1 C | 16/04   | G 1 1 C | 17/00 | 6 2 3 Z |

| G 1 1 C | 16/02   | G 1 1 C | 17/00 | 6 1 2 F |

| G 1 1 C | 16/06   | G 1 1 C | 17/00 | 6 3 4 Z |

| H 0 1 L | 21/8247 | G 1 1 C | 17/00 | 6 3 3 B |

| H 0 1 L | 27/115  | H 0 1 L | 29/78 | 3 7 1   |

請求項の数 16 (全 23 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2001-115678 (P2001-115678)  |

| (22) 出願日  | 平成13年4月13日 (2001.4.13)        |

| (65) 公開番号 | 特開2002-313090 (P2002-313090A) |

| (43) 公開日  | 平成14年10月25日 (2002.10.25)      |

| 審査請求日     | 平成14年5月21日 (2002.5.21)        |

|           |                                               |

|-----------|-----------------------------------------------|

| (73) 特許権者 | 000002369<br>セイコーエプソン株式会社<br>東京都新宿区西新宿2丁目4番1号 |

| (74) 代理人  | 100090479<br>弁理士 井上 一                         |

| (74) 代理人  | 100090387<br>弁理士 布施 行夫                        |

| (74) 代理人  | 100090398<br>弁理士 大渕 美千栄                       |

| (72) 発明者  | 亀井 輝彦<br>長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内        |

審査官 小松 正

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

1つのワードゲートと、第1，第2のコントロールゲートにより制御される第1，第2の不揮発性メモリ素子とを有するメモリセルを、列方向及び行方向にそれぞれ複数配列してなるメモリセルアレイ領域と、

前記メモリセルアレイ領域内の前記複数のメモリセルの各々の前記第1，第2のコントロールゲートを駆動するコントロールゲート駆動部と、

を有し、

前記メモリセルアレイ領域は、前記行方向で分割された複数のセクタ領域を有し、

前記複数のセクタ領域の各々は、前記行方向で複数に分割された複数のブロックを有し 10

、

前記コントロールゲート駆動部は、前記複数のセクタ領域の各一つについてそれぞれ複数のコントロールゲートドライバを有し、前記複数のコントロールドライバの各々は、前記複数のブロックのうち1以上のブロックに対応して配置され、かつ、対応ブロック内の全メモリセルの前記第1及び第2のコントロールゲートの電位を設定することを特徴とする不揮発性半導体記憶装置。

## 【請求項 2】

請求項1において、

前記複数のブロックは、前記列方向で複数に分割された複数のラージブロックと、前記複数のラージブロックの各々を前記列方向でさらに細分割された複数のスマールブロック

を有し、

前記複数のコントロールドライバの各々は、前記複数のラージブロックの各々に対応して配置され、かつ対応するラージブロックに設けられた前記複数のスマートブロック内に配置された全メモリセルの前記第1及び第2のコントロールゲートの電位を設定することを特徴とする不揮発性半導体記憶装置。

【請求項3】

請求項1において、

前記複数のブロックは、前記列方向で複数に分割された複数のラージブロックと、前記複数のラージブロックの各々を前記列方向でさらに細分割された複数のスマートブロックを有し、

10

前記複数のコントロールドライバの各々は、前記複数のラージブロックの各々に設けられた前記複数のスマートブロックの各々に対応して設けられ、かつ、対応するスマートブロックに配置された全メモリセルの前記第1及び第2のコントロールゲートの電位を設定することを特徴とする不揮発性半導体記憶装置。

【請求項4】

請求項1乃至3のいずれかにおいて、

前記複数のコントロールゲートドライバは、一つのセクタ領域内のデータ消去時に、該一つのセクタ領域内の全ての前記第1、第2のコントロールゲートに第1の消去用高電位を供給して、前記複数のセクタ領域の各々にて一括してデータを消去することを特徴とする不揮発性半導体記憶装置。

20

【請求項5】

請求項4において、

前記複数のセクタ領域の各々には、前記列方向に沿って形成された複数のコントロールゲート線が設けられ、

前記コントロールゲート駆動部は、前記複数のセクタ領域の各々に配置された前記複数のコントロールゲート線の各々に、ゲート回路を経由せずに直接接続されていることを特徴とする不揮発性半導体記憶装置。

【請求項6】

請求項5において、

前記複数のコントロールゲート線は、

30

前記コントロールゲート駆動部に直接接続された複数のメインコントロールゲート線と、

前記複数のメインコントロールゲート線と前記複数のメモリセルの前記第1、第2のコントロールゲートとを接続する複数のサブコントロールゲート線と、

を含むことを特徴とする不揮発性半導体記憶装置。

【請求項7】

請求項6において、

前記複数のセクタ領域の各々に設けられた偶数のメインコントロールゲート線には、偶数列の前記複数メモリセルの各々の前記第2のコントロールゲートと奇数列の前記複数メモリセルの各々の前記第1のコントロールゲートとが共通接続された複数のサブコントロールゲートが接続され、前記複数のセクタ領域の各々に設けられた奇数のメインコントロールゲート線には、奇数列の前記複数メモリセルの各々の前記第2のコントロールゲートと偶数列の前記複数メモリセルの各々の前記第1のコントロールゲートとが共通接続された複数のサブコントロールゲート線が接続されていることを特徴とする不揮発性半導体記憶装置。

40

【請求項8】

請求項7において、

前記複数のセクタ領域の各々に対応して設けられた前記複数のコントロールゲートドライバの各々には、k本のメインコントロールゲート線が接続され、

前記複数のセクタ領域の各々には、k本のサブコントロールゲート線が接続されるメモ

50

リセル群からなる各入出力ビットに対応したメモリブロックが、前記行方向に複数配置され、

前記行方向に沿って延びる複数の配線が設けられ、前記  $k$  本のメインコントロールゲート線の各々と、それと対応する前記  $k$  本のサブコントロールゲート線の各々とが、前記複数の配線の各々を介してそれぞれ接続されていることを特徴とする不揮発性半導体記憶装置。

**【請求項 9】**

請求項 8 において、

前記メモリブロックの前記行方向に沿ったメモリセル数を 4 とし、 $k = 4$  に設定したことと特徴とする不揮発性半導体記憶装置。 10

**【請求項 10】**

請求項 1 乃至 9 のいずれかにおいて、

前記複数のセクタ領域の各々には、

前記列方向に沿って形成された複数のビット線と、

少なくともデータのプログラム時及び読み出し時に、前記複数のビット線を駆動するビット線駆動部と、

がさらに設けられていることを特徴とする不揮発性半導体記憶装置。

**【請求項 11】**

請求項 10 において、

一つのセクタ領域毎のデータ消去時に、該一つのセクタ領域に形成された前記複数のビット線に第 2 の消去用高電位を供給する消去用ビット線駆動部がさらに設けられていることを特徴とする不揮発性半導体記憶装置。 20

**【請求項 12】**

請求項 10 または 11 において、

前記複数のビット線は、不純物層にて形成されていることを特徴とする不揮発性半導体記憶装置。

**【請求項 13】**

請求項 12 において、

前記複数のセクタ領域の各々は、他のセクタと分離された一つのウェル領域に形成され、前記ウェル領域に第 2 の消去用高電位を供給する消去用ウェル駆動部が設けられていることを特徴とする不揮発性半導体記憶装置。 30

**【請求項 14】**

請求項 12 または 13 において、

前記不純物層にて形成された前記複数のビット線の各々にそれぞれ接続される複数のメインビット線が設けられ、前記複数のメインビット線から前記複数のビット線にそれぞれ至る各経路途中に、ゲート回路が設けられていないことを特徴とする不揮発性半導体記憶装置。

**【請求項 15】**

請求項 1 乃至 14 のいずれかにおいて、

前記メモリセルアレイ領域には、前記行方向に沿って配列された前記複数のメモリセルの各々の前記ワードゲートにそれぞれ共通接続された複数のワード線が、前記行方向に沿って設けられ、

前記メモリセルアレイ領域の前記行方向の一端には、前記複数のワード線を駆動するワード線駆動部が設けられていることを特徴とする不揮発性半導体記憶装置。

**【請求項 16】**

請求項 1 乃至 15 のいずれかにおいて、

前記第 1 , 第 2 の不揮発性メモリ素子の各々は、酸化膜 (O) 、窒化膜 (N) 及び酸化膜 (O) からなるONO膜を電荷のトラップサイトとして有することを特徴とする不揮発性半導体記憶装置。

**【発明の詳細な説明】**

**【0001】****【発明の属する技術分野】**

本発明は、1つのワードゲートと、2つのコントロールゲートにより制御される2つの不揮発性メモリ素子を備えたメモリセルにて構成される不揮発性半導体記憶装置に関する。

**【0002】****【背景技術】**

不揮発性半導体装置として、チャネルとゲートとの間のゲート絶縁層が、酸化シリコン膜、窒化シリコン膜及び酸化シリコン膜の積層体からなり、窒化シリコン膜に電荷がトラップされるMONOS(Metal-Oxide-Nitride-Oxide-Semiconductorまたは-substrate)型が知られている。

10

**【0003】**

このMONOS型不揮発性半導体記憶装置は、文献(Y.Hayashi,et al,2000 Symposium on VLSI Technology Digest of Technical Papers p.122-p.123)に開示されている。この文献には、1つのワードゲートと、2つのコントロールゲートにより制御される2つの不揮発性メモリ素子(MONOSメモリセル)を備えたツインMONOSフラッシュメモリセルが開示されている。すなわち、1つのフラッシュメモリセルが、電荷のトラップサイトを2つ有している。

**【0004】**

このような構造を有する複数のツインMONOSフラッシュメモリセルを行方向及び列方向にそれぞれ複数配列させて、メモリセルアレイ領域が構成される。

20

**【0005】****【発明が解決しようとする課題】**

このツインMONOSフラッシュメモリセルを駆動するには、2本のビット線と、1本のワード線と、2本のコントロールゲート線とを要する。ただし、多数のメモリセルを駆動するに際して、異なるコントロールゲートであっても同じ電位に設定する場合には、これらの線を共通接続することができる。

**【0006】**

ここで、フラッシュメモリの動作には、データの消去、プログラム及び読み出しがある。データのプログラム及び読み出しへは、通常、8ビットまたは16ビットの選択セルにて同時に実施されるが、データの消去はさらに広い範囲で同時に実施できる。

30

**【0007】**

ここで、この種の不揮発性メモリでは、データのディスターブが課題となっている。データのディススターブとは、選択セルのコントロールゲート線及びビット線に高電位を印加してプログラムまたは消去するときに、共用される配線によって非選択セクタ領域内のセルにも高電位が印加され、プログラムの度にその状態が繰り返されることでプログラムまたは消去されて、非選択セルのデータがディスターブされることを言う。

**【0008】**

このような事態を防止するには、選択ゲート回路を設けて、選択セクタのセルにのみ高電位が印加され、非選択セクタのセルには高電位が印加されないようにすることができる。

**【0009】**

40

しかし、このようにすると、選択ゲート回路のために面積を占有され、メモリセルの高集積化が妨げられる。さらには、選択ゲートにて電圧降下が生ずると、プログラム時または消去時に選択セクタのセルに高電位を供給するために、電圧降下分を上乗せして供給する必要がある。結果的に、低電圧駆動が妨げられ、特に携帯機器のように低消費電力化が求められる機器には不適合となる。

**【0010】**

さらに、今後は携帯機器等から高速にてデータをリードする要求が高まるが、高速駆動の点でも改善の余地があった。

**【0011】**

そこで、本発明は、選択セルでのプログラム時または消去時に非選択セクタのセルにてデ

50

ータがディスターブされることを回避しながら、しかも選択ゲート回路を要せずに高集積化が可能な不揮発性半導体記憶装置を提供することにある。

【0012】

本発明の他の目的は、選択ゲート回路を不要とすることで電圧降下を回避して、消費電力を低減することができる不揮発性半導体装置を提供することにある。

【0013】

本発明のさらに他の目的は、高電位が供給されるコントロールゲート線の負荷容量を低減して高速駆動を可能とした不揮発性半導体記憶装置を提供することにある。

【0014】

【課題を解決するための手段】

本発明の一態様に係る不揮発性半導体記憶装置は、1つのワードゲートと、2つのコントロールゲートにより制御される2つの不揮発性メモリ素子を有するメモリセルを、列方向及び行方向にそれぞれ複数配列してなるメモリセルアレイ領域を有する。不揮発性半導体記憶装置はさらに、メモリセルアレイ領域内の複数のメモリセルの各々の第1，第2のコントロールゲートを駆動するコントロールゲート駆動部を有する。

【0015】

メモリセルアレイ領域は、行方向で分割された複数のセクタ領域を有する。この複数のセクタ領域の各々は、行方向に沿った複数の各列にそれぞれ配列された複数のメモリセルを有する。

【0016】

複数のセクタ領域の各々は、列方向で複数に分割された複数のブロックを有する。コントロールゲート駆動部は、複数のセクタ領域の各一つについてそれぞれ複数のコントロールゲートドライバを有する。この複数のコントロールドライバの各々は、複数のブロックのうちの互いに異なる1以上のブロックに配置された全メモリセルの前記第1及び第2のコントロールゲートの電位を設定する。

【0017】

本発明の一態様によれば、ある一つのセクタ領域内のある一つのブロックに配置された選択セルについてプログラムする際には、そのセクタ領域内で選択されたブロックに配置されたメモリセル（選択セル及び非選択セル）のコントロールゲート電位のみを、対応するコントロールゲートドライバによってプログラム電位とする。選択セクタ内の他のブロック及び非選択セクタ領域では、それに対応するコントロールゲートドライバによって、プログラム電位以外の電位に設定できるので、非選択のセクタ領域内の非選択セルにてデータがディスターブされることがない。しかもこのことは、選択ゲート回路を用いずに達成できるため、メモリセルを高集積化することができる。また、選択ゲート回路での電圧降下も生じないので、低電圧駆動が可能となり、特に携帯機器のメモリとして有効に利用できる。さらには、一つのコントロールゲートドライバには一つのブロック内のメモリセルのみが接続されるので、一つのセクタ領域内の全てのメモリセルを接続するものと比較して、コントロールゲート線に接続される負荷容量（ゲート容量）が低減される。よって、メモリの高速駆動も可能となる。

【0018】

複数のブロックとして、列方向で複数に分割された複数のラージブロックと、その複数のラージブロックの各々を列方向でさらに細分割された複数のスマールブロックを有することができる。

【0019】

この場合、複数のコントロールドライバの各々は、複数のラージブロックのうちの互いに異なる一つに配置され、かつ複数のスマールブロック内に配置された全メモリセルの第1及び第2のコントロールゲートの電位を設定することができる。

【0020】

あるいは、複数のコントロールドライバの各々は、複数のラージブロックの各々について互いに異なる一つのスマールブロックに配置された全メモリセルの前記第1及び第2のコ

10

20

30

40

50

ントロールゲートの電位を設定することができる。

【0021】

本発明の一態様において、データ消去時に複数のコントロールゲートドライバの一つが選択されて、該一つのセクタ領域内の全ての第1，第2のコントロールゲートに第1の消去用高電位を供給することができる。こうして、複数のセクタ領域の各々にて一括してデータ消去を実施することができる。

【0022】

本発明の一態様においてはさらに、複数のセクタ領域の各々には、列方向に沿って形成された複数のコントロールゲート線が設けられ、コントロールゲート駆動部は、複数のセクタ領域の各々に配置された複数のコントロールゲート線の各々に、ゲート回路を経由せずに直接接続されていることが好ましい。

10

【0023】

このように、面積を増大させ、電圧降下を生じさせるゲート回路を排除しても、非選択のセクタ領域内の非選択セルに高電位が印加されることはない。

【0024】

ここで、この複数のコントロールゲート線は、コントロールゲート駆動部に直接接続された複数のメインコントロールゲート線と、複数のメインコントロールゲート線と複数のメモリセルの前記第1，第2のコントロールゲートとを接続する複数のサブコントロールゲート線とを含むことができる。これらは、層の異なる金属配線にて形成することができる。

20

【0025】

このとき、複数のセクタ領域の各々に設けられた偶数のメインコントロールゲート線には、偶数列の複数メモリセルの各々の第2のコントロールゲートと奇数列の複数メモリセルの各々の第1のコントロールゲートとが共通接続された複数のサブコントロールゲートを接続することができる。一方、複数のセクタ領域の各々に設けられた奇数のメインコントロールゲート線には、奇数列の複数メモリセルの各々の第2のコントロールゲートと偶数列の複数メモリセルの各々の第1のコントロールゲートとが共通接続された複数のサブコントロールゲート線を接続することができる。

【0026】

また、複数のセクタ領域の各々に対応して設けられた複数のコントロールゲートドライバの各々にk本のメインコントロールゲート線が接続される場合には、複数のセクタ領域の各々には、k本のサブコントロールゲート線が接続されるメモリセル群からなる各入出力ビットに対応したメモリプロックが、行方向に複数配置される。このとき、行方向に沿って延びる複数の配線を設けることが好ましい。こうすると、k本のメインコントロールゲート線の各々と、それと対応するk本のサブコントロールゲート線の各々とを、複数の配線の一つを介して接続することができる。

30

30

【0027】

特に好ましい形態として、メモリプロックの行方向に沿ったメモリセル数を4とすることができます。この場合にはk=4に設定され、コントロールゲートドライバには4本のメインコントロールゲート線が接続される。メモリプロックは、行方向に4セル有するため計8ビットとなり、1本のサブコントロールゲート線を2ビットに共用することで、4本のサブコントロールゲート線が配置される。

40

40

【0028】

本発明の一態様では、複数のセクタ領域の各々に、列方向に沿って形成された複数のビット線と、少なくともデータのプログラム時及び読み出し時に複数のビット線を駆動するビット線駆動部とをさらに有することができる。

【0029】

ビット線駆動部はデータ消去時に複数のビット線を駆動するようにしてよいが、消去用ビット線駆動部をさらに設けても良い。この消去用ビット線駆動部は、一つのセクタ領域毎のデータ消去時に、該一つのセクタ領域に形成された複数のビット線に第2の消去用高

50

電位を供給する。

**【0030】**

複数のセクタ領域の各々は、他のセクタと分離された一つのウェル領域に形成することができる。この場合、そのウェル領域に第2の消去用高電位を供給する消去用ウェル駆動部を設けることができる。

**【0031】**

また、複数のビット線を不純物層にて形成することができ、この複数のビット線の各々に、複数のメインビット線の各々を接続しても良い。メインビット線を金属配線とすれば、ビット線の低抵抗化が可能であり、また不純物層を列方向で連続させずに不連続としても、その不連続な各ビット線にメインビット線を介して給電できる。

10

**【0032】**

このとき、複数のメインビット線から前記複数のビット線に至る経路途中に、ゲート回路が設けないことが好ましい。ゲート回路はビット線の配線容量を高めるほか、ゲート回路にて電圧降下が生ずることもあり、低電圧駆動の妨げとなるからである。

**【0033】**

メモリセルアレイ領域には、行方向に沿って配列された前記複数のメモリセルの各々のワードゲートにそれぞれ共通接続された複数のワードを、行方向に沿って設けることができる。こうして、複数のセクタ領域にて複数のワード線は共用される。なお、メモリセルアレイ領域の行方向の一端に、複数のワード線を駆動するワード線駆動部を設けることができる。不揮発性半導体記憶装置の記憶容量をさらに大容量化するには、行方向にてワード線ドライバを挟んだ両側に、複数のメモリセルアレイ領域をそれぞれ配置しても良い。

20

**【0034】**

第1、第2の不揮発性メモリ素子の各々は、酸化膜(O)、窒化膜(N)及び酸化膜(O)からなるONO膜を電荷のトラップサイトとして有することができるが、これに限らず他の構造を採用することができる。

**【0035】**

**【発明の実施の形態】**

以下、本発明の実施の形態について、図面を参照して説明する。

**【0036】**

**(メモリセル構造)**

30

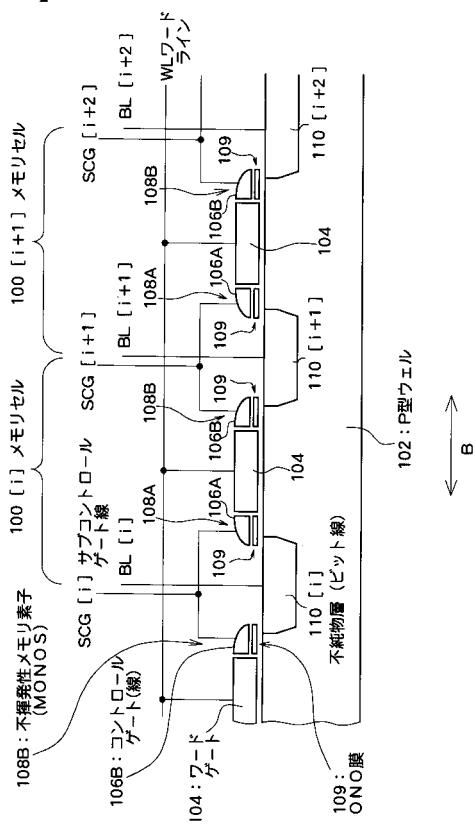

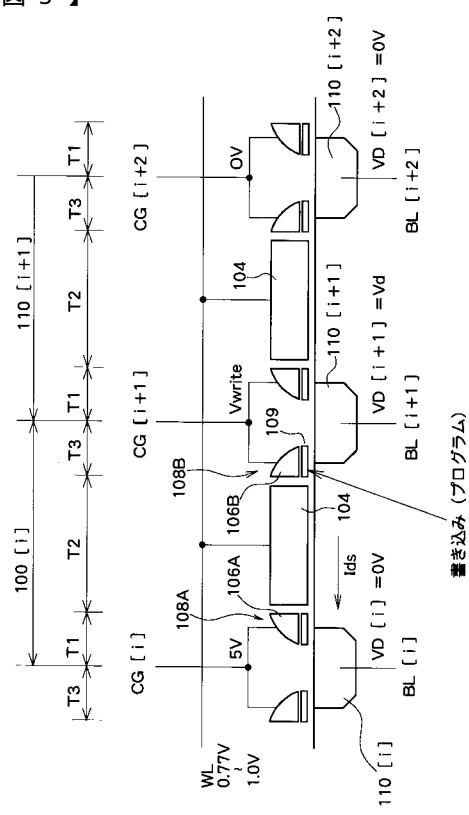

図1は不揮発性半導体記憶装置の一断面を示し、図2はその等価回路図である。図1において、1つのメモリセル100は、P型ウェル102上にゲート酸化膜を介して例えばポリサイドにて形成されたワードゲート104と、第1、第2のコントロールゲート106A、106Bと、第1、第2のメモリ素子(MONOSメモリセル)108A、108Bとを有する。

**【0037】**

第1、第2のコントロールゲート106A、106Bは、ワードゲート104の両側壁に形成され、ワードゲート104とはそれぞれ電気的に絶縁されている。

**【0038】**

第1、第2のメモリ素子108A、108Bの各々は、MONOSのM(金属)に相当するポリシリコンにて形成される第1、第2のコントロールゲート106A、106Bの一つと、P型ウェル102との間に、酸化膜(O)、窒化膜(N)及び酸化膜(O)を積層することで構成される。なお、第1、第2のコントロールゲート106A、106Bは、シリサイドなどの導電材で構成することができる。

40

**【0039】**

このように、1つのメモリセル100は、スプリットゲート(第1、第2のコントロールゲート106A、106B)を備えた第1、第2のMONOSメモリセル108A、108Bを有し、第1、第2のMONOSメモリセル108A、108Bにて一つのワードゲート104を共用している。

**【0040】**

50

この第1，第2のMONOSメモリセル108A，108Bは、それぞれ電荷のトラップサイトとして機能する。第1，第2のMONOSメモリセル108A，108Bの各々は、ONO膜109にて電荷をトラップすることが可能である。

図1及び図2に示すように、行方向(図1及び図2の第2の方向B)に間隔をおいて配列された複数のワードゲート104は、ポリサイドなどで形成される1本のワード線WLと共に接続されている。

#### 【0041】

また、図1に示すコントロールゲート106A，106Bは、列方向(図1の紙面に垂直な第1の方向A)に沿って延び、列方向に配列される複数のメモリセル100にて共用される。よって、符号106A，106Bをコントロールゲート線とも称する。

10

#### 【0042】

ここで、[i]番目のメモリセル100[i]のコントロールゲート線106Bと、[i+1]番目のメモリセル100[i+1]のコントロールゲート線106Aとには、例えばワードゲート、コントロールゲート、ワード線よりも上層の第1層の金属層で形成されるサブコントロールゲート線SCG[i+1]が接続されている。

#### 【0043】

P型ウェル102には、[i]番目のメモリセル100[i]のMONOSメモリセル108Bと、[i+1]番目のメモリセル100[i+1]のMONOSメモリセル108Aとに共用される[i+1]番目の不純物層110[i+1]が設けられている。

20

#### 【0044】

これらの不純物層110[i]，[i+1]，[i+2]は例えばP型ウェル内に形成されるn型不純物層で、列方向(図1の紙面に垂直な第1の方向A方向)に沿って延び、列方向に配列される複数のメモリセル100にて共用されるビット線として機能する。よって、符号110[i]，[i+1]，[i+2]などをビット線BL[i]，[i+1]，[i+2]とも称する。

#### 【0045】

(メモリセルからのデータ読み出し)

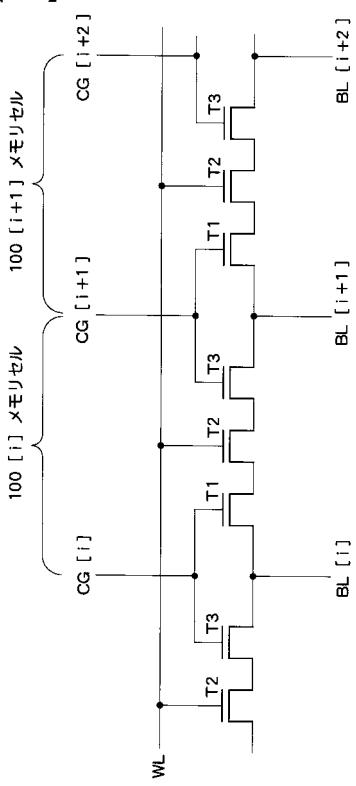

一つのメモリセル100は、図2に示すように、ワードゲート104により駆動されるトランジスタT2と、第1，第2のコントロールゲート106A，106Bによりそれぞれ駆動されるトランジスタT1，T3とを直列に接続したものと模式化することができる。

30

#### 【0046】

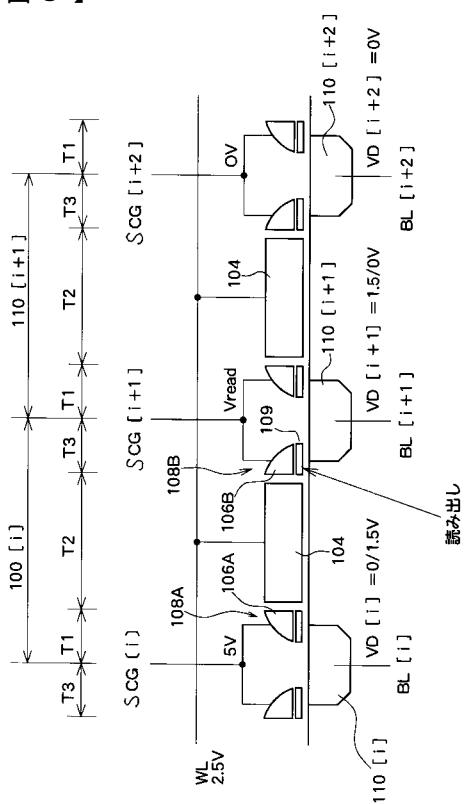

メモリセル100の動作を説明するに際して、図3に示すように、隣接する2つのメモリセル100[i]，[i+1]の各所の電位の設定についてまず説明する。図3は、メモリセル100[i]のワードゲート104の右側のMONOSメモリセル108Bからのデータ読み出しについて説明する図である。なお、以下の動作説明において、トランジスタT1～T3のしきい値電圧は2.5V未満と仮定する。

#### 【0047】

この場合、メモリセル100[i]と同じ行にある各ワードゲート104に例えば2.5Vを印加して、各トランジスタT2をオンさせる。また、メモリセル100[i]の左側のコントロールゲート106Aに、サブコントロールゲート線SCG[i]を介してオーバライド電圧(例えば5V)を印加して、MONOSメモリセル108Aに相当するトランジスタT1をオンさせる。メモリセル100[i]の右側のコントロールゲート106Bの電位VCGとして、読み出し電位Vreadを印加する。

40

#### 【0048】

このとき、ワードゲート104の右側のMONOSメモリセル108Bに電荷が蓄積されていたか否かで、MONOSメモリセル108Bに相当するトランジスタT3の動作は以下のように分かれる。

#### 【0049】

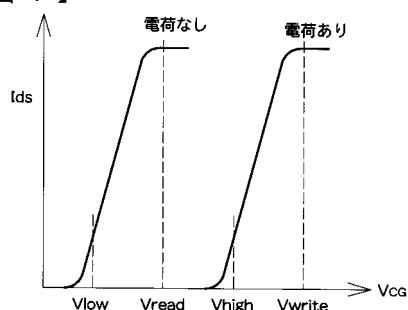

図4は、メモリセル100[i]の右側のコントロールゲート106Bへの印加電圧と、それによって制御されるMONOSメモリセル108Bに相当するトランジスタT3のソ

50

ース - ドレイン間に流れる電流  $I_{ds}$  との関係を示している。

#### 【0050】

図4に示すように、MONOSメモリセル108Bに電荷が蓄積されていない場合には、コントロールゲート電位  $V_{CG}$  が低いしきい値電圧  $V_{low}$  を超えると電流  $I_{ds}$  が流れ始める。これに対して、MONOSメモリセル108Bに電荷が蓄積されている場合には、コントロールゲート電位  $V_{CG}$  が高いしきい値電圧  $V_{high}$  を超えない限り電流  $I_{ds}$  が流れ始めない。

#### 【0051】

ここで、データ読み出し時にコントロールゲート106Bに印加される電圧  $V_{read}$  は、2つのしきい値電圧  $V_{low}$ ,  $V_{high}$  のほぼ中間電圧（例えば2.5V）に設定されている。10

#### 【0052】

従って、MONOSメモリセル108Bに電荷が蓄積されていない場合には電流  $I_{ds}$  が流れ、MONOSメモリセル108Bに電荷が蓄積されている場合には電流  $I_{ds}$  が流れないことになる。

#### 【0053】

ここで、データ読み出し時にはビット線  $BL[i]$ （不純物層  $110[i]$ ）の電位  $V_D[i]$  を0Vに、ビット線  $BL[i+1]$ （不純物層  $110[i+1]$ ）の電位  $V_D[i+1]$  を1.5Vにそれぞれ設定しておく。こうすると、MONOSメモリセル108Bに電荷が蓄積されていない場合には電流  $I_{ds}$  が流れため、オン状態のトランジスタ  $T_1$ ,  $T_2$  を介して、電位  $V_D[i]$  は0V~1.5Vと変化し、電位  $V_D[i+1]$  は1.5V~0Vと変化する。これに対し、MONOSメモリセル108Bに電荷が蓄積されている場合には電流  $I_{ds}$  が流れないとため、トランジスタ  $T_1$ ,  $T_2$  がオン状態であっても、電位  $V_D[i]$  は0Vのまま、電位  $V_D[i+1]$  は1.5Vのまま変化しない。よって、一対のビット線  $BL[i]$ ,  $[i+1]$  の電位を検出することで、メモリセル100[i]のMONOSメモリセル108Bからのデータ読み出しが可能となる。20

#### 【0054】

なお、メモリセル100[i+1]でもトランジスタ  $T_1$ ,  $T_2$  はオンしているが、トランジスタ  $T_3$  のコントロールゲート電位  $V_{CG}$  は0Vとされ、図3の2つのしきい値電圧  $V_{low}$ ,  $V_{high}$  の双方より電位  $V_{CG}$  が低いので、メモリセル100[i+1]にてソース - ドレイン電流は流れることがない。よって、メモリセル100[i+1]でのデータ蓄積状況が、メモリセル100[i]からのデータ読み出しに悪影響を与えることがない。30

#### 【0055】

メモリセル100[i]の左側のMONOSメモリセル108Aからデータを読み出すには、メモリセル100[i-1], [i]の各所の電位を、上記と同様に設定すればよい。40

#### 【0056】

（メモリセルのプログラミング）

図5は、メモリセル100[i]のワードゲート104の右側のMONOSメモリセル108Bのデータプログラミングについて説明する図である。なお、このデータプログラミング動作の前には、後述するデータ消去動作が実施されている。

#### 【0057】

図5では、図3と同じく、サブコントロールゲート線  $SCG[i]$  の電位はオーバライド電位（例えば5V）とされ、サブコントロールゲート線  $SCG[i+2]$  の電位は0Vとされている。しかし、各ワードゲート104の電位は、ワード線  $WL$  により例えば0.77~1.0V程度に設定される。また、メモリセル100[i+1]の右側のコントロールゲート108Bの電位は、サブコントロールゲート線  $SCG[i+1]$  を介して、図4に示す書き込み電位  $V_{write}$ （例えば5~6V）に設定され、[i+1]番目の不純物層  $110[i+1]$ （ビット線  $BL[i+1]$ ）の電位  $V_D[i+1]$  は例えば4.550

~ 5 V に設定される。

#### 【0058】

こうすると、メモリセル 100 [ i ] のトランジスタ T1, T2 がそれぞれオンして、不純物層 110 [ i ] に向けて電流 Ids が流れる一方で、MONOS メモリセル 108B のONO膜 109 にはチャンネルホットエレクトロン (CHE) がトラップされる。こうして、MONOS メモリセル 108B のプログラミング動作が実施されて、データの「0」または「1」が書き込まれる。

#### 【0059】

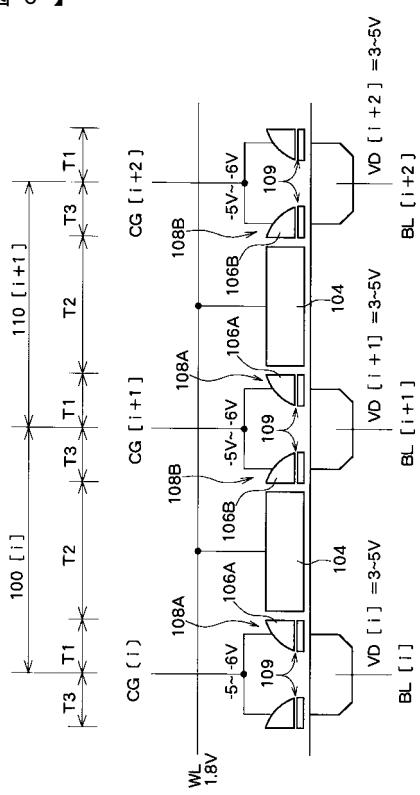

(メモリセルのデータ消去)

図6は、ワード線 WL に接続された2つのメモリセル 100 [ i ], [ i + 1 ] のデータ消去について説明する図である。 10

#### 【0060】

図6では、各ワードゲート 104 の電位は、ワード線 WL によって例えば 1.8 V に設定され、サブコントロールゲート線 SCG [ i ], [ i + 1 ], [ i + 2 ] によって、コントロールゲート 106A, 106B の電位は例えば -5 ~ -6 V 程度（第1の消去用高電位）に設定される。さらに、不純物層（ビット線）110 [ i ], [ i + 1 ], [ i + 2 ] の各電位は、P型ウェル電位と等しい 3 ~ 5 V（第2の消去用高電位）に設定される。

#### 【0061】

こうすると、各 MONOS メモリセル 108A, 108B のONO膜 109 にトラップされていた電子は、金属（M）に印加された第1の消去用高電位と、シリコン（S）に印加された第2の消去用高電位とで形成される電界により、トンネル効果により抜かれて消去される。これにより、複数メモリセルにて同時にデータ消去が可能となる。なお、消去動作としては、上述のものとは異なり、ビット線となる不純物層の表面のバンド・バンドトンネリングによりホットホールを形成し、蓄えられていたエレクトロンを消去するものであっても良い。

#### 【0062】

(不揮発性半導体記憶装置の全体構成)

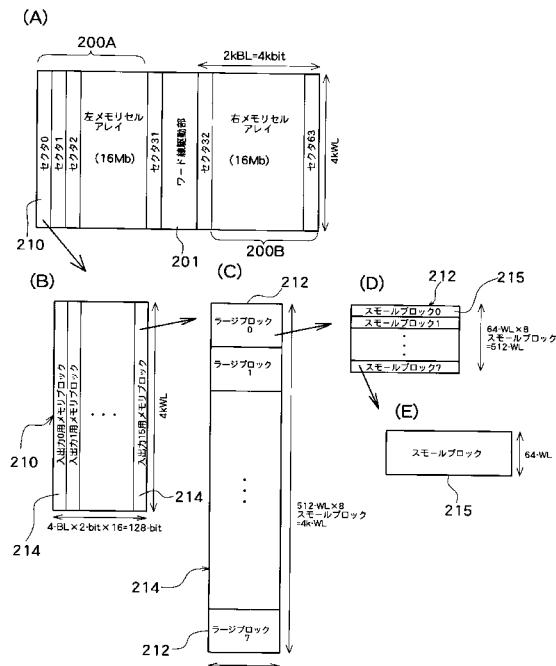

上述のメモリセル 100 を用いて構成される不揮発性半導体記憶装置の全体構成について、図7(A) ~ 図7(E) を参照して説明する。

#### 【0063】

図7(A) は 1チップの不揮発性半導体記憶装置の平面レイアウト図であり、ワード線駆動部 201 を挟んだ左右のメモリセルアレイ領域 200A, 200B は、例えば 32 個のセクタ領域 210 にそれぞれ分割されている。1チップの不揮発性半導体記憶装置としては、第0 ~ 第63 のセクタ領域 210 を有する。

32 個のセクタ領域 210 は、図7(A) に示すように左右のメモリセルアレイ領域 200A, 200B を第2の方向（行方向）B でそれぞれ分割したので、各セクタ領域 210 は第1の方向（列方向）A を長手方向とする縦長形状を有する。データ消去の最小単位がセクタ領域 210 であり、セクタ領域 210 内の記憶データは一括消去される。

#### 【0064】

左右のメモリアレイ領域 200A, 200B の各々は、例えば 4K 本のワード線 WL と 2K 本のビット線 BL を有する。ここで、本実施の形態では 1 本のビット線 BL に 2 つの MONOS メモリセル 108A, 108B が接続されるため、2K 本のビット線 BL は 4K bit の記憶容量を意味する。図7(A) の不揮発性半導体記憶装置は左右のメモリアレイ領域 200A, 200B を有するため、メモリ全体として (4K 本のワード線 WL) × (2K 本のビット線 BL) × 2 × 2 で定義される記憶容量を有する。各セクタ領域 210 の記憶容量はメモリ全体の記憶容量の 1 / 64 であり、(4K 本のワード線 WL) × (64 本のビット線 BL) × 2 で定義される記憶容量を有する。

#### 【0065】

図7(B) は、図7(A) に示す不揮発性半導体記憶装置の一つのセクタ領域 210 の詳細を示している。図7(B) に示すように、各セクタ領域 210 は第2の方向にて分割さ 40

20

30

40

50

れ、16ビットのデータをリード・ライト可能にI/O0～I/O15用の16個のメモリブロック（入出力ビットに対応したメモリブロック）214を有している。各メモリブロック214は、図7（B）に示すように、4k（4096）本のワード線WLを有する。

#### 【0066】

図7（C）に示すように、図7（B）に示す一つのメモリブロック214は、第1の方向Aにて8個のラージブロック212に分割されている。この各ラージブロック212は、図7（D）に示すように、第1の方向Aにて8個のスマールブロック215に分割されている。

各スマールブロック215は、図7（E）に示すように、64本のワード線WLを有する。

。

#### 【0067】

よって、一つのラージブロック212に配されるワード線WLの総数（冗長用も含む）は、 $64\text{本} \times 8\text{スマールブロック} = 512\text{本}$ となる。このため、一つのセクタ領域210に配されるワード線WLの総数は、 $512\text{（本)} \times 8\text{（ラージブロック)} = 4096\text{本}$ となる。

#### 【0068】

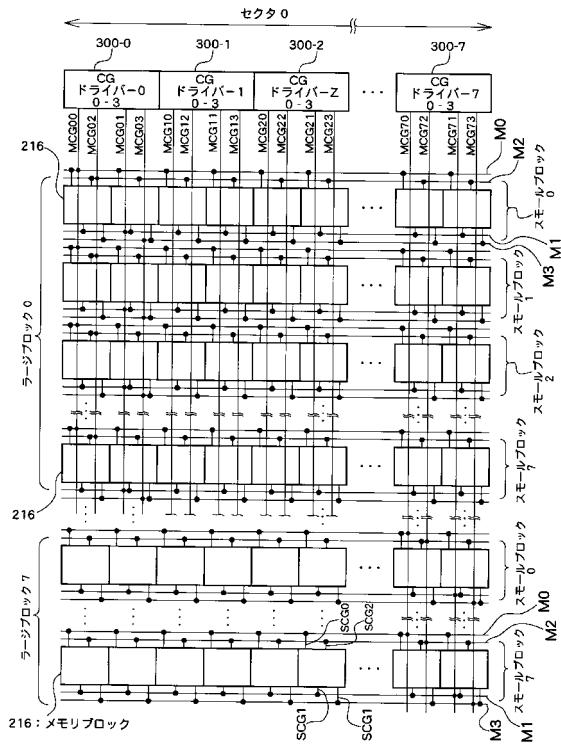

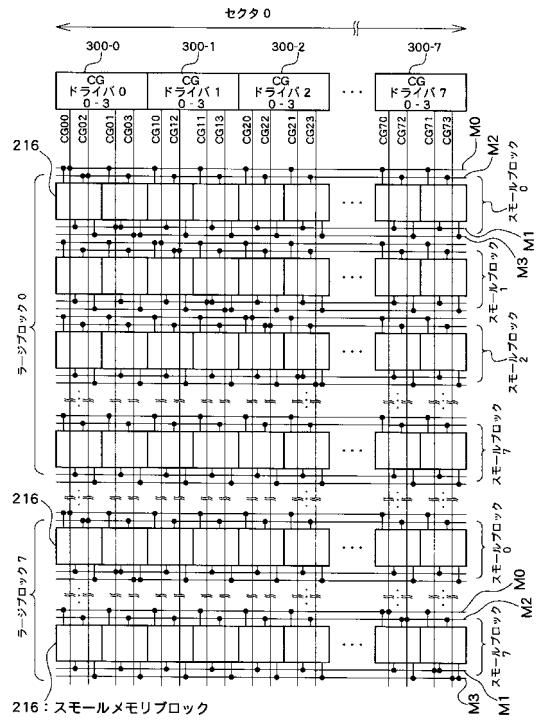

##### （セクタ領域の詳細）

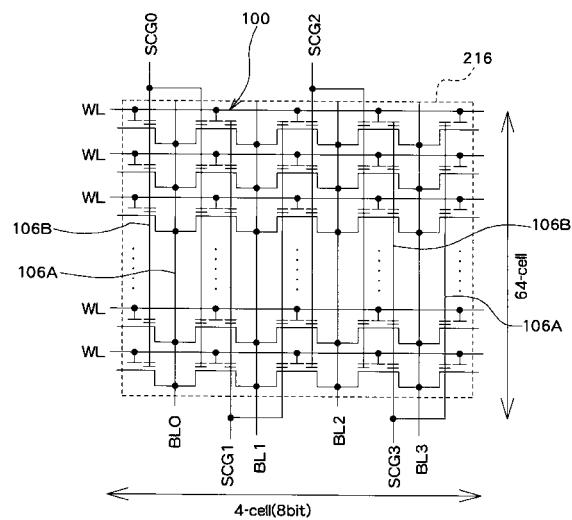

図8は、図7（A）に示すセクタ領域0の詳細を示している。図8に示すスマールメモリブロック216は、図9に示すように、メモリセル100を列方向に例えば64個、行方向に例えば4個配列したものである。一つのスマールメモリブロック216には、例えば第1層の金属配線層である4本のサブコントロールゲート線SCG0～SCG3と、データの入出力線である4本のビット線BL0～BL3と、64本のワード線WLとが接続されている。

#### 【0069】

ここで、偶数のコントロールゲート線SCG0, SCG2には、偶数列（第0列または第2列）の複数メモリセルの各々の第2のコントロールゲート106Bと奇数列（第1列または第3列）の複数メモリセルの各々の第1のコントロールゲート106Aとが共通接続されている。同様に、奇数のサブコントロールゲート線SCG1, SCG3には、奇数列（第1列または第3列）の複数メモリセルの各々の第2のコントロールゲート106Bと偶数列（第2列または第4列）の複数メモリセルの各々の第1のコントロールゲート106Aとが共通接続されている。

30

#### 【0070】

図8に示すように、スマールメモリブロック216が列方向に64個配列され、16ビットの入出力を行うために、I/O0～I/O15に対応した16個のスマールメモリブロック216が行方向に配列されている。

#### 【0071】

各スマールメモリブロック216では、コントロールゲート線SCG0が、行方向に延びる例えば第2層の金属配線M0に共通接続されている。同様に、16本のサブコントロールゲート線SCG1は金属配線M1に、16本のサブコントロールゲート線SCG2は金属配線M2に、16本のサブコントロールゲート線SCG3は金属配線M3にそれぞれ共通接続されている。

40

#### 【0072】

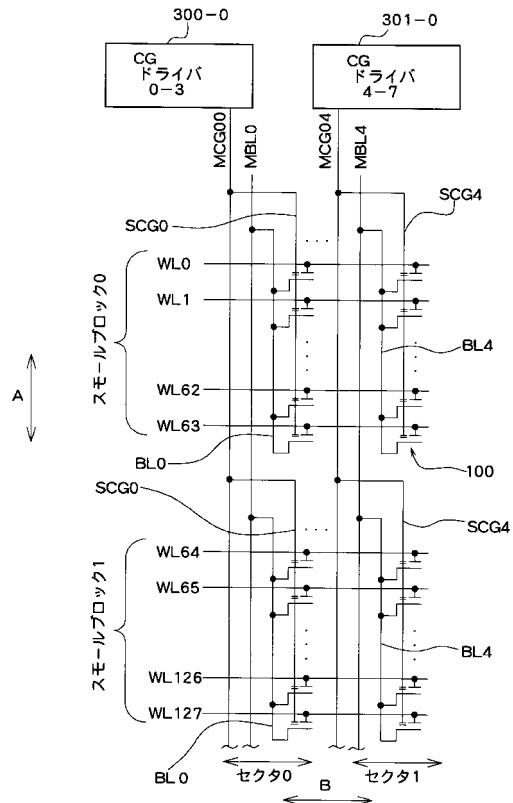

このセクタ領域0のコントロールゲート駆動部である8個のCGドライバ300-0～300-7が設けられている。CGドライバ300-0から列方向に延びる4本のメインコントロールゲート線MCG00～MCG03が設けられ、これらは例えば第3層の金属配線により形成されている。同様に、CGドライバ301-0からは4本のメインコントロールゲート線MCG10～MCG13が、CGドライバ300-2からは4本のメインコントロールゲート線MCG20～MCG23が、…CGドライバ300-7からは4本のメインコントロールゲート線MCG70～MCG73が、それぞれ列方向に延びている。

50

**【0073】**

ここで、CGドライバ300-0から列方向に延びる4本のメインコントロールゲート線MCG00～MCG03は、図8に示すようにラージブロック0の領域に亘って延びている。そして、ラージブロック0～7の各々に配置された8本、計64本の金属配線M0は、メインコントロールゲート線MCG00に共通接続されている。同様に、64本の金属配線M1はメインコントロールゲート線MCG01に、64本の金属配線M2はメインコントロールゲート線MCG02に、64本の金属配線M3はメインコントロールゲート線MCG03にそれぞれ共通接続されている。

**【0074】**

換言すれば、CGドライバ300-0から列方向に延びる4本のメインコントロールゲート線MCG00～MCG03は、図8に示すようにラージブロック0内に配置された全メモリセルの第1，第2のコントロールゲート106A，106Bにのみ電位を供給可能で、他のラージブロック1～7には接続されていない。

10

**【0075】**

同様に、図8では省略されているが、CGドライバ300-1はラージブロック1と、CGドライバ300-2はラージブロック2と、…CGドライバ300-6はラージブロック6とそれぞれ接続されている。

**【0076】**

図8ではさらに、CGドライバ300-7がラージブロック7とのみ接続されている状態が図示されている。

20

**【0077】**

図10は、相隣り合うセクタ領域0とセクタ領域1との関係を示している。セクタ領域0とセクタ領域1とはワード線WLが共用されるが、メインコントロールゲート線MCG及びメインビット線MBLはそれぞれ独立して設けられている。特に図10では、セクタ領域0に対応するドライバの一つであるCGドライバ300-0と、セクタ領域1に対応するドライバの一つであるCGドライバ301-0とが示され、CGドライバはセクタ領域毎に独立して設けられている。

**【0078】**

また、例えばセクタ領域0を例に挙げれば、スマールメモリブロック216毎に配置された複数のサブコントロールゲート線SCG0はメインコントロールゲート線MCG00に共通接続されている。このメインコントロールゲート線MCG00から各サブコントロールゲート線SCG0に至る各経路途中には、ゲート回路は配置されていない。

30

**【0079】**

同様に、スマールメモリブロック216毎に配置された複数のビット線BL0（不純物層）は、金属配線であるメインビット線MBL0に共通接続されている。このメインビット線MBL0から各ビット線BL0に至る各経路途中にも、ゲート回路は配置されていない。なお、以上のこととは他のセクタ領域1～7についても同様である。

**【0080】****(動作説明)**

ここで、本実施形態の不揮発性半導体記憶装置でのデータ消去時とプログラム時について、設定されるコントロールゲート線CG、ビット線BL及びワード線WLの各電位を、下記の表1に示す。

40

**【0081】****【表1】**

|       | 選択セル |    |      | 非選択セル(選択セクタ内) |    |    | 非選択セル(非選択セクタ内) |    |        |

|-------|------|----|------|---------------|----|----|----------------|----|--------|

|       | CG   | BL | WL   | CG            | BL | WL | CG             | BL | WL     |

| 消去    | -5V  | 5V | 1.8V | -             | -  | -  | 0V             | 0V | 1.8V   |

| プログラム | 5V   | 5V | 1V   | 5V            | 5V | 0V | 0V             | 0V | 0Vor1V |

50

**【0082】**

表1において、データ消去時には例えばセクタ領域0（選択セクタ）内は全て選択セルとなり、4096本のワード線WLには1.8Vが供給される。また、CGドライバ300-0～300-7によって32本の全てのメインコントロールゲート線MCG00～MCG03, MCG10～MCG13, … MCG70～MCG73に第1の消去用高電位（例えば-5V）が供給され、セクタ領域0（選択セクタ）内の全メモリセルのコントロールゲート106A, 106Bに、一括して第1の消去用高電位を供給することができる。このとき、セクタ領域0内の全ビット線BLには第2の消去用高電位（例えば5V）が供給されるが、その供給方法については後述する。こうして、選択されたセクタ領域0内の全メモリセルにてデータ消去を実施できる。

10

**【0083】**

このとき、非選択である例えばセクタ領域1では、4096本の全ワード線WLに1.8Vが供給されるが、コントロールゲートCG及びビット線BLはセクタ領域0とは独立して0Vを供給できるので、非選択セクタにてデータ消去が実施されることはない。

**【0084】**

次に、プログラミング動作について説明する。選択されたセクタ領域0内の例えばラージブロック0に配置された16個のI/Oにそれぞれ対応する各一つのMONOSメモリセルにて、16ビット同時にデータプログラミングが実施される。このために、セクタ領域0内の選択セルに接続されたいずれか1本のワード線WLに1Vが供給され、他の4095本のワード線WLは0Vに設定される。また、セクタ領域0内のラージブロック0に配置された、各I/O0～I/O15に対応する16個のメモリブロック214において、図5のCG[i], CG[i+1]に相当する2本のコントロールゲート線CGに5Vを供給し、他のコントロールゲート線CGは0Vに設定する。さらに、セクタ領域0内の各メモリブロック214において、図5のビット線BL[i+1]に相当する1本のビット線BLに5Vを供給し、他のビット線BLは0Vに設定する。これにより、セクタ領域0内のラージブロック0に配置された各メモリブロック214内の各一つのMONOSメモリセルにてデータプログラミングが実施される。

20

**【0085】**

このとき、表1に示すように、選択されたセクタ領域0内のラージブロック0に配置された非選択セルにおいては、ワード線WLは0Vに設定されるが、コントロールゲート線CG及びビット線BLには共に5Vの高電位が印加される。

30

**【0086】**

一方、表1に示すように、非選択のセクタ領域内における非選択セルにおいては、コントロールゲート線CG及びビット線BLには共に0Vが印加される。よって、非選択セクタ領域内では、プログラム時と同様な高電位が印加されることで生ずるディスターブが非選択セルに生ずることがない。このことは、選択されたセクタ領域0内のラージブロック0を除くラージブロック1-7に配置された非選択セルについても同様である。

**【0087】**

選択されたセクタ領域0内のラージブロック0に配置された非選択セルには高電位が印加されてしまうが、このような高電位はセクタ領域0内のラージブロック0にてプログラミングを実施する場合にのみ印加される。よって、いずれか一つのセクタ領域でのプログラミングが実施される度に、他のセクタ領域内の非選択セルに高電位が印加されるものと比較すれば、高電位が印加される頻度が大幅に低減し、ディスターブが生ずることを防止できる。

40

**【0088】****(比較例1の説明)**

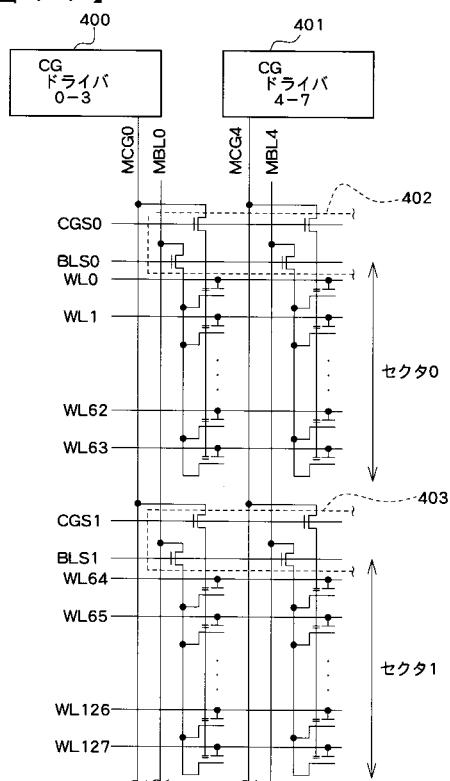

図11は、比較例1の構成を示している。この比較例1では、メモリセルアレイ領域は、列方向で分割され、列方向を長手方向とする複数のセクタ領域0, 1, …を有する。また比較例1では、CGドライバ400, 401はセクタ領域0, 1にそれぞれ対応して設けられずに、両セクタ領域0, 1に共用されている。

50

## 【0089】

ここで、図11に示すように、セクタ領域0に対応して選択ゲート領域402が、セクタ領域1に対応して選択ゲート領域403がそれぞれ設けられている。選択ゲート領域402, 403に配置されたN型MOSトランジスタ群は、選択信号線CGS0, CGS1の電位に基づいて、CGドライバ400, 401から供給される電位をセクタ領域0, 1に供給するか否かを選択するものである。同様に、選択ゲート領域402, 403に配置された他のN型MOSトランジスタ群は、選択信号線BLS0, BLS1の電位に基づいて、セクタ領域0, 1のピット線BLの接続／非接続を選択している。

## 【0090】

図11に示す比較例1の不揮発性半導体記憶装置でのデータ消去時とプログラム時について、設定されるコントロールゲート線CG、ピット線BL、ワード線WL及び選択信号線CGS, BLSの各電位を、下記の表2に示す。

## 【0091】

## 【表2】

|       | 選択セル |    |      |     |     | 非選択セル(選択セクタ内) |    |    |     |     | 非選択セル(非選択セクタ内) |    |      |     |     |

|-------|------|----|------|-----|-----|---------------|----|----|-----|-----|----------------|----|------|-----|-----|

|       | CG   | BL | WL   | CGS | BLS | CG            | BL | WL | CGS | BLS | CG             | BL | WL   | CGS | BLS |

| 消去    | -5V  | 5V | 1.8V | 0V  | 6V  | -             | -  | -  | -   | -   | FL             | FL | 1.8V | -5V | 0V  |

| プログラム | 5V   | 5V | 1V   | 6V  | 6V  | 5V            | 5V | 0V | 6V  | 6V  | FL             | FL | 0V   | 0V  | 0V  |

## 【0092】

表2に示すように、比較例1においても実質的に表1に示す本実施形態での設定電位と同じ電位に設定できるが、これらは選択ゲート領域402, 403を設けることで達成できるのである。もし選択ゲート領域402, 403が存在しなければ、選択されたセクタ領域0での選択セルのプログラミング時に、非選択のセクタ領域1の非選択セルにも高電位が印加されてしまう。このようにセクタ領域を越えてプログラム時の高電位が非選択セルにも印加されると、プログラムの度に非選択セルに高電位が印加され、ディスターープが生じてしまう。

## 【0093】

比較例1では、上記のようなディスターープの発生を防止するために、各セクタ領域毎に選択ゲート領域を設けることが不可欠である。しかし、このような選択ゲート領域の占有スペース分だけ面積が増大し、メモリセルの集積度が低下してしまう。

## 【0094】

さらに比較例1では、選択ゲート領域402, 403にN型MOSトランジスタを使用すると、そこで電圧降下が生ずるため、CGドライバ400, 401からは本来必要な第1の消去用高電位に電圧降下分の電圧を上乗せして供給しなければならず、高電圧化してしまう。

## 【0095】

上述した本発明の実施形態では、ディスターープを回避しながらも選択ゲート領域を省略でき、メモリセルの高集積化と低電圧駆動とが可能となる。

## 【0096】

## (比較例2)

図15は比較例2の構成を示している。図15においても、本実施の形態と同様なセクタ領域0～31に分割されている。ただし、例えばセクタ領域0のコントロールゲート駆動部としてCGドライバ300のみが設けられている。このCGドライバ300から列方向に延びる4本のメインコントロールゲート線MCG0～MCG3が設けられ、これらは例えば第3層の金属配線により形成されている。そして、ラージブロック0～7の各々に配置された8本、計64本の金属配線M0は、メインコントロールゲート線MCG0に共通接続されている。同様に、64本の金属配線M1はメインコントロールゲート線MCG1に、64本の金属配線M2はメインコントロールゲート線MCG2に、64本の金属配線

10

20

30

40

50

M3はメインコントロールゲート線MCG3にそれぞれ共通接続されている。

【0097】

図15に示す比較例2においても、セクタ領域0内にデータのプログラミングを実施している時には、他のセクタ領域1-31ではメモリセルに高電位を印加しなくて済み、しかも選択ゲート領域を設けずともディスターブを防止することができる。ただし、比較例2ではセクタ領域0のいずれかのメモリセルについてデータプログラミングを実施している時には、このセクタ領域0内の全てのメモリセルに高電位が等しく印加されることになり、この点で本実施の形態よりも劣っている。

【0098】

比較例2ではさらに、メインコントロールゲート線MCG0~MCG3の各々に対して、

ラージブロック0~7に亘る列方向の全てのメモリセルが接続される。

10

よって、本実施の形態のようにメインコントロールゲート線がいずれか一つのラージブロック内のメモリセルに接続されるものと比較すれば、本実施の形態のメインコントロールゲート線に接続される負荷容量（ゲート容量）は比較例2の1/8となる。

【0099】

高電位が供給されるメインコントロールゲート線に接続される負荷容量が大きいと、メインコントロールゲート線をその高電位に充電するまでに要する時間が長くなり、高速駆動が不可能となるが、本実施の形態はその点で比較例2よりも優れている。

【0100】

なお、図10に示す本発明の実施形態においては、ビット線BLについては選択ゲートを追加することも可能である。このようにして、選択されたセクタ0中の非選択セルについては、ビット線BLを選択ゲートによってフローティング状態としても良い。こうすると、プログラムが選択されたセクタ領域0内の非選択セルのビット線BLは、高電位とならない。よって、非選択セルでのデータのディスターブはさらに低減できる。なお、選択ゲートを介してビット線に高電位を供給する時には、電圧降下が生ずるおそれは残る。

20

【0101】

(1チップメモリの構成)

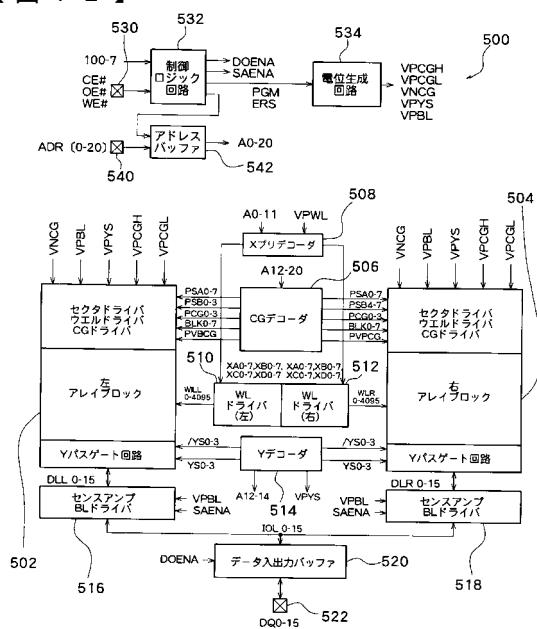

図12は、上述の不揮発性半導体記憶装置を1チップ化したときの概略ブロック図である。図12において、このICチップ500には、左アレイブロック502及び右アレイブロック504が設けられている。この左右のアレイブロック502, 504の各々は、図7にて説明したメモリセルアレイ領域を含んでいる。

30

【0102】

この左右のアレイブロック502, 504の間には、CGデコーダ506、Xプリデコーダ508、WLドライバ(左)510、WLドライバ(右)512及びYデコーダ514が配置されている。

【0103】

左右のメモリブロック502, 504には、センスアンプ/BLDライバ516, 518がそれぞれ接続されている。このセンスアンプ/BLDライバ516, 518のいずれか一方に対して、16ビットの信号I00-15が、データイン/アウトバッファ520及び入出力端子522を介して入出力される。

40

【0104】

ICチップ500にはさらに、コマンド端子530を介して入力される各種イネーブル信号に基づいて、制御ロジック信号を生成する制御ロジック回路532が設けられている。この制御ロジック回路532からの出力に基づいて、コントロールゲート線WL及びビット線BLなどに供給される各種電位が電位生成回路534にて生成される。

【0105】

一方、アドレス端子640を介して外部から入力されるアドレス信号ADR[0-20]に基づいて、アドレスバッファ542にて内部アドレス信号A0-20が生成される。この内部アドレス信号A0-20の定義を下記の表3に示す。

【0106】

50

【表3】

| アドレス     | グループ | ファンクション          |

|----------|------|------------------|

| A[20:15] | セクタ  | Choose 1 of 64   |

| A[14:12] | 行    | Choose 1 of 8    |

| A[11:0]  | 列    | Choose 1 of 4096 |

## 【0107】

表3に示すように、内部アドレス信号の上位6ビットA[20:15]は、図7(A)に示すセクタ領域0-63の一つを選択するのに用いられる。内部アドレス信号の中位3ビットA[14:12]は、図9に示す一つのスマールメモリブロック216の中から8ビットのうちの一つを選択するのに用いられる。内部アドレス信号の下位12ビットA[11:0]は、4096本のワード線WLの一本を選択するために用いられる。

10

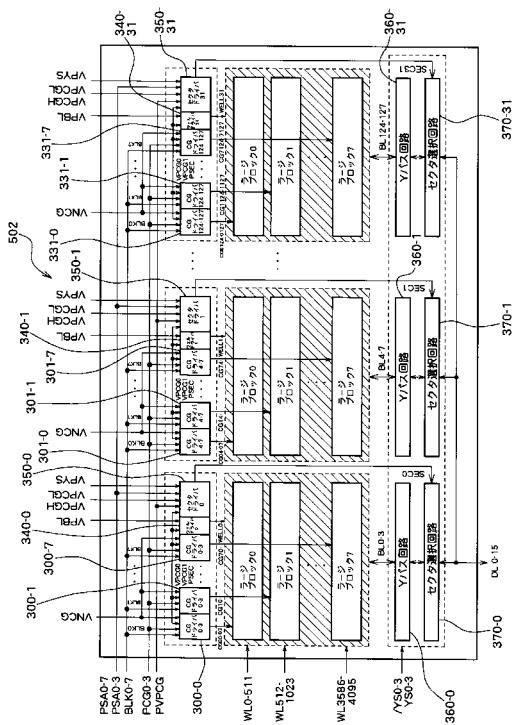

## 【0108】

図13は、図12に示す左メモリブロック502の詳細を示している。このメモリブロック502は、図7(A)と同様に32分割されたセクタ領域0-31を有し、セクタ領域0-31の各々には図7(B)と同様に8つのラージブロック0-7が設けられている。

11

## 【0109】

図13に示すように、32個のセクタ領域の各一つと対応してCGドライバ300~331が設けられている。セクタ領域0に対応するCGドライバ300は、図8に示したものと同じであり、ラージブロック0-8から成るセクタ領域0内の各メモリセルにコントロールゲート電位を直接供給するものである。他のCGドライバ301~331も同様の機能を有する。

20

## 【0110】

図13において、32個のセクタ領域0-31の各一つに対応して、消去用ビット線駆動部であるウェルドライバ340-0~340-31が設けられている。ウェルドライバ340-0は、セクタ領域0内の例えばP型ウェルに第2の消去用高電位を供給して、第2の消去用高電位に設定するものである。他のウェルドライバ340-1~340-31も同様の機能を有する。

30

## 【0111】

図13において、32個のセクタ領域0-31の各一つに対応して、セクタデコーダ350-0~350-31が設けられている。セクタデコーダ350-0は、内部アドレス信号の上位6ビットA[20:15]にて生成される信号をデコードする。そして、セクタ0が選択された際には、セクタデコード350-0がCGドライバ300、ウェルドライバ340-0を駆動して、必要な電位がコントロールゲート線CG、ビット線BLに供給されるようとする。

31

## 【0112】

図13において、32個のセクタ領域0-31の各一つに対応して、Yバス回路360-0~360-31と、セクタ選択回路370-0~370-31が設けられている。Yバス回路360-0~360-31は、図12に示すYデコーダ514からの信号に基づいて、16個の各I/Oに接続されたビット線BL0-3の一本を選択する。セクタ選択回路370-0~370-31は、対応するセクタデコーダ360-0~360-31からの選択信号SEC0~SEC31に基づいて、図12に示すセンスアンプ/BLドライバ516との接続/非接続を行う。

40

## 【0113】

なお、本発明は上述した実施の形態に限定されるものではなく、本発明の要旨の範囲内で種々の変形実施が可能である。

## 【0114】

例えば、不揮発性メモリ素子108A, 108Bの構造については、MONOS構造に限

50

定されるものではない。1つのワードゲート104と第1，第2のコントロールゲート106A，106Bにより、2箇所にて独立して電荷をトラップできる他の種々のメモリセルを用いた不揮発性半導体記憶装置に、本発明を適用することができる。

#### 【0115】

また、上述の実施形態では、セクタ領域の分割数、ラージブロック、スマールブロックの分割数については一例であり、他の種々の変形実施が可能である。すなみに、ラージブロックの分割数を8としたのはメタル配線ピッチの制約から決められた。もしメタル配線ピッチを狭く出来れば、分割数をさらに増やすことができる。例えば16分割にすれば、1本のコントロールゲート線の負荷容量（ゲート容量）はさらに減るので、より高速駆動が可能となる。ただし、16分割とするとメインコントロールゲート線の数が増えるので、ライン＆スペースを狭くするか、面積を増大させるしかない。また、コントロールゲートドライバの数も増えるので、その分面積が増大する。

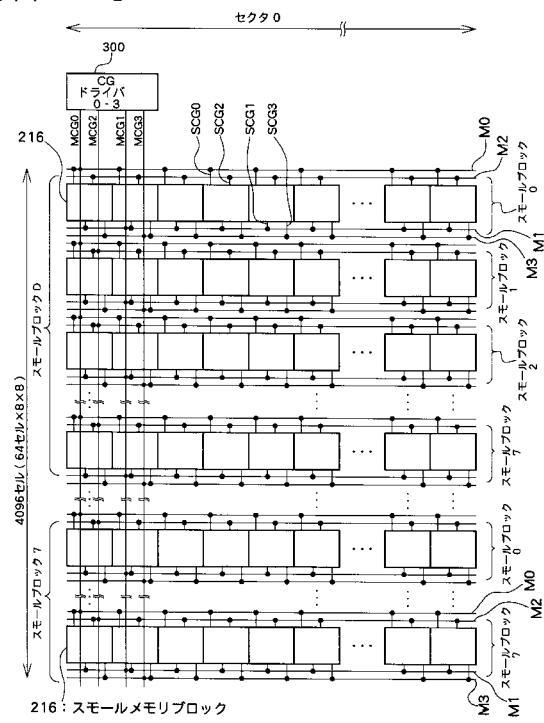

#### 【0116】

図14は、図8に示すスマールメモリブロック216に対する配線の変形例を示している。図14では、CGドライバ300-0からのメインコントロールゲート線MCG00～MCG03は、図8のようにラージブロック0内の全てのスマールブロック0～7に接続されるのではなく、ラージブロック0～7の各スマールブロック0にのみ接続されている。CGドライバ300-1は、ラージブロック0～7の各スマールブロック2にのみ接続されている。CGドライバ300-7は、ラージブロック0～7の各スマールブロック7のみに接続されている。

#### 【0117】

図14に示す接続形態であっても、図8に示す接続形態と同様な作用・効果を奏すことができる。

#### 【図面の簡単な説明】

【図1】本発明の一実施の形態に係る不揮発性半導体記憶装置に用いられるメモリセルの断面図である。

【図2】図1に示すメモリセルの等価回路図である。

【図3】図1に示す不揮発性半導体記憶装置でのデータ読み出し動作を説明するための概略説明図である。

【図4】図1に示すメモリセルでのコントロールゲート電圧VCGとソース-ドレイン電流Idsとの関係を示す特性図である。

【図5】図1に示す不揮発性半導体記憶装置でのデータ書き込み（プログラム）動作を説明するための概略説明図である。

【図6】図1に示す不揮発性半導体記憶装置でのデータ消去動作を説明するための概略説明図である。

【図7】図7(A)は図1に示す不揮発性半導体記憶装置全体の平面レイアウト図、図7(B)は図7(A)中の一つのセクタ領域の平面図、図7(C)は図7(B)中の一つのメモリブロックの平面図、図7(D)は図7(C)中の一つのラージブロックの平面図、図7(E)は図7(D)中の一つのスマールブロックの平面図である。

【図8】図7(B)に示す一つのセクタ領域の多数のメモリブロックとその配線とを説明するための概略説明図である。

【図9】図8に示すスマールメモリブロックの詳細を示す回路図である。

【図10】隣り合うセクタ領域の関係を示す回路図である。

【図11】図10に対する比較例1の構成を示す回路である。

【図12】1チップ化された不揮発性半導体記憶装置のブロック図である。

【図13】図12に示す左メモリブロックの詳細を示すブロック図である。

【図14】一つのセクタ領域内のスマールメモリブロックに対する配線を図8とは異ならせた変形例を説明するための概略説明図である。

【図15】図8及び図14とはさらに異なる配線とした比較例2の構成を説明するための概略説明図である。

10

20

30

40

50

## 【符号の説明】

|                         |                        |    |

|-------------------------|------------------------|----|

| 1 0 0                   | メモリセル                  |    |

| 1 0 2                   | P型ウェル                  |    |

| 1 0 4                   | ワードゲート                 |    |

| 1 0 6 A , 1 0 6 B       | コントロールゲート(線)           |    |

| 1 0 8 A , 1 0 8 B       | 不揮発性メモリ素子(MONOSメモリセル)  |    |

| 1 0 9                   | ONO膜                   |    |

| 1 1 0                   | 不純物層(ピット線)             |    |

| 2 0 0 A , 2 0 0 B       | メモリセルアレイ領域             |    |

| 2 0 1                   | ワード線駆動部                | 10 |

| 2 1 0                   | セクタ領域                  |    |

| 2 1 2                   | ラージブロック                |    |

| 2 1 4                   | メモリブロック                |    |

| 2 1 5                   | スマールブロック               |    |

| 2 1 6                   | スマールメモリブロック            |    |

| 3 0 0 - 0 ~ 3 3 1 - 7   | CG(コントロールゲート)ドライバ      |    |

| 3 4 0 - 0 ~ 3 4 0 - 3 1 | ウェルドライバ(消去用ピット線駆動部)    |    |

| 3 5 0 - 0 ~ 3 5 0 - 3 1 | セクタドライバ                |    |

| 3 6 0 - 0 ~ 3 6 0 - 3 1 | Yバス回路                  |    |

| 3 7 0 - 0 ~ 3 7 0 - 3 1 | セクタ選択回路                | 20 |

| 4 0 0 , 4 0 1           | CG(コントロールゲート)ドライバ      |    |

| 4 0 2 , 4 0 3           | 選択ゲート領域                |    |

| 5 0 0                   | I Cチップ                 |    |

| 5 0 2 , 5 0 4           | アレイブロック                |    |

| 5 0 6                   | CGデコーダ                 |    |

| 5 0 8                   | Xプリデコーダ                |    |

| 5 1 0 , 5 1 2           | WL(ワード線)ドライバ           |    |

| 5 1 4                   | Yデコーダ                  |    |

| 5 1 6 , 5 1 8           | センスアンプ/BLドライバ          |    |

| 5 2 0                   | データイン/アウトバッファ          | 30 |

| 5 2 2                   | 入出力端子                  |    |

| 5 3 0                   | コマンド端子                 |    |

| 5 3 2                   | 制御ロジック回路               |    |

| 5 3 4                   | 電位生成回路                 |    |

| 5 4 0                   | アドレス端子                 |    |

| 5 4 2                   | アドレスバッファ               |    |

| W L                     | ワード線                   |    |

| B L                     | ピット線(不純物層)             |    |

| M B L                   | メインピット線                |    |

| S C G                   | サブコントロールゲート線(第1層金属配線)  | 40 |

| M 0 ~ M 3               | 第2層金属配線                |    |

| M C G                   | メインコントロールゲート線(第3層金属配線) |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【 図 1 4 】

【 図 1 5 】

---

フロントページの続き

(51) Int.Cl.<sup>7</sup> F I

H 01 L 29/788 H 01 L 27/10 4 3 4

H 01 L 29/792

(56) 参考文献 特開2002-230988 (JP, A)

特開2002-353346 (JP, A)

(58) 調査した分野(Int.Cl.<sup>7</sup>, DB名)

G11C 16/00-16/34

H01L 21/8247, 27/115, 29/788, 29/7927