(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6324098号

(P6324098)

(45) 発行日 平成30年5月16日(2018.5.16)

(24) 登録日 平成30年4月20日(2018.4.20)

(51) Int.Cl.

F 1

|             |               |                  |             |               |                |

|-------------|---------------|------------------|-------------|---------------|----------------|

| <b>G09F</b> | <b>9/00</b>   | <b>(2006.01)</b> | <b>G09F</b> | <b>9/00</b>   | <b>3 3 8</b>   |

| <b>H01L</b> | <b>29/786</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b>  | <b>6 1 2 C</b> |

| <b>H01L</b> | <b>21/336</b> | <b>(2006.01)</b> | <b>H01L</b> | <b>29/78</b>  | <b>6 1 9 A</b> |

| <b>G02F</b> | <b>1/1368</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/1368</b> |                |

| <b>G02F</b> | <b>1/1345</b> | <b>(2006.01)</b> | <b>G02F</b> | <b>1/1345</b> |                |

請求項の数 10 (全 16 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2014-21746 (P2014-21746)    |

| (22) 出願日  | 平成26年2月6日(2014.2.6)           |

| (65) 公開番号 | 特開2015-148728 (P2015-148728A) |

| (43) 公開日  | 平成27年8月20日(2015.8.20)         |

| 審査請求日     | 平成29年1月11日(2017.1.11)         |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 502356528<br>株式会社ジャパンディスプレイ<br>東京都港区西新橋三丁目7番1号 |

| (74) 代理人  | 110000408<br>特許業務法人高橋・林アンドパートナーズ               |

| (72) 発明者  | 小高 和浩<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内       |

| (72) 発明者  | 佐藤 敏浩<br>東京都港区西新橋三丁目7番1号 株式会社ジャパンディスプレイ内       |

審査官 村川 雄一

最終頁に続く

(54) 【発明の名称】表示装置及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

基板上に、薄膜トランジスタを備える画素を複数配置した表示部と、前記薄膜トランジスタの動作を制御するための信号が入力される複数の端子が配列された端子部と、を有する表示装置の製造方法であって、

前記基板上に第1絶縁膜を形成し、

前記第1絶縁膜上に前記薄膜トランジスタを形成し、

前記薄膜トランジスタの形成後に前記表示部と前記端子部とに第2絶縁膜を形成し、

前記第2絶縁膜に、前記薄膜トランジスタの少なくとも一部を露出させるコンタクトホールを形成するとともに、前記端子部において複数の開口部を形成し、

前記第2絶縁膜上に、前記薄膜トランジスタに前記コンタクトホールを介して接続される複数の信号線と、前記複数の信号線の形成とともに、前記開口部を間に挟むように複数の端子配線を形成し、

前記複数の信号線及び前記複数の端子配線上に有機絶縁膜からなる第3絶縁膜を形成することを含むことを特徴とする表示装置の製造方法。

## 【請求項 2】

前記端子部において、前記第3絶縁膜を一部除去して前記複数の端子配線を露出させ、

前記複数の端子配線の前記露出された部分を覆う導電膜を形成することをさらに含むことを特徴とする請求項1に記載の表示装置の製造方法。

## 【請求項 3】

10

20

基板上に、薄膜トランジスタを備える画素を複数配置した表示部と、

前記薄膜トランジスタの動作を制御するための信号が入力される複数の端子が配列された端子部と、を有する表示装置の製造方法であって、

前記基板上に第1絶縁膜を形成し、

前記第1絶縁膜上に前記薄膜トランジスタを形成し、

前記薄膜トランジスタの形成後に前記表示部と前記端子部とに第2絶縁膜を形成し、

前記第2絶縁膜に、前記薄膜トランジスタの少なくとも一部を露出させるコンタクトホールを形成するとともに、前記端子部において複数の開口部を形成し、

前記第2絶縁膜上に、前記薄膜トランジスタに前記コンタクトホールを介して接続される複数の信号線と、前記複数の信号線の形成と同時に、前記開口部を間に挟むように複数の端子配線を形成し、

前記複数の信号線上に有機絶縁膜からなる第3絶縁膜を形成し、

前記第3絶縁膜及び前記複数の端子配線上に、無機絶縁膜からなる第4絶縁膜を形成し

、前記端子部において、前記第4絶縁膜を一部除去して前記複数の端子配線を露出させ、前記複数の端子配線の前記露出された部分を覆う導電膜を形成し、

前記導電膜上に、第5絶縁膜を形成することを含み、

前記第5絶縁膜を一部除去して前記導電膜を露出させることをさらに含むこと特徴とする表示装置の製造方法。

#### 【請求項4】

前記導電膜を、透光性を有する導電膜を用いて形成することを特徴とする請求項2または3に記載の表示装置の製造方法。

#### 【請求項5】

前記第3絶縁膜を、アクリルまたはポリイミドを用いて形成することを特徴とする請求項1乃至4のいずれか一項に記載の表示装置の製造方法。

#### 【請求項6】

基板上に、薄膜トランジスタを備える画素を複数配置した表示部と、

前記薄膜トランジスタの動作を制御するための信号が入力される複数の端子が配列された端子部と、を有する表示装置であって、

前記基板上に配置された第1絶縁膜と、

前記第1絶縁膜上に配置された前記薄膜トランジスタと、

前記表示部及び前記端子部に配置され、前記薄膜トランジスタの少なくとも一部を露出させるコンタクトホールと、前記複数の端子の間に配置される開口部と、を備える第2絶縁膜と、

前記第2絶縁膜上に配置され、前記コンタクトホールを介して前記薄膜トランジスタに接続される複数の信号線と、前記端子部に配置される複数の端子配線と、

前記複数の信号線上に配置される有機絶縁膜からなる第3絶縁膜と、

前記第3絶縁膜及び前記複数の端子配線上に配置される無機絶縁膜からなり、前記複数の端子配線の一部を露出させる複数の貫通孔を備える第4絶縁膜と、

前記第4絶縁膜上に配置され、前記複数の貫通孔を介してそれぞれ前記複数の端子配線に接続される前記複数の端子と、

前記複数の端子上に、前記複数の端子の一部を露出させて配置される第5絶縁膜と、を備えること特徴とする表示装置。

#### 【請求項7】

前記複数の端子は、前記第3絶縁膜上に配置され、前記第3絶縁膜に形成された複数の貫通孔を介してそれぞれ前記複数の端子配線と接続されることを特徴とする請求項6に記載の表示装置。

#### 【請求項8】

前記複数の端子は、透光性を有する導電膜を用いて形成されることを特徴とする請求項6又は請求項7に記載の表示装置。

10

20

30

40

50

**【請求項 9】**

前記第3絶縁膜は、アクリルまたはポリイミドを用いて形成されることを特徴とする請求項6乃至8のいずれか一項に記載の表示装置。

**【請求項 10】**

前記第4絶縁膜及び前記第5絶縁膜は、前記開口部に重畳するように形成されることを特徴とする請求項6乃至9のいずれか一項に記載の表示装置。

**【発明の詳細な説明】****【技術分野】**

10

**【0001】**

本発明は、複数の端子が配置された端子部を備える表示装置及びその製造方法に関する。

**【背景技術】****【0002】**

近年、液晶表示装置や、有機EL(Organic Electroluminescence)表示装置など、薄膜トランジスタ(TFT)を用いて各画素の表示階調を制御する表示装置が開発されている。このような表示装置は、薄膜トランジスタを備える複数の画素の各々に電流を供給する必要があることから、外部回路等に接続されて電流の供給を受ける複数の端子の配置された端子部及び複数の端子に接続される複数の配線を含む配線部を備える。これらの表示装置は、端子部及び配線部の劣化を防止し、端子部における接続の信頼性を向上させることが重要な課題となっている。

20

**【0003】**

このため、従来の表示装置には、TFT基板上の端子部において、絶縁膜を用いて突起を形成し、突起上に形成された端子用導電膜と、フレキシブル配線基板に形成されたバンプとの間に熱硬化性の絶縁性フィルムを配置し、絶縁性フィルムを押しのけさせて端子用導電膜とバンプとを接触させることにより導通させるものが提案されている(例えば、特許文献1参照)。

**【先行技術文献】****【特許文献】**

30

**【0004】**

【特許文献1】特開2008-065135号公報

**【発明の概要】****【発明が解決しようとする課題】****【0005】**

しかしながら、上述した従来の表示装置のように、端子部に形成された突起部分と外部回路に形成されたバンプとで接続箇所が限定される場合には、絶縁性フィルムにより信頼性は確保されるものの、接続抵抗が高くなる虞があり、また、複数の微細な突起を形成する必要があるため、製造プロセスへの負荷が高くなる虞があった。

**【0006】**

40

そこで、本発明は上述した課題に鑑みてなされたものであり、外部回路を実装する際に、実装歩留りを悪化させることなく、高信頼性を確保することの可能な表示装置及びその製造方法を提供することを目的とする。また、このような表示装置を、製造プロセスを大幅に変更することなく、簡易な製造工程で実現することを目的とする。

**【課題を解決するための手段】****【0007】**

本発明の一実施形態に係る表示装置の製造方法は、基板上に、薄膜トランジスタを備える画素を複数配置した表示部と、複数の前記薄膜トランジスタの動作を制御するための信号が入力される複数の端子が配列された端子部と、を有する表示装置の製造方法であって、前記基板上に第1絶縁膜を形成し、前記第1絶縁膜上に前記複数の薄膜トランジスタを

50

形成し、前記薄膜トランジスタの形成後に前記表示部と前記端子部とに第2絶縁膜を形成し、前記第2絶縁膜に、前記複数の薄膜トランジスタの少なくとも一部を露出させるコンタクトホールを形成し、前記端子部においては前記複数の端子の間に開口部を形成し、前記第2絶縁膜上に、前記複数の薄膜トランジスタに前記コンタクトホールを介して接続される複数の信号線と、前記複数の信号線と同層の複数の端子配線を形成し、前記複数の信号線及び前記複数の端子配線上に有機膜からなる第3絶縁膜を形成することを含むことを特徴とする。

【0008】

前記端子部において、前記第3絶縁膜を一部除去して前記複数の端子配線を露出させ、前記複数の端子配線の前記露出された部分を覆う導電膜を形成することをさらに含んでもよい。

10

【0009】

本発明の他の実施形態に係る表示装置の製造方法は、基板上に、薄膜トランジスタを備える画素を複数配置した表示部と、複数の前記薄膜トランジスタの動作を制御するための信号が入力される複数の端子が配列された端子部と、を有する表示装置の製造方法であって、前記基板上に第1絶縁膜を形成し、前記第1絶縁膜上に前記複数の薄膜トランジスタを形成し、前記薄膜トランジスタの形成後に前記表示部と前記端子部とに第2絶縁膜を形成し、前記第2絶縁膜に、前記複数の薄膜トランジスタの少なくとも一部を露出させるコンタクトホールを形成し、前記端子部においては前記複数の端子の間に開口部を形成し、前記第2絶縁膜上に、前記複数の薄膜トランジスタに前記コンタクトホールを介して接続される複数の信号線と、前記複数の信号線と同層の複数の端子配線を形成し、前記複数の信号線上に有機膜からなる第3絶縁膜を形成し、前記第3絶縁膜及び前記複数の端子配線上に、無機膜からなる第4絶縁膜を形成し、前記端子部において、前記第4絶縁膜を一部除去して前記複数の端子配線を露出させ、前記複数の端子配線の前記露出された部分を覆う導電膜を形成し、前記導電膜上に、第5絶縁膜を形成することを含み、前記第5絶縁膜を一部除去して前記導電膜を露出させることをさらに含むこと特徴とする。

20

【0010】

前記導電膜を、透光性を有する導電膜を用いて形成してもよい。

【0011】

また、前記第3絶縁膜を、アクリルまたはポリイミドを用いて形成してもよい。

30

【0012】

本発明の一実施形態に係る表示装置は、基板上に、薄膜トランジスタを備える画素を複数配置した表示部と、複数の前記薄膜トランジスタの動作を制御するための信号が入力される複数の端子が配列された端子部と、を有する表示装置であって、前記基板上に配置された第1絶縁膜と、前記第1絶縁膜上に配置された前記複数の薄膜トランジスタと、前記表示部及び前記端子部に配置され、前記複数の薄膜トランジスタの少なくとも一部を露出させるコンタクトホールと、前記複数の端子の間に配置される開口部とを備える第2絶縁膜と、前記第2絶縁膜上に配置され、前記複数の薄膜トランジスタに前記コンタクトホールを介して接続される複数の信号線と、前記端子部に配置される複数の端子配線と、前記複数の信号線及び前記複数の端子配線上に配置される有機膜からなる第3絶縁膜と、を備えることを特徴とする。

40

【0013】

前記複数の端子は、前記第3絶縁膜上に配置され、前記第3絶縁膜に形成された複数の貫通孔を介してそれぞれ前記複数の端子配線と接続されてもよい。

【0014】

本発明の他の実施形態に係る表示装置は、基板上に、薄膜トランジスタを備える画素を複数配置した表示部と、複数の前記薄膜トランジスタの動作を制御するための信号が入力される複数の端子が配列された端子部と、を有する表示装置であって、前記基板上に配置された第1絶縁膜と、前記第1絶縁膜上に配置された複数の前記薄膜トランジスタと、前記表示部及び前記端子部に配置され、前記複数の薄膜トランジスタの少なくとも一部を露

50

出させるコンタクトホールと、前記複数の端子の間に配置される開口部とを備える第2絶縁膜と、前記第2絶縁膜上に配置され、前記複数の薄膜トランジスタに前記コンタクトホールを介して接続される複数の信号線と、前記端子部に配置される複数の端子配線と、前記複数の信号線上に配置される有機膜からなる第3絶縁膜と、前記第3絶縁膜及び前記複数の端子配線上に配置される無機膜からなり、前記複数の端子配線の一部を露出させる複数の貫通孔を備える第4絶縁膜と、前記第4絶縁膜上に配置され、前記複数の貫通孔を介してそれぞれ前記複数の端子配線に接続される前記複数の端子と、前記複数の端子上に、前記複数の端子の一部を露出させて配置される第5絶縁膜と、を備えること特徴とする。

**【0015】**

前記複数の端子は、透光性を有する導電膜を用いて形成されるものであってもよい。

10

**【0016】**

また、前記第3絶縁膜は、アクリルまたはポリイミドを用いて形成されるものであってもよい。

**【図面の簡単な説明】**

**【0017】**

**【図1】**本発明の一実施形態に係る表示装置の概略構成を示す平面図である。

**【図2】**本発明の一実施形態に係る表示装置の概略構成を示す縦断面図である。

**【図3A】**本発明の一実施形態に係る表示装置の概略構成を示す図であり、(a)は表示装置の平面図であり、(b)は表示装置の断面図である。

**【図3B】**本発明の一実施形態に係る表示装置の概略構成を示す斜視図である。

20

**【図4】**本発明の第1の実施形態に係る表示装置の概略構成を示す断面図である。

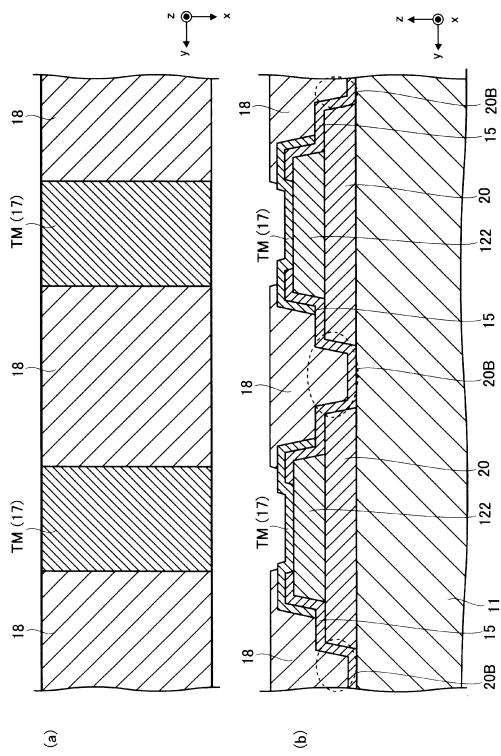

**【図5】**本発明の第1の実施形態に係る表示装置の端子部の概略構成を示す図であり、(a)は端子部の平面図であり、(b)は端子部の断面図である。

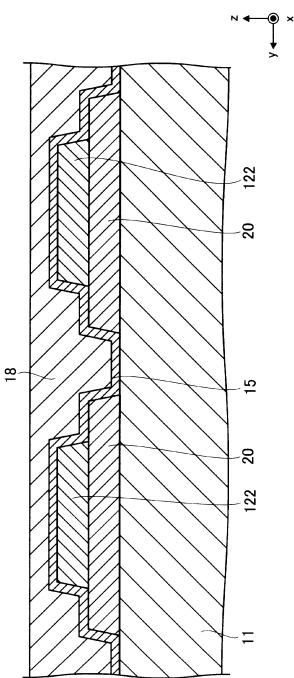

**【図6】**本発明の第1の実施形態に係る表示装置の配線部の概略構成を示す断面図である。

**【図7】**本発明の第2の実施形態に係る表示装置の概略構成を示す断面図である。

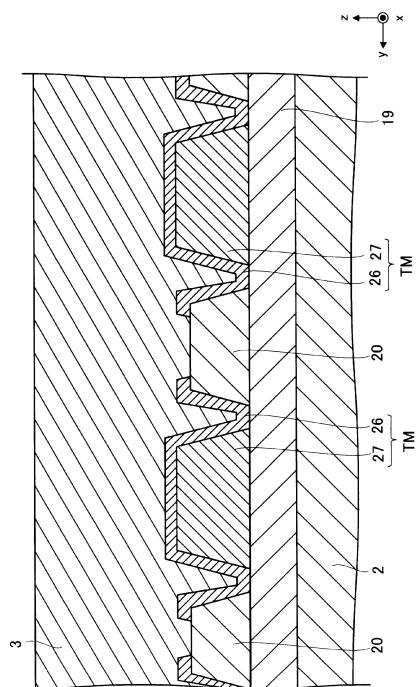

**【図8】**本発明の第2の実施形態に係る表示装置の端子部の概略構成を示す図であり、(a)は端子部の平面図であり、(b)は端子部の断面図である。

**【図9】**本発明の第2の実施形態に係る表示装置の配線部の概略構成を示す断面図である。

30

**【図10】**従来の表示装置の概略構成を示す断面図である。

**【発明を実施するための形態】**

**【0018】**

以下、図面を参照しながら、本発明の表示装置の実施形態について説明する。なお、本発明の表示装置は、以下の実施形態に限定されることなく、種々の変形を行ない実施することが可能である。

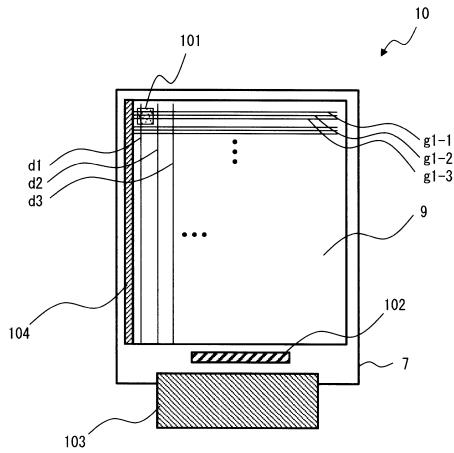

**【0019】**

図1に、本発明の一実施形態に係る表示装置10の概略構成を示す。本実施形態に係る表示装置10は、基板7上に形成された、複数の画素101の配置される表示部9、ドライバIC102、外部回路103、及び走査線駆動回路104を備える。表示部9には、図中の横方向に走る複数の制御信号線g1-1～g1-3と縦方向に走る複数のデータ信号線d1～d3とが互いに交差して配置され、制御信号線g1-1～g1-3とデータ信号線d1～d3との交差部に対応する位置に、複数の画素101がマトリクス状に配置される。

40

**【0020】**

図1には、一例として、一画素101あたり3本の制御信号線g1-1～g1-3と1本のデータ信号線d1とが交差して配置される構成を図示しているが、この構成に限定されるものではない。電源線等の一定の電圧を供給する配線が表示部9に配置されてもよい。各画素101には、制御信号線g1-1～g1-3から供給される制御信号に応じて画素101に供給されるデータ電圧の書き込みを制御することにより画素101の発光を制

50

御する薄膜トランジスタと、データ信号線 d 1 ~ d 3 から供給されるデータ電圧を保持する容量素子等を備える画素回路が配置される。

#### 【 0 0 2 1 】

基板 7 上には、駆動回路 104 に導通して駆動回路 104 に対して電源電圧や駆動信号を供給するとともにグランドへの接地を行うための多数の配線パターンが形成される。なお、図 1 に示す表示装置 10 は、一つの駆動回路 104 を備える構成として図示されているが、表示部 9 の周辺領域に、複数の駆動回路 104 が配置されていてもよい。各配線パターンの端部は、基板 7 上に形成された複数の端子にそれぞれ接続され、複数の端子は、外部から駆動電力、駆動信号及びアース電位等を供給する外部回路 103 に接続される。外部回路 103 は、フレキシブルプリント回路基板 ( F P C :Flexible printed circuits ) であってもよい。10

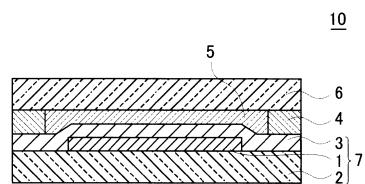

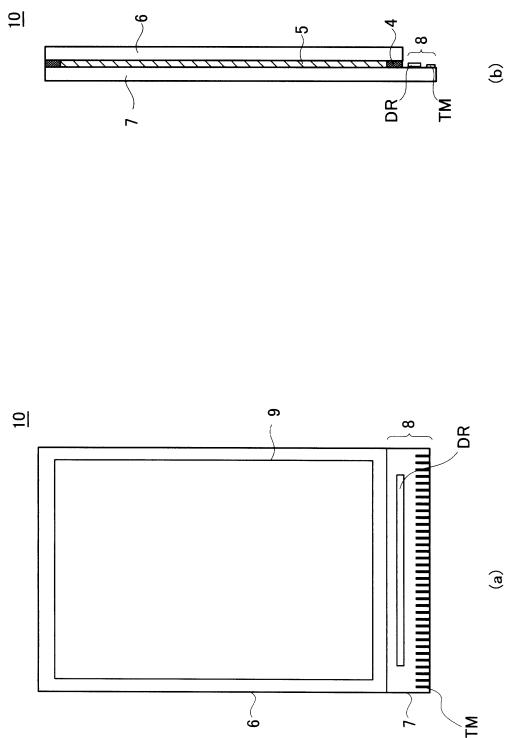

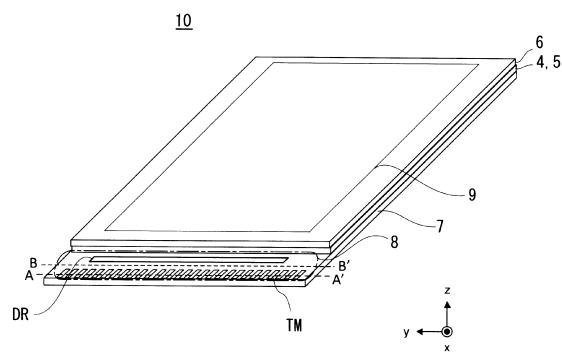

#### 【 0 0 2 2 】

以下、図 2、図 3 A 及び図 3 B を参照し、本発明の一実施形態に係る表示装置 10 の構成をより詳細に説明する。図 2 は、本発明の一実施形態に係る表示装置 10 を示す縦断面図である。図 3 A ( a ) は表示装置 10 の平面図であり、図 3 A ( b ) は表示装置 10 の断面図である。図 3 B は、本発明の一実施形態に係る表示装置 10 の概略構成を示す斜視図である。

#### 【 0 0 2 3 】

なお、以下では、本発明の一実施形態に係る表示装置の開示例として、有機 E L 発光層 1 を備える有機 E L 表示装置を例に挙げて説明するが、本実施形態に係る表示装置 10 は、液晶表示装置、その他の自発光型表示装置、電気泳動素子等を有する電子ペーパー型表示装置等、あらゆるフラットパネル型の表示装置についても同様に適用可能である。例えば、表示装置 10 は、基板 7 と対向して配置される対向基板との間に画素 101 ごとに配置される液晶層と、液晶層に光を供給するバックライトとを備える液晶表示装置であってもよい。20

#### 【 0 0 2 4 】

本発明の一実施形態に係る表示装置 10 は、図 2 に示すように、ガラス等の硬質な基板 2 上に、表示部 9 の各画素 101 を構成する有機 E L 発光層 1 を備えて形成されてもよい。図 2 では詳細な図示を省略しているが、有機 E L 発光層 1 は、基板 2 側から順に、例えば、TFT 駆動回路層、反射電極、有機 E L 層、透明電極が積層されることにより構成される。有機 E L 層は、例えば、正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層が積層されて構成される。30

#### 【 0 0 2 5 】

有機 E L 発光層 1 は、雰囲気中の水分に曝されると急速に劣化するため、外気から密閉される必要がある。このため、有機 E L 発光層 1 の表面は、例えば、CVD 成膜された窒化シリコン膜等からなる透明な封止膜 3 によって覆われるとともに、ガラス等の硬質透明部材からなる基板 6 によって覆われる。以下、基板 2 上に有機 E L 発光層 1 及び封止膜 3 が形成された構成を「第 1 基板 7」といい、これに合わせて、対向して配置される対向基板 6 を「第 2 基板 6」という。第 2 基板 6 は、カラーフィルタを含んでもよく、表示装置 10 の仕様によってはタッチパネル機能を備えた薄膜デバイス等を備えるものであってもよい。40

#### 【 0 0 2 6 】

図 2 に示すように、表示装置 10 は、第 1 基板 7 と第 2 基板 6 との間隙において、両者間の距離を一定に保つことにより有機 E L 発光層 1 の表面と第 2 基板 6 の表面とを平行に保つとともに、両者の界面における反射や屈折を防止するために、例えば、エポキシ樹脂等の透明な樹脂 4、5 が充填される。また、樹脂 4、5 以外にも、シール材等の公知の材料を用いて第 1 基板 7 と第 2 基板 6 との間隙を維持してもよい。また、第 1 基板 7 と第 2 基板 6 との間隙がシール材等を用いて維持される構成であれば、第 1 基板 7 と第 2 基板 6 との間に空隙を有する構成としてもよい。このように第 1 基板 7 上に第 2 基板 6 が接合されることにより表示装置 10 が構成される。50

**【 0 0 2 7 】**

このような構成を備える表示装置 10 は、図 3 A 及び図 3 B に示すように、画像を表示するための領域であって複数の画素 101 が配置される表示部 9 と、外部回路と電気的な接続を行うための複数の端子 TM が配置される領域である端子部 8 とを備える。

**【 0 0 2 8 】**

図 3 A 及び図 3 B に示すように、端子部 8 において、複数の端子 TM は、図 2 に示す封止膜 3、樹脂 4、5 及び第 2 基板 6 に覆われずに露出されて形成される。複数の端子 TM の露出された端部は、例えば、駆動信号を供給する外部回路 103 ( 図 1 に図示 ) に接続される。また、複数の端子 TM は、基板 2 上に形成された配線及びドライバ DR 等を介して有機 EL 発光層 1 の薄膜トランジスタ等に接続される。なお、図 3 A 及び図 3 B に示すドライバ DR が、図 1 に示すドライバ IC 102 に対応する。10

**【 0 0 2 9 】**

このような表示装置 10 の製造工程上、有機 EL 発光層 1 を覆う封止膜 3 を、パテーニングせずに基板 2 の全面を覆って成膜した場合、端子部 8 においては、複数の端子 TM を封止膜 3 から露出させる処理を行う必要がある。複数の端子 TM を露出させる方法としては、端子部 8 上に封止膜 3 を形成した後、テープ剥離やエッティング ( ドライまたはウェット ) により端子部 8 上の封止膜 3 を除去する方法が知られている。

**【 0 0 3 0 】**

また、端子部 8 の劣化を防止するために、複数の端子 TM 及び配線上に窒化シリコン膜等の無機膜を用いて保護膜を形成することがある。しかし、端子部 8 の保護膜に無機膜を用いてしまうと、保護膜が封止膜 3 と同じ無機膜となってしまうことから、端子部 8 上の封止膜 3 をエッティングにより除去する際に保護膜まで除去してしまう虞がある。20

**【 0 0 3 1 】**

そこで、従来の表示装置には、複数の端子および配線上に保護膜を形成しない構成とするものがある。このような従来の表示装置の端子部の構成を、図 10 を参照して説明する。。

**【 0 0 3 2 】**

図 10 は、従来の表示装置の端子部の概略構成を示す断面図であり、図 3 B に示す A - A' 線で端子部を切断した場合の二つの端子 TM の断面構成を示したものである。端子 TM は、基板 2 上に形成された第 1 絶縁膜 19 上に、各端子 TM が第 2 絶縁膜 20 によって絶縁されるように第 2 絶縁膜 20 の間に形成される。第 1 絶縁膜 19 及び第 2 絶縁膜 20 は酸化シリコン膜や窒化シリコン膜等を用いて形成されてもよく、第 1 絶縁膜 19 及び第 2 絶縁膜 20 はそれぞれ各画素 101 の薄膜トランジスタを形成する際に形成する、アンダーコート膜または層間絶縁膜と呼ばれる絶縁膜と同じ層に同じ材料を用いて形成されてもよい。また、第 1 絶縁膜 19 及び第 2 絶縁膜 20 は複数層を含み得る。30

**【 0 0 3 3 】**

端子 TM 及び端子 TM に接続される配線は、アルミニウム等の金属を用いて第 2 絶縁膜 20 の高さよりも高い凸部 27 を形成した後、ITO 等の透明導電膜 26 により凸部 27 を覆って形成される。封止膜 3 は、このように最表面が ITO 等の透明導電膜 26 で覆われた端子 TM 及び配線上に形成される。しかし、このような従来の表示装置の端子 TM 及び配線は、封止膜 3 を除去する際などに、凸部 27 のエッジ部分上に形成された透明導電膜 26 から凸部 27 を構成するアルミニウム等の金属が露出するといった信頼性の問題を発生させる虞があった。40

**【 0 0 3 4 】**

このため、複数の端子 TM の保護膜として有機膜を用いる場合がある。有機膜は、例えば、アクリル、ポリイミド等の有機材料を用いて形成される。しかし、このような有機膜は膜厚を制御することが難しく、端子 TM の接触面と保護膜との間に段差を生じさせてしまう虞があった。また、有機膜を端子 TM の保護膜として用いる場合、有機膜の厚さによつては外部回路 103 の実装時に使用される異方性導電膜 ( ACF ) の導電粒子の形状に制約が生じ、実装不良を引き起こす虞があった。50

**【 0 0 3 5 】**

そこで、本発明者は、端子部 8 において外部回路 103 等の実装に影響を与えることなく、複数の端子 TM を保護可能な方法を検討し、本発明に至った。

**【 0 0 3 6 】**

## (第 1 の実施形態)

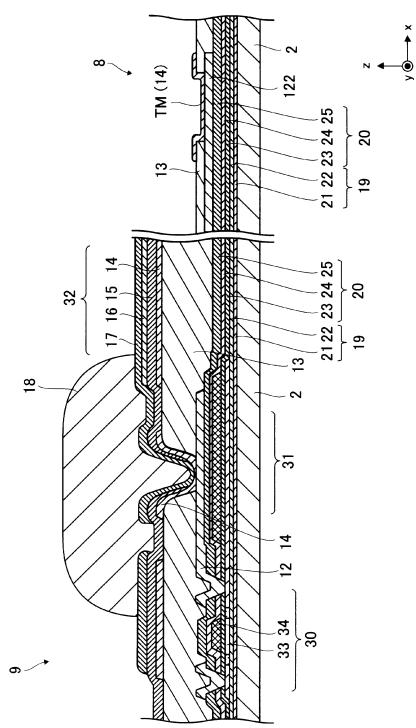

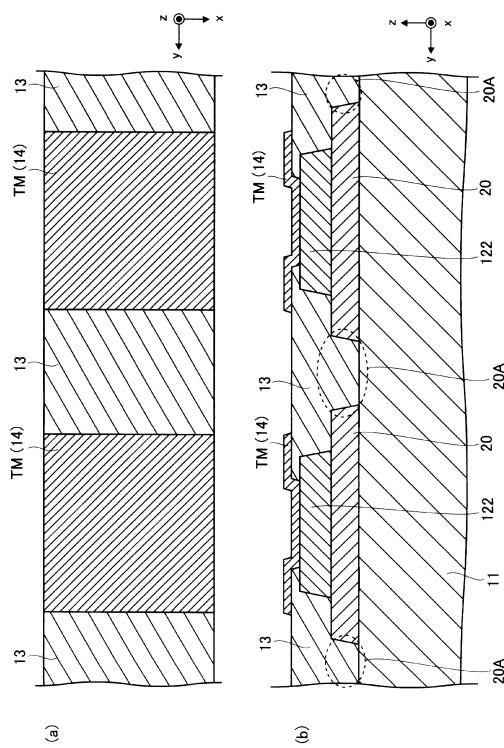

以下、図 4 乃至図 6 を参照し、本発明の第 1 の実施形態に係る表示装置 10 の概略構成について説明する。図 4 は、本発明の第 1 の実施形態に係る表示装置 10 の概略構成を示す断面図である。図 5 は、本発明の第 1 の実施形態に係る表示装置 10 の端子部の概略構成を示す図であり、(a) は端子部の平面図であり、(b) は端子部の断面図である。図 6 は、本発明の第 1 の実施形態に係る表示装置 10 の配線部の概略構成を示す断面図である。

10

**【 0 0 3 7 】**

なお、以下では本実施形態に係る表示装置 10 の開示例として、有機 EL 発光層 1 を備える有機 EL 表示装置を例に挙げて説明するが、本実施形態に係る表示装置 10 は、薄膜トランジスタを用いて各画素の表示階調を制御する表示装置であれば、上述したように、液晶表示装置、その他の自発光型表示装置、電気泳動素子等を有する電子ペーパー型表示装置等、あらゆるフラットパネル型の表示装置について同様に適用可能である。また、以下、図 1 乃至図 3 に示して上述した構成と同様の構成については同じ符号を付し、その詳細な説明について省略する。

**【 0 0 3 8 】**

20

図 4 は、本発明の第 1 の実施形態に係る表示装置 10 の端子部 8 のうち、一つの端子に対応する領域と、表示部 9 のうち、一つの画素 101 に対応する領域の断面構成を図示したものである。図 4 に示すように、表示部 9 の一つの画素 101 に対応する領域は、薄膜トランジスタを含むトランジスタ部 30、信号線 12 からの電圧を保持する容量素子を含む容量部 31、各画素 101 の発光領域である画素部 32 を含む。

**【 0 0 3 9 】**

図 4 に示すように、基板 2 上には、薄膜トランジスタ下に酸化シリコン膜や窒化シリコン膜等を用いて形成された 2 層の絶縁膜 21、22 からなる第 1 絶縁膜 19 が形成される。この第 1 絶縁膜 19 の上にはポリシリコン層 33、ゲート絶縁膜 23、ゲート電極層 34 が形成される。ポリシリコン層 33 は一部に不純物がドープされ、ドレイン電極やソース電極が接続されて、薄膜トランジスタが構成されている。薄膜トランジスタ上には層間絶縁膜として酸化シリコン膜や窒化シリコン膜等を用いて形成された 2 層の絶縁膜 24、25 が形成される。端子部 8 や表示部 9 の一部ではゲート絶縁膜 23 と 2 層の絶縁膜 24、25 によって第 2 絶縁膜 20 が形成される。なお、図 4 には、第 1 絶縁膜 19 及び第 2 絶縁膜 20 が複数層からなる構成の一例として、2 層または 3 層からなる第 1 絶縁膜 19 及び第 2 絶縁膜 20 を図示しているが、図示した構成に限定されるものではない。例えば、第 2 絶縁膜 20 は薄膜トランジスタ上に形成された絶縁膜で構成され、ゲート絶縁膜 23 を含まなくてもよい。この場合、ゲート絶縁膜 23 はポリシリコン層 33 上のみに形成されている。

30

**【 0 0 4 0 】**

40

第 2 絶縁膜 20 には、複数の薄膜トランジスタの少なくとも一部を開口するコンタクトホールが形成される。表示部 9 の第 2 絶縁膜 20 上には複数の信号線 12 が形成され、複数の信号線 12 はコンタクトホールを介して薄膜トランジスタに接続される。薄膜トランジスタに接続された信号線 12 は、有機膜からなる第 3 絶縁膜 13 によって覆われる。第 3 絶縁膜 13 上には、第 3 絶縁膜 13 に形成されたコンタクトホールにより信号線 12 に接続された第 1 導電膜 14、第 1 導電膜 14 上に形成された第 4 絶縁膜 15、及び第 4 絶縁膜 15 上に形成された第 2 導電膜 17 が形成される。第 1 導電膜 14、第 4 絶縁膜 15、及び第 2 導電膜 17 により、容量部 31 に並列な容量素子が形成される。第 1 導電膜 14 は ITO 等の透光性を有する導電膜を用いて形成され、第 4 絶縁膜 15 は窒化シリコン等の無機膜を用いて形成され、第 2 導電膜 17 は ITO 等の透光性を有する導電膜を用い

50

て形成される。

**【0041】**

また、図4に示す画素部32において、第2導電膜17下に、アルミニウム等からなる反射電極16が配置されて有機EL発光層1のアノード電極（陽極、反射電極）を構成してもよい。図4には図示していないが、第2導電膜17上有機EL層及び透明電極（陰極）が形成されて有機EL発光層1を構成してもよい。また、第2導電膜17上有各画素101を区画するバンク層として有機膜からなる第5絶縁膜18が形成される。

**【0042】**

一方、図4に示す端子部8において、第2絶縁膜20上には複数の端子配線122が形成される。端子配線122は第3絶縁膜13によって覆われている。、端子配線122上の第3絶縁膜13の一部が除去され、端子配線122の一部が第3絶縁膜13から露出されて形成される。露出された端子配線122上に、第3絶縁膜13の上面までを一部覆って、ITO等の透明導電膜からなる第1導電膜14が形成される。第1導電膜14は、上述したように表示部9においては容量素子を構成する層である。このように、端子部8には、図2A乃至図3に示して上述した複数の端子TMを構成する第1導電膜14が形成される。

**【0043】**

以下、図5及び図6を参照し、端子部8に形成される複数の端子TM及び配線の製造工程について詳細に説明する。

**【0044】**

図5(b)は、図3Bに示すA-A'線で表示装置10の端子部8を切断した場合の二つの端子TMの断面構成を示す図であり、図5(a)は、図5(b)に示す二つの端子TMの平面構成を示す図である。図6は、図3Bに示すB-B'線で表示装置10の配線部を切断した場合の二つの端子配線122の断面構成を示す図である。

**【0045】**

図5(b)及び図6に示す基板11は、図4に示す基板2上に第1絶縁膜19が配置された構成を図示したものである。端子部8において、基板11上に、上述したように、層間絶縁膜と同層に同じ材料を用いて第2絶縁膜20を形成する。基板11上に形成された第2絶縁膜20は、図5(b)に点線20Aで囲む範囲に図示したように、端子配線122の配置されない領域をエッチング等の公知の方法を用いて除去して開口部を形成する。このような端子部8における第2絶縁膜20のエッチング工程は、表示部9における薄膜トランジスタの層間絶縁膜（第2絶縁膜20）のエッチング工程と同時に、一つのマスクを用いて実施することができる。このとき、表示部9においては、複数の薄膜トランジスタの複数の電極上の第2絶縁膜20をエッチングして第2絶縁膜20に複数のコンタクトホールを形成する。第2絶縁膜20にこのような複数のコンタクトホールを形成することにより、後述する接続工程において複数の信号線12が形成されると、第2絶縁膜20の複数のコンタクトホールを介して複数の信号線12と複数の薄膜トランジスタとをそれぞれ接続させることができる。

**【0046】**

なお、第2絶縁膜20をパターニングにより除去することにより形成される開口部の形状は、図5(b)に点線20Aで示す範囲及び開口部の形状に限らず、後述する製造工程において第2絶縁膜20上に塗布される第3絶縁膜13を所望の膜厚とする塗布量に応じて決定される。従って、端子部8の第2絶縁膜20は、第3絶縁膜13の塗布量によっては、端子配線122の配置されない領域に第2絶縁膜20を除去しない部分があつてもよく、図5(b)に図示した構成に限定されるものではない。

**【0047】**

次に、第2絶縁膜20上に、アルミニウム等の金属材料を用いて信号線12及び端子配線122を形成する。信号線12及び端子配線122は、第2絶縁膜20上に成膜された金属膜をパターニングすることにより表示部9及び端子部8において一つのマスクを用いて同時に形成する。これにより、表示部9においては、図4に示すように、第2絶縁膜2

10

20

30

40

50

0のコンタクトホールを介して薄膜トランジスタのソース／ドレイン電極と接続される信号線12が形成されてもよく、端子部8においては、図5(b)及び図6に示すように、第2絶縁膜20上に端子配線122が形成される。

#### 【0048】

次に、表示部9及び端子部8において、信号線12及び端子配線122上に、信号線12及び端子配線122を覆う第3絶縁膜13を形成する。第3絶縁膜13は、アクリル、ポリイミド等の有機材料を用いて形成する。このとき、端子部8においては第2絶縁膜20が除去された開口部に、第3絶縁膜13の有機材料が充填される。このとき、第2絶縁膜20の開口部の開口面積を最適化することにより、端子配線122上に形成される第3絶縁膜13の膜厚を、所望の膜厚に制御することが可能となる。

10

#### 【0049】

つまり、端子配線122上に形成される第3絶縁膜13の膜厚を例えば1μm以下の薄い膜厚とする場合、第2絶縁膜20の一部を除去することなく、第3絶縁膜13の有機材料の塗布量を微調整することのみで膜厚を制御する工程は、本実施形態のように第2絶縁膜20を所望の面積で除去した後に有機材料を塗布して膜厚を制御する工程よりも、膜厚の制御に高い精度が要求される。従って、本実施形態によると、予め第2絶縁膜20を一部除去しておくことにより、第3絶縁膜13の膜厚の制御を容易なものすることができ、また、第2絶縁膜20を一部除去する工程は、表示部9における薄膜トランジスタの層間絶縁膜(第2絶縁膜20)のパターニングと同時に行うことができるため、既存の製造プロセスを大幅に変更することなく、簡易な製造方法で、端子配線122上に所望の膜厚の第3絶縁膜13を形成することが可能となる。

20

#### 【0050】

このような製造工程により、端子配線122を覆う保護膜として第3絶縁膜13が形成される。また、図5(b)に示すように、端子部8において、第3絶縁膜13をエッチングにより一部除去して端子配線122を露出させる貫通孔を形成する。貫通孔によって端子配線122が露出された領域上に、ITO等の透明導電膜からなる第1導電膜14を塗布してパターニングすることにより、複数の端子TMが形成される。このとき、第1導電膜14の端子配線122との接触面から第3絶縁膜13の上面に延長された部分に段差が形成される。しかし、本実施形態によれば、このような第1導電膜14に形成される段差を約1μm以下に形成することができる。

30

#### 【0051】

このように、本実施形態によれば、端子TMを構成する第1導電膜14に形成される段差を約1μm以下と小さくすることができる。これにより、端子部8に外部回路103を実装する際に用いられる異方性導電膜(ACF)について、導電粒子径の小さなものを選択することができ、端子TMの接続抵抗を低減させることができるとなる。すなわち、端子TMに形成される段差が1μm以上であると、異方性導電膜(ACF)の導電粒子をうまく潰せない状態が発生し、線欠陥等の不具合が発生する虞があることから、導電粒子径の大きなものを選択する必要があった。しかし、導電粒子径の大きな異方性導電膜(ACF)を選択すると、配線ピッチを狭められなくなる問題や、単位面積当たりの粒子数が少なくなることにより接続面積が小さくなり、接続抵抗が上昇する問題を生じさせる虞があった。このため、本実施形態のように、第3絶縁膜13の膜厚を制御して第1導電膜14に形成される段差を約1μm以下とすることにより、導電粒子径の小さな異方性導電膜(ACF)を選択することができるため、接続抵抗を低減させることができとなり、実装不良が生じることを防ぐことが可能となる。

40

#### 【0052】

また、本実施形態によると、端子TM間及び端子配線122上に保護膜として形成される第3絶縁膜13が有機材料を用いて形成されることから、有機膜からなる保護膜によって耐水性を向上させ、端子TM及び端子配線122の腐食を防止することができる。従つて、端子部8における接続の信頼性を向上させることができとなる。

#### 【0053】

50

以上のとおり、本実施形態によると、端子部 8 の各端子 T M 及び端子配線 1 2 2 を有機膜からなる第 3 絶縁膜 1 3 によって保護しつつ、第 3 絶縁膜 1 3 を所望の膜厚に形成することができるため、外部回路 1 0 3 を実装する際に、実装歩留りを悪化させることなく、表示装置の高信頼性を確保することが可能となる。また、このような表示装置を、製造プロセスを大幅に変更することなく、簡易な製造工程により実現することができる。

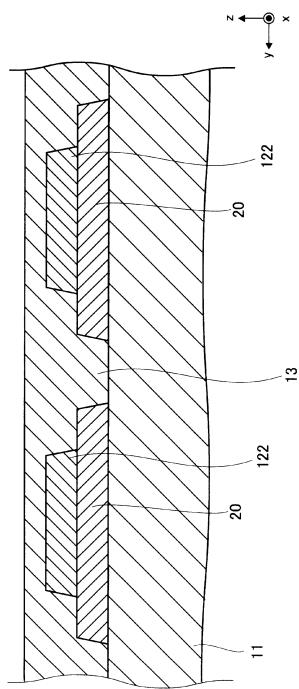

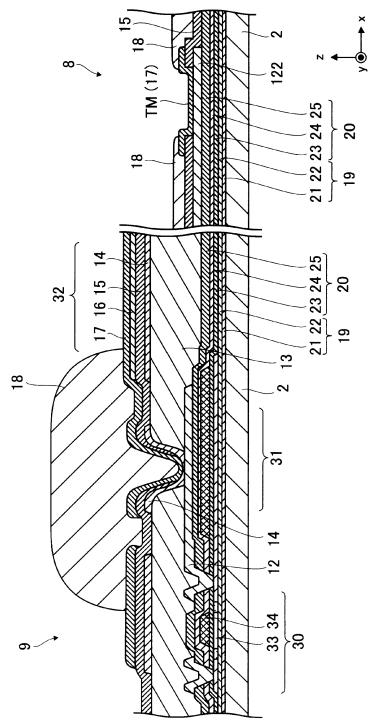

#### 【 0 0 5 4 】

##### ( 第 2 の実施形態 )

以下、図 7 乃至図 9 を参照し、本発明の第 2 の実施形態に係る表示装置の概略構成について説明する。図 7 は、本発明の第 2 の実施形態に係る表示装置の概略構成を示す断面図である。図 8 は、本発明の第 2 の実施形態に係る表示装置の端子部の概略構成を示す図であり、( a ) は端子部の平面図であり、( b ) は端子部の断面図である。図 9 は、本発明の第 2 の実施形態に係る表示装置の配線部の概略構成を示す断面図である。

10

#### 【 0 0 5 5 】

なお、本発明の第 2 の実施形態に係る表示装置 1 0 は、本発明の第 1 の実施形態に係る表示装置 1 0 とは、保護膜として第 3 絶縁膜 1 3 のような有機膜のみならず、有機膜下に無機膜からなる保護膜を配置した点においてその構成が異なる。従って、以下、図 4 乃至図 6 に示して上述した構成と同様の構成については同じ符号を付し、その詳細な説明を省略する。

#### 【 0 0 5 6 】

図 7 に示すように、本発明の第 2 の実施形態に係る表示装置 1 0 は、基板 2 上に、本発明の第 1 の実施形態に係る表示装置 1 0 と同様に、第 1 絶縁膜 1 9 及び第 2 絶縁膜 2 0 が形成される。端子部 8 の第 2 絶縁膜 2 0 は、図 8 ( b ) に点線 2 0 B で囲む範囲に図示したように、本発明の第 1 の実施形態に係る表示装置 1 0 と同様に、端子配線 1 2 2 の配置されない領域をエッティング等の公知の方法を用いて除去して開口部を形成する。このエッティング工程は、表示部 9 における薄膜トランジスタの層間絶縁膜（第 2 絶縁膜 2 0 ）のエッティング工程と同時にを行うことができる。

20

#### 【 0 0 5 7 】

第 2 絶縁膜 2 0 上に金属膜をパターニングして信号線 1 2 及び端子配線 1 2 2 を形成した後、第 2 絶縁膜 2 0 並びに信号線 1 2 及び端子配線 1 2 2 を覆う、無機膜からなる第 4 絶縁膜 1 5 を形成する。第 4 絶縁膜 1 5 は、表示部 9 において容量部 3 1 の容量素子を構成する層であり、窒化シリコン等の無機膜を用いて形成する。

30

#### 【 0 0 5 8 】

次に、端子配線 1 2 2 上の第 4 絶縁膜 1 5 をエッティングにより一部除去して端子配線 1 2 2 を露出させ、端子配線 1 2 2 の露出された領域上に、I T O 等の透明導電膜からなる第 2 導電膜 1 7 を塗布してパターニングすることにより、複数の端子 T M を形成する。第 2 導電膜 1 7 は、端子配線 1 2 2 の露出された領域とその周辺領域である第 4 絶縁膜 1 5 の上面を一部覆って形成される。第 2 導電膜 1 7 は、有機 E L 発光層 1 のアノード電極（陽極）を構成する層であってもよい。

#### 【 0 0 5 9 】

このように形成された第 4 絶縁膜 1 5 及び第 2 導電膜 1 7 上に、アクリル、ポリイミド等の有機材料を用いて第 5 絶縁膜 1 8 を形成する。第 5 絶縁膜 1 8 は、表示部 9 においては、各画素 1 0 1 の領域を区画するバンク層として機能する層である。第 5 絶縁膜 1 8 は、端子部 8 において、端子 T M を構成する部分の第 2 導電膜 1 7 が露出されるようにパターニングされて形成される。このような第 5 絶縁膜 1 8 のパターニングの工程は、表示部 9 においてバンク層を形成する際のパターニングと同時にを行うことができる

40

#### 【 0 0 6 0 】

また、第 5 絶縁膜 1 8 は、端子部 8 において第 2 絶縁膜 2 0 が除去されることにより形成された、図 8 ( b ) に点線 2 0 B で囲む範囲に示す開口部に充填される。従って、本実施形態においても、第 1 の実施形態に係る表示装置 1 0 の製造工程と同様に、第 2 絶縁膜 2 0 の開口部の開口面積を最適化することにより、第 2 導電膜 1 7 上に形成される第 5 絶縁膜 1 8 の充填量を最適化することができる。

50

縁膜 18 の膜厚を、所望の膜厚に制御することが可能となる。従って、既存の製造プロセスを大幅に変更することなく、簡易な製造方法で、端子 TM を構成する第 2 導電膜 17 と第 2 導電膜 17 上の第 5 絶縁膜 18 との間に形成される段差を、外部回路 103 の実装に影響を与えることがない程度に小さくすることができる。

#### 【0061】

また、本実施形態によると、窒化シリコン等の無機膜からなる第 4 絶縁膜 15 によって端子配線 122 を保護する構成を備えている上、この第 4 絶縁膜 15 上に有機膜である第 5 絶縁膜 18 が形成される構成を備えていることから、耐水性を向上させることができ、腐食を防止し、より高い信頼性を有する表示装置 10 を製造することができる。

#### 【0062】

以上のとおり、本発明の第 1 及び第 2 の実施形態によると、端子部 8 の各端子 TM 及び端子配線 122 を有機膜からなる第 3 絶縁膜 13 または第 5 絶縁膜 18 によって保護しつつ、第 3 絶縁膜 13 または第 5 絶縁膜 18 を所望の膜厚に形成することができるので、外部回路 103 を実装する際に、実装歩留りを悪化させることなく、表示装置の高信頼性を確保することができる。また、このような表示装置を、製造プロセスを大幅に変更することなく、簡易な製造工程により実現することができる。

#### 【符号の説明】

#### 【0063】

1 ... 有機 E L 発光層、2 ... 基板、3 ... 封止膜、4、5 ... 樹脂、6 ... 第 2 基板、7 ... 第 1 基板、8 ... 端子部、9 ... 表示部、10 ... 表示装置、11 ... 基板、12 ... 信号線、13 ... 第 3 絶縁膜、14 ... 第 1 導電膜、15 ... 第 4 絶縁膜、17 ... 第 2 導電膜、18 ... 第 5 絶縁膜、19 ... 第 1 絶縁膜、20 ... 第 2 絶縁膜、30 ... トランジスタ部、31 ... 容量部、32 ... 画素部、101 ... 画素、103 ... 外部回路、104 ... 駆動回路、122 ... 端子配線、TM ... 端子

【図 1】

【図 2】

【図3A】

【図3B】

【図4】

【図5】

【 図 6 】

【 义 7 】

【 四 8 】

【図9】

【図10】

---

フロントページの続き

| (51)Int.Cl. |       | F I                                      |

|-------------|-------|------------------------------------------|

| G 0 9 F     | 9/30  | (2006.01) G 0 9 F 9/30 3 3 0             |

| H 0 1 L     | 51/50 | (2006.01) G 0 9 F 9/30 3 3 8             |

| H 0 5 B     | 33/06 | (2006.01) H 0 5 B 33/14 A                |

| H 0 5 B     | 33/10 | (2006.01) H 0 5 B 33/06<br>H 0 5 B 33/10 |

(56)参考文献 米国特許出願公開第2007/0075313(US, A1)

国際公開第2007/063667(WO, A1)

米国特許出願公開第2009/0141438(US, A1)

特開2000-221540(JP, A)

米国特許第06366331(US, B1)

特開平11-327465(JP, A)

特開2006-066206(JP, A)

特開平10-170933(JP, A)

特開2005-099301(JP, A)

## (58)調査した分野(Int.Cl., DB名)

|         |             |

|---------|-------------|

| G 0 9 F | 9 / 0 0     |

| G 0 2 F | 1 / 1 3 4 5 |

| G 0 2 F | 1 / 1 3 6 8 |

| G 0 9 F | 9 / 3 0     |

| H 0 1 L | 2 1 / 3 3 6 |

| H 0 1 L | 2 9 / 7 8 6 |

| H 0 1 L | 5 1 / 5 0   |

| H 0 5 B | 3 3 / 0 6   |

| H 0 5 B | 3 3 / 1 0   |