(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4939201号

(P4939201)

(45) 発行日 平成24年5月23日(2012.5.23)

(24) 登録日 平成24年3月2日(2012.3.2)

(51) Int.Cl.

H03M 1/08 (2006.01)

F 1

H03M 1/08

A

請求項の数 12 外国語出願 (全 13 頁)

(21) 出願番号 特願2006-340437 (P2006-340437)

(22) 出願日 平成18年12月18日 (2006.12.18)

(65) 公開番号 特開2007-195159 (P2007-195159A)

(43) 公開日 平成19年8月2日 (2007.8.2)

審査請求日 平成21年10月27日 (2009.10.27)

(31) 優先権主張番号 11/333935

(32) 優先日 平成18年1月18日 (2006.1.18)

(33) 優先権主張国 米国(US)

(73) 特許権者 502188642

マーベル ワールド トレード リミテッド

バルバドス国 ビービー14027, セントマイケル、ブリトンズ ヒル、ガンサイ

トロード、エル ホライズン

(74) 代理人 100094318

弁理士 山田 行一

(74) 代理人 100123995

弁理士 野田 雅一

(72) 発明者 セハット スタージャ

アメリカ合衆国、カリフォルニア州、ロス

アルトス ヒルズ、エレナ ロード

27330

最終頁に続く

(54) 【発明の名称】パイプライン型アナログ・デジタル変換器

## (57) 【特許請求の範囲】

## 【請求項 1】

パイプライン型アナログ・デジタル変換器(ADC)であって、

入力電圧と第1の残差電圧のうちの一方及び第1の基準電圧を受け取り、第1のデジタル信号及び第2の残差電圧を発生する第1のADCステージと、

前記第1のADCステージからの前記第2の残差電圧と、前記第1の基準電圧より低く該第1の基準電圧から独立した第2の基準電圧とを受け取り、第2のデジタル信号を発生する第2のADCステージと、

アナログ基準電圧である前記第1の基準電圧を発生するアナログ電圧源と、

デジタル基準電圧である前記第2の基準電圧を発生するデジタル電圧源と、

を備えるパイプライン型ADC。

10

## 【請求項 2】

前記第1の基準電圧を受け取るアナログ回路と、

前記第2の基準電圧を受け取るデジタル回路と、

を更に備える、請求項1に記載のパイプライン型ADC。

## 【請求項 3】

前記第1のADCステージが、

前記入力電圧と前記第1の残差電圧のうちの前記一方をサンプルしホールドする第1のサンプルホールドモジュールと、

前記第1のサンプルホールドモジュールの出力を前記第1のデジタル信号に変換する第

20

1のアナログ・デジタル変換器と、

前記第1のデジタル信号を第1のアナログ信号に変換する第1のデジタル・アナログ変換器と、

を更に備える、請求項1に記載のパイプライン型ADC。

**【請求項4】**

前記第1のADCステージが、

前記第1のサンプルホールドモジュールの前記出力と前記第1のアナログ信号との間の差を発生する差分モジュールと、

前記差を増幅する増幅モジュールと、

を更に備える、請求項3に記載のパイプライン型ADC。

10

**【請求項5】**

前記第2の基準電圧より低い第3の基準電圧を受け取る第3のADCステージを更に備える、請求項1に記載のパイプライン型ADC。

**【請求項6】**

前記第3のADCステージが前記第2のADCステージから第3の残差電圧を受け取る、請求項5に記載のパイプライン型ADC。

**【請求項7】**

アナログ基準電圧又はデジタル基準電圧のうち一方である第3の基準電圧を受け取る少なくとも一つの追加のADCステージを更に備える、請求項1に記載のパイプライン型ADC。

20

**【請求項8】**

請求項1記載のパイプライン型ADCを備える集積回路であって、

前記アナログ電圧源及び前記デジタル電圧源が電圧レギュレータを含む、集積回路。

**【請求項9】**

前記アナログ電圧源が電源から電力を受け取り、前記デジタル電圧源が前記電源から電力を受け取る、請求項8に記載の集積回路。

**【請求項10】**

前記第1の基準電圧及び前記第2の基準電圧のうち少なくとも一方から独立した第3の基準電圧を受け取る少なくとも一つの追加のADCステージを更に備える、請求項1に記載のパイプライン型ADC。

30

**【請求項11】**

前記第1のサンプルホールドモジュール、前記第1のアナログ・デジタル変換器、及び前記第1のデジタル・アナログ変換器の各々が、前記アナログ基準電圧を受け取り、

前記第2のADCステージが、

前記第2の残差電圧をサンプルしホールドする第2のサンプルホールドモジュールと

、前記第2のサンプルホールドモジュールの出力を前記第2のデジタル信号に変換する第2のアナログ・デジタル変換器と、

前記第2のデジタル信号を第2のアナログ信号に変換する第2のデジタル・アナログ変換器と、

を有し、

前記第2のサンプルホールドモジュール、前記第2のアナログ・デジタル変換器、及び前記第2のデジタル・アナログ変換器の各々が、前記デジタル基準電圧を受け取る、請求項3に記載のパイプライン型ADC。

40

**【請求項12】**

前記第1のADCステージが、前記入力電圧を受け取り、

前記入力電圧が、アナログ入力電圧であり、

前記第1のADCステージが、前記アナログ入力電圧を量子化することにより前記第1のデジタル信号を生成し、該第1のデジタル信号と前記アナログ基準電圧に基づいて第1

50

のアナログ出力電圧を生成し、

前記第2のA D Cステージが、前記第1のアナログ出力電圧を受け取り、該第1のアナログ出力電圧を量子化することにより前記第2のデジタル信号を生成し、該第2のデジタル信号と前記デジタル基準電圧に基づいて第2のアナログ出力電圧を生成する、

請求項1に記載のパイプライン型A D C。

【発明の詳細な説明】

【分野】

【0 0 0 1】

[0001]本開示は、パイプライン型アナログ・デジタル変換器（A D C）に関するものである。 10

【背景】

【0 0 0 2】

[0002]電子デバイスの消費電力の削減は、特に、ラップトップコンピュータ、携帯情報端末、携帯電話機、M P 3プレーヤー、及び、その他の装置のようなバッテリー電源式装置にとってますます重要になっている。アナログ・デジタル変換器（A D C）は、アナログ信号をデジタル信号に変換するために、一般にこれらの電子デバイスにおいて使用されている。A D Cは、複数のステージを利用するパイプライン型A D Cを含むことがある。各ステージは、パイプライン型A D Cへのアナログ入力電圧 $V_{in}$ 又は前のステージからの残差電圧 $V_{res}$ をサンプリングするサンプルホールド回路を使用する。さらに、各ステージは基準電圧 $V_{ref}$ を受け取る。 20

【0 0 0 3】

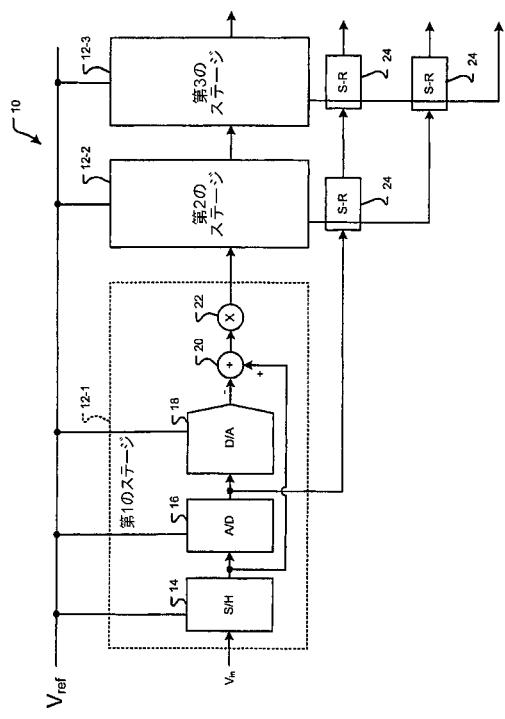

[0003]ここで図1を参照する。この図は、典型的なパイプライン型A D Cを示している。A D C10は、直列にカスケード接続された複数のステージ12-1、12-2及び12-3（総称してステージ12）を含んでいる。3段のステージ12-1、12-2及び12-3が示されているが、パイプライン型A D Cに含まれるステージは増減してもよい。幾つかのA / D変換器ステージ12は、アナログ入力信号 $V_{in}$ 又は前のステージからの残差信号 $V_{res}$ をサンプルしホールドするサンプルホールドモジュール14を含んでいる。低分解能A / Dサブ変換器モジュール16は、ホールドされたアナログ信号を $B_i$ ビットの分解能に量子化する。ここで、 $i$ は、パイプライン型A / D変換器10の現在ステージに対応する。1ステージ当たりのビット数 $B_i$ 及び/又はステージ数は、ある程度においては、所望のサンプリングレート及び分解能によって決定される。A / Dサブ変換器モジュール16の出力は、得られたデジタル出力信号を元のアナログ表現に変換する低分解能D / Aサブ変換器モジュール18に供給される。 30

【0 0 0 4】

[0004]D / Aサブ変換器モジュール18は、同ステージの対応のA / Dサブ変換器モジュール16の分解能と等しい分解能を有し得る。差分モジュール20は、D / Aサブ変換器モジュール18からのアナログ出力を電圧入力 $V_{in}$ から減算し、残差信号 $V_{res}$ を発生する。残差信号 $V_{res}$ は、ホールドされたアナログ信号（ $V_{in}$ 又は前のステージからの $V_{res}$ ）と再構成されたアナログ信号との間の差に等しい。 40

【0 0 0 5】

[0005]アナログステージ間差分モジュール22は、残差信号を増幅するため使用される。増幅された残差信号は、パイプライン型A D C10の次のステージ12-2へ出力される。パイプライン型A D C10の第1のA D Cステージ12-1は最新のアナログ入力サンプルに基づいて動作し、第2のA D Cステージ12-2は前の入力サンプルの増幅された残差に基づいて動作する。第3のステージ12-3は第2のA D Cステージ12-2によって出力された増幅された残差に基づいて動作する。

【0 0 0 6】

[0006]動作の並行性によって、変換速度が1ステージ内で要する時間によって決定されることが可能になる。現在のステージが前のステージから受け取ったアナログ入力サンプルに基づく動作を終了すると、現在のステージは次のサンプルに基づく動作のために利用 50

可能となる。

**【概要】**

**【0007】**

[0007]パイプライン型アナログ・デジタル変換器が、入力電圧と第1の残差電圧とのうちの一方及び第1の基準電圧を受け取り、第1のデジタル信号及び第2の残差電圧を発生する第1のADCステージを備える。第2のADCステージは、第1のADCステージからの第2の残差電圧と、第2の基準電圧とを受け取り、第2のデジタル信号を発生する。第2の基準電圧は第1の基準電圧より低い。

**【0008】**

[0008]また、システムが、上記のパイプライン型アナログ・デジタル変換器を備え、第1の基準電圧を供給する第1の電圧源を更に備える。第2の電圧源は第2の基準電圧を供給する。アナログ回路が、第1の基準電圧を受け取る。デジタル回路が、第2の基準電圧を受け取る。

**【0009】**

[0009]また、集積回路が、上記のパイプライン型アナログ・デジタル変換器を備え、第1の基準電圧を供給する第1の電圧源を更に備える。第2の電圧源が、第2の基準電圧を供給する。アナログ回路が、第1の基準電圧を受け取る。デジタル回路が、第2の基準電圧を受け取る。

**【0010】**

[0010]他の特徴では、第1のADCステージは、入力電圧と第1の残差電圧のうちの一方をサンプルしホールドするサンプルホールドモジュールを更に備える。アナログ・デジタル変換器は、サンプルホールドモジュールの出力をデジタル信号に変換する。デジタル・アナログ変換器が、デジタル信号をアナログ信号に変換する。第1のADCステージは、サンプルホールドモジュールの出力とアナログ信号との間の差を生成する差分モジュールを更に備える。増幅モジュールが、この差を増幅する。

**【0011】**

[0011]また、集積回路が、上記のパイプライン型アナログ・デジタル変換器を備え、第1の基準電圧を発生するアナログ電圧源を更に備える。第1の基準電圧は、アナログ基準電圧である。デジタル電圧源が、第2の基準電圧を発生する。第2の基準電圧は、デジタル基準電圧である。

**【0012】**

[0012]また、システムが、上記のパイプライン型アナログ・デジタル変換器を備え、第1の基準電圧を発生するアナログ電圧源を更に備える。第1の基準電圧は、アナログ基準電圧である。デジタル電圧源が、第2の基準電圧を発生する。第2の基準電圧は、デジタル基準電圧である。

**【0013】**

[0013]本開示内容の更なる適用分野が、後述する詳細な説明から明白になる。詳細な説明と特定の実施例は、開示内容の好ましい実施形態を示しているが、例示の目的だけを意図するものであり、開示内容の範囲を制限することを意図しないものであることを、理解すべきである。

**【0014】**

[0014]本開示内容は、詳細な説明と添付図面から更に十分に理解されるようになる。

**【詳細な説明】**

**【0015】**

[0027]以下の説明は本質的に単なる例示であり、開示内容、その適用、又は、使用を制限することを全く意図していない。明瞭にするために、同じ参照番号を類似の要素を特定するために図面中で使用する。本明細書で使用するように、モジュール、回路、及び／又は、デバイスという用語は、特定用途向け集積回路（ASIC）、電子回路、一つ以上のソフトウェア又はファームウェアプログラムを実行するプロセッサ（共有、専用又はグループ）及びメモリ、組み合わせ論理回路、並びに／若しくは、上記の機能を提供するその

10

20

30

40

50

他の適当なコンポーネントを指す。本明細書で使用するように、AとBとCのうちの少なくとも一つという句は、非排他的論理和を使用する論理的な(A又はB又はC)を意味することを理解すべきである。また、方法中のステップは、本開示内容の原理を変更することなく、異なる順序で実行してもよいことを理解すべきである。

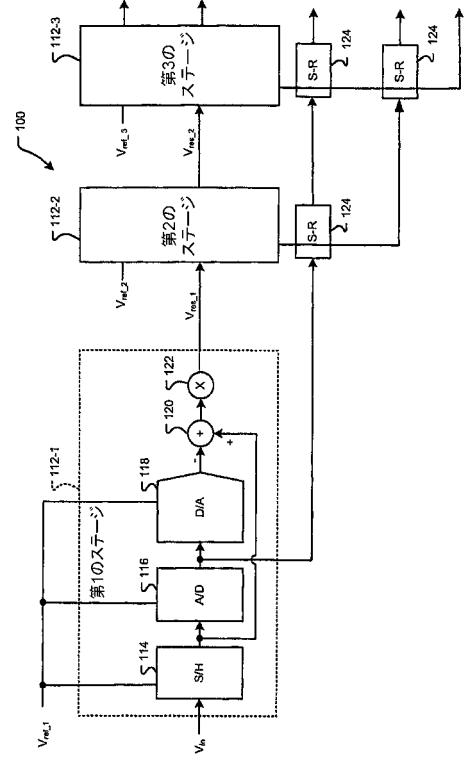

#### 【0016】

[0028]次に図2を参照する。この図は、本発明によるパイプライン型ADC100を、複数の基準電圧 $V_{ref-i}$ を含めて示している。ここで、iは、パイプライン型ADC100の現在のステージに対応している。パイプライン型ADC100は、ステージ112-1、112-2及び112-3(総称してステージ112)と、サンプルホールド回路114と、ADCモジュール116と、デジタル・アナログ変換器(DAC)118と、差分モジュール120と、増幅モジュール122と、を備えている。3段のステージを示しているが、使用するステージは増減してもよい。図2において、 $V_{ref-1} > V_{ref-2}$ かつ $V_{ref-1} > V_{ref-3}$ である。パイプライン型ADC100の後続のステージによるビットの量子化は、現在のステージと同じ信号対雑音レベル(SNR)を必要とせず、従って、より低い基準電圧が第2のステージと第3のステージのうちの少なくとも一方のために使用される。

10

#### 【0017】

[0029]パイプライン型ADC100のステージ112-1、112-2及び112-3によって消費される電力は各ステージの基準電圧に関連している。その結果、パイプライン型ADC100は、図1に示したものと同じ基準電圧が供給されるステージを有するパイプライン型ADCより少ない電力を消費する傾向がある。

20

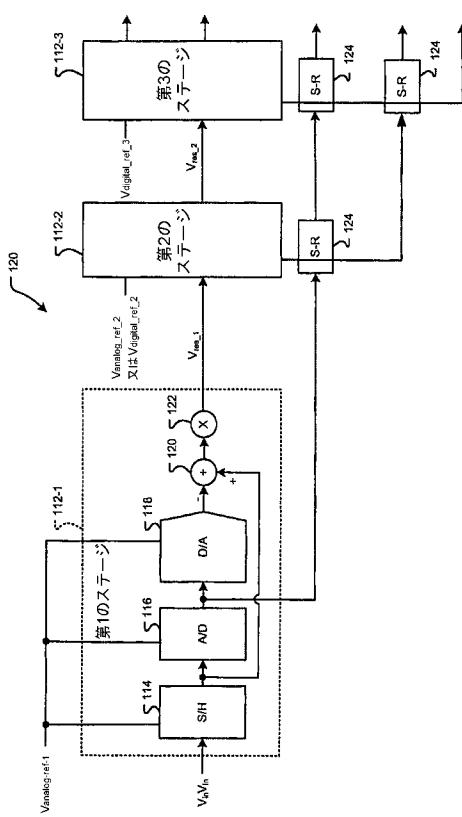

#### 【0018】

[0030]次に図3を参照する。この図は、パイプライン型ADC120を、異なる基準電圧 $V_{ref-i}$ を含めて示している。ここで、iは、パイプライン型ADC120の現在のステージに対応する。基準電圧 $V_{ref-1}$ のうちの少なくとも一つは、ADC120を収容するシステム内のアナログ回路用のアナログ電源電圧 $V_{analog-ref}$ から得られ、基準電圧のうちの少なくとも一つは、ADC120を収容するシステム内のデジタル回路用のデジタル電源電圧 $V_{digital-ref}$ から得られる。

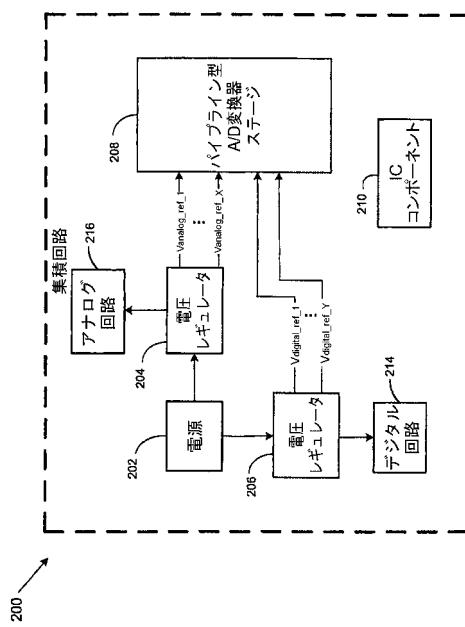

#### 【0019】

[0031]次に図4を参照する。この図は、集積回路(IC)200を示している。一以上の電源202が、未調整の電圧を電圧レギュレータ204及び206に供給する。第1の電圧レギュレータ204は、アナログ電源電圧 $V_{analog-ref-1}$ 、 $V_{analog-ref-2}$ 、 $\dots$ 、及び $V_{analog-ref-X}$ を供給する。ここで、Xは、零より大きい整数である。第2の電圧レギュレータ206は、デジタル電源電圧 $V_{digital-ref-1}$ 、 $V_{digital-ref-2}$ 、 $\dots$ 、及び $V_{digital-ref-Y}$ を供給する。ここで、Yは、零より大きい整数である。IC200は、付加的な回路機能を実行するためICコンポーネント210を含んでいてもよい。第1の電圧レギュレータ204はまた、IC200内の一以上のアナログ回路216に給電する。第2の電圧レギュレータ206はまた、一以上のデジタル回路214に給電する。

30

#### 【0020】

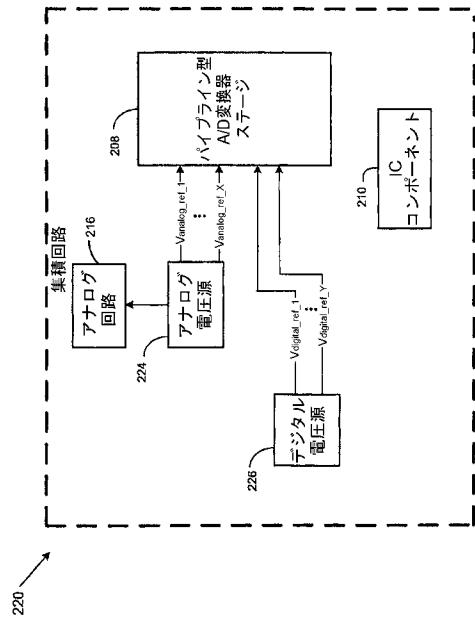

[0032]次に図5を参照する。この図は、集積回路220を示している。アナログ電圧源224は、アナログ電源電圧 $V_{analog-ref-1}$ 、 $V_{analog-ref-2}$ 、 $\dots$ 、及び $V_{analog-ref-X}$ を発生する。ここで、Xは、零より大きい整数である。デジタル電圧源226は、デジタル電源電圧 $V_{digital-ref-1}$ 、 $V_{digital-ref-2}$ 、 $\dots$ 、及び $V_{digital-ref-Y}$ を供給する。ここで、Yは、零より大きい整数である。IC220はまた、付加的な回路機能を実行するためICコンポーネント210を含んでいてもよい。アナログ電圧源224はまた、IC200内の一以上のアナログ回路216に給電する。デジタル電圧源226はまた、一以上のデジタル回路214に給電する。

40

#### 【0021】

10

20

30

40

50

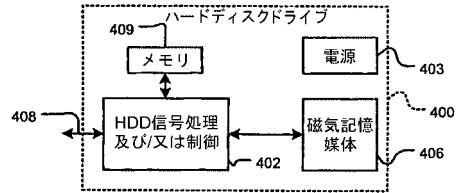

[0033] 次に図 6 A ~ 6 G を参照する。これらの図は、本デバイスの種々の例示的な実装形態を示している。まず、図 6 A を参照する。本デバイスを、ハードディスクドライブ 400 内の一以上の ADC において実装することが可能である。本デバイスは、図 6 A では全体的に参照符号 402 で特定されている信号処理回路及び / 又は制御回路の何れか又は両者、並びに / 若しくは、電源 403 において実施してもよいし、及び / 又は、実施されてもよい。幾つかの実装形態では、HDD 400 内の信号処理回路及び / 又は制御回路 402、並びに / 若しくは、その他の回路（図示せず）は、データを処理し、符号化及び / 又は暗号化を実行し、計算を実行し、並びに / 若しくは、磁気記憶媒体 406 へ出力され、及び / 又は、磁気記憶媒体 406 から受け取られるデータをフォーマット化してもよい。

## 【0022】

10

[0034] HDD 400 は、コンピュータ、携帯情報端末、携帯電話機、メディア又は MP3 プレーヤー等のような携帯計算デバイス、及び / 又は、他のデバイスといったホスト装置（図示せず）と、一以上の有線又は無線通信リンク 408 を介して通信する。HDD 400 は、ランダムアクセスメモリ（RAM）、フラッシュメモリのような低レイテンシー不揮発性メモリ、リードオンリーメモリ（ROM）、及び / 又は、その他の適当な電子データ記憶装置といったメモリ 409 に接続されていてもよい。

## 【0023】

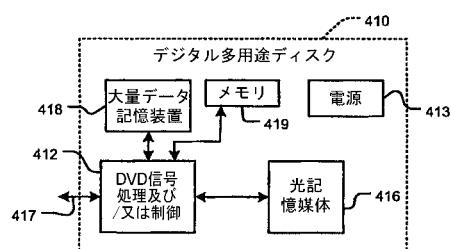

[0035] 次に図 6 B を参照する。本デバイスを、デジタル多用途ディスク（DVD）ドライブ 410 内の 1 台以上の ADC において実装することが可能である。本デバイスは、図 6 B では全体的に参照符号 412 で特定されている信号処理回路及び / 又は制御回路の何れか又は両方、DVD ドライブ 410 の大量データ記憶装置、並びに / 若しくは、電源 413 において実装してもよいし、及び / 又は、実装されてもよい。DVD 410 内の信号処理及び / 又は制御回路 412、並びに / 若しくは、その他の回路（図示せず）は、データを処理し、符号化及び / 又は暗号化を実行し、計算を実行し、並びに / 若しくは、光記憶媒体 416 から読み出されるか、及び / 又は、光記憶媒体 416 に書き込まれるデータをフォーマット化してもよい。幾つかの実装形態では、DVD 410 内の信号処理及び / 又は制御回路 412、並びに / 若しくは、他の回路（図示せず）が、符号化及び / 又は復号、並びに / 若しくは、DVD ドライブと関連する他の信号処理機能のような別の機能を実行することも可能である。

20

## 【0024】

30

[0036] DVD ドライブ 410 は、一以上の有線又は無線通信リンク 417 を介して、コンピュータ、テレビ装置、又は、その他の装置のような出力装置（図示せず）と通信してもよい。DVD 410 は、不揮発方式でデータを格納する大量データ記憶装置 418 に接続していてもよい。大量データ記憶装置 418 は、ハードディスクドライブ（HDD）を含んでいてもよい。HDD は、図 6 A に示す構造を有していてもよい。HDD は、約 1.8 インチより小さい直径を有する一以上のプラッタを含むミニ HDD であってもよい。DVD 410 は、例えば、RAM、ROM、フラッシュメモリのような低レイテンシー不揮発性メモリ、及び / 又は、その他の適当な電子データ記憶装置といったメモリ 419 に接続されていてもよい。

## 【0025】

40

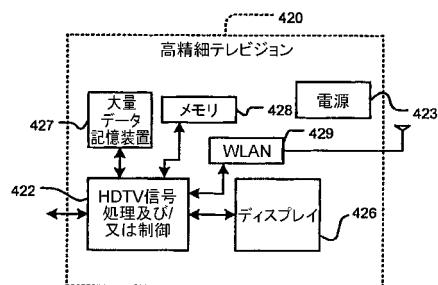

[0037] 次に図 6 C を参照する。本デバイスを、高精細テレビ装置（HDTV）420 内の一以上の ADC において実装してもよい。本デバイスは、図 6 E では全体的に参照符号 422 で特定されている信号処理回路及び / 又は制御回路の何れか又は両方、WLAN インターフェイス、HDTV 420 の大容量データ記憶装置、並びに / 若しくは、電源 423 において実装してもよいし、及び / 又は、実装されてもよい。HDTV 420 は、有線又は無線フォーマットのいずれかで HDTV 入力信号を受信し、ディスプレイ 426 用の HDTV 出力信号を発生する。幾つかの実装形態では、HDTV 420 の信号処理回路及び / 又は制御回路 422、及び / 又は、他の回路（図示せず）が、データを処理し、符号化及び / 又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに / 若しくは、必要に応じて他のタイプの HDTV 处理を実行する。

50

## 【0026】

[0038] HDTV 420 は、光及び／又は磁気記憶装置のような不揮発方式でデータを格納する大量データ記憶装置427に接続してもよい。少なくとも一つのHDDは、図6Aに示した構造を有していてもよく、及び／又は、少なくとも一つのDVDは、図6Bに示した構造を有していてもよい。HDDは、約1.8インチより小さい直径を有する一以上のプラッタを含むミニHDDであってもよい。HTV420は、RAM、ROM、フラッシュメモリのような低レイテンシー不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置といったメモリ428に接続されてもよい。HTV420はまた、WLANネットワークインターフェイス429を介してWLANとの接続をサポートしてもよい。

10

## 【0027】

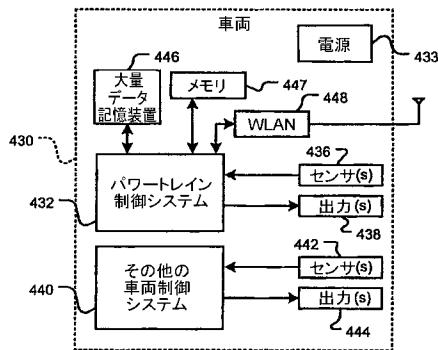

[0039] 次に図6Dを参照する。本デバイスを、車両430の制御システム、WLANインターフェイス、車両制御システムの大容量データ記憶装置、及び／又は、電源433における一以上のADCにおいて、実施してもよい、及び／又は、実施されてもよい。幾つかの実装形態では、本デバイスは、パワートレイン制御システム432を実現する。パワートレイン制御システム432は、温度センサ、圧力センサ、回転センサ、流量センサ、及び／又は、その他の適当なセンサといった一以上のセンサからの入力を受け、並びに／若しくは、エンジン動作パラメータ、トランスマッショントラクション動作パラメータ、及び／又は、他の制御信号といった一以上の出力制御信号を発生する。

20

## 【0028】

[0040] 本デバイスは、車両430の他の制御システムにおいて実施されることもある。制御システム440は、同様に、入力センサ442から信号を受信し、及び／又は、一以上の出力デバイス444へ制御信号を出力する。幾つかの実装形態では、制御システム440が、アンチロックブレーキシステム(ABS)、ナビゲーションシステム、テレマティックスシステム、車線離脱システム、適応走行制御システム、又は、ステレオ、DVD、コンパクトディスクのような車両娛樂システムなどの一部であってもよい。

30

## 【0029】

[0041] パワートレイン制御システム432は、不揮発方式でデータを格納する大量データ記憶装置446に接続してもよい。大容量データ記憶装置446は、光記憶装置及び／又は磁気記憶装置、例えば、ハードディスクドライブHDD及び／又はDVDを含んでいてもよい。少なくとも一つのHDDは、図6Aに示した構造を有していてもよく、及び／又は、少なくとも一つのDVDは、図6Bに示した構造を有していてもよい。HDDは、約1.8インチより小さい直径を有する1個以上のプラッタを含むミニHDDであってもよい。パワートレイン制御システム432は、RAM、ROM、フラッシュメモリのような低レイテンシー不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置といったメモリ447に接続されてもよい。パワートレイン制御システム432はまた、WLANネットワークインターフェイス448を介してWLANとの接続をサポートしてもよい。制御システム440も同様に、大容量データ記憶装置、メモリ、及び／又は、WLANインターフェイス(図示せず)を含んでいてもよい。

30

## 【0030】

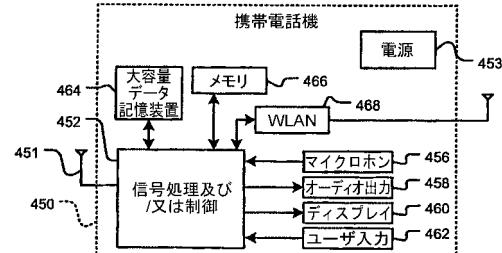

[0042] 次に図6Eを参照する。本デバイスを、セルラーアンテナ451を含み得る携帯電話機450内の一以上のADCにおいて実装してもよい。本デバイスは、図6Eでは全体的に参照符号452で特定されている信号処理回路及び／又は制御回路の何れか又は両方、WLANインターフェイス、携帯電話機450の大容量データ記憶装置、並びに／若しくは、電源453において実装してもよいし、そして／又は、実装されてもよい。幾つかの実装形態では、携帯電話機450は、マイクロホン456、スピーカー及び／又はオーディオ出力ジャックのようなオーディオ出力458、ディスプレイ460、並びに／若しくは、キーパッド、ポインティングデバイス、音声作動装置、及び／又は、その他の入力装置のような入力デバイス462を備えている。携帯電話機450内の信号処理及び／又は制御回路452、並びに／若しくは、その他の回路(図示せず)は、データを処理し

40

50

、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに／若しくは、その他の携帯電話機機能を実行してもよい。

### 【0031】

[0043]携帯電話機450は、例えば、ハードディスクドライブHDD及び／又はDVDといった光及び／又は磁気記憶装置のように不揮発方式でデータを格納する大量データ記憶装置464に接続していてもよい。少なくとも一つのHDDは、図6Aに示した構造を有していてもよく、及び／又は、少なくとも一つのDVDは図6Bに示した構造を有していてもよい。HDDは、約1.8インチより小さい直径を有する一以上のプラッタを含むミニHDDであってもよい。携帯電話機450は、RAM、ROM、フラッシュメモリのような低レイテンシー不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置といったメモリ466に接続されていてもよい。携帯電話機450はまた、WLANネットワークインターフェイス468を介してWLANとの接続をサポートしてもよい。10

### 【0032】

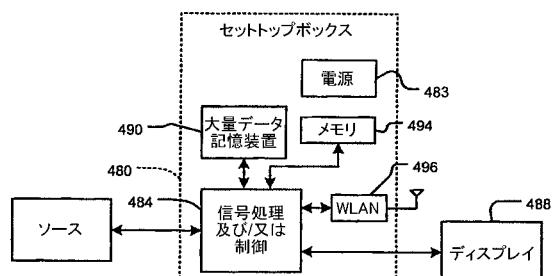

[0044]次に図6Fを参照する。本デバイスを、セットトップボックス480内の一以上のADCにおいて実装してもよい。本デバイスは、図6Fでは全体的に参照符号484で特定されている信号処理回路及び／又は制御回路の何れか又は両方、WLANインターフェイス、セットトップボックス480の大容量データ記憶装置、並びに／若しくは、電源483において実装してもよいし、そして／又は、実装されてもよい。セットトップボックス480は、ブロードバンドソースのようなソースから信号を受信し、テレビ装置、モニター、並びに／若しくは、その他のビデオ及び／又はオーディオ出力装置といったディスプレイ488に適した標準及び／又は高精細のオーディオ／ビデオ信号を出力する。セットトップボックス480の信号処理及び／又は制御回路484、並びに／若しくは、その他の回路（図示せず）は、データを処理し、符号化及び／又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに／若しくは、その他のセットトップボックス機能を実行してもよい。20

### 【0033】

[0045]セットトップボックス480は、不揮発方式でデータを格納する大量データ記憶装置490に接続していてもよい。大量データ記憶装置490は、光及び／又は磁気記憶装置、例えば、ハードディスクドライブHDD及び／又はDVDを含んでいてもよい。少なくとも一つのHDDは図6Aに示した構造を有していてもよく、及び／又は、少なくとも一つのDVDは図6Bに示した構造を有していてもよい。HDDは、約1.8インチより小さい直径を有する一以上のプラッタを含むミニHDDでもよい。セットトップボックス480は、RAM、ROM、フラッシュメモリのような低レイテンシー不揮発性メモリ、及び／又は、その他の適当な電子データ記憶装置といったメモリ494に接続されていてもよい。セットトップボックス480はまた、WLANネットワークインターフェイス496を介してWLANとの接続をサポートしてもよい。30

### 【0034】

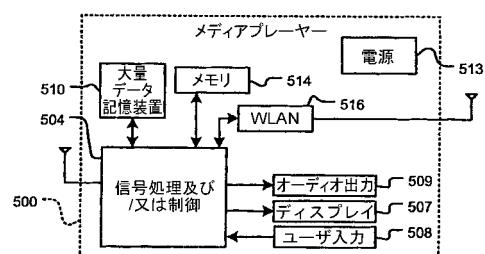

[0046]次に図6Gを参照する。本デバイスを、メディアプレーヤー500内の一以上のADCにおいて実装することが可能である。本デバイスは、図6Gでは全体的に参照符号504で特定されている信号処理回路及び／又は制御回路の何れか又は両方、WLANインターフェイス、メディアプレーヤー500の大容量データ記憶装置、並びに／若しくは、電源503において実施してもよいし、そして／又は、実施されてもよい。幾つかの実装形態では、メディアプレーヤー500は、ディスプレイ507、及び／又は、キーパッド、タッチパッドなどのようなユーザ入力508を備えている。幾つかの実装の形態では、メディアプレーヤー500は、グラフィカルユーザインターフェイス(GUI)を採用する。GUIは、通常、ディスプレイ507及び／又はユーザ入力508を介するメニュー、ドロップダウンメニュー、アイコン、及び／又は、ポイントアンドクリックインターフェイスを採用する。メディアプレーヤー500は、スピーカージャック及び／又はオーディオ出力ジャックのようなオーディオ出力509を更に備えている。メディアプレーヤー500の信号処理及び／又は制御回路504、並びに／若しくは、その他の回路（図示4050

せず)が、データを処理し、符号化及び/又は暗号化を実行し、計算を実行し、データをフォーマット化し、並びに/若しくは、その他のメディアプレーヤー機能を実行してもよい。

### 【0035】

[0047] メディアプレーヤー 500 は、不揮発方式で圧縮オーディオ及び/又はビデオコンテンツといったデータを格納する大量データ記憶装置 510 に接続してもよい。幾つかの実装形態では、圧縮オーディオファイルは、MP3 フォーマット、若しくは、その他の適当な圧縮オーディオ及び/又はビデオフォーマットに準拠したファイルを含む。大量データ記憶装置は、光及び/又は磁気記憶装置、例えば、ハードディスクドライブ HDD 及び/又は DVD を含んでいてもよい。少なくとも一つの HDD は図 6A に示した構造を有していてもよく、及び/又は、少なくとも一つの DVD は図 6B に示した構造を有していてもよい。HDD は、約 1.8 インチより小さい直径を有する一以上のプラッタを含むミニ HDD であってもよい。メディアプレーヤー 500 は、RAM、ROM、フラッシュメモリのような低レイテンシー不揮発性メモリ、及び/又は、その他の適当な電子データ記憶装置といったメモリ 514 に接続されていてもよい。メディアプレーヤー 500 はまた、WLAN ネットワークインターフェイス 516 を介して WLAN との接続をサポートしてもよい。更なる実装形態が、上述したものに加えて、想定される。

10

### 【0036】

[0048] 当業者は、上記の説明から本開示内容の幅広い教示を種々の形式で実施可能であることを理解することができる。したがって、本開示内容は特定の実施例を含むが、図面、明細書及び特許請求の範囲を検討すれば、その他の変形が当業者には明白であるので、本開示内容の真の範囲は特定の実施例のように限定されるべきではない。

20

### 【図面の簡単な説明】

### 【0037】

【図 1】従来技術によるパイプライン型アナログ・デジタル変換器(ADC)の機能ブロック図である。

30

【図 2】本発明による例示的なパイプライン型 ADC の機能ブロック図である。

【図 3】本発明による別の例示的なパイプライン型 ADC の機能ブロック図である。

【図 4】本発明によるパイプライン型 ADC を含む集積回路の機能ブロック図である。

【図 5】アナログ電圧源とデジタル電圧源と本発明によるパイプライン型 ADC とを含む集積回路の機能ブロック図である。

30

【図 6 A】ハードディスクドライブの機能ブロック図である。

【図 6 B】デジタル多用途ディスク(DVD)の機能ブロック図である。

【図 6 C】高精細テレビ装置の機能ブロック図である。

【図 6 D】車両制御システムの機能ブロック図である。

【図 6 E】携帯電話機の機能ブロック図である。

【図 6 F】セットトップボックスの機能ブロック図である。

【図 6 G】メディアプレーヤーの機能ブロック図である。

### 【符号の説明】

### 【0038】

40

100...パイプライン型アナログ・デジタル変換器、112...ステージ、112-1...第1のA/D変換器ステージ、112-2...第2のA/D変換器ステージ、112-3...第3のA/D変換器ステージ、114...サンプルホールドモジュール、116...ADCモジュール、118...デジタル・アナログ変換器、120...差分モジュール、122...増幅モジュール。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6 A】

【図6 B】

【図6 C】

【図 6 D】

【図 6 E】

【図 6 F】

【図 6 G】

---

フロントページの続き

審査官 柳下 勝幸

(56)参考文献 特開2004-312702(JP,A)

特開2002-314420(JP,A)

特開平05-252034(JP,A)

特開2003-008439(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M1/00-1/88