(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6306743号

(P6306743)

(45) 発行日 平成30年4月4日(2018.4.4)

(24) 登録日 平成30年3月16日(2018.3.16)

(51) Int.Cl.

F 1

|             |              |                  |      |       |   |

|-------------|--------------|------------------|------|-------|---|

| <b>H05K</b> | <b>3/46</b>  | <b>(2006.01)</b> | H05K | 3/46  | B |

| <b>H01L</b> | <b>23/14</b> | <b>(2006.01)</b> | H01L | 23/14 | R |

| <b>H05K</b> | <b>1/02</b>  | <b>(2006.01)</b> | H05K | 1/02  | J |

|             |              |                  | H05K | 3/46  | Q |

|             |              |                  | H05K | 3/46  | N |

請求項の数 21 (全 13 頁)

(21) 出願番号 特願2016-567193 (P2016-567193)

(86) (22) 出願日 平成27年4月27日 (2015.4.27)

(65) 公表番号 特表2017-516308 (P2017-516308A)

(43) 公表日 平成29年6月15日 (2017.6.15)

(86) 國際出願番号 PCT/US2015/027806

(87) 國際公開番号 WO2015/175197

(87) 國際公開日 平成27年11月19日 (2015.11.19)

審査請求日 平成29年8月7日 (2017.8.7)

(31) 優先権主張番号 14/276,763

(32) 優先日 平成26年5月13日 (2014.5.13)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 507364838

クアルコム、インコーポレイテッド

アメリカ合衆国 カリフォルニア 921

21 サンディエゴ モアハウス ドラ

イブ 5775

(74) 代理人 100108453

弁理士 村山 靖彦

(74) 代理人 100163522

弁理士 黒田 晋平

(72) 発明者 ホウサム・ワフィク・ジョマ

アメリカ合衆国・カリフォルニア・921

21-1714・サン・ディエゴ・モアハ

ウス・ドライブ・5775

最終頁に続く

(54) 【発明の名称】基板および基板を形成する方法

## (57) 【特許請求の範囲】

## 【請求項 1】

コア材料の銅層上に光活性誘電体層を直接積層するステップと、

前記光活性誘電体層に複数のトレースパターンを形成するステップと、

前記光活性誘電体層に埋め込まれた複数のトレースを形成するために前記複数のトレースパターンをめっきするステップと、

前記複数のトレースパターンをめっきした後、前記光活性誘電体層上に絶縁性誘電体層を形成するステップであって、前記絶縁性誘電体層は前記複数のトレースを被覆し、および前記絶縁性誘電体層は非光活性誘電体材料からなる、ステップと、

前記絶縁性誘電体層および前記光活性誘電体層を通るビアを形成するステップと、

前記絶縁性誘電体層上に追加のルーティングパターンを形成するステップと、

前記コア材料を除去するステップと、

はんだマスクを施すステップと

を含む基板を製造する方法。

## 【請求項 2】

前記複数のトレースの各々が、5 μmの幅および前記複数のトレースの各々の間に5 μmの間隙を有する、請求項1に記載の方法。

## 【請求項 3】

前記複数のトレースの各々が、2 μmの幅および前記複数のトレースの各々の間に2 μmの間隙を有する、請求項1に記載の方法。

10

20

**【請求項 4】**

前記ビアがスキップビアである、請求項 1 に記載の方法。

**【請求項 5】**

前記ビアがパッドレススキップビアである、請求項 1 に記載の方法。

**【請求項 6】**

前記光活性誘電体層が 10 μm 未満である、請求項 1 に記載の方法。

**【請求項 7】**

前記光活性誘電体層が約 5 μm である、請求項 1 に記載の方法。

**【請求項 8】**

前記絶縁性誘電体層が約 15 μm である、請求項 1 に記載の方法。 10

**【請求項 9】**

前記ビアが底部分より小さい上部分を有している、請求項 1 に記載の方法。

**【請求項 10】**

永続的光活性誘電体層および前記永続的光活性誘電体層上の絶縁性誘電体層を含むコアレス基板と、

前記永続的光活性誘電体層に埋め込まれた複数のトレースであって、前記絶縁性誘電体層は、前記複数のトレースを被覆し、および前記絶縁性誘電体層は前記光活性誘電体層と異なる材料からなる、複数のトレースと、

前記絶縁性誘電体層および前記永続的光画像形成可能誘電体層を通って延在する第 1 のビアと、 20

前記絶縁性誘電体層および前記永続的光画像形成可能誘電体層を通って延在する、前記第 1 のビアに最も近い第 2 のビアと、

前記絶縁性誘電体層上のはんだレジスト積層体層に埋め込まれ、前記第 1 のビアと前記第 2 のビアとを接続するように構成されたビアトレースとを含む、半導体構造。

**【請求項 11】**

前記複数のトレースの各々が、5 μm の幅および前記複数のトレースの各々の間に 5 μm の間隙を有する、請求項 10 に記載の半導体構造。

**【請求項 12】**

前記複数のトレースの各々が、2 μm の幅および前記複数のトレースの各々の間に 2 μm の間隙を有する、請求項 10 に記載の半導体構造。 30

**【請求項 13】**

前記ビアがスキップビアである、請求項 10 に記載の半導体構造。

**【請求項 14】**

前記ビアがパッドレススキップビアである、請求項 10 に記載の半導体構造。

**【請求項 15】**

前記光活性誘電体層が 10 μm 未満である、請求項 10 に記載の半導体構造。

**【請求項 16】**

前記光活性誘電体層が約 5 μm である、請求項 10 に記載の半導体構造。 40

**【請求項 17】**

前記絶縁性誘電体層が約 15 μm である、請求項 10 に記載の半導体構造。

**【請求項 18】**

前記絶縁性誘電体層が、非光活性誘電体層である、請求項 10 に記載の半導体構造。

**【請求項 19】**

永続的光活性誘電体層および絶縁性誘電体層を含むコアレス基板と、

前記永続的光活性誘電体層に埋め込まれた複数のトレースであって、前記絶縁性誘電体層は前記複数のトレースを被覆し、および前記絶縁性誘電体層は前記光活性誘電体層と異なる材料からなる、複数のトレースと、

前記絶縁性誘電体層および前記永続的光画像形成可能誘電体層を通って延在する、導通させるための第 1 の手段と、 50

前記絶縁性誘電体層および前記永続的光画像形成可能誘電体層を通って延在する、前記導通させるための第1の手段に最も近い、導通させるための第2の手段と、

前記絶縁性誘電体層上のはんだレジスト積層体層に埋め込まれ、前記導通させるための第1の手段と前記導通させるための第2の手段とを接続するように構成されたビアトレースと

を含む、半導体構造。

【請求項 20】

前記複数のトレースの各々が、 $5 \mu m$ の幅および前記複数のトレースの各々の間に $5 \mu m$ の間隙を有する、請求項1-9に記載の半導体構造。

【請求項 21】

前記複数のトレースの各々が、 $2 \mu m$ の幅および前記複数のトレースの各々の間に $2 \mu m$ の間隙を有する、請求項19に記載の半導体構造。

## 【発明の詳細な説明】

### 【技術分野】

[ 0 0 0 1 ]

本開示は、一般に、半導体に関し、より詳細には、限定はしないが、半導体パッケージ基板の形成のための方法に関する。

【背景技術】

[ 0 0 0 2 ]

従来、半導体パッケージは、1つの選択肢として、細かいルーティングを可能にし、シリコンとマザーボードとの間の空間転換部として機能するように、中央のガラス強化のコア材料上への層ごとの積層を通して形成される。しかしながら、この手法は、特に、ダイが分割され、両ダイ間の極めて細かいルーティングが必要とされる場合には、十分なルーティング密度を与えられない場合がある。あるいは、半導体パッケージは、第1の層が埋め込まれるコアレスプロセスを通して形成することができ、このことは、シード層の除去の必要性を取り除くので、より細かいルーティングを提供する（補償の向上）。有機基板を介して形成されたこれら2つの手法は、一般に、シード層スパッタリング、薄い液体レジストを使用し、薄い銅ルーティング層を形成する「ファブ様（f a b - l i k e）」プロセスを利用する、シリコンインターポーザおよび有機インターポーザと競合しようとしている。これは極めて細かいルーティングを与えるが、コストおよびCu厚さ、その結果の電気抵抗率が主な欠点である。したがって、本明細書で提供する改善された方法および装置を含む、従来の方法を改善する方法に対する長年にわたる産業界のニーズが存在する。

( 0 0 0 3 )

本教示を特徴付ける発明性がある特徴は、さらなる目的および利点とともに、詳細な説明および添付の図からより十分に理解される。図面の各々は例示および説明のみのために与えられ、本教示を限定しない。

## 【発明の概要】

#### 【課題を解決するための手段】

[ 0 0 0 4 ]

以下は、本明細書で開示する装置および方法に関する 1 つまたは複数の態様および / または実施形態に関する簡略化された概要を提示する。したがって、以下の概要是、すべての考えられる態様および / または実施形態に関する包括的な概説と見なすべきでなく、また、すべての考えられる態様および / もしくは実施形態に関する最もしくは決定的な要素を識別するか、または任意の特定の態様および / もしくは実施形態に関する範囲を定めるものと見なすべきでない。したがって、以下の概要是、以下に提示される詳細な説明に先立って、本明細書で開示する装置および方法に関する 1 つまたは複数の態様および / または実施形態に関する特定の概念を簡略化された形で提示することが唯一の目的である。

[ 0 0 0 5 ]

本開示のいくつかの例示的な実施形態は、第1の誘電体層に埋め込まれた極めて細かいトレースを含む第1および第2の誘電体層と、第1および第2の両誘電体層間に延在するランディング／キャップチャパッドレスビアとを有するコアレス基板構造を形成するためのシステム、装置、および方法を対象とする。

#### 【0006】

本開示のいくつかの実施形態では、本システム、装置、および方法は、コアを形成するステップと、光活性（光画像形成可能（photolabile））誘電体層によってコアの上部に積層するステップと、光活性誘電体層内に複数のトレースパターンを形成するステップと、複数のトレースを形成するために複数のトレースパターンをめっきするステップと、光活性誘電体層上に絶縁性誘電体層を形成するステップと、絶縁性誘電体層および光活性誘電体層を通るビアを形成するステップと、絶縁性誘電体層上に追加のルーティングパターンを形成するステップと、コアを除去するステップと、はんだマスクを追加するステップとを含む。10

#### 【0007】

本開示のいくつかの実施形態では、本システム、装置、および方法は、永続的光活性誘電体層および絶縁性誘電体層を有するコアレス基板と、永続的光活性誘電体層に埋め込まれた複数のトレースと、絶縁性誘電体層および永続的光画像形成可能誘電体層を通って延在する、導通させるための手段とを含む、半導体構造を含む。

#### 【0008】

本明細書で開示する装置および方法に関連する他の目的および利点は、添付の図面および詳細な説明に基づいて、当業者には明らかになるであろう。20

#### 【0009】

添付の図面は、本教示の例を説明するために提示され、限定するためのものではない。添付の図面は、本開示の実施形態の説明を助けるために提示され、実施形態の限定ではなく、実施形態の例示のためにのみ提供される。

#### 【0010】

本開示の態様およびその付隨する利点の多くは、以下の詳細な説明を参照することによって、本開示を限定するためではなく単に例示するために提示される添付の図面とともに検討されると、より良く理解されるようになるので、本開示の態様およびその付隨する利点の多くに関するより完全な諒解が容易に得られるであろう。30

#### 【図面の簡単な説明】

#### 【0011】

【図1A】本開示の一実施形態による例示的な基板のトップダウン図である。

【図1B】図1Aの例示的な基板の図示された切断線に沿った側面図である。

【図1C】図1Aの例示的な基板の図示された切断線に沿った側面図である。

【図2A】テンポラリコアの積層およびめっきを示す本開示の一実施形態による例示的な方法および装置を示す図である。

【図2B】スキップビア形成およびセミアディティブめっきプロセスを示す本開示の一実施形態による例示的な方法および装置を示す図である。

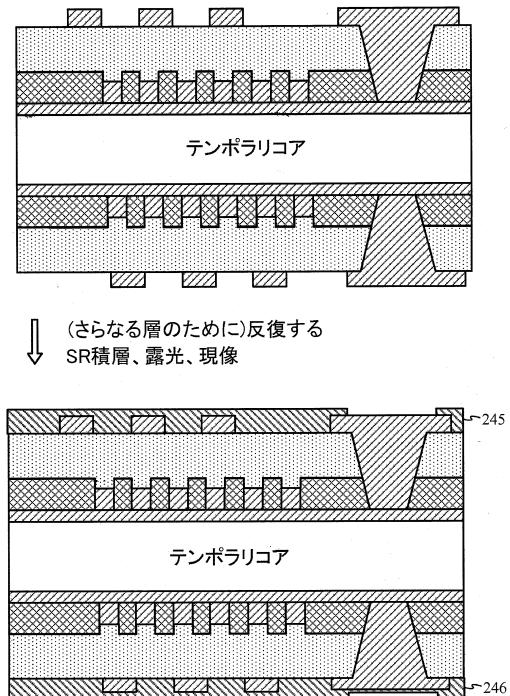

【図3A】S R 積層、露光、および現像を示す本開示の一実施形態による例示的な方法および装置を示す図である。40

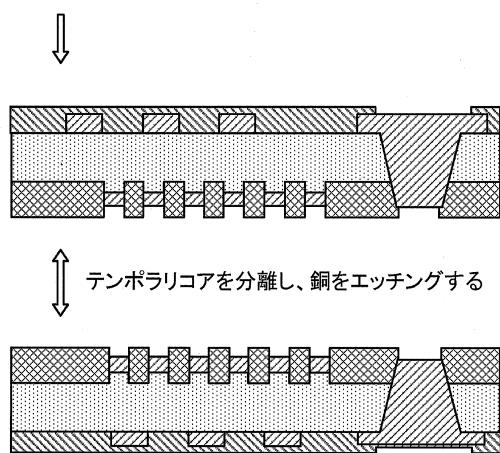

【図3B】テンポラリコアの分離および銅エッチングを示す本開示の一実施形態による例示的な方法および装置を示す図である。

#### 【発明を実施するための形態】

#### 【0012】

慣例に従って、図面に示される特徴は、一定の縮尺で描かれていない可能性がある。したがって、示された特徴の寸法は、明快にするために、任意に拡大または縮小されている可能性がある。慣例に従って、図面のうちのいくつかは、明快にするために簡略化されている。したがって、図面は、特定の装置または方法のすべての構成要素を示すとは限らない。さらに、同様の参照番号は、本明細書および図を通して同様の特徴を示す。50

## 【0013】

光活性（光画像形成可能）誘電体、パッドレススキップビア、および埋込型トレースを有するコアレス基板の形成のためのシステム、装置、および方法が与えられる。本明細書で開示する例示的な方法は、有利なことに、長年にわたる産業界のニーズおよびこれまでに同定されていない他のニーズに対処し、従来の方法の欠点を軽減する。たとえば、本明細書で開示する実施形態によって与えられる利点は、コスト節約の改善、より容易な製造、より低い高さプロファイル、従来のデバイスよりも小さいプロファイルを有するバンブパッド内のビアである。

## 【0014】

本開示の例示的な実施形態に関する具体例を示すために、次の説明および関連の図面において様々な態様が開示される。代替実施形態は、本開示を読めば当業者に明らかとなり、本開示の範囲または趣旨から逸脱することなく構築され、実践され得る。加えて、本明細書で開示する態様および実施形態の関連する詳細を不明瞭にしないように、よく知られている要素は詳細には説明されず、または省略され得る。

10

## 【0015】

「例示的な」という言葉は、「例、事例、または例示として役立つ」ことを意味するように本明細書において使用される。「例示的」として本明細書で説明するいかなる実施形態も、他の実施形態よりも好ましいまたは有利であると必ずしも解釈されるべきではない。同様に、「実施形態」という用語は、すべての実施形態が論じられる特徴、利点または動作モードを含むことを必要としない。本明細書において「一例では」、「例」、「1つの特徴では」、および／または「特徴」という用語を使用する場合、必ずしも同じ特徴および／または例を指すとは限らない。さらに、特定の特徴および／または構造は、1つもしくは複数の他の特徴および／または構造と組み合わせることができる。その上、本明細書で説明する装置の少なくとも一部分は、本明細書で説明する方法の少なくとも一部分を実行するように構成することができる。

20

## 【0016】

本明細書で使用する用語は、特定の実施形態について説明することのみを目的とするものであり、本発明の実施形態を限定するものではない。本明細書で使用する単数形「a」、「a n」、および「t h e」は、文脈が別段に明確に示すのでなければ、複数形も含むものとする。本明細書で使用する場合、「備える（c o m p r i s e s）」、「備えている（c o m p r i s i n g）」、「含む（i n c l u d e s）」、および／または「含んでいる（i n c l u d i n g）」という用語は、述べられた特徴、整数、ステップ、動作、要素、および／または構成要素の存在を明示するが、1つまたは複数の他の特徴、整数、ステップ、動作、要素、構成要素、および／またはそれらのグループの存在または追加を排除するものではないことがさらに理解されよう。

30

## 【0017】

「接続される」、「結合される」という用語、またはそれらのいかなる変形形態も、要素間の直接的または間接的な任意の接続または結合を意味し、仲介要素を介して互いに「接続」または「結合」される2つの要素間に仲介要素の存在を含むことができることに留意されたい。要素間の結合および／または接続は、物理的、論理的、またはそれらの組合せであってもよい。本明細書で使用する要素は、たとえば、1つまたは複数のワイヤ、ケーブル、および／またはプリントされた電気接続部を使用することによって、ならびに電磁エネルギーを使用することによって互いに「接続」または「結合」することができる。電磁エネルギーは、無線周波数領域、マイクロ波領域、および／または光学的（可視と不可視の両方の）領域の波長を有することができる。これらは、いくつかの非限定的かつ非網羅的な例である。

40

## 【0018】

「信号」という用語は、データ信号、オーディオ信号、ビデオ信号、マルチメディア信号、アナログ信号、および／またはデジタル信号などの任意の信号を含むことができるこ

50

とを理解されたい。多種多様な技術および技法のうちのいずれかを使用して情報および信

号を表すことができる。たとえば、本明細書で説明するデータ、命令、処理ステップ、コマンド、情報、信号、ビット、および／もしくはシンボルは、電圧、電流、電磁波、磁場および／または磁性粒子、光場および／もしくは光学粒子、またはそれらの任意の組合せによって表すことができる。

#### 【0019】

本明細書における「第1の」、「第2の」などの呼称を使用する要素のあらゆる参照は、これらの要素の数量および／または順序を限定するものではない。むしろ、これらの呼称は、2つ以上の要素、および／または要素の例を区別する都合のよい方法として使用されている。したがって、第1および第2の要素への参照は、2つの要素のみを使用することができること、または第1の要素が第2の要素に必ず先行しなければならないことを意味しない。また、別段に記載されていない限り、1組の要素は、1つまたは複数の要素を含むことができる。加えて、明細書または特許請求の範囲に使用される「A、B、またはCのうちの少なくとも1つ」という形態の用語は、「AもしくはBもしくはCまたはこれらの要素の任意の組合せ」と解釈することができる。10

#### 【0020】

本明細書では、特定の特徴について説明するために特定の用語が使用される。「モバイルデバイス」という用語は、限定はしないが、モバイルフォン、モバイル通信デバイス、ペーディヤ、携帯情報端末、個人情報管理装置、モバイルハンドヘルドコンピュータ、ラップトップコンピュータ、ワイヤレスデバイス、ワイヤレスモデム、および／または通常個人によって持ち運ばれ、かつ／もしくは通信機能（たとえば、ワイヤレス、セルラー、赤外線、短距離無線など）を有する他のタイプの携帯型電子デバイスについて説明することができる。さらに、「ユーザ機器」（UE）、「モバイル端末」、「モバイルデバイス」、および「ワイヤレスデバイス」という用語は、互換性のある場合がある。20

#### 【0021】

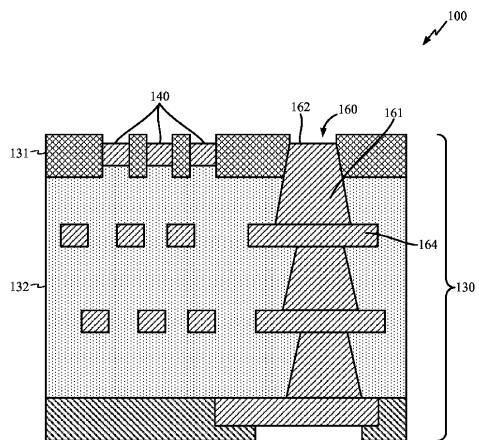

図1Aは、パッドレスビアと埋込型トレースを有する光画像形成可能誘電体層とを有するコアレス基板を含む半導体パッケージの例示的な実施形態を示す。図1に示すように、半導体パッケージ100は、基板130の上部に2つの活性ダイ110および120を含み得る。基板130は、複数の埋込型トレース140、ビアによって接続されたトレース150、ならびにパッドレススキップビア160および170を含み得る。ビアトレース150は、2つの活性ダイ110と120とを接続し得る。パッドレススキップビア160および170を介してビアトレース150を活性ダイ110および120に結合することによって、ビアトレース接続がなされ得る。30

#### 【0022】

図1Bは、図1Aに示す、指示された切断線に沿った、例示的な実施形態の断面図を示す。図1Bに示すように、半導体パッケージ100は、第1の誘電体層131、第2の誘電体層132、パッドレススキップビア160、および第1の誘電体層131に埋め込まれた複数のトレース140を有する基板130を含み得る。図示された実施形態は、複数のビアおよび第2の誘電体層領域を含むが、これはオプションである。第1の誘電体層131は、液体または乾式フィルムとして施され得る光活性材料であり得る。第2の誘電体層132は、シリカベースのエポキシ材料などの、層131とは異なる組成物であり得る。パッドレススキップビア160は、本体161、上部分162、底部分163、およびカバーパッド164を含み得る。上部分162は、ランディングパッドまたはキャプチャパッドなしに形成され得る。底部分163は、カバーパッド164とともに形成され得る。40

#### 【0023】

図1Bに示すように、埋込型トレース140は、信号ルーティングを容易にするために銅などの導電性材料から形成され得る。トレースは、誘電体層131内に極めて細かいパターニングで形成され得る。極めて細かいパターニングは、 $2\text{ }\mu\text{m}$  /  $2\text{ }\mu\text{m}$ などの、 $5\text{ }\mu\text{m}$  /  $5\text{ }\mu\text{m}$ 未満の低いラインアンドスペース寸法を可能にし得る。誘電体層131は、誘電体層132よりも小さい寸法であり得る。たとえば、誘電体層131は約5~50

10  $\mu\text{m}$ の厚さであり得るが、誘電体層132は約15  $\mu\text{m}$ の厚さであり得る。パッドレススキップビア160は、底部分163よりも小さい上部分162を有し得る。たとえば、上部分162は35  $\mu\text{m}$ の直径で底部分163は40  $\mu\text{m}$ の直径である。ビア160に対するキャップチャパッドまたはランディングパッドの欠如は、追加のルーティングまたはトレースのために、より高いルーティング密度の誘電体層131を可能にし得る。

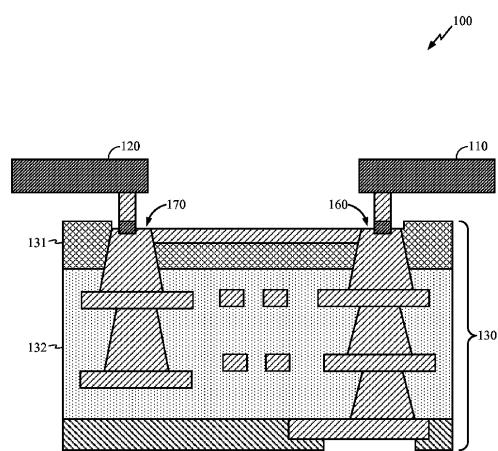

#### 【0024】

図1Cは、図1Aに示す、指示された切断線に沿った、例示的な実施形態の断面図を示す。図1Cに示すように、半導体パッケージ100は、第1のダイ110、第2のダイ120、第1の誘電体層131および第2の誘電体層132を有する基板130、パッドレススキップビア160および170、ならびにビアトレース150を含み得る。ビアトレースまたはルーティング150は、ビア160および170に接続する場合があり、ダイ110と120との間の接続を提供し得る。

10

#### 【0025】

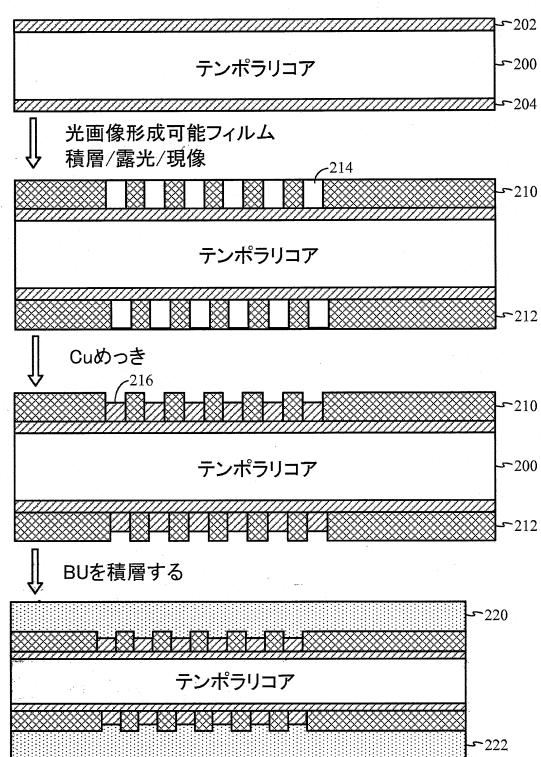

図2Aは、コアレス基板の形成のための方法の例示的な実施形態を示す。図2Aでは、テンポラリコア200は、第1の銅層202および第2の銅層204を有し得る。2つの銅層が示されるが、コア200が1つの層のみを含む場合があり、これらの層が導電性金属などの他の材料から構成される場合があることを理解されたい。

#### 【0026】

次に、第1の誘電体層210が第1の銅層202に施され、第2の誘電体層212が第2の銅層204に施される。第1および第2の誘電体層210および212は、光活性液体または乾式光画像形成可能フィルムであり得る。第1および第2の誘電体層210および212は、約5～10  $\mu\text{m}$ の厚さに積層またはキュアされる場合があり、トレースパターン214を含む場合がある。2つの層210および212が示されるが、1つの層のみが使用され得ることを理解されたい。トレースパターン214は、極めて細かく、2/2  $\mu\text{m}$ などの、5/5  $\mu\text{m}$ 未満のラインスペース寸法を有し得る。層210および212は、UV光などの光に露光され、トレースパターン214内的一部分を除去するように現像され得る。

20

#### 【0027】

トレースパターン214内の材料が除去された後、コア200は、トレースパターン214の空隙内に銅をめっきする銅めっきプロセスを受ける場合がある。図2Aにおいてわかるように、めっきプロセスは、トレースパターン214の空隙の一部分のみに銅をめっきし得る。これにより、得られる銅トレース216は、感光層の厚さよりも小さい寸法を有することが可能になり得る。上述のように、めっき材料は、銅以外とすることができる。感光層210および212は、めっきプロセス後に残る場合があり、コア200からストリッピングされる必要がない場合がある。ストリッピングプロセスを回避することにより、銅トレースは、銅シード層エッチングまたは銅粗面化ステップを考慮してトレース寸法（トレース幅）に関する追加の補償がなされる必要がないので、より容易にバーントレースに適合し得る。このことにより、ストリッピングプロセスおよびエッチングプロセスの間のトレースリフティングの問題が低減される。

30

#### 【0028】

次に、第3の誘電体層220が第1の誘電体層210に施され、第4の誘電体層222が第2の誘電体層212に施される。第3および第4の誘電体層220および222は、第1および第2の誘電体層210および212とは異なる組成物であり得る。層220および222の組成物は、シリカベースのエポキシ材料などの、非光活性材料であり得る。第3および第4の層220および222は、第1および第2の層210および212の厚さよりも大きい厚さに積層またはビルトアップされ得る。たとえば、第1および第2の層210および212は約5～10  $\mu\text{m}$ である場合があり、第3および第4の層220および222は約15  $\mu\text{m}$ である場合がある。

40

#### 【0029】

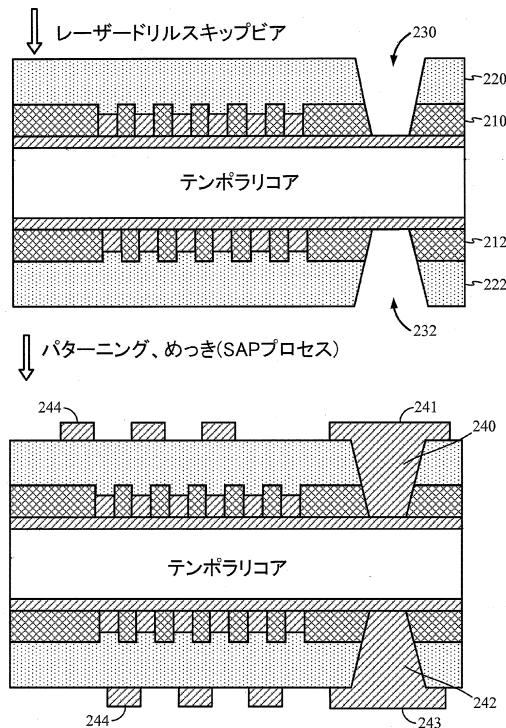

図2Bは、コアレス基板の形成のための方法の例示的な実施形態を示す。図2Bに示す

10

20

30

40

50

ように、第3および第4の誘電体層220および222を施した後、第1のビア230および第2のビア232が形成され得る。第1および第2のビア230および232は、レーザードリリングまたはアブレーションなどの化学的プロセスまたは機械的プロセスによって形成され得る。第1および第2のビアは、第3および第4の層220および222の外側エッジまたは側面から第1および第2の銅層202および204まで延在し得る。これにより、ビア230および232をランディングパッドまたはキャプチャパッドなしに形成することが可能になり、このことが、より細かいか、または追加のルーティングおよびトレースのための水平スペースを節約する。次に、カバーパッド241を含む第1のパッドレススキップビア240およびカバーパッド243を含む第2のパッドレスビア242と底部トレース244とを形成するために、銅めっきプロセスを含むセミアディティブプロセス(SAP)が適用される。

### 【0030】

図3Aおよび図3Bは、コアレス基板の形成のための方法の例示的な実施形態を示す。図3Aでは、図2Bに示したプロセスが継続される。図3Aに示すように、第3および第4の誘電体層220および222の上部に追加の誘電体層を追加することによって、追加のビアが形成され得る。次いで、これらの追加の誘電体層は、追加のビアおよびビアトレースを形成するために図2Bに示すプロセスを経る場合がある。追加のビアは、追加された誘電体層の外面から、以前形成されたビアのカバーパッドまでビアを拡張する化学的プロセスまたは機械的プロセスによって形成され得る。図3Aに示すように、追加の誘電体層および関連のビアが所望されない場合、構造は、ビアトレース244とカバーパッド241および243の一部分とを被覆するSR層245および246を積層し、露光し、現像するSRプロセスを受ける場合がある。図3Bに示すように、テンポラリコア200ならびに銅層202および204が除去される。コア200は、機械的プロセスによって分離される場合があり、銅層202および204は、分離後にエッチング除去され得る。

### 【0031】

本発明の別の実施形態では、半導体構造は、永続的光活性誘電体層および絶縁性誘電体層を有するコアレス基板と、永続的光活性誘電体層に埋め込まれた複数のトレースと、絶縁性誘電体層および永続的光画像形成可能誘電体層を通じて延在する、導通させるための手段とを含み得る。導通させるための手段は、1つまたは複数の隣接する層の平面を通る半導体構造内の層間で電気信号を導通させる(電気的接続を提供する)バスまたは道を提供する。導通させるための手段は、層間で電気信号を導通させるために1つの層内に開口部を設けるビア(垂直相互接続アクセス部)であり得る。導通させるための手段は、半導体構造を通してホールによって電気的に接続された半導体構造の様々な層上の対応する位置の2つのパッドから構成され得る。ホールは、電気めっき、伝導性材料によるホールのライニング、伝導性材料によるホールの充填、またはチューブもしくはリベットによって、導電性にされる場合がある。導通させるための手段は、スキップビア、マクロビア、スルーホールビア、スルーシリコンビア、ブラインドビア、またはベリードビアであり得る。導通させるための手段は、ホールを充填するバレルまたは導電性チューブ、バレルと非接続金属層との間のアンチパッドまたはクリアランスホールを含む場合があり、場合によつては、バレルの各端部を構成要素、平面、またはトレースに接続するパッドを含む場合がある。

### 【0032】

上記の説明は銅に言及するが、銅の代わりに代替材料を使用できることを理解されたい。代替材料は、エッチングに耐える機械的構造、またはエッチングに耐えるためにコーティングされ得る構造を含み得る。

### 【0033】

本明細書で説明する方法の実施形態は、いくつかの用途および集積回路に使用することができる。たとえば、説明した実施形態は、適切な通信を保証するために両ダイ間のデュ

アルダイ（ダイ区分）高密度ルーティングに使用され得る。説明した実施形態は、シリコンインターポーザまたは有機インターポーザを使用せずに使用される場合があるが、製造コストを低減する場合がある。説明した実施形態は、高密度ルーティング用途のプロセッサ、メモリ、または電力管理デバイスのために使用される場合がある。さらなる用途は、当業者には直ちに明らかになるはずである。

#### 【0034】

本出願に記述されるか、例示されるか、または図示されたもののいずれも、任意の構成要素、ステップ、特徴、物体、利益、利点、または均等物が特許請求の範囲に記載されているかどうかにかかわらず、それらの構成要素、ステップ、特徴、物体、利益、利点、または均等物を公衆に献呈することを意図していない。

10

#### 【0035】

デバイスについていくつかの態様について説明してきたが、これらの態様が対応する方法の説明も構成し、したがって、デバイスのブロックまたは構成要素が対応する方法ステップまたは方法ステップの特徴としても理解されるべきであることは言うまでもない。それと同様に、方法ステップに関してまたは方法ステップとして説明した態様は、対応するブロックまたは対応するデバイスの詳細もしくは特徴の説明も構成する。方法ステップのいくつかまたはすべては、たとえば、マイクロプロセッサ、プログラマブルコンピュータ、または電子回路などのハードウェア装置によって（またはハードウェア装置を使用して）実行することができる。いくつかの例示的な実施形態では、最も重要な方法ステップのうちのいくつかまたは複数は、そのような装置によって実行され得る。

20

#### 【0036】

上記で説明した例示的な実施形態は、本開示の原理の説明を構成しているにすぎない。本明細書で説明した構成および詳細の修正および変形が他の当業者に明らかになることは言うまでもない。したがって、本開示は、本説明に基づいて提示された具体的な詳細と、本明細書の例示的な実施形態の説明とによってではなく、添付の特許請求の範囲の保護範囲によってのみ限定されるものとする。

#### 【0037】

上記の発明を実施するための形態では、例示的な実施形態において、様々な特徴が互いにグループ化されることがわかる。本開示のこのやり方は、特許請求された例示的な実施形態が、それぞれの請求項に明示的に述べられたものよりも多い特徴を必要とするものとして理解されるべきでない。むしろ、発明性がある内容が、開示された個々の例示的な実施形態のすべての特徴よりも少なく存在し得るという現実がある。したがって、以下の特許請求の範囲は、これによって本説明に組み込まれたものと見なされるべきであり、各請求項はそれ自体、別々の例示的な実施形態として存在し得る。各請求項がそれ自体、別々の例示的な実施形態として存在し得るが、従属請求項は、特許請求の範囲内で1つまたは複数の請求項との具体的な組合せを参照することができる一方で、他の例示的な実施形態は、前記従属請求項の任意の他の従属請求項の主題との組合せ、または任意の特徴の他の従属請求項および独立請求項との組合せを包含するか、または含む場合もあることに留意されたい。そのような組合せは、具体的な組合せが意図されていないことを明示的に表現されなければ、本明細書で提案される。さらに、請求項の特徴は、前記請求項が独立請求項に直接従属していないとも、任意の他の独立請求項に含まれる場合があることも意図される。

30

#### 【0038】

本説明または特許請求の範囲に開示された方法は、本方法のそれぞれのステップまたは動作を実行するための手段を含むデバイスによって実行され得ることにさらに留意されたい。

40

#### 【0039】

さらに、いくつかの例示的な実施形態では、個々のステップ／動作は、複数のサブステップに再分割されるか、または複数のサブステップを含むことができる。そのようなサブステップは、個々のステップの開示に含まれ、個々のステップの開示の一部分となり得る

50

。

## 【0040】

したがって、本開示の一実施形態は、位置推定のための方法を具現化するコンピュータ可読媒体を含むことができる。したがって、本開示は図示の例に限定されず、本明細書で説明する機能を実行するためのいかなる手段も、本開示の実施形態に含まれる。

## 【0041】

上記開示は、本発明の実例実施形態を示したものであるが、添付の特許請求の範囲で定義されている本発明の範囲を逸脱することなく、本明細書において様々な変更および修正を加えることができることに留意されたい。本明細書で説明される本発明の実施形態による方法クレームの機能、ステップ、および／または動作は、任意の特定の順序で実行される必要はない。さらに、本発明の要素は、単数形において記載または特許請求されている場合があるが、単数形に限定することが明示的に述べられていない限り、複数形も考えられる。

## 【符号の説明】

## 【0042】

|     |                |    |

|-----|----------------|----|

| 100 | 半導体パッケージ       | 10 |

| 110 | 活性ダイ、第1のダイ     |    |

| 120 | 活性ダイ、第2のダイ     |    |

| 130 | 基板             |    |

| 131 | 第1の誘電体層        | 20 |

| 132 | 第2の誘電体層        |    |

| 140 | 埋込型トレース        |    |

| 150 | ビアトレース         |    |

| 160 | パッドレススキップビア    |    |

| 161 | パッドレススキップビア本体  |    |

| 162 | 上部分            |    |

| 163 | 底部分            |    |

| 164 | カバーパッド         |    |

| 170 | パッドレススキップビア    |    |

| 200 | テンポラリコア        | 30 |

| 202 | 第1の銅層          |    |

| 204 | 第2の銅層          |    |

| 210 | 第1の誘電体層        |    |

| 212 | 第2の誘電体層        |    |

| 214 | トレースパターン       |    |

| 216 | 銅トレース          |    |

| 220 | 第3の誘電体層        |    |

| 222 | 第4の誘電体層        |    |

| 230 | 第1のビア          |    |

| 232 | 第2のビア          | 40 |

| 240 | 第1のパッドレススキップビア |    |

| 241 | カバーパッド         |    |

| 242 | 第2のパッドレスビア     |    |

| 243 | カバーパッド         |    |

| 244 | 底部トレース         |    |

| 245 | S R層           |    |

| 246 | S R層           |    |

【図 1 A】

【図 1 B】

FIG. 1A

FIG. 1B

【図 1 C】

【図 2 A】

【図 2B】

FIG. 2B

【図 3A】

FIG. 3A

【図 3B】

FIG. 3B

---

フロントページの続き

(72)発明者 オマー・ジェームズ・ブチール

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 クイウォン・カン

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

(72)発明者 チン - クアン・キム

アメリカ合衆国・カリフォルニア・92121-1714・サン・ディエゴ・モアハウス・ドライ

ヴ・5775

審査官 小林 大介

(56)参考文献 特開2007-173775(JP,A)

特開2001-036238(JP,A)

特開2004-039867(JP,A)

特開2002-164467(JP,A)

米国特許出願公開第2010/0213601(US,A1)

特開2013-214579(JP,A)

特開2014-093330(JP,A)

(58)調査した分野(Int.Cl., DB名)

H05K 1/02

H05K 3/46

H01L 23/12-23/14