(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

PARIS

(11) N° de publication :

(à n'utiliser que pour les commandes de reproduction)

2 675 634

(21) N° d'enregistrement national :

91 04636

(51) Int Cl<sup>5</sup> : H 01 L 33/00

(12)

## DEMANDE DE BREVET D'INVENTION

A1

(22) Date de dépôt : 16.04.91.

(30) Priorité :

(71) Demandeur(s) : FRANCE TELECOM, Kazmierski Christophe — FR et ROBEIN Didier — FR.

(43) Date de la mise à disposition du public de la demande : 23.10.92 Bulletin 92/43.

(56) Liste des documents cités dans le rapport de recherche : Se reporter à la fin du présent fascicule.

(60) Références à d'autres documents nationaux apparentés :

(72) Inventeur(s) : Kazmierski Christophe et Robein Didier.

(73) Titulaire(s) : FRANCE TELECOM.

(74) Mandataire : Brevatome.

(54) Dispositif optoélectronique à très faible capacité parasite.

(57) Dispositif optoélectronique comprenant

- . un substrat (40) en matériau semi-conducteur dopé n;

- . sur le substrat (40), une couche de confinement latéral (50) en matériau semi-conducteur dopé de manière à rendre ce matériau semi-isolant;

- . un ruban (30) comprenant un matériau actif (32), ce ruban (30) étant enterré dans la couche de confinement latéral (50) et en contact avec le substrat (40), la couche de confinement latéral (50) ayant un sillon (52) creusé au-dessus et le long du ruban (30);

- . une couche d'isolation (70) en matériau semi-conducteur dopé n déposée de part et d'autre du sillon (52) sur la couche de confinement latéral (50);

- . une couche de confinement vertical (60) en matériau semi-conducteur dopé p déposée sur la couche d'isolation (70) et remplaçant le sillon (52) de la couche de confinement latéral (50);

- . un contact électrique (80, 90) déposé sur la couche de confinement latéral au moins à la verticale du ruban (30).

FR 2 675 634 - A1

DISPOSITIF OPTOELECTRONIQUE A TRES FAIBLE CAPACITE PARASITE

Description

La présente invention concerne un dispositif optoélectronique à très faible capacité parasite. Elle s'applique notamment à la réalisation de laser semi-conducteur, de modulateur optique ou d'amplificateur à très grande vitesse de commutation commandée électriquement.

On connaît la structure dite BRS ("Buried Ridge Stripe" selon la terminologie anglo-saxonne usuelle) décrite dans l'article de J.C.Bouley et autres, publié dans Proceedings of the 9th IEEE International Laser Conference p.54 (1984) qui permet la réalisation de dispositifs optoélectroniques à grande vitesse de commutation et en particulier de lasers semi-conducteurs.

Un laser semi-conducteur réalisé selon la technique BRS comporte un ruban comprenant une couche active à faible gap enfouie dans une couche de confinement de gap plus large. Le confinement est alors électrique et optique. Le ruban guide le faisceau lumineux produit lors de l'excitation électrique. La cavité optique nécessaire à l'obtention de l'effet laser est constituée par les extrémités clivées ou gravées du ruban.

Les dispositifs optoélectroniques réalisés selon la technique BRS répondent très rapidement aux excitations électriques : le temps de réponse ultime est limité par les processus de relaxation des porteurs dans les bandes de conduction et de valence ; il peut donc atteindre théoriquement des durées de l'ordre de la picoseconde.

Néanmoins, une telle vitesse de fonctionnement est limitée plus sévèrement par la structure même

du composant et de ses éléments électriques parasites. En général, le circuit parasite est équivalent à un circuit RC où R est la résistance d'accès à la zone active et C une capacité parasite.

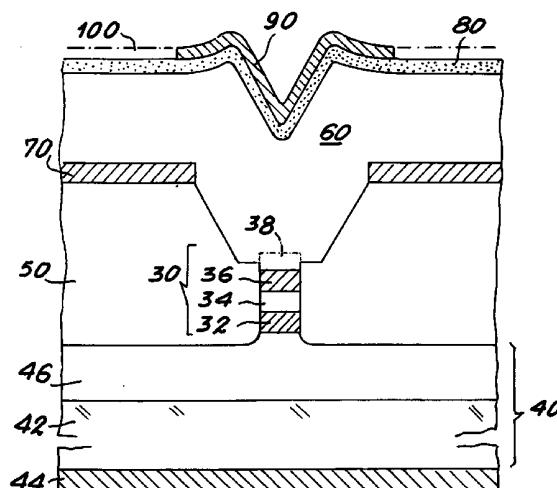

5 La figure 1 représente schématiquement une structure laser connue décrite dans l'article de J.E.Bowers et autres, paru dans Electronics Letters, Vol.23, n°24, p.1263-1265, 19 Novembre 1987. Ce dispositif est dérivé d'une structure BRS et possède

10 un temps de réponse amélioré.

15

Un ruban 10 comprenant une couche en matériau actif repose sur un substrat 12 en InP dopé n. Les deux côtés latéraux du ruban 10 sont entourés par une couche de confinement latéral 14 en InP semi-isolant.

Une couche de confinement vertical 16, en InP dopé p, repose à la verticale du ruban 10 dans un sillon correspondant à l'empreinte du masque servant lors de l'étape d'épitaxie sélective pour former la

20 couche 14. La couche de confinement vertical 16 est tronquée et ses faces latérales sont entourées d'une couche diélectrique 18 en polyimide.

La face supérieure est recouverte d'une couche de contact 20.

25 Le temps de réponse court ( $R*C$  environ 4 ps) d'une telle structure est obtenu grâce à la surface de contact limitée entre la couche de confinement vertical 16 et la couche semi-isolante 14. En effet, cette jonction lorsqu'elle existe est une source de

30 fuite de courant due à une diffusion d'accepteurs de la couche de confinement vertical 16 dans la couche semi-isolante 14 qui perd alors des propriétés diélectriques.

Cette structure présente malgré tout un

35 certain nombre d'inconvénients.

Sa réalisation fait appel à une étape d'épitaxie sélective pour la constitution de la couche de confinement latéral semi-isolante 14. Or, on sait que la présence du masque d'arrêt de croissance (dont 5 seule l'empreinte en forme de sillon est visible sur la figure 1) est une source de perturbations et de défauts du matériau semi-isolant, et ceci à proximité directe de la couche active.

De plus, la couche de confinement vertical 10 16 est d'abord déposée sur tout le matériau semi-isolant 14 puis tronqué par gravure. Lors de cette étape d'épitaxie, les diffusions du zinc (dopant p de la couche 16) vers la couche semi-isolante 14 et du fer (dopant de la couche 14) vers la couche de confinement 15 vertical 16 sont possibles entraînant des fuites de courant et l'augmentation de la capacité parasite.

Enfin, la couche de confinement vertical 16 tronquée, ne présentant qu'une faible largeur et entourée par la couche diélectrique 18 en polyimide, 20 ne possède pas de bonnes propriétés thermiques. De plus, cette faible largeur augmente la résistance d'accès, ce qui a pour conséquence d'élever le temps de réponse de la structure.

La présente invention a pour but de pallier 25 ces inconvénients. Elle préconise une structure dans laquelle la zone active est entourée par un volume important de matériau semi-conducteur et semi-isolant (pour la bonne tenue thermique du dispositif), sans faire appel à une épitaxie sélective (engendrant des 30 défauts), et permettant de bloquer l'interdiffusion des accepteurs de la couche de confinement vertical vers la couche semi-isolante et du dopant de la couche semi-isolante vers la couche de confinement vertical.

Pour cela, une couche d'isolation est déposée 35 sur la couche semi-isolante, permettant ainsi d'étendre

le dépôt de la couche de confinement vertical sans risque d'interdiffusion.

De manière plus précise, la présente invention concerne un dispositif optoélectronique comprenant :

- 5 . un substrat en matériau semi-conducteur dopé n ;

- . sur le substrat, une couche de confinement latéral en matériau semi-conducteur dopé de manière à rendre ce matériau semi-isolant ;

- . un ruban comprenant un matériau actif, ce ruban 10 étant enterré dans la couche de confinement latéral et en contact avec le substrat, la couche de confinement latéral ayant un sillon creusé au-dessus et le long du ruban ;

- . une couche d'isolation en matériau semi-conducteur 15 dopé n déposée de part et d'autre du sillon sur la couche de confinement latéral ;

- . une couche de confinement vertical en matériau semi-conducteur dopé p déposée sur la couche d'isolation et remplissant le sillon de la couche 20 de confinement latéral ;

- . un contact électrique déposé sur la couche de confinement latéral au moins à la verticale du ruban.

De manière avantageuse, la couche de confinement vertical présente une forme en V à la 25 verticale du ruban comprenant le matériau actif, le contact électrique épousant cette forme.

La forme en V permet d'augmenter la surface de métallisation du contact et donc de diminuer la résistance de contact. Elle permet aussi de diminuer 30 la résistance d'accès à la zone active et donc participe à l'amélioration du temps de réponse du dispositif.

Selon une réalisation particulière, le substrat, la couche de confinement latéral et la couche de confinement vertical sont en un premier matériau 35 semi-conducteur choisi dans la catégorie III-V, le

ruban étant constitué de composants appartenant à la catégorie III-V, la couche d'isolation étant en un second matériau semi-conducteur différent du premier et choisi dans la catégorie III-V.

5 Avantageusement, la couche d'isolation est en matériau semi-conducteur quaternaire qui permet la réalisation d'une couche d'isolation très fine.

La présente invention concerne aussi un procédé de fabrication d'un dispositif optoélectronique

10 comprenant les étapes suivantes :

- a) réalisation d'un ruban reposant sur un substrat comprenant au moins une couche en matériau actif recouverte d'une couche de protection et une couche supérieure d'arrêt d'attaque chimique,

- 15 b) dépôt d'une couche de confinement latéral sur le substrat et recouvrant le ruban,

- c) gravure d'un sillon dans la couche de confinement latéral, à la verticale du ruban, la profondeur du sillon étant limitée par la couche d'arrêt

20 d'attaque chimique.

Avantageusement, on élimine la couche d'arrêt d'attaque chimique après cette dernière étape.

Selon une variante du procédé, pour graver le sillon, on dépose, sur la couche de confinement latéral un masque de gravure constituant une couche d'isolation.

Selon une autre caractéristique, on dépose une couche de confinement vertical sur la couche d'isolation, cette couche de confinement vertical

30 remplissant le sillon de manière à ménager une forme en V à la surface libre de cette couche de confinement vertical et en ce qu'on forme un contact électrique épousant ladite forme en V.

Avantageusement, le dépôt de la couche de

35 confinement vertical est effectué par épitaxie en

phase vapeur.

D'autres caractéristiques et avantages de l'invention apparaîtront mieux après la description qui suit donnée à titre explicatif et nullement limitatif. Cette description se réfère à des dessins annexés sur lesquels :

la figure 1, déjà décrite, représente schématiquement un dispositif optoélectronique conforme à l'art antérieur ;

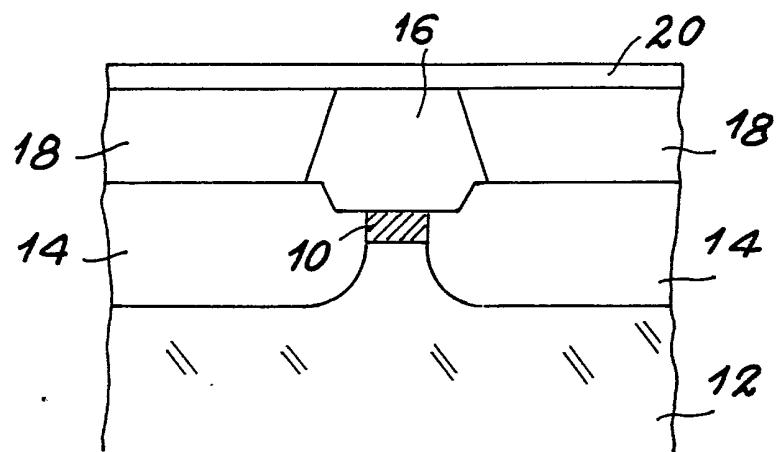

10 la figure 2 représente schématiquement, en coupe, un dispositif optoélectronique conforme à l'invention,

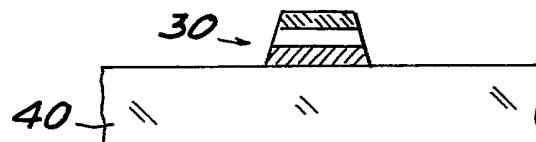

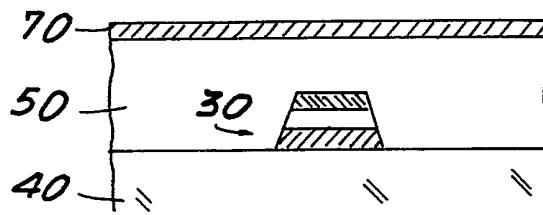

15 les figures 3a à 3e représentent schématiquement différentes étapes du procédé de réalisation d'un dispositif conforme à l'invention.

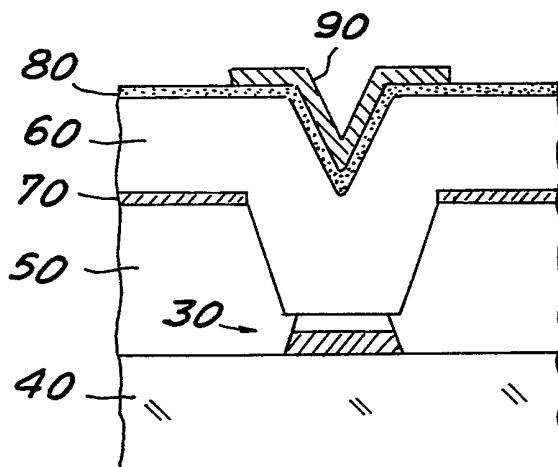

En référence à la figure 2, on décrit maintenant un dispositif optoélectronique conforme à l'invention. Dans cet exemple de réalisation, les matériaux semi-conducteurs sont choisis dans la 20 catégorie III-V sans que ceci constitue pour autant une limitation du domaine d'application de l'invention.

Comme on peut le voir sur la figure 2, un ruban 30 comprenant un matériau actif repose sur un substrat 40.

25 Le substrat 40 comprend une première couche 42 par exemple en InP dopé n-. Le dopant n peut être du silicium, soufre, étain ; sa concentration est comprise dans une fourchette allant de  $5.10^{17}$  à  $3.10^{18}$  at/cm<sup>3</sup> et, par exemple, est égale à 30  $1.10^{18}$  at/cm<sup>3</sup>.

La surface inférieure de la première couche 42 est métallisée pour former une électrode 44 par exemple en TiAu.

35 Dans l'exemple représenté, le substrat 40 comprend encore, reposant sur la face supérieure de

la couche 42, une couche-tampon 46 elle aussi en InP dopé n avec du silicium à une concentration de  $1.10^{18}$  at/cm<sup>3</sup>.

Dans la réalisation représentée, le ruban 5 30 comprend trois couches 32, 34, 36.

La première couche 32 est en matériau actif. Elle peut être réalisée en GaInAsP massif (par exemple : Ga<sub>0,24</sub> In<sub>0,76</sub> As<sub>0,52</sub> P<sub>0,48</sub> pour l'émission laser à 1,3 μm ou bien Ga<sub>0,39</sub> In<sub>0,61</sub> As<sub>0,87</sub> P<sub>0,13</sub> pour 10 l'émission laser à 1,55 μm) ou encore composée d'un empilement de couches alternativement en GaInAs et GaInAsP de manière à former une structure à "puits quantiques" avec un guide optique en GaInAsP à composition constante ou graduelle mais différente 15 de la composition du matériau à "puits quantiques". De cette manière, le dispositif peut fonctionner dans une gamme de longueurs d'onde allant de 1200 à 1600 nm. Par exemple, pour un fonctionnement à 1550 nm, les compositions respectives peuvent être Ga<sub>0,47</sub> In<sub>0,53</sub> 20 As et Ga<sub>0,24</sub> In<sub>0,76</sub> As<sub>0,52</sub> P<sub>0,48</sub>.

La seconde couche 34 du ruban est une couche de protection de la couche en matériau actif d'épaisseur comprise entre 0,01 et 0,1 micromètre ; elle peut être en InP de type P dopé Zn à la concentration 25  $5.10^{17}$  at/cm<sup>3</sup>.

Cette couche de protection évite le contact de la couche active avec l'air ou tout autre couche.

Dans la réalisation représentée sur la figure 2, le ruban 30 comporte une troisième couche 36. Cette 30 couche 36 est facultative, elle réalise un réseau de Bragg périodique de miroir distribué ("Distributed feedback" en terminologie anglo-saxonne). La couche 36 peut être constituée par un empilement de couches en GaInAsP et InP par exemple : Ga<sub>0,24</sub> In<sub>0,76</sub> As<sub>0,52</sub> 35 P<sub>0,48</sub> et InP. Le réseau est par exemple gravé

chimiquement ou par gravure sèche ou par tout autre procédé connu.

Dans le cas où le dispositif comprend une telle couche 36, la couche de protection permet de 5 contrôler la distance séparant la couche 36 et la couche active 32.

Le ruban 30 comprend éventuellement une couche supplémentaire d'arrêt d'attaque chimique 38 dont le rôle et la composition seront décrits plus 10 loin.

Le ruban 30 présente une largeur de 1 à 3 micromètres, par exemple 2  $\mu\text{m}$ . Sa hauteur est par exemple comprise entre 0,2 et 0,6 micromètres.

Le ruban 30 est enterré dans une couche 15 de confinement latéral 50 en matériau semi-conducteur dopé de manière à le rendre semi-isolant. Le matériau peut être de l'InP dopé par exemple avec du fer en concentration pouvant aller de  $1.10^{16}$  at/cm<sup>3</sup> à 20  $5.10^{17}$  at/cm<sup>3</sup>. La concentration peut par exemple être égale à  $1.10^{17}$  at/cm<sup>3</sup>.

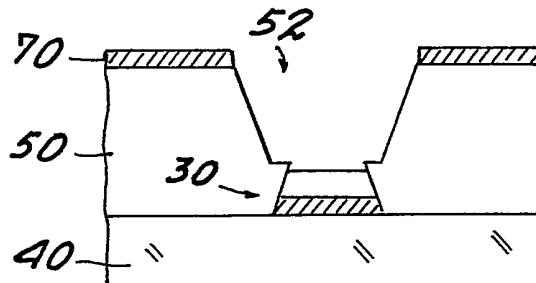

La couche de confinement latéral 50 comprend un sillon 52 creusé au-dessus et le long du ruban 30. Ce sillon permet de diminuer la surface de contact entre la couche de confinement latéral et une couche 25 de confinement vertical décrite plus loin.

La géométrie du sillon résulte du type de gravure utilisé : rectangulaire, trapézoïdale, cylindrique ou combinaison de ces géométries. L'ouverture supérieure du sillon 52 présente une largeur 30 comprise entre 1 et 5 micromètres, par exemple 2 micromètres environ.

La hauteur totale de la couche de confinement latéral, supérieure à 1 micromètre et par exemple égale à 2 micromètres, résulte d'un compromis entre 35 la nécessité d'une hauteur suffisante pour diminuer

la capacité parasite, l'obtention d'une bonne isolation et une surface de contact faible au niveau du sillon 52. Par ailleurs, on comprend que plus la hauteur du ruban 30 est importante, plus la surface de contact 5 au niveau du sillon 52 est faible.

La couche de confinement latéral 50 est recouverte par une couche de confinement vertical 60 qui remplit le sillon 52. Cette couche 60 est en matériau semi-conducteur dopé p, par exemple en InP dopé avec Zn en concentration comprise entre 10  $1.10^{17}$  at/cm<sup>3</sup> et  $5.10^{18}$  at/cm<sup>3</sup>, par exemple  $2.10^{18}$  at/cm<sup>3</sup>.

L'extension sur toute la largeur du dispositif de la couche de confinement vertical 60 permet de 15 répartir la résistance d'accès et de la diminuer au niveau du ruban 30. D'autre part, cette extension permet d'obtenir une bonne tenue thermique du dispositif.

Afin de limiter l'interdiffusion des dopants 20 entre les couches de confinement latéral et vertical 50, 60, une couche d'isolation 70 est disposée de part et d'autre du sillon 52 à l'interface entre les couches de confinement 50, 60. Cette couche d'isolation 70 permet en particulier de préserver le caractère 25 diélectrique de la couche semi-isolante et par là, contribue à la diminution de la capacité parasite.

Cette couche d'isolation est réalisée en matériau semi-conducteur dopé n d'un type différent du matériau utilisé pour les couches de confinement. 30 De manière avantageuse, on utilise un matériau quaternaire, ce qui autorise une très faible épaisseur de couche, de l'ordre de 0,1  $\mu\text{m}$ .

La couche d'isolation 70 peut être en GaInAsP  $\text{Ga}_{0,24}\text{In}_{0,76}\text{As}_{0,52}\text{P}_{0,48}$  dopé avec du silicium en 35 concentration pouvant aller de  $1.10^{16}$  à  $2.10^{18}$  at/cm<sup>3</sup>

et par exemple égale à  $1.10^{18}$  at/cm<sup>3</sup>.

La couche de confinement vertical 60 présente une forme en V à la verticale du ruban 30 comprenant le matériau actif.

5 Une couche de contact 80 par exemple en  $\text{Ga}_{0,47} \text{In}_{0,53} \text{As}$  recouvre la surface supérieure de la couche de confinement vertical 60. Cette couche de contact est dopée p<sup>+</sup> avec du Zn en concentration pouvant aller de  $5.10^{18}$  à  $2.10^{19}$  at/cm<sup>3</sup> et par exemple égale à  $1.10^{19}$  at/cm<sup>3</sup>. Un contact électrique est réalisé par une électrode 90 disposée au niveau du V. Cette électrode 90 est par exemple en TiPt.

La forme en V du contact électrique permet de diminuer la résistance d'accès à la couche active tout en diminuant la résistance de contact grâce à l'augmentation de la surface utile métallisée.

Eventuellement, le dispositif comprend une couche diélectrique 100 en  $\text{Si}_3\text{N}_4$  ou  $\text{SiO}_2$  déposée de part et d'autre de l'électrode 90. Cette couche 100 permet d'assurer une isolation électrique autour de l'électrode.

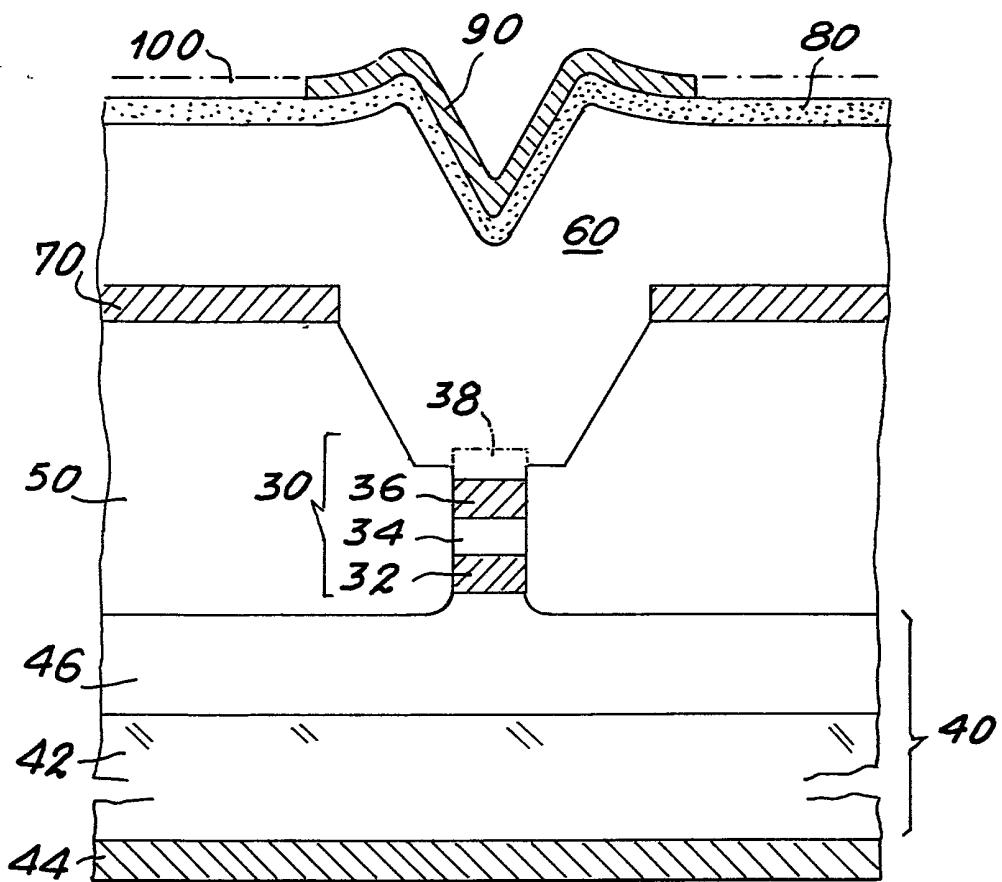

En référence aux figures 3a à 3e, on décrit maintenant un procédé de réalisation d'un dispositif optoélectronique conforme à l'invention.

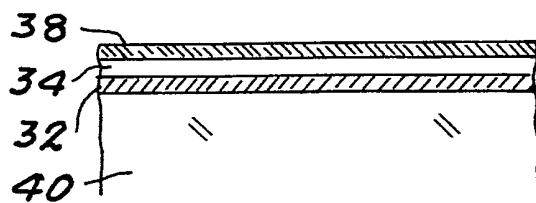

25 On réalise tout d'abord (figure 3a), par exemple grâce à un cycle d'épitaxie en phase vapeur (MOVPE), un substrat 40 recouvert par une couche en matériau actif 32. Le substrat 40 est, comme on l'a vu précédemment, constitué d'une première couche et 30 d'une couche-tampon.

La couche en matériau actif est recouverte par une couche de protection 34. Une couche supérieure d'arrêt d'attaque chimique 38, d'une épaisseur pouvant aller de 0,01 à 0,5 micromètre et par exemple égale à 0,2 m peut être en  $\text{Ga}_{0,24} \text{In}_{0,76} \text{As}_{0,52} \text{P}_{0,48}$  dopé

p avec du zinc à la concentration  $5 \cdot 10^{17}$  at/cm<sup>3</sup>.

Ces premiers dépôts peuvent être aussi effectués suivant d'autres techniques connues, par exemple l'épitaxie ou phase liquide (LPE) ou l'épitaxie 5 par jets moléculaires avec leurs variantes.

Une couche supplémentaire supportant un réseau de Bragg peut éventuellement être intercalée entre la couche 34 et la couche supérieure 38. La réalisation d'un tel réseau est connue et on en trouve 10 par exemple une description dans l'article M.Razeghi et d'autres, publié dans Applied Physics Letters, volume 45 (1984) page 784 ; la réalisation d'un tel réseau n'est donc pas détaillée ici afin d'alléger la description.

15 Les couches 32, 34, 36 sont ensuite gravées par exemple suivant la direction cristallographique <110>. La gravure peut être effectuée par une attaque chimique avec HBr:Br:H<sub>2</sub>O ou par une attaque ionique réactive du type "Reactive Ion Etching" ou "Reactive 20 Ion Beam Etching" (RIE, RIBE) ou leurs combinaisons.

Par cette gravure, on réalise un ruban 30 (figure 3b).

On dépose ensuite, par exemple lors d'un second cycle d'épitaxie en phase vapeur, une couche 25 semi-isolante de confinement latéral 50 recouverte d'une couche bloquante 70 (figure 3c).

Une seconde gravure est ensuite effectuée : dans un premier temps, une ouverture (d'une largeur pouvant aller de 1 à 5 micromètres) est pratiquée 30 sélectivement dans la couche bloquante 70 grâce à une solution de gravure n'agissant pas sur la couche semi-isolante. Dans le cas d'une couche bloquante en GaInAsP et d'une couche semi-isolante en InP, la solution de gravure peut être H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (10:1:1).

35 Dans un second temps, on grave sélectivement

la couche semi-isolante 50, la couche bloquante 70 servant alors de masque de gravure. Cette gravure effectuée par exemple à l'aide d'une solution de HCl:H<sub>3</sub>P0<sub>4</sub> (2:1) est précisément stoppée par la couche 5 d'arrêt chimique 38.

Eventuellement, de manière à éviter des pertes optiques, la couche d'arrêt chimique 38 est éliminée sélectivement par exemple à l'aide d'une solution de H<sub>2</sub>S0<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O. La couche de protection 10 34 (ou la couche supportant le réseau) sert alors de couche d'arrêt d'attaque chimique.

Le second cycle de gravure décrit ci-dessus est chimique, mais il est possible d'effectuer un usinage ionique et/ou plasma. Dans ce cas, les couches 15 d'arrêt d'attaque (couches 38 et 34 selon la gravure effectuée) permettent un contrôle de profondeur d'attaque en analysant les espèces ioniques ou moléculaires dans la chambre d'usinage. L'épaisseur de ces couches peut être alors extrêmement faible 20 (de l'ordre de quelques nanomètres).

Comme on peut le voir sur la figure 3d, à la fin du second cycle de gravure, la couche de confinement latéral 50 est creusée d'un sillon 52 à la verticale du ruban 30. Elle est d'autre part 25 recouverte par la couche bloquante 70 qui a servi de masque de gravure et qui sert par la suite de couche d'isolation.

On dépose ensuite, grâce à un cycle d'épitaxie en phase vapeur, une couche de confinement 60 qui 30 recouvre la couche d'isolation 70 et remplit le sillon 52. La couche de confinement vertical est elle-même recouverte par une couche de contact 80 déposée lors du même cycle d'épitaxie en phase vapeur.

L'épitaxie en phase vapeur permet de ménager 35 dans ces couches de confinement vertical et de contact

60, 80 une forme en V à la verticale du ruban 30.

Une électrode 90 est constituée grâce à une métallisation (par exemple en TiPt) au niveau du V (figure 3e).

5 Le dispositif est entièrement réalisé lorsqu'on a déposé une électrode (par exemple en TiAu) sur la face inférieure du substrat. On peut aussi comme on l'a déjà indiqué, assurer une isolation électrique de la surface supérieure du dispositif

10 grâce à un dépôt d'une couche diélectrique 100 (figure 2).

Si l'on désire utiliser le dispositif optoélectronique de l'invention en tant que laser, il est nécessaire de polir ou de cliver les faces

15 du dispositif parallèles à la feuille sur laquelle est représentée la figure 2.

Le dispositif optoélectronique de l'invention présente une bande passante pouvant être supérieure à 18 GHz non limitée par le produit RC de la structure

20 grâce entre autres à son mode de réalisation qui évite le recours une étape d'épitaxie sélective détériorant ce facteur.

### Revendications

1. Dispositif optoélectronique, caractérisé en ce qu'il comprend :

- un substrat (40) en matériau semi-conducteur dopé n ;

- sur le substrat (40), une couche de confinement latéral (50) en matériau semi-conducteur dopé de manière à rendre ce matériau semi-isolant ;

- 5      • un ruban (30) comprenant un matériau actif (32), ce ruban (30) étant enterré dans la couche de confinement latéral (50) et en contact avec le substrat (40), la couche de confinement latéral (50) ayant un sillon (52) creusé au-dessus et le long du ruban (30) ;

- 10     • une couche d'isolation (70) en matériau semi-conducteur dopé n déposée de part et d'autre du sillon (52) sur la couche de confinement latéral (50) ;

- 15     • une couche de confinement vertical (60) en matériau semi-conducteur dopé p déposée sur la couche d'isolation (70) et remplissant le sillon (52) de la couche de confinement latéral (50) ;

- 20     • un contact électrique (80, 90) déposé sur la couche de confinement latéral au moins à la verticale du ruban (30).

2. Dispositif optoélectronique selon la revendication 1, caractérisé en ce que la couche de confinement vertical (60) présente une forme en V à la verticale du ruban (30) comprenant le matériau actif, le contact électrique (80, 90) épousant cette forme.

30        3. Dispositif optoélectronique selon la revendication 1, caractérisé en ce que le substrat (40), la couche de confinement latéral (50) et la couche de confinement vertical (60) sont en un premier matériau semi-conducteur choisi dans la catégorie

III-V, le ruban (30) étant constitué de composants appartenant à la catégorie III-V, la couche d'isolation (70) étant en un second matériau semi-conducteur différent du premier et choisi dans la catégorie III-V.

5           4. Dispositif optoélectronique selon la revendication 1, caractérisé en ce que la couche d'isolation (70) est en matériau semi-conducteur quaternaire.

10          5. Procédé de fabrication d'un dispositif optoélectronique conforme à la revendication 1, caractérisé en ce qu'il comprend les étapes suivantes :

a) réalisation d'un ruban (30) reposant sur un substrat (40) et comprenant au moins une couche en matériau actif (32) recouverte d'une couche de protection 15 (34) et une couche supérieure d'arrêt d'attaque chimique (38),

b) dépôt d'une couche de confinement latéral (50) sur le substrat (40) et recouvrant le ruban (30),

c) gravure d'un sillon (52) dans la couche de confinement latéral (50), à la verticale du ruban (30), la profondeur du sillon étant limitée par la couche d'arrêt d'attaque chimique (38).

20          6. Procédé selon la revendication 5, caractérisé en ce qu'on élimine la couche d'arrêt d'attaque chimique (38) après l'étape c).

25          7. Procédé selon la revendication 5, caractérisé en ce que pour graver le sillon (52), on dépose sur la couche de confinement latéral (50) un masque de gravure constituant une couche 30 d'isolation (70).

35          8. Procédé selon la revendication 7, caractérisé en ce qu'on dépose une couche de confinement vertical (60) sur la couche d'isolation (70), cette couche de confinement vertical (60) remplissant le sillon (52) de manière à ménager une forme en V à

la surface libre de cette couche de confinement vertical et en ce qu'on forme un contact électrique (80, 90) épousant ladite forme en V.

5 9. Procédé selon la revendication 8, caractérisé en ce que le dépôt de la couche de confinement vertical (60) est effectué par épitaxie en phase vapeur.

1,2

FIG. 1

FIG. 2

2.2

FIG. 3 a

FIG. 3 b

FIG. 3 c

FIG. 3 d

FIG. 3 e

INSTITUT NATIONAL

de la

PROPRIETE INDUSTRIELLE

## RAPPORT DE RECHERCHE

établi sur la base des dernières revendications

déposées avant le commencement de la rechercheFR 9104636

FA 457800

Page 1

| DOCUMENTS CONSIDERES COMME PERTINENTS                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                              | Revendications concernées de la demande examinée                                                                                                                                                                                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Catégorie                                                                                                                                                                                                                                                                                          | Citation du document avec indication, en cas de besoin, des parties pertinentes                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |  |

| X                                                                                                                                                                                                                                                                                                  | OPTICAL FIBER COMMUNICATION CONFERENCE 1990<br>TECHNICAL DIGEST SERIES<br>vol. 1, 22 Janvier 1990, SAN FRANCISCO, CA, US<br>page 213;<br>T.SAZAKI ET AL.: 'A 2.5mA THRESHOLD CURRENT<br>OPERATION AND 5-Gbits/s ZERO-BIAS CURRENT<br>MODULATION OF 1.5 micrometers MQW-DFB LASER<br>DIODES'<br>* le document en entier *<br>* le document en entier *<br>--- | 1, 3                                                                                                                                                                                                                                                                                                                                               |  |

| A                                                                                                                                                                                                                                                                                                  | PATENT ABSTRACTS OF JAPAN<br>vol. 15, no. 200 (E-1070)22 Mai 1991<br>& JP-A-3 054 883 ( SUMITOMO ELECTRIC IND LTD ) 8<br>Mars 1991<br>* abrégé *<br>---                                                                                                                                                                                                      | 2, 5, 7, 8                                                                                                                                                                                                                                                                                                                                         |  |

| X                                                                                                                                                                                                                                                                                                  | PATENT ABSTRACTS OF JAPAN<br>vol. 15, no. 200 (E-1070)22 Mai 1991<br>& JP-A-3 054 883 ( SUMITOMO ELECTRIC IND LTD ) 8<br>Mars 1991<br>* abrégé *<br>---                                                                                                                                                                                                      | 1, 3                                                                                                                                                                                                                                                                                                                                               |  |

| A                                                                                                                                                                                                                                                                                                  | APPLIED PHYSICS LETTERS.<br>vol. 51, no. 12, 21 Septembre 1987, NEW YORK US<br>pages 874 - 876;<br>H.ISHIGURO ET AL.: 'VERY LOW THRESHOLD PLANAR<br>BURIED HETEROSTRUCTURE InGaAsP/InP LASER DIODES<br>PREPARED BY THREE-STAGE METALORGANIC CHEMICAL<br>VAPOR DEPOSITION'<br>* le document en entier *<br>---                                                | 1, 4, 5                                                                                                                                                                                                                                                                                                                                            |  |

| A                                                                                                                                                                                                                                                                                                  | SECOND INTERNATIONAL CONFERENCE-INDIUM PHOSPHIDE<br>AND RELATED MATERIALS<br>23 Avril 1990, DENVER, COLORADO, US<br>pages 161 - 164;<br>B.I.MILLER ET AL.: 'TERTIARYBUTYLARSINE AS A<br>SUBSTITUTE FOR AsH <sub>3</sub> : APPLICATION TO InGaAsP/InP<br>PHOTONIC INTEGRATED CIRCUITS'<br>* figure 1 *<br>---                                                 | 1                                                                                                                                                                                                                                                                                                                                                  |  |

| A, D                                                                                                                                                                                                                                                                                               | ELECTRONICS LETTERS.<br>vol. 23, no. 24, 19 Novembre 1987, ENAGE GB<br>pages 1263 - 1265;<br>BOWERS ET AL.: 'HIGH-SPEED, POLYIMIDE-BASED<br>SEMI-INSULATING PLANAR BURIED HETEROSTRUCTURES'                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                                                                                  |  |

| Date d'achèvement de la recherche<br>14 JANVIER 1992                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                              | Examinateur<br>LINA F.                                                                                                                                                                                                                                                                                                                             |  |

| CATEGORIE DES DOCUMENTS CITES                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                              | T : théorie ou principe à la base de l'invention<br>E : document de brevet bénéficiant d'une date antérieure<br>à la date de dépôt et qui n'a été publié qu'à cette date<br>de dépôt ou qu'à une date postérieure.<br>D : cité dans la demande<br>L : cité pour d'autres raisons<br>.....<br>& : membre de la même famille, document correspondant |  |

| X : particulièrement pertinent à lui seul<br>Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie<br>A : pertinent à l'encontre d'au moins une revendication ou arrière-plan technologique général<br>O : divulgation non-écrite<br>P : document intercalaire |                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                    |  |

**INSTITUT NATIONAL

de la

PROPRIÉTÉ INDUSTRIELLE**

## RAPPORT DE RECHERCHE

établi sur la base des dernières revendications déposées avant le commencement de la recherche

FR 9104636

FA 457800

Page 2

Page 2

**DOCUMENTS CONSIDÉRÉS COMME PERTINENTS**

| Catégorie | Citation du document avec indication, en cas de besoin,<br>des parties pertinentes                                                                                                                                                                                                                             | Revendications<br>concernées<br>de la demande<br>examinée |   |                                               |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---|-----------------------------------------------|

|           |                                                                                                                                                                                                                                                                                                                |                                                           | 1 | DOMAINES TECHNIQUES<br>RECHERCHES (Int. Cl.5) |

| A, D      | <p>APPLIED PHYSICS LETTERS.<br/>vol. 45, no. 7, 1 Octobre 1984, NEW YORK US<br/>pages 784 - 786;<br/>M.RAZEGHI ET AL.: 'CW OPERATION OF 1.57<br/>micrometers Ga(x)In(1-x)As(y)P(1-y)InP<br/>DISTRIBUTED FEEDBACK LASERS GROWN BY<br/>LOW-PRESSURE METALORGANIC CHEMICAL VAPOR<br/>DEPOSITION'</p> <p>-----</p> |                                                           |   |                                               |

Date d'achèvement de la recherche

14 JANVIER 1992

Examinateur

LINA F.

**CATEGORIE DES DOCUMENTS CITES**

X : particulièrement pertinent à lui seul

Y : particulièrement pertinent en combinaison avec un autre document de la même catégorie

A : pertinent à l'encontre d'au moins une revendication ou arrière-plan technologique général

O : divulgation non-écrite

P : document intercalaire

T : théorie ou principe à la base de l'invention

E : document de brevet bénéficiant d'une date antérieure à la date de dépôt et qui n'a été publié qu'à cette date de dépôt ou qu'à une date postérieure.

D : cité dans la demande

L : cité pour d'autres raisons

& : membre de la même famille, document correspondant

PO FORM 1503 03.82 (P0413)