(10) DE 11 2009 002 444 T5 2012.01.19

(12)

## Veröffentlichung

der internationalen Anmeldung mit der

(87) Veröffentlichungs-Nr.: **WO 2010/043032**

in deutscher Übersetzung (Art. III § 8 Abs. 2 IntPatÜG)

(21) Deutsches Aktenzeichen: **11 2009 002 444.0**

(86) PCT-Aktenzeichen: **PCT/CA2009/001451**

(86) PCT-Anmeldetag: **14.10.2009**

(87) PCT-Veröffentlichungstag: **22.04.2010**

(43) Veröffentlichungstag der PCT Anmeldung

in deutscher Übersetzung: **19.01.2012**

(51) Int Cl.:

**G11C 7/10 (2006.01)**

**G11C 16/06 (2006.01)**

**G11C 5/06 (2006.01)**

**G11C 7/22 (2006.01)**

(30) Unionspriorität:

**61/105,061 14.10.2008 US**

**61/111,013 04.11.2008 US**

**12/401,963 11.03.2009 US**

(74) Vertreter:

**derzeit kein Vertreter bestellt**

(71) Anmelder:

**Mosaid Technologies Inc., Kanata, Ontario, CA**

(72) Erfinder:

**Kim, Jin-Ki, Ontario, CA; Pyeon, Hong Beom, Ontario, CA**

(54) Bezeichnung: **A composite memory having a bridging device for connecting discrete memory devices to a system**

(57) Zusammenfassung: Eine Kompositsspeichervorrichtung enthält diskrete Speichervorrichtungen und eine Brückenvorrichtung zum Steuern der diskreten Speichervorrichtungen in Reaktion auf globale Speichersteuersignale, die ein Format oder Protokoll haben, das mit den Speichervorrichtungen nicht kompatibel ist. Die diskreten Speichervorrichtungen können kommerzielle, serienmäßig produzierte Speichervorrichtungen oder kundenspezifische Speichervorrichtungen sein, die auf native oder lokale Speichersteuersignale ansprechen. Die globalen und lokalen Speichersteuersignale enthalten Befehle und Befehlssignale, die jeweils verschiedene Formate haben. Die Kompositsspeichervorrichtung enthält ein System-In-Package mit Halbleiterchips der diskreten Speichervorrichtungen und der Brückenvorrichtung oder kann eine Schaltungsplatine aufweisen, auf der die gepackten diskreten Speichervorrichtungen und eine ge packte Brückenvorrichtung montiert sind.

**Beschreibung****QUERBEZUG ZU VERWANDTEN ANMELDUNGEN**

**[0001]** Diese Anmeldung beansprucht die Priorität der U. S. Provisional Patent Application No. 61/105,061, angemeldet am 14. Oktober 2008, der U. S. Provisional Patent Application No. 61/111,013, angemeldet am 4. November 2008, und der U.S. Patent Application No. 12/401,963, angemeldet am 11. März 2009, deren Offenbarungen hiermit durch Bezugnahme in ihrer Gesamtheit in die vorliegende Anmeldung aufgenommen werden.

**HINTERGRUND**

**[0002]** Bei derzeit verfügbaren Produkten der Industrie- und Unterhaltungselektronik sind Halbleiterspeicheranordnungen überaus wichtige Komponenten. Zum Beispiel basieren Computer, Mobiltelefone und andere tragbare elektronische Geräte auf irgendeiner Form von Speichervorrichtung zum Speichern von Daten. Obwohl viele Speichervorrichtungen normalerweise als Rohstoffe oder als diskrete Speichervorrichtungen verfügbar sind, hat die Forderung nach immer höheren Ebenen der Integration und nach einer größeren Eingabe/Ausgabe-Bandbreite (I/O-Bandbreite) zur Entwicklung von eingebetteten Speichern geführt, die mit Systemen integriert werden können, wie zum Beispiel Mikrocontroller und andere Verarbeitungsschaltungen.

**[0003]** Bei den meisten Unterhaltungselektronikgeräten werden nicht-flüchtige Speicher, wie zum Beispiel Flash-Speichervorrichtungen, zum Speichern von Daten verwendet. Die Nachfrage nach Flash-Speichervorrichtungen steigt weiterhin signifikant, da diese Vorrichtungen bei verschiedenen Anwendungen, die große Mengen an nicht-flüchtigen Speichern erfordern, sehr gut geeignet sind, während sie gleichzeitig nur wenig Platz in Anspruch nehmen. Beispielsweise sind Flash-Speicher in großem Umfang in verschiedenen Vorrichtungen der Unterhaltungselektronik zu finden, wie zum Beispiel Digitalkameras, Mobiltelefone, USB-Flash-Laufwerke (USB = Universal Serial Bus) und tragbare Musikabspielgeräte, um Daten zu speichern, die von diesen Vorrichtungen verwendet werden. Ferner werden Flash-Speichervorrichtungen für Festkörper-Laufwerke (Solid State Drive = SSD) als Ersatz für Festplatten-Laufwerke (Hard Disk Drive = HDD) verwendet. Diese tragbaren Vorrichtungen sind vorzugsweise bezüglich Formfaktorgröße und Gewicht minimiert. Unglücklicherweise erfordern Multimedia- und SSD-Anwendungen große Mengen an Speicher, wodurch sich die Formfaktorgröße und das Gewicht der zugehörigen Geräte erhöhen können. Hersteller von Geräten der Unterhaltungselektronik müssen daher einen Kompromiss machen, indem sie die Menge an physikalischem Speicher begrenzen, der in dem Produkt enthalten ist, um deren Größe und Gewicht für die Konsumenten in einem akzeptablen Rahmen zu halten. Außerdem, obwohl Flash-Speicher eine höhere Dichte pro Einheitsfläche als DRAM oder SRAM haben, ist ihre Leistungsfähigkeit infolge ihrer relativ geringen I/O-Bandbreite begrenzt, was sich negativ auf ihren Lese- und Schreibdurchsatz auswirkt.

**[0004]** Um die immer noch stark anwachsende Nachfrage nach Speichervorrichtungen und nach Anwendungen für Speichervorrichtungen zu erfüllen, ist es gewünscht, Speichervorrichtungen mit hoher Leistungsfähigkeit verfügbar zu haben, d. h. Vorrichtungen, mit höherer I/O-Bandbreite, höherem Lese- und Schreibdurchsatz sowie erhöhter Funktionsflexibilität.

**ZUSAMMENFASSUNG**

**[0005]** In der vorliegenden Anmeldung wird eine Kompositsspeichervorrichtung mit einer Brückenvorrichtung und mit diskreten Speichervorrichtungen offenbart. Die Speichervorrichtungen sind beispielsweise Flash-Speicher, DRAMs (Dynamic Random Access Memories) und SRAMs (Static Random Access Memories), DiNOR-Flash-EEPROM-Vorrichtungen, serielle Flash-EEPROM-Vorrichtungen, Ferro-RAM-Vorrichtungen, Magneto-RAM-Vorrichtungen, Phasenwechsel-RAM-Vorrichtungen oder geeignete Kombinationen aus diesen und/oder anderen Vorrichtungen.

**[0006]** Gemäß einem Aspekt ist eine Kompositsspeichervorrichtung mit mindestens einer diskreten Speichervorrichtung und einer Brückenvorrichtung vorgesehen. Diese mindestens eine diskrete Speichervorrichtung führt Speicheroperationen in Reaktion auf lokale Speichersteuersignale aus, die ein erstes Format haben. Die Brückenvorrichtung empfängt globale Speichersteuersignale, die ein zweites Format haben, und konvertiert die globalen Speichersteuersignale in die lokalen Speichersteuersignale.

**[0007]** In einem Ausführungsbeispiel kann die Brückenvorrichtung einen lokalen Eingabe/Ausgabe-Port (I/O-Port), der mit der mindestens einen diskreten Speichervorrichtung verbunden ist, einen globalen Eingabe-Port

zum Empfangen der globalen Speichersteuersignale und einen globalen Ausgabe-Port haben, um entweder die globalen Speichersteuersignale oder Lesedaten von der mindestens einen diskreten Speichervorrichtung zu liefern.

**[0008]** Die mindestens eine diskrete Speichervorrichtung und die Brückenvorrichtung können in einem Gehäuse eingekapselt sein. Der globale Eingabe-Port und der globale Ausgabe-Port können mit Leitungen des Gehäuses elektrisch gekoppelt sein. Elektrische Leiter können verwendet werden, um den lokalen Eingabe/Ausgabe-Port mit der mindestens einen diskreten Speichervorrichtung zu koppeln. Alternativ kann der lokale Eingabe/Ausgabe-Port drahtlos mit der mindestens einen diskreten Speichervorrichtung gekoppelt sein.

**[0009]** Bei einem weiteren Ausführungsbeispiel kann die mindestens eine diskrete Speichervorrichtung eine gepackte Speichervorrichtung sein, und die Brückenvorrichtung kann eine gepackte Brückenvorrichtung sein. Die gepackte Speichervorrichtung und die gepackte Brückenvorrichtung können auf einer Schaltungsplatine montiert sein. Der lokale Eingabe/Ausgabe-Port, der globale Eingabe-Port und der globale Ausgabe-Port können elektrisch mit Leitungen der gepackten Brückenvorrichtung gekoppelt sein. Die gepackte Speichervorrichtung kann Speicherleitungen haben, die elektrisch mit dem lokalen Eingabe/Ausgabe-Port der gepackten Brückenvorrichtung verbunden sind.

**[0010]** Bei einem Ausführungsbeispiel können die globalen Speichersteuersignale in der Kompositsspeichervorrichtung in einem globalen Befehl empfangen werden. Der globale Befehl kann außerdem einen Adresskopf enthalten. Der Adresskopf kann eine globale Vorrichtungsadresse, die einer ausgewählten Kompositsspeichervorrichtung entspricht, und eine lokale Vorrichtungsadresse enthalten, die einer ausgewählten diskreten Speichervorrichtung der mindestens einen diskreten Speichervorrichtung in der ausgewählten Kompositsspeichervorrichtung entspricht.

**[0011]** Bei einem Ausführungsbeispiel der Kompositsspeichervorrichtung kann das erste Format ein serielles Datenschnittstellenformat oder ein ONFI-Spezifikationsschnittstellenformat umfassen, und das zweite Format kann ein asynchrones Flash-Speicherformat umfassen.

**[0012]** Gemäß einem weiteren Aspekt ist ein Speichersystem mit einer Speichersteuerung und n Kompositsspeichervorrichtungen vorgesehen, die seriell miteinander sowie mit der Speichersteuerung in einer Ringtopologiekonfiguration verbunden sind. Die Speichersteuerung liefert einen globalen Befehl, der einer Speicheroperation entspricht. Jede der n Kompositsspeichervorrichtungen enthält m diskrete Speichervorrichtungen und eine Brückenvorrichtung. Die Brückenvorrichtung einer ausgewählten Kompositsspeichervorrichtung der n Kompositsspeichervorrichtungen empfängt den globalen Befehl und liefert lokale Speichersteuersignale, die der Speicheroperation entsprechen, zu einer ausgewählten diskreten Speichervorrichtung der m diskreten Speichervorrichtungen, wobei n und m Integerwerte größer als 0 sind.

**[0013]** Bei einem Ausführungsbeispiel kann jede der n Kompositsspeichervorrichtungen ein System in einem Gehäuse (System in Package = SIP) oder eine Schaltungsplatine (PCB) sein. Die m diskreten Speichervorrichtungen und die Brückenvorrichtung können gepackte Vorrichtungen mit Gehäuseleitungen sein, die mit Leiterbahnen auf der Schaltungsplatine verbunden sind.

**[0014]** Bei einem weiteren Ausführungsbeispiel kann die Brückenvorrichtung eine Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle, eine Formatkonvertierungsschaltung und eine Speichervorrichtungsschnittstelle aufweisen. Die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle hat einen Eingabe-Port zum Empfangen des globalen Befehls und einen Ausgabe-Port zum Liefern des globalen Befehls. Die Brückenvorrichtung vergleicht die globale Vorrichtungsadresse mit einer vorbestimmten Adresse, die in einem globalen Vorrichtungsadressregister gespeichert ist, und wenn die globale Vorrichtungsadresse mit der vorbestimmten Adresse übereinstimmt, konvertiert die Formatkonvertierungsschaltung die globalen Speichersteuersignale des globalen Befehls, die ein erstes Format haben, in die lokalen Speichersteuersignale, die ein zweites Format haben. Die Speichervorrichtungsschnittstelle liefert dann die lokalen Speichersteuersignale in Reaktion auf die lokale Vorrichtungsadresse zu der ausgewählten diskreten Speichervorrichtung.

**[0015]** Bei einem Ausführungsbeispiel enthält die Formatkonvertierungsschaltung einen Befehlsformatwandler und einen Datenformatwandler. Der Befehlsformatwandler konvertiert die globalen Speichersteuersignale, die das erste Format haben, in die lokalen Speichersteuersignale, die das zweite Format haben. Der Datenformatwandler konvertiert Lesedaten aus der ausgewählten diskreten Speichervorrichtung vom zweiten Format in das erste Format. Bei einer Schreiboperation konvertiert der Datenformatwandler Schreibdaten vom ersten Format in das zweite Format.

**[0016]** Bei einem noch weiteren Ausführungsbeispiel kann eine Kompositsspeichervorrichtung in dem Speichersystem verschiedene Typen von diskreten Speicher vorrichtungen enthalten. In solchen Fällen kann die Brückenvorrichtung eine Anzahl von Formatkonvertierungsschaltungen aufweisen, die jedem Typ der verschiedenen Typen von diskreten Speichervorrichtungen entsprechen.

**[0017]** Gemäß einem weiteren Aspekt ist ein Kompositsspeichervorrichtungsgehäuse vorgesehen. Das Kompositsspeichervorrichtungsgehäuse enthält mindestens eine diskrete Speichervorrichtung und eine Brückenvorrichtung. Die mindestens eine diskrete Speichervorrichtung führt Speicheroperationen in Reaktion auf lokale Speichersteuersignale durch, die ein erstes Format haben. Die Brückenvorrichtung empfängt globale Speichersteuersignale, die ein zweites Format haben, und konvertiert die globalen Speichersteuersignale in die lokalen Speichersteuersignale. Die Brückenvorrichtung und die mindestens eine diskrete Speichervorrichtung sind in einer gestapelten Weise relativ zueinander angeordnet.

**[0018]** Gemäß einem noch weiteren Aspekt ist ein Speichermodul vorgesehen. Das Speichermodul enthält mindestens eine gepackte diskrete Speichervorrichtung und eine gepackte Brückenvorrichtung. Die mindestens eine gepackte diskrete Speichervorrichtung weist Speichervorrichtungsleitungen auf, die mit Leiterbahnen einer Schaltungsplatine verbunden sind. Die mindestens eine gepackte Speichervorrichtung führt Speicheroperationen in Reaktion auf lokale Speichersteuersignale durch, die ein erstes Format haben. Die gepackte Brückenvorrichtung weist Brückenvorrichtungsleitungen auf, die mit den Leiterbahnen der Schaltungsplatine verbunden sind. Die mindestens eine gepackte Brückenvorrichtung empfängt globale Speichersteuersignale, die ein zweites Format haben, und konvertiert die globalen Speichersteuersignale in die lokalen Speichersteuersignale.

**[0019]** Gemäß einem weiteren Aspekt ist eine Brückenvorrichtung vorgesehen, um auf eine diskrete Speichervorrichtung in Reaktion auf globale Signale zuzugreifen, die ein globales Format haben. Die Brückenvorrichtung hat eine Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle und eine Brückenvorrichtungs-Speichervorrichtungsschnittstelle. Die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle kommuniziert die globalen Signale, die das globale Format haben, zu und von der Brückenvorrichtung. Die Brückenvorrichtungs-Speichervorrichtungsschnittstelle kommuniziert lokale Signale, die ein lokales Format haben, zwischen der Brückenvorrichtung und der diskreten Speichervorrichtung. Die lokalen Signale entsprechen funktional den globalen Signalen und haben ein lokales Format, das verschieden ist von dem globalen Format.

**[0020]** Gemäß einem weiteren Aspekt ist ein Speichersystem mit einer Speichersteuerung und n Kompositsspeichervorrichtungen vorgesehen. Die Speichersteuerung liefert, einen globalen Befehl, der einer Speicheroperation entspricht. Die n Kompositsspeichervorrichtungen sind parallel zueinander und mit der Speichersteuerung verbunden, wobei jede der n Kompositsspeichervorrichtungen m diskrete Speichervorrichtungen und eine Brückenvorrichtung enthält. Die Brückenvorrichtung einer ausgewählten Kompositsspeichervorrichtung der n Kompositsspeichervorrichtungen empfängt den globalen Befehl, um lokale Speichersteuersignale, die der Speicheroperation entsprechen, zu einer ausgewählten diskreten Speichervorrichtung der m diskreten Speichervorrichtungen zu tiefen, wobei n und m Integerwerte größer als 0 sind.

**[0021]** Weitere Aspekte und Merkmale der vorliegenden Erfindung werden für den Fachmann beim Lesen der folgenden Beschreibung spezieller Ausführungsbeispiele der Erfindung zusammen mit den beiliegenden Figuren offensichtlich.

#### KURZBESCHREIBUNG DER ZEICHNUNGEN

**[0022]** Ausführungsbeispiele der vorliegenden Erfindung werden nun lediglich anhand eines Beispiels unter Bezugnahme auf die beigefügten Figuren beschrieben, in denen:

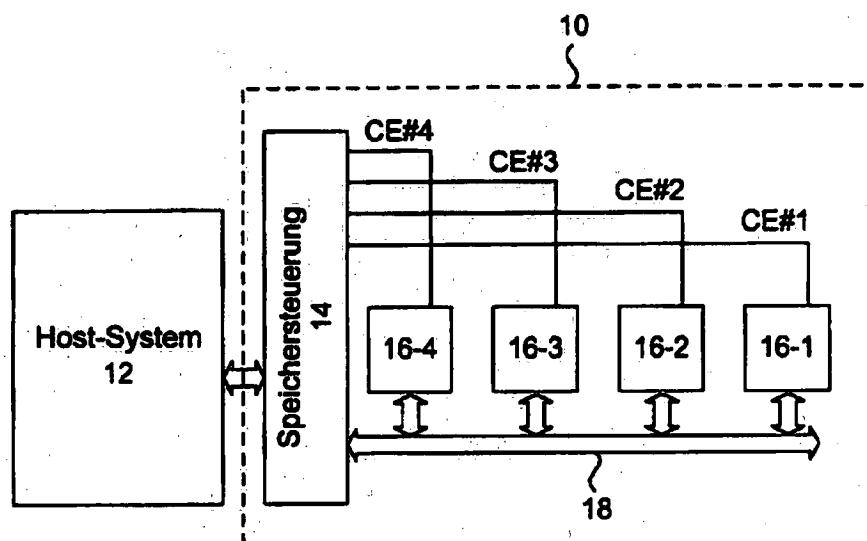

**[0023]** [Fig. 1A](#) ein Blockdiagramm von einem beispielhaften nicht-flüchtigen Speichersystem ist;

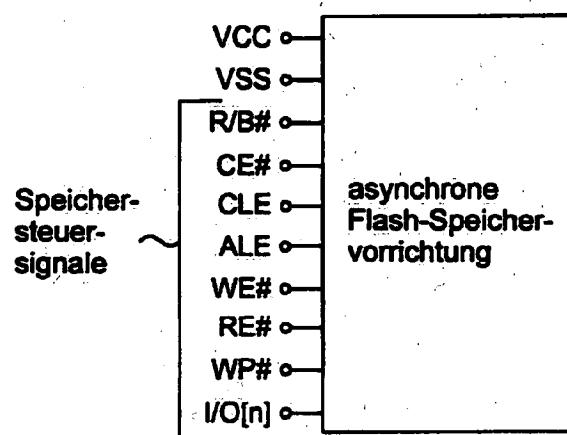

**[0024]** [Fig. 1B](#) eine Darstellung von einer diskreten Flash-Speichervorrichtung ist, die in dem beispielhaften Speichersystem aus [Fig. 1A](#) verwendet wird;

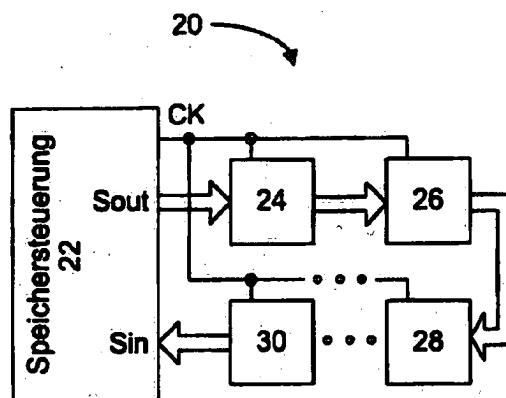

**[0025]** [Fig. 2A](#) ein Blockdiagramm von einem beispielhaften seriellen Speichersystem ist;

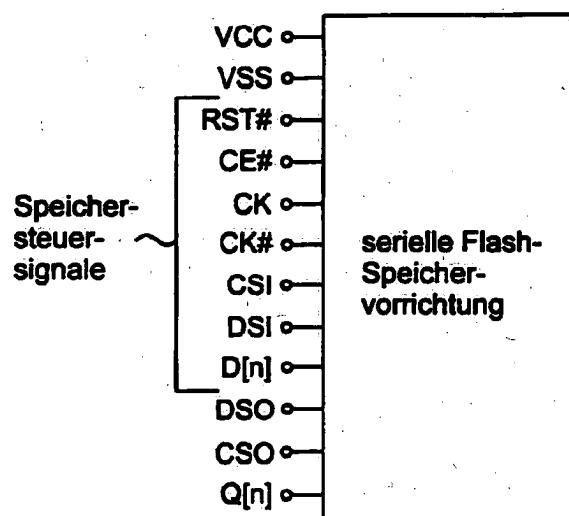

**[0026]** [Fig. 2B](#) eine Darstellung von einer diskreten seriellen Schnittstellen-Flash-Speichervorrichtung ist, die in dem beispielhaften Speichersystem aus [Fig. 2A](#) verwendet wird;

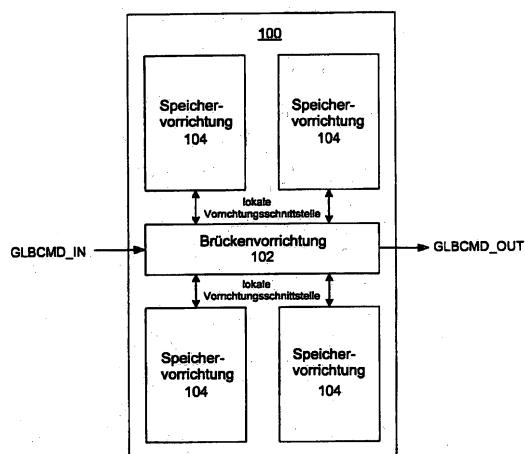

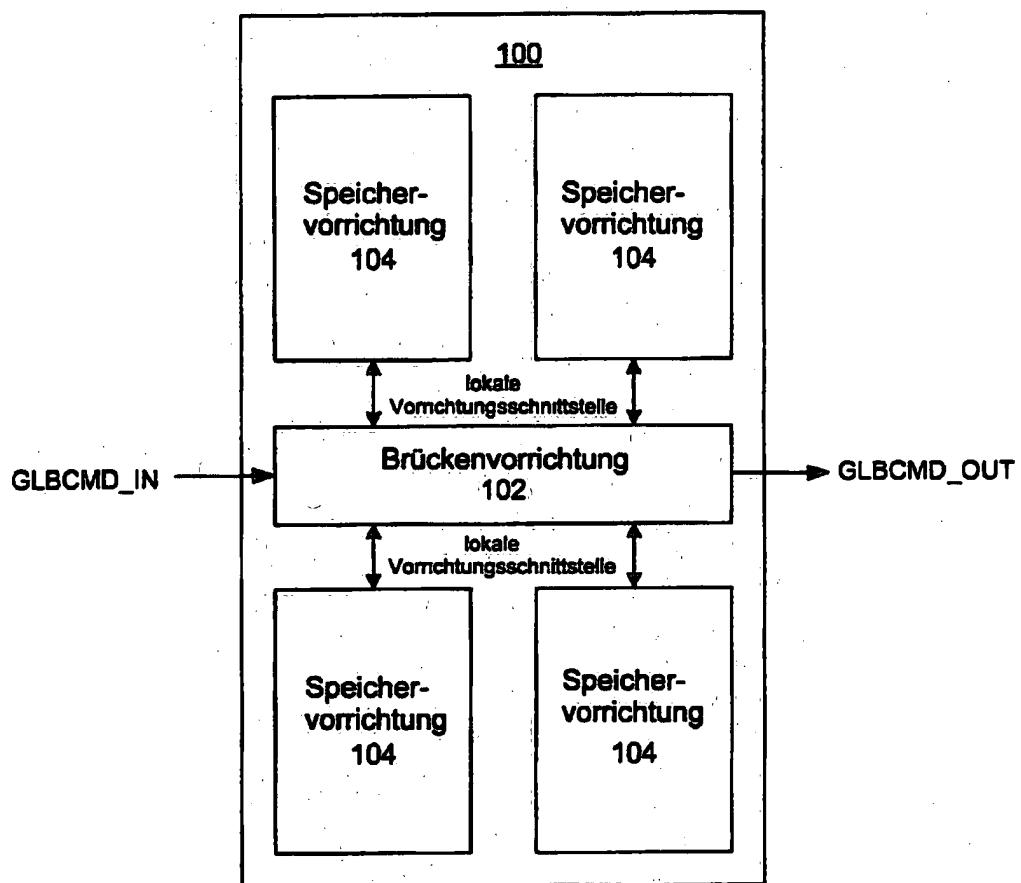

[0027] [Fig. 3A](#) ein Blockdiagramm von einer Kompositsspeichervorrichtung mit vier diskreten Speichervorrichtungen und einer Brückenvorrichtung gemäß einem Ausführungsbeispiel ist;

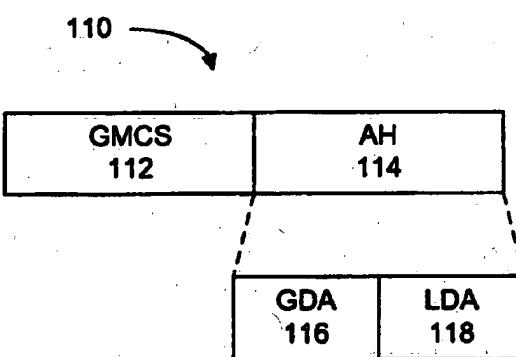

[0028] [Fig. 3B](#) eine Darstellung von einem globalen Befehl gemäß einem vorliegenden Ausführungsbeispiel ist;

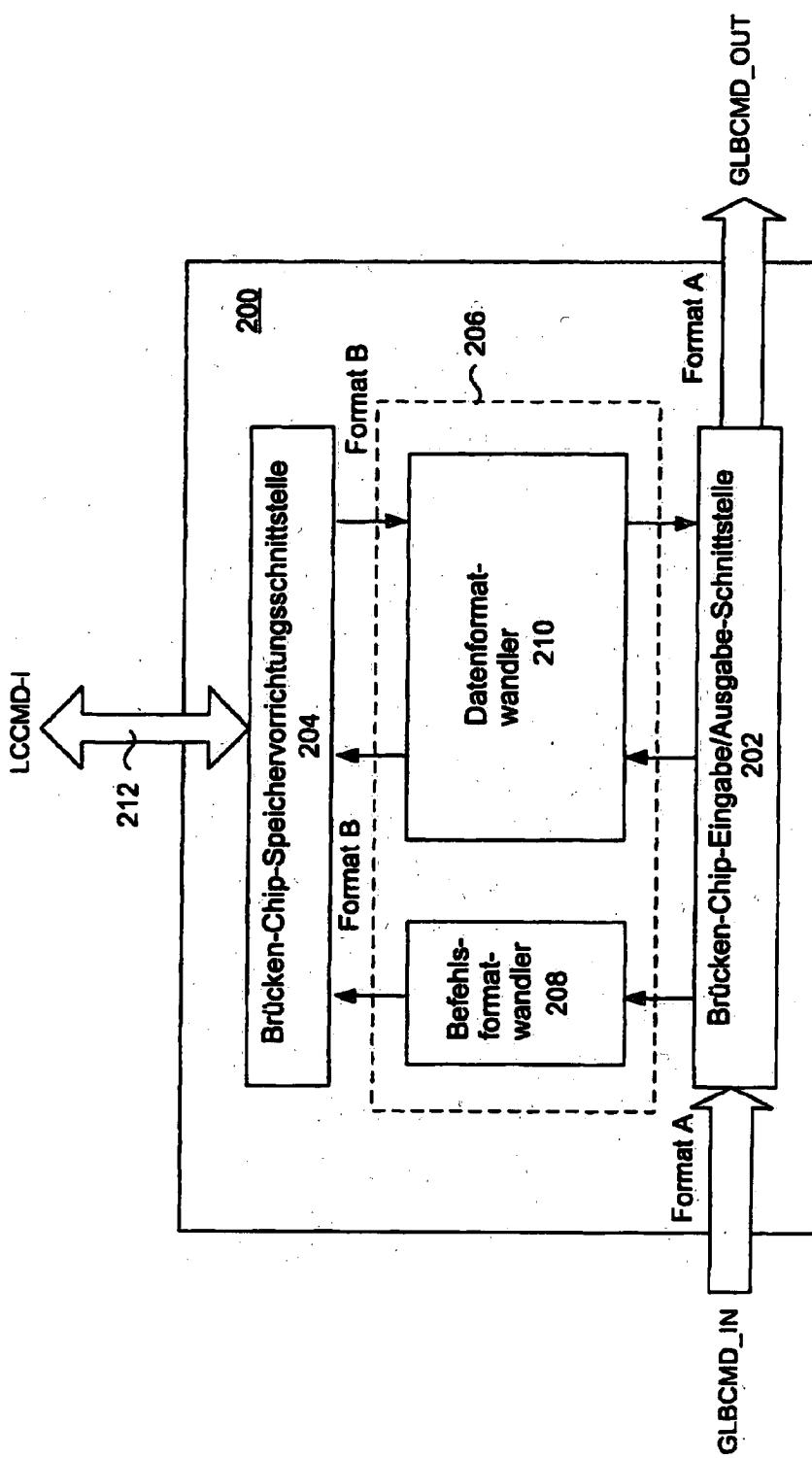

[0029] [Fig. 4](#) ein Blockdiagramm von einer Brückenvorrichtung gemäß einem Ausführungsbeispiel ist;

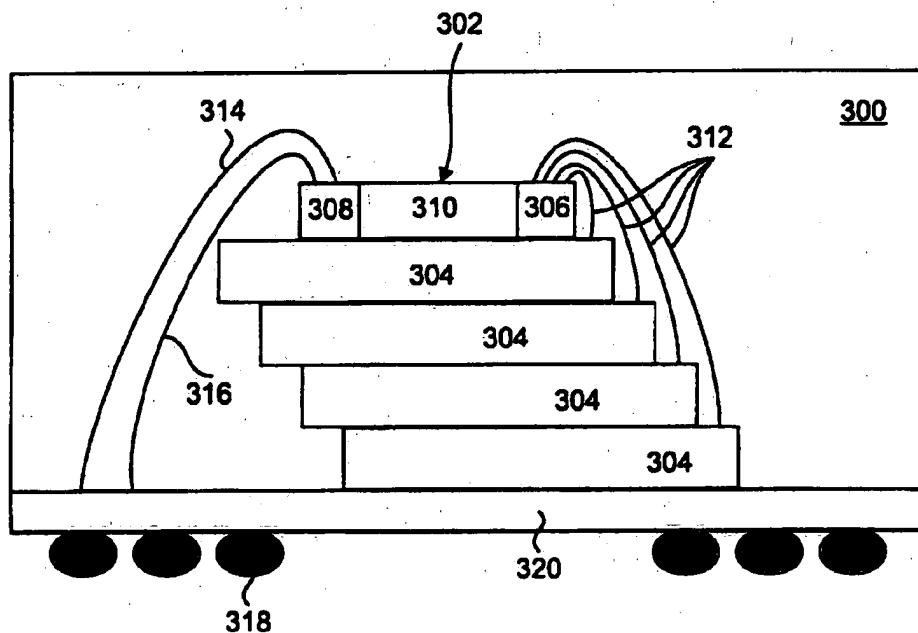

[0030] [Fig. 5A](#) eine Querschnittsansicht von einer Kompositsspeichervorrichtung in einem Gehäuse gemäß einem weiteren Ausführungsbeispiel ist

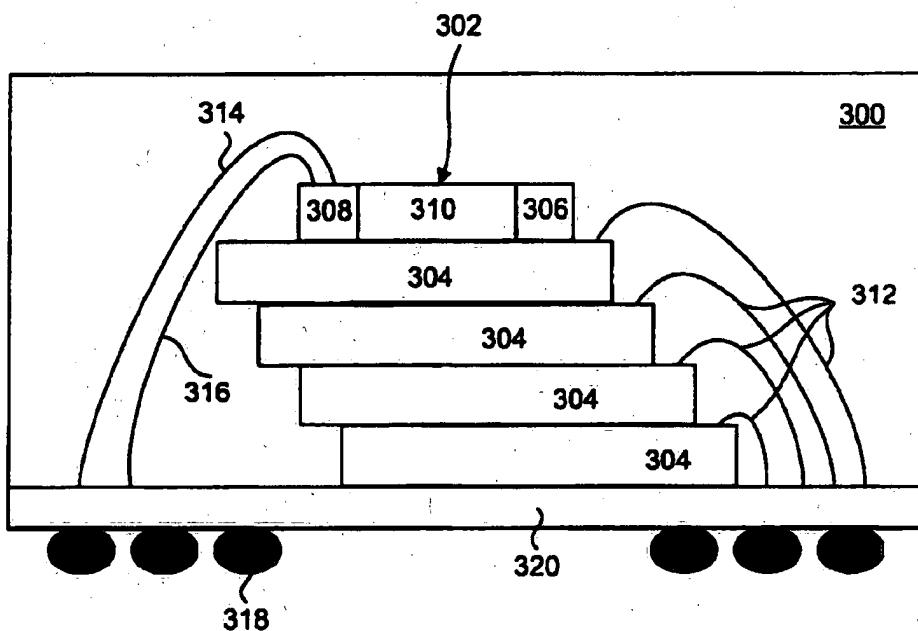

[0031] [Fig. 5B](#) eine Querschnittsansicht von einer anderen Kompositsspeichervorrichtung in einem Gehäuse gemäß einem weiteren Ausführungsbeispiel ist;

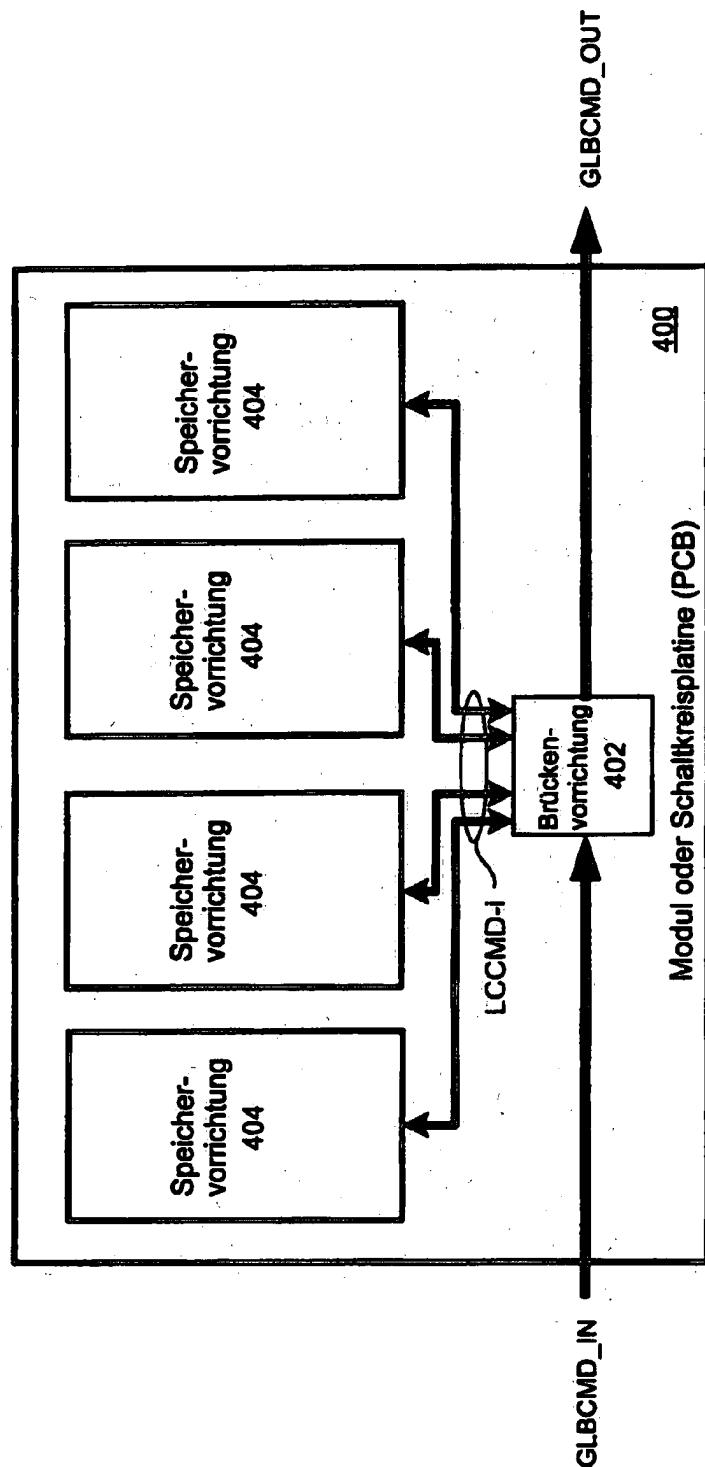

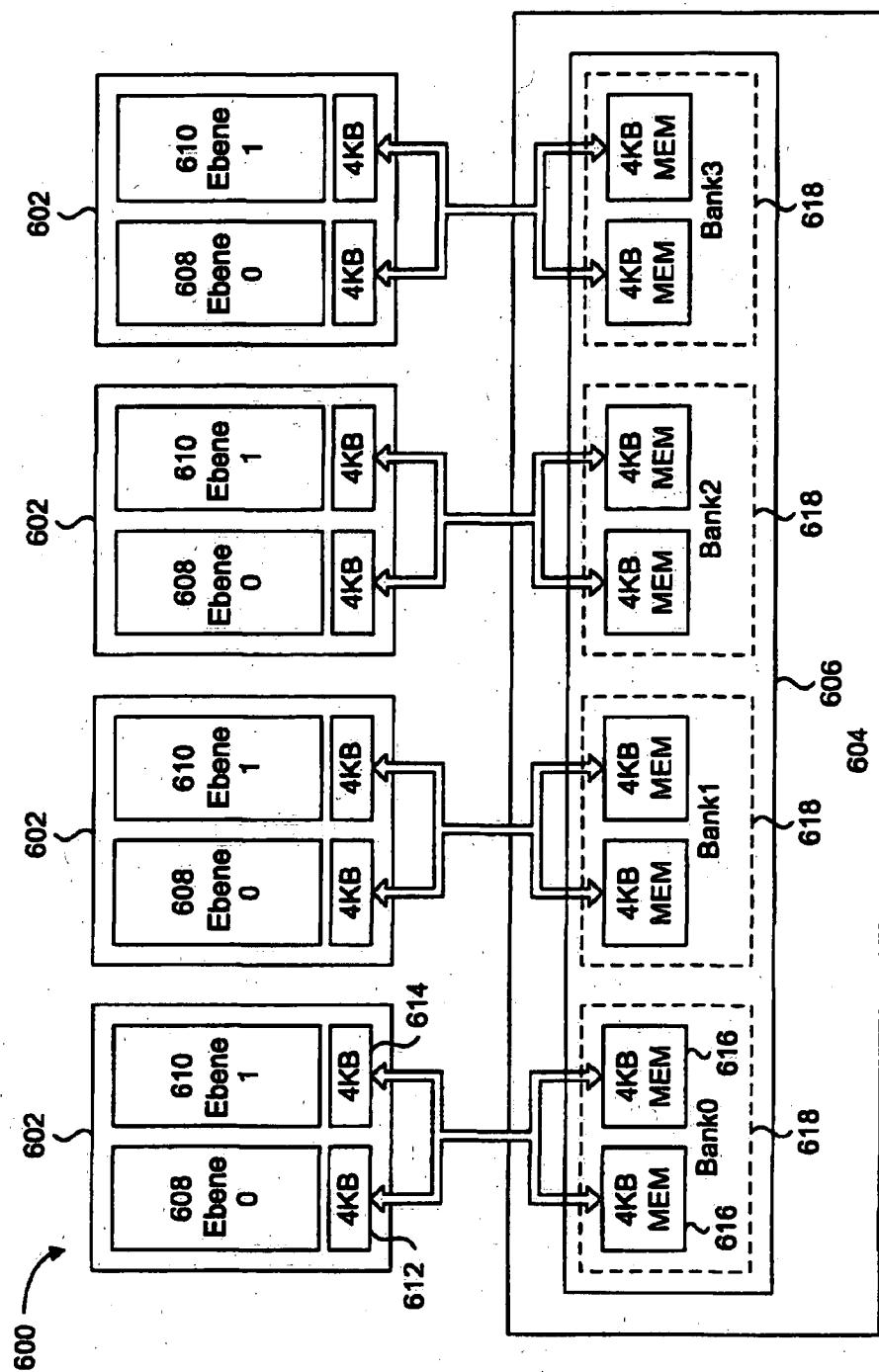

[0032] [Fig. 6](#) ein Blockdiagramm von einem Speichersystem mit einer Anzahl von diskreten Speichervorrichtungen ist, die mit einer Brückenvorrichtung in einem Modul gemäß einem weiteren Ausführungsbeispiel verbunden sind;

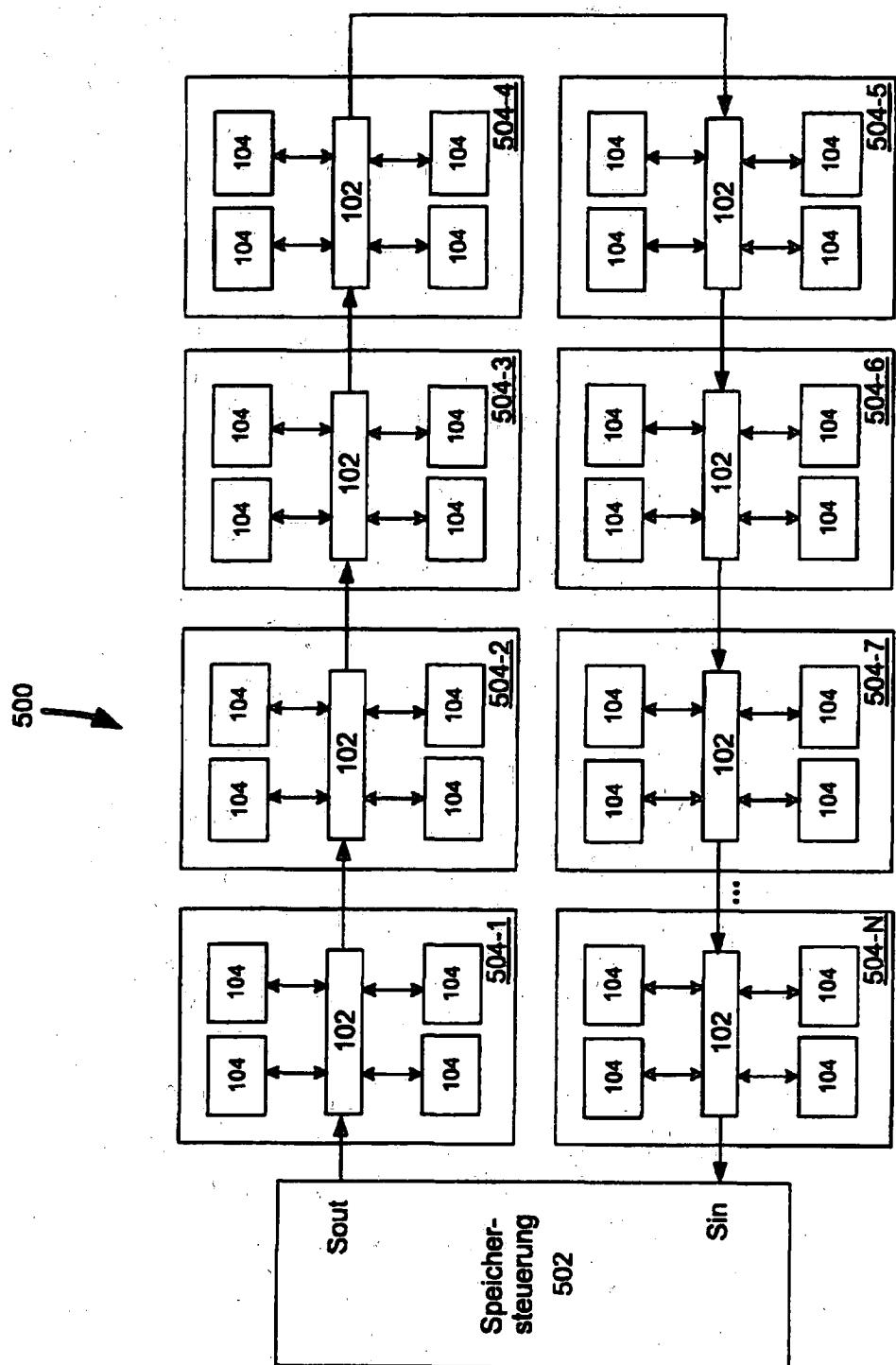

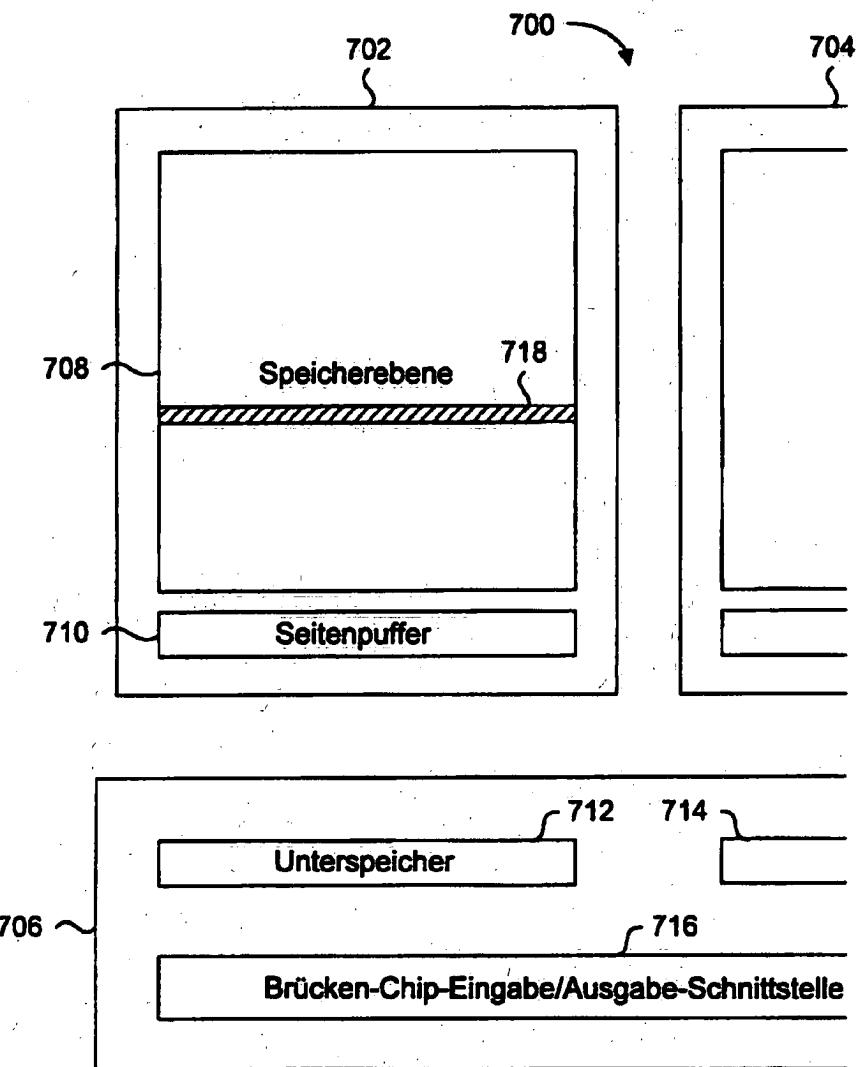

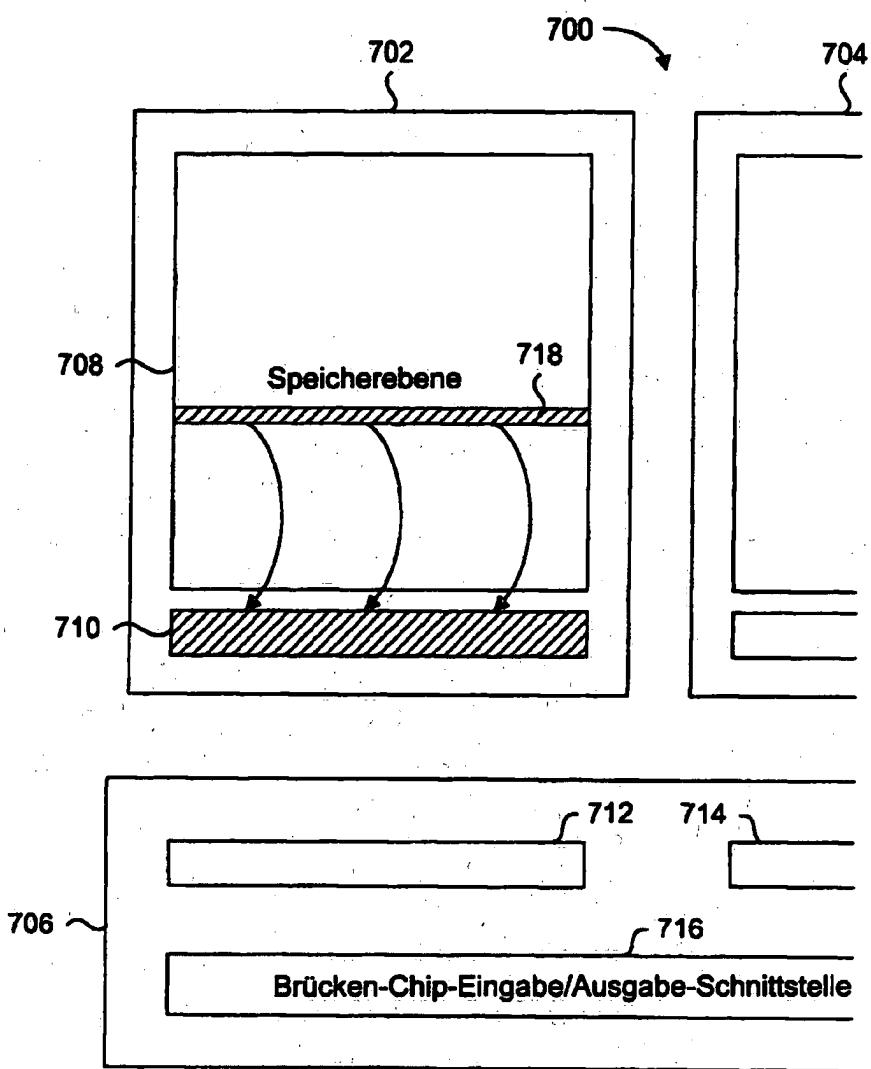

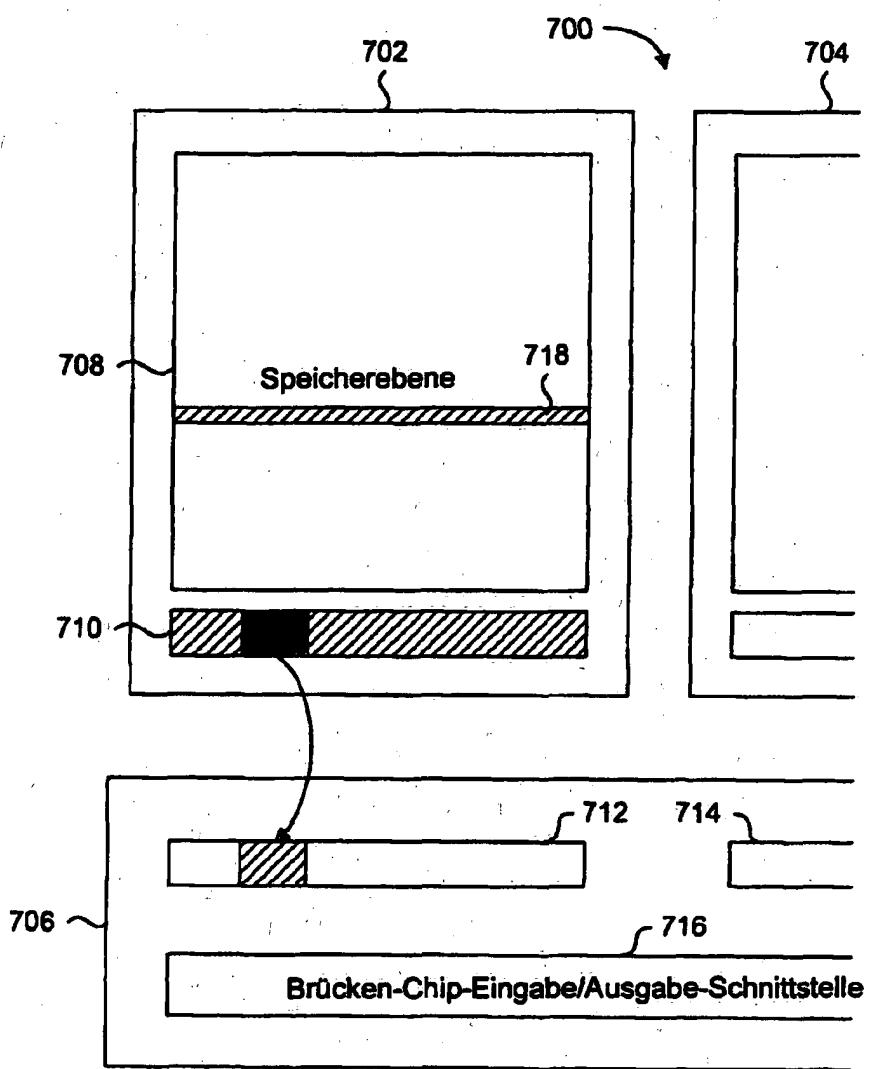

[0033] [Fig. 7](#) ein Blockdiagramm von einem Speichersystem mit einer Anzahl von Kompositsspeichervorrichtungen ist, die mit einer Steuerung in einem seriell angeschlossenen Speichersystem gemäß einem Ausführungsbeispiel verbunden sind;

[0034] [Fig. 8](#) ein Blockdiagramm ist, das das Speicher-Mapping der Brückenvorrichtung aus [Fig. 3A](#) zu NAND-Flash-Speichervorrichtungen gemäß einem vorliegenden Ausführungsbeispiel zeigt;

[0035] [Fig. 9A](#), [Fig. 9B](#) und [Fig. 9C](#) eine beispielhafte Leseoperation von einer NAND-Flash-Speichervorrichtung unter Verwendung der Brückenvorrichtung aus [Fig. 3A](#) zeigen;

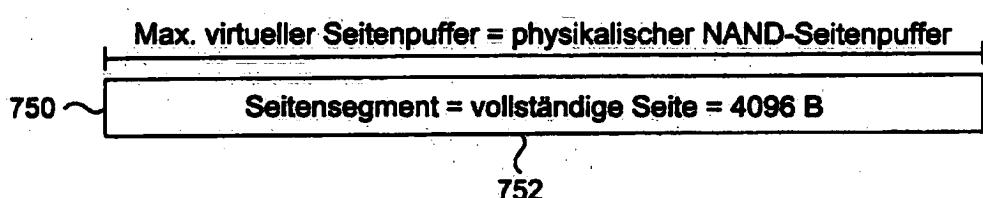

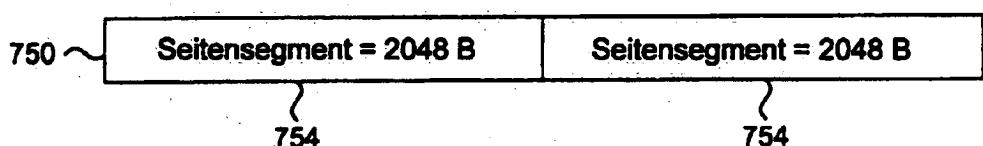

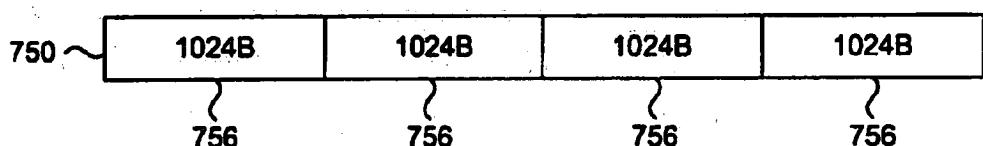

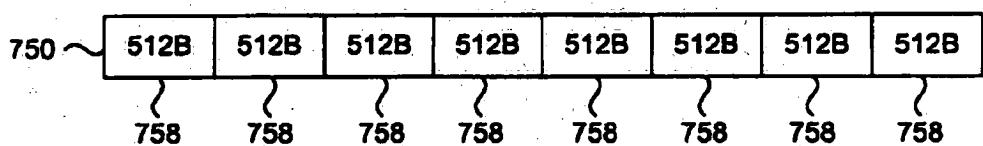

[0036] [Fig. 10A](#), [Fig. 10B](#), [Fig. 10C](#) und [Fig. 10D](#) beispielhafte virtuelle Seitenkonfigurationen für jede Speicherbank der Brückenvorrichtung aus [Fig. 3A](#) zeigen;

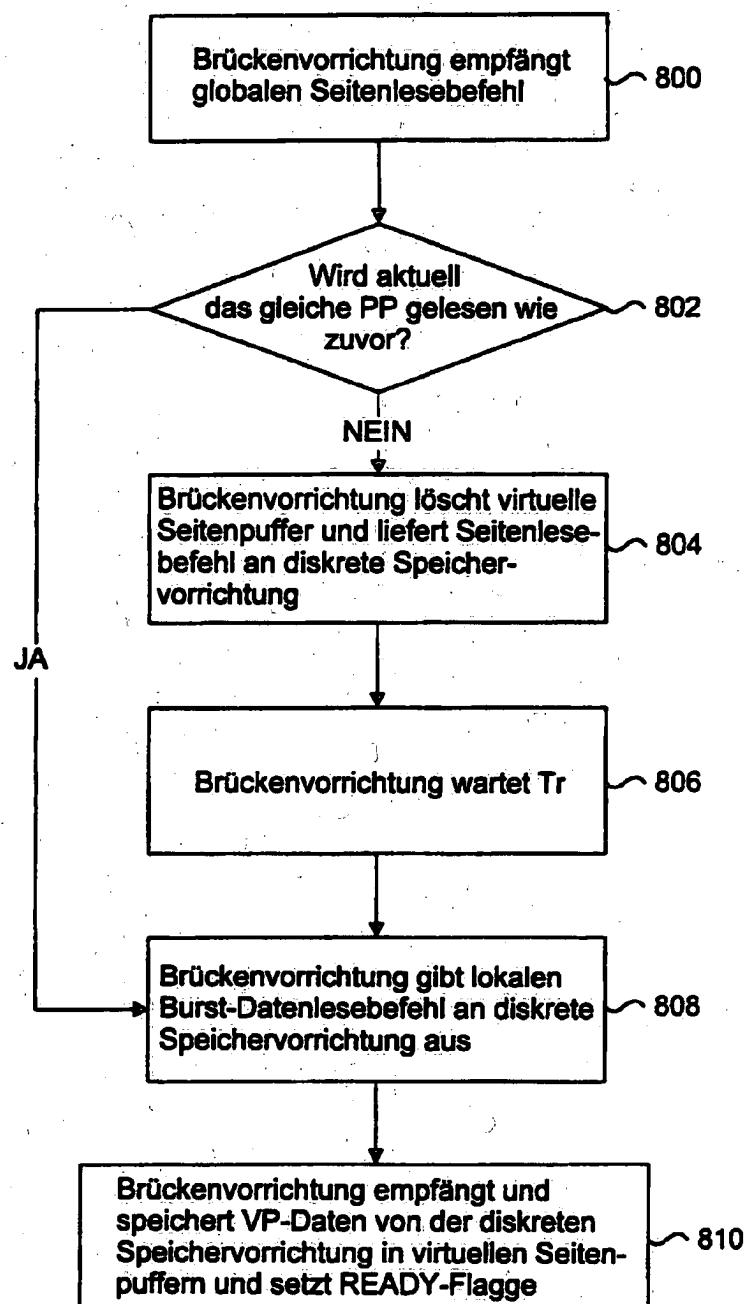

[0037] [Fig. 11](#) ein Flussdiagramm ist, das ein Verfahren zum Lesen von Daten von einer Kompositsspeichervorrichtung gemäß einem vorliegenden Ausführungsbeispiel zeigt; und

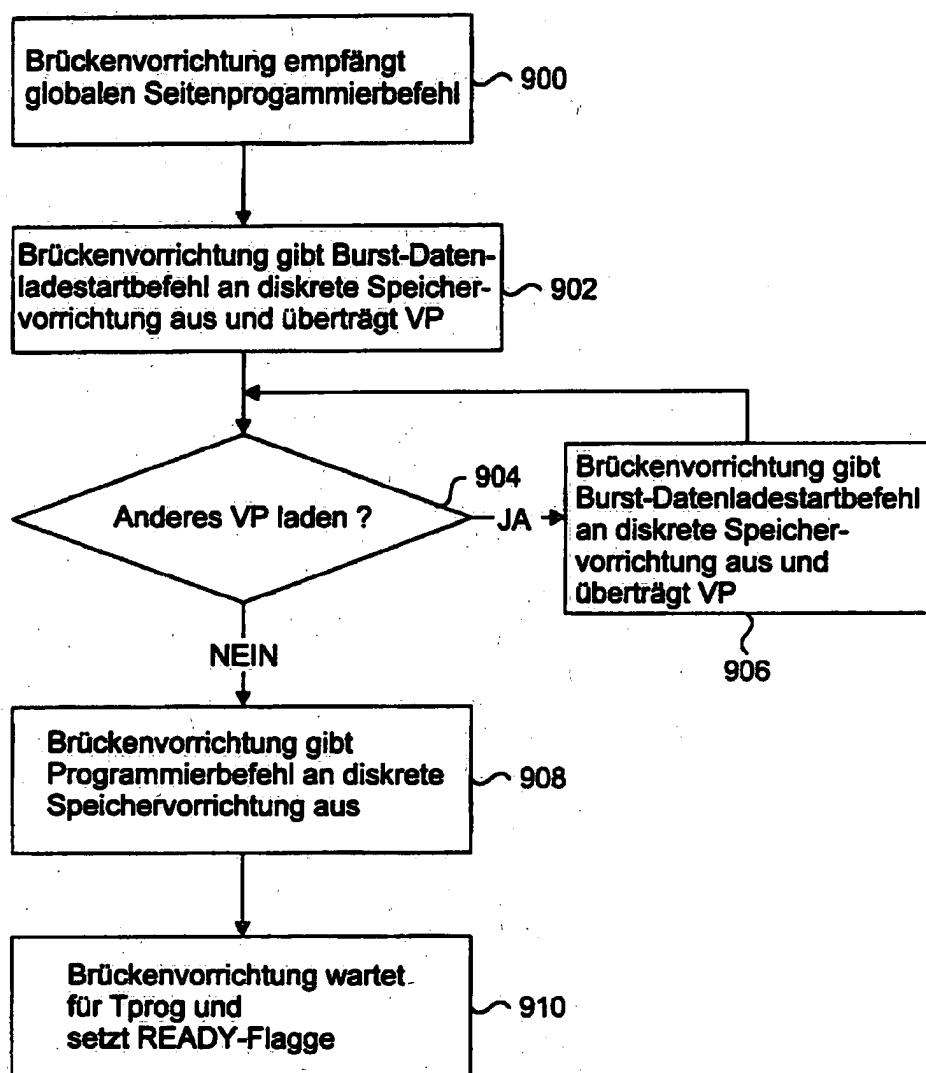

[0038] [Fig. 12](#) ein Flussdiagramm ist, das ein Verfahren zum Schreiben von Daten in eine Kompositsspeichervorrichtung gemäß einem vorliegenden Ausführungsbeispiel zeigt.

#### DETAILLIERTE BESCHREIBUNG

[0039] Die Ausführungsbeispiele der vorliegenden Erfindung sind allgemein auf eine Kompositsspeichervorrichtung gerichtet, die diskrete Speichervorrichtungen und eine Brückenvorrichtung enthält, um die diskreten Speichervorrichtungen in Reaktion auf globale, Speichersteuersignale zu steuern, die ein Format oder Protokoll haben, das mit dem der Speichervorrichtungen nicht kompatibel ist. Die diskreten Speichervorrichtungen können kommerzielle, serienmäßig produzierte Speichervorrichtungen oder kundenspezifische Speichervorrichtungen sein, die auf native oder lokale Speichersteuersignale ansprechen. Die globalen und lokalen Speichersteuersignale enthalten Befehle und Befehlssignale, die jeweils verschiedene Formate haben.

[0040] Gemäß einem Ausführungsbeispiel enthält die Brückenvorrichtung (oder der Chip) eine Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle, eine Formatkonvertierungsschaltung und eine Speichervorrichtungsschnittstelle. Die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle kommuniziert mit einer Speichersteuerung oder mit einer anderen Kompositsspeichervorrichtung in einem globalen Format. Die Formatkonvertierungsschaltung konvertiert globale Speichersteuersignale vom globalen Format in ein entsprechendes lokales Format, das mit den damit verbundenen diskreten Speichervorrichtungen kompatibel ist. Auf das globale Format folgen lediglich die globalen Speichersteuersignale, die von den Brückenvorrichtungen empfangen werden, während auf das lokale Format lediglich die lokalen Speichersteuersignale folgen, die von den diskreten Speichervorrichtungen verwendet werden. Folglich kommuniziert die Speichervorrichtungsschnittstelle mit jeder diskreten Speichervorrichtung, die mit der Brückenvorrichtung verbunden sind, in dem lokalen Format.

[0041] Das System und die Vorrichtung gemäß der hier beschriebenen Techniken können bei einem Speichersystem angewendet werden, das eine Mehrzahl von seriell verbundenen Vorrichtungen enthält. Die Vor-

richtungen sind beispielsweise Speichervorrichtungen, wie DRAMs (Dynamic Random Access Memories), SRAMs (Static Random Access Memories), Flash-Speicher, DiNOR-Flash EEPROM-Speicher, serielle Flash-EEPROM-Speicher, Ferro-RAM-Speicher, Magneto-RAM-Speicher, Phasenwechsel-RAM-Speicher und irgendein anderer geeigneter Typ von Speicher.

**[0042]** Es folgen Beschreibungen von zwei verschiedenen Speichervorrichtungen und Speichersystemen, um ein besseres Verständnis der nachfolgend beschriebenen Ausführungsbeispiele der Kompositsspeichervorrichtung und der Brückenvorrichtung zu erhalten.

**[0043]** [Fig. 1A](#) ist ein Blockdiagramm eines nicht-flüchtigen Speichersystems **10**, das mit einem Host-System **12** integriert ist. Das System **10** enthält eine Speichersteuerung **14** in Kommunikation mit dem Host-System **12** sowie eine Mehrzahl von nicht-flüchtigen Speichervorrichtungen **16-1**, **16-2**, **16-3** und **16-4**. Beispielsweise können die nicht-flüchtigen Speichervorrichtungen **16-1** bis **16-4** diskrete asynchrone Flash-Speichervorrichtungen sein. Das Host-System **12** enthält eine Verarbeitungsvorrichtung, wie zum Beispiel einen Mikrocontroller, einen Mikroprozessor oder ein Computersystem. Das System **10** aus [Fig. 1A](#) ist organisiert, um einen Kanal **18** aufzuweisen, wobei die Speichervorrichtung **16-1** bis **16-4** parallel mit dem Kanal **18** verbunden sind. Für den Fachmann ist offensichtlich, dass das System **10** mehr oder weniger als vier damit verbundene Speichervorrichtungen haben kann. In dem aktuell gezeigten Beispiel sind die Speichervorrichtungen **16-1** bis **16-4** asynchron und parallel miteinander verbunden.

**[0044]** Der Kanal **18** enthält einen Satz von gemeinsamen Bussen, die Daten und Steuerleitungen enthalten, die mit allen ihren zugehörigen Speichervorrichtungen verbunden sind. Jede Speichervorrichtung wird durch jeweilige Chip-Auswahlsignale (Chip Enable Signals) CE1#, CE2#, CE3# und CE4# aktiviert oder deaktiviert, die durch die Speichersteuerung **14** geliefert werden. In diesem und in nachfolgenden Beispielen gibt "#" an, dass das Signal ein aktives LOW-Level-Logiksignal ist. In diesem Schema ist zu einem Zeitpunkt normalerweise eines der Chip-Auswahlsignale ausgewählt, um eine zugehörige Speichervorrichtung der nicht-flüchtigen Speichervorrichtungen **16-1** bis **16-4** zu aktivieren. Die Speichersteuerung **14** ist verantwortlich für die Ausgabe von Befehlen und Daten über den Kanal **18** zu einer ausgewählten Speichervorrichtung in Reaktion auf die Operation des Host-Systems **12**. Die von den Speichervorrichtungen ausgegebenen Lesedaten werden über den Kanal **18** zurück zur Speichersteuerung **14** und zum Host-System **12** übertragen. Das System **10** enthält allgemein einen Bus mit mehreren Abzweigungen (Multi-Drop-Bus), wobei die Speichervorrichtungen **16-1** bis **16-4** parallel mit dem Kanal **18** verbunden sind.

**[0045]** [Fig. 1B](#) ist eine Darstellung von einer der diskreten Flash-Speichervorrichtungen **16-1** bis **16-4**, die in dem Speichersystem aus [Fig. 1A](#) verwendet werden können. Diese Flash-Speichervorrichtung hat mehrere Eingabe- und Ausgabe-Ports, die beispielsweise Stromversorgungs-Ports, Steuer-Ports und Daten-Ports umfassen. Der Begriff "Port" bezieht sich auf generische Eingabe- oder Ausgabeanschlüsse in der Speichervorrichtung, die zum Beispiel Gehäusestifte, Gehäuselötpunkte, Chip-Bondpads sowie drahtlose Sender und Empfänger umfassen. Die Stromversorgungs-Ports umfassen VCC und VSS, um Energie an alle Schaltungen der Flash-Speichervorrichtung zu liefern. Es können weitere Stromversorgungs-Ports vorgesehen sein, um nur die Eingabe- und Ausgabepuffer zu speisen, was in der Technik bekannt ist. Die nachfolgende Tabelle 1 zeigt eine Auflistung der Steuer- und Daten-Ports sowie ihre zugehörigen Beschreibungen, Definitionen und beispielhaften Logikzustände. Es sei angemerkt, dass die Gehäusestifte und Kugelgitter-Arrays physikalische Beispiele von Ports sind, die verwendet werden, um Signale oder Spannungen von einer gepackten Vorrichtung mit einer Platine zu koppeln. Diese Ports können andere Typen von Verbindungen umfassen, wie zum Beispiel Anschlüsse und Kontakte für eingebettete Systeme und System-In-Package-Systeme (SIP-Systeme).

Tabelle 1

| Port | Beschreibung                                                                                                                                                                                                                                                                                                                              |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| R/B# | Ready/Busy: R/B# ist ein Open-Drain-Port, und das Ausgabesignal wird verwendet, um die Operationsbedingung der Vorrichtung anzugeben. Das R/B#-Signal befindet sich während der Programmier-, Lösch- und Lese-Operationen im Busy-Zustand (R/B# = LOW) und kehrt nach Beendigung der Operation in den Ready-Zustand (R/B# = HIGH) zurück. |

|        |                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE#    | Chip-Enable: die Vorrichtung geht in einen LowPower-Standby-Modus, wenn CE# auf HIGH geht, während sich die Vorrichtung im Ready-Zustand befindet. Das CE#-Signal wird ignoriert, wenn sich die Vorrichtung im Busy-Zustand (R/B# = LOW) befindet, wie zum Beispiel während einer Programmier- oder Lösch- oder Lese-Operation, und geht nicht in den Standby-Modus, auch wenn der CE#-Eingang auf HIGH geht. |

| CLE    | Command-Latch-Enable: das CLE-Eingabesignal wird verwendet, um das Laden des Operationsmodusbefehls in das interne Befehlsregister zu steuern. Der Befehl wird bei der ansteigenden Flanke des WE#-Signals im Befehlsregister von dem I/O-Port verriegelt, während CLE HIGH ist.                                                                                                                              |

| ALE    | Adress-Latch-Enable (ALE): das ALE-Signal wird verwendet, um das Laden von Adressinformationen in das interne Adressregister zu steuern. Adressinformationen werden bei der ansteigenden Flanke des WE# Signals im Adressregister von dem I/O-Port verriegelt, während ALE HIGH ist.                                                                                                                          |

| WE#    | Write-Enable: das WE#-Signal wird verwendet, um die Gewinnung von Daten von dem I/O-Port zu steuern.                                                                                                                                                                                                                                                                                                          |

| RE#    | Read-Enable: das RE-Signal steuert die serielle Datenausgabe. Die Daten sind nach der abfallenden Flanke von RE# verfügbar.                                                                                                                                                                                                                                                                                   |

| WP#    | Write-Protect: das WP# Signal wird verwendet, um die Vorrichtung gegen unbeabsichtigtes Programmieren oder Löschen zu schützen. Der interne Spannungsregler (Hochspannungsgenerator) wird zurückgesetzt, wenn WP# LOW ist. Das Signal wird normalerweise verwendet, um die Daten während der Energie-EIN/AUS-Sequenz zu schützen, wenn die Eingabesignale ungültig sind.                                      |

| I/O[n] | I/O-Port: werden als ein Port zum Übertragen von Adressen, Befehlen und Eingabe/Ausgabe-Daten von und zu der Vorrichtung verwendet. Die Variable n kann ein Integer-Wert von ungleich Null sein.                                                                                                                                                                                                              |

**[0046]** Alle Signale, die in Tabelle 1 aufgeführt sind, werden allgemein als die Speichersteuersignale zum Betreiben der in [Fig. 1B](#) dargestellten beispielhaften Flash-Speichervorrichtung bezeichnet. Es sei angemerkt, dass der letzte Port I/O[n] als ein Speichersteuersignal betrachtet wird, da er Befehle empfangen kann, die die Flash-Speichervorrichtung instruieren, spezifische Operationen durchzuführen. Da ein Befehl, der an Port I/O [n] anliegt, eine Kombination von logischen Zuständen ist, die auf jede einzelne Leitung angewendet werden, die I/O[n] ausmachen, wirkt der logische Zustand jedes Signals von I/O[n] in der gleichen Weise wie, eines der anderen Speichersteuersignale, wie zum Beispiel WP#. Der wesentliche Unterschied besteht darin, dass eine spezielle Kombination von logischen Zuständen I/O[n] die Flash-Speichervorrichtung steuert, um eine Funktion durchzuführen. Die Befehle werden über ihre I/O-Ports empfangen, und die Befehlssignale umfassen die übrigen Steuer-Ports. Für den Fachmann ist offensichtlich, dass in dem Befehl Operations-Codes (OpCodes) zur Verfügung gestellt werden, um spezifische Speicheroperationen durchzuführen. Mit Ausnahme des Chip-Enable CE# sind alle anderen Ports mit jeweiligen globalen Leitungen gekoppelt, die den Kanal 18 ausmachen. Einzelne Chip-Auswahlsignale werden durch die Speichersteuerung 14 an jede Flash-Speichervorrichtung geliefert. Alle Ports werden in einer vorbestimmten Weise gesteuert, um Speicheroperationen durchzuführen. Dies umfasst Signal-Timing und Sequenzieren von spezifischen Steuersignalen, während Adressen, Befehle und I/O-Daten an den I/O-Ports bereitgestellt werden. Daher haben die Speichersteuersignale zum Steuern der asynchronen Flash-Speichervorrichtung aus [Fig. 1B](#) ein spezielles Format oder Protokoll.

**[0047]** Jede der nicht-flüchtigen Speichervorrichtungen aus [Fig. 1A](#) hat eine spezifische Datenschnittstelle zum Empfangen und Liefern von Daten. In dem Beispiel aus [Fig. 1A](#) ist dies eine parallele Datenschnittstelle, die allgemein in asynchronen Flash-Speichervorrichtungen verwendet wird. Parallel Standard-Datenschnittstellen, die parallel mehrere Datenbits liefern, haben den bekannten Nachteil, dass sie unter Effekten einer Kommunikationsverschlechterung leiden, wie zum Beispiel Gegensprechen, Signalverschiebung und Signalabschwächung, wodurch sich die Signalqualität verschlechtert, wenn sie jenseits ihrer Nennbetriebsfrequenz betrieben werden.

**[0048]** Um den Datendurchsatz zu erhöhen, ist eine Speichervorrichtung mit einer seriellen Datenschnittstelle in der U.S. Patent Application Nr. 20070153576 mit dem Titel "Memory with Output Control" und in der U.S. Patent Application Nr. 20070076502 mit dem Titel "Daisy Chain Cascading Devices" offenbart, die Daten mit einer Frequenz von beispielsweise 200 MHz seriell empfängt und liefert. Dies wird als ein serielles Datenschnittstel-

lenformat bezeichnet. Wie in diesen Patent Applications offenbart, kann die beschriebene Speichervorrichtung in einem System von Speichervorrichtungen verwendet werden, die seriell miteinander verbunden sind.

**[0049]** [Fig. 2A](#) ist ein Blockdiagramm, das die konzeptionelle Struktur eines seriellen Speichersystems darstellt. In [Fig. 2A](#) enthält das serielle Speichersystem **20** mit Ringtopologie eine Speichersteuerung **22** mit einem Satz von Ausgabe-Ports  $S_{out}$  und einem Satz von Eingabe-Ports  $S_{in}$  sowie Speichervorrichtungen **24, 26, 28** und **30**, die in Serie verbunden sind. Die Speichervorrichtungen können beispielsweise serielle Schnittstellen-Flash-Speichervorrichtungen sein. Obwohl in [Fig. 2A](#) nicht gezeigt, hat jede Speichervorrichtung einen Satz von Eingabe-Ports  $S_{in}$  und einen Satz von Ausgabe-Ports  $S_{out}$ . Diese Sätze von Eingabe- und Ausgabe-Ports enthalten einen oder mehrere individuelle Eingabe/Ausgabe-Ports, wie zum Beispiel physikalische Stifte oder Verbindungen, wodurch die Speichervorrichtung mit dem System als ein Teil davon gekoppelt ist. Bei einem Beispiel können die Speichervorrichtungen Flash-Speichervorrichtungen sein. Alternativ können die Speichervorrichtungen DRAM, SRAM, DiNOR-Flash-EEPROM, serielle Flash-EEPROM, Ferro-RAM, Magneto-RAM, Phasenwechsel-RAM oder irgendein anderer geeigneter Typ von Speichervorrichtungen sein, die eine Eingabe/Ausgabeschnittstelle haben, die mit einer spezifischen Befehlsstruktur kompatibel ist, um Befehle durchzuführen oder um Befehle und Daten zur nächsten Speichervorrichtung durchzuleiten. Das aktuelle Beispiel aus [Fig. 2A](#) enthält vier Speichervorrichtungen, jedoch können alternative Konfigurationen auch eine einzelne Speichervorrichtung oder eine geeignete Anzahl von Speichervorrichtungen enthalten. Wenn folglich die Speichervorrichtung **24** die erste Vorrichtung des Systems **20** ist, da sie mit  $S_{out}$  verbunden ist, dann ist die Speichervorrichtung **30** die N-te oder letzte Vorrichtung, da sie mit  $S_{in}$  verbunden ist, wobei N eine Integerzahl größer Null ist. Die Speichervorrichtungen **26** bis **28** sind dann seriell verbundene Speichervorrichtungen zwischen der ersten und der letzten Speichervorrichtung. In dem Beispiel aus [Fig. 2A](#) sind die Speichervorrichtungen **24** bis **30** synchron und in Serie miteinander sowie mit der Speichersteuerung **22** verbunden.

**[0050]** [Fig. 2B](#) ist eine Darstellung der seriellen Schnittstellen-Flash-Speichervorrichtung (zum Beispiel 24 bis 30), die in dem Speichersystem aus [Fig. 2A](#) verwendet werden kann. Diese beispielhafte serielle Schnittstellen-Flash-Speichervorrichtung hat Stromversorgungs-Ports, Steuer-Ports und Daten-Ports. Die Stromversorgungs-Ports enthalten VCC und VSS, um allen Schaltungen der Flash-Speichervorrichtung Energie zuzuführen. Es können zusätzliche Stromversorgungs-Ports vorgesehen sein, um nur die Eingabe- und Ausgabepuffer mit Energie zu versorgen, was in der Technik allgemein bekannt ist. Die nachfolgende Tabelle 2 enthält eine Auflistung der Steuer- und Daten-Ports, deren zugehörigen Beschreibungen und beispielhafte logische Zustände.

Tabelle 2

| Port   | Beschreibung                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK/CK# | Clock: CK ist die System-Takteingabe. CK und CK# sind unterschiedliche Takteingaben. Alle Befehle, Adressen, Eingabedaten und Ausgabedaten beziehen sich auf die sich kreuzenden Flanken von CK und CK# in beiden Richtungen.                                                                                                                                                                                                                                                                                  |

| CE#    | Chip-Enable: Wenn CE# LOW ist, wird die Vorrichtung aktiviert. Wenn die Vorrichtung eine Programmier- oder Löschoperation startet, kann der Chip-Enable-Port rückgesetzt werden. Außerdem werden die internen Taktsignale bei CE# LOW aktiviert und bei CE# HIGH deaktiviert.                                                                                                                                                                                                                                  |

| RST#   | Chip-Reset: RST# liefert einen Reset für die Vorrichtung. Wenn RST# HIGH ist, befindet sich die Vorrichtung im normalen Betriebsmodus. Wenn RST# LOW ist, geht die Vorrichtung in den Reset-Modus.                                                                                                                                                                                                                                                                                                             |

| D[n]   | Daten-Eingabe ( $n = 1, 2, 3, 4, 5, 6, 7$ oder $8$ ) empfängt Befehls-, Adress- und Eingabedaten. Wenn die Vorrichtung im '1-Bit-Link-Modus (= default)' konfiguriert ist, dann ist D1 das einzige gültige Signal und empfängt ein Byte eines Pakets an 8 Schnittpunkten von CK/CK#. Wenn die Vorrichtung im '2-Bit-Link-Modus' konfiguriert ist, dann sind D1 und D2 die einzigen gültigen Signale und empfangen ein Byte eines Pakets an 4 Schnittpunkten von CK/CK#. Unbenutzte Eingabe-Ports sind geerdet. |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Q[n] | Daten-Ausgabe: (n = 1, 2, 3, 4, 5, 6, 7 oder 8) überträgt Ausgabedaten während der Leseoperation. Wenn die Vorrichtung im '1-Bit-Link-Modus (= default)' konfiguriert ist, ist Q1 das einzige gültige Signal und überträgt ein Byte eines Pakets an 8 Schnittpunkten von CK/CK#. Wenn die Vorrichtung im '2-Bit-Link-Modus' konfiguriert ist, sind Q1 und Q2 die einzigen gültigen Signale und übertragen ein Byte eines Pakets an 4 Schnittpunkten von CK/CK#. Unbenutzte Ausgabe-Ports sind DNC (Do Not Connect). |

| CSI  | Command Strobe Input: Wenn CSI HIGH ist, werden Befehls-, Adress- und Eingabedaten durch D[n] an den Schnittpunkten von CK und CK# verriegelt. Wenn CSI LOW ist, ignoriert die Vorrichtung Eingabesignale von D[n].                                                                                                                                                                                                                                                                                                 |

| CSO  | Command Strobe Output: Das Echo-Signal CSO ist eine zurück übertragene Version des Quellensignals CSI.                                                                                                                                                                                                                                                                                                                                                                                                              |

| DSI  | Data Strobe Input: Aktiviert den Q[n]-Puffer wenn es HIGH ist. Wenn DSI LOW ist, hält der Q[n]-Puffer die Daten, auf die zuvor zugegriffen wurde.                                                                                                                                                                                                                                                                                                                                                                   |

| DSO  | Data Strobe Output: Das Echo-Signal DSO ist eine zurück übertragene Version des Quellensignals DSI.                                                                                                                                                                                                                                                                                                                                                                                                                 |

**[0051]** Mit Ausnahme der Signale CSO, DSO und Q[n] sind alle in Tabelle 2 aufgelisteten Signale die Speichersteuersignale zum Betreiben der in [Fig. 2B](#) dargestellten beispielhaften Flash-Speichervorrichtung. CSO und DSO sind zurück übertragene Versionen von CSI und DSI, und Q[n] ist eine Ausgabe, um Befehle und Daten zur Verfügung zu stellen. Die Befehle werden über ihre D[n]-Ports empfangen, und die Befehlssignale umfassen die Steuer-Ports RST#, CE#, CK, CK#, CSI und DSI. In der in [Fig. 2A](#) gezeigten beispielhaften Konfiguration werden alle Signale seriell von der Speichersteuerung **22** zu jeder seriellen Speichervorrichtung geleitet, mit Ausnahme von CE# und RST#, die allen Speichervorrichtungen parallel zugeführt werden. Die serielle Schnittstellen-Flash-Speichervorrichtung aus [Fig. 2B](#) empfängt daher Speichersteuersignal, die ihr eigenes Format oder Protokoll haben, um darin Speicheroperationen durchzuführen.

**[0052]** Weitere Details des seriell gekoppelten Speichersystems aus [Fig. 2](#) sind in der U.S. Patent Publication Nr. 20090039927 mit dem Titel "Clock Mode Determination in a Memory System" offenbart, die am 15. Februar 2008 angemeldet wurde und ein serielles Speichersystem, bei dem jede Speichervorrichtung ein paralleles Taktsignal empfängt, und ein serielles Speichersystem beschreibt, bei dem jede Speichervorrichtung ein synchrones Quellentaktsignal empfängt.

**[0053]** Mit sowohl den allgemein verfügbaren asynchronen Flash-Speichervorrichtungen aus [Fig. 1B](#) als auch mit den seriellen Schnittstellen-Flash-Speichervorrichtungen aus [Fig. 2B](#) wird es einem Speichersystemhersteller ermöglicht, beide Typen von Speichersystemen zur Verfügung zu stellen. Dies führt jedoch vermutlich zu höheren Kosten für den Speichersystemhersteller, da zwei verschiedene Typen von Speichervorrichtungen hergestellt und verkauft werden müssen. Für den Fachmann ist offensichtlich, dass der Preis pro Speichervorrichtung sinkt, wenn große Mengen verkauft werden können, um die Kosten des Speichersystems zu minimieren. Obwohl ein Hersteller beide Typen von Speichersystemen liefern kann, trägt er das Risiko, dass ein Typ von Speichervorrichtung aus dem Markt fällt, wenn die Nachfrage des Marktes für den anderen Typ ansteigt. Dies kann dazu führen, dass Speichervorrichtungen zum Verkauf stehen, die nicht benutzt werden können.

**[0054]** Wie in [Fig. 1B](#) und in [Fig. 2B](#) gezeigt, sind die funktionalen Zuweisungen oder Definitionen der Ports der asynchronen und seriellen Schnittstellen-Flash-Speichervorrichtungen im Wesentlichen verschieden voneinander und daher nicht kompatibel zueinander. Die funktionalen Port-Definitionen und Sequenzen oder das Timing von Signalsätzen, die für die Steuerung von diskreten Speichervorrichtungen verwendet werden, werden als Protokoll oder Format bezeichnet. Daher arbeiten die asynchronen und seriellen Flash-Speichervorrichtungen auf Basis verschiedener Speichersteuersignalformate. Das bedeutet, dass die serielle Schnittstellen-Flash-Speichervorrichtung aus [Fig. 2B](#) nicht in einem Speichersystem verwendet werden kann, das mehrere Abzweigungen hat, und folglich kann die asynchrone Flash-Speichervorrichtung aus [Fig. 1B](#) nicht in einem seriell gekoppelten Speichersystem mit Ringtopologie verwendet werden.

**[0055]** Obwohl serielle Schnittstellen-Flash-Speichersysteme, wie sie in [Fig. 2A](#) und in [Fig. 2B](#) gezeigt sind, aufgrund ihrer besseren Leistungsfähigkeit im Vergleich zu asynchronen Flash-Speichervorrichtungen aus [Fig. 1A](#) und [Fig. 1B](#) bevorzugt sind, können es Speichersystemhersteller nicht wollen, ihre eigenen Vorräte an asynchronen Flash-Speichervorrichtungen zu verkaufen. Aufgrund ihrer allgegenwärtigen Verwendung in der Industrie sind asynchrone Flash-Speichervorrichtungen preiswert zu kaufen im Vergleich zu weniger bekannt-

ten alternativen Flash-Speichervorrichtungen, wie zum Beispiel die seriellen Schnittstellen-Flash-Speichervorrichtung aus [Fig. 2A](#). Derzeit haben Speichersystemhersteller keine Lösung, um die Vorteile der besseren Leistungsfähigkeit von seriell verbundenen Vorrichtungen mit minimalem Kostenüberhang zu nutzen.

**[0056]** Durch zumindest einige beispielhafte Ausführungsbeispiele wird eine Kompositsspeichervorrichtung mit hoher Leistungsfähigkeit zur Verfügung gestellt, die einen Hochgeschwindigkeits-Schnittstellen-Chip oder eine Brückenvorrichtung zusammen mit diskreten Speichervorrichtungen in einem Multi-Chip-Gehäuse (MCP) oder System-In-Package (SIP) enthält. Die Brückenvorrichtung hat eine I/O-Schnittstelle, wobei das System darin integriert ist, und empfängt globale Speichersteuersignale, die einem globalen Format folgen, und konvertiert die Befehle in lokale Speichersteuersignale, die einem nativen oder lokalen Format folgen, das mit den diskreten Speichervorrichtungen kompatibel ist. Die Brückenvorrichtung ermöglicht daher die Wiederverwendung von diskreten Speichervorrichtungen, wie zum Beispiel NAND-Flash-Vorrichtungen, während die Leistungsvorteile erreicht werden, die durch die I/O-Schnittstelle der Brückenvorrichtung geboten werden. Die Brückenvorrichtung kann als ein diskreter Logik-Chip verkörpert sein, der in dem Gehäuse mit diskreten Speichervorrichtungs Chips integriert ist.

**[0057]** In den vorliegenden Beispielen ist das globale Format ein serielles Datenformat, das mit der seriellen Flash-Speichervorrichtung aus [Fig. 2A](#) und [Fig. 2B](#) kompatibel ist, und das lokale Format ist eine paralleles Datenformat, das mit der asynchronen Flash-Speichervorrichtung aus [Fig. 1A](#) und [Fig. 2B](#) kompatibel ist. Jedoch sind die Ausführungsbeispiele der vorliegenden Erfindung nicht auf die obigen beispielhaften Formate beschränkt, da irgendein Paar von Speichersteuersignalformaten verwendet werden kann, und zwar abhängig vom Typ der diskreten Speichervorrichtungen, die in der Kompositsspeichervorrichtung verwendet werden, und vom Typ des Speichersystems, in dem die Kompositsspeichervorrichtung verwendet wird. Beispielsweise kann das globale Format des Speichersystems dem Open-NAND-Flash-Schnittstellen-Standard (ONFi) folgen, und das lokale Format kann dem asynchronen Flash-Speichervorrichtungs-Speichersteuersignalformat folgen. Zum Beispiel ist ein spezieller ONFi-Standard die ONFi 2.0 Spezifikation. Alternativ kann das globale Format dem asynchronen Flash-Speichervorrichtungs-Speichersteuersignalformat folgen, und das lokale Format kann dem ONFi 2.0 Spezifikationsformat folgen. Allgemein ist die ONFi-Spezifikation ein synchrones Protokoll mit mehreren Abzweigungen, wobei Daten und Formate der entsprechenden Speichervorrichtung über ihre Daten-Eingabe/Ausgabe-Ports synchron mit einem Takt zur Verfügung gestellt werden. Mit anderen Worten, eine ONFi-kompatible Speichervorrichtung kann gewisse Ähnlichkeiten mit einer asynchronen NAND-Flash-Speichervorrichtung haben, die parallele bidirektionale Eingabe/Ausgabe-Ports hat, wobei ein wichtiger Unterschied darin besteht, dass die ONFi-kompatible Vorrichtung ein Taktsignal empfängt.

**[0058]** [Fig. 3A](#) ist ein Blockdiagramm von einer Kompositsspeichervorrichtung gemäß einem vorliegenden Ausführungsbeispiel. Wie in [Fig. 3A](#) gezeigt, enthält die Kompositsspeichervorrichtung **100** eine Brückenvorrichtung **102**, die mit vier diskreten Speichervorrichtungen **104** verbunden ist. Jede der diskreten Speichervorrichtungen **104** können asynchrone Flash-Speichervorrichtungen mit einer Speicherkapazität von beispielsweise 8 GB sein, anstelle der 8 GB-Vorrichtungen kann jedoch eine diskrete Flash-Speichervorrichtung mit irgend-einer Kapazität verwendet werden. Außerdem ist die Kompositsspeichervorrichtung **100** nicht auf die Verwendung mit vier diskreten Speichervorrichtungen beschränkt. Es kann irgendeine geeignete Anzahl von diskreten Speichervorrichtungen enthalten sein, sofern die Brückenvorrichtung **102** ausgestaltet ist, um die maximale Anzahl von diskreten Speichervorrichtungen in der Kompositsspeichervorrichtung **100** aufzunehmen.

**[0059]** Die Kompositsspeichervorrichtung **100** hat einen Eingabe-Port GLBCMD\_IN zum Empfangen eines globalen Befehls und einen Ausgabe-Port GLBCMD\_OUT zum Durchlassen des empfangenen globalen Befehls und der gelesenen Daten. [Fig. 3B](#) ist ein Schema, das die Hierarchie eines globalen Befehls gemäß einem vorliegenden Ausführungsbeispiel darstellt. Der globale Befehl **110** enthält globale Speichersteuersignale (GMCS) **112**, die ein spezifisches Format haben, und einen Adresskopf (AH) **114**. Diese globalen Speichersteuersignale **112** liefern einen Speicherbefehl und Befehlssignale, wie zum Beispiel die Speichersteuersignale für die serielle Schnittstellen-Flash-Speichervorrichtung aus [Fig. 2B](#). Der Adresskopf **114** enthält Adressinformationen, die auf Systemebene und auf Ebene der Kompositsspeichervorrichtung verwendet werden. Diese zusätzlichen Adressinformationen enthalten eine globale Vorrichtungsadresse (GDA) **116** zum Auswählen einer Kompositsspeichervorrichtung, um einen OpCode in dem Speicherbefehl durchzuführen, und eine lokale Vorrichtungsadresse (LDA) **118** zum Auswählen einer bestimmten diskreten Vorrichtung in der ausgewählten Kompositsspeichervorrichtung, um den OpCode durchzuführen. Zusammenfassend enthält der globale Befehl alle Speichersteuersignale, die einem Format entsprechen, sowie weitere Adressinformationen, die erforderlich sein können, um die Kompositsspeichervorrichtung oder die diskreten Speichervorrichtungen darin auszuwählen oder zu steuern.

**[0060]** Es sei angemerkt, dass die Brückenvorrichtung **102** nicht den OpCode durchführt oder auf irgendeine Speicherstelle mit der Zeilen- und Adressinformation zugreift. Die Brückenvorrichtung **102** verwendet die globale Vorrichtungsadresse **116**, um zu bestimmen, ob sie ausgewählt wurde, um die empfangenen globalen Speichersteuersignale **112** zu konvertieren. Wenn sie ausgewählt ist, dann verwendet die Brückenvorrichtung **102** die lokale Vorrichtungsadresse **118**, um zu bestimmen, an welche der diskreten Speichervorrichtungen die konvertierten globalen Speichersteuersignale **112** gesendet werden. Um mit allen vier diskreten Speichervorrichtungen **104** zu kommunizieren, enthält die Brückenvorrichtung **102** vier Sätze von lokalen I/O-Ports (nicht gezeigt), die jeweils mit einer zugehörigen diskreten Speichervorrichtung verbunden sind, wie später erläutert wird. Jeder Satz von lokalen I/O-Ports beinhaltet all die Signale, die die diskrete Speichervorrichtung benötigt, um korrekt zu arbeiten, und funktioniert somit als eine lokale Vorrichtungsschnittstelle.

**[0061]** Lesedaten werden durch eine der Flash-Speichervorrichtungen **104** von der Kompositsspeichervorrichtung **100** oder von einer vorhergehenden Kompositsspeichervorrichtung zur Verfügung gestellt insbesondere kann die Brückenvorrichtung **102** mit einer Speichersteuerung eines Speichersystems oder mit einer anderen Brückenvorrichtung von einer anderen Kompositsspeichervorrichtung in einem System von seriell gekoppelten Vorrichtungen verbunden sein. Der Eingabe-Port GLBCMD\_IN und der Ausgabe-Port GLBCMD\_OUT können gepackte Stifte oder andere physikalische Leiter oder irgendwelche anderen Schaltungen sein, um die globalen Befehlssignale und Lesedaten zu und von der Kompositsspeichervorrichtung **100**, und insbesondere zu und von der Brückenvorrichtung **102**, zu senden bzw. zu empfangen. Die Brückenvorrichtung **102** weist daher entsprechende Verbindungen zum Eingabe-Port GLBCMD\_IN und zum Ausgabe-Port GLBCMD\_OUT auf, um eine Kommunikation mit einer externen Steuerung, wie zum Beispiel der Speichersteuerung **22** aus [Fig. 2A](#), oder mit den Brückenvorrichtungen von anderen Kompositsspeichervorrichtungen in dem System zu ermöglichen. Wie in dem Ausführungsbeispiel aus [Fig. 7](#) gezeigt, können viele Kompositsspeichervorrichtungen seriell miteinander verbunden sein.

**[0062]** [Fig. 4](#) ist ein Blockdiagramm von einer Brückenvorrichtung **200** gemäß einem Ausführungsbeispiel, das der in [Fig. 3A](#) gezeigten Brückenvorrichtung **102** entspricht. Die Brückenvorrichtung **200** enthält eine Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202**, eine Speichervorrichtungsschnittstelle **204** und einen Formatwandler **206**. Der Formatwandler **206** beinhaltet einen Befehlsformatwandler **208**, um globaler Speichersteuersignale, die globale Befehle und globale Befehlssignale enthalten, von einem ersten Format in ein zweites Format zu konvertieren, und einen Datenformatwandler **210**, um Daten zwischen dem ersten Format und dem zweiten Format zu konvertieren. Der Befehlsformatwandler **208** enthält ferner eine Zustandsmaschine (nicht gezeigt), um die diskreten Speichervorrichtungen, wie zum Beispiel die diskreten Speichervorrichtungen **104** aus [Fig. 3A](#), gemäß dem zweiten Format in Reaktion auf die globalen Speichersteuersignale in dem ersten Format zu steuern.

**[0063]** Die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** kommuniziert mit externen Vorrichtungen, beispielsweise mit einer Speichersteuerung oder mit einer anderen Kompositsspeichervorrichtungen. Die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** empfängt globale Befehle von einer Speichersteuerung oder einer anderen Kompositsspeichervorrichtung in dem globalen Format, wie zum Beispiel in einem seriellen Befehlsformat. Unter weiterer Bezugnahme auf [Fig. 3B](#) verarbeitet die Logik in der Eingabe/Ausgabe-Schnittstelle **202** die globale Vorrichtungsadresse **116** des globalen Befehls **110**, um zu bestimmen, ob der globale Befehl **110** die entsprechende Kompositsspeichervorrichtung adressiert, und verarbeitet die lokale Vorrichtungsadresse **118** in dem globalen Befehl **110**, um zu bestimmen, welche der diskreten Speichervorrichtungen der zugehörigen Kompositsspeichervorrichtung den konvertierten Befehl empfangen soll, der einen OpCode sowie optionale Zeilen- und Spalten-Adressen sowie optionale Schreibdaten enthält. Wenn der globale Befehl an eine diskrete Speichervorrichtung adressiert ist, die mit der Brückenvorrichtung **200** verbunden ist, dann konvertiert der Befehlsformatwandler **208** in dem Formatwandler **206** die globalen Speichersteuersignale **112**, die den OpCode und Befehlssignale sowie Zeilen- und Adressinformationen enthalten, von dem globalen Format in das lokale Format und liefert sie zur Speichervorrichtungsschnittstelle **204**. Dieser konvertierte lokale Befehl enthält lokale Signale, die funktional den globalen Signalen des globalen Formats entsprechen. In einigen Fällen können mehrere lokale Befehle in Reaktion auf einen einzigen globalen Befehl ausgegeben werden, da mehrere lokale Befehle erforderlich sein können, um die Operation des globalen Befehls vollständig durchzuführen. Wenn Schreibdaten zur Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** beispielsweise in einem seriellen Datenformat geliefert werden, enthält die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** eine seriell/parallel-Wandlerschaltung, um Datenbits in einem parallelen Format zur Verfügung zu stellen. Für Leseoperationen enthält die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** eine parallel/seriell-Wandlerschaltung, um Datenbits in einem seriellen Format zwecks Ausgabe durch den GLBCMD\_OUT-Ausgabe-Port zur Verfügung zu stellen.

**[0064]** Es wird angenommen, dass das globale Format und das lokale Format bekannt sind, wobei die Logik in dem Befehlsformatwandler **208** speziell ausgestaltet ist, um die logische Konvertierung der Signale so durchzuführen, dass sie zu den diskreten Speichervorrichtungen **104** kompatibel sind. Es wird angemerkt, dass der Befehlsformatwandler **208** eine Steuerlogik enthalten kann, die zumindest im Wesentlichen ähnlich der einer Speichersteuerung eines Speichersystems ist, die verwendet wird, um die diskreten Speichervorrichtungen mit Speichersteuersignalen zu steuern, die ein natives Format haben. Beispielsweise kann der Befehlsformatwandler **208** effektiv die gleiche Steuerlogik wie die Speichersteuerung **14** aus [Fig. 1A](#) enthalten, wenn die diskreten Speichervorrichtungen asynchrone Speichervorrichtungen sind, wie beispielsweise die Speichervorrichtungen **16-1** bis **16-4**. Das bedeutet, dass die Steuerlogik in dem Befehlsformatwandler **208** das Timing und Sequenzieren der Speichersteuersignale im lokalen Format bewirkt, das nativ zu den diskreten Speichervorrichtungen ist.

**[0065]** Wenn der globale Befehl einer Datenschreiboperation entspricht, dann konvertiert der Datenformatwandler **210** in dem Formatwandler **206** die Daten vom globalen Format in das lokale Format und liefert sie zur Speichervorrichtungsschnittstelle **204**. Die Bits der Lese- oder Schreibdaten erfordern keine logische Konvertierung, und somit stellt der Datenformatwandler **210** ein korrektes Mapping der Bitpositionen der Daten zwischen dem ersten Datenformat und dem zweiten Datenformat sicher. Der Formatwandler **206** funktioniert als ein Datenpuffer zum Speichern von Lesedaten aus den diskreten Speichervorrichtungen oder von Schreibdaten, die von der Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** empfangen werden. Daher können Fehlanpassungen hinsichtlich der Datenbreite zwischen dem globalen Format und dem lokalen Format kompensiert werden. Außerdem können verschiedene Datenübertragungsraten zwischen den diskreten Speichervorrichtungen und der Brückenvorrichtung **200** sowie zwischen der Brückenvorrichtung **200** und anderen Kompositsspeichervorrichtungen durch die Pufferfunktion des Datenformatwandlers **210** kompensiert werden.

**[0066]** Die Speichervorrichtungsschnittstelle **204** liefert oder kommuniziert dann den konvertierten Befehl im lokalen Befehlsformat zur diskreten Speichervorrichtung, die durch die lokale Vorrichtungsadresse **118** in dem globalen Befehl **110** aus [Fig. 3B](#) ausgewählt ist. Im vorliegenden Ausführungsbeispiel wird der konvertierte Befehl über einen Befehlspfad **212** zur Verfügung gestellt. In einem Ausführungsbeispiel beinhaltet der Befehlspfad **212** i Sätze von bestimmten lokalen I/O-Ports LCCMD-i bzw. Kanäle, die zwischen jeder diskreten Speichervorrichtung in der Kompositsspeichervorrichtung und der Speichervorrichtungsschnittstelle **204** verbunden sind. Die Variable **i** ist eine Integerzahl, die der Anzahl von diskreten Speichervorrichtungen in der Kompositsspeichervorrichtung entspricht. Beispielsweise enthält jeder LCCMD-i-Kanal alle in [Fig. 1B](#) und Tabelle 1 gezeigten Ports. Bei einem alternativen Ausführungsbeispiel enthält ein LCCMD-i-Kanal beispielsweise alle Ports von einer ONFi-kompatiblen Vorrichtung, einschließlich eines Taktsignals, das in einer Taktshaltung des Befehlsformatwandlers **208** erzeugt werden kann. Die Taktzeugungsschaltungen und -techniken sind in der Technik allgemein bekannt, und bei dem vorliegenden Ausführungsbeispiel können Taktdividierer oder -multiplizierer vorgesehen sein, um Taktsignale mit einer gewünschten Frequenz aus einem einzelnen "Master"-Taktsignal zu erzeugen.

**[0067]** Es folgt eine Beschreibung von einem beispielhaften Betrieb der Brückenvorrichtung **200** unter weiterer Bezugnahme auf die Kompositsspeichervorrichtung **100** aus [Fig. 3A](#). Für eine Leseoperation erreicht ein globaler Befehl, wie zum Beispiel ein globaler Lesebefehl, die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** über den Eingabe-Port GLBCMD-IN. Dieser globale Lesebefehl enthält die globalen Speichersteuersignale, die einen OpCode sowie Zeilen- und Spalteninformationen im globalen Format zur Verfügung stellen, damit Daten von einer diskreten Speichervorrichtung **104** ausgelesen werden, die mit der Brückenvorrichtung **200** verbunden ist. Wenn die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **202** bestimmt, dass sie für den globalen Lesebefehl ausgewählt wurde, und zwar durch Vergleich der globalen Vorrichtungsadresse **116** mit einer vorbestimmten Adresse der Kompositsspeichervorrichtung **100**, dann konvertiert der Befehlsformatwandler **208** den globalen Lesebefehl in das lokale Format, das mit der diskreten Speichervorrichtung **104** kompatibel ist, in der der Lesedatenbefehl ausgeführt werden soll. Wie später beschrieben wird, kann die Kompositsspeichervorrichtung eine zugewiesene Adresse haben. Die lokale Vorrichtungsadresse **118** des globalen Lesebefehls wird zur Speichervorrichtungsschnittstelle **204** geleitet, und der konvertierte Lesedatenbefehl wird zu der diskreten Speichervorrichtung geliefert, die durch die lokale Vorrichtungsadresse adressiert ist, und zwar über einen entsprechenden Satz von logischen I/O-Ports des Befehlspfades **212**.

**[0068]** Daten, die als Lesedaten bezeichnet werden, werden aus der ausgewählten diskreten Speichervorrichtung **104** ausgelesen und im lokalen Format über die gleichen lokalen I/O-Ports der Speichervorrichtungsschnittstelle **204** zum Datenformatwandler **210** geliefert. Der Datenformatwandler **210** konvertiert dann die Lesedaten vom lokalen Format in das globale Format und liefert die Lesedaten von der ausgewählten diskreten Speichervorrichtung **104** zur Speichersteuerung über den Ausgabe-Port GLBCMD\_OUT der Brückenvorrich-

tungsschnittstelle **202**. Die Brückenvorrichtungsschnittstelle **202** enthält einen internen Schaltkreis, um entweder die Lesedaten vom Datenformatwandler **210** oder den Eingabe-Port GLBCMD\_IN mit dem Ausgabe-Port GLBCMD\_OUT zu koppeln.

**[0069]** [Fig. 3A](#), die vorstehend beschrieben wurde, ist eine funktionale Darstellung einer Kompositsspeichervorrichtung gemäß einem Ausführungsbeispiel. [Fig. 5](#) zeigt eine Kompositsspeichervorrichtung, die als ein System-In-Package (SIP) hergestellt wurde, die der Kompositsspeichervorrichtung entspricht, die in [Fig. 3A](#) gezeigt ist, und zwar gemäß einem anderen Ausführungsbeispiel. [Fig. 5](#) zeigt einen Querschnitt einer Kompositsspeichervorrichtung, die in einem Gehäuse (Package) gestapelt ist. Das Gehäuse **300** enthält eine Brückenvorrichtung **302**, die der Brückenvorrichtung **102** aus [Fig. 3A](#) entspricht, sowie vier diskrete Speichervorrichtungen **304**, die jeweils den diskreten Speichervorrichtungen **104** entsprechen, die ebenfalls in [Fig. 3A](#) gezeigt sind. In dem vorliegenden Ausführungsbeispiel sind diese Vorrichtungen hergestellte Halbleiter-Chips. Die Brückenvorrichtung **302** kommuniziert mit den Speichervorrichtungen **304** über eine Speichervorrichtungsschnittstelle **306** in einem lokalen Datenformat, wie zum Beispiel das parallele asynchrone NAND-Format. Die Brückenvorrichtung **302** kommuniziert mit einer Speichersteuerung (nicht gezeigt) oder mit einer anderen Brückenvorrichtung der Kompositsspeichervorrichtungen über die Brückenvorrichtungs-Eingabe/Ausgabe-Schnittstelle **308** in einem globalen Format, wie zum Beispiel das vorstehend beschriebene serielle Datenformat. Der Formatwandler **310** beinhaltet den vorstehend beschriebenen Befehlsformatwandler **208** und den Datenformatwandler **210** aus [Fig. 3A](#), um eine unidirektionale Befehlsformatkonvertierung und eine bidirektionale Datenformatkonvertierung zwischen sich selbst und den diskreten Speichervorrichtungen **304** zu bewirken.

**[0070]** In dem aktuell gezeigten Beispiel wird das Kompositsspeichervorrichtungsgehäuse **300** als ein SIP-System oder ein Multi-Chip-Gehäusesystem (MCP) bezeichnet. In dem Gehäuse sind die Brückenvorrichtung **302** und alle vier diskreten Speichervorrichtungen **304** eingekapselt. Lokale Kommunikationsanschlüsse, dargestellt durch Drähte **312**, verbinden die I/O-Ports von jeder diskreten Speichervorrichtung **304** mit der Speichervorrichtungsschnittstelle **306** der Brückenvorrichtung **302**. Jeder Draht **312** stellt einen Kanal LCCMD-i dar, der alle Signale trägt, die dem lokalen Format entsprechen. Ein beispielhaftes lokales Format ist das asynchrone Flash-Speicherformat, das die in Tabelle 1 gezeigten Signale enthält. Globale Kommunikationsanschlüsse, dargestellt durch Drähte **314** und **316**, verbinden den Eingabe-Port GLBCMD\_IN bzw. den Ausgabe-Port GLBCMD\_OUT mit Gehäuseleitungen **318** über ein optionales Gehäusesubstrat **320**. Die physikalische Anordnung der Brückenvorrichtung **302** und der diskreten Speichervorrichtungen **304** relativ zueinander hängt von der Position der Bondpads der diskreten Speichervorrichtungen **304** und von der Position der Bondpads der Brückenvorrichtung **302** ab.

**[0071]** In dem Ausführungsbeispiel aus [Fig. 5A](#) sind die Daten-Bondpads von jeder diskreten Speichervorrichtung **304** direkt mit den Bondpads der Brückenvorrichtung **302** verbunden. Die Daten-Bondpads von jeder diskreten Speichervorrichtung **304** bilden einen Kanal, der mit bestimmten zugehörigen Daten-Bondpads der Brückenschaltung **302** verbunden werden kann. Bei dem alternativen Ausführungsbeispiel, das in [Fig. 5B](#) gezeigt ist, ist jede diskrete Speichervorrichtung **304** mit der Brückenschaltung **302** über Leiterbahnen verbunden, die in dem Gehäusesubstrat **320** ausgebildet sind. Insbesondere sind die Bonddrähte **312** elektrisch mit Bonddrähten **314** über solche Leiterbahnen verbunden, die in dem Substrat **320** ausgebildet sind. Bei einem Ausführungsbeispiel ist jede diskrete Speichervorrichtung **304** elektrisch mit entsprechenden Daten-Bondpads der Brückenschaltung **302** über einen jeweiligen Kanal verbunden, wie in dem Ausführungsbeispiel aus [Fig. 5A](#). Alternativ enthält die Brückenvorrichtung **302** lediglich einen Satz von Daten-Bondpads, die parallel mit den Daten-Bondpads von jeder diskreten Speichervorrichtung **304** verbunden sind. Daher gibt es einen Kanal, der gemeinsam von allen diskreten Speichervorrichtungen **304** benutzt wird. Bei diesem alternativen Ausführungsbeispiel können die Leiterbahnen, die in dem Substrat **320** ausgebildet sind, parallel mit Brückenvorrichtung **302** und den diskreten Speichervorrichtungen **304** gekoppelt sein, was als eine Multi-Drop-Konfiguration (Konfiguration mit mehreren Abzweigungen) bezeichnet wird.

**[0072]** In dem derzeit gezeigten Beispiel aus [Fig. 5A](#) sind die diskreten Speichervorrichtungen **304** so angeordnet, dass ihre Bondpads in Richtung nach oben zeigen und sie in einem stufenweise versetzten Muster übereinander gestapelt sind, so dass sie freiliegen und nicht die Bondpads der Vorrichtungen überdecken, die in der Nähe einer Kante des Chips angeordnet sind. Die Brückenvorrichtung **302** ist mit ihren Bondpads so angeordnet, dass sie in Richtung nach oben zeigen, und ist auf der obersten diskreten Speichervorrichtung **304** des Stapsels gestapelt. Andere Konfigurationen sind möglich, und zwar abhängig von der Anordnung der Bondpads der diskreten Speichervorrichtungen. Außerdem können anstelle der Bonddrähte auch andere Kommunikationsanschlüsse verwendet werden. Zum Beispiel kann eine drahtlose Kommunikation über induktive Kopplungstechnologie verwendet werden, oder es kann anstelle von Bonddrähten eine Silizium-Durchkontaktierungsverbindung (TSV) verwendet werden. Die U.S. Patent Publication Nr. 2009/0020855 mit dem

Titel "Method for Stacking Serially-Connected Integrated Circuits and Multi-Chip Device Made from Same" zeigt eine Technik, um Chips aufeinander zu stapeln. Die Brückenvorrichtung **302** tragt nicht signifikant zur Größe des Stapels in dem Gehäuse **300** bei. Es sollte folglich für den Fachmann offensichtlich sein, dass die Kompositsspeichervorrichtung **300** nur einen minimalen Raum in einem größeren System einnimmt, während gleichzeitig eine hohe Speicherkapazität zur Verfügung gestellt wird.

**[0073]** [Fig. 6](#) zeigt ein anderes Ausführungsbeispiel der Kompositsspeichervorrichtung aus [Fig. 3A](#), die als ein Modul oder auf einer Schaltkreisplatine (PCB) vorgesehen ist. Wie in [Fig. 6](#) gezeigt, enthält die Kompositsspeichervorrichtung **400** eine Brückenvorrichtung **402** und vier diskrete Speichervorrichtungen **404**. Die Brückenvorrichtung **402** und die diskreten Speichervorrichtungen **404** sind gepackte Vorrichtungen, was bedeutet, dass sie jeweils in einem Halbleiter-Chip eingekapselt sind und Geräteleitungen haben, die mit vorgeformten Leiterbahnen auf der Schaltkreisplatine gebondet sind. Die Brückenvorrichtung **402** ist mit einzelnen diskreten Speichervorrichtungen **404** über die Leiterbahnen verbunden, die als bestimmte lokale I/O-Ports oder Kanäle LCCMD-i für jede Speichervorrichtung **404** organisiert sind. Das Modul oder PCB, das die Brückenvorrichtung enthält, weist einen Eingabe-Port GLBCMD\_IN zum Empfangen von globalen Befehlen und einen Ausgabe-Port GLBCMD\_OUT zum Bereitstellen von Lesedaten und globalen Befehlen auf, die am Eingabe-Port empfangen werden. Diese Eingabe- und Ausgabe-Ports können mit einer Steuerung (nicht gezeigt) oder mit anderen Kompositsspeichervorrichtungen verbunden sein. Wie für die Ausgestaltungen von [Fig. 5A](#) und [Fig. 5B](#) beschrieben, können die einzelnen diskreten Speichervorrichtungen **404** jeweils direkt mit der Brückenvorrichtung **402** verbunden sein, oder alternativ können die einzelnen Speichervorrichtungen **404** in der Konfiguration mit mehreren Abzweigungen parallel mit der Brückenvorrichtung **402** verbunden sein.

**[0074]** Die Ausführungsbeispiele der Kompositsspeichervorrichtungen der [Fig. 5A](#), [Fig. 5B](#) und [Fig. 6](#) können gemäß einem weiteren Ausführungsbeispiel in einem Speichersystem, wie zum Beispiel dem seriellen Speichersystem aus [Fig. 2A](#), verwendet werden. Somit ist das Speichersystem **500** aus [Fig. 7](#) ähnlich dem seriellen Speichersystem **20** aus [Fig. 2A](#). Das Speichersystem **500** enthält eine Speichersteuerung **502** und Kompositsspeichervorrichtungen **504-1** bis **504-j**, wobei j eine Integerzahl ist. Die einzelnen Kompositsspeichervorrichtungen **504-1** bis **504-j** sind seriell mit der Speichersteuerung **502** verbunden. Ähnlich wie bei dem System **20** aus [Fig. 2A](#) ist die Kompositsspeichervorrichtung **504-1** die erste Kompositsspeichervorrichtung des Speichersystems **500**, da sie mit einem Ausgabe-Port  $S_{out}$  der Speichersteuerung **410** verbunden ist, und die Speichervorrichtung **504-n** ist die letzte Vorrichtung, da sie mit einem Eingabe-Port  $S_{in}$  der Speichersteuerung **410** verbunden ist. Die Kompositsspeichervorrichtungen **504-2** bis **504-7** sind dann seriell verbundene Speichervorrichtungen, die zwischen der ersten und der letzten Kompositsspeichervorrichtung angeschlossen sind. Der Port  $S_{out}$  liefert einen globalen Befehl in einem globalen Format. Der Port  $S_{in}$  empfängt Lesedaten im globalen Format und den globalen Befehl, da dieser durch alle Kompositsspeichervorrichtungen geleitet wird.

**[0075]** Jede der Kompositsspeichervorrichtungen, die in [Fig. 7](#) gezeigt sind, ist ähnlich der Kompositsspeichervorrichtung **100**, die in [Fig. 3A](#) gezeigt ist. Jede der Kompositsspeichervorrichtungen weist eine Brückenvorrichtung **102** und vier diskrete Speichervorrichtungen **104** auf. Wie vorstehend beschrieben wurde, ist jede Brückenvorrichtung **102** in jeder Kompositsspeichervorrichtung mit jeweiligen diskreten Speichervorrichtungen **104** sowie entweder mit der Speichersteuerung **502** und/oder einer vorhergehenden oder einer nachfolgenden Kompositsspeichervorrichtung in der seriellen Ringtopologie oder der seriellen Verbindungskonfiguration gekoppelt. Die Funktion von jeder Kompositsspeichervorrichtung **504-1** bis **504-j** ist die gleiche, wie vorstehend für die Ausführungsbeispiele aus [Fig. 3A](#) und [Fig. 4](#) beschrieben wurde.

**[0076]** In dem Speichersystem **500** ist jede Kompositsspeichervorrichtung einer eindeutigen globalen Vorrichtungsadresse zugewiesen. Diese eindeutige globale Vorrichtungsadresse kann in einem Vorrichtungsadressregister der Brückenvorrichtung **102** und insbesondere in einem Register der Eingabe/Ausgabe-Schnittstelle **202** des Brückenvorrichtungs-Blockdiagramms gespeichert sein, das in [Fig. 4](#) gezeigt ist. Diese Adresse kann während einer Einschaltphase des Speichersystems **500** unter Verwendung eines Vorrichtungsadressen-Zuweisungsschemas automatisch zugewiesen werden, das in der U.S. Patent Publication Nr. 20080192649 offenbart ist, die den Titel "Apparatus and Method for Producing Identifiers Regardless of Mixed Device Type in a Serial Interconnection" hat. Außerdem kann jede Kompositsspeichervorrichtung **504** ein diskretes Vorrichtungsregister aufweisen, um Informationen hinsichtlich der Anzahl der diskreten Speichervorrichtungen in jeder Kompositsspeichervorrichtung **504** zu speichern. Während der gleichen Betriebs-Einschaltphase kann die Speichersteuerung daher jedes diskrete Vorrichtungsregister abfragen und die Anzahl der diskreten Speichervorrichtungen in jeder Kompositsspeichervorrichtung aufzeichnen. Folglich kann die Speichersteuerung selektiv einzelne diskrete Speichervorrichtungen **104** in jeder Kompositsspeichervorrichtung **504** des Speichersystems **500** adressieren.

**[0077]** Es folgt eine Beschreibung der Funktion des Speichersystems **500** unter Verwendung eines Beispiels, in dem die Kompositsspeichervorrichtung **504-3** ausgewählt wurde, um eine Speicheroperation durchzuführen. Im vorliegenden Beispiel ist das Speichersystem **500** ein seriell angeschlossenes Speichersystem, das ähnlich dem in **Fig. 2** gezeigten System ist, und bei dem angenommen wird, dass jede der diskreten Speichervorrichtungen **104** eine asynchrone NAND-Flash-Speichervorrichtung ist. Daher sind die Brückenvorrichtungen **102** in jeder der Kompositsspeichervorrichtungen **504-1** bis **504-j** ausgestaltet, um globale Befehle in einem globalen Format zu empfangen, die durch die Speichersteuerung **502** ausgegeben werden, und um sie in ein lokales Format zu konvertieren, das mit den NAND-Flash-Speichervorrichtungen kompatibel ist. Es wird ferner angenommen, dass das Speichersystem eingeschaltet wurde und Adressen für jede Kompositsspeichervorrichtung adressiert wurden.

**[0078]** Die Speichersteuerung **502** gibt einen globalen Befehl von ihrem Port  $S_{out}$  aus, der eine globale Vorrichtungsadresse **116** enthält, die der Kompositsspeichervorrichtung **504-3** entspricht. Die erste Kompositsspeichervorrichtung **504-1** empfängt den globalen Befehl, und ihre Brückenvorrichtung **102** vergleicht ihre zugewiesene globale Vorrichtungsadresse mit der in dem globalen Befehl. Da die globalen Vorrichtungsadressen nicht übereinstimmen, ignoriert die Brückenvorrichtung **102** für die Kompositsspeichervorrichtung den globalen Befehl und leitet den globalen Befehl zum Eingabe-Port der Kompositsspeichervorrichtung **504-2** weiter. Der gleiche Vorgang findet in der Kompositsspeichervorrichtung **504-2** statt, da ihre zugewiesene globale Vorrichtungsadresse nicht mit derjenigen in dem globalen Befehl übereinstimmt. Folglich wird der globale Befehl zur Kompositsspeichervorrichtung **504-3** weitergeleitet.

**[0079]** Die Brückenvorrichtung **102** der Kompositsspeichervorrichtung **504-3** bestimmt eine Übereinstimmung zwischen ihrer zugewiesenen globalen Vorrichtungsadresse und derjenigen in dem globalen Befehl. Daher fährt die Brückenvorrichtung **102** der Kompositsspeichervorrichtung **504-3** fort, die globalen Speichersteuersignale in das lokale Format zu konvertieren, das mit den NAND-Flash-Speichervorrichtungen kompatibel ist. Die Brückenvorrichtung sendet dann den konvertierten Befehl zur NAND-Flash-Speichervorrichtung, die durch die lokale Vorrichtungsadresse **118** ausgewählt ist, die in dem globalen Befehl enthalten ist. Die ausgewählte NAND-Flash-Vorrichtung führt dann die Operation entsprechend den lokalen Speichersteuersignalen durch, die sie empfangen hat.

**[0080]** Während die Brückenvorrichtung **102** der Kompositsspeichervorrichtung **504-3** den globalen Befehl konvertiert, leitet sie den globalen Befehl zur nächsten Kompositsspeichervorrichtung weiter. Die übrigen Kompositsspeichervorrichtungen ignorieren den globalen Befehl, der möglicherweise am Port  $S_{in}$  der Speichersteuerung **502** empfangen wird. Wenn der globale Befehl einer Leseoperation entspricht, dann liefert die ausgewählte NAND-Flash-Speichervorrichtung der Kompositsspeichervorrichtung **504-3** Lesedaten zu ihrer zugehörigen Brückenvorrichtung **102** im lokalen Format. Die Brückenvorrichtung **102** konvertiert dann die Lesedaten in das globale Format und leitet sie durch ihren Ausgabe-Port zur nächsten Kompositsspeichervorrichtung weiter. Die Brückenvorrichtungen **102** aller übrigen Kompositsspeichervorrichtungen leiten die Lesedaten zum Port  $S_{in}$  der Speichersteuerung **502** weiter. Für den Fachmann ist offensichtlich, dass andere globale Befehle ausgegeben werden können, um die Leseoperation durchzuführen, von denen alle durch die Brückenvorrichtung **102** der ausgewählten Kompositsspeichervorrichtung konvertiert werden.