(12)发明专利

(10)授权公告号 CN 105745747 B

(45)授权公告日 2019.02.12

(21)申请号 201480063290.2

(73)专利权人 高通股份有限公司

(22)申请日 2014.10.24

地址 美国加利福尼亚州

(65)同一申请的已公布的文献号

(72)发明人 S·S·宋 Z·王 C·F·耶普

申请公布号 CN 105745747 A

(74)专利代理机构 上海专利商标事务所有限公司 31100

(43)申请公布日 2016.07.06

代理人 袁逸

(30)优先权数据

(51)Int.Cl.

61/908,007 2013.11.22 US

H01L 21/8234(2006.01)

14/283,168 2014.05.20 US

G03F 7/20(2006.01)

(85)PCT国际申请进入国家阶段日

H01L 27/02(2006.01)

2016.05.19

(56)对比文件

(86)PCT国际申请的申请数据

US 2002/0068447 A1, 2002.06.06,

PCT/US2014/062276 2014.10.24

US 2012/0180016 A1, 2012.07.12,

(87)PCT国际申请的公布数据

CN 101673735 A, 2010.03.17,

W02015/076978 EN 2015.05.28

审查员 金政

权利要求书1页 说明书6页 附图12页

(54)发明名称

用于栅极图案化的合并光刻工艺

(57)摘要

用于在管芯上制造器件的方法，和管芯上的器件。一种方法可包括将第一区域图案化以用第一工艺创建具有第一栅极长度和第一接触多晶硅间距(CPP)的第一栅极。该第一CPP小于单图案光刻限制。该方法还包括将第一区域图案化以用第二工艺创建具有第二栅极长度或者第二CPP的第二栅极。该第二CPP小于该单图案光刻限制。该第二栅极长度与该第一栅极长度不同。

1. 一种用于在管芯上制造多个器件的方法，包括

将第一区域图案化以用第一工艺创建具有第一栅极长度和接触多晶硅间距CPP的多个第一栅极，所述CPP小于单图案光刻限制；

根据单元交换工艺来图案化所述第一区域；以及

制造一对第二栅极，所述一对第二栅极被布置成代替所述多个第一栅极中的一些第一栅极，所述一对第二栅极具有第二栅极长度和所述CPP，所述单元交换工艺不同于所述第一工艺，所述第二栅极长度与所述第一栅极长度不同。

2. 如权利要求1所述的方法，其特征在于，所述第一工艺是自对准双图案化(SADP)工艺。

3. 如权利要求2所述的方法，其特征在于，所述单元交换工艺是光刻-蚀刻-光刻-蚀刻(LELE)工艺。

4. 如权利要求1所述的方法，其特征在于，所述单元交换工艺是在由所述第一工艺形成的栅极之间执行的第二光刻工艺。

5. 如权利要求1所述的方法，其特征在于，所述多个器件被集成到移动电话、机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、计算机、手持式个人通信系统(PCS)单元、便携式数据单元、和/或位置固定的数据单元中。

6. 一种半导体装置，包括：

第一区域中的具有第一栅极长度和接触多晶硅间距CPP的多个第一栅极长度器件，所述CPP小于单图案光刻限制；以及

所述第一区域中的一对第二栅极长度器件，所述一对第二栅极长度器件被布置成代替所述多个第一栅极长度器件中的一些第一栅极长度器件，所述一对第二栅极长度器件具有第二栅极长度和所述CPP，所述第二栅极长度与所述第一栅极长度不同。

7. 如权利要求6所述的半导体装置，其特征在于，所述多个第一栅极长度器件具有比所述一对第二栅极长度器件更一致的关键尺寸一致性。

8. 如权利要求6所述的半导体装置，其特征在于，进一步包括具有第三栅极长度的第三栅极长度器件。

9. 如权利要求6所述的半导体装置，其特征在于，所述装置被集成到移动电话、机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、计算机、手持式个人通信系统(PCS)单元、便携式数据单元和/或固定位置数据单元中。

10. 一种用于在管芯上制造多个器件的方法，包括

用于将第一区域图案化以用第一工艺创建具有第一栅极长度和接触多晶硅间距CPP的多个第一栅极的步骤，所述CPP小于单图案光刻限制；以及

用于根据单元交换工艺来图案化所述第一区域并且随后制造一对第二栅极的步骤，所述一对第二栅极被布置成代替所述多个第一栅极中的一些第一栅极，所述一对第二栅极具有第二栅极长度和所述CPP，所述单元交换工艺不同于所述第一工艺，并且所述第二栅极长度与所述第一栅极长度不同。

11. 如权利要求10所述的方法，其特征在于，所述多个器件被集成到移动电话、机顶盒、音乐播放器、视频播放器、娱乐单元、导航设备、计算机、手持式个人通信系统(PCS)单元、便携式数据单元、和/或位置固定的数据单元中。

## 用于栅极图案化的合并光刻工艺

[0001] 相关申请的交叉引用

[0002] 本申请根据35U.S.C. §119(e)的规定要求于2013年11月22日提交的题为“MERGING LITHOGRAPHY PROCESSES FOR GATE PATTERNING(用于栅极图案化的合并光刻工艺)”的美国临时专利申请No.61/908,007的权益，并且该临时申请的公开通过援引被明确地整体纳入于此。

### 背景技术

[0003] 领域

[0004] 本公开的诸方面涉及半导体器件，并且尤其涉及减小场效应晶体管(FET)结构中的栅极长度和间距。

[0005] 背景

[0006] 随着半导体器件尺寸的减小，为这些器件创建图案的能力变得越来越困难。对于10纳米(nm)接触多晶硅(P0)间距(CPP)器件来说，可以使用多个图案化步骤来达到该器件尺寸。例如，一种相关技术方法被称为光刻-蚀刻光刻-蚀刻(LELE)，其使用交织或交错的较大间距图案来实现较小间距大小。尽管如此，LELE仍然受限于较大的线边缘粗糙度(LER)、较大的栅极-栅极间隔变化、和较大的关键尺寸变化。

[0007] 另一相关技术方法是使用沉积在心轴上的分隔件来定义栅极长度(Lg)的自对准双图案化(SADP)。虽然SADP具有比LELE更好的关键尺寸一致性，但是附加的掩模被用于在用SADP生产的器件中产生不同的栅极长度。这限制了SADP工艺对于较大集成电路的有用性。

[0008] 概述

[0009] 一种用于在管芯上制造器件的方法可包括将第一区域图案化以用第一工艺创建具有第一栅极长度和第一接触多晶硅间距(CPP)的第一栅极。该第一CPP小于单图案光刻限制。该方法还包括将第一区域图案化以用第二工艺创建具有第二栅极长度或第二CPP的第二栅极。该第二CPP小于单图案光刻限制。该第二栅极长度与该第一栅极长度不同。

[0010] 一种装置可包括第一区域中的具有第一栅极长度和第一接触多晶硅间距(CPP)的第一栅极长度器件。该第一CPP小于单图案光刻限制。该装置还包括该第一区域中的具有第二栅极长度或第二CPP的至少一个第二栅极长度器件。该第二CPP小于单图案光刻限制。该第二栅极长度与该第一栅极长度不同。

[0011] 一种装备可包括第一区域中具有第一栅极长度和第一接触多晶硅间距(CPP)的用于选择性地传导电流的第一装置。该第一CPP小于单图案光刻限制。该装备还包括具有至少一个具有第二栅极长度或第二CPP的第二栅极长度器件的用于选择性地传导电流的第二装置。该第二CPP小于单图案光刻限制。该第二栅极长度与该第一栅极长度不同。

[0012] 这已较宽泛地勾勒出本公开的特征和技术优势以便下面的详细描述可以被更好地理解。本公开的附加特征和优点将在下文描述。本领域技术人员应该领会，本公开可容易地被用作修改或设计用于实施与本公开相同的目的的其他结构的基础。本领域技术人员还

应认识到,这样的等效构造并不脱离所附权利要求中所阐述的本公开的教导。被认为是本公开的特性的新颖特征在其组织和操作方法两方面连同进一步的目的和优点在结合附图来考虑以下描述时将被更好地理解。然而,要清楚理解的是,提供每一幅附图均仅用于解说和描述目的,且无意作为对本公开的限定的定义。

[0013] 附图简述

- [0014] 为了更全面地理解本公开,现在结合附图参阅以下描述。

- [0015] 图1A-1J解说了根据本公开的一个或多个方面的半导体器件的侧视图。

- [0016] 图2A-2M解说了根据本公开的一个或多个方面的制造半导体器件的工艺。

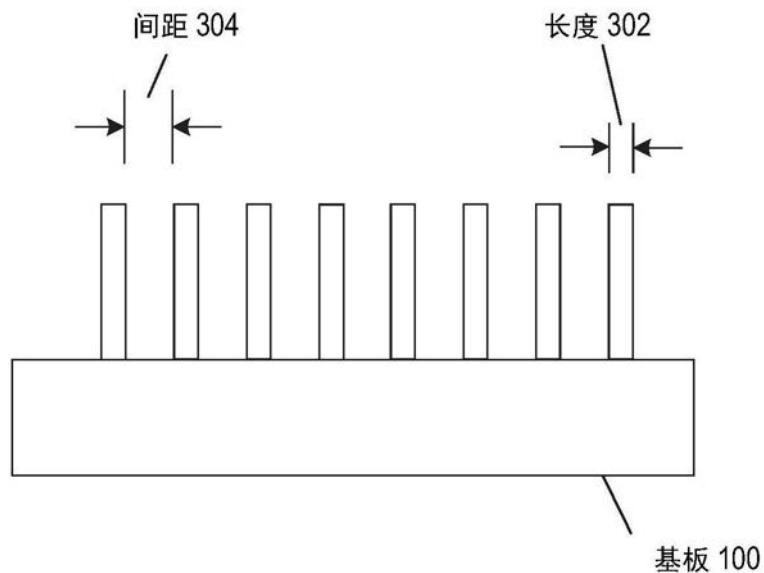

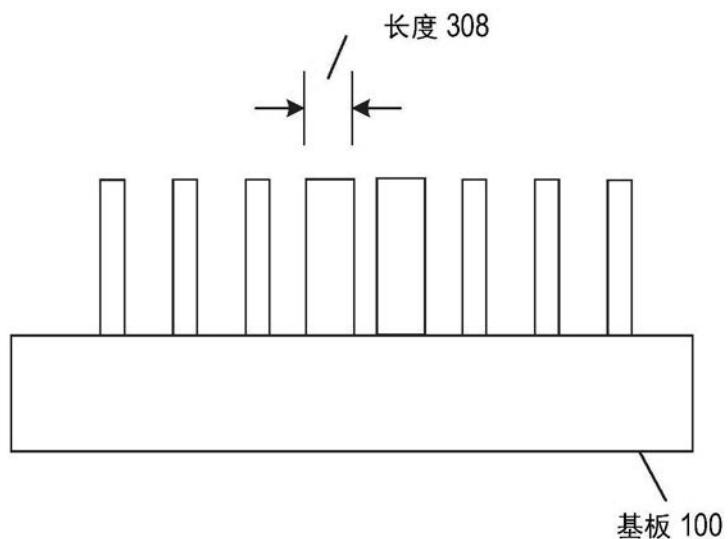

- [0017] 图3A-3C解说了根据本公开的一个或多个方面的半导体器件的侧视图。

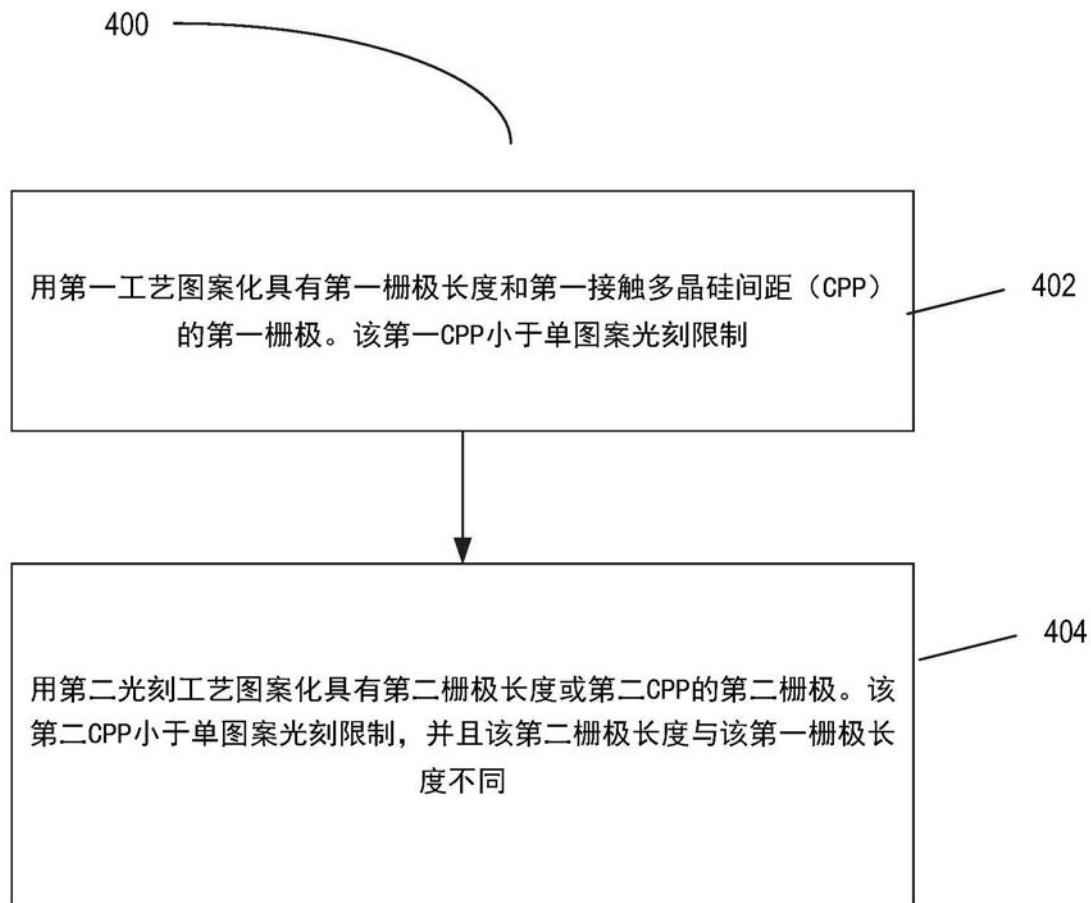

- [0018] 图4是解说根据本公开的一方面的用于制造器件的方法的过程流程图。

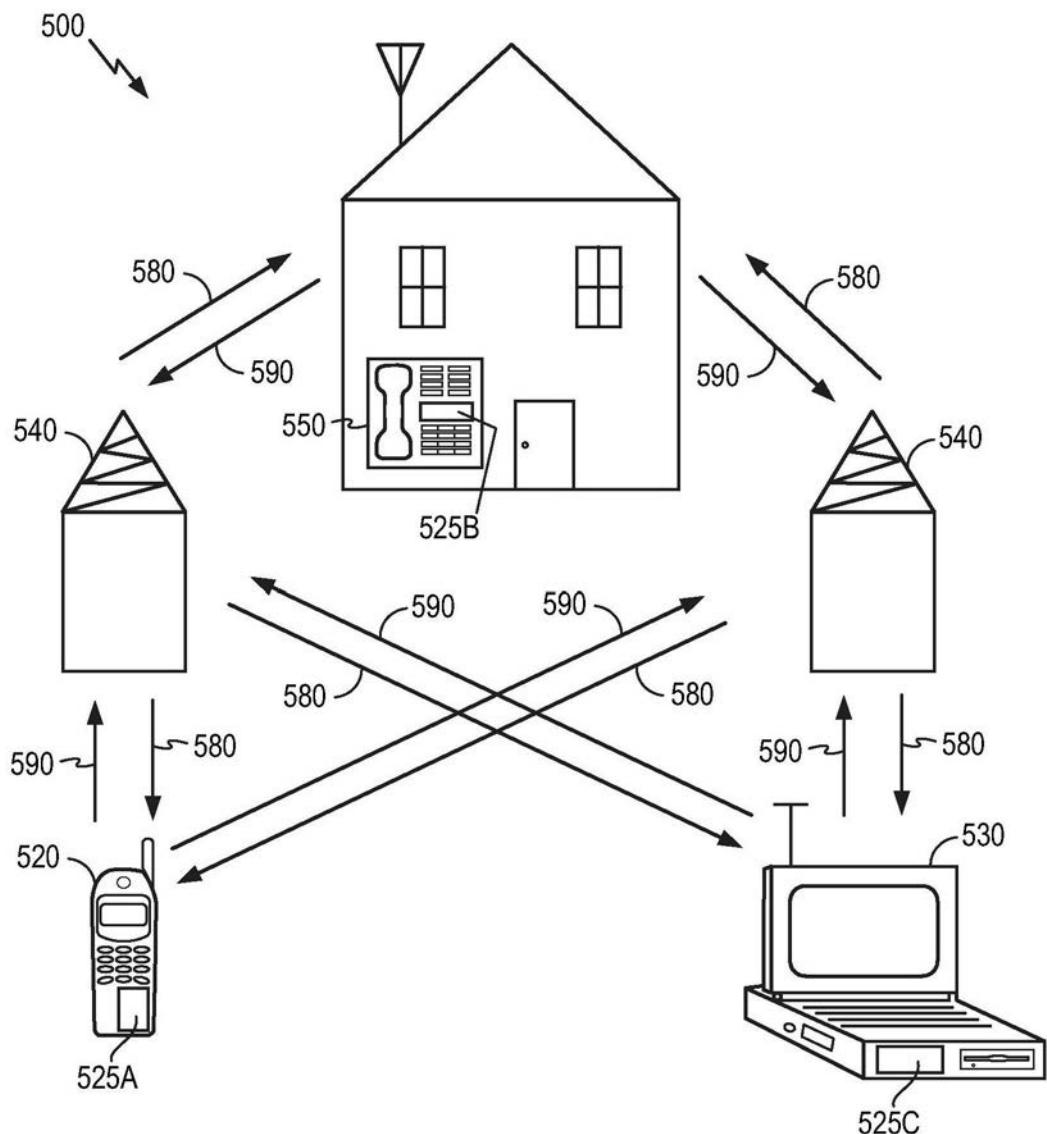

- [0019] 图5是示出其中可有利地采用本公开的一方面的示例性无线通信系统的框图。

- [0020] 图6是解说根据本公开的一个方面的用于半导体组件的电路、布局、以及逻辑设计的设计工作站的框图。

[0021] 详细描述

[0022] 以下结合附图阐述的详细描述旨在作为各种配置的描述,而无意表示可实践本文中所描述的概念的仅有的配置。本详细描述包括具体细节以便提供对各种概念的透彻理解。然而,对于本领域技术人员将显而易见的是,没有这些具体细节也可实践这些概念。在一些实例中,以框图形式示出众所周知的结构和组件以避免湮没此类概念。如本文所述的,术语“和/或”的使用旨在代表“可兼性或”,而术语“或”的使用旨在代表“排他性或”。

[0023] 十(10)纳米(nm)接触多晶硅(P0)间距(CPP)几何形态可以为器件的图案化使用六十(64)nm基本几何形态。为了在器件中创建这样大小的基本几何形态,经常使用193个交织的双图案化。两种方法能够在器件中创建该基本几何形态。第一光刻工艺(光刻-刻蚀光刻-刻蚀(LELE))使用自我交织(例如,覆盖)的一百二十八(128)nm间距图案来将128nm特征的大小降低到64nm特征。通过交叠掩模,128nm特征能够被切掉一半以获得64nm基本CPP。第二光刻工艺(自对准双图案化(SADP))使用沉积在虚设心轴图案上的分隔件来定义栅极长度(Lg)。这类似于在FinFET器件中创建鳍结构。

[0024] 本公开的一方面合并了SADP和LELE以允许电路或器件之内的多个栅极长度。使用SADP提供了更严苛的关键尺寸(CD)控制和更少的变化,但是仅允许单一栅极长度。在本公开的一个方面,一个掩模被用于SADP工艺。使用LELE提供了相同器件内的多个栅极长度和灵活的CPP。在本公开的一方面,LELE的使用使用了两个掩模。在本公开的一方面,SADP和LELE两者的切割图案也使用单一掩模,这提供了四个掩模过程。

[0025] 在本公开的一方面,SADP的使用实现了较小CPP下的较小栅极长度。通过结合SADP和LELE,实现了较小(可能是最小)CPP下的多个栅极长度。进一步,LELE还允许输入-输出(I/O)和模拟器件在较大CPP下的较大栅极长度。

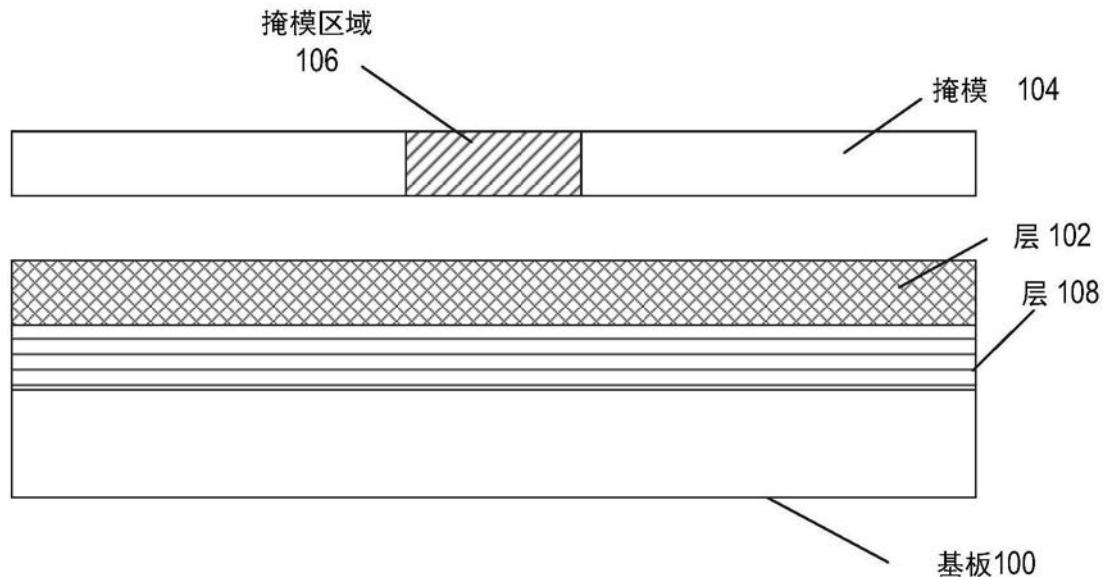

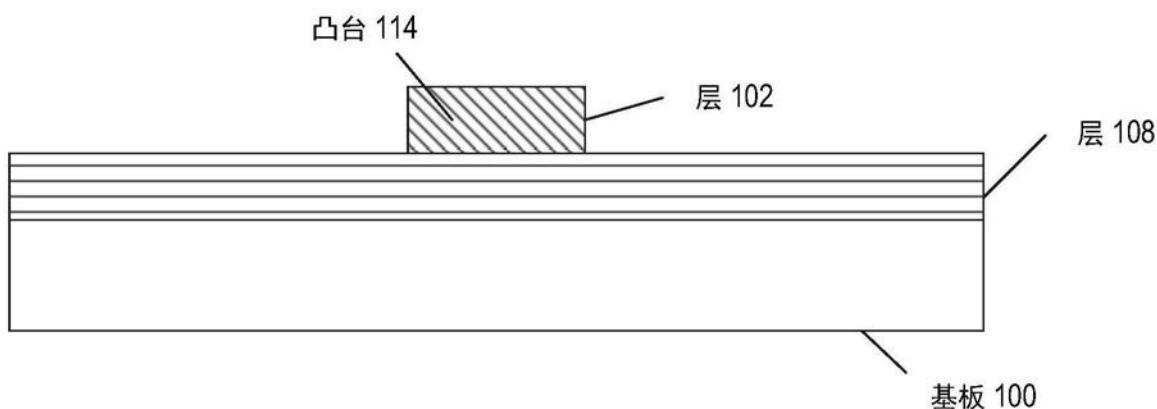

[0026] 图1A-1J解说了根据本公开的一个或多个方面的半导体器件的侧视图。在图1A-1J中,一般地示出了LELE工艺。图1A解说了具有层102和层108的基板100。层102和108可以是硬掩模层、光致抗蚀剂层或者可以是氧化硅、多晶硅或其他材料层。图1A中还示出了具有掩模区域106的掩模104。在图1B中,掩模104被放置成邻近于层102和基板100,从而将层102图案化。

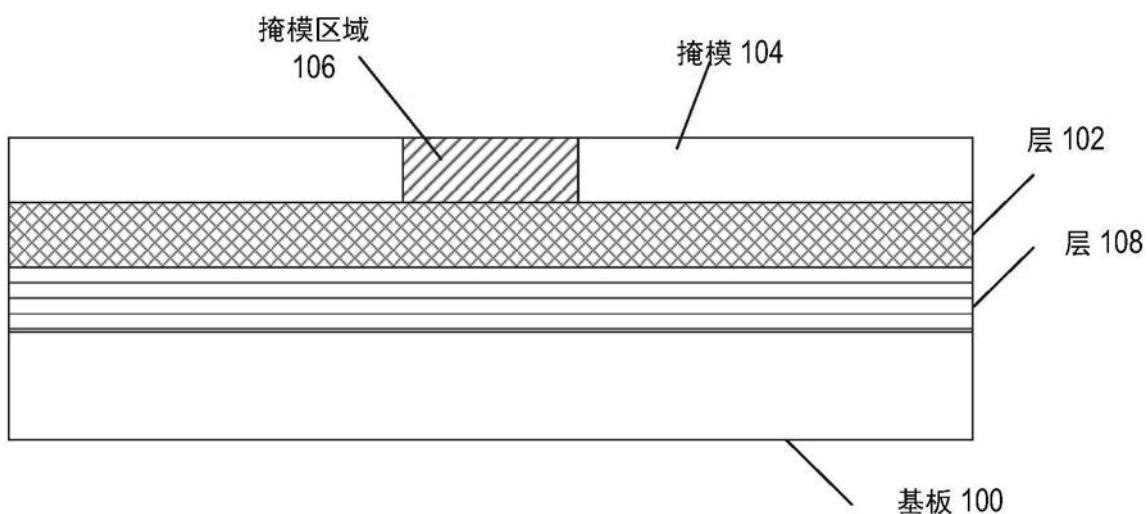

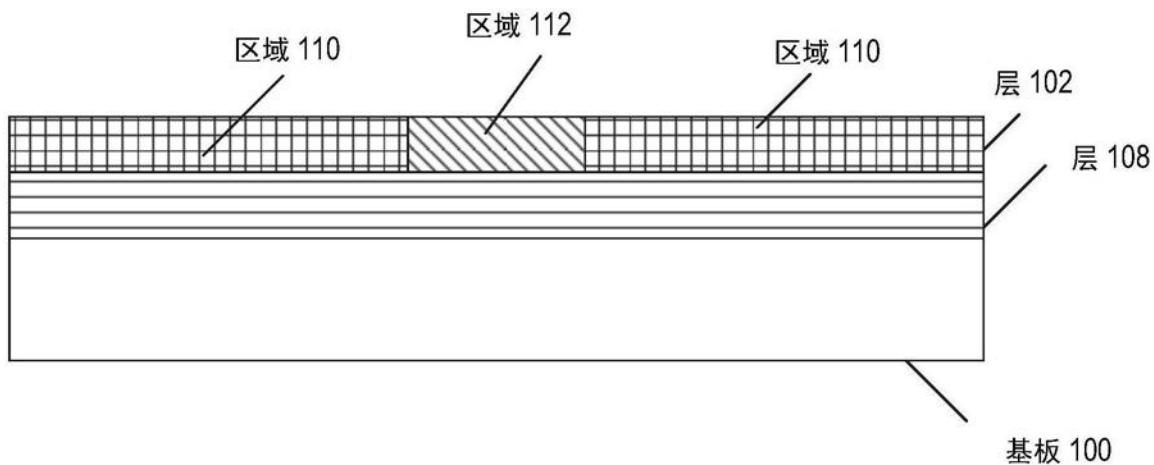

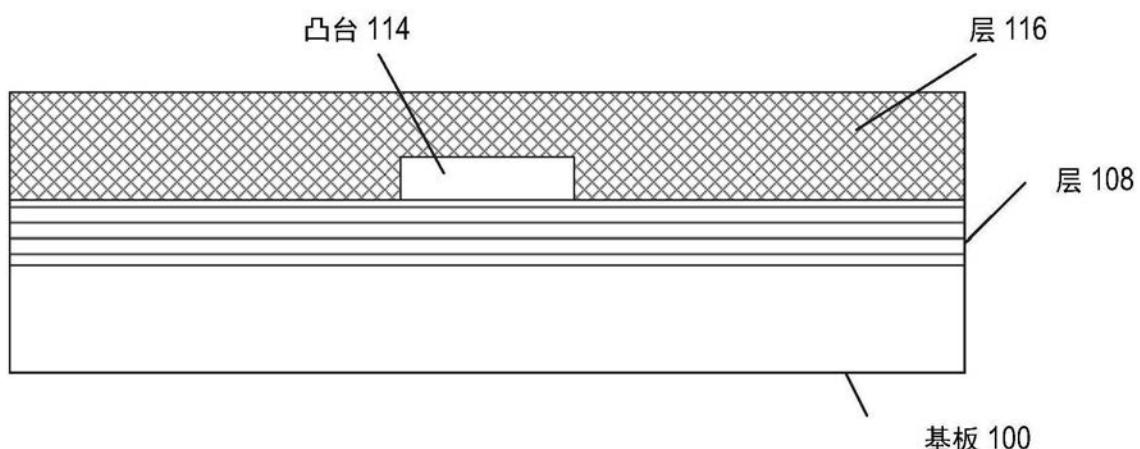

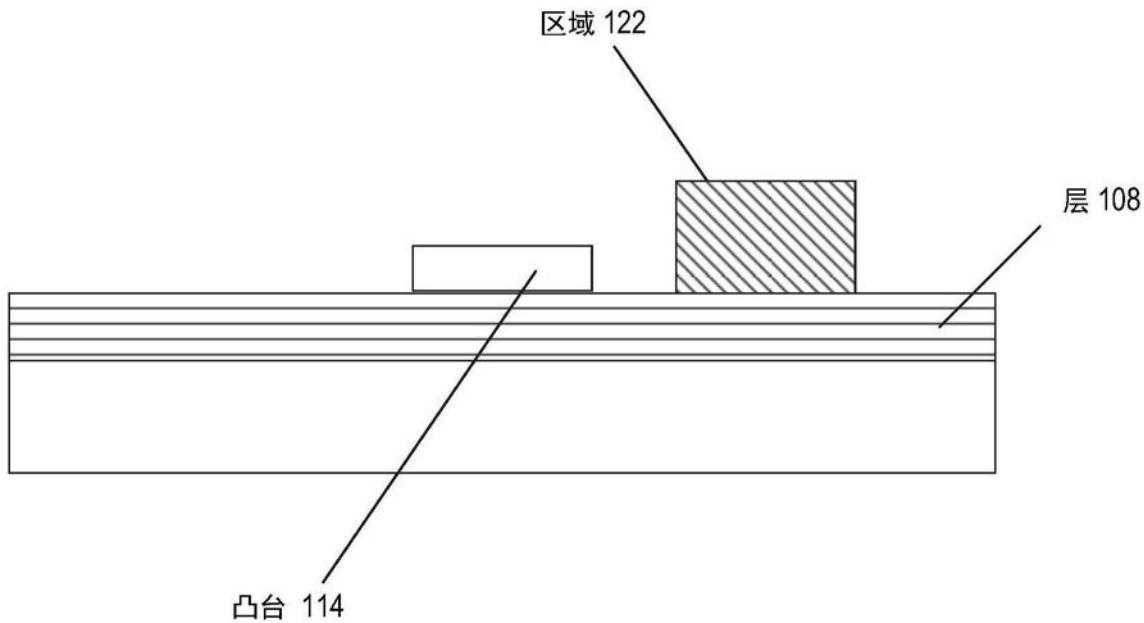

[0027] 图1C解说了层102，其中层102的区域110不被掩模区域106遮蔽，并且区域112被掩模区域106遮蔽。图1A-1C描述了本公开的LELE工艺的“第一次光刻”或“第一光刻”部分。图1D解说了凸台114，取决于总体器件设计，其可以是层102的一部分，或者可以是另一层的一部分。图1D描述了本公开的LELE工艺的“第一次蚀刻”。

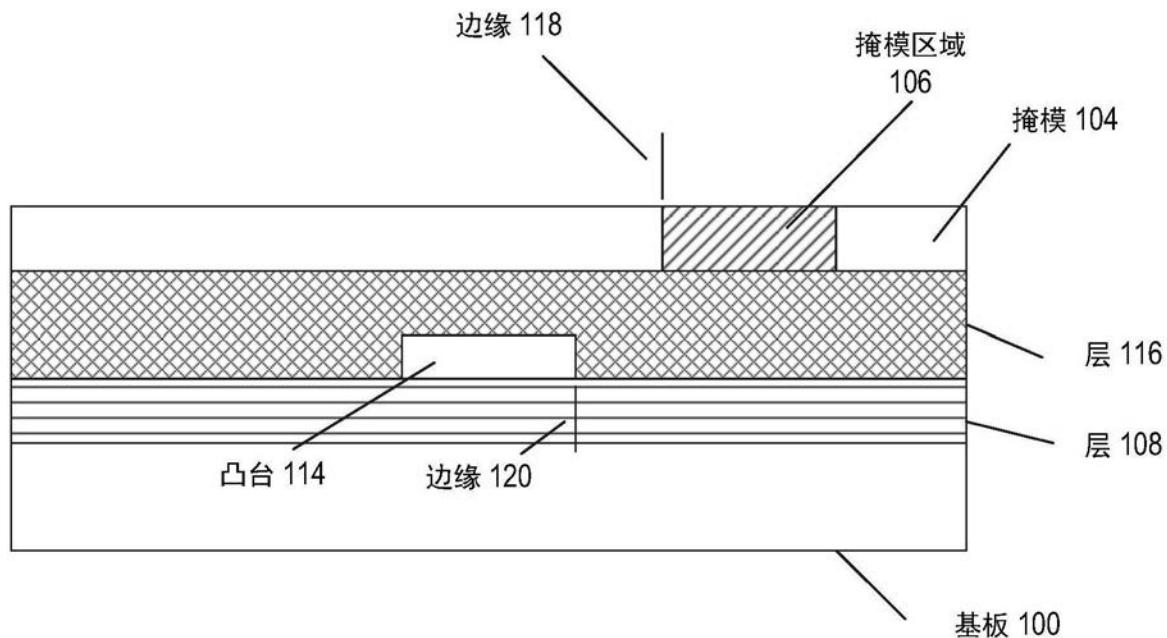

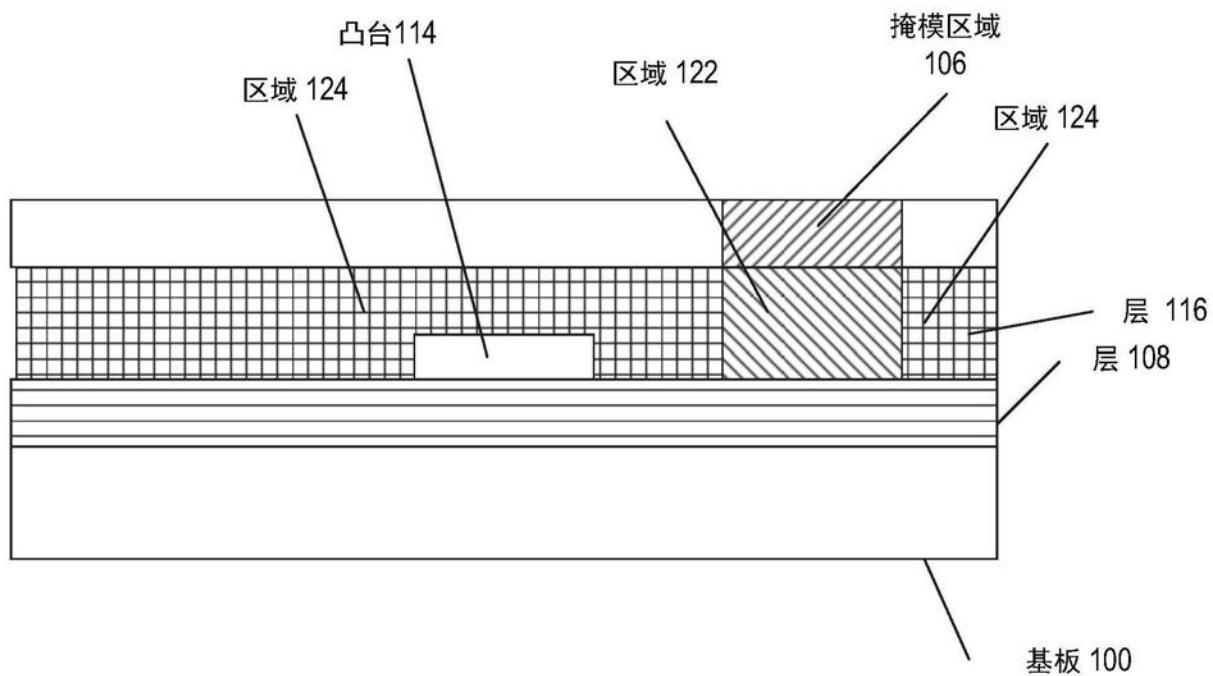

[0028] 图1E解说了另一层116，其可以是光致抗蚀剂，或者可以是硅、氧化硅、多晶硅或者其他材料。图1F解说了掩模104，其中掩模区域106的边沿118与凸台114的边沿120偏离。图1G解说了层116的暴露，其中区域122使用掩模区域106遮蔽，而区域124维持不被遮蔽。图1H示出了层108上的区域122和凸台114。图1E-1H解说了本公开的LELE工艺的“第二次光刻”部分。

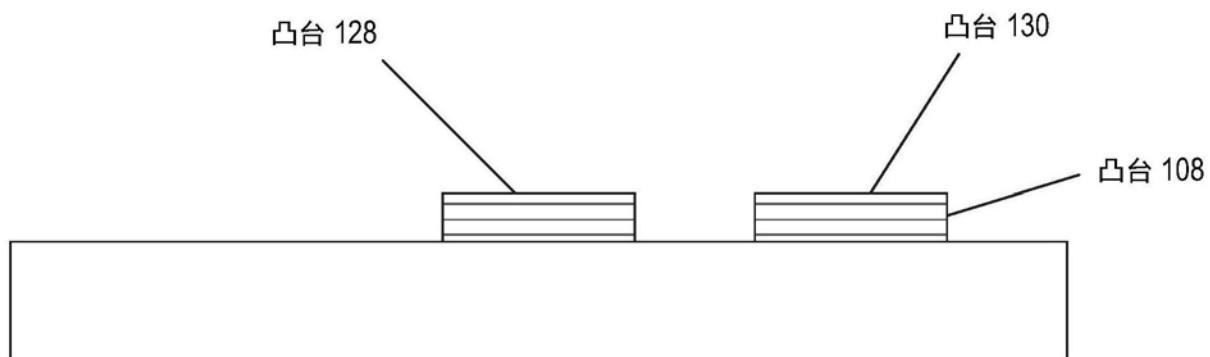

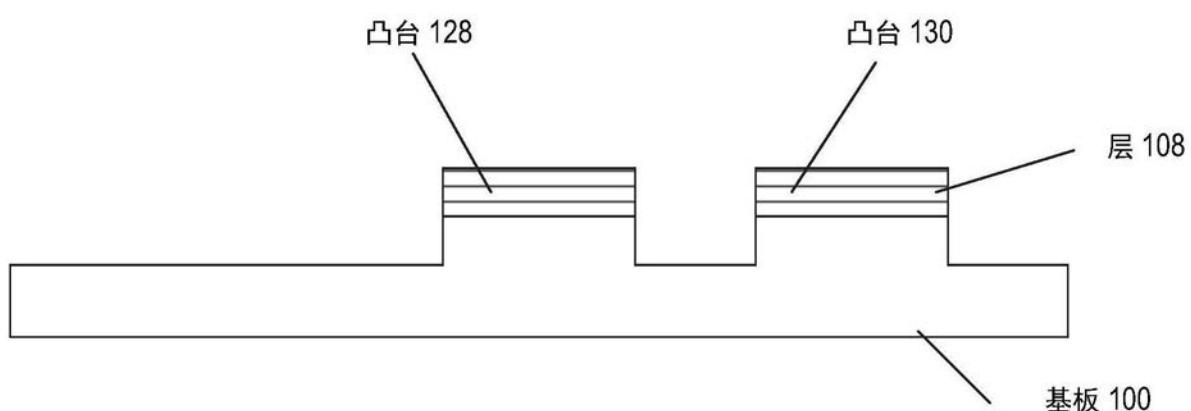

[0029] 图1I解说了蚀刻或移除层108的诸部分，以创建凸台128和凸台130，该凸台128和凸台130在凸台114和区域122的下面。图1J解说了蚀刻基板100，其中凸台128和130充当掩模以保护基板100的诸部分。图1H-1J描述了本公开的LELE工艺的“第二次蚀刻”部分。

[0030] 通过放置掩模区域106，通过在LELE工艺的第一次光刻和第二次光刻之间“交织”掩模区域106创建了凸台128和130的宽度以及由此在基板100或器件中的其他层上创建的特征。然而，区域122（由掩模区域106定义）限制了凸台130能够离另一凸台128或另一器件距离有多近，因为区域122防止在区域122下面发生任何蚀刻或其他处理。这限制了基板100上的器件的栅极到栅极间隔。换言之，可以在第一区域中执行LELE工艺，并且可以在第二区域中执行SADP工艺。进一步，可以在由SADP工艺所产生的特征或栅极之间执行LELE工艺。

[0031] 图2A-2M解说了根据本公开的一个或多个方面的制造半导体器件的工艺。

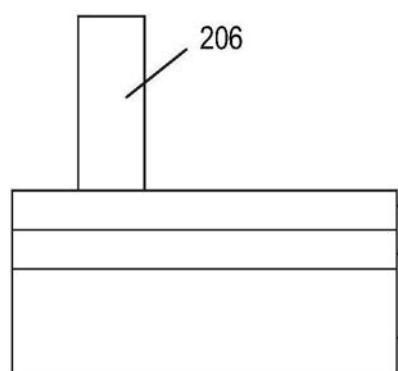

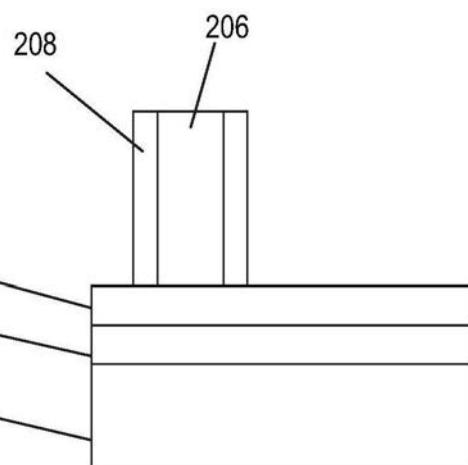

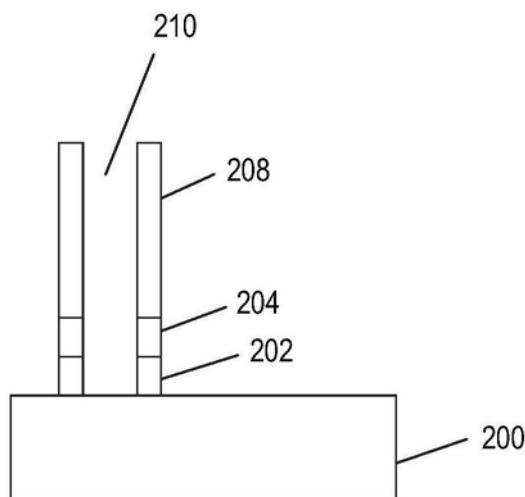

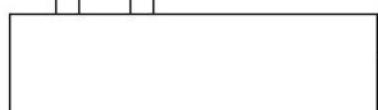

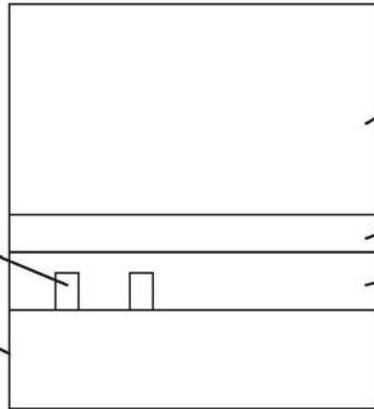

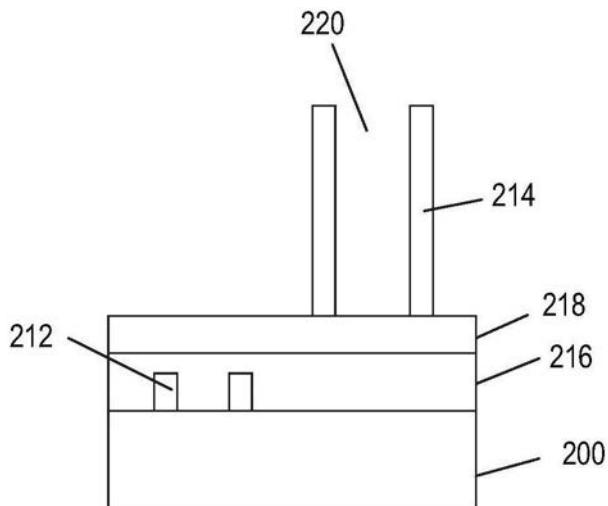

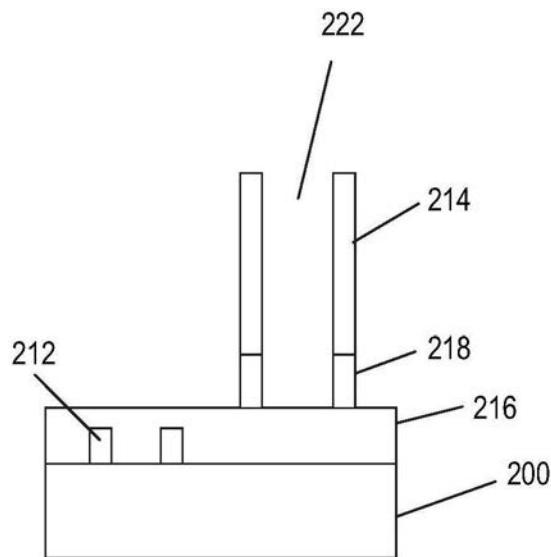

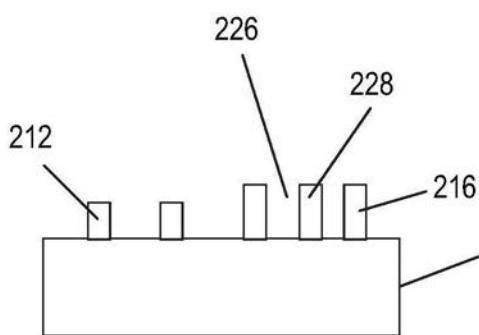

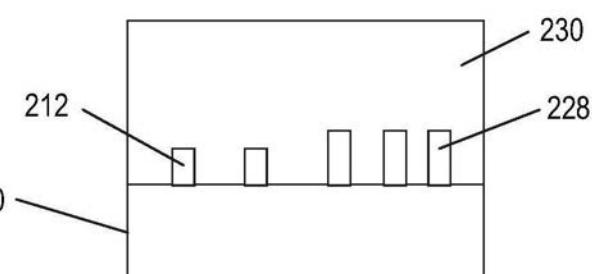

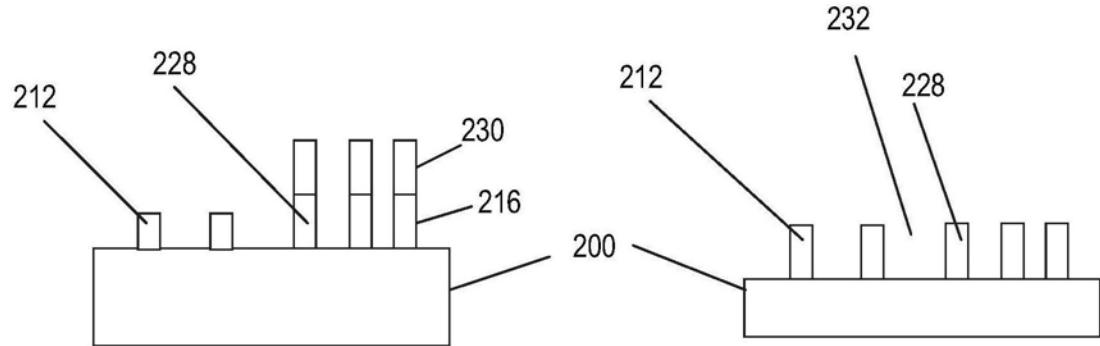

[0032] 图2A解说了使用SADP掩模。示出了具有硬掩模层202和204的基板200，并且在硬掩模层204上沉积了心轴206。图2B解说了分隔件层208在心轴206上的沉积。图2C解说了心轴206以及硬掩模层202和204的蚀刻210。分隔件层208厚度定义了SADP工艺中的栅极长度。图2D示出分隔件层208和硬掩模层204被移除，从而将栅极长度图案212留在基板200上。图2E示出了光致抗蚀剂（PR）层214和硬掩模层216、218的沉积。在图2F中应用了第二掩模，并且光致抗蚀剂层214被暴露或者图案化220，这是第一LELE图案。

[0033] 在本公开中，SADP掩模创建了基板200的第一区域中的第一栅极的图案，并且在基板200的第一区域中执行LELE图案化。由此，在本公开的一方面，SADP器件和LELE器件可以在基板200的第一区域中彼此交织或毗邻。

[0034] 进一步，第一区域中的SADP图案创建了第一栅极长度和第一接触多晶硅间距（CPP）。第一CPP可以小于单图案光刻限制。第一区域中的LELE图案创建了第二栅极长度或第二CPP，其中第二CPP也小于单图案光刻限制。该第二栅极长度可以与该第一栅极长度不同。作为示例而非限定，第一和第二CPP的范围可以在40和80纳米之间，而第一和第二栅极长度的范围可以在10和30纳米之间。

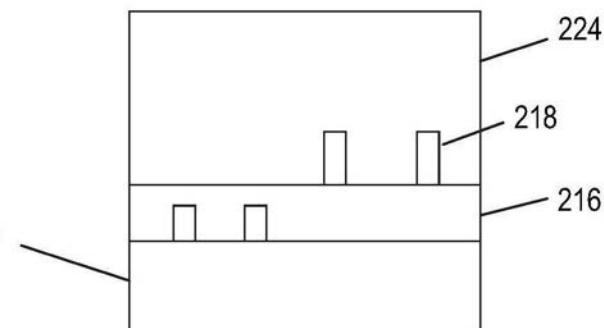

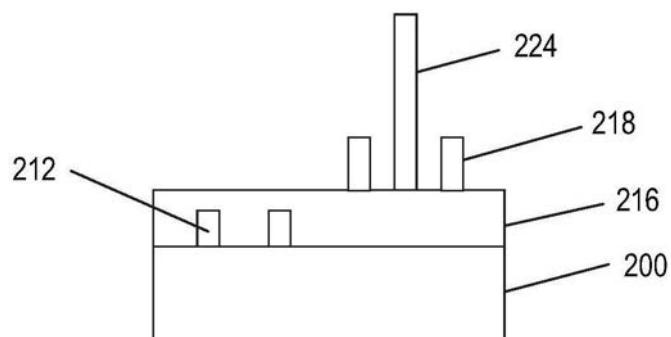

[0035] 图2G解说了通过蚀刻222的硬掩模层移除。图2H解说了应用第二光致抗蚀剂224。图2I解说了使用第三掩模、第二LELE图案，这将第二光致抗蚀剂224图案化。图2J解说了基于第二LELE图案的硬掩模层216的蚀刻226，以创建栅极长度图案228。图2K解说了另一光致抗蚀剂230沉积。图2L示出了切割掩模的图案化。图2M解说了根据本公开的一方面的蚀刻232到基板200中以将栅极长度图案212和228创建到基板200中。

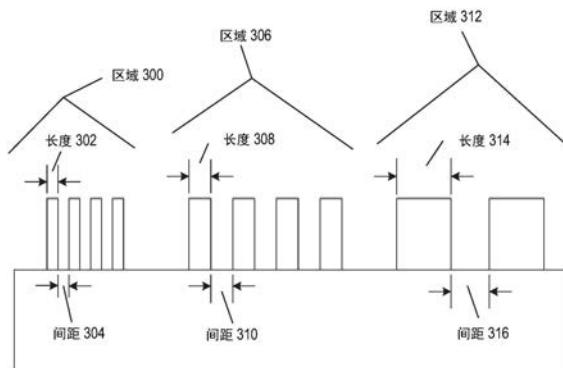

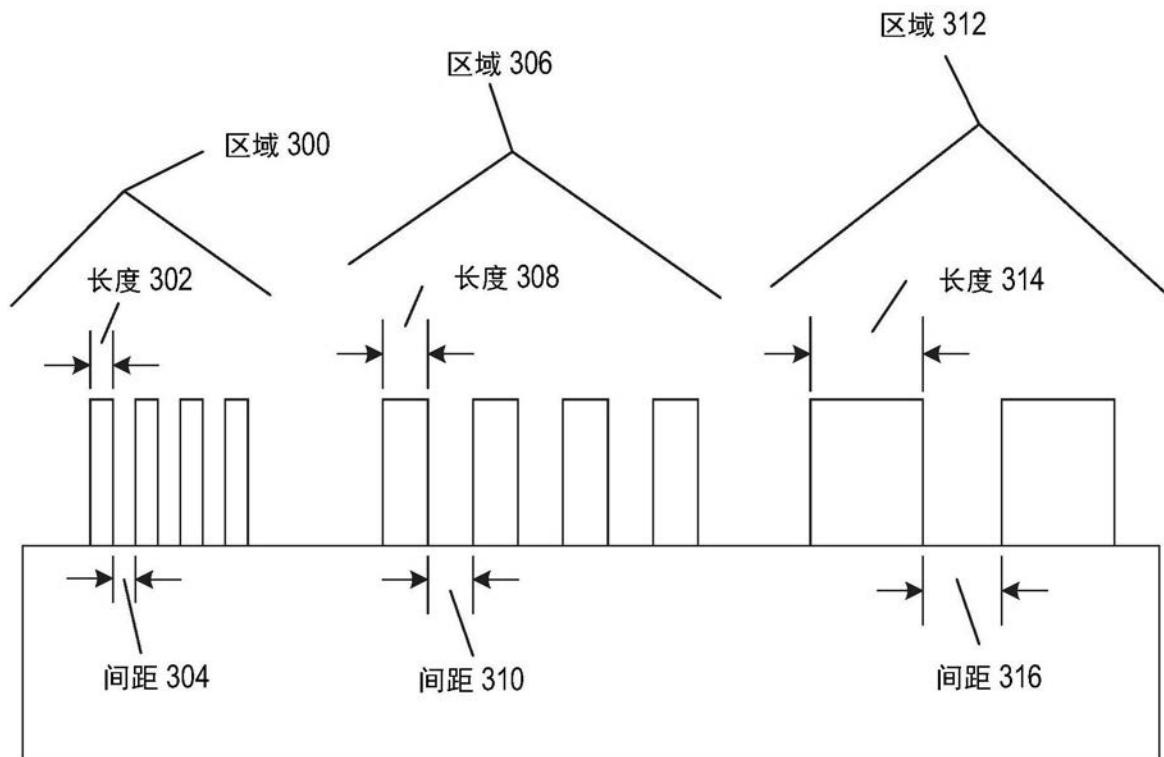

[0036] 图3A解说了根据本公开的一个或多个方面的半导体器件的侧视图。区域300示出

了在较小间距 (CPP) 304下的经SADP图案化的栅极长度302,该间距304具有改进的关键尺寸一致性,并且在器件之间具有较小的间距变化。区域306示出了在第二间距 (CPP) 310下的经LELE图案化的栅极长度308,该间距310可以是较小的CPP或者与区域300相同的CPP 310。区域312解说了在较大间距 (CPP) 下的较大栅极长度314,该间距316可以使用参照图1A-1J描述的LELE工艺制成。

[0037] 图3B解说了根据本公开的一个或多个方面的半导体器件的侧视图。最初以较小间距 (CPP) 304用经SADP图案化的栅极长度302形成多个器件。在图3C中,在基板100的相同区域或区划内执行LELE单元交换。在本公开的该方面,执行LELE单元交换过程以制造一对经LELE图案化的器件,该器件具有经LELE图案化的栅极长度308,该栅极长度308大于经SADP图案化的栅极长度302。经LELE图案化的栅极长度器件的间距可以和间距304相同。

[0038] 图4是解说根据本公开的一方面的用于制造器件的方法400的过程流程图。在框402中,用第一光刻工艺图案化至少第一栅极,该第一栅极具有第一栅极长度和第一接触多晶硅间距 (CPP) 。第一CPP小于单图案光刻限制。例如,第一栅极使用如图1A-1J中所示的SADP来图案化。在框404中,使用第二光刻工艺图案化具有第二栅极长度或第二CPP的第二栅极。第二CPP小于单图案光刻限制并且第二栅极长度与第一栅极长度不同。例如,第二栅极使用图2A-2M中的LELE工艺来图案化。

[0039] 根据本公开的进一步方面,公开了一种半导体装备。在一个配置中,该装备包括具有第一栅极长度和第一接触多晶硅间距 (CPP) 的用于选择性地传导电流的第一装置。该第一装置可以是使用如图3的区域300中所描述的SADP工艺制成的晶体管。该装备还包括具有至少一个具有第二栅极长度和第二CPP的第二栅极长度器件的用于选择性地传导电流的第二装置。该第二装置可以是使用如图3的区域306或区域312中所描述的LELE工艺制成的晶体管。在另一方面,前述装置可以是被配置成执行由前述装置所述的功能的任何模块或任何设备。

[0040] 图5是示出其中可有利地采用本公开的一方面的示例性无线通信系统500的框图。出于解说目的,图5示出了三个远程单元520、530和550以及两个基站540。将认识到,无线通信系统可具有远多于此的远程单元和基站。远程单元520、530和550包括IC器件525A、525C和525B,这些IC器件包括所公开的器件。将认识到,其他设备也可包括所公开的器件,诸如基站、交换设备、和网络装备。图5示出了从基站540到远程单元520、530和550的前向链路信号580,以及从远程单元520、530和550到基站540的反向链路信号590。

[0041] 在图5中,远程单元520被示为移动电话,远程单元530被示为便携式计算机,而远程单元550被示为无线本地环路系统中的固定位置远程单元。例如,这些远程单元可以是移动电话、手持式个人通信系统 (PCS) 单元、便携式数据单元 (诸如个人数据助理)、启用GPS的设备、导航设备、机顶盒、音乐播放器、视频播放器、娱乐单元、固定位置数据单元 (诸如仪表读数装置)、或者存储或取回数据或计算机指令的其他设备、或者其组合。尽管图5解说了根据本公开的各方面的远程单元,但本公开并不被限定于所解说了的这些示例性单元。本公开的各方面可以合适地在包括所公开的器件的许多设备中使用。

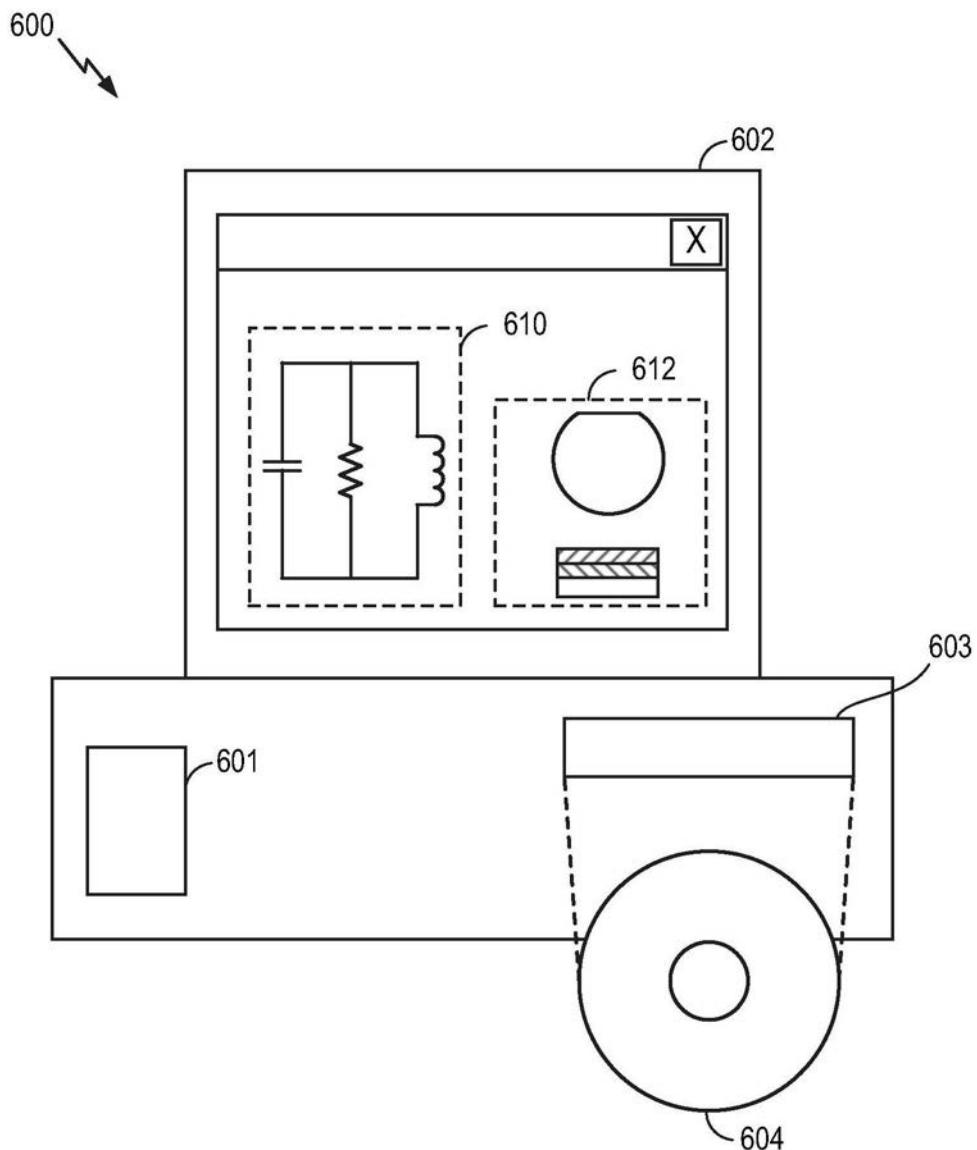

[0042] 图6是解说用于半导体组件(诸如以上公开的器件)的电路、布局以及逻辑设计的设计工作站的框图。设计工作站600包括硬盘601,该硬盘601包含操作系统软件、支持文件、以及设计软件(诸如Cadence或OrCAD)。设计工作站600还包括促成对电路610或半导体组件

612(诸如根据本公开的一方面的器件)的设计的显示器602。提供存储介质604以用于有形地存储电路610或半导体组件612的设计。电路610或半导体组件612的设计可以用文件格式(诸如GDSII或GERBER)存储在存储介质604上。存储介质604可以是CD-ROM、DVD、硬盘、闪存、或者其他合适的设备。此外,设计工作站600包括用于从存储介质604接受输入或者将输出写到存储介质604的驱动装置603。

[0043] 存储介质604上记录的数据可指定逻辑电路配置、用于光刻掩模的图案数据、或者用于串写工具(诸如电子束光刻)的掩模图案数据。该数据可进一步包括与逻辑仿真相关联的逻辑验证数据,诸如时序图或网电路。在存储介质604上提供数据通过减少用于设计半导体晶片的工艺数目来促成电路610或半导体组件612的设计。

[0044] 对于固件和/或软件实现,这些方法体系可以用执行本文所描述功能的模块(例如,规程、函数等等)来实现。有形地体现指令的机器可读介质可被用来实现本文所述的方法体系。例如,软件代码可被存储在存储器中并由处理器单元来执行。存储器可以在处理器单元内或在处理器单元外部实现。如本文所用的,术语“存储器”是指长期、短期、易失性、非易失性类型存储器、或其他存储器,而并不限于特定类型的存储器或存储器数目、或记忆存储在其上的介质的类型。

[0045] 如果以固件和/或软件实现,则功能可作为一条或多条指令或代码存储在计算机可读介质上。示例包括编码有数据结构的计算机可读介质和编码有计算机程序的计算机可读介质。计算机可读介质包括物理计算机存储介质。存储介质可以是能被计算机存取的可用介质。作为示例而非限定,此类计算机可读介质可包括RAM、ROM、EEPROM、CD-ROM或其他光盘存储、磁盘存储或其他磁存储设备、或能被用来存储指令或数据结构形式的期望程序代码且能被计算机访问的任何其他介质;如本文中所使用的盘(disk)和碟(disc)包括压缩碟(CD)、激光碟、光碟、数字多用碟(DVD)、软盘和蓝光碟,其中盘常常磁性地再现数据,而碟用激光光学地再现数据。上述的组合应当也被包括在计算机可读介质的范围内。

[0046] 除了存储在计算机可读介质上,指令和/或数据还可作为包括在通信装置中的传输介质上的信号来提供。例如,通信装置可包括具有指示指令和数据的信号的收发机。这些指令和数据被配置成使一个或多个处理器实现权利要求中叙述的功能。

[0047] 尽管已详细描述了本公开及其优势,但是应当理解,可在本文中作出各种改变、替代和变更而不会脱离如由所附权利要求所定义的本公开的技术。例如,诸如“上方”和“下方”之类的关系术语是关于基板或电子器件使用的。当然,如果该基板或电子器件被颠倒,则上方变成下方,反之亦然。此外,如果是侧面取向的,则上方和下方可指代基板或电子器件的侧面。而且,本申请的范围并非旨在被限定于说明书中所描述的过程、机器、制造、物质组成、装置、方法和步骤的特定配置。如本领域的普通技术人员将容易从本公开领会到的,根据本公开,可以利用现存或今后开发的与本文所描述的相应配置执行基本相同的功能或实现基本相同结果的过程、机器、制造、物质组成、装置、方法或步骤。因此,所附权利要求旨在将这样的过程、机器、制造、物质组成、装置、方法或步骤包括在其范围内。

[0048] 技术人员将进一步领会,结合本文的公开所描述的各种解说性逻辑框、模块、电路、和算法步骤可被实现为电子硬件、计算机软件、或两者的组合。为清楚地解说硬件与软件的这一可互换性,各种解说性组件、块、模块、电路、和步骤在上面是以其功能性的形式作一般化描述的。此类功能性是被实现为硬件还是软件取决于具体应用和施加于整体系统的

设计约束。技术人员可针对每种特定应用以不同方式来实现所描述的功能性,但此类实现决策不应被解读为致使脱离本发明的范围。

[0049] 结合本文的公开所描述的各种解说性逻辑框、模块、以及电路可用设计成执行本文中描述的功能的通用处理器、数字信号处理器(DSP)、专用集成电路(ASIC)、现场可编程门阵列(FPGA)或其他可编程逻辑器件、分立的门或晶体管逻辑、分立的硬件组件、或其任何组合来实现或执行。通用处理器可以是微处理器,但在替换方案中,处理器可以是任何常规的处理器、控制器、微控制器、或状态机。处理器还可以被实现为计算设备的组合,例如DSP与微处理器的组合、多个微处理器、与DSP核心协作的一个或更多个微处理器、或任何其他此类配置。

[0050] 结合本公开所描述的方法或算法的步骤可直接在硬件中、在由处理器执行的软件模块中、或在这两者的组合中体现。软件模块可驻留在RAM、闪存、ROM、EPROM、EEPROM、寄存器、硬盘、可移动盘、CD-ROM或本领域中所知的任何其他形式的存储介质中。示例性存储介质耦合到处理器以使得该处理器能从/向该存储介质读写信息。替换地,存储介质可以被整合到处理器。处理器和存储介质可驻留在ASIC中。ASIC可驻留在用户终端中。替换地,处理器和存储介质可作为分立组件驻留在用户终端中。

[0051] 在一个或多个示例性设计中,所描述的功能可以在硬件、软件、固件、或其任何组合中实现。如果在软件中实现,则各功能可以作为一条或多条指令或代码存储在计算机可读介质上或藉其进行传送。计算机可读介质包括计算机存储介质和通信介质两者,其包括促成计算机程序从一地向另一地转移的任何介质。存储介质可以是可被通用或专用计算机访问的任何可用介质。作为示例而非限定,这样的计算机可读介质可以包括RAM、ROM、EEPROM、CD-ROM或其他光盘存储、磁盘存储或其他磁存储设备、或能被用来携带或存储指令或数据结构形式的指定程序代码手段且能被通用或专用计算机、或者通用或专用处理器访问的任何其他介质。任何连接也被正当地称为计算机可读介质。例如,如果软件是使用同轴电缆、光纤电缆、双绞线、数字订户线(DSL)、或诸如红外、无线电、以及微波之类的无线技术从web网站、服务器、或其他远程源传送而来,则该同轴电缆、光纤电缆、双绞线、DSL、或诸如红外、无线电、以及微波之类的无线技术就被包括在介质的定义之中。如本文中所使用的盘(disk)和碟(disc)包括压缩碟(CD)、激光碟、光碟、数字多用碟(DVD)、软盘和蓝光碟,其中盘(disk)往往以磁的方式再现数据而碟(disc)用激光以光学方式再现数据。上述的组合应当也被包括在计算机可读介质的范围内。

[0052] 提供对本公开的先前描述是为使得本领域任何技术人员皆能够制作或使用本公开。对本公开的各种修改对本领域技术人员来说都将是显而易见的,且本文中所定义的普适原理可被应用到其他变型而不会脱离本公开的精神或范围。由此,本公开并非旨在被限定于本文中所描述的示例和设计,而是应被授予与本文中所公开的原理和新颖性特征相一致的最广范围。

图1A

图1B

图1C

图1D

图1E

图1F

图1G

图1H

图1I

图1J

图 2A

图 2B

图2C

212

图 2D

212

200

图 2E

图2F

图 2G

图 2H

图2I

图 2J

图 2K

图 2L

图 2M

图3A

图3B

图3C

图4

图5

图6