(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0098114

(43) 공개일자 2014년08월07일

(51) 국제특허분류(Int. Cl.)

*H04N 19/625* (2014.01) *H04N 19/60* (2014.01)

(21) 출원번호 10-2014-7015180

(22) 출원일자(국제) 2012년11월06일

심사청구일자 없음

(85) 번역문제출일자 2014년06월03일

(86) 국제출원번호 PCT/US2012/063709

(87) 국제공개번호 WO 2013/070605

국제공개일자 2013년05월16일

(30) 우선권주장

61/556,681 2011년11월07일 미국(US)

61/556,823 2011년11월07일 미국(US)

(71) 출원인

보이아이디 스케일, 인크.

미국 엘라웨어 19809, 월밍턴, 벨뷰 파크웨이

200, 스위트 300

(72) 발명자

정지에

미국 캘리포니아주 92129 샌 디에고 골드피쉬 웨

이 7785

예양

미국 캘리포니아주 92130 샌 디에고 펠먼 웨이

5001

(74) 대리인

김태홍, 김성기

전체 청구항 수 : 총 34 항

(54) 발명의 명칭 홀수-짝수 정수 변환 백그라운드를 사용하는 비디오 및 데이터 처리

### (57) 요약

정수 변환, 및/또는 정수 변환 동작을 위한, 데이터(예컨대, 잔자 비디오 데이터)를 변환하기 위한 방법, 장치 및 시스템이 개시되어 있다. 프로세서 및 메모리를 포함할 수 있는 장치가 이러한 방법, 장치 및 시스템 중에 포함되어 있다. 메모리는 변환 행렬 세트 및 변환 행렬 세트 중 임의의 변환 행렬을 사용하여 데이터(예컨대, 잔자 비디오 데이터)를 변환하기 위해 프로세서에 의해 실행가능한 명령어들을 포함할 수 있다. 변환 행렬 세트의 각각의 변환 행렬은 직교일 수 있거나, 다른 대안으로서, 거의 직교일 수 있고, 완전 인수분해가능(fully factorizable)일 수 있다. 변환 행렬 세트의 각각의 변환 행렬은 상이한 수의 요소들을 가질 수 있다. 각자의 수의 요소들의 각각의 요소는 정수이다. 각각의 변환 행렬의 기저 벡터들(basis vectors)의 노름들(norms) 간의 차는 주어진 임계값을 만족시키고, 기저 벡터들은 DCT(discrete cosine transform) 행렬의 대응하는 기저 벡터들과 비슷하다.

### 대표도

10

## 특허청구의 범위

### 청구항 1

프로세서 및 메모리를 포함하는 장치로서,

상기 메모리는 변환 행렬 세트 및 상기 변환 행렬 세트 중 임의의 변환 행렬을 사용하여 데이터를 변환하기 위해 상기 프로세서에 의해 실행가능한 명령어들을 포함하고,

상기 변환 행렬 세트의 각각의 변환 행렬은 직교성이고, 상이한 수의 요소들을 가며;

각자의 수의 요소들의 각각의 요소는 정수이고;

각각의 변환 행렬의 기저 벡터들(basis vectors)의 노름들(norms) 간의 차는 주어진 임계값을 만족시키며;

상기 기저 벡터들은 DCT(discrete cosine transform, 이산 코사인 변환) 행렬의 대응하는 기저 벡터들과 비슷한 것인 장치.

### 청구항 2

프로세서 및 메모리를 포함하는 장치로서,

상기 메모리는 변환 행렬 세트 및 상기 변환 행렬 세트 중 임의의 변환 행렬을 사용하여 데이터를 변환하기 위해 상기 프로세서에 의해 실행가능한 명령어들을 포함하고,

상기 변환 행렬 세트의 각각의 변환 행렬은 거의 직교성이고, 상이한 수의 요소들을 가지며, 완전 인수분해가능(fully factorizable)이고;

각자의 수의 요소들의 각각의 요소는 정수이고;

각각의 변환 행렬의 기저 벡터들의 노름들 간의 차는 주어진 임계값을 만족시키며;

상기 기저 벡터들은 DCT(discrete cosine transform) 행렬의 대응하는 기저 벡터들과 비슷한 것인 장치.

### 청구항 3

제1항 또는 제2항에 있어서, 상기 메모리는 상기 변환 행렬 세트를 생성하여 상기 메모리에 저장하기 위해 상기 프로세서에 의해 실행가능한 명령어들을 더 포함하는 것인 장치.

### 청구항 4

제1항 또는 제2항에 있어서, 상기 주어진 임계값은, 만족될 때, 상기 기저 벡터들의 노름들이 거의 같다는 것을 나타내는 임계값을 포함하는 것인 장치.

### 청구항 5

제1항 또는 제2항에 있어서, 상기 기저 벡터들은 왜곡의 척도에 따라 DCT(discrete cosine transform) 행렬의 대응하는 기저 벡터들과 비슷한 것인 장치.

### 청구항 6

제1항 또는 제2항에 있어서, 상기 기저 벡터들은 왜곡의 척도에 따라 - 사전 정의된 임계값을 만족시키는 왜곡의 척도에 따르는 것을 포함함 - , DCT(discrete cosine transform) 행렬의 대응하는 기저 벡터들과 비슷한 것인 장치.

### 청구항 7

제5항 또는 제6항에 있어서, 상기 왜곡의 척도는 상기 DCT 행렬에 기초하는 것인 장치.

### 청구항 8

제5항 내지 제7항 중 어느 한 항에 있어서, 상기 왜곡의 척도는 상기 기저 벡터들 및 상기 DCT 행렬의 대응하는

기저 벡터들 중 적어도 일부에 기초하는 것인 장치.

### 청구항 9

제1항 내지 제8항 중 어느 한 항에 있어서, 상기 변환 행렬 세트의 각각의 변환 행렬은 짹수 부분 및 홀수 부분으로 분해가능한 것인 장치.

### 청구항 10

제1항 내지 제9항 중 어느 한 항에 있어서, 상기 변환 행렬 세트의 각각의 변환 행렬은  $2^N \times 2^N$  요소들을 포함하고, 여기서 N은 양의 정수인 것인 장치.

### 청구항 11

제10항에 있어서, 상기 변환 행렬 세트의 각각의 변환 행렬은 짹수 부분 및 홀수 부분으로 분해가능하고, 상기 짹수 부분 및 상기 홀수 부분 각각은  $2^{N-1} \times 2^{N-1}$  요소들을 포함하는 것인 장치.

### 청구항 12

제11항에 있어서, 상기 짹수 부분은 인자 M에 의해 스케일링되고, 여기서 M은 양의 정수인 것인 장치.

### 청구항 13

제11항에 있어서, 상기 홀수 부분에 의한 변환은 단일 층 웨이블릿 분해(one-layer wavelet decomposition)로부터 얻어진 각각의 서브대역에  $2^{N-2}$  차원 변환을 적용한 결과를 포함하는 것인 장치.

### 청구항 14

제13항에 있어서, 상기 결과는 인자 M에 의해 스케일링되고, 여기서 M은 양의 정수인 것인 장치.

### 청구항 15

제14항에 있어서, 웨이블릿 변환은 Haar 변환인 것인 장치.

### 청구항 16

제1항 내지 제15항 중 어느 한 항에 있어서, 상기 장치는 비디오 인코더, 비디오 디코더, 및 무선 송수신 유닛 (wireless transmit and/or receiver unit, WTRU) 중 임의의 것인 장치.

### 청구항 17

N 차원 정수 변환을 사용하여 잔차(residual) 비디오 데이터를 처리하는 방법으로서,

예조건화 유닛(preconditioning unit)에서, 잔차 비디오 데이터의 벡터를 수신하는 단계;

변환을 위한 제1 및 제2 중간 출력 벡터들을 형성하기 위해 상기 예조건화 유닛에서 잔차 비디오 데이터의 벡터를 처리하는 단계;

제1 변환 유닛에서 제1 중간 출력 벡터(intermediate output vector)를 수신하는 단계;

$N/2$  차원 정수 짹수 부분 변환 행렬 및  $N/2$  차원 정수 홀수 부분 행렬의 기저 벡터들을 사용하여 짹수번째 변환 계수들(even-indexed transform coefficients)을 형성하기 위해 상기 제1 변환 유닛에서 상기 제1 중간 출력 벡터를 변환하는 단계;

제2 변환 유닛에서 상기 제2 중간 출력 벡터를 수신하는 단계; 및

연속적인  $N/2$  차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리함으로써 홀수번째 변환 계수들(odd-indexed transform coefficients)을 형성하기 위해 상기 제2 변환 유닛에서 상기 제2 중간 출력 벡터를 변환하는 단계를 포함하고, 상기  $N/2$  차원 정수 행렬들은 N 차원 변환 행렬의 홀수 부분을 전체적으로 인수분해하는 것인 잔차 비디오 데이터 처리 방법.

**청구항 18**

제17항에 있어서, 상기 연속적인  $N/2$  차원 정수 행렬들은  $N/4$  차원 홀수 부분 행렬에 기초하고, 연속적인  $N/2$  차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리하는 것은,

상기 제2 중간 출력 벡터의 제1 서브대역 및 제2 서브대역을 생성하는 것; 및

상기  $N/4$  차원 홀수 부분 행렬을 상기 제1 서브대역 및 상기 제2 서브대역 각각에 적용하는 것을 포함하는 것인 방법.

**청구항 19**

제17항에 있어서, 상기  $N$  차원 정수 변환은 8 차원 정수 변환이고, 상기 연속적인  $N/2$  차원 정수 행렬들은 3개의 연속적인 4 차원 정수 행렬들을 포함하는 것인 방법.

**청구항 20**

제19항에 있어서, 제1 연속적인 4 차원 정수 행렬은 하나의 대각선을 따른 우 대칭(even symmetry) 및 다른 대각선을 따른 기 대칭(odd symmetry)을 포함하고, 제2 연속적인 4 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 영 대칭(zero symmetry)을 포함하며, 제3 연속적인 4 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 기 대칭을 포함하는 것인 방법.

**청구항 21**

제17항에 있어서, 상기  $N$  차원 정수 변환은 16 차원 정수 변환이고, 상기 연속적인  $N/2$  차원 정수 행렬들은 4개의 연속적인 8 차원 정수 행렬들을 포함하는 것인 방법.

**청구항 22**

제21항에 있어서, 제1 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 기 대칭을 포함하고, 제2 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 영 대칭을 포함하며, 제3 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 영 대칭을 포함하고, 제4 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 기 대칭을 포함하는 것인 방법.

**청구항 23**

제17항에 있어서, 상기  $N$  차원 정수 변환은 8 차원 정수 변환이고, 연속적인  $N/2$  차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리하는 것은,

제1 중간 변환 요소 세트를 형성하기 위해 제1 4 차원 정수 행렬을 통해 상기 제2 중간 출력 벡터를 처리하는 것;

제2 중간 변환 요소 세트를 형성하기 위해 제2 4 차원 정수 행렬을 통해 상기 제1 중간 변환 요소 세트를 처리하는 것; 및

상기 홀수번째 변환 계수들을 형성하기 위해 제3 4차원 정수 행렬을 통해 상기 제2 중간 변환 요소 세트를 처리하는 것을 포함하는 것인 방법.

**청구항 24**

제17항에 있어서, 상기  $N$  차원 정수 변환은 16 차원 정수 변환이고, 연속적인  $N/2$  차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리하는 것은,

제1 중간 변환 요소 세트를 형성하기 위해 제1 8 차원 정수 행렬을 통해 상기 제2 중간 출력 벡터를 처리하는 것;

제2 중간 변환 요소 세트를 형성하기 위해 제2 8 차원 정수 행렬을 통해 상기 제1 중간 변환 요소 세트를 처리하는 것;

제3 중간 변환 요소 세트를 형성하기 위해 제3 8 차원 정수 행렬을 통해 상기 제2 중간 변환 요소 세트를 처리

하는 것; 및

상기 홀수번째 변환 계수들을 형성하기 위해 제4 8차원 정수 행렬을 통해 상기 제3 중간 변환 요소 세트를 처리하는 것을 포함하는 것인 방법.

### 청구항 25

제17항에 있어서, 상기 N 차원 정수 변환은 32 차원 정수 변환이고, 연속적인 N/2 차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리하는 것은,

제1 중간 변환 요소 세트를 형성하기 위해 제1 16 차원 정수 행렬을 통해 상기 제2 중간 출력 벡터를 처리하는 것;

제2 중간 변환 요소 세트를 형성하기 위해 제2 16 차원 정수 행렬을 통해 상기 제1 중간 변환 요소 세트를 처리하는 것;

제3 중간 변환 요소 세트를 형성하기 위해 제3 16 차원 정수 행렬을 통해 상기 제2 중간 변환 요소 세트를 처리하는 것; 및

상기 제3 중간 변환 요소 세트를 각자의 4 차원 정수 행렬에 의한 변환을 위한 4개의 벡터들로 분해하기 위해 제4 16 차원 정수 행렬을 통해 상기 제3 중간 변환 요소 세트를 처리하는 것; 및

상기 홀수번째 변환 계수들을 형성하기 위해 각자의 4 차원 정수 행렬에 4개의 벡터들 각각을 적용하는 것을 포함하는 것인 방법.

### 청구항 26

N 차원 정수 변환을 사용하여 잔차 비디오 데이터를 처리하는 장치로서,

상기 장치는 예조건화 유닛, 제1 변환 유닛, 및 제2 변환 유닛을 포함하고,

상기 예조건화 유닛은 잔차 비디오 데이터의 벡터를 수신하도록 구성되어 있고;

상기 예조건화 유닛은 변환을 위한 제1 및 제2 중간 출력 벡터들을 형성하기 위해 상기 잔차 비디오 데이터의 벡터를 처리하도록 구성되어 있으며;

상기 제1 변환 유닛은 상기 제1 중간 출력 벡터를 수신하도록 구성되어 있고;

상기 제1 변환 유닛은 N/2 차원 정수 짹수 부분 변환 행렬 및 N/2 차원 정수 홀수 부분 행렬의 기저 벡터들을 사용하여 짹수번째 변환 계수들을 형성하기 위해 상기 제1 중간 출력 벡터를 변환하도록 구성되어 있으며;

상기 제2 변환 유닛은 상기 제2 중간 출력 벡터를 수신하도록 구성되어 있고;

상기 제2 변환 유닛은 연속적인 N/2 차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리함으로써 홀수번째 변환 계수들을 형성하기 위해 상기 제2 중간 출력 벡터를 변환하도록 구성되어 있으며, 상기 N/2 차원 정수 행렬들은 N 차원 변환 행렬의 홀수 부분을 전체적으로 인수분해하는 것인 잔차 비디오 데이터 처리 장치.

### 청구항 27

제26항에 있어서, 상기 연속적인 N/2 차원 정수 행렬들은 N/4 차원 홀수 부분 행렬에 기초하고, 상기 제2 변환 유닛은 상기 제2 중간 출력 벡터의 제1 서브대역 및 제2 서브대역을 생성하고, 연속적인 N/2 차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리할 때 상기 N/4 차원 홀수 부분 행렬을 상기 제1 서브대역 및 상기 제2 서브대역 각각에 적용하도록 구성되어 있는 것인 장치.

### 청구항 28

제26항에 있어서, 상기 N 차원 정수 변환은 8 차원 정수 변환이고, 상기 연속적인 N/2 차원 정수 행렬들은 3개의 연속적인 4 차원 정수 행렬들을 포함하는 것인 장치.

### 청구항 29

제28항에 있어서, 제1 연속적인 4 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 기 대칭을 포함하고, 제2 연속적인 4 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 영

대칭을 포함하며, 제3 연속적인 4 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 기 대칭을 포함하는 것인 장치.

### 청구항 30

제26항에 있어서, 상기 N 차원 정수 변환은 16 차원 정수 변환이고, 상기 연속적인 N/2 차원 정수 행렬들은 4개의 연속적인 4 차원 정수 행렬들을 포함하는 것인 장치.

### 청구항 31

제30항에 있어서, 제1 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 기 대칭을 포함하고, 제2 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 영 대칭을 포함하며, 제3 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 영 대칭을 포함하고, 제4 연속적인 8 차원 정수 행렬은 하나의 대각선을 따른 우 대칭 및 다른 대각선을 따른 기 대칭을 포함하는 것인 장치.

### 청구항 32

제26항에 있어서, 상기 N 차원 정수 변환은 8 차원 정수 변환이고, 연속적인 N/2 차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리할 때, 상기 제2 변환 유닛은,

제1 중간 변환 요소 세트를 형성하기 위해 제1 4 차원 정수 행렬을 통해 상기 제2 중간 출력 벡터를 처리하고;

제2 중간 변환 요소 세트를 형성하기 위해 제2 4 차원 정수 행렬을 통해 상기 제1 중간 변환 요소 세트를 처리하며;

상기 홀수번째 변환 계수들을 형성하기 위해 제3 4차원 정수 행렬을 통해 상기 제2 중간 변환 요소 세트를 처리하도록 구성되어 있는 것인 장치.

### 청구항 33

제26항에 있어서, 상기 N 차원 정수 변환은 16 차원 정수 변환이고, 연속적인 N/2 차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리할 때, 상기 제2 변환 유닛은,

제1 중간 변환 요소 세트를 형성하기 위해 제1 8 차원 정수 행렬을 통해 상기 제2 중간 출력 벡터를 처리하고;

제2 중간 변환 요소 세트를 형성하기 위해 제2 8 차원 정수 행렬을 통해 상기 제1 중간 변환 요소 세트를 처리하며;

제3 중간 변환 요소 세트를 형성하기 위해 제3 8 차원 정수 행렬을 통해 상기 제2 중간 변환 요소 세트를 처리하고;

상기 홀수번째 변환 계수들을 형성하기 위해 제4 8차원 정수 행렬을 통해 상기 제3 중간 변환 요소 세트를 처리하도록 구성되어 있는 것인 장치.

### 청구항 34

제26항에 있어서, 상기 N 차원 정수 변환은 32 차원 정수 변환이고, 연속적인 N/2 차원 정수 행렬들을 통해 상기 제2 중간 출력 벡터를 처리할 때, 상기 제2 변환 유닛은,

제1 중간 변환 요소 세트를 형성하기 위해 제1 16 차원 정수 행렬을 통해 상기 제2 중간 출력 벡터를 처리하고;

제2 중간 변환 요소 세트를 형성하기 위해 제2 16 차원 정수 행렬을 통해 상기 제1 중간 변환 요소 세트를 처리하며;

제3 중간 변환 요소 세트를 형성하기 위해 제3 16 차원 정수 행렬을 통해 상기 제2 중간 변환 요소 세트를 처리하고;

상기 제3 중간 변환 요소 세트를 각자의 4 차원 정수 행렬에 의한 변환을 위한 4개의 벡터들로 분해하기 위해 제4 16 차원 정수 행렬을 통해 상기 제3 중간 변환 요소 세트를 처리하며;

상기 홀수번째 변환 계수들을 형성하기 위해 각자의 4 차원 정수 행렬에 상기 4개의 벡터들 각각을 적용하도록

구성되어 있는 것인 장치.

## 명세서

### 배경기술

[0001]

디지털 비디오 기능이 디지털 텔레비전, 디지털 직접 방송 시스템, 무선 방송 시스템, PDA(personal digital assistant), 랩톱 또는 데스크톱 컴퓨터, 디지털 카메라, 디지털 레코딩 장치, 비디오 게임 장치, 비디오 게임 콘솔, 셀룰러, 위성 또는 기타 무선 전화 등을 비롯한 광범위한 장치들에 포함될 수 있다. 많은 디지털 비디오 장치들은, 디지털 비디오 정보를 보다 효율적으로 전송 및 수신하기 위해, MPEG(Moving Picture Experts Group)에 의해 정의된 표준들(MPEG-2, MPEG-4 등); 및 ITU(International Telecommunications Union)에 의해 정의된 표준들[ITU-T H.263 또는 ITU-T H.264/MPEG-4, Part 10, AVC(Advanced Video Coding)], 및 이러한 표준들의 확장들에 기술되어 있는 것과 같은 비디오 압축 기법들을 구현한다.

[0002]

비디오 압축 기법들은 비디오 시퀀스에 본질적인 중복성을 감소시키거나 제거하기 위해 공간 예측(spatial prediction) 및/또는 시간 예측(temporal prediction)을 수행할 수 있다. 블록 기반 비디오 코딩의 경우, 비디오 프레임 또는 슬라이스가 블록들("비디오 블록들")로 분할될 수 있다. 다양한 코딩 기법들에 따르면, 인트라 코딩된(intra-coded)(I) 프레임 또는 슬라이스 내의 비디오 블록들은 이웃 블록들에 대한 공간 예측을 사용해 인코딩된다. 인터 코딩된(inter-coded)(P 또는 B) 프레임 또는 슬라이스 내의 비디오 블록들은 동일한 프레임 또는 슬라이스 내의 이웃 비디오 블록들에 대한 공간 예측 또는 다른 참조 프레임들 내의 비디오 블록들에 대한 시간 예측을 사용할 수 있다.

### 발명의 내용

[0003]

정수 변환, 및/또는 정수 변환 동작을 위한, 데이터[예컨대, 잔차(residual) 비디오 데이터]를 변환하기 위한 방법, 장치 및 시스템이 개시되어 있다. 프로세서 및 메모리를 포함할 수 있는 장치가 이러한 방법, 장치 및 시스템 중에 포함되어 있다. 메모리는 변환 행렬 세트 및 변환 행렬 세트 중 임의의 변환 행렬을 사용하여 데이터(예컨대, 잔차 비디오 데이터)를 변환하기 위해 프로세서에 의해 실행가능한 명령어들을 포함할 수 있다. 변환 행렬 세트의 각각의 변환 행렬은 직교성이고, 상이한 수의 요소들을 가진다. 각자의 수의 요소들의 각각의 요소는 정수이다. 각각의 변환 행렬의 기저 벡터들(basis vectors)의 노름들(norms) 간의 차는 주어진 임계값을 만족시키고, 기저 벡터들은 DCT(discrete cosine transform, 이산 코사인 변환) 행렬의 대응하는 기저 벡터들과 비슷하다.

[0004]

대안으로서, 변환 행렬 세트의 각각의 변환 행렬은 거의 직교성이고, 상이한 수의 요소들을 가지며, 완전 인수 분해가능(fully factorizable)일 수 있다.

[0005]

또한, N 차원 정수 변환(order-N integer transform)을 사용하여 잔차 비디오 데이터를 처리하는 방법이 이 방법, 장치 및 시스템 중에 포함된다. 이 방법은, 제1 예조건화 유닛(preconditioning unit)에서, (예컨대, 잔차) 비디오 데이터의 벡터를 수신하는 단계 및 변환을 위한 제1 및 제2 중간 출력 벡터들을 형성하기 위해 제1 예조건화 유닛에서 (예컨대, 잔차) 비디오 데이터의 벡터를 처리하는 단계를 포함할 수 있다. 이 방법은 또한 제1 변환 유닛에서 제1 중간 출력 벡터(intermediate output vector)를 수신하는 단계 및 N/2 차원 정수 짹수 부분 변환 행렬(even part transform matrix) 및 N/2 차원 정수 홀수 부분 행렬의 기저 벡터들을 사용하여 짹수번째 변환 계수들(even-indexed transform coefficients)을 형성하기 위해 제1 변환 유닛에서 제1 중간 출력 벡터를 변환하는 단계를 포함할 수 있다. 이 방법은 제2 변환 유닛에서 제2 중간 출력 벡터를 수신하는 단계 및 연속적인 N/2 차원 정수 행렬들을 통해 제2 중간 출력 벡터를 처리함으로써 홀수번째 변환 계수들(odd-indexed transform coefficients)을 형성하기 위해 제2 변환 유닛에서 제2 중간 출력 벡터를 변환하는 단계를 더 포함할 수 있다. N/2 차원 정수 행렬들은 N 차원 변환 행렬의 홀수 부분을 전체적으로 인수분해할 수 있다.

### 도면의 간단한 설명

[0006]

예로서 본 명세서에 첨부된 도면들과 관련하여 이하의 이하의 상세한 설명으로부터 보다 상세하게 이해될 수 있다. 이러한 첨부 도면 내의 도면들은, 상세한 설명과 같이, 예이다. 그에 따라, 도면 및 상세한 설명은 제한하는 것으로 생각되어서는 안되며, 다른 똑같이 효과적인 예가 가능하고 있을 수 있다. 게다가, 도면에서 유사한 참조 번호는 유사한 요소를 나타낸다.

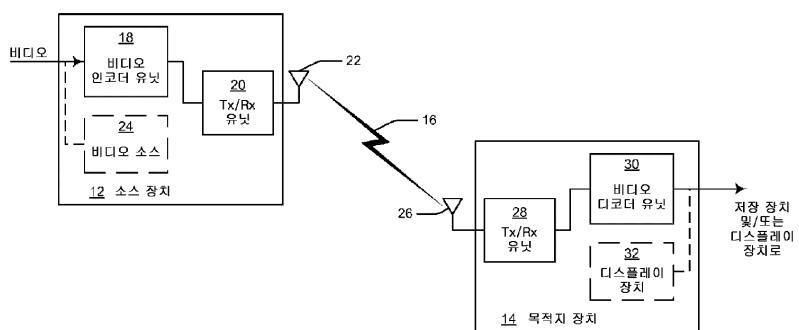

도 1a는 하나 이상의 실시예들이 수행 및/또는 구현될 수 있는 한 예시적인 비디오 인코딩 및 디코딩 시스템을

나타낸 블록도.

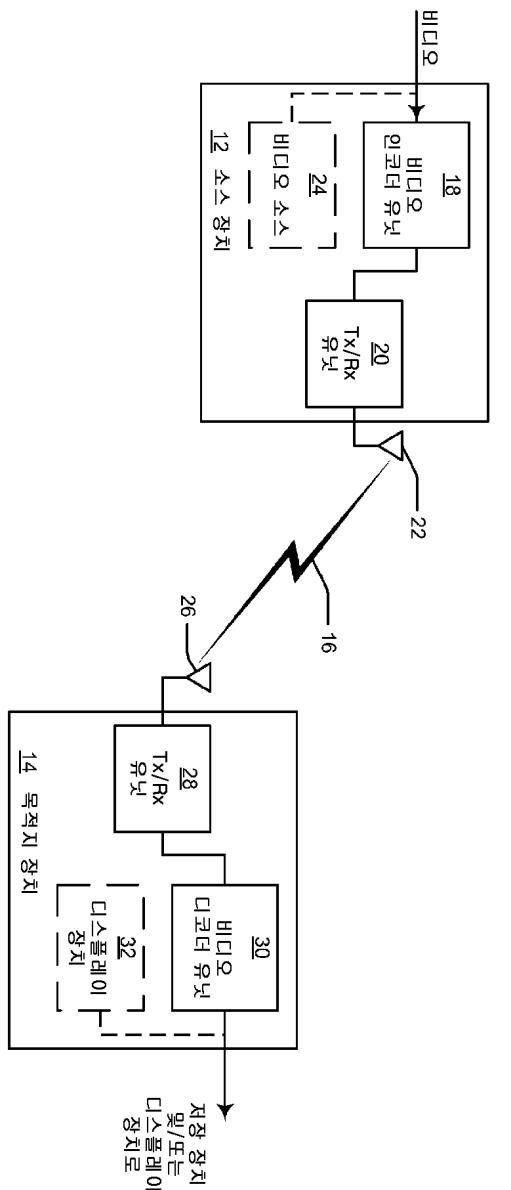

도 1b는 도 1a의 시스템 등의 비디오 인코딩 및/또는 디코딩 시스템에서 사용하기 위한 한 예시적인 비디오 인코더 유닛을 나타낸 블록도.

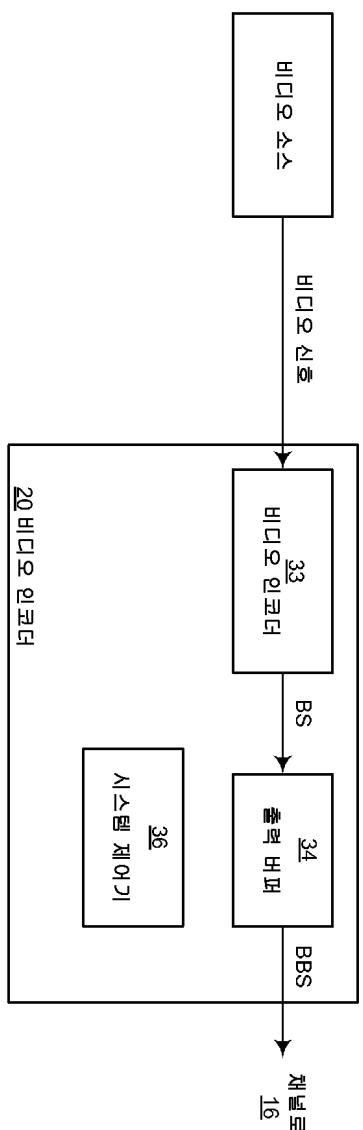

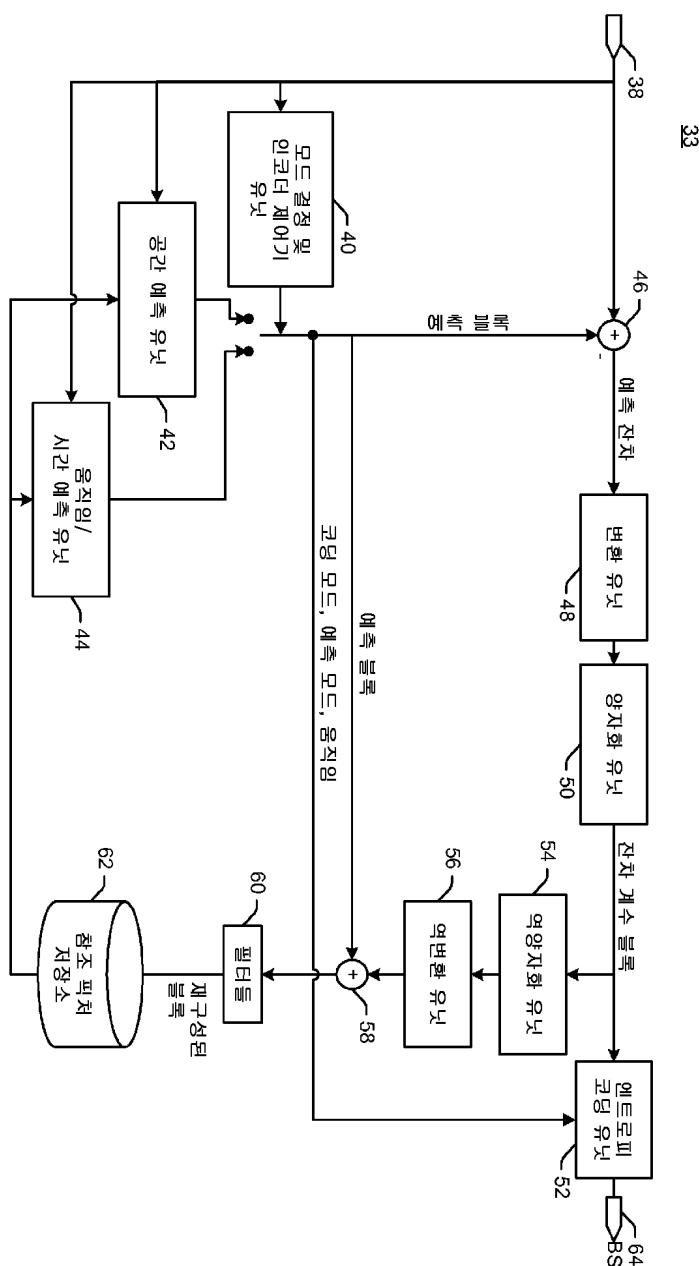

도 1c는 도 1a 및 도 1b의 비디오 인코더 유닛 등의 비디오 인코더 유닛에서 사용하기 위한 비디오 인코더의 한 예를 나타낸 블록도.

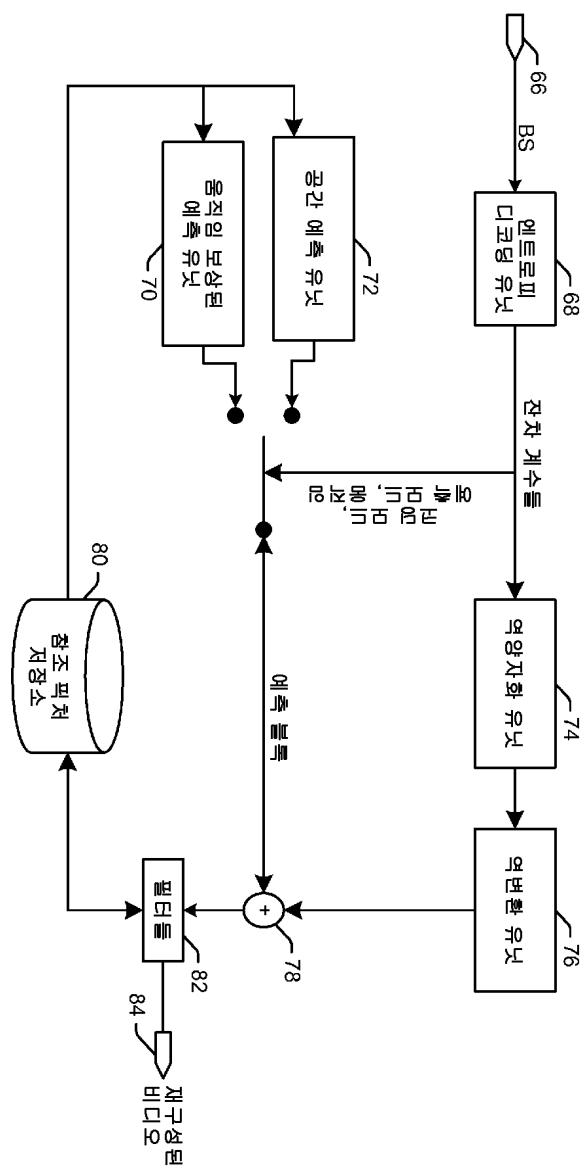

도 1d는 도 1a 및 도 1b의 비디오 디코더 유닛 등의 비디오 디코더 유닛에서 사용하기 위한 비디오 디코더의 한 예를 나타낸 블록도.

도 2는 비제한적인 실시예에 따른 한 예시적인 32 차원 변환 행렬을 나타낸 도면.

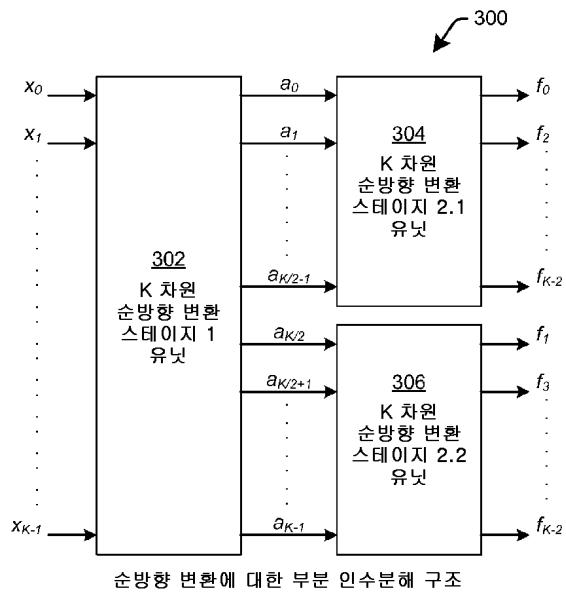

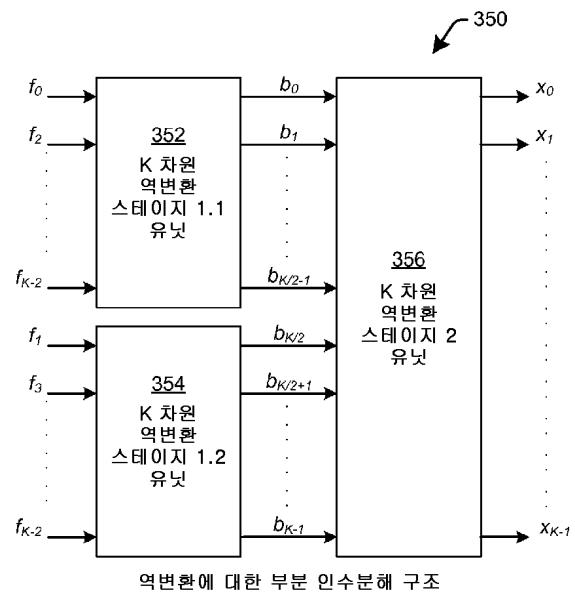

도 3a 및 도 3b는 K 차원 변환에 대한 부분 인수분해(partial factorization)를 수행하는 한 예시적인 구조를 나타낸 블록도.

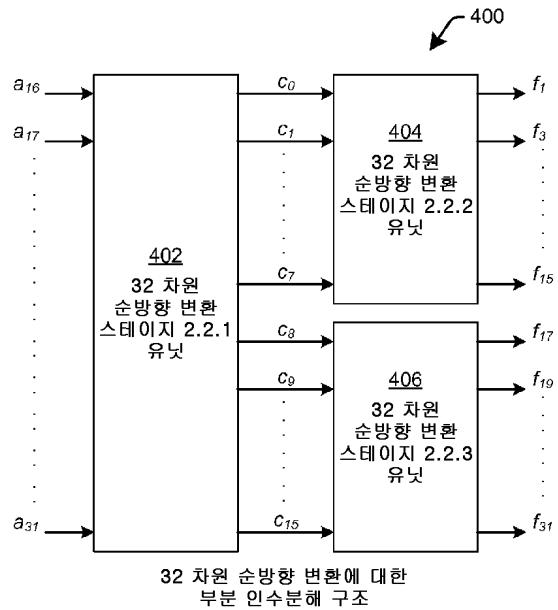

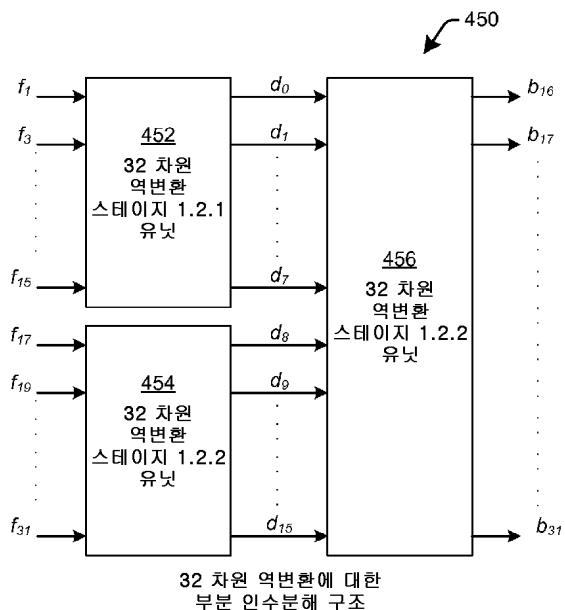

도 4a 및 도 4b는 32 차원 변환에 대한 부분 인수분해를 수행하는 한 예시적인 구조를 나타낸 블록도.

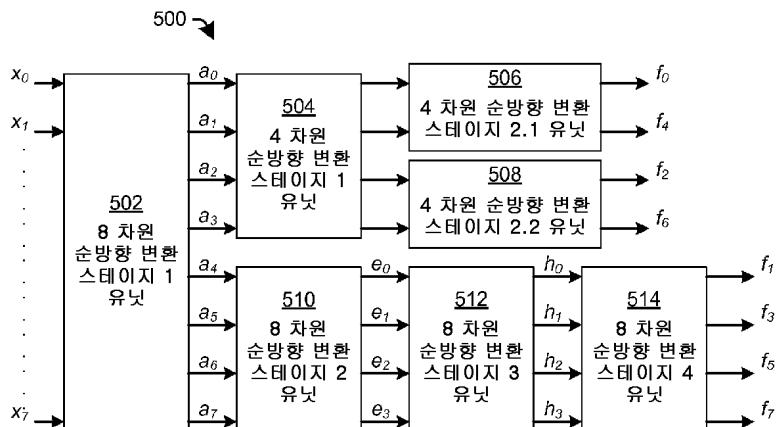

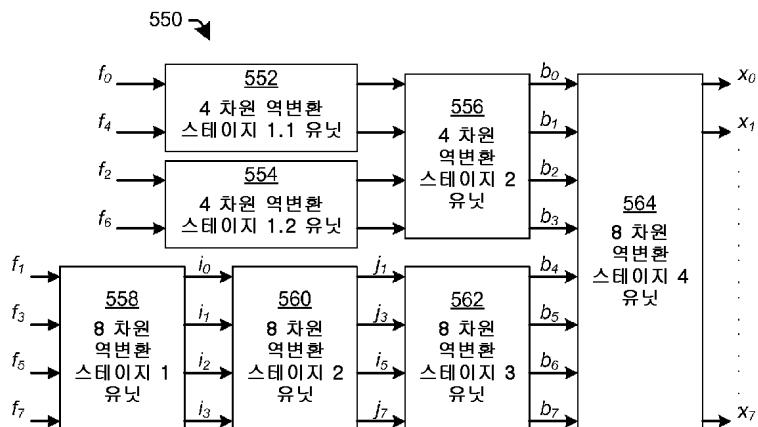

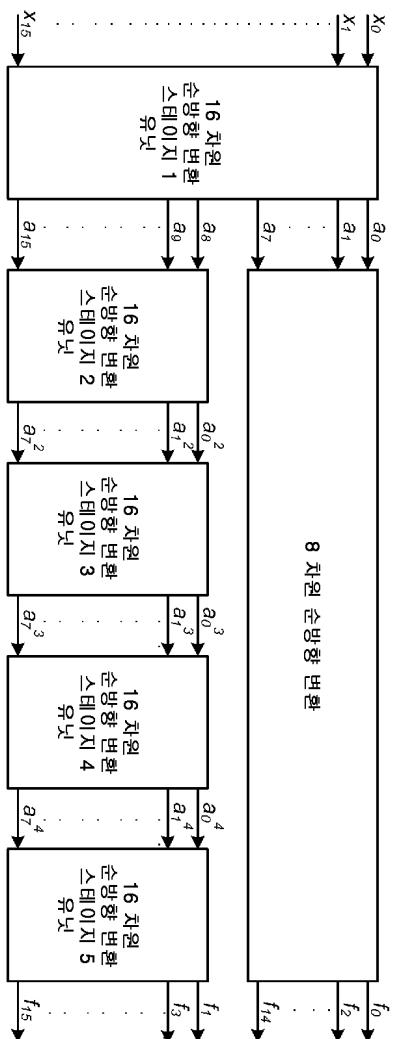

도 5a 및 도 5b는 8 차원 변환에 대한 완전 인수분해(full factorization)를 수행하는 한 예시적인 구조를 나타낸 블록도.

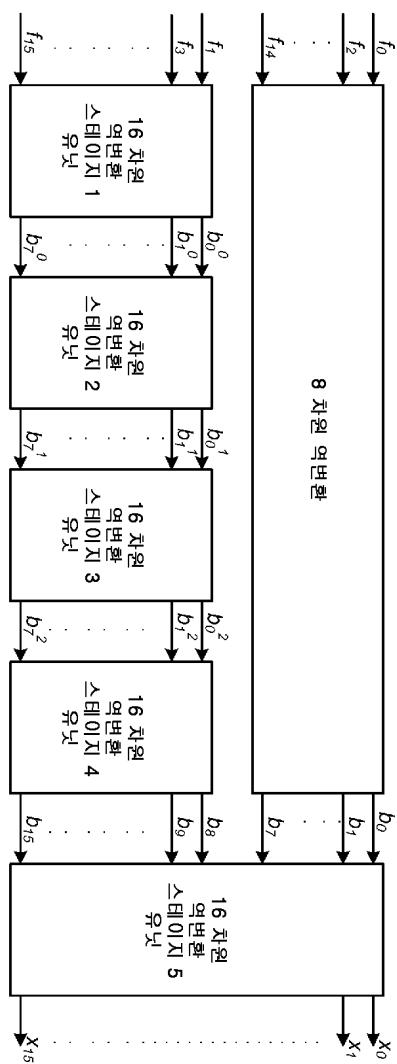

도 6a 및 도 6b는 16 차원 변환에 대한 완전 인수분해를 수행하는 한 예시적인 구조를 나타낸 블록도.

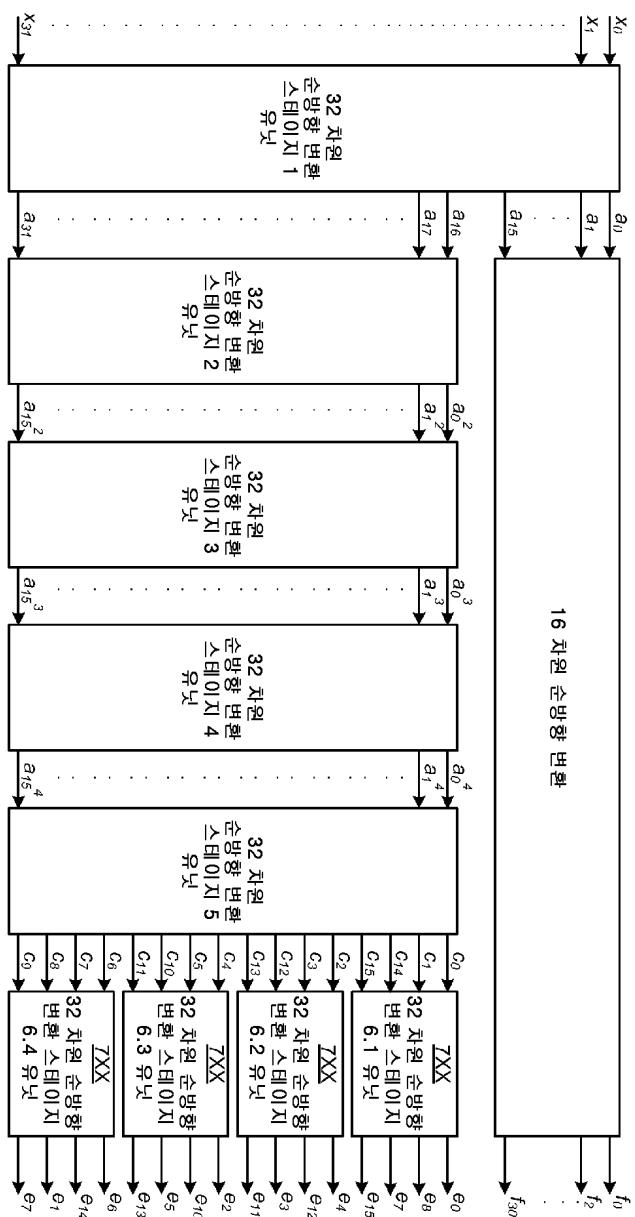

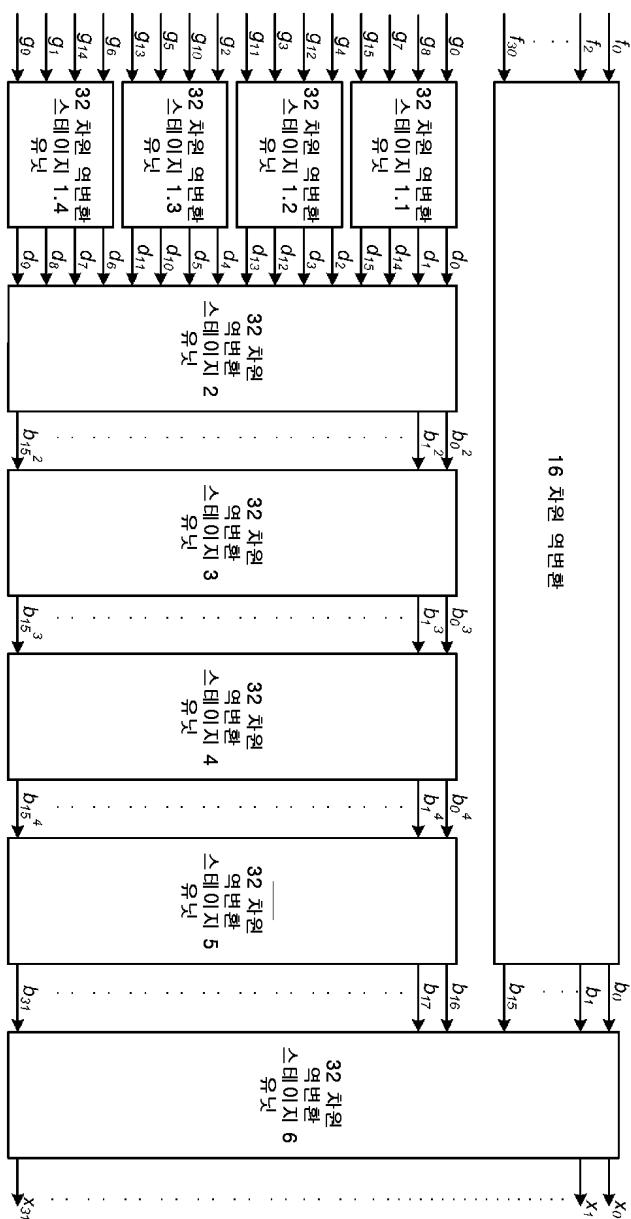

도 7a 및 도 7b는 32 차원 변환에 대한 완전 인수분해를 수행하는 한 예시적인 구조를 나타낸 블록도.

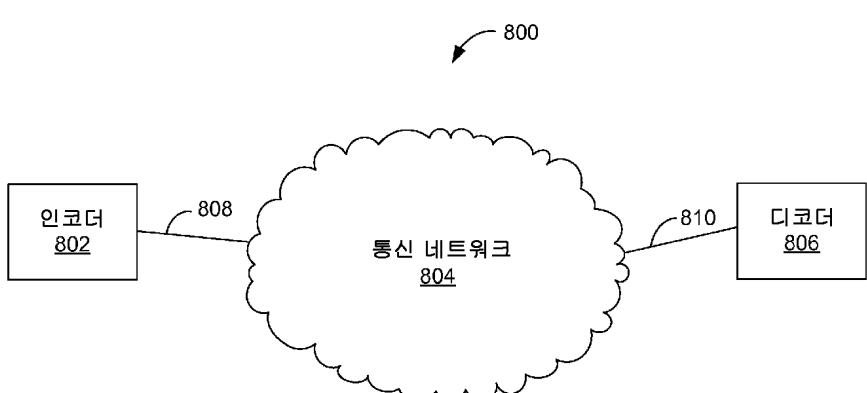

도 8은 비제한적인 실시예에 따른 통신 시스템을 나타낸 도면.

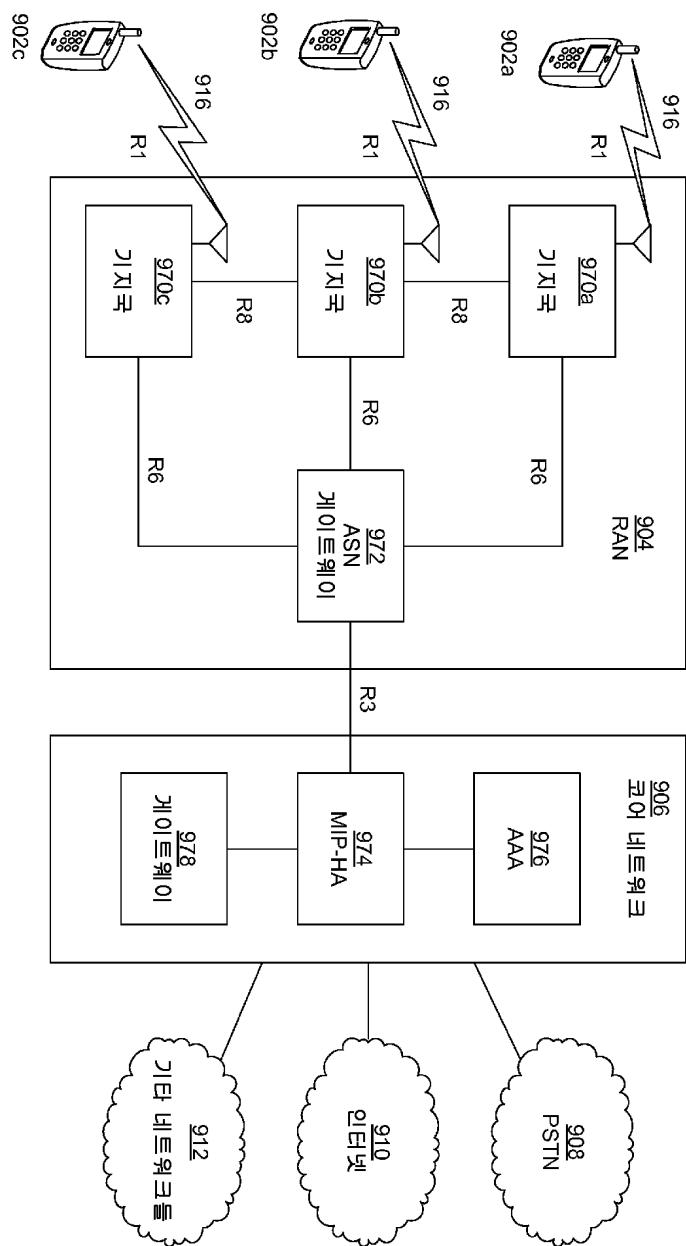

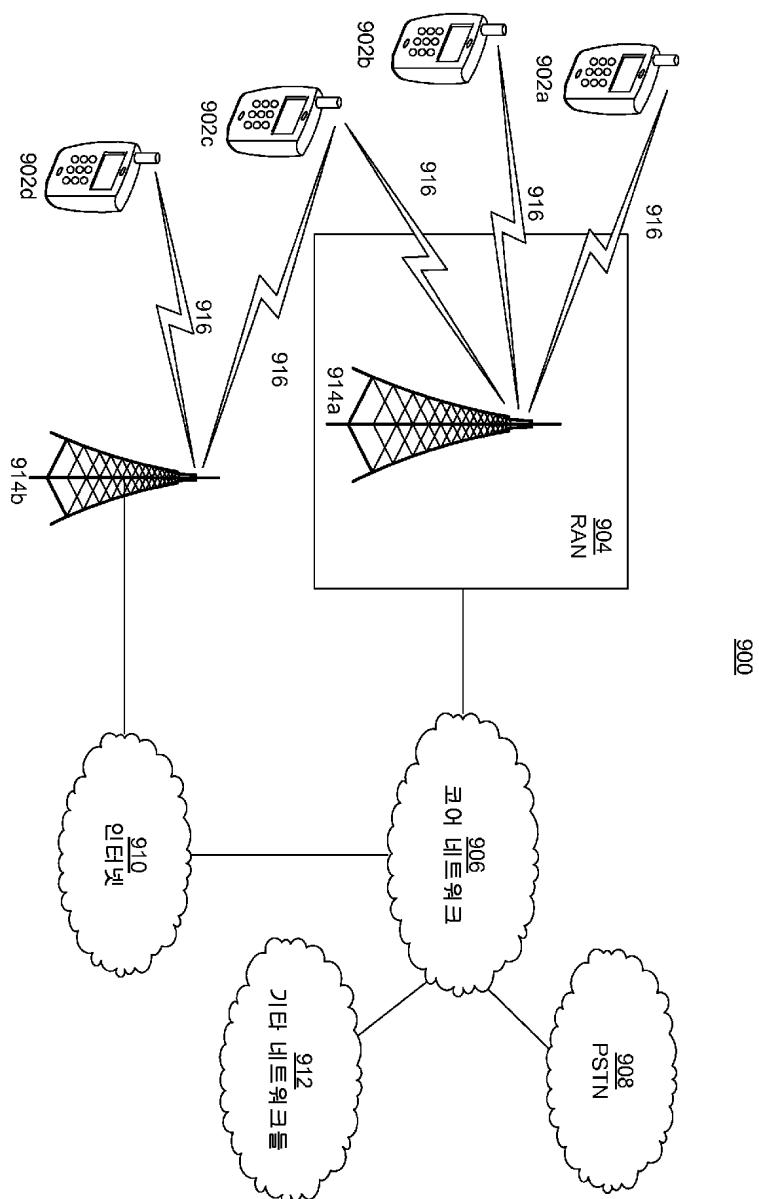

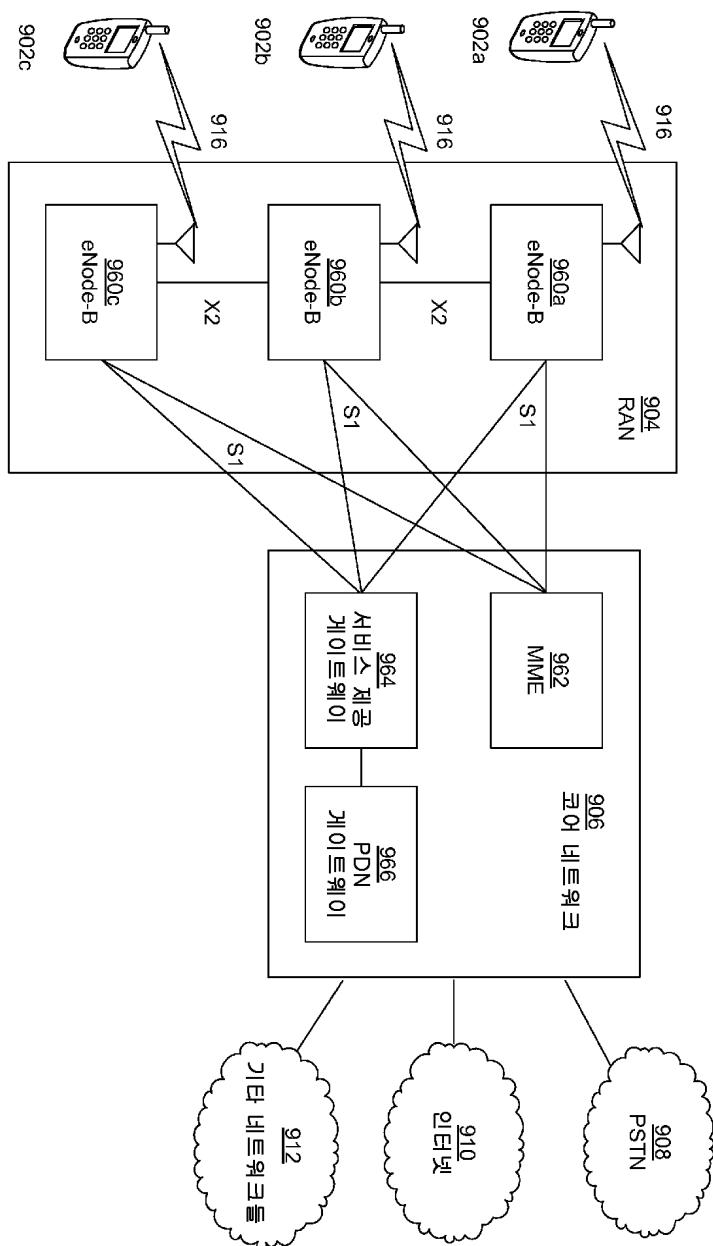

도 9a는 하나 이상의 개시된 실시예들이 구현될 수 있는 예시적인 통신 시스템의 시스템도.

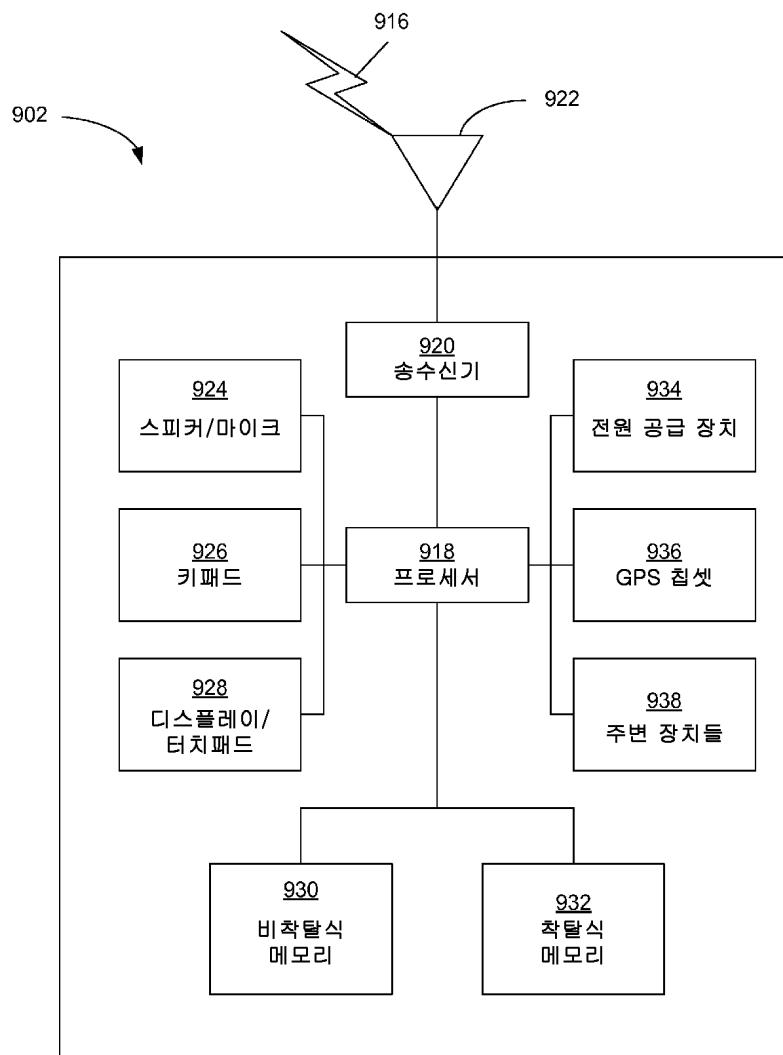

도 9b는 도 9a에 예시된 통신 시스템 내에서 사용될 수 있는 한 예시적인 WTRU(wireless transmit/receive unit, 무선 송수신 유닛)의 시스템도.

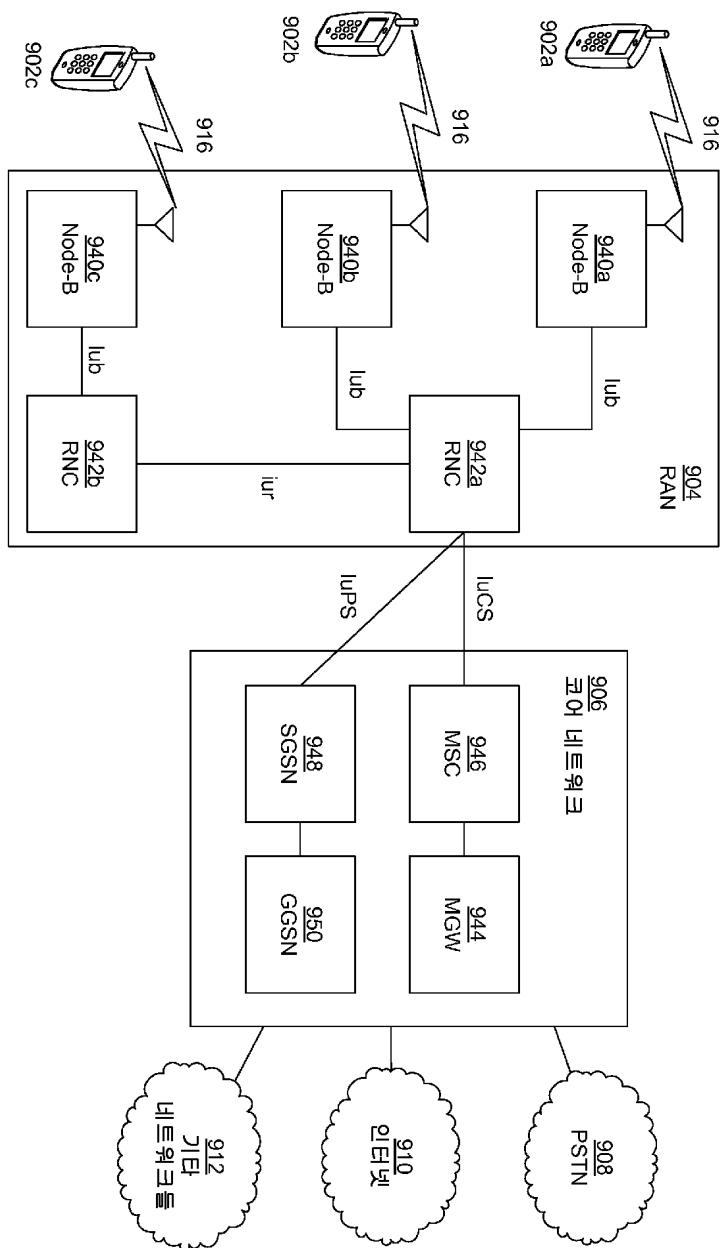

도 9c, 도 9d 및 도 9e는 도 9a에 예시되어 있는 통신 시스템 내에서 사용될 수 있는 예시적인 무선 액세스 네트워크 및 예시적인 코어 네트워크의 시스템도.

### 발명을 실시하기 위한 구체적인 내용

[0007]

이하의 상세한 설명에, 본 명세서에 개시된 실시예들 및 예들에 대한 완전한 이해를 제공하기 위해 다수의 구체적인 상세가 기재되어 있다. 그렇지만, 이러한 실시예들 및 예들이 본 명세서에 기재된 구체적인 상세의 일부 또는 전부를 사용하지 않고 실시될 수 있다는 것을 잘 알 것이다. 다른 경우들에, 이하의 설명을 모호하게 하지 않기 위해 공지의 방법, 절차, 구성요소 및 회로에 대해서는 상세히 설명하지 않았다. 게다가, 본 명세서에 구체적으로 기술되어 있지 않은 실시예들 및 예들이 본 명세서에 개시되어 있는 실시예들 및 기타 예들 대신에 또는 그와 함께 실시될 수 있다.

[0008]

### 예시적인 시스템 아키텍처

[0009]

도 1a는 하나 이상의 실시예들이 수행 및/또는 구현될 수 있는 한 예시적인 비디오 인코딩 및 디코딩 시스템(10)을 나타낸 블록도이다. 시스템(10)은 인코딩된 비디오 정보를 통신 채널(16)을 통해 목적지 장치(14)로 전송하는 소스 장치(12)를 포함할 수 있다.

[0010]

소스 장치(12) 및 목적지 장치(14)는 매우 다양한 장치들 중 임의의 것일 수 있다. 어떤 실시예들에서, 소스 장치(12) 및 목적지 장치는 통신 채널(16) - 이 경우에, 통신 채널(16)은 무선 링크를 포함함 - 을 통해 비디오 정보를 전달할 수 있는 무선 핸드셋 또는 임의의 무선 장치 등의 WTRU(wireless transmit/receive unit, 무선 송수신 유닛)를 포함할 수 있다. 그렇지만, 본 명세서에 명시적으로, 암시적으로 및/또는 본질적으로 기술되거나, 개시되거나 다른 방식으로 제공된(총칭하여 "제공된") 방법, 장치 및 시스템이 무선 응용 또는 설정으로 꼭 제한되는 것은 아니다. 예를 들어, 이를 기법은 공중파 텔레비전 방송, 케이블 텔레비전 전송, 위성 텔레비전 전송, 인터넷 비디오 전송, 저장 매체 상에 인코딩되어 있는 인코딩된 디지털 비디오, 또는 기타 시나리오들에 적용될 수 있다. 그에 따라, 통신 채널(16)은 인코딩된 비디오 데이터의 전송에 적합한 무선 또는 유선 매체의 임의의 조합을 포함할 수 있고/있거나 그러한 무선 또는 유선 매체의 임의의 조합일 수 있다.

[0011]

소스 장치(12)는 비디오 인코더 유닛(18), 송수신(Tx/Rx) 유닛(20), 및 Tx/Rx 요소(22)를 포함할 수 있다. 도시

된 바와 같이, 소스 장치(12)는 선택적으로 비디오 소스(24)를 포함할 수 있다. 목적지 장치(14)는 Tx/Rx 요소(26), Tx/Rx 유닛(28), 및 비디오 디코더 유닛(30)을 포함할 수 있다. 도시된 바와 같이, 목적지 장치(14)는 선택적으로 디스플레이 장치(32)를 포함할 수 있다. Tx/Rx 유닛들(20, 28) 각각은 송신기, 수신기, 또는 송신기와 수신기의 조합(예컨대, 송수신기, 송신기-수신기)일 수 있거나 이들을 포함할 수 있다. Tx/Rx 요소들(22, 26) 각각은, 예를 들어, 안테나일 수 있다. 본 개시 내용에 따르면, 소스 장치(12)의 비디오 인코더 유닛(18) 및/또는 목적지 장치의 비디오 디코더 유닛(30)은 본 명세서에 제공된 코딩 기법들을 적용하도록 설정 및/또는 구성(총칭하여 "구성")되어 있을 수 있다.

[0012] 소스 및 목적지 장치들(12, 14)은 기타 요소들/구성요소들 또는 설비들을 포함할 수 있다. 예를 들어, 소스 장치(12)는 외부 비디오 소스로부터 비디오 데이터를 수신하도록 구성되어 있을 수 있다. 그리고, 목적지 장치(14)는, (예컨대, 일체형) 디스플레이 장치(32)를 포함하는 것 및/또는 사용하는 것보다는, 외부 디스플레이 장치(도시 생략)와 인터페이스할 수 있다. 어떤 실시예들에서, 비디오 인코더 유닛(18)에 의해 발생된 데이터 스트림은, 데이터를 반송과 신호 상에 변조할 필요 없이(예컨대, 직접 디지털 전송에 의해), 다른 장치들로 전달될 수 있고, 여기서 다른 장치들은 전송을 위해 데이터를 변조할 수 있거나 그렇지 않을 수 있다.

[0013] 도 1의 예시된 시스템(10)은 한 예에 불과하다. 본 명세서에 제공된 기법들은 임의의 디지털 비디오 인코딩 및/또는 디코딩 장치에 의해 수행될 수 있다. 비록 일반적으로 본 명세서에 제공된 기법들이 개별적인 비디오 인코딩 및/또는 비디오 디코딩 장치들에 의해 수행되지만, 기법들이 또한 결합된 비디오 인코더/디코더(통상적으로, "코텍"이라고 함)에 의해 수행될 수 있다. 더욱이, 본 명세서에 제공된 기법들은 또한 비디오 전처리기(video preprocessor) 등에 의해 수행될 수 있다. 소스 장치(12) 및 목적지 장치(14)는 이러한 코딩 장치들의 예에 불과하고, 여기서 소스 장치(12)는 목적지 장치(14)로 전송하기 위한 인코딩된 비디오 정보를 발생시킨다[및/또는 비디오 데이터를 수신하고 목적지 장치(14)로 전송하기 위한 인코딩된 비디오 정보를 발생시킨다]. 어떤 실시예들에서, 장치들(12, 14)은 실질적으로 대칭적으로 동작할 수 있고, 따라서 장치들(12, 14) 각각은 비디오 인코딩 및 디코딩 구성요소들 및/또는 요소들(총칭하여 "요소들")을 포함한다. 따라서, 시스템(10)은, 예컨대, 비디오 스트리밍, 비디오 재생, 비디오 방송, 화상 전화 및 화상 회의 중 임의의 것을 위해, 장치들(12, 14) 사이의 단방향 및 양방향 비디오 전송 중 임의의 것을 지원할 수 있다. 어떤 실시예들에서, 소스 장치(12)는, 예를 들어, 하나 이상의 목적지 장치들에 대한 인코딩된 비디오 정보를 발생시키도록(및/또는 비디오 데이터를 수신하고 하나 이상의 목적지 장치들에 대한 인코딩된 비디오 정보를 발생시키도록) 구성되어 있는 비디오 스트리밍 서버일 수 있고, 여기서 목적지 장치들은 유선 및/또는 무선 통신 시스템들을 통해 소스 장치(12)와 통신하고 있을 수 있다.

[0014] 외부 비디오 소스 및/또는 비디오 소스(24)는 비디오 카메라, 이전에 캡처된 비디오를 가지고 있는 비디오 보관소(video archive), 및/또는 비디오 콘텐츠 제공자로부터의 비디오 피드(video feed) 등의 비디오 캡처 장치일 수 있고 및/또는 그를 포함할 수 있다. 다른 대안으로서, 외부 비디오 소스 및/또는 비디오 소스(24)는 컴퓨터 그래픽 기반 데이터를 소스 비디오로서 발생시킬 수 있거나, 라이브 비디오, 보관된 비디오, 및 컴퓨터 발생 비디오의 조합을 발생시킬 수 있다. 어떤 실시예들에서, 비디오 소스(24)가 비디오 카메라인 경우, 소스 장치(12) 및 목적지 장치(14)는 카메라 폰 또는 비디오 폰일 수 있거나 이들을 구현할 수 있다. 그렇지만, 앞서 언급한 바와 같이, 본 명세서에 제공된 기법들은 일반적으로 비디오 코딩에 적용가능할 수 있고, 무선 및/또는 유선 응용들에 적용될 수 있다. 어쨌든, 캡처된, 사전 캡처된, 컴퓨터 발생 비디오, 비디오 피드, 또는 기타 유형의 비디오 데이터(총칭하여, "비인코딩된 비디오")가 인코딩된 비디오 정보를 형성하기 위해 비디오 인코더 유닛(18)에 의해 인코딩될 수 있다.

[0015] Tx/Rx 유닛(20)은 인코딩된 비디오 정보를 지니고 있는 하나 이상의 변조된 신호들을 형성하기 위해, 예컨대, 통신 표준에 따라, 인코딩된 비디오 정보를 변조할 수 있다. Tx/Rx 유닛(20)은 또한 변조된 신호들을 전송을 위해 그의 송신기로 전달할 수 있다. 송신기는 변조된 신호들을 Tx/Rx 요소(22)를 통해 목적지 장치(14)로 전송할 수 있다.

[0016] 목적지 장치(14)에서, Tx/Rx 유닛(28)은 채널(16)을 거쳐 Tx/Rx 요소(26)를 통해 변조된 신호들을 수신할 수 있다. Tx/Rx 유닛(28)은 인코딩된 비디오 정보를 획득하기 위해 변조된 신호들을 복조할 수 있다. Tx/Rx 유닛(28)은 인코딩된 비디오 정보를 비디오 디코더 유닛(30)으로 전달할 수 있다.

[0017] 비디오 디코더 유닛(30)은 디코딩된 비디오 데이터를 획득하기 위해 인코딩된 비디오 정보를 디코딩할 수 있다. 인코딩된 비디오 정보는 비디오 인코더 유닛(18)에 의해 정의되는 구문 정보(syntax information)를 포함할 수 있다. 이 구문 정보는 하나 이상의 요소들("구문 요소들")을 포함할 수 있고; 이를 중 일부 또는 전부는 인코딩

된 비디오 정보를 디코딩하는 데 유용할 수 있다. 구문 요소들은, 예를 들어, 인코딩된 비디오 정보의 특성들을 포함할 수 있다. 구문 요소들은 또한 인코딩된 비디오 정보를 형성하는 데 사용되는 비인코딩된 비디오의 특성들을 포함할 수 있고, 및/또는 그의 처리를 기술할 수 있다.

[0018] 비디오 디코더 유닛(30)은 나중에 저장 및/또는 외부 디스플레이(도시 생략) 상에 디스플레이하기 위해 디코딩된 비디오 데이터를 출력할 수 있다. 다른 대안으로서, 비디오 디코더 유닛(30)은 디코딩된 비디오 데이터를 디스플레이 장치(32)로 출력할 수 있다. 디스플레이 장치(32)는 디코딩된 비디오 데이터를 사용자에게 디스플레이하도록 구성되어 있는 각종의 디스플레이 장치들의 임의의 개별 장치, 다수의 장치들, 조합, 다수의 장치들의 조합일 수 있고 및/또는 그를 포함할 수 있다. 이러한 디스플레이 장치들의 예는 LCD(liquid crystal display, 액정 디스플레이), 플라즈마 디스플레이, OLED(organic light emitting diode, 유기 발광 다이오드) 디스플레이, CRT(cathode ray tube, 음극선관) 등을 포함한다.

[0019] 통신 채널(16)은 RF(radio frequency, 무선 주파수) 스펙트럼 또는 하나 이상의 물리 전송 선로, 또는 무선 및 유선 매체의 임의의 조합 등의 임의의 무선 또는 유선 통신 매체일 수 있다. 통신 채널(16)은 LAN(local area network, 근거리 통신망), WAN(wide-area network, 원거리 통신망), 또는 인터넷 등의 글로벌 네트워크(global network)와 같은 패킷 기반 네트워크의 일부를 형성할 수 있다. 통신 채널(16)은 일반적으로, 유선 또는 무선 매체의 임의의 적당한 조합을 비롯하여, 소스 장치(12)로부터 목적지 장치(14)로 비디오 데이터를 전송하는 임의의 적당한 통신 매체, 또는 상이한 통신 매체들의 집합체를 나타낸다. 통신 채널(16)은 소스 장치(12)로부터 목적지 장치(14)로의 통신을 용이하게 해주는 데 유용할 수 있는 라우터, 스위치, 기지국, 또는 임의의 다른 장비를 포함할 수 있다. 장치들(12, 14) 사이의 이러한 통신을 용이하게 해줄 수 있는 한 예시적인 통신 시스템의 상세가 도 8, 도 9a 내지 도 9e를 참조하여 이하에서 제공된다. 장치들(12, 14)을 나타낼 수 있는 장치들의 상세도 역시 이하에서 제공된다.

[0020] 비디오 인코더 유닛(18) 및 비디오 디코더 유닛(30)은, 예를 들어, MPEG-2, H.261, H.263, H.264, H.264/AVC, H.264, SVC 확장에 따라 확장된 H.264("H.264/SVC") 등과 같은 하나 이상의 표준들 및/또는 규격들에 따라 동작할 수 있다. 그렇지만, 본 명세서에 제공된 방법, 장치 및 시스템이, 아직 개발되지 않은 장래의 비디오 인코더, 디코더 및/또는 코덱을 비롯하여, 상이한 표준들에 따라(및/또는 상이한 표준들에 부합하게) 구현되는 기타 비디오 인코더, 디코더 및/또는 코덱에, 또는 독점 비디오 인코더, 디코더 및/또는 코덱에 적용가능하다는 것을 잘 알 것이다. 게다가, 그렇지만, 본 명세서에 제공된 기법들이 임의의 특정의 코딩 표준으로 제한되지 않는다.

[0021] 앞서 살펴본 H.264/AVC의 관련 부분들은 ITU(International Telecommunications Union)로부터 ITU-T 권고 H.264로서, 또는 보다 구체적으로는, "ITU-T Rec. H.264 and ISO/IEC 14496-10 (MPEG4-AVC), 'Advanced Video Coding for Generic Audiovisual Services,' v5, March, 2010"로서 이용가능하고, 이는 참조 문헌으로서 본 명세서에 포함되고, 본 명세서에서, H.264 표준 또는 H.264 규격, 또는 H.264/AVC 표준 또는 규격이라고 지칭될 수 있다. H.264/AVC 표준은 JVT(Joint Video Team)라고 하는 공동 파트너쉽(collective partnership)의 산물로서 ISO/IEC MPEG과 함께 ITU-T VCEG(Video Coding Experts Group)에 의해 작성되었다. 어떤 측면들에서, 본 명세서에 제공된 기법들은 H.264 표준에 일반적으로 부합하는 장치들에 적용될 수 있다. JVT는 H.264/AVC 표준의 확장에 관하여 계속 작업하고 있다.

[0022] H.264/AVC 표준을 진보시키기 위한 작업이 KTA(Key Technologies Area) 포럼 등의 ITU-T의 다양한 포럼들에서 착수되었다. 포럼들 중 적어도 일부는, 부분적으로, H.264/AVC 표준이 나타내는 것보다 더 높은 코딩 효율을 나타내는 코딩 기술들의 진보를 추구하고 있다. 예를 들어, ISO/IEC MPEG 및 ITU-T VCEG는 차세대 비디오 코딩 및 압축 표준, 즉 HEVC(High Efficiency Video Coding) 표준을 개발하기 시작한 JCT-VC(Joint Collaborative Team on Video Coding)를 설립하였다. 어떤 측면들에서, 본 명세서에 제공된 기법들은 H.264/AVC 및/또는 HEVC(현재 초안) 표준들에 대한 및/또는 이들에 따른 코딩 향상들을 제공할 수 있다.

[0023] 비록 도 1a 내지 도 1d에는 도시되어 있지 않지만, 어떤 측면들에서, 비디오 인코더 및 비디오 디코더 유닛들(18, 30) 각각은 (적절한 경우) 오디오 인코더 및/또는 디코더를 포함할 수 있고 및/또는 이들과 통합되어 있을 수 있다. 비디오 인코더 및 비디오 디코더 유닛들(18, 30)은 공동 데이터 스트림 내의 또는, 대안적으로, 개별적인 데이터 스트림 내의 오디오 및 비디오 둘 다의 인코딩을 처리하기 위해 적절한 MUX-DEMUX 유닛들 또는 기타 하드웨어 및/또는 소프트웨어를 포함할 수 있다. 적용가능한 경우, MUX-DEMUX 유닛들은, 예를 들어, ITU-T 권고 H.223 멀티플렉서 프로토콜, 또는 UDP(user datagram protocol) 등의 기타 프로토콜들에 부합할 수 있다.

[0024] 비디오 인코더 및 비디오 디코더 유닛들(18, 30) 각각 또는 그 중 다수가 하나 이상의 인코더들 또는 디코더들

에 포함될 수 있고, 그 중 임의의 것은 코덱의 일부로서 통합되어 있을 수 있으며, 각자의 카메라, 컴퓨터, 모바일 장치, 가입자 장치, 방송 장치, 셋톱 박스, 서버, 등과 통합되어 있거나 다른 방식으로 결합되어 있을 수 있다. 게다가, 비디오 인코더 유닛(18) 및 비디오 디코더 유닛(30)은, 각각, 하나 이상의 마이크로프로세서, DSP(digital signal processor), ASIC(application specific integrated circuit), FPGA(field programmable gate array), 이산 논리, 소프트웨어, 하드웨어, 펌웨어 또는 이들의 임의의 조합 등의 각종의 적당한 인코더 및 디코더 회로들 중 임의의 것으로서 구현될 수 있다. 다른 대안으로서, 비디오 인코더 및 비디오 디코더 유닛들(18, 30) 중 어느 하나 또는 둘 다가 실질적으로 소프트웨어로 구현될 수 있고, 그에 따라, 비디오 디코더 유닛(18) 및/또는 비디오 인코더 유닛(30)의 요소들이 동작들이 하나 이상의 프로세서(도시 생략)에 의해 실행되는 적절한 소프트웨어 명령어들에 의해 수행될 수 있다. 다시 말하지만, 이러한 실시예는, 프로세서에 부가하여, 외부 저장 장치(예를 들어, 비휘발성 메모리의 형태로 되어 있음), 출력 인터페이스 등과 같은 오프칩 구성요소들도 포함할 수 있다.

[0025] 다른 실시예들에서, 비디오 인코더 유닛(18) 및 비디오 디코더 유닛(30) 각각의 요소들 중 어떤 요소들은 하드웨어로서 구현될 수 있는 반면, 다른 요소들은 하나 이상의 프로세서들에 의해 실행되는 적절한 소프트웨어 명령어들을 사용하여 구현될 수 있다. 비디오 인코더 및/또는 비디오 디코더 유닛들(18, 30)의 요소들의 동작들이 하나 이상의 프로세서들에 의해 실행되는 소프트웨어 명령어들에 의해 수행될 수 있는 임의의 실시예에서, 이러한 소프트웨어 명령어들은 CPU에 의해 판독가능한 자기 디스크, 광 디스크, 및 임의의 다른 휴발성[예컨대, 랜덤 액세스 메모리(RAM)] 또는 비휘발성[예컨대, 판독 전용 메모리(ROM)] 대용량 저장 시스템을 비롯한 컴퓨터 판독가능 매체 상에 유지될 수 있다. 컴퓨터 판독가능 매체는 처리 시스템 상에만 존재하거나 처리 시스템에로 커리거나 원격일 수 있는 다수의 상호연결된 처리 시스템 간에 분산되어 있는 협력하는 또는 상호연결된 컴퓨터 판독가능 매체를 포함할 수 있다.

[0026] 도 1b는 도 1a의 시스템(10) 등의 비디오 인코딩 및/또는 디코딩 시스템에서 사용하기 위한 한 예시적인 비디오 인코더 유닛(18)을 나타낸 블록도이다. 비디오 인코더 유닛(18)은 비디오 인코더(33), 출력 버퍼(34) 및 시스템 제어기(36)를 포함할 수 있다. 비디오 인코더 유닛(18)과 같이, 전체로서, 비디오 인코더(33)(또는 그의 하나 이상의 요소들)는, 예를 들어, H.261, H.263, H.264, H.264/AVC, H.264/SVC, HEVC 등과 같은 하나 이상의 표준들 및/또는 규격들에 따라 구현될 수 있다. 그렇지만, 본 명세서에 제공된 방법, 장치 및 시스템이 상이한 표준들에 따라 구현되는 다른 비디오 인코더들에 또는 아직 개발되지 않은 장래의 코덱들을 비롯한 독점 코덱들에 적용가능하다고 생각된다.

[0027] 비디오 인코더(33)는 비디오 소스(24) 및/또는 외부 비디오 소스 등의 비디오 소스로부터 제공되는 비디오 신호를 수신할 수 있다. 이 비디오 신호는 비인코딩된 비디오를 포함할 수 있다. 비디오 인코더(33)는 비인코딩된 비디오를 인코딩하여, 인코딩된(즉, 압축된) 비디오 비트스트림(bit stream, BS)을 그 출력에서 제공할 수 있다.

[0028] 인코딩된 비디오 비트스트림(BS)이 출력 버퍼(34)에 제공될 수 있다. 출력 버퍼(34)는 인코딩된 비디오 비트스트림(BS)을 버퍼링하고, 통신 채널(16)을 통해 전송하기 위해 이러한 인코딩된 비디오 비트스트림(BS)을 버퍼링된 비트스트림(buffered bit stream, BBS)로서 제공할 수 있다.

[0029] 출력 버퍼(34)로부터 출력되는 버퍼링된 비트스트림(BBS)은 나중에 보거나 전송하기 위해 저장 장치(도시 생략)에 제공될 수 있다. 다른 대안으로서, 비디오 인코더 유닛(18)은 버퍼링된 비트스트림(BBS)이 명시된 일정한 및/또는 가변 비트 레이트로(예컨대, 아주 낮은 또는 최소의 지연으로) 통신 채널(16)을 통해 전송될 수 있는 화상 통신을 위해 구성될 수 있다.

[0030] 인코딩된 비디오 비트스트림(BS) 및, 차례로, 버퍼링된 비트스트림(BBS)은 인코딩된 비디오 정보의 비트들을 전달할 수 있다. 버퍼링된 비트스트림(BBS)의 비트들은 인코딩된 비디오 프레임들의 스트림으로서 배열될 수 있다. 인코딩된 비디오 프레임들은, 기술 분야의 당업자라면 잘 알 것인 바와 같이, 인트라 코딩된 프레임(예컨대, I 프레임), 인터 코딩된 프레임(예컨대, B 프레임 또는 P 프레임) 등일 수 있다. 인코딩된 비디오 프레임들의 스트림은, 예를 들어, 일련의 GOP들로서 배열될 수 있고, 각각의 GOP의 인코딩된 비디오 프레임들은 명시된 순서로 배열되어 있다. 일반적으로, 각각의 GOP는 인트라 코딩된 프레임(예컨대, I 프레임)으로 시작하고, 이어서 하나 이상의 인터 코딩된 프레임들(예컨대, P 프레임 및/또는 B 프레임)이 따라온다. 각각의 GOP는 통상적으로 단지 하나의 인트라 코딩된 프레임을 포함하지만, GOP들 중 임의의 것은 다수를 포함할 수 있다. 유의할 점은, 장래의 B 프레임이 실시간 저지연 응용에 사용되지 않을 수 있다는 것이다[왜냐하면, 예를 들어, 양방향 예측이 통상적으로, 예를 들어, 단방향 예측(P 프레임)과 비교하여 부가의 코딩 지연을 야기하기 때문임]. 기술

분야의 당업자라면 잘 알 것인 바와 같이, 부가의 및/또는 기타 프레임 유형들이 지원되고 인코딩된 비디오 프레임들의 특정의 순서가 수정될 수 있다.

[0031] 각각의 GOP는 구문 데이터("GOP 구문 데이터")를 포함할 수 있다. GOP 구문 데이터는 GOP의 헤더에, GOP의 하나 이상의 프레임들의 헤더에, 또는 다른 곳에 배치될 수 있다. GOP 구문 데이터는 각자의 GOP의 인코딩된 비디오 프레임들의 순서, 분량 및/또는 유형을 나타내고 및/또는 각자의 GOP의 인코딩된 비디오 프레임들을 다른 방식으로 기술할 수 있다. 각각의 인코딩된 비디오 프레임은 구문 데이터("인코딩된 프레임 구문 데이터")를 포함할 수 있다. 인코딩된 프레임 구문 데이터는 각자의 인코딩된 비디오 프레임에 대한 인코딩 모드를 나타내거나 다른 방식으로 기술할 수 있다.

[0032] 시스템 제어기(36)는 채널(16)과 연관되어 있는 다양한 파라미터들 및/또는 제약조건들, 비디오 인코더 유닛(18)의 계산 능력, 사용자의 요구 등을 모니터링할 수 있고, 채널(16)의 명시된 제약조건 및/또는 상태에 적당한 부수적인 QoE(quality of experience, 체감 품질)를 제공하기 위해 목표 파라미터들을 설정할 수 있다. 목표 파라미터들 중 하나 이상이 명시된 제약조건 및/또는 채널 상태에 따라 때때로 조절될 수 있다. 한 예로서, QoE가, 예를 들어, 인코딩된 비디오 시퀀스의 상태 지각 품질(relative perceptive quality)이라고 흔히 말해지는 척도를 비롯하여, 비디오 품질을 평가하는 하나 이상의 척도를 사용하여 정량적으로 평가될 수 있다. 예를 들어, 피크 신호대 잡음비(peak-signal-to-noise ratio, "PSNR") 척도를 사용하여 측정된, 인코딩된 비디오 시퀀스의 상태 지각 품질은 인코딩된 비트스트림(BS)의 비트 레이트(bit rate, BR)에 의해 제어된다. 인코딩된 비트스트림(BS)의 비트 레이트(BR)와 연관되어 있는 제약조건들 내에서 비디오의 상태 지각 품질을 최대화하기 위해 목표 파라미터들[예를 들어, 양자화 파라미터(quantization parameter, QP)를 포함함] 중 하나 이상이 조절될 수 있다.

[0033] 도 1c는 도 1a 및 도 1b의 비디오 인코더 유닛(18) 등의 비디오 인코더 유닛에서 사용하기 위한 비디오 인코더(33)의 한 예를 나타낸 블록도이다. 비디오 인코더(33)는 입력(38), 모드 결정 및 인코더 제어기 유닛(40), 공간 예측 유닛(42), 움직임/시간 예측 유닛(44), 제1 합산기(46), 변환 유닛(48), 양자화 유닛(50), 엔트로피 코딩 유닛(52), 역양자화 유닛(54), 역변환 유닛(56), 제2 합산기(58), 필터들(60), 참조 픽처 저장소(62), 및 출력(64)을 포함할 수 있다. 비디오 인코더(33)는 부가의 및/또는 상이한 요소들을 포함할 수 있다. 이러한 요소들은 간략함 및 명확함을 위해 예시되어 있지 않다.

[0034] 게다가, 도 1c에 도시되어 있고 본 명세서에 제공된 비디오 인코더(33)의 상세는 단지 예시를 위한 것이며, 실세계 구현들은 다를 수 있다. 실세계 구현은, 예를 들어, 보다 많은, 보다 적은 및/또는 상이한 요소들을 포함할 수 있고, 및/또는 도 1c에 도시되어 있는 배열과 상이하게 배열되어 있을 수 있다. 예를 들어, 개별적으로 도시되어 있지만, 변환 유닛(48) 및 양자화 유닛(50) 둘 다의 기능들 중 일부 또는 전부가, 예를 들어, H.264 표준의 코어 변환(core transform)을 사용하는 구현들과 같은 실세계 구현들 중 일부에서 고도로 통합되어 있을 수 있다. 이와 유사하게, 역양자화 유닛(54) 및 역변환 유닛(56)이 실세계 구현들(예컨대, H.264 표준 부합 구현들) 중 일부에서 고도로 통합되어 있을 수 있지만, 마찬가지로 개념적 목적을 위해 개별적으로 예시되어 있다.

[0035] 앞서 살펴본 바와 같이, 비디오 인코더(33)는 그의 입력(38)에서 비디오 신호를 수신할 수 있다. 비디오 인코더(33)는 수신된 비인코딩된 비디오로부터 인코딩된 비디오 정보를 발생시키고, 인코딩된 비디오 정보(예컨대, 인트라 프레임 또는 인터 프레임 중 임의의 것)를 그의 출력(64)으로부터 인코딩된 비디오 비트스트림(BS)의 형태로 출력할 수 있다. 비디오 인코더(33)는, 예를 들어, 하이브리드 비디오 인코더로서 동작할 수 있고, 비인코딩된 비디오를 인코딩하기 위해 블록 기반 코딩 프로세스를 이용할 수 있다. 이러한 인코딩 프로세스를 수행할 때, 비디오 인코더(33)는 통상적으로 비인코딩된 비디오의 개별 프레임, 픽처 또는 영상(총칭하여, "비인코딩된 픽처")에 대해 동작한다.

[0036] 블록 기반 인코딩 프로세스를 용이하게 해주기 위해, 비디오 인코더(33)는 그 입력(38)에 수신된 각각의 비인코딩된 픽처를 다수의 비인코딩된 비디오 블록들로 슬라이싱, 파티셔닝, 분할, 또는 다른 방식으로 세그먼트화(총칭하여, "세그먼트화")할 수 있다. 어떤 경우에, 비디오 인코더(33)는 먼저 비인코딩된 픽처를 다수의 비인코딩된 비디오 세그먼트들(예컨대, 슬라이스들)로 세그먼트화할 수 있고, 이어서 비인코딩된 비디오 세그먼트들 각각을 비인코딩된 비디오 블록들로 세그먼트화할 수 있다. 비디오 인코더(33)는 비인코딩된 비디오 블록들을 공간 예측 유닛(42), 움직임/시간 예측 유닛(44) 및/또는 제1 합산기(46)에 전달, 공급, 송신 또는 다른 방식으로 제공할 수 있다. 이하에서 더 상세히 기술하는 바와 같이, 비인코딩된 비디오 블록들은 블록별로 제공될 수 있다.

- [0037] 공간 예측 유닛(42)은 비인코딩된 비디오 블록들을 수신하고, 이러한 비디오 블록들을 인트라 모드에서 인코딩 할 수 있다. 인트라 모드는 몇가지 공간 기반 압축 모드들 중 임의의 것을 말하고, 인트라 모드에서의 인코딩은 비인코딩된 픽처의 공간 기반 압축을 제공하려고 노력한다. 공간 기반 압축(있는 경우)은 비인코딩된 픽처 내의 비디오 정보의 공간 중복성을 감소시키거나 제거하는 것으로부터 얻어질 수 있다. 예측 블록들을 형성할 시에, 공간 예측 유닛(42)은 이미 인코딩 및/또는 재구성되어 있는 비인코딩된 픽처의 하나 이상의 비디오 블록들(각각, "인코딩된 비디오 블록들" 및/또는 "재구성된 비디오 블록들")에 대해 각각의 비인코딩된 비디오 블록의 공간 예측(또는 "인트라 예측")을 수행할 수 있다. 인코딩된 및/또는 재구성된 비디오 블록들은 비인코딩된 비디오 블록의 이웃이거나, 그에 인접해 있거나, 그와 아주 근접해 있을 수 있다.

- [0038] 움직임/시간 예측 유닛(44)은 입력(38)으로부터 비인코딩된 비디오 블록들을 수신하고, 이들을 인터 모드에서 인코딩할 수 있다. 인터 모드는, 예를 들어, P 모드(단방향 예측) 또는 B 모드(양방향 예측)를 비롯하여 몇가지 시간 기반 압축 모드들 중 임의의 것을 말한다. 인터 모드에서의 인코딩은 비인코딩된 픽처의 시간 기반 압축을 제공하려고 노력한다. 시간 기반 압축(있는 경우)은 비인코딩된 픽처와 하나 이상의 참조(예컨대, 인접) 픽처들 간의 비디오 정보의 시간 중복성을 감소시키거나 제거하는 것으로부터 얻어질 수 있다. 움직임/시간 예측 유닛(44)은 참조 픽처들의 하나 이상의 비디오 블록들에 대해 각각의 비인코딩된 비디오 블록의 시간 예측(또는 "인터 예측")을 수행할 수 있다. 수행된 시간 예측은 단방향 예측(예컨대, P 모드의 경우)이거나, 대안적으로, 양방향 예측(예컨대, B 모드의 경우)일 수 있다.

- [0039] 단방향 예측 하에서, 참조 비디오 블록들은 이전에 인코딩된 및/또는 재구성된 픽처들로부터 온 것일 수 있고, 어떤 경우에, 단지 하나의 이전에 인코딩된 및/또는 재구성된 픽처로부터 온 것일 수 있다. 인코딩된 및/또는 재구성된 픽처들은 비인코딩된 픽처의 이웃이거나, 그에 인접해 있거나, 그와 아주 근접해 있을 수 있다.

- [0040] 양방향 예측 하에서, 참조 비디오 블록들은 비디오 스트림의 하나 이상의 이전에 인코딩된 및/또는 재구성된 픽처들과 하나 이상의 다른 비인코딩된 픽처들로부터 온 것일 수 있다. 인코딩된 및/또는 재구성된 픽처들 및 다른 비인코딩된 픽처들은 비인코딩된 픽처의 이웃이거나, 그에 인접해 있거나, 그와 아주 근접해 있을 수 있다.

- [0041] (H.264/AVC 또는 HEVC 등의 최근의 비디오 코딩 표준들에 대해서와 같이) 다수의 참조 픽처들이 지원되는 경우, 각각의 비디오 블록에 대해, 그의 참조 픽처 인덱스(reference picture index)가 차후의 출력 및/또는 전송을 위해 엔트로피 코딩 유닛(52)으로 송신될 수 있다. 참조 인덱스는 시간 예측이 참조 픽처 저장소(62) 내의 어느 참조 픽처(들)로부터 이루어지는지를 식별하는 데 사용될 수 있다.

- [0042] 통상적으로 고도로 통합되어 있지만, 움직임 추정 및 움직임 보상을 위한 움직임/시간 예측 유닛(44)의 기능들이 개별적인 엔터티들 또는 유닛들(도시 생략)에 의해 수행될 수 있다. 움직임 추정은 참조 픽처 비디오 블록들에 대해 각각의 비인코딩된 비디오 블록의 움직임을 추정하기 위해 수행될 수 있고, 비인코딩된 비디오 블록에 대한 움직임 벡터를 발생시키는 것을 수반할 수 있다. 움직임 벡터는 코딩되고 있는 비인코딩된 비디오 블록에 대한 예측 블록의 변위를 나타낼 수 있다. 이 예측 블록은, 픽셀 차(pixel difference)의 면에서, 코딩되고 있는 비인코딩된 비디오 블록과 가장 가깝게 일치하는 것으로 밝혀진 참조 픽처 비디오 블록이다. 이 일치는 SAD(sum of absolute difference, 절대차 합), SSD(sum of square difference, 제곱차 합), 또는 기타 차 척도(difference metric)에 의해 판정될 수 있다. 움직임 보상은 움직임 추정에 의해 결정된 움직임 벡터에 기초하여 예측 블록을 페치(fetch)하거나 발생시키는 것을 수반할 수 있다.

- [0043] 움직임/시간 예측 유닛(44)은 비인코딩된 비디오 블록을 참조 픽처 저장소(64)에 저장되어 있는 참조 픽처들로부터의 참조 비디오 블록들과 비교함으로써 비인코딩된 비디오 블록의 움직임 벡터를 계산할 수 있다. 움직임/시간 예측 유닛(44)은 참조 픽처 저장소(62)에 포함되어 있는 참조 픽처의 분수 픽셀 위치들(fractional pixel positions)에 대한 값을 계산할 수 있다. 어떤 경우에, 비디오 인코더(33)의 합산기(58) 또는 다른 유닛은 재구성된 비디오 블록들에 대한 분수 픽셀 위치 값을 계산할 수 있고, 이어서 재구성된 비디오 블록들을, 분수 픽셀 위치들에 대한 계산된 값을 함께, 참조 픽처 저장소(62)에 저장할 수 있다. 움직임/시간 예측 유닛(44)은 또한 (예컨대, I 프레임 또는 P 프레임의) 참조 픽처의 하위 정수 픽셀들(sub-integer pixels)을 보간할 수 있다.

- [0044] 움직임/시간 예측 유닛(44)은 선택된 움직임 예측자(motion predictor)에 대해 움직임 벡터를 인코딩하도록 구성되어 있을 수 있다. 움직임/시간 예측 유닛(44)에 의해 선택된 움직임 예측자는, 예를 들어, 이미 인코딩되어 있는 이웃 블록들의 움직임 벡터들의 평균과 동등한 벡터일 수 있다. 비인코딩된 비디오 블록에 대한 움직임 벡터를 인코딩하기 위해, 움직임/시간 예측 유닛(44)은, 움직임 벡터 차 값을 형성하기 위해, 움직임 벡터와 움직

임 예측자 간의 차를 계산할 수 있다.

[0045] H.264는 잠재적 참조 프레임 세트를 "리스트(list)"라고 한다. 참조 픽처 저장소(62)에 저장되어 있는 참조 픽처 세트는 참조 프레임들의 이러한 리스트에 대응할 수 있다. 움직임/시간 예측 유닛(44)은 참조 픽처 저장소(62)로부터의 참조 픽처들의 참조 비디오 블록들을 (예컨대, P 프레임 또는 B 프레임의) 비인코딩된 비디오 블록과 비교할 수 있다. 참조 픽처 저장소(62) 내의 참조 픽처들이 하위 정수 픽셀들에 대한 값들을 포함할 때, 움직임/시간 예측 유닛(44)에 의해 계산된 움직임 벡터는 참조 픽처의 하위 정수 픽셀 위치(sub-integer pixel location)를 참조할 수 있다. 움직임/시간 예측 유닛(44)은 계산된 움직임 벡터를 엔트로피 코딩 유닛(52)으로 그리고 움직임/시간 예측 유닛(44)의 움직임 보상 기능들로 송신할 수 있다. 움직임/시간 예측 유닛(44)(또는 그의 움직임 보상 기능들)은 코딩되고 있는 비인코딩된 비디오 블록에 대한 예측 블록의 오차 값을 계산할 수 있다. 움직임/시간 예측 유닛(44)은 예측 블록에 기초하여 예측 데이터를 계산할 수 있다.

[0046] 모드 결정 및 인코더 제어기 유닛(40)은 코딩 모드들(인트라 모드 또는 인터 모드) 중 하나를 선택할 수 있다. 모드 결정 및 인코더 제어기 유닛(40)은, 예를 들어, 레이트 왜곡 최적화법에 기초하여 및/또는 각각의 모드에서 생성된 오차 결과에 기초하여 그렇게 할 수 있다.

[0047] 비디오 인코더(33)는 움직임/시간 예측 유닛(42)으로부터 제공된 예측 데이터를 코딩되고 있는 비인코딩된 비디오 블록으로부터 차감함으로써 잔차들의 블록("잔차 비디오 블록")을 형성할 수 있다. 합산기(46)는 이 차감 동작을 수행하는 한 요소 또는 다수의 요소들을 나타낸다.

[0048] 변환 유닛(48)은 잔차 비디오 블록을 픽셀 값 영역(pixel value domain)으로부터 주파수 영역 등의 변환 영역(transform domain)으로 변환하기 위해 이러한 잔차 비디오 블록에 변환을 적용할 수 있다. 이 변환은, 예를 들어, 본 명세서에 제공된 변환, DCT(discrete cosine transform), 또는 개념적으로 유사한 변환 중 임의의 것일 수 있다. 이 변환의 다른 예들은 H.264에 정의된 것, 웨이블릿 변환, 정수 변환, 서브대역 변환 등을 포함한다. 어쨌든, 변환 유닛(48)에서 잔차 비디오 블록에 변환을 적용하는 것은 잔차 비디오 블록의 변환 계수들("잔차 변환 계수들")의 대응하는 블록을 생성한다. 이를 잔차 변환 계수는 잔차 비디오 블록의 주파수 성분들의 크기를 나타낼 수 있다. 변환 유닛(48)은 잔차 변환 계수들 및 움직임 벡터들을 양자화 유닛(50)으로 전달할 수 있다.

[0049] 양자화 유닛(50)은 인코딩된 비트 레이트를 추가로 감소시키기 위해 잔차 변환 계수들을 양자화할 수 있다. 양자화 프로세스는, 예를 들어, 잔차 변환 계수들 중 일부 또는 전부와 연관되어 있는 비트 깊이(bit depth)를 감소시킬 수 있다. 어떤 경우에, 양자화 유닛(50)은, 양자화된 변환 계수들의 블록을 형성하기 위해, 잔차 변환 계수들의 값들을 QP에 대응하는 양자화 레벨로 나눌 수 있다. 양자화의 정도가 QP 값을 조절함으로써 수정될 수 있다. 일반적으로, 양자화 유닛(50)은 원하는 수의 양자화 스텝들을 사용하여 잔차 변환 계수들을 나타내기 위해 양자화를 적용하고, 사용되는 스텝들의 수는 잔차 비디오 블록을 나타내는 데 사용되는 인코딩된 비디오 비트들의 수를 결정할 수 있다. 양자화 유닛(50)은 레이트 제어기(rate controller)(도시 생략)로부터 QP 값을 획득할 수 있다. 양자화 후에, 양자화 유닛(50)은 양자화된 변환 계수들 및 움직임 벡터들을 엔트로피 코딩 유닛(52)에 그리고 역양자화 유닛(54)에 제공할 수 있다.

[0050] 엔트로피 코딩 유닛(52)은 엔트로피 코딩된 계수들(즉, 비트스트림)을 형성하기 위해 엔트로피 코딩을 양자화된 변환 계수들에 적용할 수 있다. 엔트로피 코딩 유닛(52)은 엔트로피 코딩된 계수들을 형성하기 위해 적응적 가변 길이 코딩(adaptive variable length coding, CAVLC), 컨텍스트 적응적 이진 산술 코딩(context adaptive binary arithmetic coding, CABAC), 또는 다른 엔트로피 코딩 기법을 사용할 수 있다. CABAC는, 기술 분야의 당업자라면 잘 알 것인 바와 같이, 상황 정보(contextual information)("컨텍스트")의 입력을 필요로 한다. 이 컨텍스트는, 예를 들어, 이웃하는 비디오 블록들에 기초할 수 있다.

[0051] 엔트로피 코딩 유닛(52)은 엔트로피 코딩된 계수들을 움직임 벡터들과 함께 원시 인코딩된 비디오 비트스트림의 형태로 내부 비트스트림 포맷터(internal bit-stream formatter)(도시 생략)에 제공할 수 있다. 이 비트스트림 포맷터는, 비디오 디코더 유닛(30)이 원시 인코딩된 비디오 비트스트림으로부터 인코딩된 비디오 블록을 디코딩 할 수 있게 하기 위해, 헤더 및/또는 기타 정보를 비롯한 부가 정보를 원시 인코딩된 비디오 비트스트림에 첨부하여 출력 버퍼(34)(도 1b)에 제공되는 인코딩된 비디오 비트스트림(BS)을 형성할 수 있다. 엔트로피 코딩 후에, 엔트로피 코딩 유닛(52)으로부터 출력 버퍼(34)에 제공되는 인코딩된 비디오 비트스트림(BS)은 채널(16)을 통해 목적지 장치(14)로 전송되거나 나중에 전송 또는 검색하기 위해 보관될 수 있다.

[0052] 어떤 실시예들에서, 엔트로피 코딩 유닛(52) 또는 비디오 인코더(33)의 다른 유닛이, 엔트로피 코딩에

부가하여, 다른 코딩 기능들을 수행하도록 구성되어 있을 수 있다. 예를 들어, 엔트로피 코딩 유닛(52)은 비디오 블록들에 대한 CBP 값들을 결정하도록 구성되어 있을 수 있다. 또한, 어떤 실시예들에서, 엔트로피 코딩 유닛(52)은 비디오 블록에서 양자화된 변환 계수들의 런 렌스 코딩(run length coding)을 수행할 수 있다. 한 예로서, 엔트로피 코딩 유닛(52)은 비디오 블록에서 양자화된 변환 계수들을 배열하고 추가의 압축을 위해 영들의 런(run)을 인코딩하기 위해 지그재그 스캔 또는 기타 스캔 패턴을 적용할 수 있다. 엔트로피 코딩 유닛(52)은 또한 인코딩된 비디오 비트스트림(BS)에서의 전송을 위해 적절한 구문 요소들로 헤더 정보를 구성할 수 있다.

[0053] (예컨대, 참조 픽처 리스트 내의 참조 픽처들 중 하나 내의) 예컨대, 참조 비디오 블록들 중 하나로서 나중에 사용하기 위해, 픽셀 영역에서 잔차 비디오 블록을 재구성하기 위해, 역양자화 유닛(54) 및 역변환 유닛(56)은, 각각, 역양자화 및 역변환을 적용할 수 있다.

[0054] 모드 결정 및 인코더 제어기 유닛(40)은 재구성된 잔차 비디오 블록을 참조 픽처 저장소(62)에 저장되어 있는 참조 픽처들 중 하나의 참조 픽처의 예측 블록에 가산함으로써 참조 비디오 블록을 계산할 수 있다. 모드 결정 및 인코더 제어기 유닛(40)은 또한 움직임 추정에서 사용하기 위한 (예컨대, 반픽셀 위치들에 대한) 하위 정수 픽셀 값들을 계산하기 위해 하나 이상의 보간 필터들을 재구성된 잔차 비디오 블록에 적용할 수 있다.

[0055] 합산기(58)는, 참조 픽처 저장소(62)에 저장하기 위한 재구성된 비디오 블록을 생성하기 위해, 재구성된 잔차 비디오 블록을 움직임 보상된 예측 비디오 블록에 가산할 수 있다. 후속하는 비인코딩된 비디오 내의 비인코딩된 비디오 블록을 인터 코딩하기 위해, 재구성된(픽셀 값 영역) 비디오 블록이 움직임/시간 예측 유닛(44)(또는 그의 움직임 추정 기능들 및/또는 그의 움직임 보상 기능들)에 의해 참조 블록들 중 하나로서 사용될 수 있다.

[0056] 필터들(60)은 디블록킹 필터(deblocking filter)를 포함할 수 있다. 디블록킹 필터는 재구성된 매크로블록들에 존재할 수 있는 시각적 아티팩트들을 제거하는 동작을 할 수 있다. 이들 아티팩트는, 예를 들어, 상이한 인코딩 모드들(I 유형, P 유형 또는 B 유형 등)의 사용으로 인해 인코딩 프로세스에서 유입될 수 있다. 아티팩트들은, 예를 들어, 수신된 비디오 블록들의 경계 및/또는 가장자리에 존재할 수 있고, 디블록킹 필터는 시각적 품질을 향상시키기 위해 비디오 블록들의 경계 및/또는 가장자리를 매끄럽게 하는 동작을 할 수 있다. 원하는 경우, 디블록킹 필터는 통상적으로 합산기(58)의 출력을 필터링할 것이다.

[0057] 도 1d는 도 1a 및 도 1b의 비디오 디코더 유닛(30) 등의 비디오 디코더 유닛에서 사용하기 위한 비디오 디코더(35)의 한 예를 나타낸 블록도이다. 비디오 디코더(35)는 입력(66), 엔트로피 디코딩 유닛(68), 움직임 보상 예측 유닛(70), 공간 예측 유닛(72), 역양자화 유닛(74), 역변환 유닛(76), 참조 픽처 저장소(80), 필터들(82), 합산기(78) 및 출력(84)을 포함할 수 있다. 비디오 디코더(35)는 일반적으로, 비디오 인코더(33)(도 1c)와 관련하여 제공된 인코딩 프로세스와 상반되는 디코딩 프로세스를 수행할 수 있다. 이 디코딩 프로세스는 다음과 같이 수행될 수 있다.

[0058] 움직임 보상 예측 유닛(70)은 엔트로피 디코딩 유닛(68)으로부터 수신된 움직임 벡터들에 기초하여 예측 데이터를 발생시킬 수 있다. 움직임 벡터들은 인코딩된 움직임 벡터에 대응하는 비디오 블록에 대한 움직임 예측자에 대해 인코딩될 수 있다. 움직임 보상 예측 유닛(70)은 움직임 예측자를, 예를 들어, 디코딩될 비디오 블록에 이웃하는 블록들의 움직임 벡터들의 메디안(median)으로서 결정할 수 있다. 움직임 예측자를 결정한 후에, 움직임 보상 예측 유닛(70)은, 인코딩된 비디오 비트스트림(BS)으로부터 움직임 벡터 차 값을 추출하고 움직임 벡터 차 값을 움직임 예측자에 가산함으로써, 인코딩된 움직임 벡터를 디코딩할 수 있다. 움직임 보상 예측 유닛(70)은 움직임 예측자를 인코딩된 움직임 벡터와 동일한 분해능으로 양자화할 수 있다. 다른 대안으로서, 움직임 보상 예측 유닛(70)은 모든 인코딩된 움직임 예측자들에 대해 동일한 정밀도를 사용할 수 있다. 다른 대안으로서, 움직임 보상 예측 유닛(70)은 상기 방법들 중 어느 하나를 사용하도록 그리고 인코딩된 비디오 비트스트림(BS)으로부터 획득된 시퀀스 파라미터 세트, 슬라이스 파라미터 세트, 또는 픽처 파라미터 세트에 포함되어 있는 데이터를 분석함으로써 어느 방법을 사용할지를 결정하도록 구성되어 있을 수 있다.

[0059] 움직임 벡터를 디코딩한 후에, 움직임 보상 예측 유닛(70)은 참조 픽처 저장소(80)의 참조 픽처로부터 움직임 벡터에 의해 식별된 예측 비디오 블록을 추출할 수 있다. 움직임 벡터가 반픽셀 등의 분수 픽셀 위치를 가리키는 경우, 움직임 보상 예측 유닛(70)은 분수 픽셀 위치에 대한 값을 보간할 수 있다. 움직임 보상 예측 유닛(70)은 이를 값을 보간하기 위해 적응적 보간 필터 또는 고정 보간 필터를 사용할 수 있다. 게다가, 움직임 보상 예측 유닛(70)은, 수신된 인코딩된 비디오 비트스트림(BS)으로부터, 필터들(82) 중 어느 것을 사용할지의 표식, 및 어떤 실시예들에서, 필터들(82)에 대한 계수들을 획득할 수 있다.

[0060] 공간 예측 유닛(72)은, 공간적으로 인접한 블록들로부터 예측 비디오 블록을 형성하기 위해, 인코딩된 비디오

비트스트림(BS)에서 수신된 인트라 예측 모드를 사용할 수 있다. 역양자화 유닛(74)은 인코딩된 비디오 비트스트림(BS)에서 제공되고 엔트로피 디코딩 유닛(68)에서 디코딩되는 양자화된 블록 계수들을 역양자화(nverse quantize 또는 de-quantize)할 수 있다. 역양자화 프로세스는, 예컨대, H.264에 의해 정의되는 바와 같은 종래의 프로세스를 포함할 수 있다. 역양자화 프로세스는 또한 양자화의 정도 그리고, 마찬가지로, 적용되어야만 하는 역양자화의 정도를 결정하기 위해 각각의 비디오 블록에 대해 비디오 인코더(33)에 의해 계산된 양자화 파라미터(QP)의 사용을 포함할 수 있다.

[0061] 역변환 유닛(76)은, 픽셀 영역에서의 잔차 비디오 블록들을 생성하기 위해, 역변환(예컨대, 본 명세서에 제공된 변환 중 임의의 변환의 역), 역 DCT, 역 정수 변환, 또는 개념적으로 유사한 역변환 프로세스를 변환 계수들에 적용할 수 있다. 움직임 보상 예측 유닛(70)은, 어쩌면 보간 필터들에 기초한 보간을 수행하여, 움직임 보상된 블록들을 생성할 수 있다. 서브픽셀 정밀도를 갖는 움직임 추정을 위해 사용될 보간 필터들에 대한 식별자들이 비디오 블록의 구문 요소들에 포함될 수 있다. 움직임 보상 예측 유닛(70)은, 참조 블록의 하위 정수 픽셀들에 대한 보간된 값들을 계산하기 위해, 비디오 블록의 인코딩 동안 비디오 인코더(33)에 의해 사용된 것과 같은 보간 필터들을 사용할 수 있다. 움직임 보상 예측 유닛(70)은 수신된 구문 정보에 따라 비디오 인코더(33)에 의해 사용된 보간 필터들을 결정하고, 예측 블록들을 생성하기 위해 보간 필터들을 사용할 수 있다.

[0062] 움직임 보상 예측 유닛(70)은 인코딩된 비디오 시퀀스의 픽처(들)를 인코딩하기 위해 사용된 비디오 블록들의 크기들을 결정하기 위한 구문 정보, 인코딩된 비디오 시퀀스의 프레임의 각각의 비디오 블록이 어떻게 파티셔닝 되는지를 기술하는 파티션 정보, 각각의 파티션이 어떻게 인코딩되는지를 나타내는 모드들, 각각의 인터 인코딩된 비디오 블록에 대한 하나 이상의 참조 픽처들, 및 인코딩된 비디오 시퀀스를 디코딩하기 위한 기타 정보 중 일부를 사용할 수 있다.

[0063] 합산기(78)는, 디코딩된 비디오 블록들을 형성하기 위해, 잔차 블록들을 움직임 보상 예측 유닛(70) 또는 공간 예측 유닛(72)에 의해 발생된 대응하는 예측 블록들과 합산할 수 있다. 원하는 경우, 디블록킹 필터[예컨대, 필터들(82)]가 또한 블록화 현상 아티팩트들(blockiness artifacts)을 제거하기 위해 디코딩된 비디오 블록들을 필터링하는 데 적용될 수 있다. 디코딩된 비디오 블록들은 이어서 참조 픽처 저장소(80)에 저장되고, 참조 픽처 저장소(80)는 후속하는 움직임 보상을 위한 참조 비디오 블록들을 제공하고 또한 디스플레이 장치[도 1의 디스플레이 장치(34) 등] 상에 제시하기 위한 디코딩된 비디오를 생성한다.

[0064] 각각의 비디오 블록이 인코딩 및/또는 디코딩 프로세스를 거칠 때, 이러한 비디오 블록의 비디오 정보가 상이하게 표현될 수 있다. 예를 들어, 비디오 블록은 (i) 픽셀 영역에서의 픽셀 데이터; (ii) 비인코딩된 비디오 블록들과 예측 블록 사이의 픽셀 차들을 나타내는 잔차 데이터("잔차들"); (iii) (예컨대, 변환의 적용 이후의) 변환 영역에서의 변환 계수들; 및 (iv) 양자화된 변환 영역에서의 양자화된 변환 계수들을 포함할 수 있다.

[0065] 각각의 비디오 블록은 주어진 차원들 또는 총칭하여 "크기"를 가질 수 있다. 비디오 블록 크기는 코딩 표준에 의존할 수 있다. 한 예로서, H.264 표준은 루마 성분(luma component)에 대한 16x16, 8x8, 또는 4x4 그리고 크로마 성분(chroma component)에 대한 8x8 등의 다양한 비디오 블록 크기들에서 인트라 예측을 지원하고, 루마 성분에 대한 16x16, 16x8, 8x16, 8x8, 8x4, 4x8 및 4x4 그리고 크로마 성분에 대한 대응하는 스케일링된 크기들 등의 다양한 블록 크기들에서 인터 예측을 지원한다. H.264 표준에서, 16 픽셀 x 16 픽셀의 차원을 가지는 비디오 블록은 일반적으로 매크로블록(macroblock, MB)라고 하고, 16 픽셀 x 16 픽셀 미만을 갖는 비디오 블록은 일반적으로 MB의 파티션["MB 파티션(MB partition)"]이라고 한다. HEVC에서, "코딩 단위(coding unit)" 또는 CU라고 하는 비디오 블록은 고해상도(예컨대, 1080p 이상) 비디오 신호를 보다 효율적으로 압축하기 위해 사용될 수 있다. HEVC에서, CU 크기는 파라미터 시퀀스 세트에 설정되어 있고, 64x64 픽셀 정도로 크게 또는 4x4 픽셀 정도로 작게 설정될 수 있다. CU는 개별적인 예측 방법들이 적용되는 예측 단위들(prediction unit, PU)로 추가로 파티셔닝될 수 있다. 각각의 비디오 블록(MB, CU, PU 등)은 공간 예측 유닛(42) 및/또는 움직임/시간 예측 유닛(44)을 사용하여 처리될 수 있다.

[0066] 본 명세서에서 사용되는 바와 같이, "NxN"과 "N by N"은 수직 및 수평 차원 둘 다에서의 성분들(예컨대, 픽셀, 잔차, 변환 계수, 양자화된 변환 계수 등)의 면에서 블록의 크기를 가리키기 위해 사용될 수 있다(예컨대, 16x16 요소들). 일반적으로, 16x16 비디오 블록은 수직 방향에서 16개의 요소들(y=16) 및 수평 방향에서 16개의 요소들(x=16)을 가질 것이다. 마찬가지로, NxN 블록은 일반적으로 수직 방향에서 N개의 요소들 및 수평 방향에서 N개의 요소들을 가지며, 여기서 N은 음이 아닌 정수 값을 나타낸다. 비디오 블록 내의 요소들은 행과 열로 배열될 수 있다. 더욱이, 비디오 블록들은 수평 방향에서 수직 방향에서와 동일하거나 상이한 수의 픽셀들을 가질 수 있다. 예를 들어, 비디오 블록들은 NxM 픽셀들을 포함할 수 있고, 여기서 M이 꼭 N과 같을 필요는 없다.

[0067] H.264/AVC 표준은 4 차원 및 8 차원 정수 변환, 즉  $T_4$  및  $T_8$ 을 아래에 주어진 바와 같이 규정하고 있다:

### 수학식 1

$$T_4 = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 2 & 1 & -1 & -2 \\ 1 & -1 & -1 & 1 \\ 1 & -2 & 2 & -1 \end{bmatrix}$$

[0068]

### 수학식 2

$$T_8 = \begin{bmatrix} 8 & 8 & 8 & 8 & 8 & 8 & 8 & 8 \\ 12 & 10 & 6 & 3 & -3 & -6 & -10 & -12 \\ 8 & 4 & -4 & -8 & -8 & -4 & 4 & 8 \\ 10 & -3 & -12 & -6 & 6 & 12 & 3 & -10 \\ 8 & -8 & -8 & 8 & 8 & -8 & -8 & 8 \\ 6 & -12 & 3 & 10 & -10 & -3 & 12 & -6 \\ 4 & -8 & 8 & -4 & -4 & 8 & -8 & 4 \\ 3 & -6 & 10 & -12 & 12 & -10 & 6 & -3 \end{bmatrix}$$

[0069]

[0070] 이들 2개의 정수 변환  $T_4$  및  $T_8$ 은 직교성이고, 아주 낮은 복잡도를 가진다. 그렇지만, 이러한 변환의 기저 벡터들은 DCT와 실질적으로 상이하고, 따라서 성능은 일반적으로 DCT보다 더 나쁘다. 그에 부가하여, 기저 벡터들의 노름들(norms)이 서로 상이하다. 가역성 및 에너지 보존에 있어서, 이 단점을 보상하기 위해 변환 후에 스케일링 프로세스가 수행되어야만 하고, 이는 계산 복잡도 및 메모리 요구사항을 증가시킨다. 그에 부가하여, 이러한 스케일링 행렬들은 종종 변환마다 상이하다. 예를 들어, 4 차원 및 8 차원 변환  $T_4$  및  $T_8$ 은 상이한 스케일링 행렬들의 사용을 필요로 한다. 상이한 스케일링 행렬들의 사용은 코덱 설계 및 구현을 더욱 복잡하게 하고, 필요할 때 부가의 변환을 지원하는 것을 더 어렵게 만든다.

[0071] 앞서 살펴본 바와 같이, HEVC에서, CU 크기 및 PU 크기는 64x64 요소들 정도로 클 수 있고, 4 차원 및 8 차원보다 큰 변환이 요구된다. 현재, HEVC에서 4개의 변환 크기들이 사용된다: 4 차원, 8 차원, 16 차원 및 32 차원.

[0072] 변환 행렬 세트를 가지는 장치 및 유형의(tangible) 컴퓨터 판독가능 저장 매체가 본 명세서에 개시되어 있다. 변환 행렬 세트의 각각의 변환 행렬은 직교성이고, 상이한 수의 요소들을 가진다. 각자의 수의 요소들의 각각의 요소는 정수이다. 각각의 변환 행렬의 기저 벡터들의 노름들 간의 차는 주어진 임계값을 만족시킨다. 그리고 기저 벡터들은 DCT 행렬의 대응하는 기저 벡터들과 비슷하다. 주어진 임계값은, 예를 들어, 만족될 때, 기저 벡터들의 노름들(norms) 간의 차가 [예컨대, 특정의 정밀도 내에서] 무시할 정도라는 것을 나타내는 임계값일 수 있다. 다른 대안으로서, 주어진 임계값은, 만족될 때, 기저 벡터들의 노름들이 거의 같다는 것을 나타내는 임계값일 수 있다. 일 실시예에서, 기저 벡터들은 왜곡의 척도에 따라 대응하는 DCT 기저 벡터들과 비슷하다. 일 실시예에서, 기저 벡터들은 사전 정의된 임계값을 만족시키는 왜곡의 척도에 따라 대응하는 DCT 기저 벡터들과 비슷하다.

[0073] N 차원 정수 변환(즉,  $T_N$ )을 발생시키는 및/또는 사용하는 방법, 장치 및 시스템이 또한 개시되어 있으며, 여기서 N은 4, 8, 16, 32 등일 수 있다. 본 명세서에 개시되어 있는 다양한 실시예들에서, 변환의 "차원"은, 예를 들어, "K 차원(order-K)" 등과 같은 용어를 비롯한 다른 표기법들을 사용하여 표현될 수 있다.

[0074] N 차원 정수 변환  $T_N$  각각은 직교성일 수 있다. 직교성이기 때문에, 이들 N 차원 정수 변환  $T_N$ 은 (비직교 변환과 달리) 재구성 오차(reconstruction error)의 평균 에너지를 양자화 오차(quantization error)의 평균 에너지와 같게 만들 수 있고, 따라서 비직교 변환보다 더 나은 변환 성능을 가질 수 있다.

[0075]  $N$  차원 정수 변환  $T_N$  각각은 거의 같은 노름들("  $T_N$  기저 벡터 노름들")을 가지는 기저 벡터들("  $T_N$  기저 벡터들")을 가질 수 있다. 예를 들어,  $T_N$  기저 벡터 노름들 간의 차가 주어진 임계값보다 작을 수 있다.  $T_N$  기저 벡터들은, 예를 들어, DCT의 기저 벡터들("DCT 기저 벡터들")과 비슷할 수 있다.  $T_N$  기저 벡터들과 DCT 기저 벡터들 간의 차는 DCT 왜곡에 의해 측정될 수 있다. 그리고, DCT 왜곡이 사전 정의된 임계값보다 작을 때,  $T_N$  기저 벡터들은 DCT 기저 벡터들과 비슷할 수 있다. DCT 왜곡의 계산은 변환의 기저 벡터들의 전부 또는 일부분을 포함할 수 있다. 일 실시예에서,  $T_N$ 의 DCT 왜곡은 다음과 같이 계산될 수 있다. 먼저,  $T_N$  기저 벡터들 각각이 정규화된다.  $T_N$  기저 벡터들은  $T_N$  기저 벡터들 각각을 그 자신의 노름으로 나누는 것에 의해 정규화될 수 있다. 그 후에, DCT 왜곡이 이하의 수학식 3 및 수학식 4를 사용하여 계산될 수 있고:

### 수학식 3

$$DistortionMaxtrix = ICT_N \times DCT_N^T$$

[0076] 여기서  $ICT_N$ 은 정규화된  $T_N$ 이고,  $DCT_N$ 은  $N \times N$  DCT 행렬이며,

### 수학식 4

$$Distortion_{DCT} = \frac{1}{N} \sum_{s \in S} \sum_{\substack{j=0 \\ j \neq s}}^{N-1} \left| \frac{DistortionMaxtrix(s, j)}{DistortionMaxtrix(s, s)} \right|$$

[0077] 여기서  $S$ 는 변환의 기저 벡터 세트이다.  $S$ 는 모든 기저 벡터들(예컨대,  $s$ 는  $\{0, 1, \dots, 2, N-1\}$ 일 수 있음) 또는 기저 벡터들의 일부분(예컨대,  $s$ 는  $\{0, 1, 2, 7, 10, \dots\}$ 일 수 있음)을 포함할 수 있다.

[0078] 일 실시예에서,  $N$  차원 정수 변환  $T_N$ 은 특수한 대칭 및 구조를 나타내는 각자의 변환 행렬들을 가질 수 있다. 이를 대칭 및 구조는, 예를 들어, 본 명세서에 개시된 것과 같은 고속 알고리즘의 사용을 용이하게 해줄 수 있다. 일 실시예에서,  $N$  차원 정수 변환  $T_N$ 의 순방향 변환(forward transform), 양자화, 역양자화 및/또는 역변환 중 임의의 것이 16 비트 산술을 사용하여 구현될 수 있다.

[0079] 또한, 여러 계열의  $N$  차원 변환이 본 명세서에 개시되어 있고, 여기서  $N$ 은 8, 16 및 32이다. 동일한 계열의 각각의 변환  $T_N$ 은 동일한 구조["변환 계열 구조(transform family structure)"]를 가질 수 있다. 예를 들어, 8 차원 변환 계열의 변환  $T_8$ 은 모두가 8 차원 변환 계열 구조를 가질 수 있다. 16 차원 변환 계열의 변환  $T_{16}$ 은 모두가 16 차원 변환 계열 구조를 가질 수 있고, 32 차원 변환 계열의 변환  $T_{32}$ 은 모두가 32 차원 변환 계열 구조를 가질 수 있다. 변환 계열 구조들은 이러한 대응하는 계열의 각각의 변환  $T_N$ 이 완전 인수분해되고 고속 알고리즘을 사용하여 구현될 수 있게 할 수 있다. 완전 인수분해를 사용하여 구현가능한 것에 부가하여, 각각의 계열의 변환 내에서의 많은 실시예들이,  $N$  차원 정수 변환(즉,  $T_N$ )과 같이, (i) 직교성 또는 거의 직교성일 수 있고, (ii) 거의 같은 노름들을 가지는 기저 벡터들을 가질 수 있다. 이를 기저 벡터는 또한 DCT 행렬의 기저 벡터들과 비슷할 수 있다. 게다가, 이러한 실시예들의 순방향 변환, 양자화, 역양자화 및 역변환 중 임의의 것이 16 비트 산술을 사용하여 수행될 수 있고 및/또는 16 비트 산술을 사용하도록 구성되어 있는 구조로 구현될 수 있다. 다른 대안으로서, 실시예들의 순방향 변환, 양자화, 역양자화 및 역변환 중 임의의 것이 또한 다른 산술 형식을 사용하여 수행될 수 있고/있거나 다른 산술 형식을 사용하도록 구성되어 있는 구조로 구현될 수 있다.

### $N$ 차원 정수 변환의 예시적인 변환 행렬

[0080] 일 실시예에서,  $K$  차원 변환  $T_K$ 가 중간 행렬(즉,  $T_K'$ )을 사용하여 형성될 수 있다. 일 실시예에 따르면, 중간 행렬  $T_K'$ 은 중간 변환 계수 행렬과 짹수-홀수 분해 행렬의 행렬 곱셈으로 표현될 수 있다. 중간 변환 계수 행렬은 짹수 부분 및 홀수 부분을 포함할 수 있다. A 짹수-홀수 분해 행렬을  $K$  차원 변환  $T_K$ 에 적용하는 것은  $K$  차원

변환  $T_K$ 를 짝수 부분 및 홀수 부분으로 분해할 수 있다. 짝수 부분은, 예를 들어,  $N/2$  차원(즉, 저차원) 변환  $T_{K/2}$ 일 수 있고, 홀수 부분은 저차원 변환 행렬  $P_{K/2}$ 일 수 있다. 일 실시예에서, 중간 행렬  $T_K'$ 은 다음과 같이 표현될 수 있다:

### 수학식 5

$$[0084] T_K' = \begin{bmatrix} T_{K/2} & 0 \\ 0 & P_{K/2} \end{bmatrix} \begin{bmatrix} I_{K/2} & J_{K/2} \\ I_{K/2} & -J_{K/2} \end{bmatrix}$$

[0085] 여기서  $K = 2^z$ 이고,  $z$ 는 양의 정수이며,  $\begin{bmatrix} T_{K/2} & 0 \\ 0 & P_{K/2} \end{bmatrix}$ 는 중간 변환 계수 행렬일 수 있고,  $\begin{bmatrix} I_{K/2} & J_{K/2} \\ I_{K/2} & -J_{K/2} \end{bmatrix}$ 는 짝수-홀수 분해 행렬일 수 있다. 짝수-홀수 분해 행렬에서,  $I_N$  및  $J_N$ 은 다음과 같이 정의될 수 있다:

### 수학식 6

$$[0086] I_N(i, j) = \begin{cases} 1 & i = j \text{인 경우} \\ 0 & 그렇지 않은 경우 \end{cases} \quad 0 \leq i, j \leq N - 1$$

### 수학식 7

$$[0087] J_N(i, j) = \begin{cases} 1 & (i + j) = N - 1 \text{인 경우} \\ 0 & 그렇지 않은 경우 \end{cases} \quad 0 \leq i, j \leq N - 1$$

[0088] 중간 행렬  $T_N'$ 으로부터  $N$  차원 변환 행렬  $T_N$ 으로의 변환은 다음과 같이 수행될 수 있다:

### 수학식 8

$$[0089] T_N(i, j) = \begin{cases} T_N'(n, j) & i = 2n \text{인 경우} \\ T_N'\left(n + \frac{N}{2}, j\right) & i = 2n + 1 \text{인 경우} \end{cases} \quad 0 \leq i, j \leq K - 1$$

[0090] 예로서, 일 실시예에 따른, 8 차원 변환  $T_8$ 을 형성하기 위한 중간 행렬(즉,  $T_8'$ )은 중간 변환 계수 행렬

$\begin{bmatrix} T_4 & 0 \\ 0 & P_4 \end{bmatrix}$  와 짝수-홀수 분해 행렬  $\begin{bmatrix} I_4 & J_4 \\ I_4 & -J_4 \end{bmatrix}$ 의 행렬 곱셈으로 표현될 수 있다. 예를 들어, 중간 행렬  $T_8'$ 은 다음과 같이 표현될 수 있다:

### 수학식 9

$$T_8' = \begin{bmatrix} T_4 & 0 \\ 0 & P_4 \end{bmatrix} \begin{bmatrix} I_4 & J_4 \\ I_4 & -J_4 \end{bmatrix}$$

[0091]

$$\begin{bmatrix} T_4 & 0 \\ 0 & P_4 \end{bmatrix}$$

[0092] 중간 변환 계수 행렬  $\begin{bmatrix} T_4 & 0 \\ 0 & P_4 \end{bmatrix}$  는 짹수 부분 및 홀수 부분을 포함할 수 있다. 짹수 부분은 4 차원 변환  $T_4$  (즉, 보다 낮은  $N/2$  차원, 단,  $N=8$ )의 변환 행렬일 수 있고, 홀수 부분은 저차원 행렬  $P_4$ 일 수 있다. 일 실시예에 따른 4 차원 행렬  $T_4$ (또는, 수학식 9와 관련하여, "저차원 짹수 부분 행렬")는 다음과 같을 수 있다:

### 수학식 10

$$T_4 = \begin{bmatrix} 128 & 128 & 128 & 128 \\ 167 & 70 & -70 & -167 \\ 128 & -128 & -128 & 128 \\ 70 & -167 & 167 & -70 \end{bmatrix}$$

[0093]

[0094] 4 차원 행렬  $T_4$ 의 변환 계수들은 다수의 인자들에 기초하여 경험적으로 결정될 수 있다. 이들 인자는, 예를 들어, 변환 계수들 모두가 정수인 것, 4 차원 변환  $T_4$ 가 직교인 것,  $T_4$  기저 벡터 노름들이 같거나 거의 같은 것(예컨대, 임계값을 만족시킴) 및  $T_4$  기저 벡터들이 DCT 기저 벡터들과 비슷한 것(예컨대, DCT 왜곡이 사전 정의된 임계값보다 작아야 한다는 조건을 만족시키는 것)을 포함할 수 있다.

[0095]

일 실시예에 따른 저차원 행렬  $P_4$ (또는, 수학식 9와 관련하여, "저차원 홀수 부분 행렬")는 다음과 같을 수 있다:

### 수학식 11

$$P_4 = \begin{bmatrix} 185 & 144 & 96 & 37 \\ 144 & -37 & -185 & -96 \\ 96 & -185 & 37 & 144 \\ 37 & -96 & 144 & -185 \end{bmatrix}$$

[0096]

[0097] 저차원 행렬  $P_4$ 의 요소는 다수의 인자들에 기초하여 경험적으로 결정될 수 있다. 이들 인자는, 예를 들어, 요소들 모두가 정수인 것, 저차원 행렬  $P_4$ 가 직교인 것, 저차원 행렬  $P_4$  기저 벡터 노름들이 같거나 거의 같은 것(예컨대, 임계값을 만족시킴) 및 저차원 행렬  $P_4$  기저 벡터들이 DCT 기저 벡터들과 비슷한 것(예컨대, DCT 왜곡이 사전 정의된 임계값보다 작아야 한다는 조건을 만족시키는 것)을 포함할 수 있다.

[0098] 짹수-홀수 분해 행렬의  $I_4$  및  $J_4$ 는, 각각, 상기 수학식 6 및 수학식 7로서 표현될 수 있다.

[0099] 수학식 8 내지 수학식 11의 적용으로부터, 8 차원 정수 변환  $T_8$ 은 다음과 같을 수 있다:

### 수학식 12

$$T_8 = [$$

$$\begin{array}{cccccccc} 128 & 128 & 128 & 128 & 128 & 128 & 128 & 128 \\ 185 & 144 & 96 & 37 & -37 & -96 & -144 & -185 \\ 167 & 70 & -70 & -167 & -167 & -70 & 70 & 167 \\ 144 & -37 & -185 & -96 & 96 & 185 & 37 & -144 \\ 128 & -128 & -128 & 128 & 128 & -128 & -128 & 128 \\ 96 & -185 & 37 & 144 & -144 & -37 & 185 & -96 \\ 70 & -167 & 167 & -70 & -70 & 167 & -167 & 70 \\ 37 & -96 & 144 & -185 & 185 & -144 & 96 & -37 \end{array}]$$

[0100]

[0101] 일 실시예에서,  $N$  차원 정수 변환  $T_N$  각각은 저차원 정수 변환으로 표현될 수 있다. 예를 들어, 일 실시예에 따

른, 16 차원 변환  $T_{16}$ 을 형성하기 위한 중간 행렬  $T_{16}'$ 은 중간 변환 계수 행렬  $\begin{bmatrix} T_8 & 0 \\ 0 & P_8 \end{bmatrix}$  짹수-홀수 분해

행렬  $\begin{bmatrix} I_8 & J_8 \\ I_8 & -J_8 \end{bmatrix}$ 의 행렬 곱셈으로 표현될 수 있다. 중간 변환 계수 행렬  $\begin{bmatrix} T_8 & 0 \\ 0 & P_8 \end{bmatrix}$ 은 짹수 부분 및 홀수 부분을 포함할 수 있다. 짹수 부분은 8 차원(즉, 저차원) 변환  $T_8$ 일 수 있고, 홀수 부분은 저차원 변환 행렬  $P_4$ 일 수 있다. 중간 행렬  $T_{16}'$ 은 다음과 같이 표현될 수 있다:

### 수학식 13

$$T_{16}' = \begin{bmatrix} T_8 & 0 \\ 0 & P_8 \end{bmatrix} \begin{bmatrix} I_8 & J_8 \\ I_8 & -J_8 \end{bmatrix}$$

[0102]

[0103] 여기서  $P_8$ 은 다음과 같이 정의될 수 있다:

## 수학식 14

$$P_8 = [$$

$$180 \ 173 \ 160 \ 140 \ 115 \ 85 \ 53 \ 17$$

$$115 \ 85 \ 53 \ 17 \ -180 \ -173 \ -160 \ -140$$

$$160 \ 140 \ -180 \ -173 \ -53 \ -17 \ 115 \ 85$$

$$17 \ 53 \ -85 \ -115 \ 140 \ 160 \ -173 \ -180$$

$$53 \ -17 \ -115 \ 85 \ 160 \ -140 \ -180 \ 173$$

$$173 \ -180 \ -140 \ 160 \ -85 \ 115 \ 17 \ -53$$

$$140 \ -160 \ 173 \ -180 \ -17 \ 53 \ -85 \ 115$$

$$85 \ -115 \ 17 \ -53 \ 173 \ -180 \ 140 \ -160$$

]

[0104]

[0105] 수학식 6 내지 수학식 8, 수학식 13 및 수학식 14에 기초하여, 16 차원 변환 행렬  $T_{16}$ 은 다음과 같을 수 있다:

## 수학식 15

$$T_{16} = [$$

$$128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128 \ 128$$

$$180 \ 173 \ 160 \ 140 \ 115 \ 85 \ 53 \ 17 \ -17 \ -53 \ -85 \ -115 \ -140 \ -160 \ -173 \ -180$$

$$185 \ 144 \ 96 \ 37 \ -37 \ -96 \ -144 \ -185 \ -185 \ -144 \ -96 \ -37 \ 37 \ 96 \ 144 \ 185$$

$$115 \ 85 \ 53 \ 17 \ -180 \ -173 \ -160 \ -140 \ 140 \ 160 \ 173 \ 180 \ -17 \ -53 \ -85 \ -115$$

$$167 \ 70 \ -70 \ -167 \ -167 \ -70 \ 70 \ 167 \ 167 \ 70 \ -70 \ -167 \ -167 \ -70 \ 70 \ 167$$

$$160 \ 140 \ -180 \ -173 \ -53 \ -17 \ 115 \ 85 \ -85 \ -115 \ 17 \ 53 \ 173 \ 180 \ -140 \ -160$$

$$144 \ -37 \ -185 \ -96 \ 96 \ 185 \ 37 \ -144 \ -144 \ 37 \ 185 \ 96 \ -96 \ -185 \ -37 \ 144$$

$$17 \ 53 \ -85 \ -115 \ 140 \ 160 \ -173 \ -180 \ 180 \ 173 \ -160 \ -140 \ 115 \ 85 \ -53 \ -17$$

$$128 \ -128 \ -128 \ 128 \ -128 \ 128 \ 128 \ -128 \ -128 \ 128 \ 128 \ -128 \ 128 \ -128 \ 128$$

$$53 \ -17 \ -115 \ 85 \ 160 \ -140 \ -180 \ 173 \ -173 \ 180 \ 140 \ -160 \ -85 \ 115 \ 17 \ -53$$

$$96 \ -185 \ 37 \ 144 \ -144 \ -37 \ 185 \ -96 \ -96 \ 185 \ -37 \ -144 \ 144 \ 37 \ -185 \ 96$$

$$173 \ -180 \ -140 \ 160 \ -85 \ 115 \ 17 \ -53 \ 53 \ -17 \ -115 \ 85 \ -160 \ 140 \ 180 \ -173$$

$$70 \ -167 \ 167 \ -70 \ -70 \ 167 \ -167 \ 70 \ 70 \ -167 \ 167 \ -70 \ -70 \ 167 \ -167 \ 70$$

$$140 \ -160 \ 173 \ -180 \ -17 \ 53 \ -85 \ 115 \ -115 \ 85 \ -53 \ 17 \ 180 \ -173 \ 160 \ -140$$

$$37 \ -96 \ 144 \ -185 \ 185 \ -144 \ 96 \ -37 \ -37 \ 96 \ -144 \ 185 \ -185 \ 144 \ -96 \ 37$$

$$85 \ -115 \ 17 \ -53 \ 173 \ -180 \ 140 \ -160 \ 160 \ -140 \ 180 \ -173 \ 53 \ -17 \ 115 \ -85$$

]

[0106]

[0107] 일 실시예에서, N 차원 정수 변환  $T_N$  각각은 저차원 정수 변환으로 표현될 수 있다. 일 실시예에 따른, 32 차원

$$\begin{bmatrix} T_{16} & 0 \\ 0 & P_{16} \end{bmatrix}$$

변환  $T_{32}$ 를 형성하기 위한 중간 행렬  $T_{32}'$ 은 중간 변환 계수 행렬

$$\begin{bmatrix} I_{16} & J_{16} \\ I_{16} & -J_{16} \end{bmatrix}$$

의 행렬 곱셈으로 표현될 수 있다. 중간 변환 계수 행렬  $\begin{bmatrix} T_{16} & 0 \\ 0 & P_{16} \end{bmatrix}$ 은 짹수 부분 및 홀수 부분을 포함할 수 있다. 짹수 부분은 16 차원(즉, 저차원) 변환  $T_{16}$ 일 수 있고, 홀수 부분은 저차원 변환 행렬  $P_{16}$ 일 수 있다. 중간 행렬  $T_{32}'$ 은 다음과 같이 표현될 수 있다:

### 수학식 16

$$[0108] T_{32}' = \begin{bmatrix} T_{16} & 0 \\ 0 & P_{16} \end{bmatrix} \begin{bmatrix} I_{16} & J_{16} \\ I_{16} & -J_{16} \end{bmatrix}$$

[0109] 일 실시예에서, 수학식 16의 저차원 행렬  $P_{16}$ 은 다음과 같이 정의될 수 있다:

### 수학식 17

$$[0110] P_{16} = \begin{bmatrix} P_8 & 0 \\ 0 & P_8 \end{bmatrix} W$$

[0111] 여기서  $\begin{bmatrix} P_8 & 0 \\ 0 & P_8 \end{bmatrix}$ 은 웨이블릿 분해를 위한 저차원 중간 행렬이고,  $W$ 는  $16 \times 16$  웨이블릿 변환일 수 있으며, 그의 한 예가 다음과 같이 나타내어질 수 있다:

### 수학식 18

$$[0112] W = \begin{bmatrix} 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 \\ 1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 0 & 1 & -1 & 0 & 0 & 0 & 0 \end{bmatrix}$$

[0113] 웨이블릿 변환은, 예를 들어, Haar 변환일 수 있다. 웨이블릿 변환은 또한 다른 웨이블릿 변환일 수 있다. 웨이블릿 분해를 위한 저차원 중간 행렬에서의  $P_8$ 은 보다 낮은 8 차원 변환  $T_8$ (즉,  $N/4$  차원 변환)일 수 있다. 수학식 6 내지 수학식 8, 및 수학식 16 내지 수학식 18에 기초하여, 도 2에 나타낸 32 차원 변환 행렬  $T_{16}'$ 이 발생될 수 있다.

### 예시적인 동작

[0115] 도 1c 및 도 1d를 참조하면, 비디오 인코더(33) 및 비디오 디코더(35)에 대해, 비디오 인코더(33)의 변환 유닛 (48)에의 입력의 동적 범위 및 비디오 디코더(35)의 역변환(74)의 출력의 동적 범위가 동일할 수 있다. 비디오 인코더(33) 및/또는 비디오 디코더(35)에서의 변환 동작들에 대해, 이 동적 범위가 먼저 검출될 수 있고, 이어

서 비트 깊이("BD")에 의해 표현될 수 있다. 한 예로서, 동적 범위가 [-255, 255]인 경우, BD는 8이다. 동적 범위가 [-1023, 1023]인 경우, BD는 10이다. 동적 범위를 결정한 후에, 변수  $\Delta BD$ 가 계산될 수 있다. 변수  $\Delta BD$ 가, 예를 들어, BD-8로서 계산될 수 있다.

[0116] 비디오 인코더(33)에서, 예측 잔차 블록  $X_{MxN}$  - 그 크기는  $M \times N$ 임( $M, N \in \{4, 8, 16, 32\}$ ) - 이, 그 결과, 변환 유닛(48), 양자화 유닛(50), 역양자화 유닛(54) 및 역변환 유닛(56)에서 처리된다. 비디오 처리의 이들 4개의 동작이 이하에서 더 상세히 제공된다. 본 명세서에서 사용되는 바와 같이, 역양자화 유닛(54) 및 역변환 유닛(56)에서 수행되는 동작들은, 각각, 역양자화 및 역변환이라고 할 수 있다. 비디오 디코더(35)에서, 역양자화 유닛(74) 및 역변환 유닛(76)에서 수행되는 동작들은 통상적으로 역양자화 유닛(54) 및 역변환 유닛(56)에서 수행되는 것과 동일하다.

#### 순방향 변환

[0118] 순방향 변환에의 입력은  $X_{MxN}$ 로 표시된 예측 잔차 블록일 수 있다.  $X_{MxN}$ 에 대해 2-D 순방향 변환을 수행하기 위해,  $X_{MxN}$ 에서의  $M$ 개의 행 및  $N$ 개의 열이 각각의 차원에서 순차적으로 변환되고, 이들은, 각각, 수평 및 수직 순방향 변환이라고 한다. 수평 또는 수직 순방향 변환 중 어느 하나가 먼저 형성될 수 있다.

[0119] 수평 순방향 변환이 먼저 수행되는 경우,  $X_{MxN}$ 은 먼저 우측에  $T_N^T$ 으로 곱해지고[윗첨자 T는 전치 행렬을 의미함] 16 비트 산술을 수용하기 위해 적당한 비트 수 만큼 우측으로 시프트된다. 그 결과,  $U_{MxN}$ 은 다음과 같을 수 있다:

#### 수학식 19

$$U_{MxN} = (X_{MxN} \times T_N^T + f_{fwd,h}) >> (\log_2(N) + \Delta BD)$$

[0120] 여기서  $T_N$ ( $N \in \{4, 8, 16, 32\}$ )은 상기와 같고, “ $>>$ ”은 우측 시프트를 의미한다. 인자  $f_{fwd,h}$ 는 반올림을 위한 것이고, 범위  $[0, 2^{(\log_2(N) + \Delta BD)}]$ 에 있을 수 있다. 본 명세서에서의 설명의 간략함을 위해,  $f_{fwd,h}$ 는  $2^{(\log_2(N) + \Delta BD - 1)}$ 일 수 있다.

[0122] 수평 순방향 변환 후에, 중간 블록  $U_{MxN}$ 에 대해 수직 순방향 변환이 수행될 수 있다. 수직 순방향 변환의 프로세스는 다음과 같을 수 있다:

#### 수학식 20

$$Y_{MxN} = (T_M \times U_{MxN} + f_{fwd,v}) >> (\log_2(M) + 7)$$

[0124] 여기서 인자  $f_{fwd,v}$ 는 범위  $[0, 2^{(\log_2(M) + 7)}]$ 에 있을 수 있고, 본 명세서에서의 설명의 간략함을 위해,  $2^{(\log_2(M) + 6)}$ 일 수 있다.

[0125] 그렇지만, 수직 순방향 변환이 먼저 수행될 수 있는 경우,  $X_{MxN}$ 은 먼저 좌측에  $T_M$ 으로 곱해지고 16 비트 산술에 적합하도록 하기 위해 적당한 비트 수 만큼 우측으로 시프트된다. 그 결과,  $U_{MxN}$ 은 다음과 같을 수 있다:

## 수학식 21

$$[0126] U_{M \times N} = (T_M \times X_{M \times N} + f_{fwd, v}) \gg (\log_2(M) + \Delta BD)$$

[0127] 인자  $f_{fwd, v}$ 는 반올림을 위한 것이고, 범위  $[0, 2^{(\log_2(M) + \Delta BD)}]$ 에 있을 수 있다. 본 명세서에서의 설명의 간략함을 위해,  $f_{fwd, v}$ 는  $2^{(\log_2(M) + \Delta BD - 1)}$ 일 수 있다.

[0128] 수직 순방향 변환 후에, 중간 블록  $U_{M \times N}$ 에 대해 수평 순방향 변환이 수행될 수 있다. 수평 순방향 변환의 프로세스는 다음과 같을 수 있다:

## 수학식 22

$$[0129] Y_{M \times N} = (U_{M \times N} \times T_N^T + f_{fwd, h}) \gg (\log_2(N) + 7)$$

[0130] 여기서 인자  $f_{fwd, h}$ 는 범위  $[0, 2^{(\log_2(N) + 7)}]$ 에 있을 수 있고, 본 명세서에서의 설명의 간략함을 위해,  $2^{(\log_2(N) + 6)}$ 일 수 있다.

## 양자화

[0132] 양자화의 입력은 2-D 순방향 변환의 출력(즉,  $Y_{M \times N}$ )일 수 있다.  $Y_{M \times N}$  내의 모든 요소들에 대한 양자화 프로세스가 동일하거나 상이할 수 있다. 요소  $Y_{M \times N}(i, j)$  ( $0 \leq i \leq M - 1, 0 \leq j \leq N - 1$ ) 및 관련 양자화 스텝 크기(quantization stepsize)  $W_{M \times N}(i, j)$ 가 주어진 경우, 양자화 프로세스는 다음과 같을 수 있고:

## 수학식 23

$$[0133] Z_{M \times N}(i, j) = (Y_{M \times N}(i, j) \times S_{M \times N}(i, j) + f_{M \times N, q}(i, j)) \gg (Q_{M \times N}(i, j) + 7 - \frac{1}{2} \log_2(M \times N) - \Delta BD)$$

[0134] 여기서  $f_{M \times N, q}(i, j)$ 는 반올림을 위한 인자이고, 범위  $[0, 2^{(Q_{M \times N}(i, j) + 7 - \frac{1}{2} \log_2(M \times N) - \Delta BD)}]$ 에 있을 수 있다. 본 명세서에서의 설명의 간략함을 위해,  $f_{M \times N, q}(i, j)$ 는  $2^{(Q_{M \times N}(i, j) + 6 - \frac{1}{2} \log_2(M \times N) - \Delta BD)}$ 일 수 있다. 수학식 23에서,  $S_{M \times N}(i, j)$  및  $Q_{M \times N}(i, j)$ 는 다음과 같은 관계식을 만족시킬 수 있다:

## 수학식 24

$$[0135] \frac{S_{M \times N}(i, j)}{2^{Q_{M \times N}(i, j)}} \approx \frac{1}{W_{M \times N}((i, j))}$$

[0136] 여기서  $\approx$ 는  $S_{M \times N}(i, j)$ 를 곱하고 이어서  $Q_{M \times N}(i, j)$  비트만큼 우측으로 시프트하는 것이 양자화 스텝 크기  $W_{M \times N}(i, j)$ 로 나누는 것을 근사화하기 위해 사용된다는 것을 의미한다. 보다 정확한 근사화는 우측 시프트 비트의 수  $Q_{M \times N}(i, j)$ 를 증가시키는 것에 의해 달성될 수 있다.

### 역양자화

[0138] 역양자화는 입력  $Z_{M \times N}$ 을 사용하여  $Y'_{M \times N}$ 을 재구성하는 데 사용될 수 있다. 재구성된 블록은  $Y'_{M \times N}$ 으로 표시되어 있다. 직관적으로,  $Y'_{M \times N}(i, j)$ 는  $Z_{M \times N}(i, j)$ 와 양자화 스텝 크기  $W_{M \times N}(i, j)$ 를 곱한 것과 같을 수 있다. 그렇지만,  $W_{M \times N}(i, j)$ 가 꼭 정수일 필요는 없고, 따라서 수학식 24와 유사한 근사화가 또한 수학식 25에서와 같이 역양자화를 위해 수행될 수 있다:

### 수학식 25

$$\frac{D_{M \times N}(i, j)}{2^{IQ_{M \times N}(i, j)}} \approx W_{M \times N}((i, j))$$

[0139]

[0140] 이와 유사하게, 큰  $IQ_{M \times N}(i, j)$ 는 높은 정밀도를 의미한다. 역양자화 프로세스는 다음과 같을 수 있다:

### 수학식 26

$$Y'_{M \times N}(i, j) = (Z_{M \times N}(i, j) \times D_{M \times N}(i, j) + f_{M \times N, dq}(i, j)) \gg (IQ_{M \times N}(i, j) + \frac{1}{2} \log_2(M \times N) - 7 + \Delta BD)$$

[0141]

[0142]  $f_{M \times N, dq}(i, j)$ 는 반올림을 위한 인자이고, 범위  $[0, 2^{(IQ_{M \times N}(i, j) + \frac{1}{2} \log_2(M \times N) - 7 + \Delta BD)}]$ 에 있어야만 한다. 본 명세서에서의 설명의 간략함을 위해,  $f_{M \times N, dq}(i, j)$ 는  $2^{(IQ_{M \times N}(i, j) + \frac{1}{2} \log_2(M \times N) - 8 + \Delta BD)}$ 과 같고/같거나 그에 따를 수 있다. 유의할 점은, 0보다 작은  $(IQ_{M \times N}(i, j) + \frac{1}{2} \log_2(M \times N) - 7 + \Delta BD)$ 의 값이 좌측 시프트를 의미한다는 것이고, 이 경우에  $f_{M \times N, dq}(i, j)$ 는 0으로 설정될 수 있다.

[0143]

### 역변환

[0144] 역변환에의 입력은 역양자화된 블록  $Y'_{M \times N}$ 일 수 있다.  $Y'_{M \times N}$ 에 대해 2-D 역변환을 수행하기 위해,  $Y'_{M \times N}$ 에서의 M개의 행 및 N개의 열이, 각각, 수평 및 수직 역변환을 사용하여, 순차적으로 변환된다. 수평 또는 수직 역변환 중 어느 하나가 먼저 수행될 수 있다.

[0145]

수평 역변환이 먼저 수행되는 경우,  $Y'_{M \times N}$ 은 먼저 우측에  $T_N$ 으로 곱해지고 16 비트 산술을 수용하기 위해 적당한 비트 수 만큼 우측으로 시프트된다. 얻어진 중간 블록  $V_{M \times N}$ 은 다음과 같을 수 있다:

### 수학식 27

$$V_{M \times N} = (Y'_{M \times N} \times T_N + f_{inv, h}) \gg 8$$

[0146]

[0147] 인자  $f_{inv, h}$ 는 범위  $[0, 256]$ 에 있을 수 있다. 본 명세서에서의 설명의 간략함을 위해,  $f_{inv, h}$ 는 128일 수 있다.

[0148] 수평 역변환 후에, 중간 블록  $V_{MxN}$ 에 대해 수직 역변환이 수행될 수 있다. 수직 역변환의 프로세스는 다음과 같을 수 있다:

### 수학식 28

$$X'_{MxN} = (T_M^T \times V_{MxN} + f_{inv,v}) \gg (13 - \Delta BD)$$

[0149] 여기서 인자  $f_{inv,v}$ 는 범위  $[0, 2^{(13-\Delta BD)}]$ 에 있을 수 있고, 본 명세서에서의 설명의 간략함을 위해,  $2^{(12-\Delta BD)}$  일 수 있다.

[0150] [0151] 수직 역변환이 먼저 수행되는 경우,  $Y'_{MxN}$ 은 먼저 좌측에  $T_M^T$ 으로 곱해지고 16 비트 산술을 수용하기 위해 적당한 비트 수 만큼 우측으로 시프트된다. 얻어진 중간 블록  $V_{MxN}$ 은 다음과 같을 수 있다:

### 수학식 29

$$V_{MxN} = (T_M^T \times Y'_{MxN} + f_{inv,v}) \gg 8$$

[0152] [0153] 인자  $f_{inv,v}$ 는 반올림을 위한 것이고, 범위  $[0, 256]$ 에 있을 수 있다. 본 명세서에서의 설명의 간략함을 위해,  $f_{inv,v}$ 는 128일 수 있다.

[0154] 수직 역변환 후에, 중간 블록  $V_{MxN}$ 에 대해 수평 역변환이 수행될 수 있다. 수평 역변환의 프로세스는 다음과 같을 수 있고:

### 수학식 30

$$X'_{MxN} = (V_{MxN} \times T_N + f_{inv,h}) \gg (13 - \Delta BD)$$

[0155] [0156] 여기서 인자  $f_{inv,h}$ 는 범위  $[0, 2^{(13-\Delta BD)}]$ 에 있을 수 있고, 본 명세서에서의 설명의 간략함을 위해,  $2^{(12-\Delta BD)}$  일 수 있다.

[0157] 이하의 표 1은, 수평 변환이 수직 변환보다 먼저 수행되는 것으로 가정하여, 앞서 개시되어 있는 것과 같은 동작들의 각각의 단계 후의 동적 범위를 요약한 것이다. 표로부터 명백한 바와 같이, 프로세스들 모두가 16 비트 산술을 사용하여 구현될 수 있다.

### 표 1

| 동작들       |                               | 출력 비트 깊이                     |

|-----------|-------------------------------|------------------------------|

| 입력        | $X_{MxN}$                     | $9 + \Delta BD$              |

| 수평 순방향 변환 | $X_{MxN}$                     | $16 + \log_2(N) + \Delta BD$ |

| 우측 시프트    | $\gg (\log_2(N) + \Delta BD)$ | 16                           |

| 수직 순방향 변환 | $T_M \times U_{MxN}$          | $23 + \log_2(M)$             |

|               |                                                                                                             |                                                             |

|---------------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| 우측 시프트        | $>> (\log_2(M) + 7)$                                                                                        | 16                                                          |

| 스텝 크기 W로 양자화  | $(Y_{MxN} \times S_{MxN} + f_{MxN,q}) >> (Q_{MxN} + \frac{1}{2} \log_2(M \times N) - \log_2 W - \Delta BD)$ | $9 + \Delta BD + \frac{1}{2} \log_2(M \times N) - \log_2 W$ |

| 스텝 크기 W로 역양자화 | $(Z_{MxN} \times D_{MxN} + f_{MxN,dq}) >> (\frac{1}{2} \log_2(M \times N) - 7 + I_{MxN} + \Delta BD)$       | 16                                                          |

| 수평 역변환        | $Y'_{MxN} \times T_N$                                                                                       | 23                                                          |

| 우측 시프트        | $>> 8$                                                                                                      | 15                                                          |

| 수직 역변환        | $T_M^T \times V_{MxN}$                                                                                      | 22                                                          |

| 우측 시프트        | $>> (13 - \Delta BD)$                                                                                       | $9 + \Delta BD$                                             |

| 출력            | $X'_{MxN}$                                                                                                  | $9 + \Delta BD$                                             |

[0159] 표 1 - 다양한 동작들 후의 동적 범위(수평 변환이 먼저 수행됨)

#### 순방향 변환/역변환의 인수분해

[0161] 순방향 변환 및 역변환의 정의들은 수학식 19 내지 수학식 22 및 수학식 27 내지 수학식 30 등의 행렬 곱셈을 포함한다. 특정의 구현 플랫폼들에 대해, 행렬 곱셈의 복잡도가 높다. 행렬 곱셈의 단순화가 본 명세서에 제공되어 있다. 단순화의 적어도 일부는 변환  $T_N$ , 홀수 부분, 웨이블릿 분해를 위한 저차원 중간 행렬, 및 웨이블릿 분해 행렬 등의 대칭성에 기초하여 개발되었다.

#### 변환에 대한 일반 부분 인수분해

[0163] 도 3a 및 도 3b는 K 차원 변환에 대한 부분 인수분해를 수행하는 한 예시적인 구조를 나타낸 블록도이다. K 차원 변환( $K \in \{4, 8, 16, 32\}$ )에 대한 부분 인수분해를 수행하는 예시적인 순방향 변환 구조, 모듈 또는 유닛(총칭하여, "유닛")이 도 3a에 도시되어 있다. 순방향 변환 유닛(300)은 2개의 스테이지들로 분해될 수 있다. 제1 스테이지는 스테이지 1 유닛(302)을 포함할 수 있고, 제2 스테이지는 2개의 스테이지 2 유닛들(304, 306)을 포함할 수 있다.  $\mathbf{x} = [x_0, x_1, \dots, x_{k-1}]^T$ 의 입력 벡터를 가정할 때, 스테이지 1 유닛(302)은 다음과 같

$$\text{이 } \begin{bmatrix} I_{K/2} & J_{K/2} \\ I_{K/2} & -J_{K/2} \end{bmatrix} \text{ 와 } \mathbf{x} \text{의 행렬 곱셈을 수행하도록 구성되어 있을 수 있다:}$$

#### 수학식 31

$$\mathbf{a} = \begin{bmatrix} I_{K/2} & J_{K/2} \\ I_{K/2} & -J_{K/2} \end{bmatrix} \mathbf{x}$$

[0164]

[0165] 여기서  $\mathbf{a} = [a_0, a_1, \dots, a_{k-1}]^T$ 은 스테이지 1 유닛(302)의 중간 변환 결과 출력 및 스테이지 2 유닛들(304 및 306)에의 입력이다. 스테이지 2 유닛들(304, 306)은 중간 변환 결과  $\mathbf{a}$ 를 2개의 부분들(즉,  $\mathbf{a} = [a_0, a_1, \dots, a_{k-1}]^T$ 의 전반부 및 후반부)로 분할할 수 있다. 중간 변환 결과  $\mathbf{a}$ 의 전반부(즉,  $[a_0, a_1, \dots, a_{k/2-1}]^T$ )는 스테이지 2.1 유닛(304)에 입력될 수 있다. 스테이지 2.1 유닛(304)은, 예를 들어, 다음과 같이  $T_{K/2}$ 와의 행렬 곱셈을 수행할 수 있다:

## 수학식 32

$$[0166] [f_0, f_2, \dots, f_{k-2}]^T = T_{k/2} \times [a_0, a_1, \dots, a_{k/2-1}]^T$$

[0167] 여기서  $[f_0, f_2, \dots, f_{k-2}]^T$ 은 변환 행렬  $T_N$ 의 출력에서의 짝수번째 요소들(even-indexed elements)을 나타낸다.  $[f_0, f_2, \dots, f_{k-2}]^T$ 의 각각의 요소는 변환 행렬  $T_k$ 의 짝수 부분의 기저 벡터에 대응한다. 또한 유의할 점은,  $\mathbf{f} = [f_0, f_1, \dots, f_{k-1}]^T$ 이 1-D 순방향 변환의 출력이라는 것이다. 중간 변환 결과  $\mathbf{a}$ 의 후반부(즉,  $[a_{k/2}, a_{k/2+1}, \dots, a_{k-1}]^T$ )는 스테이지 2.2 유닛(306)에 입력될 수 있다. 스테이지 2.2 유닛(306)은, 예를 들어, 다음과 같이  $P_{k/2}$ 와의 행렬 곱셈을 수행할 수 있다:

## 수학식 33

$$[0168] [f_1, f_3, \dots, f_{k-1}]^T = P_{k/2} \times [a_{k/2}, a_{k/2+1}, \dots, a_{k-1}]^T$$

[0169] 여기서  $[f_1, f_3, \dots, f_{k-1}]^T$ 은 변환 행렬  $T_N$ 의 출력에서의 홀수번째 요소들을 나타낸다.  $[f_1, f_3, \dots, f_{k-1}]^T$ 의 각각의 요소는 변환 행렬  $T_k$ 의 홀수 부분의 기저 벡터에 대응한다.

[0170]  $K$  차원 변환( $K \in \{4, 8, 16, 32\}$ )에 대한 부분 인수분해를 수행하는 예시적인 역변환 유닛(350)이 도 3b에 도시되어 있다. 역변환 유닛(350)은 2개의 스테이지들로 분해될 수 있다. 제1 스테이지는 스테이지 1 유닛들(352 및 354)을 포함할 수 있고, 제2 스테이지는 스테이지 2 유닛(356)을 포함할 수 있다. 도시된 바와 같이,  $\mathbf{f} = [f_0, f_1, \dots, f_{k-1}]^T$ 의 짝수번째 및 홀수번째 요소들이 먼저 개별적으로 그룹화되고, 스테이지 1.1 유닛(352) 및 스테이지 1.2 유닛(354)에, 각각, 입력된다. 스테이지 1.1 유닛(352)은  $T_{k/2}^T$ 와  $[f_0, f_2, \dots, f_{k-2}]^T$ 의 행렬 곱셈을 수행할 수 있고, 스테이지 1.2 유닛(354)은, 예를 들어, 다음과 같이  $P_{k/2}^T$ 와  $[f_1, f_3, \dots, f_{k-1}]^T$ 의 행렬 곱셈을 수행할 수 있다:

## 수학식 34

$$[0171] [b_0, b_1, \dots, b_{k/2-1}]^T = T_{k/2}^T \times [f_0, f_2, \dots, f_{k-2}]^T$$

## 수학식 35

$$[0172] [b_{k/2}, b_{k/2+1}, \dots, b_{k-1}]^T = P_{k/2}^T \times [f_1, f_3, \dots, f_{k-1}]^T$$

[0173] 스테이지 1.1 유닛(352) 및 스테이지 1.2 유닛(354)의 출력들은, 각각, 중간 역변환 결과

$\mathbf{b} = [b_0, b_1, \dots, b_{k-1}]^T$  의 전반부 및 후반부일 수 있다. 중간 역변환 결과  $\mathbf{b}$ 는 스테이지 2 유닛(356)

에 입력될 수 있다. 스테이지 2 유닛(356)은, 예를 들어, 다음과 같이  $\begin{bmatrix} I_{K/2} & J_{K/2} \\ I_{K/2} & -J_{K/2} \end{bmatrix}^T$  와  $\mathbf{b}$ 의 행렬 곱셈을 수행할 수 있다:

### 수학식 36

$$[0174] \quad \mathbf{x} = \begin{bmatrix} I_{K/2} & J_{K/2} \\ I_{K/2} & -J_{K/2} \end{bmatrix}^T \mathbf{b}$$

[0175] 스테이지 2(356)는 또한 최종적인 출력 변환 계수들의 짝수 부분 및 홀수 부분을 결합시킬 수 있다.

### 32 차원 변환에 대한 예시적인 인수분해

[0177] K가, 예를 들어, 32일 때, 32 차원 변환에 대한 순방향 변환 스테이지 2.2 유닛(306) 및 역변환 스테이지 1.2 유닛(354) 각각은, 도 4a 및 도 4b에, 각각, 도시된 바와 같이, 2개의 스테이지들(400 및 450)로 인수분해될 수 있다. 도 4a에 도시된 바와 같이, 스테이지 2.2 유닛(306)은 스테이지 2.2.1 유닛(402), 스테이지 2.2.2 유닛(404) 및 스테이지 2.2.3 유닛(406)을 사용하여 수행될 수 있다. 유닛들(402, 404 및 406)에서 완료되는 행렬 곱셈들은 다음과 같을 수 있다:

### 수학식 37

$$[0178] \quad \mathbf{c} = W \times [a_{16}, a_{17}, \dots, a_{31}]^T$$

### 수학식 38

$$[0179] \quad [f_1, f_3, \dots, f_{15}]^T = P_8 \times [c_0, c_1, \dots, c_7]^T$$

### 수학식 39

$$[0180] \quad [f_{17}, f_{19}, \dots, f_{31}]^T = P_8 \times [c_8, c_9, \dots, c_{15}]^T$$

[0181] 여기서  $\mathbf{c} = [c_0, c_1, \dots, c_{15}]^T$  은 16x1 중간 벡터일 수 있다.

[0182] 도 4b에 도시된 바와 같이, 스테이지 1.2 유닛(354)은 스테이지 1.2.1 유닛(452), 스테이지 1.2.2 유닛(454) 및 스테이지 1.2.3 유닛(456)을 사용하여 수행될 수 있다. 유닛들(452, 454 및 456)에서 수행되는 행렬 곱셈들은 다음과 같을 수 있다:

## 수학식 40

[0183]  $[d_0, d_1, \dots, d_7]^T = P_8^T \times [f_1, f_3, \dots, f_{15}]^T$

## 수학식 41

[0184]  $[d_8, d_9, \dots, d_{15}]^T = P_8^T \times [f_{17}, f_{19}, \dots, f_{31}]^T$

## 수학식 42

[0185]  $[b_{16}, b_{17}, \dots, b_{31}]^T = W^T \times \mathbf{d}$

[0186] 여기서  $\mathbf{d} = [d_0, d_1, \dots, d_{15}]^T$  은  $16 \times 1$  중간 벡터이다.

## 8 차원 변환의 예시적인 구조

[0188] 변환 행렬  $T_8$ 은, 앞서 살펴본 바와 같이, 저차원 짹수 부분 변환 행렬 및 저차원 홀수 부분 행렬을 포함할 수 있다. 저차원 짹수 부분 행렬은, 예를 들어, 변환 행렬  $T_4$ (예를 들어, 수학식 10의 변환 행렬  $T_4$ 를 포함함)일 수 있다. 저차원 홀수 부분 행렬은 다음과 같이 10개의 파라미터들, 즉  $\{a, b, c, d, e, f, i, j, h, k\}$ 에 의해 정의될 수 있는  $P_4$ 일 수 있다:

## 수학식 43

$$P_4 = \begin{bmatrix} h \times ex(a+b) & h \times fx(c+1) & h \times fx(c-1) & h \times ex(a-b) \\ k \times j \times a & -k \times i & -k \times i \times c & -k \times j \times b \\ k \times j \times b & -k \times i \times c & k \times i & k \times j \times a \\ h \times ex(a-b) & -h \times fx(c-1) & h \times fx(c+1) & -h \times ex(a+b) \end{bmatrix}$$

[0189] 저차원 홀수 부분 행렬  $P_4$ 는 3개의  $N/2$  차원 행렬들, 즉  $M_2^4, M_3^4$ , 및  $M_4^4$ 의 곱셈과 같을 수 있다. 즉, 저

차원 홀수 부분 행렬  $P_4 = M_4^4 \times M_3^4 \times M_2^4$  이다. 일 실시예에서, 3개의  $N/2$  차원 행렬들  $M_2^4, M_3^4$ , 및

$M_4^4$ 는 다음과 같이 표현될 수 있다:

### 수학식 44

$$M_2^4 = \begin{bmatrix} a & 0 & 0 & -b \\ 0 & c & -d & 0 \\ 0 & d & c & 0 \\ b & 0 & 0 & a \end{bmatrix}, \quad M_3^4 = \begin{bmatrix} e & 0 & f & 0 \\ 0 & -i & 0 & j \\ j & 0 & -i & 0 \\ 0 & f & 0 & e \end{bmatrix}, \quad M_4^4 = \begin{bmatrix} h & 0 & 0 & h \\ 0 & 0 & k & 0 \\ 0 & k & 0 & 0 \\ h & 0 & 0 & -h \end{bmatrix}$$

[0191]

[0192] 일 실시예에서, 수학식 33에 나타낸 것과 같은 스테이지 2.2 유닛(306)에 의해 수행되는 동작들은 다음과 같이 수행될 수 있다:

### 수학식 45

$$[f_1, f_3, f_5, f_7]^T = M_4^4 \times M_3^4 \times M_2^4 \times [a_4, a_5, a_6, a_7]^T$$

[0193] [0194] 이는  $P_{k/2}$ 와의 행렬 곱셈이  $M_2^4, M_3^4$ , 및  $M_4^4$ 와 순차적으로 행렬 곱셈을 행하는 것으로 완전 인수분해될 수 있다는 것을 의미한다. 이와 유사하게, 수학식 35에 나타낸 것과 같은 스테이지 1.2 유닛(354)의 동작들은 다음과 같이 수행될 수 있다:

### 수학식 46

$$[b_4, b_5, b_6, b_7]^T = (M_2^4)^T \times (M_3^4)^T \times (M_4^4)^T \times [f_1, f_3, f_5, f_7]^T$$

[0195] [0196] 이는  $P_{k/2}^T$ 와의 행렬 곱셈이  $(M_4^4)^T, (M_3^4)^T$ , 및  $(M_2^4)^T$ 와 순차적으로 행렬 곱셈을 행하는 것으로 완전 인수분해될 수 있다는 것을 의미한다.

[0197] 도 5a 및 도 5b는 8 차원 변환에 대한 완전 인수분해를 수행하는 한 예시적인 구조를 나타낸 블록도이다. 파라미터 세트  $\{a, b, c, d, e, f, i, j, h, k\}$ 에 대한 예시적인 값들은  $\{3, 2, 5, 1, 37, 24, 37, 48, 1, 1\}$  및  $\{3, 2, 5, 1, 144, 99, 72, 99, 0.5, 1\}$ 을 포함한다. 수학식 10의 저차원 행렬  $P_4$ 는, 예를 들어, 예시적인 값들  $\{3, 2, 5, 1, 37, 24, 37, 48, 1, 1\}$ 을 사용하여 발생될 수 있다.

### 16 차원 변환의 예시적인 구조

[0198] [0199] 변환 행렬  $T_{16}$ 은, 앞서 살펴본 바와 같이, 저차원 짹수 부분 변환 행렬 및 저차원 홀수 부분 행렬을 포함할 수 있다. 저차원 짹수 부분 행렬은, 예를 들어, 임의의 8 차원 변환의 변환 행렬  $T_8$ (예를 들어, 앞서 "8 차원 변환의 예시적인 구조"라는 제목 하에 논의된 변환 행렬  $T_8$ 을 포함함)일 수 있다. 저차원 홀수 부분 행렬은 다음과 같이 10개의 파라미터들, 즉  $\{a, b, c, d, e, f, g, h, k, l, i, j\}$ 에 의해 정의될 수 있는  $P_8$ 일 수 있다:

## 수학식 47

$$P_8 = [$$

$$\begin{array}{cccccccc}

axl+bxl & cxl+dxl & exl+fxl & gxl+hxl & hxl-gxl & fxl+exl & dxl-cxl & -bxl+axl \\

-axj+bxi & -dxj-cxi & fxj+exi & gxj-hxi & hxj+gxi & exj-fxi & cxj-dxi & bxj+axi \\

axi-bxj & -dxj-cxj & fxj+exj & -gxj+hxi & -hxj-gxj & exi-fxj & cxj-dxj & -bxj-axj \\

axk & -cxk & -exk & gxk & hxk & fxk & -dxk & -bxk \\

bxk & -dxk & -fxk & hxk & -gxk & -exk & cxk & axk \\

-axj-bxi & dxj-cxi & -fxj+exi & gxj+hxi & hxj-gxi & -exj-fxi & -cxj-dxi & bxj-axi \\

-axi-bxj & -dxj+cxj & fxj-exj & gxj+hxi & hxj-gxj & exi+fxj & cxj+dxj & bxj-axj \\

axl-bxl & cxl-dxl & exl-fxl & gxl-hxl & hxl+gxl & -fxl-exl & dxl-cxl & -bxl-axl

\end{array}$$

]

[0200]

[0201] 저차원 흔수 부분 행렬  $P_8$ 은 4개의  $N/2$  차원 행렬들, 즉  $M_2^8, M_3^8, M_4^8$ , 및  $M_5^4$ 의 곱셈과 같을 수 있다.

$P_8 = M_5^4 \times M_4^8 \times M_3^8 \times M_2^8$  이다. 일 실시예에서, 4개의  $N/2$  차원 행렬들  $M_2^8, M_3^8, M_4^8$ , 및  $M_5^4$ 는 다음과 같이 표현될 수 있다:

## 수학식 48

$$M_2^8 = [$$

$$\begin{array}{cccccccc}

a & 0 & 0 & 0 & 0 & 0 & 0 & -b \\

0 & c & 0 & 0 & 0 & 0 & d & 0 \\

0 & 0 & e & 0 & 0 & -f & 0 & 0 \\

0 & 0 & 0 & g & h & 0 & 0 & 0 \\

0 & 0 & 0 & -h & g & 0 & 0 & 0 \\

0 & 0 & f & 0 & 0 & e & 0 & 0 \\

0 & -d & 0 & 0 & 0 & 0 & c & 0 \\

b & 0 & 0 & 0 & 0 & 0 & 0 & a

\end{array}$$

]

[0202]

## 수학식 49

$$M_3^8 = \begin{bmatrix} -1 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & -1 & 1 & 0 & 0 & 0 & 0 & 0 \\ 0 & 1 & 1 & 0 & 0 & 0 & 0 & 0 \\ 1 & 0 & 0 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & -1 & 0 & 0 & 1 \\ 0 & 0 & 0 & 0 & 0 & -1 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & 1 & 0 \\ 0 & 0 & 0 & 0 & 1 & 0 & 0 & 1 \end{bmatrix}$$

[0203]

]

## 수학식 50

$$M_4^8 = \begin{bmatrix} -1 & 0 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & -1 & 0 & 0 & 0 & 0 & 0 & 1 \\ 0 & 0 & -1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & -1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 1 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 & 0 & 0 & 1 & 0 \\ 0 & 1 & 0 & 0 & 0 & 0 & 0 & 1 \end{bmatrix}$$

[0204]

]

## 수학식 51

$$M_5^8 = \begin{bmatrix} 0 & 0 & 0 & 1 & -1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & j & i \\ i & -j & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & k & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & k & 0 & 0 \\ -j & -i & 0 & 0 & 0 & 0 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & i & -j \\ 0 & 0 & 0 & 1 & 1 & 0 & 0 & 0 \end{bmatrix}$$

[0205]

]

[0206]

일 실시예에서, 수학식 33에 나타낸 것과 같은 스테이지 2.2 유닛(306)에 의해 수행되는 동작들은 다음과 같이 수행될 수 있고:

## 수학식 52

$$[0207] [f_1, f_3, \dots, f_{15}]^T = M_5^8 \times M_4^8 \times M_3^8 \times M_2^8 \times [a_8, a_9, \dots, a_{15}]^T$$

[0208] 이는  $P_8$ 과의 행렬 곱셈이  $M_2^8, M_3^8, M_4^8, M_5^8$ 와 순차적으로 행렬 곱셈을 행하는 것으로 완전 인수분해될 수 있다는 것을 의미한다. 이와 유사하게, 수학식 35에 나타낸 것과 같은 스테이지 1.2 유닛(354)의 동작들은 다음과 같이 수행될 수 있다:

## 수학식 53

$$[0209] [b_8, b_9, \dots, b_{15}]^T = (M_2^8)^T \times (M_3^8)^T \times (M_4^8)^T \times (M_5^8)^T \times [f_1, f_3, \dots, f_{15}]^T$$

[0210] 이는  $P_8^T$ 과의 행렬 곱셈이  $(M_5^8)^T, (M_4^8)^T, (M_3^8)^T, (M_2^8)^T$ 와 순차적으로 행렬 곱셈을 행하는 것으로 완전 인수분해될 수 있다는 것을 의미한다.

[0211] 도 6a 및 도 6b는 16 차원 변환에 대한 완전 인수분해를 수행하는 한 예시적인 구조를 나타낸 블록도이다. 파라미터 세트  $\{a, b, c, d, e, f, g, h, k, l, i, j\}$ 에 대한 예시적인 값들은 이하의 표 2에 나타내어져 있다.

## 표 2

| <i>a</i> | <i>b</i> | <i>c</i> | <i>d</i> | <i>e</i> | <i>f</i> | <i>g</i> | <i>h</i> | <i>k</i> | <i>l</i> | <i>I</i> | <i>j</i> |

|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| 1        | 1        | 1        | 1        | 2        |          | 2        | 1        | 1        |          |          |          |

| 6        | 4        | 0        | 9        | 0        | 6        | 2        | 1        | 7        | 2        | 6        | -16      |

| 1        | 1        | 1        | 1        | 2        |          | 2        | 1        | 1        |          |          |          |

| 6        | 4        | 0        | 9        | 1        | 6        | 2        | 1        | 7        | 2        | 6        | -16      |

| 1        | 1        | 1        | 1        | 2        |          | 2        | 1        | 1        |          |          |          |

| 7        | 3        | 0        | 9        | 0        | 6        | 2        | 1        | 7        | 2        | 6        | -16      |

| 1        | 1        | 1        | 1        | 2        |          | 2        | 1        | 1        |          |          |          |

| 7        | 3        | 0        | 9        | 1        | 6        | 2        | 1        | 7        | 2        | 6        | -16      |

| 1        | 1        | 1        | 1        | 2        |          | 2        | 1        | 1        |          |          |          |

| 7        | 4        | 0        | 9        | 0        | 6        | 2        | 1        | 7        | 2        | 6        | -16      |

| 3        | 2        | 1        | 3        | 4        | 1        | 4        | 1        | 1        |          |          |          |

| 2        | 8        | 9        | 8        | 1        | 2        | 4        | 2        | 7        | 2        | 6        | -16      |

| 3        | 2        | 1        | 3        | 4        | 1        | 4        | 1        | 1        |          |          |          |

| 2        | 8        | 9        | 8        | 1        | 2        | 4        | 3        | 7        | 2        | 6        | -16      |

| 3        | 2        | 2        | 3        | 4        | 1        | 4        | 1        | 1        |          |          |          |

| 2        | 8        | 0        | 8        | 1        | 1        | 4        | 2        | 7        | 2        | 6        | -16      |

| 3        | 2        | 2        | 3        | 4        | 1        | 4        | 1        | 1        |          |          |          |

| 2        | 8        | 0        | 8        | 1        | 2        | 4        | 2        | 7        | 2        | 6        | -16      |

| 3        | 2        | 2        | 3        | 4        | 1        | 4        | 1        | 1        |          |          |          |

| 2        | 8        | 1        | 7        | 1        | 2        | 4        | 2        | 7        | 2        | 6        | -16      |

[0212]

|   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 2 | 8 | 1 | 7 | 1 | 2 | 4 | 3 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 2 | 8 | 1 | 7 | 1 | 2 | 5 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 9 | 8 | 1 | 2 | 4 | 3 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 9 | 8 | 1 | 3 | 5 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 0 | 8 | 1 | 1 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 0 | 8 | 1 | 2 | 4 | 3 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 2 | 4 | 3 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 2 | 5 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 3 | 4 | 3 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 3 | 5 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 4 | 6 | 9 | 8 | 1 | 1 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 4 | 6 | 9 | 8 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 4 | 6 | 9 | 8 | 1 | 2 | 5 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 4 | 6 | 9 | 8 | 1 | 3 | 4 | 3 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 4 | 6 | 0 | 8 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 4 | 6 | 1 | 7 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 9 | 8 | 1 | 1 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 9 | 8 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 0 | 3 | 5 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 2 | 7 | 0 | 7 | 0 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 2 | 7 | 0 | 7 | 0 | 3 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 6 | 0 | 7 | 0 | 3 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 9 | 8 | 1 | 1 | 4 | 2 | 7 | 2 | 6 |

[0213]

|   |   |   |   |   |   |   |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 9 | 8 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 0 | 8 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 2 | 4 | 2 | 7 | 2 | 6 |

| 3 | 2 | 1 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 9 | 8 | 1 | 0 | 2 | 3 | 7 | 2 | 6 |

| 3 | 2 | 2 | 3 | 4 | 1 | 4 | 1 | 1 | 1 |   |

| 3 | 7 | 1 | 7 | 1 | 3 | 4 | 2 | 7 | 2 | 6 |

| 2 | 1 | 1 | 2 | 2 |   | 3 | 2 | 1 | 1 |   |

| 3 | 9 | 3 | 7 | 9 | 8 | 3 | 0 | 4 | 7 | 0 |

| 2 | 1 | 1 | 2 | 2 |   | 3 | 2 | 1 | 1 |   |

| 3 | 9 | 4 | 6 | 9 | 9 | 3 | 0 | 4 | 7 | 0 |

| 2 | 1 | 1 | 2 | 2 |   | 3 | 2 | 1 | 1 |   |

| 3 | 9 | 5 | 6 | 9 | 9 | 3 | 0 | 4 | 7 | 0 |

| 2 | 1 | 1 | 2 | 2 |   | 3 | 2 | 1 | 1 |   |

| 3 | 9 | 4 | 7 | 9 | 8 | 3 | 0 | 4 | 7 | 0 |

| 2 | 1 | 1 | 2 | 2 |   | 3 | 2 | 1 | 1 |   |

| 3 | 9 | 5 | 6 | 9 | 9 | 3 | 0 | 4 | 7 | 0 |

[0214]

표 2 - P<sub>8</sub>에 대한 실시예들

[0215]

32 차원 변환의 예시적인 구조

[0217] 변환 행렬  $T_{32}$ 은, 앞서 살펴본 바와 같이, 저차원 짹수 부분 변환 행렬 및 저차원 홀수 부분 행렬을 포함할 수 있다. 저차원 짹수 부분 행렬은, 예를 들어, 임의의 16 차원 변환의 변환 행렬  $T_{16}$ (예를 들어, 앞서 "16 차원 변환의 예시적인 구조"라는 제목 하에 논의된 변환 행렬  $T_{16}$ 을 포함함)일 수 있다. 저차원 홀수 부분 행렬은 2개의 행렬들 X 및 Y의 행렬 곱셈에 의해 정의될 수 있는  $P_{16}$ 일 수 있다. 즉,  $P_{16} = Y \times X$ 이다. 이어서, 수학식 33에 의해 제공되는 프로세스가, 수학식 54 및 수학식 55로 나타낸 바와 같은 2개의 스테이지들로, 각각, 분해될 수 있다:

#### 수학식 54

$$\mathbf{c}^T = X \times [a_{16}, a_{17}, \dots, a_{31}]^T$$

#### 수학식 55

$$[f_1, f_3, \dots, f_{31}]^T = Y \times \mathbf{c}^T$$