(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년03월25일

(11) 등록번호 10-1244573

(24) 등록일자 2013년03월11일

- (51) 국제특허분류(Int. Cl.)

*H04N 5/365* (2011.01) *H04N 5/374* (2011.01)

- (21) 출원번호 10-2007-7027899

- (22) 출원일자(국제) 2006년05월26일

심사청구일자 2011년05월26일

- (85) 번역문제출일자 2007년11월29일

- (65) 공개번호 10-2008-0011679

- (43) 공개일자 2008년02월05일

- (86) 국제출원번호 PCT/US2006/020587

- (87) 국제공개번호 WO 2006/130519

국제공개일자 2006년12월07일

- (30) 우선권주장

11/398,514 2006년04월05일 미국(US)

60/686,160 2005년06월01일 미국(US)

- (56) 선행기술조사문헌

WO2005011264 A2\*

JP2002050752 A\*

\*는 심사관에 의하여 인용된 문헌

- (73) 특허권자

옴니비전 테크놀러지즈 인코포레이티드

미국 캘리포니아 95054 산타 클라라 버튼 드라이브 4275

- (72) 발명자

가이다쉬 로버트 마이클

미국 뉴욕주 14618 로체스터 앤틀러스 드라이브 460

엘루시윤자야 라비

미국 뉴욕주 14526 웬필드 밀포드 크로싱 197

수 웨이즈

미국 뉴욕주 14618 로체스터 크랜顿 웨이 155

- (74) 대리인

제일특허법인

전체 청구항 수 : 총 4 항

심사관 : 김용권

(54) 발명의 명칭 이미지 센서와 그 제조 방법 및 이미지 센서를 포함하는 디지털 카메라

### (57) 요약

본 명세서에는 이미지 센서의 제조 방법이 개시되었으며, 본 방법은 각각이 광검출기를 구비하는 복수의 픽셀들을 제공하는 단계와, 복수의 광검출기를 사이에서 공유되는 증폭기를 제공하는 단계와, 각 광검출기와 관련된 전달 게이트를 제공하는 단계와, 복수의 광검출기를 사이에서 공유되는 전하-전압 변환 영역을 제공하는 단계와, 각 전달 게이트와 전하-전압 변환 영역 사이의 캐페시턴스를 결정하는 단계 및 하나 이상의 픽셀 내의 물리적인 구조를 변경함으로써 캐페시턴스가 실질적으로 동일하도록 조건시키는 단계를 포함한다.

**대 표 도** - 도3

## 특허청구의 범위

### 청구항 1

이미지 센서 제조 방법으로서,

- (a) 각각이 광검출기(photodetector)를 구비하는 복수의 픽셀들을 제공하는 단계와,

- (b) 상기 복수의 광검출기를 사이에서 공유되는 증폭기를 제공하는 단계와,

- (c) 각 광검출기와 관련된 전달 게이트(transfer gate)를 제공하는 단계와,

- (d) 상기 복수의 광검출기를 사이에서 공유되는 전하-전압 변환 영역(a charge-to-voltage conversion region)을 제공하는 단계와,

- (e) 각 전달 게이트와 상기 전하-전압 변환 영역 사이의 캐패시턴스를 결정하는 단계와,

- (f) 하나 이상의 픽셀 내의 레이아웃을 변경함으로써 상기 캐패시턴스가 실질적으로 동일해지도록 수정하는 단계

를 포함하되,

상기 (f) 단계는 하나 이상의 픽셀 내의 상호접속부를 변경하는 단계를 포함하고,

상기 상호접속부는 상기 각 전달 게이트와 상기 전하-전압 변환 영역 사이의 캐패시턴스를 제공하기 위해 형성되는

이미지 센서 제조 방법.

### 청구항 2

삭제

### 청구항 3

제 1 항에 있어서,

상기 (f) 단계는 하나 이상의 전하-전압 변환 영역의 배선의 배치를 변경하는 단계를 포함하는

이미지 센서 제조 방법.

### 청구항 4

제 1 항에 있어서,

상기 (f) 단계는 하나 이상의 전달 게이트의 배선의 배치를 변경하는 단계를 포함하는

이미지 센서 제조 방법.

### 청구항 5

제 1 항에 있어서,

상기 이미지 센서는 CMOS 이미지 센서인

이미지 센서 제조 방법.

### 청구항 6

삭제

### 청구항 7

삭제

### 청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

## 명세서

### 기술 분야

[0001] 본 발명은 전반적으로 CMOS 이미지 센서 분야에 관한 것이다. 보다 구체적으로, 본 발명은 고정 패턴 노이즈(fixed pattern noise)를 감소시키도록 각 픽셀에 대해 전달 게이트(transfer gate)와 플로팅 확산부(floating diffusion) 사이의 캐패시턴스를 매칭하는 것을 포함하는 증폭기를 공유하는 이미지 센서에 관한 것이다.

### 배경 기술

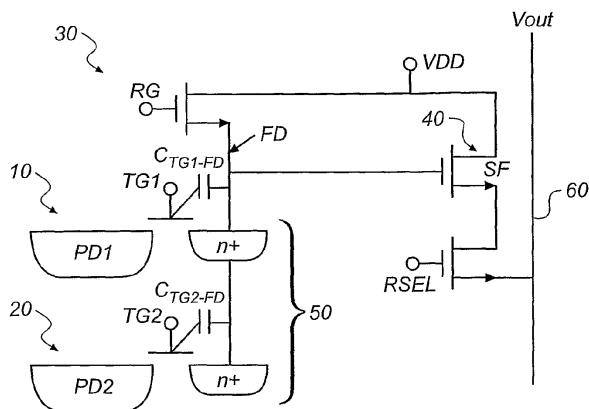

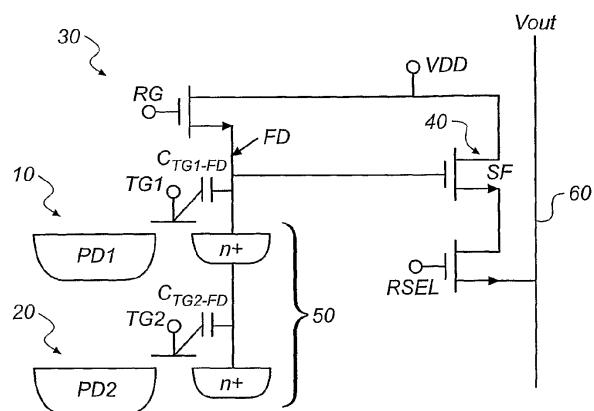

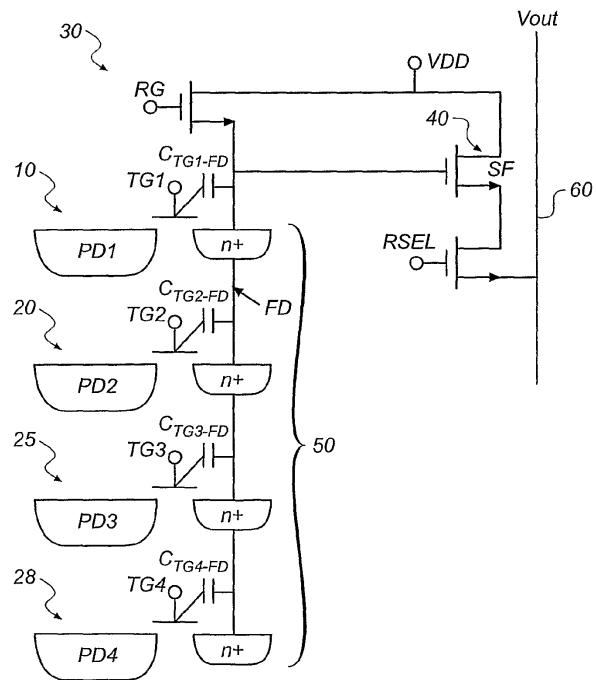

[0002] 도 1에서, 종래 기술의 공유 픽셀 개념도는 두 개의 광검출기(PD1 및 PD2), 두 개의 전달 게이트(TG1 및 TG2), 행 선택 트랜지스터(RSEL), 공통 플로팅 확산부 감지 노드(FD), 리셋 게이트(RG)를 구비한 리셋 트랜지스터 및 소스 폴로워 입력 트랜지스터(source follower input transistor)(SF)를 포함한다. 도 2의 종래 기술의 픽셀은 네 개의 광검출기 및 전달 게이트가 공통 구성요소를 공유한다는 점을 제외하고는 동일한 컨셉을 갖는다.

[0003] 이러한 설계는 TG와 FD 사이의 커플링 캐패시턴스를 형성하고 이것은 각각의 TG로부터 공통 FD로의 캐패시턴스에서의 미스매치와 관련된 고정 패턴 노이즈를 생성한다. 예를 들어, 도 1의 픽셀에서 TG1로부터 FD로의 캐패시턴스( $C_{TG1-FD}$ )가 TG2로부터 FD로의 캐패시턴스( $C_{TG2-FD}$ )와 다르다면, 전술된 캐패시턴스의 미스매치와 관련된 판독 중에 행 관련 홀-짝(odd-even) 또는 모듈로-2(modulo-2) 고정 패턴 노이즈가 존재할 것이다.

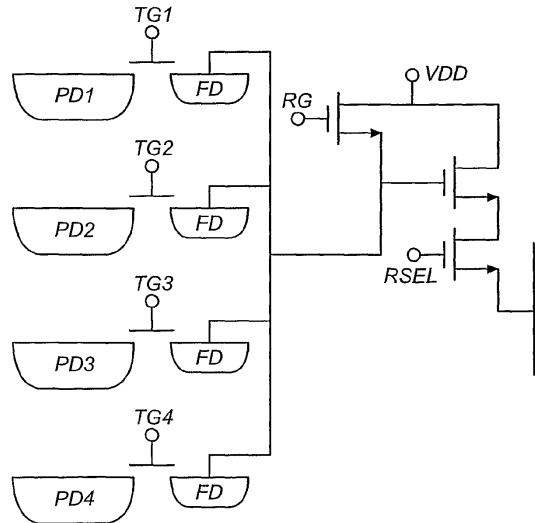

[0004] 도 2에 도시된 바와 같은 4-공유 픽셀에서 유사한 효과가 인지된다. 캐패시턴스( $C_{TG1-FD}$ ,  $C_{TG2-FD}$ ,  $C_{TG3-FD}$ ,  $C_{TG4-FD}$ )에서의 미스매치는 행 관련 모듈로-4 고정 패턴 노이즈(row correlated modulo-4 fixed pattern noise)로 이어진다. 고정 패턴 노이즈는 공간 관련성이 높기 때문에 이는 낮은 레벨에서 쉽게 검출되고 이미지 품질을 저하시킨다. TG-FD 캐패시턴스는 TG 오버랩 캐패시턴스 및 픽셀 내의 상호접속과 관련된 기생 캐패시턴스를 포함한다.

[0005] 본 발명은 공유된 증폭기 픽셀에 있어서 TG<sub>i</sub>로부터 FD로의 생성된 매칭 캐패시턴스에 대해 상세한 레이아웃 및 설계를 수행함으로써 고정 패턴 노이즈를 제거한다. 이는 TG 배선의 동일한 배치와 FD 접합 영역 및 상호접속부에 관련된 각 픽셀 내의 동일한 레벨의 상호접속 사용에 의해 실행될 수 있으나, 이것으로 제한되는 것은 아니다. 포스트 레이아웃 추출 툴(post layout extraction tools) 및 그외의 접적 회로 캐패시턴스 모델링 툴의 사용은 필요한 매칭 레벨을 설계하는 데에 사용될 수 있다. 일부 경우에서, 이것은 매칭된 TG-FD 커플링 캐패시턴스를 생성하도록 하나 또는 그 이상의 TG<sub>i</sub>-FD 영역에 대한 의도적인 추가 기생 캐패시턴스를 필요로 할 수 있다.

### 발명의 상세한 설명

[0006] 본 발명은 전술된 하나 또는 그 이상의 문제점을 극복하기 위한 것이다. 간략하게 요약하자면, 본 발명의 일 측면에 따르면, 본 발명은 (a) 각각 광검출기를 구비하는 복수의 픽셀을 제공하는 단계와, (b) 복수의 광검출기 사이에서 공유되는 증폭기를 제공하는 단계와, (c) 각 광검출기와 관련된 전달 게이트를 제공하는 단계와, (d)

복수의 광검출기 사이에서 공유되는 전하-전압 변환 영역을 제공하는 단계와, (e) 각 전달 게이트와 전하-전압 변환 영역 사이의 캐패시턴스를 결정하는 단계 및 (f) 하나 또는 그 이상의 픽셀 내의 물리적 구조를 변경함으로써 캐패시턴스가 실질적으로 동일하도록 변조시키는 단계를 포함하는 이미지 센서 제조 방법에 관한 것이다.

[0007] 본 발명의 이러한 측면, 목적, 특성 및 장점과 그 외의 측면, 목적, 특성 및 장점들은 하기의 바람직한 실시예의 상세한 설명과 첨부된 특허청구범위 및 첨부된 도면을 참조로 하여 보았을 때에 보다 명백하게 이해되고 인식될 것이다.

[0008] 본 발명은 공유된 증폭기 픽셀에 있어서 TG<sub>i</sub>로부터 FD로의 생성된 매칭 캐패시턴스에 대해 상세한 레이아웃 및 설계를 수행함으로써 고정 패턴 노이즈를 제거하는 장점을 갖는다. 이는 TG 배선의 동일한 배치와 FD 접합 영역 및 상호접속부에 관련된 각 픽셀 내의 동일한 레벨의 상호접속 사용에 의해 실행될 수 있으나, 이것으로 제한되는 것은 아니다. 포스트 레이아웃 추출 툴 및 그외의 집적 회로 캐패시턴스 모델링 툴의 사용은 필요한 매칭 레벨을 설계하는 데에 사용될 수 있다. 일부 경우에서, 이것은 매칭된 TG-FD 커플링 캐패시턴스를 생성하도록 하거나 또는 그 이상의 TG<sub>i</sub>-FD 영역에 대한 의도적인 추가 기생 캐패시턴스를 필요로 할 수 있다.

## 실시 예

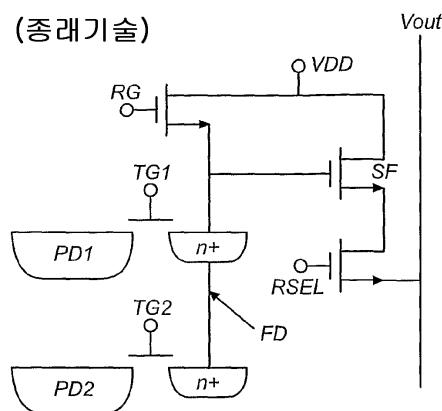

[0020] 도 3을 참조하면, 증폭기(40), 바람직하게는 소스 폴로워(source follower) SF를 공유하는 이미지 센서(30)의 두 개의 픽셀(10, 20)이 도시되었다(이미지 센서의 일부분만이 도시되었다). 바람직하게는 활성 픽셀 이미지 센서인 이미지 센서(30)는 2차원 픽셀 어레이를 포함하지만, 명확한 이해를 위해, 도 3은 2 공유 설계(2S)를 나타내도록 두 개의 픽셀을 도시하였고 도 4는 4 공유 설계(4S)를 나타낸다. 활성 픽셀은 픽셀 내에서 또는 픽셀과 관련하여 활성 회로 소자로서 사용되는 트랜지스터를 구비하는 픽셀을 지칭하며, CMOS는 상반되게 도핑된 (하나는 p-형 도핑되고 다른 하나는 n-형 도핑된) 두 개의 트랜지스터가 상보적인 방식으로 함께 배선된 "상보적 금속 산화물 실리콘(complimentary metal oxide silicon)"을 지칭한다. 활성 픽셀은 전형적으로 CMOS 설계를 사용하며 산업분야 내에서 상호교환가능하게 사용된다.

[0021] 도 3을 참조하면, 각 픽셀(10, 20)은 전하로 변환되는 입사광을 포착하기 위한 포토다이오드 PD1 및 PD2를 포함한다. 각 픽셀(10, 20)은 또한, 포토다이오드 PD1 및 PD2로부터 공유 플로팅 확산부(50) 및 이와 관련되고 공유되는 소스 폴로워 트랜지스터 SF(40)로 전하를 전달하는 전달 게이트 TG1 및 TG2를 포함한다. 리셋 게이트 RG는 플로팅 확산부(50)를 사전결정된 전하 레벨로 리셋하는 기능을 하며, 행 선택 게이트 RSEL은 판독될 특정 행을 선택한다.

[0022] 동작은 다음과 같은 방법으로 발생한다. 포토다이오드 PD1 및 PD2의 집적 후에, 행 선택 게이트 RSEL이 터온되고, 플로팅 확산부(50)가 리셋 게이트 RG를 펄스함으로써 리셋된다. 그 다음 이러한 리셋 신호가 판독된다. 전달 게이트 TG1은 펄스-온 되고 광검출기 PD1로부터의 신호 전하는 플로팅 확산부(50)로 전달되며, 신호 레벨은 신호가 증폭되는 증폭기 SF(40)를 통해 판독 버스(60)로 판독된다. 다음으로, 플로팅 확산부(50)는 리셋 게이트 RG를 다시 펄스-온 함으로써 리셋된다. 이 행에 대한 리셋 레벨이 판독된다. 다른 전달 게이트 TG2가 전하를 플로팅 확산부(50)로 전달하기 위해 펄스된다. 그 다음 이러한 신호 레벨은 신호가 증폭되는 증폭기 SF(40)를 통해 판독 버스(60)로 판독된다. 이러한 절차는 디바이스 상에 남아있는 행에 대해서 반복된다.

[0023] 플로팅 확산부(50)로의 각 전달 게이트 TG1 및 TG2의 캐패시턴스가 실질적으로 동일하도록 매칭됨을 인지하는 것은 중요하다. 이는 상징적으로 캐패시터 C<sub>TG1-FD</sub> 및 C<sub>TG2-FD</sub>로 표시된다. 캐패시턴스의 매칭은 전달 게이트 배선의 동일한 배치에 의해 실행될 수 있지만, 이것으로 제한되는 것은 아니다. 또한, 플로팅 확산부 접합 영역 및 상호접속부와 관련된 각 픽셀 내의 동일한 레벨의 상호접속부의 사용에 의해 실행될 수도 있다. 포스트 레이아웃 추출 툴 및 그외의 집적 회로 캐패시턴스 모델링 툴의 사용은 필요한 매칭 레벨을 설계하는 데에 사용될 수 있다. 일부 경우에서, 이것은 매칭된 전달 게이트-플로팅 확산부 커플링 캐패시턴스를 생성하도록 하거나 또는 그 이상의 전달 게이트-플로팅 확산부 영역에 대한 의도적인 추가 기생 캐패시턴스를 필요로 할 수 있다.

[0024] 도 4를 참조하면, 공통 구성요소를 공유하는 네 개의 픽셀들이 도시되었다. 이를 픽셀(10, 20, 25, 28)들은 두 개의 포토다이오드와 전달 게이트가 공통 구성요소를 공유하는 대신 네 개의 포토다이오드와 전달 게이트가 공통 구성요소를 공유한다는 점을 제외하면 도 3과 개념 및 동작에 있어서 동일하다. 플로팅 확산부로의 전달 게이트의 캐패시턴스는 전술된 동일한 캐패시턴스 매칭을 사용하여 매칭된다. 이러한 매칭된 캐패시턴스는 네 개

의 캐패시터  $C_{TG1-FD}$ ,  $C_{TG2-FD}$ ,  $C_{TG3-FD}$  및  $C_{TG4-FD}$ 에 의해 상징적으로 표시된다.

[0025] 도 5를 참조하면, 일반적인 소비자에게 알려진 전형적인 상업적 실시예를 나타내는 본 발명의 이미지 센서(30)를 포함하는 디지털 카메라(70)가 도시되었다.

### 도면의 간단한 설명

[0009] 도 1은 종래 기술의 증폭기를 공유하는 두 개의 픽셀의 개략도,

[0010] 도 2는 종래 기술의 증폭기를 공유하는 네 개의 픽셀의 개략도,

[0011] 도 3은 증폭기를 공유하는 두 개의 픽셀을 도시한 본 발명의 개략도,

[0012] 도 4는 증폭기를 공유하는 네 개의 픽셀을 도시한 본 발명의 개략도,

[0013] 도 5는 일반적인 소비자에게 익숙한 전형적인 상업적 실시예를 나타내는 디지털 카메라의 도면.

### 도면의 주요 부분에 대한 부호의 설명

[0015] 10 : 픽셀 20 : 픽셀

[0016] 25 : 픽셀 28 : 픽셀

[0017] 30 : 이미지 센서 40 : 증폭기 SF

[0018] 50 : 공유 플로팅 확산부 60 : 판독 버스

[0019] 70 : 디지털 카메라

## 도면

### 도면1

## 도면2

(종래기술)

## 도면3

## 도면4

## 도면5