(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-168899

(P2012-168899A)

(43) 公開日 平成24年9月6日(2012.9.6)

(51) Int.Cl.

G05F 1/56 (2006.01)

F 1

G05F 1/56

テーマコード(参考)

310U

5H430

審査請求 未請求 請求項の数 4 O L (全 8 頁)

(21) 出願番号

特願2011-31297 (P2011-31297)

(22) 出願日

平成23年2月16日 (2011.2.16)

(71) 出願人 000002325

セイコーインスツル株式会社

千葉県千葉市美浜区中瀬1丁目8番地

(74) 代理人 100154863

弁理士 久原 健太郎

(74) 代理人 100142837

弁理士 内野 則彰

(74) 代理人 100123685

弁理士 木村 信行

(72) 発明者 杉浦 正一

千葉県千葉市美浜区中瀬1丁目8番地 セイコーインスツル株式会社内

F ターム(参考) 5H430 BB01 BB09 BB11 EE04 EE17

EE18 FF02 FF13 HH03 LA01

LA06 LB02 LB06

(54) 【発明の名称】 ボルテージレギュレータ

## (57) 【要約】

【課題】オーバーシュート特性を改善した、ボルテージレギュレータの提供。

【解決手段】出力トランジスタと直列に、例えば定電流源などで構成した電流制限回路を設けて、出力過電流を制限する構成とした。また、出力端子に、例えばダイオードなどで構成した電圧制限回路を設けて、出力電圧を制限する構成とした。

【選択図】 図1

## 【特許請求の範囲】

## 【請求項 1】

出力トランジスタの出力する電圧を分圧した分圧電圧と基準電圧の差を増幅して出力し、前記出力トランジスタのゲートを制御する誤差増幅回路を有するボルテージレギュレータであって、

前記出力トランジスタと直列に接続された、前記出力トランジスタの出力電流を制限する電流制限回路を備えたことを特徴とするボルテージレギュレータ。

## 【請求項 2】

更に、出力端子に接続された、前記出力トランジスタの出力電圧を制限する電圧制限回路を備えたことを特徴とする請求項 1 に記載のボルテージレギュレータ。

10

## 【請求項 3】

前記電流制限回路は、定電流源を備えていることを特徴とする請求項 1 または 2 に記載のボルテージレギュレータ。

## 【請求項 4】

前記電圧制限回路は、1つ以上のダイオード素子で構成されることを特徴とする請求項 1 から 3 のいずれかに記載のボルテージレギュレータ。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、ボルテージレギュレータのオーバーシュート特性の改善に関する。

20

## 【背景技術】

## 【0002】

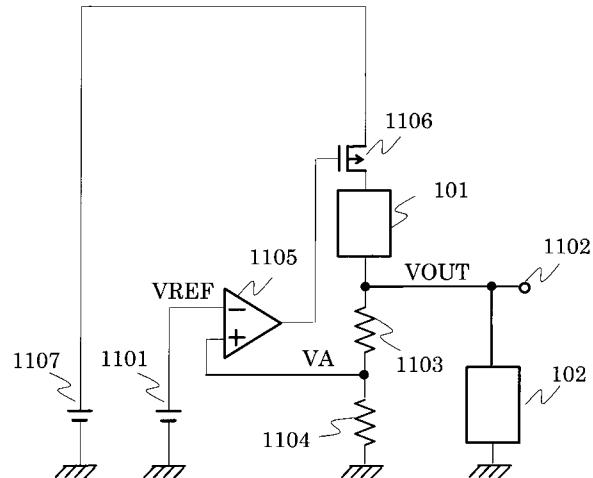

従来のボルテージレギュレータは、図 11 のブロック図に示すように、基準電圧回路 1101 と、分圧抵抗 1103 及び 1104 と、エラーアンプ 1105 と、出力トランジスタ 1106 と、から構成されている。

## 【0003】

基準電圧回路 1101 は、基準電圧 VREF を出力する。分圧抵抗 1103 及び 1104 は、ボルテージレギュレータの出力端子 1102 の出力電圧 VOUT を分圧し、分圧電圧 VA を出力する。エラーアンプ 1105 は、基準電圧 VREF と分圧電圧 VA との差電圧を増幅するし、出力電圧 VERR によって出力トランジスタ 1106 のゲートを制御する。出力トランジスタ 1106 は、電圧源 1107 の電源電圧 VDD と出力電圧 VERR によって、出力端子 1102 の出力電圧 VOUT を一定に保つ。ボルテージレギュレータは、電源電圧 VDD により動作する。

30

## 【0004】

ボルテージレギュレータは、以下のように動作して出力電圧 VOUT を一定に保つ（例えば、特許文献 1 参照）。

## 【0005】

出力電圧 VOUT が低くなると、エラーアンプ 1105 の出力電圧 VERR が低くなり、出力トランジスタ 1106 のゲート・ソース間電圧は大きくなる。従って、出力トランジスタ 1106 のON 抵抗が小さくなり、出力電圧 VOUT は高くなる。出力電圧 VOUT が高くなると、エラーアンプ 1105 の出力電圧 VERR が高くなり、出力トランジスタ 1106 のゲート・ソース間電圧は小さくなる。従って、出力トランジスタ 1106 のON 抵抗が大きくなり、出力電圧 VOUT は低くなる。

40

## 【先行技術文献】

## 【特許文献】

## 【0006】

【特許文献 1】特開平 4 - 195613 号公報（第 1 - 3 頁、第 2 図）

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】

50

しかし、従来のボルテージレギュレータでは、電源起動時や電源変動時など電源電圧  $V_{DD}$  がパルス的に変化したときや、ボルテージレギュレータの出力端子 1102 に接続された負荷が急激に変化したときに、出力電圧  $V_{OUT}$  にオーバーシュートが発生するといった問題点があった。

【課題を解決するための手段】

【0008】

本発明は、上記の様な問題点を解決するために考案されたものであり、オーバーシュート特性を改善したボルテージレギュレータを実現するものである。

【0009】

本発明のボルテージレギュレータは、基準電圧回路と、前記基準電圧回路の基準電圧に基づいた出力電圧を出力する出力端子と、前記出力電圧を分圧する分圧回路と、出力トランジスタと、前記分圧回路の出力と、前記基準電圧に基づいて、前記出力トランジスタの制御信号を出力するエラーアンプと、を有するボルテージレギュレータであって、前記ボルテージレギュレータは、更に、電圧制限回路と、電流制限回路と、を有することを特徴とするボルテージレギュレータ、とした。

10

【発明の効果】

【0010】

本発明のボルテージレギュレータによれば、出力電圧の過大なオーバーシュートを起こさず動作させることができとなり、オーバーシュート特性を改善したボルテージレギュレータを提供することが出来る。

20

【図面の簡単な説明】

【0011】

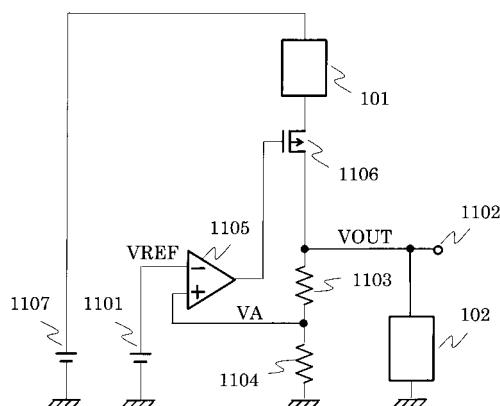

【図1】本実施形態のボルテージレギュレータを示すブロック図である。

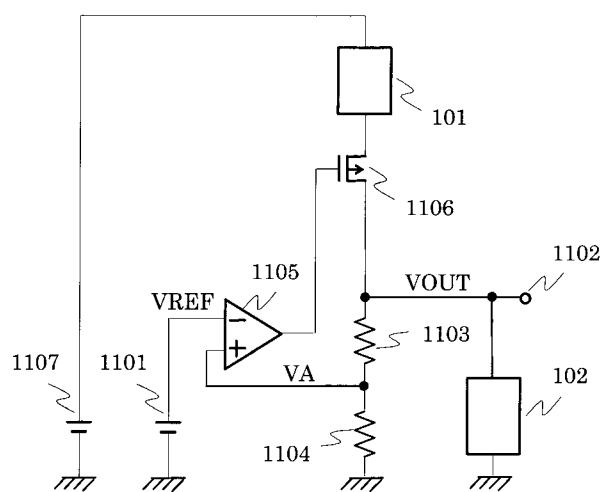

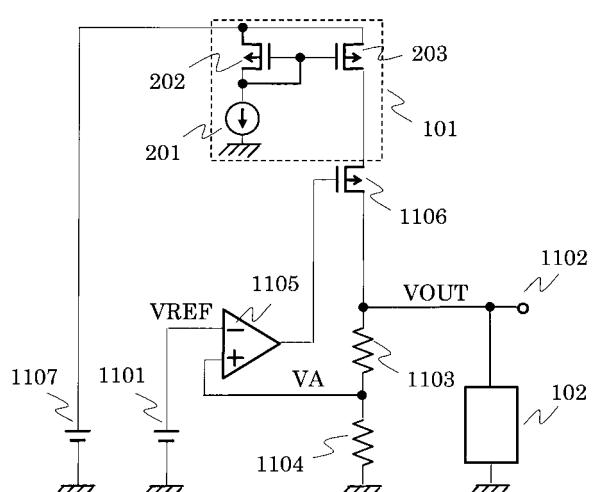

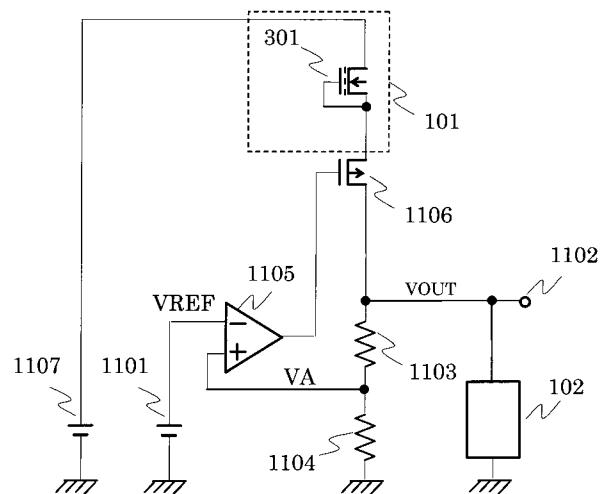

【図2】本実施形態のボルテージレギュレータの電流制限回路の一例を示すブロック図である。

【図3】本実施形態のボルテージレギュレータの電流制限回路の他の例を示すブロック図である。

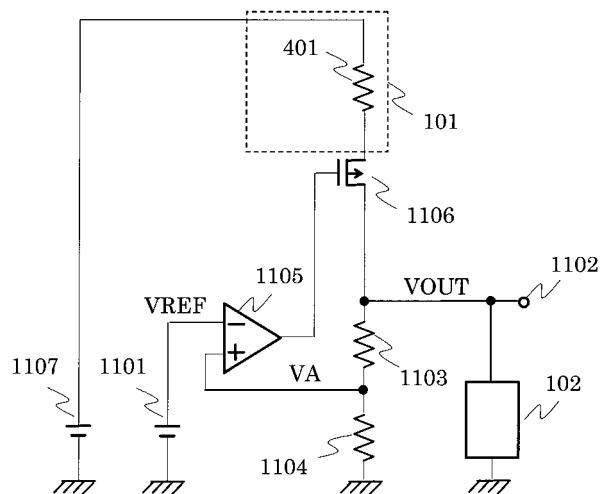

【図4】本実施形態のボルテージレギュレータの電流制限回路の他の例を示すブロック図である。

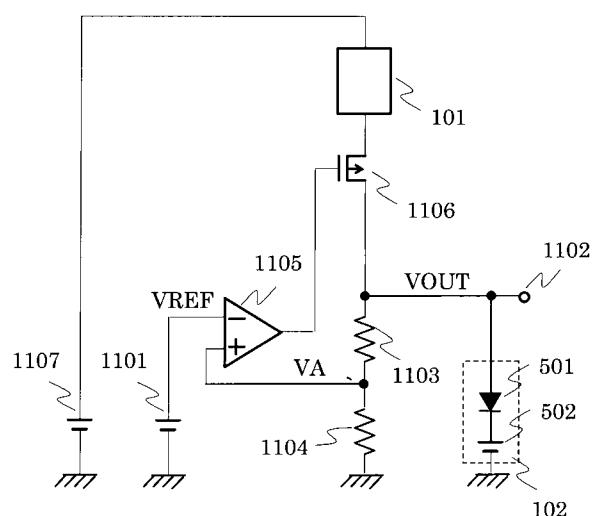

【図5】本実施形態のボルテージレギュレータの電圧制限回路の一例を示すブロック図である。

30

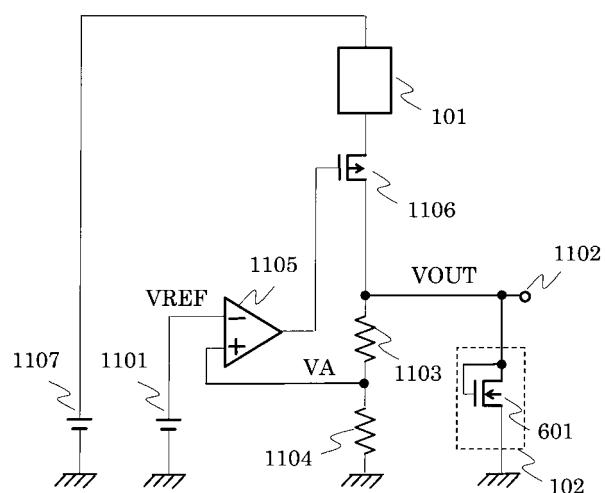

【図6】本実施形態のボルテージレギュレータの電圧制限回路の他の例を示すブロック図である。

【図7】他の実施形態のボルテージレギュレータを示すブロック図である。

【図8】他の本実施形態のボルテージレギュレータを示すブロック図である。

【図9】他の本実施形態のボルテージレギュレータを示すブロック図である。

【図10】他の実施形態のボルテージレギュレータを示すブロック図である。

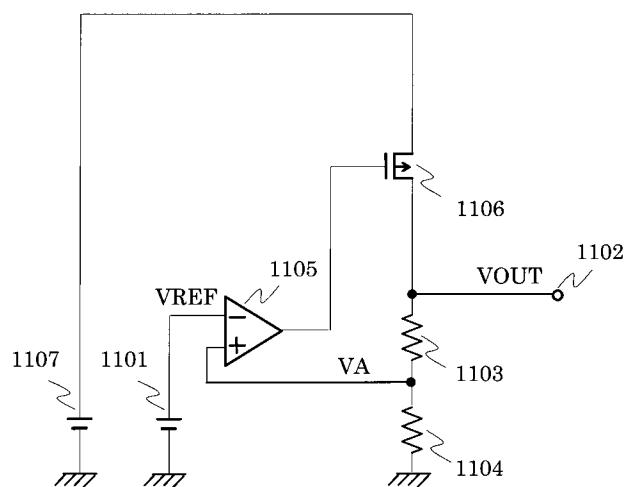

【図11】従来のボルテージレギュレータのブロック図である。

【発明を実施するための形態】

【0012】

図1は、本実施形態のボルテージレギュレータを示すブロック図である。

本実施形態のボルテージレギュレータは、基準電圧回路 1101 と、分圧抵抗 1103 及び 1104 と、エラーアンプ 1105 と、出力トランジスタ 1106 と、電流制限回路 101 と、電圧制限回路 102 と、を備えている。

【0013】

電流制限回路 101 は、電圧源 1107 と出力トランジスタ 1106 の間に設けられている。電圧制限回路 102 は、出力端子 1102 と接地端子の間に設けられている。

【0014】

電流制限回路 101 は、出力トランジスタ 1106 が流す電流の最大値を制限する機能を備えている。電流制限回路 101 は、例えば、図2に示す定電流源 201 とトランジス

40

50

タ202及び203からなるカレントミラー回路に依るものや、図3に示すデプレッショーン型のトランジスタ301に依るものや、図4に示す抵抗401に依るもので、構成される。

#### 【0015】

電圧制限回路102は、出力電圧VOUTが所望の電圧より高くなると、インピーダンスが小さくなる。電圧制限回路102は、例えば、図5に示す様なダイオード501と基準電圧回路502（基準電圧回路502は、ダイオードであっても良い）に依るものや、図6に示すような飽和接続されたトランジスタ601に依るもので、構成される。

#### 【0016】

以下に、本実施形態のボルテージレギュレータの動作について説明する。

電源起動時や電源変動時などの電源電圧VDDがパルス的に変化したとき、またはボルテージレギュレータの出力端子1102に接続された負荷が急激に変化したときに、電圧カッピングの影響や、出力トランジスタ1106の負荷への電流供給能力を超えることなどで、出力電圧VOUTが低下する。出力電圧VOUTを分圧する分圧電圧VAも低下するので、エラーアンプ1105の出力電圧VERRが低くなる。従って、出力トランジスタ1106は、ON抵抗が小さくなるので、瞬時に大きな電流を流そうとする。

#### 【0017】

このとき、出力トランジスタ1106と電圧源1107の間に設けられた電流制限回路101に依って、出力トランジスタ1106の駆動電流は制限される。例えば、図2の電流制限回路101の場合は、電流源201が流す電流を制限する。

#### 【0018】

また、出力トランジスタ1106の駆動電流が増加すると、出力電圧VOUTも高くなる。このとき、出力端子1102に設けられた電圧制限回路102によって、出力電圧VOUTは制限される。例えば、図5の電圧制限回路102の場合は、出力端子1102と接地端子の間に順バイアス接続したダイオード501によって、出力端子1102の電圧が大きくなるとインピーダンスが小さくなる。更に、出力トランジスタ1106の駆動電流はダイオード501によっても制限されるので、出力電圧VOUTは過大なオーバーシュートを起こさず動作させることが可能となる。

#### 【0019】

従って、本実施形態のボルテージレギュレータは、出力電圧の過大なオーバーシュートを起こさず動作させることが可能となり、オーバーシュート特性を改善したボルテージレギュレータを提供することが出来る。

#### 【0020】

本実施形態のボルテージレギュレータでは、分圧抵抗1103、分圧抵抗1104によって、出力電圧VOUTを分圧するものとして説明したが、これらの抵抗値は、ゼロまたは過大な値として構成しても、所望の分圧比が得られれば、同様の効果が得られる。

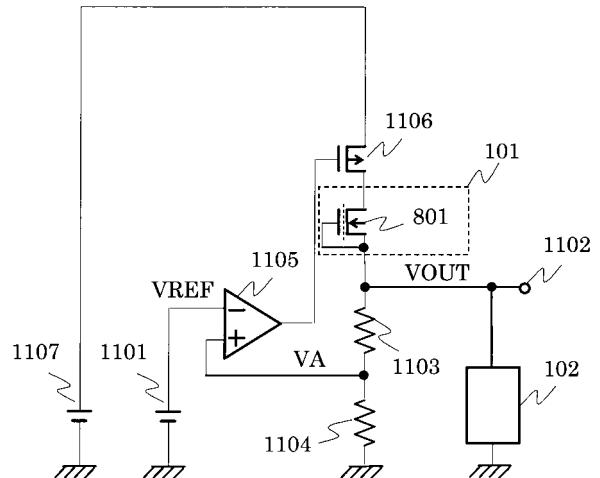

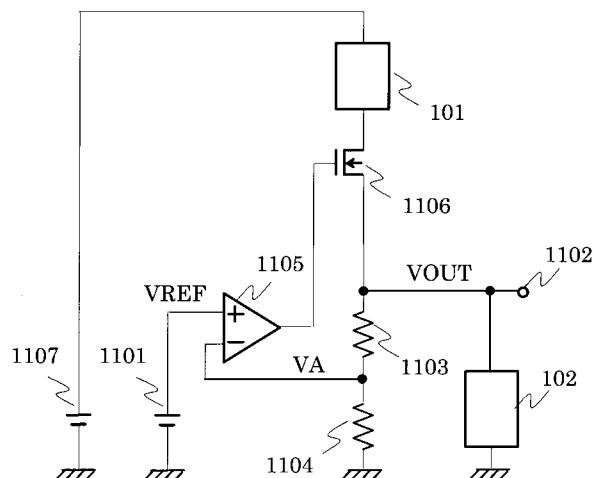

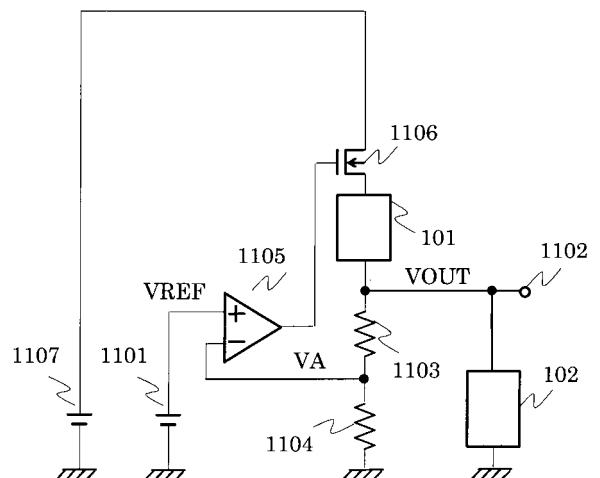

#### 【0021】

本実施形態のボルテージレギュレータでは、電流制限回路101が出力トランジスタ1106にとってハイサイドに設けられているとして説明したが、図7及び図8に示すようにロウサイドに設けられても同様の効果が得られる。図8は、電流制限回路101をデプレッショーン型トランジスタ801で構成した例を示したものである。図8において、出力電圧VOUTが高くなるほど、デプレッショーン型トランジスタ801はバックゲート電圧降下により閾値電圧が高くなり、電流をより制限するように動作する。従って、ボルテージレギュレータが安定動作しているときは、出力トランジスタ1106の駆動電流を大きくし、出力電圧VOUTが高くなったり、電流をより制限することが出来るといった、更なるメリットが得られる。

#### 【0022】

本実施形態のボルテージレギュレータでは、電流制限回路101が、図2、図3、図4、図7に示すようなものとして説明したが、同様の機能を有することが可能な、その他の構成でも同様な効果が得られる。

10

20

30

40

50

## 【0023】

本実施形態のボルテージレギュレータでは、電圧制限回路 102 が、図 5、図 6 に示す様なものとして説明したが、これらを構成するダイオードまたはトランジスタは、出力電圧  $V_{OUT}$  によって、適切に直列させても良い。また、同様の機能を有することが可能な、その他の構成でも同様な効果が得られる。例えば、ダイオードの代わりに、ダイオード接続させたトランジスタを設けても良い。

## 【0024】

本実施形態のボルテージレギュレータでは、出力トランジスタが P 型であるとして説明したが、N 型であるとしても同様な効果が得られる。この場合のブロック図の例を図 9 及び図 10 に示す。出力トランジスタは、エンハンスメント型であるか、デプレッション型であるか、その形態は限定されない。

10

## 【符号の説明】

## 【0025】

- 101 電流制限回路

- 102 電圧制限回路

- 201 電流源

- 502、1101 基準電圧回路

- 1105 エラーアンプ

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 11】