(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5352122号

(P5352122)

(45) 発行日 平成25年11月27日(2013.11.27)

(24) 登録日 平成25年8月30日(2013.8.30)

|               |                                |

|---------------|--------------------------------|

| (51) Int.Cl.  | F 1                            |

| HO 1 L 21/02  | (2006.01) HO 1 L 27/12 B       |

| HO 1 L 27/12  | (2006.01) HO 1 L 29/78 6 2 7 D |

| HO 1 L 21/336 | (2006.01) HO 1 L 29/78 6 2 7 G |

| HO 1 L 29/786 | (2006.01) HO 1 L 29/78 6 1 2 B |

|               | HO 1 L 29/78 6 2 6 C           |

請求項の数 1 (全 30 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2008-126115 (P2008-126115)  |

| (22) 出願日     | 平成20年5月13日 (2008.5.13)        |

| (65) 公開番号    | 特開2008-311636 (P2008-311636A) |

| (43) 公開日     | 平成20年12月25日 (2008.12.25)      |

| 審査請求日        | 平成23年4月18日 (2011.4.18)        |

| (31) 優先権主張番号 | 特願2007-131590 (P2007-131590)  |

| (32) 優先日     | 平成19年5月17日 (2007.5.17)        |

| (33) 優先権主張国  | 日本国 (JP)                      |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 本田 達也<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| 審査官       | 綿引 隆                                           |

最終頁に続く

(54) 【発明の名称】半導体装置の作製方法

## (57) 【特許請求の範囲】

## 【請求項 1】

所定の深さにイオンドーピング層を有する単結晶半導体基板と、前記単結晶半導体基板の上方の第1の絶縁層と、を有する構造を用意する第1の工程と、

ベース基板と、前記ベース基板の一部の上方の第2の絶縁層と、前記第2の絶縁層の上方の非単結晶半導体層と、を有する構造を用意する第2の工程と、

前記ベース基板の前記第2の絶縁層が形成されていない領域に前記第1の絶縁層を接合させる第3の工程と、

前記ベース基板の上方に前記第1の絶縁層を残存させ、且つ、前記第1の絶縁層の上方に単結晶半導体層を形成する第4の工程と、を有し、

前記第4の工程において、前記単結晶半導体基板の一部が前記イオンドーピング層において分離することによって、前記単結晶半導体層が形成され、

前記第1の絶縁層は、前記単結晶半導体層と接する第1の酸化窒化シリコン層を有し、前記第1の絶縁層は、前記第1の酸化窒化シリコン層と接する窒化酸化シリコン層を有し、

前記第2の絶縁層は、前記非単結晶半導体層と接する第2の酸化窒化シリコン層を有することを特徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

## 【技術分野】

【0001】

本発明は、半導体装置の作製方法、表示装置の作製方法、半導体装置、表示装置及び電子機器に関する。

【背景技術】

【0002】

近年、液晶表示装置、エレクトロルミネッセンス(EL)表示装置などのフラットパネルディスプレイが注目を集めている。

【0003】

フラットパネルディスプレイの駆動方式としては、パッシブマトリクス方式とアクティブマトリクス方式がある。アクティブマトリクス方式は、パッシブマトリクス方式と比較して、低消費電力化、高精細化、基板の大型化等が可能になるというメリットを有する。

10

【0004】

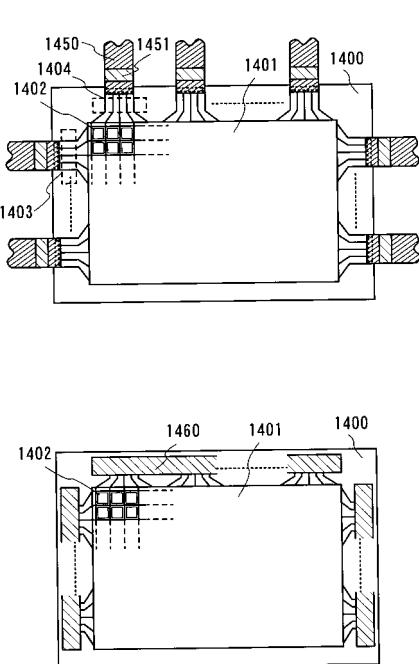

ここで、アクティブマトリクス方式の表示装置の構成例を、図14を用いて簡単に説明する。図14(A)は、駆動回路をTAB(Tape Automated Bonding)方式を用いて設ける構成の一例を示している。

【0005】

図14(A)では、絶縁表面を有する基板1400上に、画素1402をマトリクス状に配列させた画素部1401が形成されている。画素1402は、走査線側入力端子1403から延在する走査線と、信号線側入力端子1404から延在する信号線とが交差することで、マトリクス状に形成される。画素部1401の画素それぞれには、スイッチング素子とそれに接続する画素電極層が備えられている。スイッチング素子の代表的な一例はTFT(Thin Film Transistor)であり、TFTのゲート電極層側が走査線と、ソース若しくはドレイン側が信号線と接続される。また、駆動回路を構成するIC1451は、FPC(Flexible Printed Circuit)1450と接続されている。

20

【0006】

図14(A)のように、外部に駆動回路を設ける構成においては、駆動回路として、単結晶シリコンを用いたIC(集積回路)を用いることが可能であるため、駆動回路の速度に起因した問題は生じない。しかしながら、このようにICを設ける場合には、表示部とICを別々に用意する必要があること、表示部とICとの接続工程が必要であること等から、十分にコストを低減することができなかった。また、ICの分だけ、表示装置のサイズ(特に厚み)が大きくなってしまうという問題があった。

30

【0007】

そこで、上記問題点を解消するという観点から、画素部と駆動回路部を一体に形成する方法が用いられるようになった(例えば、特許文献1参照)。図14(B)は、画素部と駆動回路部を一体に形成した場合の構成の一例である。

【特許文献1】特開平8-6053号公報

【発明の開示】

【発明が解決しようとする課題】

【0008】

40

図14(B)に示す場合には、駆動回路1460の半導体層としては、画素部と同様に非晶質シリコンや微結晶シリコン、多結晶シリコンなどの非単結晶シリコンが用いられている。しかしながら、非晶質シリコンはもとより、微結晶シリコンや多結晶シリコンを用いる場合であっても、その特性は単結晶シリコンを用いる場合には遠く及ばないという問題が存在する。特に、従来の駆動回路一体型の表示装置に用いられる半導体層では、必要かつ十分な特性(移動度、S値等)を有するTFTの作製が困難であり、駆動回路という高速動作が求められる半導体装置を作製するに当たって大きな問題となっている。

【0009】

上記問題点に鑑み、本発明は、作製コストを低減しつつ、高速動作が可能な回路を設けた半導体装置の作製方法を提供することを課題の一とする。また、当該作製方法を用いた

50

半導体装置、特に、表示装置を提供することを課題の一とする。

【課題を解決するための手段】

【0010】

本発明では、駆動回路部と画素部を、異なる性質の半導体層で形成する。具体的には、駆動回路部は単結晶半導体層で形成し、画素部は非単結晶半導体層で形成する。これにより、作製のコストを低減しつつ、必要かつ十分な特性を有する駆動回路を作製することができる。

【0011】

本発明の半導体装置の作製方法の一は、単結晶半導体基板の表面から所定の深さにイオンドーピング層を形成し、単結晶半導体基板上に第1の絶縁層を形成し、絶縁性基板上の一部に第2の絶縁層を形成し、第2の絶縁層上に非単結晶半導体層を形成し、第1の絶縁層を介して、単結晶半導体基板を絶縁性基板の第2の絶縁層が形成されていない領域に接合させ、単結晶半導体基板を、イオンドーピング層において分離させる（イオンドーピング層を剥離面（分離面、劈開面と呼んでも良い）として絶縁性基板から剥離させる）ことにより、絶縁性基板上に単結晶半導体層を形成することを特徴としている。

10

【0012】

本発明の半導体装置の作製方法の他の一は、単結晶半導体基板の表面から所定の深さにイオンドーピング層を形成し、単結晶半導体基板上に第1の絶縁層を形成し、絶縁性基板上の一部に第2の絶縁層を形成し、第2の絶縁層上に非単結晶半導体層を形成し、第1の絶縁層を介して、単結晶半導体基板を絶縁性基板の第2の絶縁層が形成されていない領域に接合させ、単結晶半導体基板を、イオンドーピング層において分離させることにより、絶縁性基板上に単結晶半導体層を形成し、絶縁性基板上の単結晶半導体層を用いて高速動作が要求される回路を形成し、絶縁性基板上の非単結晶半導体層を用いて高速動作が要求されない回路を形成することを特徴としている。ここで高速動作が要求される回路とは、一定以上の周波数での駆動が求められる回路を言うものとする。一例としては、1MHz以上の周波数での動作が求められ回路を言う。用いる半導体層を求められる周波数で規定するのは、回路に用いられるスイッチング素子の動作可能な周波数が半導体材料に大きく依存しているためである。キャリア移動度が大きい単結晶半導体材料（単結晶シリコンにおける電子の場合で $500 \text{ cm}^2 / \text{V} \cdot \text{s}$ 程度）を用いたスイッチング素子は、信号の伝達速度が大きく高周波数動作に向いている。一方で、キャリア移動度の小さい非単結晶半導体材料（非晶質シリコンにおける電子の場合で $0.6 \text{ cm}^2 / \text{V} \cdot \text{s}$ 程度）を用いたスイッチング素子は、信号の伝達速度も小さく高周波数動作には向かない。なお、スイッチング素子の動作可能な周波数の上限は、材料以外のパラメータ（例えばチャネル長等）にも依存するため、一律に、ある周波数以上を高速動作と規定することは困難である。ここでは、表示装置における駆動回路に要求される性能を一応の基準として、周波数の基準を示した。

20

【0013】

本発明の表示装置の作製方法の一は、単結晶半導体基板の表面から所定の深さにイオンドーピング層を形成し、単結晶半導体基板上に第1の絶縁層を形成し、絶縁性基板上の一部に第2の絶縁層を形成し、第2の絶縁層上に非単結晶半導体層を形成し、第1の絶縁層を介して、単結晶半導体基板を絶縁性基板の第2の絶縁層が形成されていない領域に接合させ、単結晶半導体基板を、イオンドーピング層において分離させることにより、絶縁性基板上に単結晶半導体層を形成し、絶縁性基板上の単結晶半導体層を用いて駆動回路を形成し、絶縁性基板上の非単結晶半導体層を用いて表示部（画素部）の回路を形成することを特徴としている。

30

【0014】

上記において、第1の絶縁層又は第2の絶縁層は、二層以上の積層構造で形成されても良い。また、第1の絶縁層の単結晶半導体層と接する部分と、第2の絶縁層の非単結晶半導体層と接する部分とは、同じ材料を用いて形成されるようにしても良い。特に、第1の絶縁層の単結晶半導体層と接する部分と、第2の絶縁層の非単結晶半導体層と接する

40

50

部分とは、酸化窒化シリコン層及び窒化酸化シリコン層の積層構造にて形成されることが好ましい。ここで、単結晶半導体層及び非単結晶半導体層と接するのは酸化窒化シリコン層である。また、第1の絶縁層の絶縁性基板と接する部分は、酸化シリコン層にて形成されることが好ましい。中でも、有機シランを用いて化学気相成長法により酸化シリコン層を形成すると良い。

#### 【0015】

また、上記において、非単結晶半導体層の膜厚より、単結晶半導体層の膜厚を小さく形成することが好ましい。また、単結晶半導体層の膜厚と第1の絶縁層の膜厚との和が、非単結晶半導体層の膜厚と第2の絶縁層の膜厚との和に等しくなるように形成することが好ましい。ここで、等しいとは、厳密に等しいことに限らない。例えば、±5パーセント程度の相違であれば、等しいとみなすことができる。

10

#### 【0016】

また、上記において、絶縁性基板上に単結晶半導体層を形成した後にレーザー光を照射し、単結晶半導体層及び非単結晶半導体層の特性を向上させることが好ましい。なお、単結晶半導体層及び非単結晶半導体層は、絶縁性基板の一表面上に形成しても良いし、絶縁性基板の異なる表面に形成しても良い。なお、上記においては、イオンドーピング層を形成した後に絶縁層を形成する構成としているが、絶縁層を形成した後にイオンドーピング層を形成する構成としても良い。

#### 【0017】

本発明の半導体装置の一は、絶縁性基板上の第1の絶縁層及び第2の絶縁層と、第1の絶縁層上の単結晶半導体層と、第2の絶縁層上の非単結晶半導体層と、を有することを特徴としている。

20

#### 【0018】

本発明の半導体装置の他の一は、絶縁性基板上の第1の絶縁層及び第2の絶縁層と、第1の絶縁層上の単結晶半導体層と、第2の絶縁層上の非単結晶半導体層と、を有し、単結晶半導体層は高速動作が要求される回路を形成するために用いられ、非単結晶半導体層は、高速動作が要求されない回路を形成するために用いられたことを特徴としている。

#### 【0019】

本発明の表示装置の一は、絶縁性基板上の第1の絶縁層及び第2の絶縁層と、第1の絶縁層上の単結晶半導体層と、第2の絶縁層上の非単結晶半導体層と、を有し、単結晶半導体層は駆動回路を形成するために用いられ、非単結晶半導体層は、表示部（画素部）の回路を形成するために用いられたことを特徴としている。

30

#### 【0020】

上記において、第1の絶縁層又は第2の絶縁層は、二層以上の積層構造であっても良い。また、第1の絶縁層の単結晶半導体層と接する部分と、第2の絶縁層の非単結晶半導体層と接する部分とは、同じ材料であっても良い。特に、第1の絶縁層の単結晶半導体層と接する部分と、第2の絶縁層の非単結晶半導体層と接する部分とは、酸化窒化シリコン層及び窒化酸化シリコン層の積層構造であることが好ましい。ここで、単結晶半導体層及び非単結晶半導体層と接するのは酸化窒化シリコン層である。また、第1の絶縁層の、絶縁性基板と接する部分は、酸化シリコン層であることが好ましい。中でも、有機シランを用いて化学気相成長法により形成された酸化シリコンであると、なお良い。

40

#### 【0021】

また、上記において、非単結晶半導体層の膜厚より、単結晶半導体層の膜厚が小さい構成であると好ましい。また、単結晶半導体層の膜厚と第1の絶縁層の膜厚との和が、非単結晶半導体層の膜厚と第2の絶縁層の膜厚との和に等しい構成であると好ましい。ここで、等しいとは、厳密に等しいことに限らない。例えば、±5パーセント程度の相違であれば、等しいとみなすことができる。

#### 【0022】

さらに、上記の半導体装置及び表示装置を用いて様々な電子機器を提供することができる。

50

## 【発明の効果】

## 【0023】

本発明の作製方法を用いることにより、必要かつ十分な特性を有する駆動回路を作製することができる。これにより、完全なモノリシック型の半導体装置を作製することができるため、作製コストを低減することができる。また、外部にICを接続することに起因して生じる厚みを低減することができる。また、額縁部分の面積を低減した半導体装置を作製することができる。さらに、本発明を用いることにより、ガラス基板等の耐熱性が低い基板を用いて高性能な半導体装置を作製することができる。

## 【0024】

なお、高精細の表示装置を作製する場合、画素の間隔が小さくなるため、画素部の容量が小さくなる。つまり、画素部のスイッチングトランジスタに要求される特性は軽減されることになる。また、大型の表示装置を作製する場合、画素ピッチが大きくなるため、トランジスタのサイズを大きくすることができます。この場合にも、画素部のスイッチングトランジスタに要求される特性は軽減される。したがって、画素部のスイッチングトランジスタを非晶質半導体若しくは非単結晶半導体で形成したとしても十分な性能を有する。

10

## 【0025】

これに対して、大型・高精細の表示装置では、駆動回路と画素とを結ぶ配線が長くなるため、配線抵抗は増加する。つまり、駆動回路にかかる電流が増大し、負荷が大きくなる。また、画素数の増加に伴い、処理すべきデータ数が増加し、駆動回路の負荷が大きくなる。つまり、駆動回路部のトランジスタには高い性能が要求されることになる。

20

## 【0026】

このように、非単結晶半導体層と単結晶半導体層を合わせて用いることにより要求される特性を完全に満たすことができるという点で、特に、大型・高精細の表示装置において、本発明の効果は大きい。

## 【発明を実施するための最良の形態】

## 【0027】

本発明の実施の形態について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じものを指す符号は異なる図面間で共通して用いることとする。

30

## 【0028】

## (実施の形態1)

本実施の形態では、本発明に用いる半導体基板の作製方法を、図1乃至図7を用いて以下に説明する。なお、本実施の形態に係る半導体基板は、その一部を、単結晶半導体基板から、異種基板（以下、「ベース基板」という）に転写して形成するものである。

## 【0029】

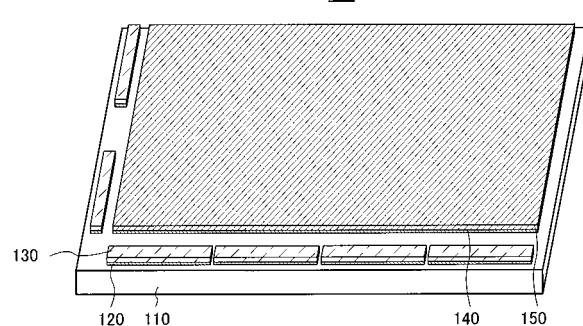

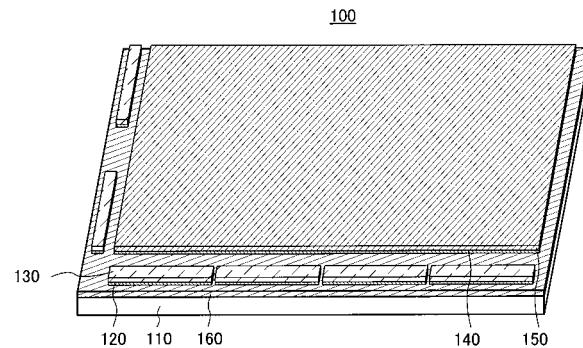

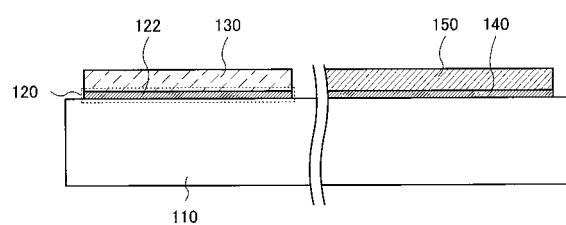

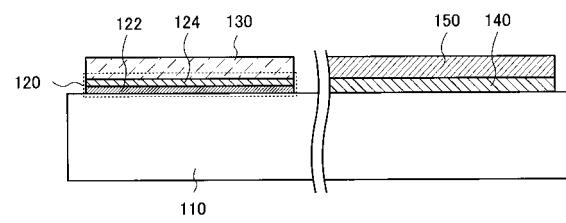

図1に、本発明に用いる半導体基板の斜視図を示す。また、図2及び図3に、本発明に用いる半導体基板の断面図を示す。

## 【0030】

40

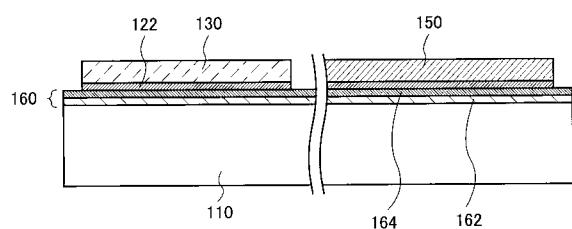

図1(A)、図2(A)、及び図2(B)において、半導体基板100は、ベース基板110の一表面上に、絶縁層120と単結晶半導体層130とが順次積層された積層体が複数設けられ、また、絶縁層140と非単結晶半導体層150とが順次積層して設けられた構成を有する。単結晶半導体層130及び非単結晶半導体層150は、絶縁層120及び絶縁層140を介してベース基板110上に設けられている。つまり、複数の単結晶半導体層130及び非単結晶半導体層150が1枚のベース基板110上に設けられることにより、1枚の半導体基板100が形成されている。なお、図1乃至図3では、便宜上、1枚の半導体基板100から一の表示装置を作製する場合の構成についてのみ示すが、本発明はこれに限定して解釈されるものではない。

## 【0031】

50

単結晶半導体層 130 として、代表的には単結晶シリコンが適用される。その他、単結晶ゲルマニウムや、ガリウムヒ素、インジウムリンなどの化合物半導体（単結晶）を適用することもできる。

【0032】

単結晶半導体層 130 の形状は特に限定されないが、矩形状（正方形を含む）とすると加工が容易になり、ベース基板 110 にも集積度良く貼り合わせることができ好ましい。

【0033】

ベース基板 110 には絶縁表面を有する基板または絶縁基板を用いる。具体的には、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイヤ基板等を用いることができる。好ましくはガラス基板を用いるのがよく、例えば第 6 世代（1500 mm × 1850 mm）、第 7 世代（1870 mm × 2200 mm）、第 8 世代（2200 mm × 2400 mm）といわれる大面積のマザーガラス基板を用いることができる。大面積のマザーガラス基板をベース基板 110 として用いることで、半導体基板の大面積化が実現できる。本実施の形態においては、1 枚のベース基板から一の表示装置を作製する場合について示すが、1 枚のベース基板から複数の表示装置を作製する場合（多面取りの場合）には、単結晶半導体層 130 及び非単結晶半導体層 150 の大きさを適宜調節して作製すれば良い。

【0034】

ベース基板 110 と単結晶半導体層 130 の間には、絶縁層 120 が設けられている。絶縁層 120 は単層構造としても積層構造としてもよいが、ベース基板 110 と接合する面（以下、「接合面」ともいう）は、平滑面を有し、親水性表面となるようにする。

【0035】

図 2 (A) は絶縁層 120 として接合層 122 を形成する例を示している。平滑面を有し親水性表面を形成できる接合層 122 としては、酸化シリコン層が適している。特に、有機シランを用いて化学気相成長法により作製される酸化シリコン層が好ましい。有機シランとしては、テトラエトキシシラン（略称；TEOS：化学式  $\text{Si}(\text{OC}_2\text{H}_5)_4$ ）、テトラメチルシラン（ $\text{Si}(\text{CH}_3)_4$ ）、トリメチルシラン（ $(\text{CH}_3)_3\text{SiH}$ ）、テトラメチルシクロテトラシロキサン（TMCTS）、オクタメチルシクロテトラシロキサン（OMCTS）、ヘキサメチルジシラザン（HMDS）、トリエトキシシラン（ $\text{SiH}(\text{OC}_2\text{H}_5)_3$ ）、トリスジメチルアミノシラン（ $\text{SiH}(\text{N}(\text{CH}_3)_2)_3$ ）等のシリコン含有化合物を用いることができる。

【0036】

上記平滑面を有し親水性表面を形成する接合層 122 は、膜厚 5 nm 乃至 500 nm の範囲で設けることが好ましい。接合層 122 の膜厚を上記範囲内とすることで、被成膜表面の表面荒れを平滑化すると共に、当該膜の成長表面の平滑性を確保することができる。また、接合層 122 と接合する基板（図 2 (A) ではベース基板 110）との貼り合わせの不良を低減することができる。なお、ベース基板 110 にも、接合層 122 と同様の酸化シリコン層を設けてもよい。絶縁表面を有する基板若しくは絶縁基板であるベース基板 110 に単結晶半導体層 130 を接合するに際し、接合を形成する面の一方若しくは双方に、好ましくは有機シランを原材料として成膜した酸化シリコン層でなる接合層を設けることで強固な接合を形成することができる。

【0037】

図 2 (B) には絶縁層 120 を積層構造とする例を示している。具体的には、絶縁層 120 として接合層 122 及び窒素含有絶縁層 124 の積層構造を形成する例を示している。なお、ベース基板 110 との接合面には接合層 122 が形成されるようにするため、単結晶半導体層 130 と接合層 122 との間に窒素含有絶縁層 124 が設けられた構成とする。窒素含有絶縁層 124 は、窒化シリコン層、窒化酸化シリコン層（ $\text{SiN}_x\text{O}_y$  :  $x > y$ ）又は酸化窒化シリコン層（ $\text{SiO}_x\text{N}_y$  :  $x > y$ ）などを用いて単層構造又は積層構造で形成する。例えば、単結晶半導体層 130 側から酸化窒化シリコン層、窒化酸化シリコン層

10

20

30

40

50

リコン層を積層して窒素含有絶縁層 124 とすることができます。

【0038】

ここで、単結晶半導体層 130 に接するように窒化酸化シリコン層を形成した場合、応力により単結晶半導体層の特性が低下してしまうという問題がある。また、可動イオンや水分等の拡散を防ぐという観点からは、窒化酸化シリコン層を設けることが好ましい。つまり、上記の例の如く、単結晶半導体層 130 側から酸化窒化シリコン層、窒化酸化シリコン層を積層して窒素含有絶縁層 124 とすることが好ましい。なお、窒素含有絶縁層 124 は、可動イオンや水分等の不純物が単結晶半導体層 130 に拡散することを防ぐために設けられており、接合層 122 はベース基板 110 と接合を形成するために設けられているという点で、その目的は異なっている。また、上記の構成はあくまでも一例であって、単結晶半導体層 130 と窒化酸化シリコン層とを接して設ける構成を排除するものではない。10

【0039】

なお、非単結晶半導体層 150 の下部に設けられた絶縁層 140 は、単結晶半導体層 130 の下部に設けられた絶縁層 120 と同じ構成とすることには限定されないが、図 2 (A) 及び図 2 (B) に示すように、少なくとも非単結晶半導体層 150 と接する材料と単結晶半導体層 130 と接する材料とを同じにすることが好ましい。接する材料と同じにすることで、後のパターニングの際の非単結晶半導体層 150 及び単結晶半導体層 130 のエッティング特性をそろえることができる。

【0040】

なお、酸化窒化シリコン層とは、その組成として、窒素よりも酸素の含有量が多いものを示し、例えば、酸素が 50 原子% 以上 70 原子% 以下、窒素が 0.5 原子% 以上 1.5 原子% 以下、珪素が 2.5 原子% 以上 3.5 原子% 以下、水素が 0.1 原子% 以上 1.0 原子% 以下の範囲で含まれるものという。また、窒化酸化シリコン層とは、その組成として、酸素よりも窒素の含有量が多いものを示し、例えば、酸素が 5 原子% 以上 3.0 原子% 以下、窒素が 2.0 原子% 以上 5.5 原子% 以下、珪素が 2.5 原子% 以上 3.5 原子% 以下、水素が 1.0 原子% 以上 3.0 原子% 以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法 (RBS : Rutherford Backscattering Spectrometry) や、水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が 100 原子% を超えない値をとる。20

【0041】

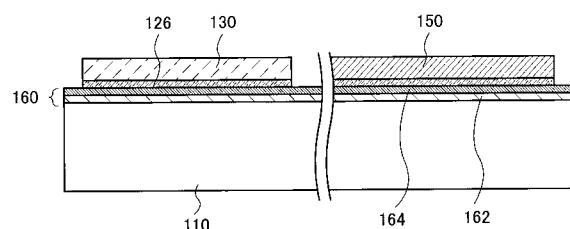

図 1 (B)、図 3 (A)、及び 3 (B) は、ベース基板 110 に接合層 164 を含む絶縁層 160 を形成する例を示している。絶縁層 160 は、単層構造でも積層構造でもよいが、単結晶半導体層 130 との接合面は平滑面を有し親水性表面を形成するようにする。なお、ベース基板 110 と接合層 164 との間には、ベース基板 110 として用いられるガラス基板からアルカリ金属若しくはアルカリ土類金属などの可動イオンの拡散を防ぐため、バリア層 162 が設けられていることが好ましい。30

【0042】

図 3 (A) は、絶縁層 160 としてバリア層 162、接合層 164 の積層構造を形成する例を示している。接合層 164 としては、前記接合層 122 と同様の酸化シリコン層を設ければよい。また、単結晶半導体層 130 に適宜接合層を設けてもよい。図 3 (A) では、単結晶半導体層 130 にも接合層 122 を設ける例を示している。このような構成とすることで、ベース基板 110 及び単結晶半導体層 130 を接合させる際に接合層同士で接合を形成するため、より強固な接合を形成することができる。バリア層 162 は、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層又は窒化酸化シリコン層を用いて単層構造又は積層構造で形成する。好ましくは、窒素を含有する絶縁層を用いて形成する。40

【0043】

図 3 (B) は、ベース基板 110 に接合層 164 を設ける例を示している。具体的には、ベース基板 110 に絶縁層 160 としてバリア層 162 と接合層 164 の積層構造を設50

けている。また、単結晶半導体層 130 には酸化シリコン層 126 を設けている。ベース基板 110 に単結晶半導体層 130 を接合する際には、酸化シリコン層 126 が接合層 164 と接合を形成する。酸化シリコン層 126 は、熱酸化法により形成されたものが好ましい。また、酸化シリコン層 126 としてケミカルオキサイドを用いることもできる。ケミカルオキサイドは、例えば、オゾン含有水で単結晶半導体基板表面を処理することで形成することができる。ケミカルオキサイドは単結晶半導体基板の表面の良好な平坦性を反映して形成されるので好ましい。

#### 【0044】

なお、非単結晶半導体層 150 の下部に設けられた絶縁層 140 は、単結晶半導体層 130 の下部に設けられた接合層 122 や酸化シリコン層 126 と同じ構成とすることには限定されないが、図 2 (A) 及び図 2 (B) に示すように、少なくとも非単結晶半導体層 150 と接する材料と単結晶半導体層 130 と接する材料とを同じにすることが好ましい。接する材料を同じにすることで、後のパターニングの際の非単結晶半導体層 150 及び単結晶半導体層 130 のエッティング特性をそろえることができる。

#### 【0045】

次に、半導体基板の製造方法について説明する。ここでは、図 2 (B) に示す半導体基板の製造方法の例について、図 4 乃至図 7 を用いて説明する。なお、図 2 (A)、図 3 (A)、図 3 (B) 等に示す半導体基板についても同様にして作製することができることはいうまでもない。

#### 【0046】

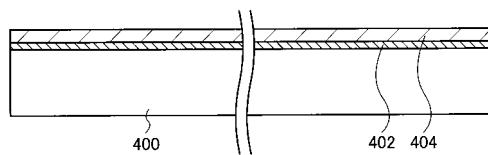

まず、図 4 (A) に示すように、ベース基板 400 上に絶縁層 402 を成膜する。ベース基板 400 としては、上記のような基板を用いることができる。また、P E T、P E S、P E N に代表されるプラスチックや、アクリル等の可撓性を有する合成樹脂からなる基板を用いることも可能である。

#### 【0047】

絶縁層 402 はベース基板 400 中に含まれるアルカリ金属やアルカリ土類金属が、半導体層中に拡散し、半導体素子の特性に悪影響を与えることを防止するために設ける。よってアルカリ金属やアルカリ土類金属の半導体層への拡散を抑制することができる窒化珪素や、窒素を含む酸化珪素といった絶縁性材料を用いて形成することができる。本実施の形態では、プラズマ C V D 法を用いて窒素を含む酸化珪素膜を 10 nm 以上 400 nm 以下 (好ましくは 50 nm 以上 300 nm 以下) の膜厚になるように形成する。

#### 【0048】

次に、絶縁層 402 上に半導体層 404 を形成する。半導体層 404 の膜厚は 25 nm 以上 100 nm 以下 (好ましくは 30 nm 以上 60 nm 以下) とする。なお半導体層 404 は、非晶質半導体であっても良いし、多結晶半導体であっても良い。また半導体としては、シリコン (Si) だけではなくシリコンゲルマニウム (SiGe) 等を用いることもできる。

#### 【0049】

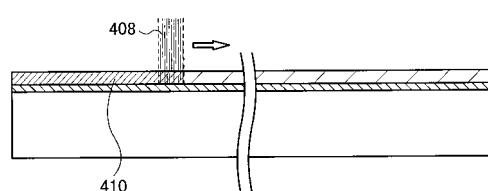

次に、図 4 (B) に示すように、半導体層 404 にレーザー光 408 を照射し、結晶化を行なう。本実施の形態のようなレーザー結晶化を行なう場合には、レーザー光に対する半導体層 404 の耐性を高めるために、500 、 1 時間程度の加熱処理工程をレーザー結晶化の工程の前に加えてよい。

#### 【0050】

レーザー結晶化の工程には、例えば、連続発振のレーザー (C W レーザー) や、擬似的な C W レーザー (発振周波数が 10 MHz 以上、好ましくは 80 MHz 以上のパルス発振レーザー) 等を用いることができる。

#### 【0051】

具体的には、連続発振のレーザーとして、A r レーザー、K r レーザー、C O<sub>2</sub> レーザー、Y A G レーザー、Y V O<sub>4</sub> レーザー、Y L F レーザー、Y A l O<sub>3</sub> レーザー、G d V O<sub>4</sub> レーザー、Y<sub>2</sub> O<sub>3</sub> レーザー、ルビーレーザー、アレキサンンドライトレーザー、T i

10

20

30

40

50

：サファイアレーザー、ヘリウムカドミウムレーザー等を挙げることができる。

【0052】

また、擬似的なCWレーザーとして、Arレーザー、Krレーザー、エキシマレーザー、CO<sub>2</sub>レーザー、YAGレーザー、YVO<sub>4</sub>レーザー、YLFレーザー、YAlO<sub>3</sub>レーザー、GdVO<sub>4</sub>レーザー、Y<sub>2</sub>O<sub>3</sub>レーザー、ルビーレーザー、アレキサンドライトレーザー、Ti：サファイアレーザー、銅蒸気レーザーまたは金蒸気レーザーのようなパルス発振レーザー等を挙げることができる。

【0053】

このようなパルス発振レーザーは、発振周波数を増加させると、連続発振レーザーと同等の効果を示すようになる。

10

【0054】

例えば連続発振が可能な固体レーザーを用いる場合、基本波の第2高調波乃至第4高調波を照射することで、大粒径の結晶を得ることができる。代表的には、YAGレーザー（基本波1064nm）の第2高調波（532nm）や第3高調波（355nm）を用いることができる。パワー密度は0.01MW/cm<sup>2</sup>以上100MW/cm<sup>2</sup>以下程度（好みは0.1MW/cm<sup>2</sup>以上10MW/cm<sup>2</sup>以下）とすれば良い。

【0055】

上記の如き半導体層404へのレーザー光の照射により、結晶性がより高められた結晶性半導体層410（又は非単結晶半導体層）が形成される。

【0056】

なお、本実施の形態においてはレーザー光の照射により結晶性半導体層410を形成する例を示したが、本発明はこれに限定して解釈されない。工程の簡略化のために、結晶化工程を経ない半導体層404を用いても良い。

20

【0057】

次に、図4（C）に示すように結晶性半導体層410を選択的にエッチングし、さらに絶縁層402をエッチングしてベース基板表面の一部を露出させる。結晶性半導体層410のエッチングの際に、後の画素TFTを構成する島状半導体層を形成してもよい。以上の工程により、ベース基板400上に結晶性半導体層410（又は非単結晶半導体層）が形成された。

【0058】

30

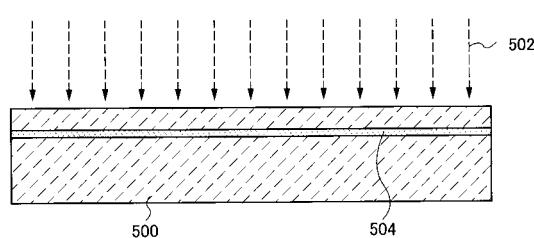

次に、単結晶半導体層を形成する。まず、単結晶半導体基板500を準備する（図5（A）、図6（A）参照）。単結晶半導体基板500としては、例えばシリコン基板やゲルマニウム基板、ガリウムヒ素やインジウムリンなどの化合物半導体基板を用いることができる。シリコン基板としては、直径5インチ（125mm）、直径6インチ（150mm）、直径8インチ（200mm）、直径12インチ（300mm）サイズのものが代表的であり、その形状は円形のものが多いが、これを矩形状に加工したものを用いても良い。また、厚さは1.5mm程度まで適宜選択できる。

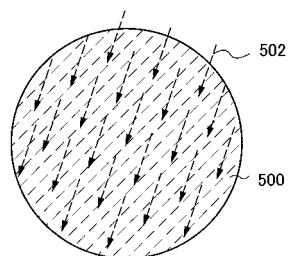

【0059】

次に、単結晶半導体基板500の表面から、電界で加速されたイオン502を所定の深さに打ち込み、イオンドーピング層504（単に損傷領域と呼ぶこともできる）を形成する（図5（A）、図6（A）参照）。ここで、イオンの打ち込みとは、イオンを電界で加速させて対象物に照射することをいう。これにより、対象物の表面から所定の深さの領域に、対象物の組成、原子配列等が変化した領域（損傷領域）を形成することができる。なお、本実施の形態においては、イオンドーピング装置を用いてイオンを打ち込んでいるため、上記損傷領域を、特に、イオンドーピング層と呼んでいる。しかしながら、ここでいう「イオンドーピング装置を用いたイオン打ち込み」は、H<sub>3</sub><sup>+</sup>イオンの割合を高めて打ち込むことを特徴とするものであるから、このような特徴を備える他の方法を用いても良い。すなわち、「イオンドーピング層」がイオンドーピング装置を用いて作製されたものに限定して解釈されるものではない。なお、質量分離を行うイオンの打ち込み方法としては、イオン注入装置を用いる方法があるが、イオンドーピング装置を用いるイオン打ち込

40

50

みはイオン注入装置を用いる場合と比較してイオンの打ち込み効率を高めることができるため、イオンドーピング装置を用いてイオンを打ち込むことが好ましいと言える。

#### 【0060】

単結晶半導体基板500へのイオン502の打ち込みは、後にベース基板400に形成される単結晶半導体層512の膜厚を考慮して行われる(図7(B)参照)。好ましくは、単結晶半導体層512の膜厚が5nm乃至500nm、より好ましくは10nm乃至200nmの厚さとなるようにする。なお、単結晶半導体層512の特性をより向上するため、単結晶半導体層の膜厚が小さくなるようにイオンドーピング層504を形成することが好ましい。具体的には、結晶性半導体層410(又は非単結晶半導体層)より単結晶半導体層512の膜厚が小さくなるように形成する。膜厚を小さくすることにより、高速化に伴う短チャネル効果を抑制することができる。また、寄生容量を低減することができる。なお、結晶性半導体層410(又は非単結晶半導体層)については、単結晶半導体層512ほどの特性を要求されるわけではないから、歩留まりの良い膜厚にて形成してやれば良い。

#### 【0061】

イオン502としては、水素、ヘリウム、又はハロゲン元素から選ばれたソースガスをプラズマ励起して生成されたイオン種を用いることが好ましい。水素イオンを打ち込む場合には、H<sup>+</sup>、H<sub>2</sub><sup>+</sup>、H<sub>3</sub><sup>+</sup>イオンを生成する際に、H<sub>3</sub><sup>+</sup>イオンの割合を高めておくとイオンの打ち込み効率を高めることができ、打ち込み時間を短縮することができるため好ましい。また、このような構成とすることで、単結晶半導体層512の剥離を容易に行うことができる。

#### 【0062】

なお、所定の深さにイオンドーピング層504を形成するために、イオン502を高ドーズ条件で打ち込む場合がある。このとき、条件によっては単結晶半導体基板500の表面が粗くなってしまう。そのため、単結晶半導体基板500の表面に、保護層として窒化シリコン層又は窒化酸化シリコン層などを膜厚50nm以上200nm以下程度の範囲で設けておいてもよい。

#### 【0063】

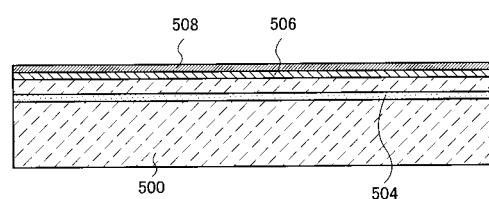

次に、単結晶半導体基板500に絶縁層506を形成した後、接合層508を形成する(図5(B)、図6(B)参照)。絶縁層506は絶縁層402と同じ材料で形成することが好ましいが、これに限定されるものではない。なお、絶縁層506と絶縁層402を同じ材料にて形成することで、エッチングの選択比を十分に確保することができる。つまり、後に形成される単結晶半導体層512と結晶性半導体層410(又は非単結晶半導体層)との膜厚が異なる場合であっても、同時にエッチングを行ってパターニングすることが可能となる。絶縁層506及び絶縁層402の一例として、酸化窒化シリコン層と窒化酸化シリコン層との積層構造を用いても良い。単結晶半導体層512と結晶性半導体層410(又は非単結晶半導体層)に接して酸化窒化シリコン層を有し、酸化窒化シリコン層と窒化酸化シリコン層とが積層された構成であれば、応力により単結晶半導体層及び結晶性半導体層410(又は非単結晶半導体層)の特性が低下してしまうという問題もなく、また、可動イオンや水分等の拡散を防ぐことが可能であり、さらに、エッチングの選択比を十分に確保することができる。

#### 【0064】

本実施の形態では絶縁層506として、プラズマCVD法を用いて、窒素を含む酸化珪素膜を形成する。接合層508は、単結晶半導体基板500がベース基板と接合を形成する面に形成する。ここで形成する接合層508としては、上記のように有機シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層が好ましい。その他に、シランを原料ガスに用いた化学気相成長法により成膜される酸化シリコン層を適用することもできる。化学気相成長法による成膜では、単結晶半導体基板500に形成したイオンドーピング層504から脱ガスが起こらない程度の温度、例えば、350以下の温度が適用される。なお、単結晶半導体基板500から単結晶半導体層512を剥離する加熱処理

10

20

30

40

50

は、化学気相成長法による成膜温度よりも高い加熱処理温度が適用される。

【0065】

なお、後に剥離によって形成される単結晶半導体層512と、絶縁層506、及び接合層508の膜厚の和が、結晶性半導体層410（または非単結晶半導体層）と絶縁層402との膜厚の和に等しくなるように、絶縁層506等を形成することが好ましい。膜厚の和が等しくなるように形成することで、配線の段切れ等を低減することができる。また、膜厚の和を等しくすることは、良好な作製プロセスが可能となる点で有効である。

【0066】

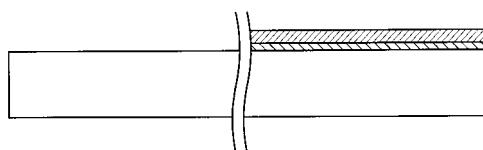

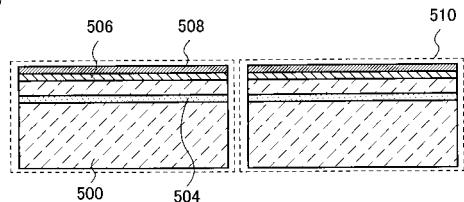

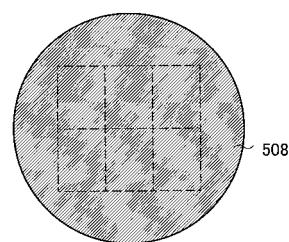

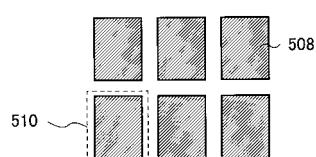

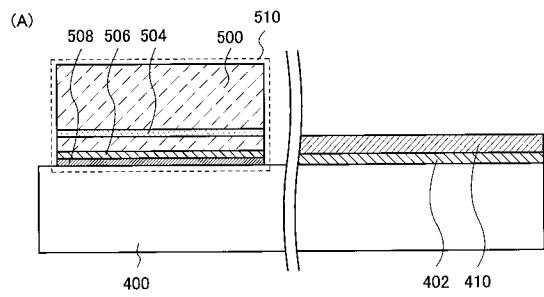

次に、単結晶半導体基板500を所望の大きさ、形状に加工する（図5（C）、図6（C）参照）。図6（C）では、円形の単結晶半導体基板500を分断して、矩形の単結晶半導体基板510を形成する例を示している。この際、絶縁層506、接合層508及びイオンドーピング層504も分断される。つまり、所望の大きさ、形状を有し、所定の深さにイオンドーピング層504が形成され、表面（ベース基板400との接合面）に接合層508が形成された単結晶半導体基板510が得られる。

10

【0067】

矩形の単結晶半導体基板510は、所望の大きさとすることができますが、ここでは、駆動回路の大きさとする。駆動回路の大きさは駆動回路として求められる面積に応じて適宜選択すればよい。単結晶半導体基板510を矩形状にすると、後の製造工程における加工が容易になり、さらに単結晶半導体基板500から効率的に矩形の単結晶半導体基板510を切り出すことも可能になるため好ましい。単結晶半導体基板500の分断は、ダイサー或いはワイヤソー等の切断装置、レーザー切断、プラズマ切断、電子ビーム切断、その他任意の切断手段を用いて行うことができる。

20

【0068】

なお、単結晶半導体基板表面に接合層を形成するまでの工程順序は、適宜入れ替えることが可能である。図5及び図6では単結晶半導体基板にイオンドーピング層を形成し、前記単結晶半導体基板の表面に絶縁層及び接合層を形成した後、前記単結晶半導体基板を所望のサイズに加工する例を示している。これに対し、例えば、単結晶半導体基板を所望のサイズに加工した後、前記所望のサイズの単結晶半導体基板にイオンドーピング層を形成し、前記所望のサイズの単結晶半導体基板の表面に絶縁層及び接合層を形成することもできる。

30

【0069】

次に、ベース基板400と単結晶半導体基板510を貼り合わせる。図7（A）には、ベース基板400と単結晶半導体基板510の接合層508を密着させ、ベース基板400と接合層508を接合させて、ベース基板400と単結晶半導体基板510を貼り合わせる例を示す。なお、接合を形成する面（接合面）は十分に清浄化しておくことが好ましい。ベース基板400と接合層508を密着させることにより接合が形成される。この接合にはファンデルワールス力が作用しており、ベース基板400と単結晶半導体基板510とを密着させて圧力をかけることで、水素結合による強固な接合を形成することができる。

40

【0070】

また、ベース基板400と接合層508との良好な接合を形成するために、接合面を活性化しておいてもよい。例えば、接合を形成する面の一方又は双方に原子ビーム又はイオンビームを照射する。原子ビーム又はイオンビームを利用する場合には、アルゴン等の不活性ガス中性原子ビーム又は不活性ガスイオンビームを用いることができる。その他に、プラズマ照射又はラジカル処理を行うことで接合面を活性化することもできる。このような表面処理により、400以下の温度であっても異種材料間の接合を形成することが容易となる。

【0071】

また、接合層508を介してベース基板400と単結晶半導体基板510を貼り合わせた後は、加熱処理や加圧処理を行うことが好ましい。加熱処理や加圧処理を行うことで接

50

合強度を向上させることが可能となる。加熱処理の温度は、ベース基板400の耐熱温度以下であることが好ましい。加圧処理においては、接合面に垂直な方向に圧力が加わるように行い、ベース基板400及び単結晶半導体基板510の耐圧性を考慮して行う。

#### 【0072】

次に、加熱処理を行い、イオンドーピング層504を剥離面として単結晶半導体基板510の一部を分離する(図7(B)参照)。加熱処理の温度は接合層508の成膜温度以上、ベース基板400の耐熱温度以下とすることが好ましい。例えば、400乃至600の加熱処理を行うことにより、イオンドーピング層504に形成された微小な空洞の体積変化が起こり、イオンドーピング層504に沿って分離(剥離、劈開と呼んでも良い)することが可能となる。接合層508はベース基板400と接合しているので、ベース基板400上には単結晶半導体層512が残存することとなる。

10

#### 【0073】

以上で、ベース基板400上に接合層508を介して単結晶半導体層512が設けられ、かつ、結晶性半導体層410(又は非単結晶半導体層)が設けられた半導体基板が形成される。なお、本実施の形態にて説明した半導体基板は、1枚のベース基板上に接合層を介して複数の単結晶半導体層が設けられた構造であるが、これに限定して解釈されない。

#### 【0074】

なお、本実施の形態においては、単結晶半導体層及び結晶性半導体層(非単結晶半導体層)は、絶縁性基板の一表面上に形成したが、本発明はこれに限らない。例えば、絶縁性基板の一表面(表面)に非単結晶半導体層を形成して表示部とし、絶縁性基板の別の表面(裏面)に単結晶半導体層を形成して駆動回路部としても良い。このような構成とすることにより、絶縁性基板の一表面をすべて表示部として用いることができるため、表示装置の額縁部分がごく僅かになり、表示面の有効利用が可能となる。また、駆動回路を単結晶半導体層にて形成することにより、駆動回路に必要かつ十分な動作速度を確保することができる。ここで、表面の表示部と裏面の駆動回路部との電気的な接続は、絶縁性基板、例えば、ガラス基板を貫通する埋め込み配線によって行うことができる。また、FPCを用いて接続することも可能である。

20

#### 【0075】

なお、剥離により得られる単結晶半導体層は、その表面を平坦化するため、化学的機械的研磨(Chemical Mechanical Polishing: CMP)を行うことが好ましい。また、CMP等の物理的研磨手段を用い、単結晶半導体層の表面にレーザー光を照射して平坦化を行ってもよい。レーザー光を照射して単結晶半導体層を平坦化する場合には、同時に、非単結晶半導体層にレーザー光を照射してその結晶性を向上させても良い。これにより、一度の工程で、単結晶半導体層の平坦化と非単結晶半導体層の特性向上とを実現することができる。つまり、非単結晶半導体層のみを結晶化する工程が不要となるため、工程数を削減することができ、作製コストの低減につながる。レーザーとしては、本実施の形態にて示した結晶化に係るレーザーなどを用いることが可能である。なお、レーザー光を照射する際は、酸素濃度が10 ppm以下の窒素雰囲気下で行うことが好ましい。これは、酸素雰囲気下でレーザー光の照射を行うと単結晶半導体層表面が荒れる恐れがあるためである。また、得られた単結晶半導体層の薄膜化を目的として、CMP等を行ってもよい。

30

#### 【0076】

なお、本実施の形態においては、イオンドーピング層504を形成した後に絶縁層506を形成する場合について説明しているが、本発明はこれに限定して解釈されない。絶縁層506を形成した後にイオンドーピング層504を形成する構成としても良い。

40

#### 【0077】

本実施の形態にて示した方法を用いることにより、単結晶半導体層と非単結晶半導体層とが併せて設けられた基板を提供することができる。これにより、高速動作が要求される回路を、単結晶半導体層を用いて形成することができる。ここで、高速動作が要求される回路とは、一定以上の周波数での駆動が求められる回路を言う。一例としては、1MHz

50

以上の周波数での動作が求められ回路を言う。用いる半導体層を求められる周波数で規定するには、回路に用いられるスイッチング素子の動作可能な周波数が半導体材料に大きく依存しているためである。キャリア移動度が大きい単結晶半導体材料（単結晶シリコンにおける電子の場合で  $500 \text{ cm}^2 / \text{V} \cdot \text{s}$  程度）を用いたスイッチング素子は、信号の伝達速度が大きく高周波数動作に向いている。一方で、キャリア移動度の小さい非単結晶半導体材料（非晶質シリコンにおける電子の場合で  $0.6 \text{ cm}^2 / \text{V} \cdot \text{s}$  程度）を用いたスイッチング素子は、信号の伝達速度も小さく高周波数動作には向かない。なお、スイッチング素子の動作可能な周波数の上限は、材料以外のパラメータ（例えばチャネル長等）にも依存するため、一律に、ある周波数以上を高速動作と規定することは困難である。ここでは、表示装置における駆動回路に要求される性能を一応の目安として、周波数の基準を示した。

10

#### 【0078】

##### （実施の形態2）

本実施の形態では、実施の形態1にて作製した半導体基板を用いて液晶表示装置を製造する方法について、図8乃至11を用いて以下に説明する。

#### 【0079】

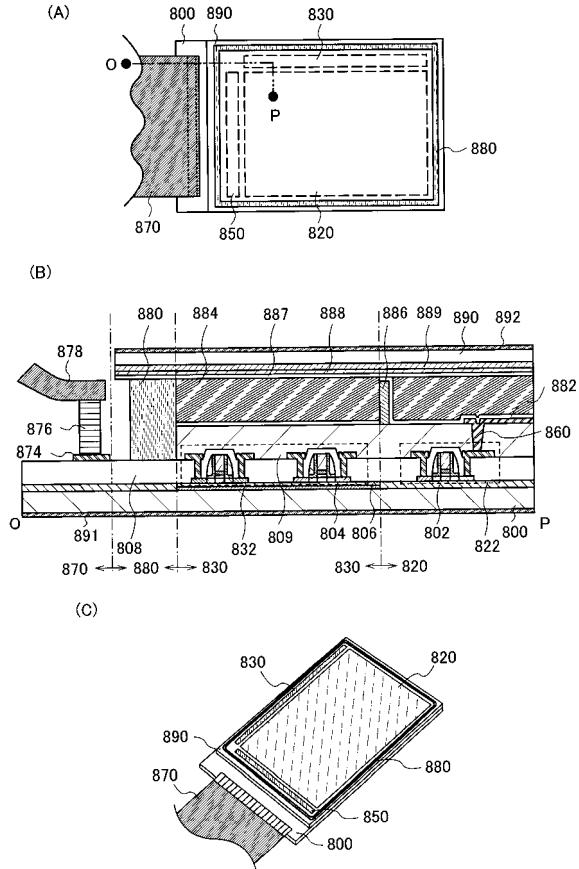

図8（A）は液晶表示装置の上面図であり、図8（B）は図8（A）の線分OPにおける断面図であり、図8（C）は液晶表示装置の斜視図である。

#### 【0080】

本実施の形態に係る液晶表示装置は、第1の基板800上に設けられた表示部820と、第1の駆動回路部830と、第2の駆動回路部850と、を有する。表示部820、第1の駆動回路部830及び第2の駆動回路部850は、シール材880によって、第1の基板800と第2の基板890との間に封止されている。また、第1の基板800上には、第1の駆動回路部830及び第2の駆動回路部850に外部からの信号を伝達する外部入力端子が接続される端子領域870が設けられる。

20

#### 【0081】

図8（B）に示すように、表示部820にはトランジスタを有する画素回路部822が設けられている。また、第1の駆動回路部830にはトランジスタを有する周辺回路部832が設けられている。第1の基板800と画素回路部822との間には、絶縁層802が設けられている。第1の基板800と周辺回路部832との間には、接合層804、絶縁層806が積層されている。なお、基板800上に下地絶縁層として機能する絶縁層を設ける構成としても良い。画素回路部822及び周辺回路部832、或いはその上層には、層間絶縁層として機能する絶縁層808、絶縁層809が設けられている。画素回路部822に形成されたトランジスタのソース電極又はドレイン電極は、絶縁層809に形成された開口を介して、画素電極860と電気的に接続される。なお、画素回路部822はトランジスタを用いた回路が集積されているが、ここでは便宜上、1つのトランジスタの断面のみを示している。同様に、周辺回路部832にもトランジスタを用いた回路が集積されているが、便宜上、2つのトランジスタの断面のみを示している。

30

#### 【0082】

画素回路部822及び周辺回路部832上には、画素電極860を覆うように形成された配向膜882と、配向膜887とで挟持された液晶層884が設けられている。液晶層884は、スペーサ886により距離（セルギャップ）が制御されている。配向膜887上には、対向電極888、カラーフィルター889を介して第2基板890が設けられている。第1の基板800及び第2の基板890はシール材880によって固着されている。

40

#### 【0083】

また、第1の基板800の外側には、偏光板891が、第2の基板890の外側には、偏光板892が設けられている。なお、本実施の形態に示す液晶表示装置は透過型であるため、第1の基板800及び第2の基板890に偏光板を設けているが、例えば、反射型の液晶表示装置とする場合には、第2の基板890のみに偏光板を設ければよい。本発明

50

は透過型、反射型、及びそれらを組み合わせた半透過型のいずれにも適用することができる。

【0084】

また、端子領域870には、端子電極874が設けられている。該端子電極874は、異方性導電層876によって、外部入力端子878と電気的に接続されている。

【0085】

次に、図8で示した液晶表示装置の製造方法の一例について説明する。

【0086】

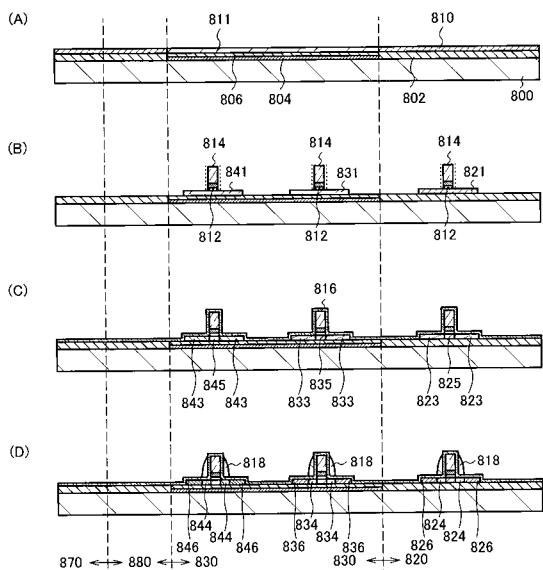

まず、半導体基板を用意する(図9(A)参照)。ここでは、図2(B)に類似した半導体基板を適用する例を示すが、本発明はこれに限定して解釈されるものではない。

10

【0087】

ベース基板である基板800上には、絶縁層802を介して非単結晶半導体層810が、接合層804及び絶縁層806を介して単結晶半導体層811が設けられている。基板800としては、絶縁表面を有する基板または絶縁基板を用いる。例えば、アルミニシリケートガラス、アルミニホウケイ酸ガラス、バリウムホウケイ酸ガラスのような電子工業用に使われる各種ガラス基板、石英基板、セラミック基板、サファイヤ基板等を用いることができる。ここでは、ガラス基板を用いるものとする。

【0088】

なお、ガラス基板からアルカリ金属若しくはアルカリ土類金属などの可動イオンの拡散を防ぐため、下地絶縁層として機能する絶縁層を別に設けても良い。具体的には、窒化シリコン層又は窒化酸化シリコン層等の窒素を含有する絶縁層を設けることが好ましい。

20

【0089】

次に、非単結晶半導体層810を選択的にエッチングして、表示部820に非単結晶半導体層821を形成し、単結晶半導体層811を選択的にエッチングして、第1の駆動回路部830に第1の単結晶半導体層831及び第2の単結晶半導体層841を形成する。そして、非単結晶半導体層821、第1の単結晶半導体層831及び第2の単結晶半導体層841上に、ゲート絶縁層812を介してゲート電極814を形成する(図9(B)参照)。

【0090】

なお、完成するトランジスタの閾値電圧を制御するため、非単結晶半導体層821、第1の単結晶半導体層831及び第2の単結晶半導体層841に低濃度の一導電型を付与する不純物元素を添加してもよい。この場合、トランジスタのチャネル形成領域にも不純物元素が添加されることになる。なお、ここで添加する不純物元素は、ソース領域又はドレイン領域として機能する高濃度不純物領域及びLD領域として機能する低濃度不純物領域よりも低い濃度で添加する。

30

【0091】

ゲート電極814は、基板全面に導電層を形成した後、該導電層を選択的にエッチングして所望の形状に加工して形成する。ここでは、ゲート電極814として導電層による積層構造を形成した後、選択的にエッチングして、分離した導電層が非単結晶半導体層821、第1の単結晶半導体層831及び第2の単結晶半導体層841をそれぞれ横断するように加工している。

40

【0092】

ゲート電極814を形成する導電層は、CVD法やスパッタリング法により、タンタル(Ta)、タンゲステン(W)、チタン(Ti)、モリブデン(Mo)、クロム(Cr)、アルミニウム(Al)、銅(Cu)、又はニオブ(Nb)等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いて基板全面に導電層を形成した後、当該導電層を選択的にエッチングして形成することができる。また、リン等の一導電型を付与する不純物元素が添加された多結晶シリコンに代表される半導体材料を用いて形成することもできる。

【0093】

50

なお、ここではゲート電極 814 を 2 層の導電層の積層構造で形成する例を示すが、ゲート電極は単層構造でも 3 層以上の積層構造でもよい。また、導電層の側面をテープ形状としてもよい。ゲート電極を導電層の積層構造とする場合、下層の導電層の幅を大きくしてもよいし、各層の側面を異なる角度のテープ形状としてもよい。

【0094】

ゲート絶縁層 812 は、CVD 法、スパッタリング法、ALD 法等を用いて、酸化シリコン、酸化窒化シリコン、酸化ハフニウム、酸化アルミニウム、酸化タンタルなどの材料を用いて形成することができる。また、非単結晶半導体層 821、第 1 の単結晶半導体層 831 及び第 2 の単結晶半導体層 841 をプラズマ処理により固相酸化又は固相窒化して形成することもできる。その他、CVD 法等により絶縁層を形成した後、当該絶縁層をプラズマ処理により固相酸化又は固相窒化して形成してもよい。

10

【0095】

なお、図 9 (B) では、ゲート絶縁層 812 とゲート電極 814 の側端部が揃うように加工される例を示すが、特に限定されず、ゲート電極 814 のエッチングにおいてゲート絶縁層 812 を残すように加工してもよい。

【0096】

また、ゲート絶縁層 812 に高誘電率物質 (high-k 材料とも呼ばれる) を用いる場合には、ゲート電極 814 を多結晶シリコン、シリサイド、金属若しくは金属窒化物で形成する。好ましくは金属若しくは金属窒化物で形成することが望ましい。例えば、ゲート電極 814 のうちゲート絶縁層 812 と接する導電層を金属窒化物材料で形成し、その上の導電層を金属材料で形成する。この組み合わせを用いることによって、ゲート絶縁層を薄膜化した場合でもゲート電極に空乏層が広がることを防ぐことができ、微細化した場合にもトランジスタの駆動能力を損なわずに済む。

20

【0097】

次に、ゲート電極 814 上に絶縁層 816 を形成する。そして、ゲート電極 814 をマスクとして一導電型を付与する不純物元素を添加する (図 9 (C) 参照)。ここでは、第 1 の駆動回路部 830 に形成された第 1 の単結晶半導体層 831 及び第 2 の単結晶半導体層 841 に相異なる導電型を付与する不純物元素を添加する例を示す。また、表示部 820 に形成された非単結晶半導体層 821 には第 1 の単結晶半導体層 831 と同じ導電型を付与する不純物元素を添加する例を示す。

30

【0098】

表示部 820 に形成された非単結晶半導体層 821 には、ゲート電極 814 をマスクとして自己整合的に一対の不純物領域 823 と、当該一対の不純物領域 823 の間に位置するチャネル形成領域 825 が形成される。

【0099】

第 1 の駆動回路部 830 に形成された第 1 の単結晶半導体層 831 には、ゲート電極 814 をマスクとして自己整合的に一対の不純物領域 833 と、当該一対の不純物領域 833 の間に位置するチャネル形成領域 835 が形成される。第 2 の単結晶半導体層 841 には、ゲート電極 814 をマスクとして自己整合的に一対の不純物領域 843 と、当該一対の不純物領域 843 の間に位置するチャネル形成領域 845 が形成される。不純物領域 833 及び不純物領域 843 は、相異なる導電型の不純物元素が添加されている。

40

【0100】

一導電型を付与する不純物元素としては、ボロン (B)、アルミニウム (Al)、ガリウム (Ga) 等の p 型を付与する元素、リン (P)、ヒ素 (As) 等の n 型を付与する元素を用いることができる。本実施の形態では、表示部 820 に形成された非単結晶半導体層 821、第 1 の駆動回路部 830 に形成された第 1 の単結晶半導体層 831 に n 型を付与する元素、例えばリンを添加する。また、第 2 の単結晶半導体層 841 に p 型を付与する元素、例えばボロンを添加する。なお、非単結晶半導体層 821、第 1 の単結晶半導体層 831 に不純物元素を添加する際は、レジストマスク等を用いて第 2 の単結晶半導体層 841 を選択的に覆えばよい。同様に、第 2 の単結晶半導体層 841 に不純物元素を添加

50

する際は、レジストマスク等を用いて非単結晶半導体層 821、第1の単結晶半導体層 831を選択的に覆えばよい。

#### 【0101】

絶縁層 816 は、CVD 法、スパッタリング法、ALD 法等を用いて、酸化シリコン或いは酸化窒化シリコン、又は窒化シリコン或いは窒化酸化シリコンなどの材料を用いて形成することができる。一導電型を付与する不純物元素を添加する際に、絶縁層 816 を通過させて添加する構成とすることで、非単結晶半導体層及び単結晶半導体層に与えるダメージを低減することができる。

#### 【0102】

次に、ゲート電極 814 の側面にサイドウォール絶縁層 818 を形成する。そして、ゲート電極 814 及びサイドウォール絶縁層 818 をマスクとして一導電型を付与する不純物元素を添加する（図 9（D）参照）。なお、非単結晶半導体層 821、第1の単結晶半導体層 831 及び第2の単結晶半導体層 841 には、それぞれ先の工程（不純物領域 823、不純物領域 833 及び不純物領域 843 を形成する工程）で添加した不純物元素と同じ導電型の不純物元素を添加する。また、先の工程で添加した不純物元素よりも高い濃度で添加する。

#### 【0103】

非単結晶半導体層 821 には、ゲート電極 814 及びサイドウォール絶縁層 818 をマスクとして自己整合的に一対の高濃度不純物領域 826 と、一対の低濃度不純物領域 824 が形成される。ここで形成される高濃度不純物領域 826 はソース領域又はドレイン領域として機能し、低濃度不純物領域 824 は LDD（Lightly Doped Drain）領域として機能する。

#### 【0104】

第1の単結晶半導体層 831 には、ゲート電極 814 及びサイドウォール絶縁層 818 をマスクとして自己整合的に一対の高濃度不純物領域 836 と、一対の低濃度不純物領域 834 が形成される。ここで形成される高濃度不純物領域 836 はソース領域又はドレイン領域として機能し、低濃度不純物領域 834 は LDD 領域として機能する。第2の単結晶半導体層 841 には、ゲート電極 814 及びサイドウォール絶縁層 818 をマスクとして自己整合的に一対の高濃度不純物領域 846 と、一対の低濃度不純物領域 844 が形成される。

#### 【0105】

なお、非単結晶半導体層 821、第1の単結晶半導体層 831 に不純物元素を添加する際は、レジストマスク等を用いて第2の単結晶半導体層 841 を選択的に覆えばよい。同様に、第2の単結晶半導体層 841 に不純物元素を添加する際は、レジストマスク等を用いて非単結晶半導体層 821、第1の単結晶半導体層 831 を選択的に覆えばよい。

#### 【0106】

サイドウォール絶縁層 818 は、絶縁層 816 を介してゲート電極 814 の側面に設けられる。例えば、ゲート電極 814 を埋め込むように形成した絶縁層を、垂直方向を主体とした異方性エッチングを行うことによって、ゲート電極 814 の側面に自己整合的に形成することができる。サイドウォール絶縁層 818 は、窒化シリコン或いは窒化酸化シリコン、又は酸化シリコン或いは酸化窒化シリコンなどの材料を用いて形成することができる。なお、絶縁層 816 を酸化シリコン又は酸化窒化シリコンを用いて形成する場合、サイドウォール絶縁層 818 を窒化シリコン又は窒化酸化シリコンを用いて形成することで、絶縁層 816 をエッチングストッパーとして機能させることができる。また、絶縁層 816 を窒化シリコン又は窒化酸化シリコンを用いて形成する場合は、サイドウォール絶縁層 818 を酸化シリコン又は酸化窒化シリコンを用いて形成すればよい。このように、エッチングストッパーとして機能しうる絶縁層を設けることで、サイドウォール絶縁層を形成する際のオーバーエッチングにより非単結晶半導体層及び単結晶半導体層がエッチングされてしまうのを防ぐことができる。

#### 【0107】

10

20

30

40

50

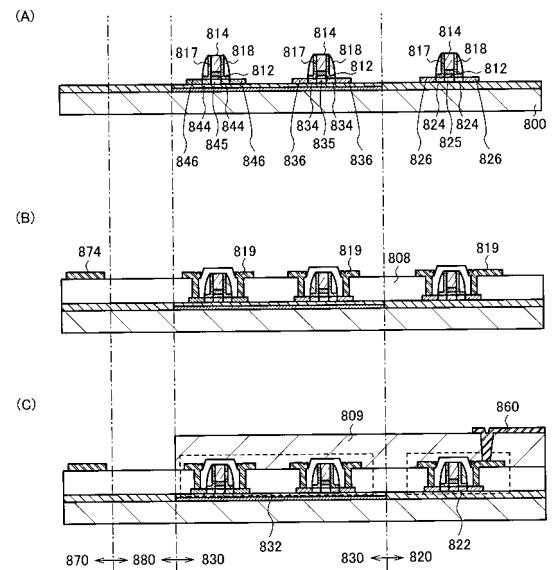

次に、絶縁層 816 の露出部をエッティングする(図10(A)参照)。絶縁層 816 は、サイドウォール絶縁層 818 及びゲート電極 814 の間、サイドウォール絶縁層 818 及び非単結晶半導体層 821 の間、サイドウォール絶縁層 818 及び第1の単結晶半導体層 831 の間、並びにサイドウォール絶縁層 818 及び第2の単結晶半導体層 841 の間に残る。

#### 【0108】

なお、ソース領域又はドレイン領域として機能する高濃度不純物領域を低抵抗化するため、シリサイド層を形成してもよい。シリサイド層としては、コバルトシリサイド若しくはニッケルシリサイドを適用すれば良い。非単結晶半導体層及び単結晶半導体層の膜厚が薄い場合には、高濃度不純物領域が形成された非単結晶半導体層及び単結晶半導体層の底部までシリサイド反応を進めてフルシリサイド化しても良い。

10

#### 【0109】

次に、基板 800 全面に絶縁層 808 を形成した後、該絶縁層 808 を選択的にエッティングして、表示部 820 の非単結晶半導体層 821 に形成された高濃度不純物領域 826 に達する開口を形成する。また、第1の駆動回路部 830 の第1の単結晶半導体層 831 及び第2の単結晶半導体層 841 に形成された高濃度不純物領域 836 及び高濃度不純物領域 846 にそれぞれ達する開口を形成する。そして、該開口を埋め込むように導電層 819 を形成する。また、端子領域 870 に端子電極 874 を形成する(図10(B)参照)。

20

#### 【0110】

絶縁層 808 は、CVD法やスパッタリング法、ALD(Atomic Layer Deposition)法、塗布法等により、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の酸素若しくは窒素を含む無機絶縁材料や、DLC(ダイヤモンドライクカーボン)等の炭素を含む絶縁材料、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機絶縁材料またはシロキサン樹脂等のシロキサン材料を用いて形成する。なお、シロキサン材料とは、Si-O-Si 結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。また、絶縁層 808 は、CVD法やスパッタリング法、ALD法を用いて絶縁層を形成した後、当該絶縁層に酸素雰囲気下又は窒素雰囲気下でプラズマ処理を行ってもよい。ここでは絶縁層 808 は単層構造の例を示すが、2層以上の積層構造としてもよい。また、無機絶縁層や、有機絶縁層を組み合わせて形成してもよい。例えば、基板 800 全面にパッシベーション層として機能する窒化シリコン膜や窒化酸化シリコン膜を形成し、その上層に平坦化層として機能するリンシリケートガラス(PSG)やボロンリンシリケートガラス(BPSG)を材料に用いた絶縁層を形成することができる。

30

#### 【0111】

導電層 819 は、ソース電極又はドレイン電極として機能する。導電層 819 は、絶縁層 808 に形成された開口を介して、非単結晶半導体層 821、第1の単結晶半導体層 831 又は第2の単結晶半導体層 841 と電気的に接続される。

40

#### 【0112】

導電層 819 は、CVD法やスパッタリング法を用いて、アルミニウム(Al)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)等の金属元素、炭素(C)やシリコン(Si)等の元素、又はこれらを含む合金材料若しくは化合物材料を用いて単層構造又は積層構造で導電層を形成し、当該導電層を選択的にエッティングすることで形成できる。アルミニウムを含む合金材料としては、例えば、アルミニウムを主成分としてニッケルを含む材料、又は、アルミニウムを主成分として、ニッケルと、炭素又はシリコンの一方又は両方を含む合金材料が挙げられる。ま

50

た、タンゲステンを含む化合物材料としては、例えばタンゲステンシリサイドが挙げられる。導電層 819 は、例えば、バリア層とアルミニウムシリコン (Al-Si) 層とバリア層の積層構造、バリア層とアルミニウムシリコン (Al-Si) 層と窒化チタン層とバリア層の積層構造を採用することができる。なお、バリア層とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、ソース電極又はドレイン電極として機能する導電層を形成する材料として最適である。また、ソース電極又はドレイン電極として機能する導電層を、上層と下層にバリア層を設けた積層構造とすると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができるため好ましい。

## 【0113】

10

端子領域 870 に形成される端子電極 874 は、後に形成される FPC 等の外部入力端子と第1の駆動回路部 830 及び第2の駆動回路部 850 とを電気的に接続させるための電極として機能する。ここでは、導電層 819 と同一の材料を用いて端子電極 874 を形成する例を示している。

## 【0114】

以上で、表示部 820 に非単結晶半導体層 821 を有するトランジスタが形成された画素回路部 822 が形成される。また、第1の駆動回路部 830 に第1の単結晶半導体層 831 を有するトランジスタ及び第2の単結晶半導体層 841 を有するトランジスタが形成された周辺回路部 832 が形成される。

## 【0115】

20

なお、本実施の形態では、非単結晶半導体層と単結晶半導体層に同時にドーピング等を適用する工程について説明したが、本発明はこれに限定されるものではない。非単結晶半導体層に最適な工程、単結晶半導体層に最適な工程を用いて液晶表示装置を作製しても良い。なお、非単結晶半導体層と単結晶半導体層に、同時にエッティングやドーピング等を適用する場合には、作製工程が非常に簡略化できるため、低コスト化、歩留まりの向上等の有利な効果が得られる。

## 【0116】

次に、表示部 820 及び第1の駆動回路部 830 上に絶縁層 809 を形成する。そして、表示部 820 上に形成された絶縁層 809 を選択的にエッティングして、画素回路部 822 に形成されたトランジスタの導電層 819 に達する開口を形成する。その後、該開口を埋め込むように画素電極 860 を形成する (図 10 (C) 参照)。

30

## 【0117】

絶縁層 809 は、表示部 820 及び第1の駆動回路部 830 の凹凸を平滑化して、平坦な表面を形成できる平坦化層であることが好ましい。例えば、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機絶縁材料又はシロキサン樹脂等のシロキサン材料を用いて形成することができる。ここでは、絶縁層 809 を単層構造とする例を示すが、2層以上の積層構造としてもよい。積層構造にする場合、例えば、有機樹脂などを上層にし、酸化シリコン、窒化シリコンまたは酸化窒化シリコン等の無機絶縁層を下層にした積層構造、又は無機絶縁層で有機絶縁層を挟持する構造とすることができる。絶縁層 809 は、各種印刷法 (スクリーン印刷、平版印刷、凸版印刷、グラビア印刷等)、液滴吐出法、ディスペンサ法等を用いて選択的に形成することができる。また、スピンドルコート法等を用いて絶縁層を全面に形成した後、所望の領域 (ここでは表示部 820 及び第1の駆動回路部 830) 以外を選択的にエッティングして絶縁層 809 を形成することもできる。

40

## 【0118】

画素電極 860 は、本実施の形態では可視光を透過する材料を用いて形成することが好ましい。可視光を透過する導電性材料としては、インジウム錫酸化物 (ITO)、酸化シリコンを含むインジウム錫酸化物 (ITSO)、酸化亜鉛 (ZnO)、酸化インジウム亜鉛 (IZO)、又はガリウムを添加した酸化亜鉛 (GZO) 等が挙げられる。一方、画素電極 860 の膜厚を十分に小さくできる場合には、上記の材料に限らない。通常の厚さで

50

は、光を透過しない材料であっても、十分に薄く形成した場合には光を透過するためである。このような場合には、タンタル (Ta)、タングステン (W)、チタン (Ti)、モリブデン (Mo)、アルミニウム (Al)、クロム (Cr)、銀 (Ag) 等の金属元素、又は当該金属元素を含む合金材料若しくは化合物材料を用いることも可能である。なお、反射型又は半透過型の液晶表示装置を作製する場合には上記の金属元素等を用いると良い。

#### 【0119】

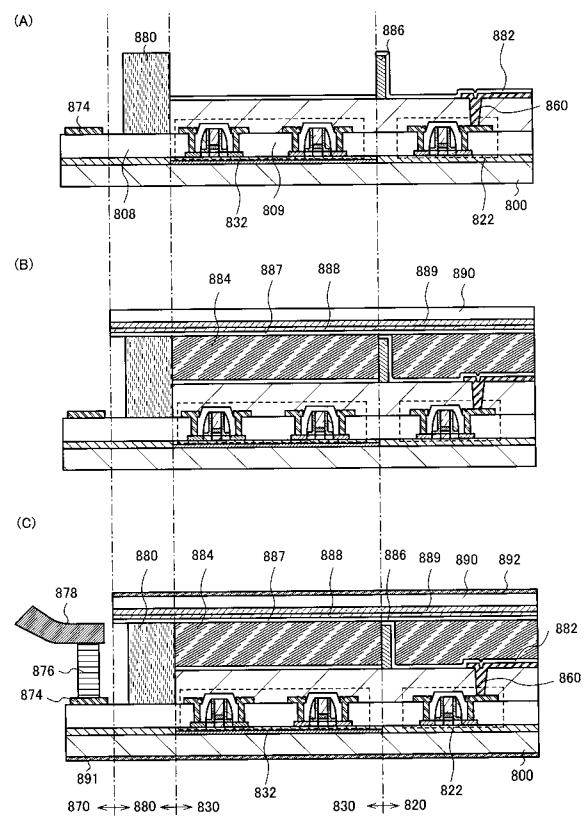

次に、スペーサ 886 を形成した後、画素電極 860 及びスペーサ 886 を覆うように配向膜 882 を形成する。そして、表示部 820 及び第 1 の駆動回路部 830、第 2 の駆動回路部 850 を囲うようにシール材 880 を形成する (図 11 (A) 参照)。

10

#### 【0120】

スペーサ 886 は、エポキシ、ポリイミド、ポリアミド、ポリイミドアミド、アクリル等の有機絶縁材料、又は酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン等の無機絶縁材料を用いて、単層構造又は積層構造で形成することができる。本実施の形態ではスペーサ 886 として柱状のスペーサを形成するため、基板全面に絶縁層を形成した後、エッチング加工して所望の形状のスペーサを得る。なお、スペーサ 886 の形状は特に限定されず、球状のスペーサを散布してもよい。スペーサ 886 により、セルギヤップを保持することができる。

#### 【0121】

配向膜 882 は、液晶を一定方向に配列させることができ可能な層である。材料は、利用する液晶の動作モードに応じて適宜選択すればよい。例えばポリイミド、ポリアミド等の材料を用いて形成し、配向処理を行うことで配向膜 882 を作製することができる。配向処理としては、ラビングや、紫外線の照射等を行えばよい。配向膜 882 の形成方法は特に限定されないが、各種印刷法や液滴吐出法を用いると、絶縁層 809 上に選択的に形成することができる。

20

#### 【0122】

シール材 880 は、表示領域を少なくとも囲うように形成する。本実施の形態では、表示部 820、第 1 の駆動回路部 830 及び第 2 の駆動回路部 850 の周辺を囲うようにシールパターンを形成する。シール材 880 としては、熱硬化樹脂や光硬化樹脂を用いることができる。なお、シール材にフィラーを含ませることでセルギヤップを保持させることもできる。シール材 880 は、後に対向電極、カラーフィルター等設けられた基板と封止する際に、光照射、加熱処理等を行って硬化を行う。

30

#### 【0123】

シール材 880 に囲まれた領域に液晶層 884 を形成する。また、カラーフィルター 889、対向電極 888、配向膜 887 が順次積層された第 2 の基板 890 と第 1 の基板 800 を貼り合わせる (図 11 (B) 参照)。

#### 【0124】

液晶層 884 は、所望の液晶材料を用いて形成する。また、液晶層 884 は、シール材 880 で形成されたシールパターン内に液晶材料を滴下して形成することができる。液晶材料の滴下は、ディスペンサ法や液滴吐出法を用いて行えばよい。なお、液晶材料は予め減圧下で脱気しておくか、滴下後に減圧下で脱気することが好ましい。また、液晶材料の滴下の際に不純物等が混入しないように、不活性雰囲気下で行うことが好ましい。また、液晶材料を滴下して液晶層 884 を形成した後、第 1 の基板 800 及び第 2 の基板 890 を貼り合わせるまでは、液晶層 884 に気泡等が入らないように減圧下で行うことが好ましい。

40

#### 【0125】

また、液晶層 884 は、第 1 の基板 800 と第 2 の基板 890 を貼り合わせた後、シール材 880 の枠状パターン内に、毛細管現象を利用して液晶材料を注入して形成することもできる。この場合、あらかじめシール材等に液晶の注入口となる部分を形成しておく。なお、液晶材料は、減圧下で注入を行うことが好ましい。

50

## 【0126】

第1の基板800と第2の基板890は、対向させて密着させた後、シール材880を硬化させて貼り合わせることができる。このとき、第2の基板890に設けられた配向膜887と、第1の基板800に設けられた配向膜882とで、液晶層884が挟持される構造となるように貼り合わせる。なお、第1の基板800と第2の基板890との貼り合わせ及び液晶層884の形成を行った後、加熱処理を行って液晶層884の配向乱れを修正することも可能である。

## 【0127】

第2の基板890としては、透光性を有する基板を用いる。例えば、アルミニノシリケートガラス、アルミニノホウケイ酸ガラス、バリウムホウケイ酸ガラス等の各種ガラス基板、石英基板、セラミック基板、サファイヤ基板等を用いることができる。

10

## 【0128】

第2の基板890上には、貼り合わせる前に、カラーフィルター889、対向電極888、配向膜887を順に形成しておく。なお、第2の基板890には、カラーフィルター889の他にブラックマトリクスを設けてもよい。また、カラーフィルター889は第2の基板890の外側に設けてもよい。また、モノカラー表示とする場合は、カラーフィルター889を設けなくともよい。また、シール材を第2の基板890側に設けてもよい。なお、シール材を第2の基板890側に設ける場合は、液晶材料は第2の基板890に設けられたシール材のパターン内に滴下する。

## 【0129】

20

対向電極888は、インジウム錫酸化物(ITO)、酸化シリコンを含むインジウム錫酸化物(ITSO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、又はガリウムを添加した酸化亜鉛(GZO)等の可視光を透過する性質を有する導電材料を用いて形成することができる。配向膜887は、上記配向膜882と同様に形成することができる。

## 【0130】

以上により、第1の基板800と第2の基板890との間に、液晶層884を含む表示部820、第1の駆動回路部830及び第2の駆動回路部850が封止された構造が得られる。なお、表示部820及び第1の駆動回路部830、第2の駆動回路部850に形成される回路部には、トランジスタの他、抵抗やコンデンサなどを同時に作製してもよい。また、トランジスタの構造は特に限定されない。例えば、1つの非単結晶半導体層又は単結晶半導体層に対して複数のゲートを設けたマルチゲート構造とすることもできる。

30

## 【0131】

次に、第1の基板800及び第2の基板890に偏光板891及び偏光板892を設け、端子電極874に異方性導電層876を介して外部入力端子878を接続する(図11(C)参照)。

## 【0132】

外部入力端子878は外部からの信号(例えばビデオ信号、クロック信号、スタート信号、リセット信号等)や電位を伝達する役目を担う。ここでは、外部入力端子878としてFPCを接続する。なお、端子電極874は、第1の駆動回路部830及び第2の駆動回路部850と電気的に接続されているものとする。

40

## 【0133】

以上により液晶表示装置を得ることができる。本実施の形態に示すように、単結晶半導体層を用いて駆動回路部を形成し、非単結晶半導体層を用いて表示部(画素部)を形成することにより、作製コストを低減しつつ、必要かつ十分な特性を有する駆動回路を作製することができる。これにより、完全なモノリシック型の半導体装置を作製することができるため、作製コストを低減することができる。また、外部にICを接続することに起因して生じる厚みを低減することができる。また、額縁部分の面積を低減した半導体装置を作製することができる。さらに、ガラス基板等の耐熱性が低い基板を用いて高性能な半導体装置を作製することができる。

50

## 【0134】

なお、本実施の形態は、実施の形態1と適宜組み合わせて用いることができる。

## 【0135】

## (実施の形態3)

実施の形態2では、液晶表示装置を用いる表示装置を作製する例を示したが、本実施の形態においてはその他の表示装置について図12を用いて説明する。

## 【0136】

図12(A)は、発光素子を用いる表示装置(発光装置、EL表示装置ともいわれる)の一例である。図12(B)は、電気泳動素子を用いる表示装置(電子ペーパ、電気泳動表示装置ともいわれる)の一例である。なお、表示素子以外の構成は実施の形態2にて示したものと同様であるため、詳細な説明は省略する。

10

## 【0137】

図12(A)は、液晶素子の代わりに発光素子1210を用いた表示装置を示している。ここでは、画素電極(陰極)1212と対向電極(陽極)1216との間に有機化合物層1214が設けられている例を示す。有機化合物層1214は、少なくとも発光層を有し、その他、電子注入層、電子輸送層、正孔輸送層、正孔注入層等を有していてもよい。また、画素電極1212の端部は隔壁層1218に覆われている。隔壁層1218は絶縁材料を用いて基板全面に成膜した後に画素電極1212の一部が露出するように加工するか、液滴吐出法等用いて選択的に形成すればよい。画素電極1212及び隔壁層1218上に、有機化合物層1214、対向電極1216が順に積層される。発光素子1210と第2の基板890との間の空間1220は、不活性気体等を充填してもよいし、樹脂等を形成してもよい。

20

## 【0138】

なお、本実施の形態においては、有機材料を用いて発光素子を形成したが、本発明はこれに限定して解釈されない。無機材料を用いて発光素子を形成しても良いし、有機材料と無機材料とを組み合わせて発光素子を形成しても良い。

## 【0139】

図12(B)は、液晶素子の代わりに電気泳動素子を用いた表示装置を示している。ここでは、画素電極1232と対向電極(共通電極)1234との間に電気泳動層1240が設けられている例を示す。電気泳動層1240は、バインダ1236によって固定された複数のマイクロカプセル1230を有している。マイクロカプセル1230は直径10 $\mu\text{m}$ 乃至200 $\mu\text{m}$ 程度であり、透明な液体と、正に帯電した白い微粒子と、負に帯電した黒い微粒子とを封入した構成となっている。当該マイクロカプセル1230は、画素電極1232と対向電極1234によって電場が与えられると、白い微粒子と、黒い微粒子が逆の方向に移動し、白または黒を表示することができる。この原理を応用した表示素子が電気泳動素子である。電気泳動素子は、液晶素子に比べて反射率が高いため、補助ライト(例えばフロントライト)が無くとも、薄暗い場所で表示部を認識することができる。また、消費電力も小さい。さらに、表示部に電源が供給されない場合であっても、一度表示した像を保持することが可能である。

30

## 【0140】

本実施の形態は、実施の形態1及び2と適宜組み合わせて用いることができる。

40

## 【0141】

## (実施の形態4)

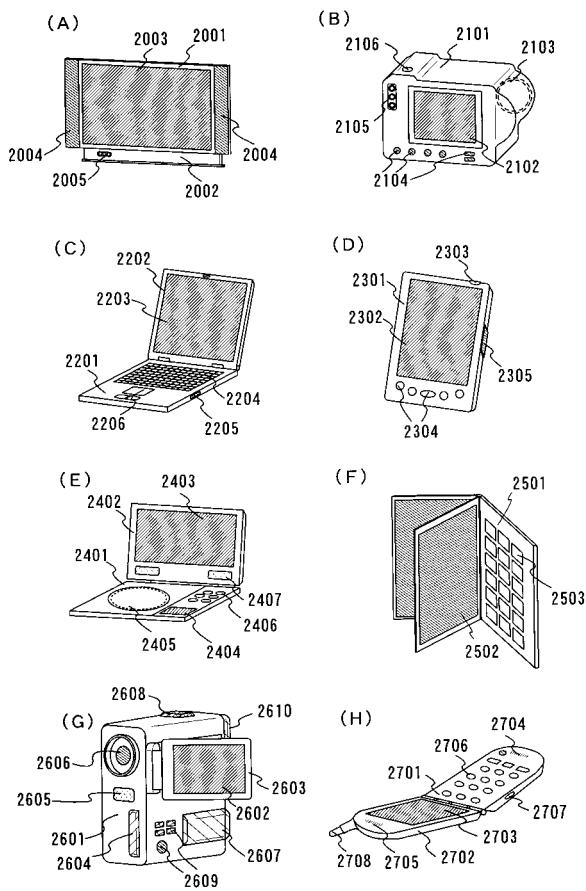

本発明の表示装置を用いた電子機器について、図13を参照して説明する。

## 【0142】

本発明の表示装置を用いた電子機器として、ビデオカメラ、デジタルカメラ等のカメラ、ゴーグル型ディスプレイ(ヘッドマウントディスプレイ)、ナビゲーションシステム、音響再生装置(カーオーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD))

50

等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。

【0143】

図13(A)はテレビ受像器又はパーソナルコンピュータのモニターである。筐体2001、支持台2002、表示部2003、スピーカー部2004、ビデオ入力端子2005等を含む。表示部2003には、本発明の表示装置が用いられている。本発明により、低コスト且つ高性能なテレビ受像器又はパーソナルコンピュータのモニターを提供することができる。

【0144】

図13(B)はデジタルカメラである。本体2101の正面部分には受像部2103が設けられており、本体2101の上面部分にはシャッターボタン2106が設けられている。また、本体2101の背面部分には、表示部2102、操作キー2104、及び外部接続ポート2105が設けられている。表示部2102には、本発明の表示装置が用いられている。本発明により、低コスト且つ高性能なデジタルカメラを提供することができる。

【0145】

図13(C)はノート型パーソナルコンピュータである。本体2201には、キーボード2204、外部接続ポート2205、ポインティングデバイス2206が設けられている。また、本体2201には、表示部2203を有する筐体2202が取り付けられている。表示部2203には、本発明の表示装置が用いられている。本発明により、低コスト且つ高性能なノート型パーソナルコンピュータを提供することができる。

【0146】

図13(D)はモバイルコンピュータであり、本体2301、表示部2302、スイッチ2303、操作キー2304、赤外線ポート2305等を含む。表示部2302には、本発明の表示装置が用いられている。本発明により、低コスト且つ高性能なモバイルコンピュータを提供することができる。

【0147】

図13(E)は画像再生装置である。本体2401には、表示部B2404、記録媒体読み込み部2405及び操作キー2406が設けられている。また、本体2401には、スピーカー部2407及び表示部A2403それぞれを有する筐体2402が取り付けられている。表示部A2403及び表示部B2404それぞれには、本発明の表示装置が用いられている。本発明の表示装置を有することにより、低コスト且つ高性能な画像再生装置を提供することができる。

【0148】

図13(F)は電子書籍である。本体2501には操作キー2503が設けられている。また、本体2501には複数の表示部2502が取り付けられている。表示部2502には、本発明の表示装置が用いられている。本発明の表示装置を有することにより、低コスト且つ高性能な電子書籍を提供することができる。

【0149】

図13(G)はビデオカメラであり、本体2601には外部接続ポート2604、リモコン受信部2605、受像部2606、バッテリー2607、音声入力部2608、操作キー2609、及び接眼部2610が設けられている、また、本体2601には、表示部2602を有する筐体2603が取り付けられている。表示部2602には、本発明の表示装置が用いられている。本発明により、低コスト且つ高性能なビデオカメラを提供することができる。

【0150】

図13(H)は携帯電話であり、本体2701、筐体2702、表示部2703、音声入力部2704、音声出力部2705、操作キー2706、外部接続ポート2707、アンテナ2708等を含む。表示部2703には、本発明の表示装置が用いられている。本発明により、低コスト且つ高性能な携帯電話を提供することができる。

10

20

30

40

50

## 【0151】

以上の様に、本発明の適用範囲は極めて広く、あらゆる分野の電子機器に用いることが可能である。なお、本実施の形態は、実施の形態1乃至3と適宜組み合わせて用いることができる。

## 【図面の簡単な説明】

## 【0152】

【図1】本発明の半導体基板の斜視図。

【図2】本発明の半導体基板の断面図。

【図3】本発明の半導体基板の断面図。

【図4】本発明の半導体基板の作製工程を示す図。

10

【図5】本発明の半導体基板の作製工程を示す図。

【図6】本発明の半導体基板の作成工程を示す図。

【図7】本発明の半導体基板の作成工程を示す図。

【図8】本発明の液晶表示装置を示す図。

【図9】本発明の液晶表示装置の作製工程を示す図。

【図10】本発明の液晶表示装置の作製工程を示す図。

【図11】本発明の液晶表示装置の作製工程を示す図。

【図12】本発明の表示装置を示す図。

【図13】本発明の電子機器を示す図。

【図14】従来の表示装置の構成例を示す図。

20

## 【符号の説明】

## 【0153】

100 半導体基板

110 ベース基板

120 絶縁層

122 接合層

124 窒素含有絶縁層

126 酸化シリコン層

130 単結晶半導体層

140 絶縁層

30

150 非単結晶半導体層

160 絶縁層

162 バリア層

164 接合層

400 ベース基板

402 絶縁層

404 半導体層

408 レーザー光

410 結晶性半導体層

500 単結晶半導体基板

40

502 イオン

504 イオンドーピング層

506 絶縁層

508 接合層

510 単結晶半導体基板

512 単結晶半導体層

800 基板

802 絶縁層

804 接合層

806 絶縁層

50

|         |            |    |

|---------|------------|----|

| 8 0 8   | 絶縁層        |    |

| 8 0 9   | 絶縁層        |    |

| 8 1 0   | 非単結晶半導体層   |    |

| 8 1 1   | 単結晶半導体層    |    |

| 8 1 2   | ゲート絶縁層     |    |

| 8 1 4   | ゲート電極      |    |

| 8 1 6   | 絶縁層        |    |

| 8 1 8   | サイドウォール絶縁層 |    |

| 8 1 9   | 導電層        |    |

| 8 2 0   | 表示部        | 10 |

| 8 2 1   | 非単結晶半導体層   |    |

| 8 2 2   | 画素回路部      |    |

| 8 2 3   | 不純物領域      |    |

| 8 2 4   | 低濃度不純物領域   |    |

| 8 2 5   | チャネル形成領域   |    |

| 8 2 6   | 高濃度不純物領域   |    |

| 8 3 0   | 駆動回路部      |    |

| 8 3 1   | 単結晶半導体層    |    |

| 8 3 2   | 周辺回路部      |    |

| 8 3 3   | 不純物領域      | 20 |

| 8 3 4   | 低濃度不純物領域   |    |

| 8 3 5   | チャネル形成領域   |    |

| 8 3 6   | 高濃度不純物領域   |    |

| 8 4 1   | 単結晶半導体層    |    |

| 8 4 3   | 不純物領域      |    |

| 8 4 4   | 低濃度不純物領域   |    |

| 8 4 5   | チャネル形成領域   |    |

| 8 4 6   | 高濃度不純物領域   |    |

| 8 5 0   | 駆動回路部      |    |

| 8 6 0   | 画素電極       | 30 |

| 8 7 0   | 端子領域       |    |

| 8 7 4   | 端子電極       |    |

| 8 7 6   | 異方性導電層     |    |

| 8 7 8   | 外部入力端子     |    |

| 8 8 0   | シール材       |    |

| 8 8 2   | 配向膜        |    |

| 8 8 4   | 液晶層        |    |

| 8 8 6   | スペーサ       |    |

| 8 8 7   | 配向膜        |    |

| 8 8 8   | 対向電極       | 40 |

| 8 8 9   | カラーフィルター   |    |

| 8 9 0   | 基板         |    |

| 8 9 1   | 偏光板        |    |

| 8 9 2   | 偏光板        |    |

| 1 2 1 0 | 発光素子       |    |

| 1 2 1 2 | 画素電極       |    |

| 1 2 1 4 | 有機化合物層     |    |

| 1 2 1 6 | 対向電極       |    |

| 1 2 1 8 | 隔壁層        |    |

| 1 2 2 0 | 空間         | 50 |

|         |                                                       |    |

|---------|-------------------------------------------------------|----|

| 1 2 3 0 | マイクロカプセル                                              |    |

| 1 2 3 2 | 画素電極                                                  |    |

| 1 2 3 4 | 対向電極                                                  |    |

| 1 2 3 6 | バインダ                                                  |    |

| 1 2 4 0 | 電気泳動層                                                 |    |

| 1 4 0 0 | 基板                                                    |    |

| 1 4 0 1 | 画素部                                                   |    |

| 1 4 0 2 | 画素                                                    |    |

| 1 4 0 3 | 走査線側入力端子                                              | 10 |

| 1 4 0 4 | 信号線側入力端子                                              |    |

| 1 4 5 0 | F P C ( F l e x i b l e P r i n t e d C i r c u i t ) |    |

| 1 4 5 1 | I C                                                   |    |

| 1 4 6 0 | 駆動回路                                                  |    |

| 2 0 0 1 | 筐体                                                    |    |

| 2 0 0 2 | 支持台                                                   |    |

| 2 0 0 3 | 表示部                                                   |    |

| 2 0 0 4 | スピーカー部                                                |    |

| 2 0 0 5 | ビデオ入力端子                                               |    |

| 2 1 0 1 | 本体                                                    |    |

| 2 1 0 2 | 表示部                                                   | 20 |

| 2 1 0 3 | 受像部                                                   |    |

| 2 1 0 4 | 操作キー                                                  |    |

| 2 1 0 5 | 外部接続ポート                                               |    |

| 2 1 0 6 | シャッターボタン                                              |    |

| 2 2 0 1 | 本体                                                    |    |

| 2 2 0 2 | 筐体                                                    |    |

| 2 2 0 3 | 表示部                                                   |    |

| 2 2 0 4 | キー ボード                                                |    |

| 2 2 0 5 | 外部接続ポート                                               |    |

| 2 2 0 6 | ポインティングデバイス                                           | 30 |

| 2 3 0 1 | 本体                                                    |    |

| 2 3 0 2 | 表示部                                                   |    |

| 2 3 0 3 | スイッチ                                                  |    |

| 2 3 0 4 | 操作キー                                                  |    |

| 2 3 0 5 | 赤外線ポート                                                |    |

| 2 4 0 1 | 本体                                                    |    |

| 2 4 0 2 | 筐体                                                    |    |

| 2 4 0 3 | 表示部 A                                                 |    |

| 2 4 0 4 | 表示部 B                                                 |    |

| 2 4 0 5 | 記録媒体読み込み部                                             | 40 |

| 2 4 0 6 | 操作キー                                                  |    |

| 2 4 0 7 | スピーカー部                                                |    |

| 2 5 0 1 | 本体                                                    |    |

| 2 5 0 2 | 表示部                                                   |    |

| 2 5 0 3 | 操作キー                                                  |    |

| 2 6 0 1 | 本体                                                    |    |

| 2 6 0 2 | 表示部                                                   |    |

| 2 6 0 3 | 筐体                                                    |    |

| 2 6 0 4 | 外部接続ポート                                               |    |

| 2 6 0 5 | リモコン受信部                                               | 50 |

|         |         |

|---------|---------|

| 2 6 0 6 | 受像部     |

| 2 6 0 7 | バッテリー   |

| 2 6 0 8 | 音声入力部   |

| 2 6 0 9 | 操作キー    |

| 2 6 1 0 | 接眼部     |

| 2 7 0 1 | 本体      |

| 2 7 0 2 | 筐体      |

| 2 7 0 3 | 表示部     |

| 2 7 0 4 | 音声入力部   |

| 2 7 0 5 | 音声出力部   |

| 2 7 0 6 | 操作キー    |

| 2 7 0 7 | 外部接続ポート |

| 2 7 0 8 | アンテナ    |

10

【図 1】

(A)

(B)

【図 2】

(A)

(B)

【図3】

(A)

(B)

【図4】

(A)

(B)

(C)

【図5】

(A)

(B)

(C)

【図6】

(A)

(B)

(C)

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

---

フロントページの続き

(56)参考文献 国際公開第2007/029389 (WO, A1)

特開2003-282885 (JP, A)

特開2001-203340 (JP, A)

特開平07-321338 (JP, A)

特開2000-077287 (JP, A)

特開平08-255762 (JP, A)

特開2005-203596 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/02

H01L 21/336

H01L 27/12

H01L 29/786