(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6140551号

(P6140551)

(45) 発行日 平成29年5月31日(2017.5.31)

(24) 登録日 平成29年5月12日(2017.5.12)

(51) Int.Cl.

F 1

|              |           |      |       |      |

|--------------|-----------|------|-------|------|

| HO1L 29/786  | (2006.01) | HO1L | 29/78 | 619A |

| HO1L 21/336  | (2006.01) | HO1L | 29/78 | 618B |

| HO1L 21/28   | (2006.01) | HO1L | 29/78 | 616V |

| HO1L 29/417  | (2006.01) | HO1L | 29/78 | 627F |

| HO1L 21/8244 | (2006.01) | HO1L | 21/28 | 301B |

請求項の数 5 (全 44 頁) 最終頁に続く

(21) 出願番号

特願2013-134515 (P2013-134515)

(22) 出願日

平成25年6月27日(2013.6.27)

(65) 公開番号

特開2014-30000 (P2014-30000A)

(43) 公開日

平成26年2月13日(2014.2.13)

審査請求日

平成28年6月14日(2016.6.14)

(31) 優先権主張番号

特願2012-147633 (P2012-147633)

(32) 優先日

平成24年6月29日(2012.6.29)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 岡崎 健一

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

(72) 発明者 肥塚 純一

栃木県栃木市都賀町升塚161-2 アド

バンスト フィルム ディバイス インク

株式会社内

最終頁に続く

(54) 【発明の名称】 半導体装置

## (57) 【特許請求の範囲】

## 【請求項1】

酸化物半導体膜と、

前記酸化物半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

前記酸化物半導体膜上、前記ゲート絶縁膜上および前記ゲート電極層上にあり、前記酸化物半導体膜に達する開口部を有する窒化シリコン膜と、

前記窒化シリコン膜上にあり、前記開口部を介して前記酸化物半導体膜と接するソース電極層およびドレイン電極層と、を有し、

前記窒化シリコン膜は、昇温脱離ガス分光法において500以下では水素分子の脱離量のピークを現さない半導体装置。 10

## 【請求項2】

酸化物半導体膜と、

前記酸化物半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

前記酸化物半導体膜上、前記ゲート絶縁膜上および前記ゲート電極層上にあり、前記酸化物半導体膜に達する開口部を有する窒化シリコン膜と、

前記窒化シリコン膜上にあり、前記開口部を介して前記酸化物半導体膜と接するソース電極層およびドレイン電極層と、を有し、

前記窒化シリコン膜は、昇温脱離ガス分光法において550以下では水素分子の脱離 20

量が  $1.5 \times 10^{20}$  個 /  $\text{cm}^3$  以下である半導体装置。

**【請求項 3】**

酸化物半導体膜と、

前記酸化物半導体膜上のゲート絶縁膜と、

前記ゲート絶縁膜上のゲート電極層と、

前記酸化物半導体膜上、前記ゲート絶縁膜上および前記ゲート電極層上にあり、前記酸化物半導体膜に達する開口部を有する窒化シリコン膜と、

前記窒化シリコン膜上にあり、前記開口部を介して前記酸化物半導体膜と接するソース電極層およびドレイン電極層と、を有し、

前記窒化シリコン膜は、昇温脱離ガス分光法において、水素分子の脱離量が  $1.0 \times 10^{20}$  個 /  $\text{cm}^3$  以上となる温度が 500 以上である半導体装置。 10

**【請求項 4】**

請求項 1 乃至 請求項 3 のいずれか一項において、

前記酸化物半導体膜が、c 軸の向きが表面に対して概略垂直である結晶を含む半導体装置。

**【請求項 5】**

請求項 1 乃至 請求項 4 のいずれか一項において、

前記酸化物半導体膜が、前記ソース電極層および前記ドレイン電極層と接する領域にリンまたはホウ素を含む半導体装置。

**【発明の詳細な説明】**

20

**【技術分野】**

**【0001】**

本発明の一態様は、半導体装置および半導体装置の作製方法に関する。

**【0002】**

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能する機器全般を指す。例えば、電気光学装置、半導体回路、および電子機器は全て半導体装置である。

**【背景技術】**

**【0003】**

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ（薄膜トランジスタ（TFT）ともいう）を構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン膜が広く知られているが、その他の材料として酸化物半導体膜が注目されている。 30

**【0004】**

トランジスタを含む半導体装置の高性能化に伴い、酸化物半導体膜を含むトランジスタにおいても、オン特性を向上させ、高速駆動を可能とすることが求められている。そこで、窒素を注入することで酸化物半導体膜の抵抗を低減し、その結果酸化物半導体膜と、ソース電極層およびドレイン電極層とのコンタクト抵抗が低減することによって、トランジスタのオン特性を向上させる方法が知られている。 40

**【0005】**

例えば、特許文献 1 には、亜鉛とインジウムと酸素を含有するアモルファス酸化物半導体膜を用い、酸化物半導体膜にイオン注入法によって窒素を含有させることで抵抗を低減し、窒素が含有された部位をソース部位またはドレイン部位とし、窒素が含有されていない部位をチャンネル部位とする電界効果型トランジスタが開示されている。

**【先行技術文献】**

**【特許文献】**

**【0006】**

【特許文献 1】特開 2010 - 93070 号公報

**【発明の概要】**

50

**【発明が解決しようとする課題】**

**【0007】**

ところで、酸化物半導体膜を用いたトランジスタは、酸化物半導体膜に水素、水分等の意図しない不純物が混入することによってキャリアが形成され、トランジスタの電気特性が変動するという問題がある。

**【0008】**

そこで、本発明の一態様は、酸化物半導体膜を用いたトランジスタのオン特性の向上および高速駆動を実現し、かつ、トランジスタに安定した電気的特性を付与して信頼性を向上させることを目的の一とする。または、酸化物半導体膜を用いたトランジスタのオン特性を向上させることを目的の一とする。または、トランジスタに安定した電気的特性を付与して信頼性を向上させることを目的の一とする。または、半導体装置を、工程を複雑化させずに作製することを目的の一とする。

10

**【課題を解決するための手段】**

**【0009】**

酸化物半導体膜と、ゲート絶縁膜と、ゲート電極層と、窒化シリコン膜とが、順に積層され、酸化物半導体膜にチャネル形成領域を有するトップゲート構造のトランジスタにおいて、酸化物半導体膜上に、酸化物半導体膜と接する窒化シリコン膜を有することで、酸化物半導体膜の一部の領域に窒素が添加され、当該領域が低抵抗領域となる。ソース電極層およびドレイン電極層は、酸化物半導体膜の低抵抗領域と接する。酸化物半導体膜の窒化シリコン膜と接していない領域（言い換えれば、ゲート絶縁膜およびゲート電極層と重畠する領域）はチャネル形成領域となる。

20

**【0010】**

したがって、本発明の一態様は、チャネル形成領域およびチャネル形成領域を挟み、窒素が含有されている一対の低抵抗領域を含む酸化物半導体膜と、チャネル形成領域上のゲート絶縁膜およびゲート電極層の積層と、低抵抗領域に接する、窒化シリコン膜と、一対の低抵抗領域のそれぞれと電気的に接続するソース電極層およびドレイン電極層と、を有し、窒化シリコン膜は、昇温脱離ガス分光法において 500 以下では水素分子の脱離量のピークを現さない半導体装置である。

**【0011】**

または、本発明の一態様は、例えば、酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜上のゲート電極層と、酸化物半導体膜上、ゲート絶縁膜上およびゲート電極層上にあり、酸化物半導体膜に達する開口部を有する窒化シリコン膜と、窒化シリコン膜上にあり、開口部を介して酸化物半導体膜と接するソース電極層およびドレイン電極層と、を有し、窒化シリコン膜は、昇温脱離ガス分光法において 500 以下では水素分子の脱離量のピークを現さない半導体装置である。

30

**【0012】**

また、該窒化シリコン膜は昇温脱離ガス分光法において 550 以下では水素分子の脱離量が  $1.5 \times 10^{20}$  個 /  $\text{cm}^3$  以下、好ましくは  $1.0 \times 10^{20}$  個 /  $\text{cm}^3$  以下、より好ましくは  $7.5 \times 10^{19}$  個 /  $\text{cm}^3$  以下とする。また、昇温脱離ガス分光法において 500 以下では水素分子の脱離量のピークを現さず、昇温脱離ガス分光法では水素分子の脱離量が  $1.0 \times 10^{20}$  個 /  $\text{cm}^3$  以上となる温度が 500 以上、より好ましくは 550 以上とする。

40

**【0013】**

チャネル形成領域および低抵抗領域は、表面に対して概略垂直な c 軸を有する結晶を含む領域とすることができます。また、チャネル形成領域は表面に対して概略垂直な c 軸を有する結晶を含む領域とし、低抵抗領域は非晶質領域としてもよい。

**【0014】**

窒化シリコン膜は、酸化物半導体膜、ゲート絶縁膜およびゲート電極層上を覆う層間絶縁膜としてもよい。また、窒化シリコン膜をゲート絶縁膜およびゲート電極層の側面と接する側壁絶縁膜としてもよい。

50

## 【0015】

また、本発明の一態様は、酸化物半導体膜は、ゲート電極層と重畠するチャネル形成領域と、側壁絶縁膜と重畠し、チャネル形成領域を挟み、窒素が含有されている一対の第1の低抵抗領域と、チャネル形成領域および第1の低抵抗領域を挟み、不純物元素が含有されており、ソース電極層およびドレイン電極層とそれぞれ接する一対の第2の低抵抗領域と、を有し、不純物元素は、リンまたはホウ素であり、第2の低抵抗領域の抵抗は第1の低抵抗領域よりも低い半導体装置である。

## 【0016】

また、酸化物半導体膜はc軸の向きが表面に対して概略垂直である結晶を含む領域とし、第2の低抵抗領域は非晶質領域とすることができます。

10

## 【0017】

また、本発明の別の一態様は、酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極層を形成し、ゲート電極層をマスクとしてゲート絶縁膜をエッチングして、酸化物半導体膜の一部を露出させ、露出させた酸化物半導体膜の一部に接して、昇温脱離ガス分光法において500以下では水素分子の脱離量のピークを現さない窒化シリコン膜を成膜することで、酸化物半導体膜の窒化シリコン膜と接する領域に窒素を添加して、低抵抗領域を形成し、低抵抗領域と電気的に接続するソース電極層またはドレイン電極層を形成し、窒化シリコン膜の成膜ガスとしてシランおよび窒素を含む混合ガスを用いる半導体装置の作製方法である。

## 【0018】

20

また、本発明の別の一態様は、酸化物半導体膜を形成し、酸化物半導体膜上にゲート絶縁膜を形成し、ゲート絶縁膜上にゲート電極層を形成し、ゲート電極層をマスクとしてゲート絶縁膜をエッチングして、酸化物半導体膜の一部を露出させ、露出させた酸化物半導体膜の一部に接して、昇温脱離ガス分光法において500以下では水素分子の脱離量のピークを現さない窒化シリコン膜を成膜することで、酸化物半導体膜の窒化シリコン膜と接する領域に窒素を添加して、低抵抗領域を形成し、低抵抗領域と電気的に接続するソース電極層またはドレイン電極層を形成し、窒化シリコン膜の成膜ガスとしてシラン、窒素およびアンモニアを含み、成膜ガス中の窒素に対するアンモニアの流量比が0.1倍以下である半導体装置の作製方法である。

## 【0019】

30

本発明の一態様は、酸化物半導体膜を形成し、酸化物半導体膜上に絶縁膜を成膜し、絶縁膜上に導電膜を成膜し、導電膜および絶縁膜を加工することで、ゲート電極層およびゲート絶縁膜を形成し、酸化物半導体膜上、ゲート絶縁膜上およびゲート電極層上に窒化シリコン膜を成膜することで、酸化物半導体膜の窒化シリコン膜と接する領域に窒素を添加して、低抵抗領域を形成し、窒化シリコン膜の一部をエッチングすることで、酸化物半導体膜に達する開口部を形成し、酸化物半導体膜上および窒化シリコン膜上にソース電極層またはドレイン電極層を形成し、窒化シリコン膜は、シラン、窒素およびアンモニアを含む成膜ガスを用い、成膜ガス中の窒素に対するアンモニアの流量比が0.1倍以下である半導体装置の作製方法である。

## 【0020】

40

また、ゲート電極層の形成後、ゲート電極層をマスクとして酸化物半導体膜に不純物元素として、リンまたはホウ素などを添加してもよい。

## 【0021】

窒化シリコン膜をエッチングすることで、ゲート電極層の側面に接する側壁絶縁膜を形成し、ゲート電極層および側壁絶縁膜をマスクとして酸化物半導体膜に不純物元素として、リンまたはホウ素などを添加してもよい。

## 【0022】

また、窒化シリコン膜の形成後に、加熱処理を行ってもよい。

## 【発明の効果】

## 【0023】

50

本発明の一態様によって、酸化物半導体膜を用いたトランジスタのオン特性を向上させることができる。または、酸化物半導体を用いたトランジスタに安定した電気的特性を付与し、信頼性を向上させることができる。また、半導体装置を、工程を複雑化させずに作製することができる。

**【図面の簡単な説明】**

**【0024】**

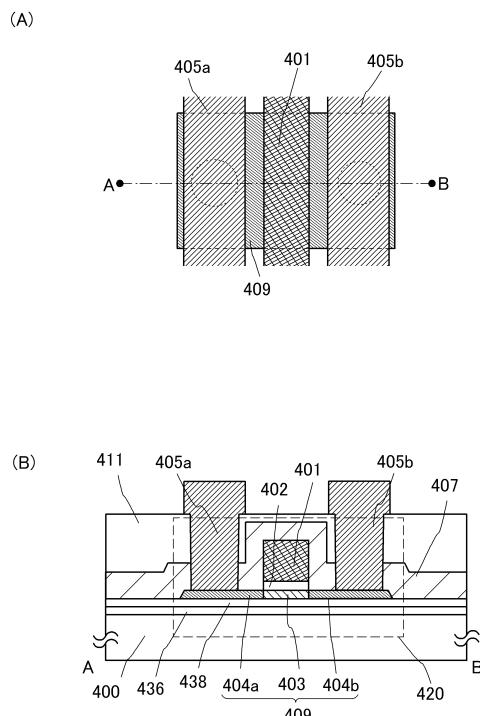

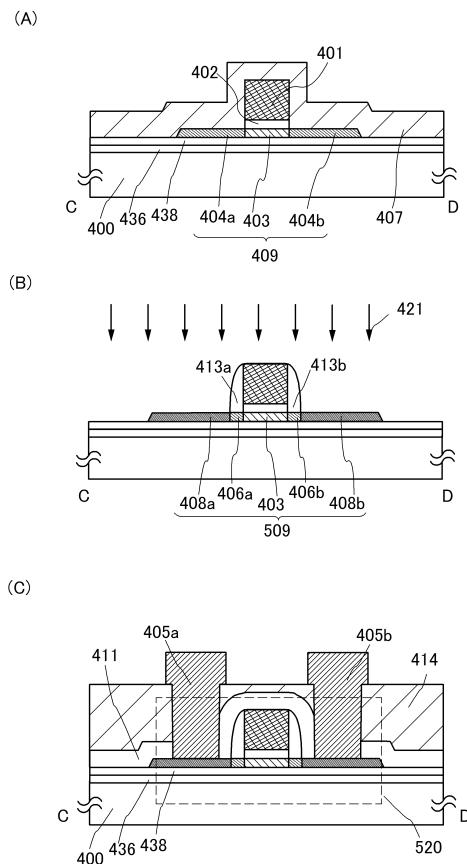

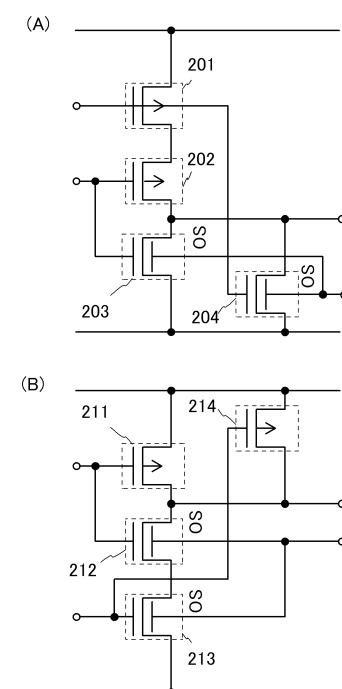

【図1】本発明の一態様の半導体装置の上面図および断面図。

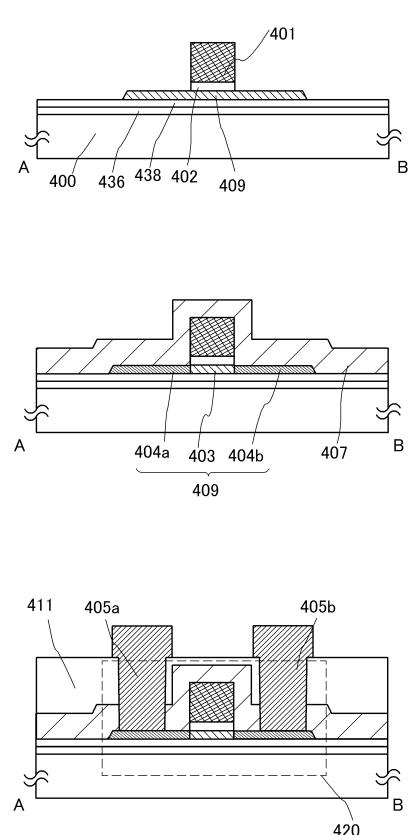

【図2】本発明の一態様の半導体装置の作製方法を説明する図。

【図3】本発明の一態様の半導体装置の断面図。

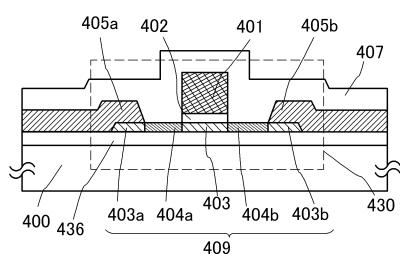

【図4】本発明の一態様の半導体装置の上面図および断面図。

10

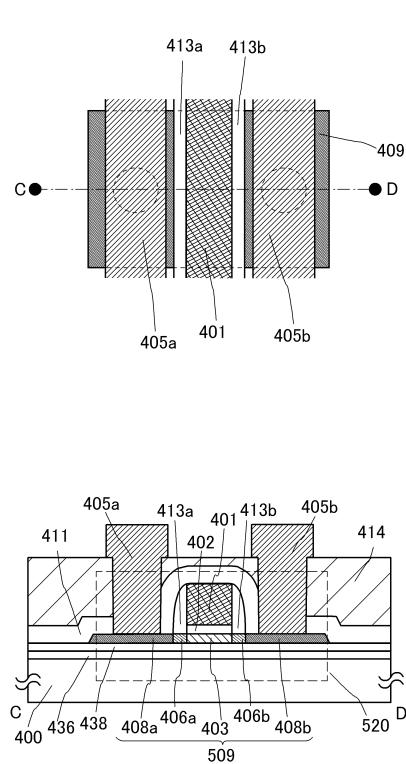

【図5】本発明の一態様の半導体装置の作製方法を説明する図。

【図6】本発明の一態様の半導体装置の断面図。

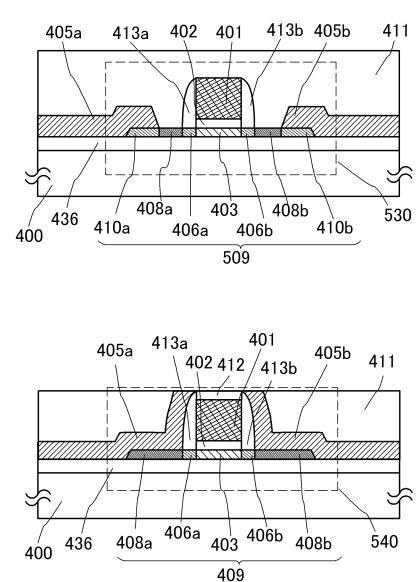

【図7】本発明の一態様の半導体装置の断面図。

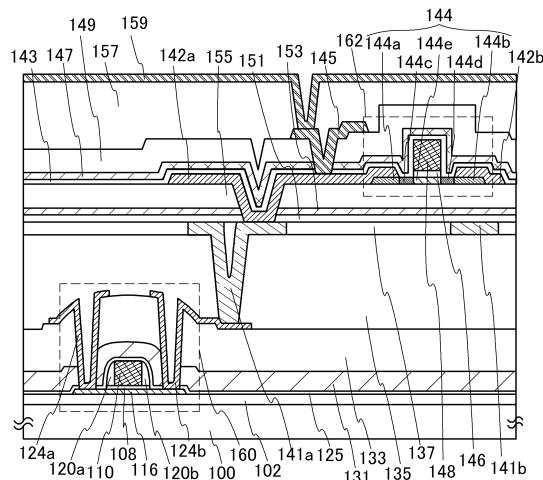

【図8】本発明の一態様の半導体装置の回路図。

【図9】本発明の一態様の半導体装置の回路図および斜視図。

【図10】本発明の一態様の半導体装置の断面図。

【図11】本発明の一態様の半導体装置の回路図。

【図12】本発明の一態様の半導体装置のブロック図。

【図13】本発明の一態様の半導体装置のブロック図。

【図14】本発明の一態様の半導体装置のブロック図。

20

【図15】本発明の一態様の電子機器を説明する図。

【図16】実施例1のTDSの結果を示す図。

【図17】実施例1のSIMSおよびRBS分析結果を示す図。

【図18】実施例2のTDSの結果を示す図。

**【発明を実施するための形態】**

**【0025】**

以下では、本発明の実施の形態について図面を用いて詳細に説明する。ただし、本発明は以下の説明に限定されず、その形態および詳細を様々に変更しうることは、当業者であれば容易に理解される。また、本発明は以下に示す実施の形態の記載内容に限定して解釈されるものではない。

30

**【0026】**

以下に説明する実施の形態において、同じものを指す符号は異なる図面間で共通して用いる場合がある。なお、図面において示す構成要素、すなわち層や領域等の厚さ、幅、相対的な位置関係等は、実施の形態において説明する上で明確性のため、誇張して示される場合がある。

**【0027】**

なお、本明細書等において「上」という用語は、構成要素の位置関係が「直上」であることを限定するものではない。例えば、「絶縁膜上のゲート電極層」の表現であれば、絶縁膜とゲート電極層との間に他の構成要素を含むものを除外しない。「下」についても同様である。

40

**【0028】**

また、本明細書等において「電極層」や「配線層」という用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極層」は「配線層」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極層」や「配線層」という用語は、複数の「電極層」や「配線層」が一体となって形成されている場合なども含む。

**【0029】**

また、「ソース」や「ドレイン」の機能は、異なる極性のトランジスタを採用する場合や、回路動作において電流の方向が変化する場合などには入れ替わることがある。このため、本明細書においては、「ソース」や「ドレイン」という用語は、入れ替えて用いることができるものとする。

50

## 【0030】

なお、本明細書等において、「電気的に接続」には、「何らかの電気的作用を有するもの」を介して接続されている場合が含まれる。ここで、「何らかの電気的作用を有するもの」は、接続対象間での電気信号の授受を可能とするものであれば、特に制限を受けない。

## 【0031】

例えば、「何らかの電気的作用を有するもの」には、電極や配線などが含まれる。

## 【0032】

## (実施の形態1)

本実施の形態では、本発明の一態様の半導体装置について図面を用いて詳細に説明する。

図1に本発明の一態様の半導体装置である、トランジスタ420の上面図および断面図を示す。図1(A)はトランジスタ420の上面図を示し、図1(B)は図1(A)に示す一点鎖線A-Bにおける断面図を示したものである。

10

## 【0033】

図1に示すトランジスタ420は、基板400上に設けられた下地絶縁膜436と、下地絶縁膜436上に設けられ、チャネル形成領域403、低抵抗領域404aおよび低抵抗領域404bを含む酸化物半導体膜409と、チャネル形成領域403上に設けられたゲート絶縁膜402およびゲート電極層401と、酸化物半導体膜409、ゲート絶縁膜402およびゲート電極層401上の窒化シリコン膜407と、窒化シリコン膜407上の層間絶縁膜411と、窒化シリコン膜407および層間絶縁膜411に設けられた開口部において、低抵抗領域404aおよび低抵抗領域404bとそれぞれ電気的に接続するソース電極層405aおよびドレイン電極層405bとを有する。

20

## 【0034】

窒化シリコン膜407は、酸化物半導体膜と接して形成されるため、膜中の水素濃度がなるべく低減されており、水素分子の脱離量が低減されている膜であることが好ましい。例えば、昇温脱離ガス分光法(TDS: Thermal Desorption Spectroscopy)による測定によって、500以下では水素分子の脱離量のピークを現さないとよい。また、TDSにおいて、水素分子の脱離量が、例えば、500以下では $1.5 \times 10^{20}$ 個/cm<sup>3</sup>以下、好ましくは $1.0 \times 10^{20}$ 個/cm<sup>3</sup>以下、より好ましくは $7.5 \times 10^{19}$ 個/cm<sup>3</sup>以下であるとよい。または、水素分子の脱離量が $1.0 \times 10^{20}$ 個/cm<sup>3</sup>以上となる温度が500以上、より好ましくは550以上であるとよい。

30

## 【0035】

また、窒化シリコン膜中の水素濃度としては、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)において、 $2.0 \times 10^{22}$ atoms/cm<sup>3</sup>以下、好ましくは、 $1.5 \times 10^{22}$ atoms/cm<sup>3</sup>以下であるとよい。

30

## 【0036】

また、窒化シリコン膜中の組成をラザフォード後方散乱法(RBS: Rutherford Backscattering Spectrometry)を用いて測定した場合、水素濃度が15atomic%以下、好ましくは10atomic%以下であるとよい。

40

## 【0037】

酸化物半導体膜409上に窒化シリコン膜407を接して成膜することで、酸化物半導体膜409の窒化シリコン膜と接する領域に窒素を添加し、抵抗の低減された領域(低抵抗領域404aおよび低抵抗領域404b)を形成する。低抵抗領域404aおよび低抵抗領域404bはチャネル形成領域403よりも電気的抵抗が低い領域である。

## 【0038】

また、酸化物半導体膜409は、c軸の向きが表面に対して概略垂直である結晶を含む、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductorともいう。)膜を用いることが好ましい。本実施の形態で

50

は、酸化物半導体膜 409 として C A A C - O S 膜を用いる。

**【0039】**

本実施の形態では、窒化シリコン膜 407 の成膜工程において、酸化物半導体膜 409 へ窒素を添加し低抵抗領域 404a および低抵抗領域 404b を形成するため、低抵抗領域 404a および低抵抗領域 404b においても C A A C - O S 膜としての結晶性を維持することができる。よって、本実施の形態における酸化物半導体膜 409 においては、チャネル形成領域 403、低抵抗領域 404a、および低抵抗領域 404b は、c 軸の向きが表面に対して概略垂直である結晶を含む。

**【0040】**

トランジスタ 420 は、酸化物半導体膜 409 の抵抗が低い領域において、酸化物半導体膜 409 とソース電極層 405a およびドレイン電極層 405b が接しているため、酸化物半導体膜 409 とソース電極層 405a およびドレイン電極層 405b とのコンタクト抵抗が低減されている。したがって、トランジスタ 420 はオン特性（例えばオン電流や電界効果移動度）が高く、高速動作、高速応答が可能な半導体装置とすることができる。

10

**【0041】**

また、層間絶縁膜として機能する窒化シリコン膜 407 の成膜工程において、酸化物半導体膜 409 に窒素を添加し、低抵抗領域 404a および低抵抗領域 404b を形成することができるため、工程を複雑化されることなくトランジスタ 420 のオン特性を向上させることができる。

**【0042】**

20

続いて、トランジスタ 420 の作製方法について図 2 を用いて説明する。

**【0043】**

まず、基板 400 上に下地絶縁膜 436 および下地絶縁膜 438 を成膜する。

**【0044】**

使用できる基板に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えばバリウムホウケイ酸ガラスやアルミニウムホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。

**【0045】**

また、基板 400 としてシリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板等を用いてもよい。また、S O I 基板、半導体基板上に半導体素子が設けられたものなどを用いることができる。

30

**【0046】**

下地絶縁膜 436 および下地絶縁膜 438 は、スパッタリング法、M B E ( M o l e c u l a r B e a m E p i t a x y ) 法、C V D ( C h e m i c a l V a p o r D e p o s i t i o n ) 、パルスレーザ堆積 ( P u l s e d L a s e r D e p o s i t i o n : P L D ) 法、A L D ( A t o m i c L a y e r D e p o s i t i o n ) 法等を適宜用いることができる。なお、下地絶縁膜 438 をスパッタリング法を用いて形成すると、水素等の不純物元素を低減することができ、後に形成される酸化物半導体膜に水素が混入することを防止することができる。

40

**【0047】**

下地絶縁膜 436 および下地絶縁膜 438 としては、無機絶縁膜を用いればよい。例えば、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、または酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜等を用いるとよい。また、これらの化合物を単層構造または 2 層以上の積層構造で形成して用いることができる。また、下地絶縁膜 436 および下地絶縁膜 438 は、同じ材料を用いた膜であってもよいし、異なる材料を用いた膜であってもよい。

**【0048】**

なお、ここで酸化窒化シリコンとは、その組成において窒素よりも酸素の含有量が多いも

50

のを示し、例として、少なくとも酸素が 50 atomic %以上 70 atomic %以下、窒素が 0.5 atomic %以上 15 atomic %以下、シリコンが 25 atomic %以上 35 atomic %以下の範囲で含まれるものという。但し、上記範囲は、ラザフォード後方散乱法や、水素前方散乱法 (HFS : Hydrogen Forward Scattering) を用いて測定した場合のものである。また、構成元素の含有比率は、その合計が 100 atomic %を超えない値をとる。

#### 【0049】

トランジスタ 420において、下地絶縁膜 436 が、基板 400 から後に形成される酸化物半導体膜 409 へ水素、水分等の不純物が混入することを防止する機能を有すると好ましい。したがって、下地絶縁膜 436 としては、窒化シリコン膜、酸化アルミニウム膜、酸化窒化シリコン膜、窒化アルミニウム膜、窒化酸化アルミニウム膜、などの無機絶縁膜を好適に用いることができる。特に、水素、水分などの不純物、および酸素の両方に対して遮断効果（ブロック効果）が高い窒化シリコン膜は好適である。10

#### 【0050】

下地絶縁膜 438 は、後に形成される酸化物半導体膜 409 と接するため、層中（バルク中）に少なくとも化学量論的組成を超える量の酸素が存在することが好ましい。例えば、下地絶縁膜 438 として、酸化シリコン膜を用いる場合には、 $\text{SiO}_{(2+\delta)}$ （ただし、 $\delta > 0$ ）とする。

#### 【0051】

また、後に形成される酸化物半導体膜 409 の平坦性を高めるために、下地絶縁膜 438 に平坦化処理を行ってもよい。平坦化処理としては、例えば、化学的機械的研磨（Chemical Mechanical Polishing : CMP）処理、ドライエッチング処理などを行えばよい。ここで、エッチングガスとしては、塩素、塩化ホウ素、塩化シリコンまたは四塩化炭素などの塩素系ガス、四フッ化炭素、フッ化硫黄またはフッ化窒素などのフッ素系ガスなどを用いればよい。20

#### 【0052】

なお、基板 400 と後に設ける酸化物半導体膜 409 との絶縁性が確保できるようであれば、下地絶縁膜を設けない構成とすることもできる。

#### 【0053】

本実施の形態では、下地絶縁膜 436 として、窒化シリコン膜を用い、下地絶縁膜 438 として酸化シリコン膜を用いる。30

#### 【0054】

続いて、下地絶縁膜 438 上に酸化物半導体膜 409 となる酸化物半導体膜を形成する。

#### 【0055】

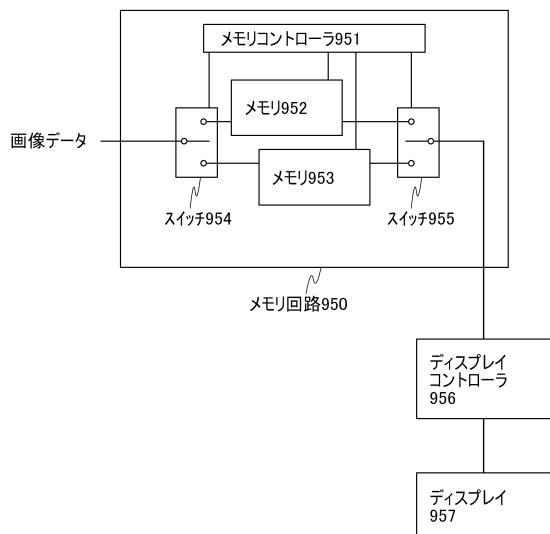

酸化物半導体膜は、少なくともインジウム (In) または亜鉛 (Zn) を含むことが好ましい。または、In と Zn の双方を含むことが好ましい。また、該酸化物半導体膜を用いたトランジスタの電気特性のばらつきを減らすため、それらと共に、スタビライザーの一または複数を有することが好ましい。

#### 【0056】

スタビライザーとしては、ガリウム (Ga)、スズ (Sn)、ハフニウム (Hf)、アルミニウム (Al)、またはジルコニウム (Zr) 等がある。また、他のスタビライザーとしては、ランタノイドである、ラントン (La)、セリウム (Ce)、プラセオジム (Pr)、ネオジム (Nd)、サマリウム (Sm)、ユウロピウム (Eu)、ガドリニウム (Gd)、テルビウム (Tb)、ジスプロシウム (Dy)、ホルミウム (Ho)、エルビウム (Er)、ツリウム (Tm)、イッテルビウム (Yb)、ルテチウム (Lu) 等がある。40

#### 【0057】

例えば、酸化物半導体として、単元系金属の酸化物である酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物である In-Zn 酸化物、Sn-Zn 酸化物、Al-Zn 酸化物、Zn-Mg 酸化物、Sn-Mg 酸化物、In-Mg 酸化物、In-Ga 酸化物、三50

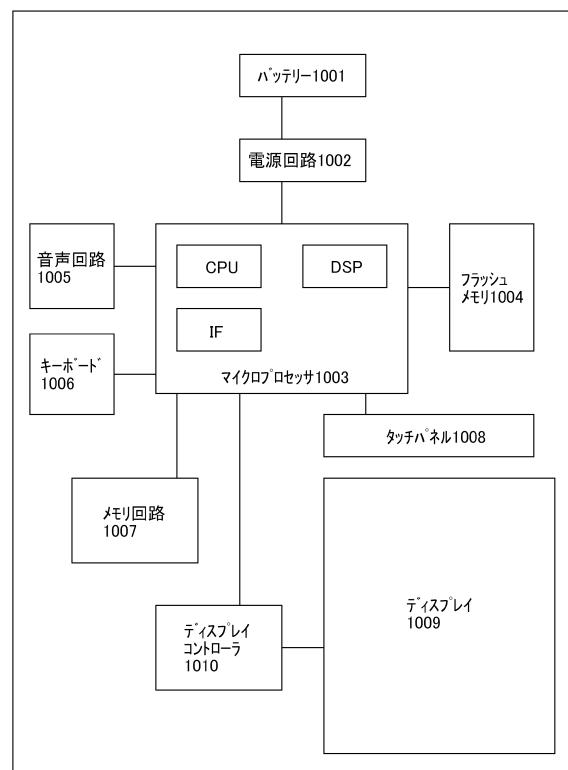

元系金属の酸化物である In - Ga - Zn 酸化物、In - Al - Zn 酸化物、In - Sn - Zn 酸化物、Sn - Ga - Zn 酸化物、Al - Ga - Zn 酸化物、Sn - Al - Zn 酸化物、In - Hf - Zn 酸化物、In - La - Zn 酸化物、In - Ce - Zn 酸化物、In - Pr - Zn 酸化物、In - Nd - Zn 酸化物、In - Sm - Zn 酸化物、In - Eu - Zn 酸化物、In - Gd - Zn 酸化物、In - Tb - Zn 酸化物、In - Dy - Zn 酸化物、In - Ho - Zn 酸化物、In - Er - Zn 酸化物、In - Tm - Zn 酸化物、In - Yb - Zn 酸化物、In - Lu - Zn 酸化物、四元系金属の酸化物である In - Sn - Ga - Zn 酸化物、In - Hf - Ga - Zn 酸化物、In - Al - Ga - Zn 酸化物、In - Sn - Al - Zn 酸化物、In - Sn - Hf - Zn 酸化物、In - Hf - Al - Zn 酸化物を用いることができる。

10

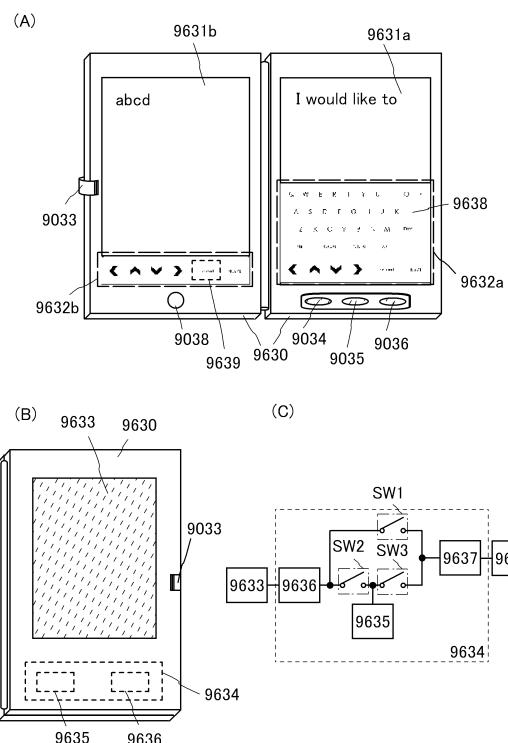

#### 【0058】

なお、ここで、例えば、In - Ga - Zn 酸化物とは、In と Ga と Zn を主成分として有する酸化物という意味であり、In と Ga と Zn の比率は問わない。また、In と Ga と Zn 以外の金属元素が入っていてもよい。

#### 【0059】

また、酸化物半導体として、 $InMO_3 (ZnO)_m$  ( $m > 0$ 、かつ、 $m$  は整数でない) で表記される材料を用いてもよい。なお、M は、Ga、Fe、Mn および Co から選ばれた一の金属元素または複数の金属元素を示す。また、酸化物半導体として、 $In_2SnO_5 (ZnO)_n$  ( $n > 0$ 、かつ、 $n$  は整数) で表記される材料を用いてもよい。

20

#### 【0060】

例えば、 $In : Ga : Zn = 1 : 1 : 1$ 、 $In : Ga : Zn = 2 : 2 : 1$ 、または  $In : Ga : Zn = 3 : 1 : 2$  の原子数比の In - Ga - Zn 酸化物やその組成の近傍の酸化物を用いることができる。または、 $In : Sn : Zn = 1 : 1 : 1$ 、 $In : Sn : Zn = 2 : 1 : 3$  または  $In : Sn : Zn = 2 : 1 : 5$  の原子数比の In - Sn - Zn 酸化物やその組成の近傍の酸化物を用いるとよい。

#### 【0061】

しかし、これらに限られず、必要とする半導体特性および電気特性（電界効果移動度、しきい値電圧、ばらつき等）に応じて適切な組成のものを用いればよい。また、必要とする半導体特性を得るために、キャリア密度や不純物濃度、欠陥密度、金属元素と酸素の原子数比、原子間距離、密度等を適切なものとすることが好ましい。

30

#### 【0062】

例えば、In - Sn - Zn 酸化物では比較的容易に高いキャリア移動度が得られる。しかしながら、In - Ga - Zn 酸化物でも、バルク内欠陥密度を低くすることによりキャリア移動度を上げることができる。

#### 【0063】

また、本実施の形態に用いる酸化物半導体膜としては、エネルギーギャップが 2 eV 以上、好ましくは 2.5 eV 以上、より好ましくは 3 eV 以上である酸化物半導体膜を用いる。このように、エネルギーギャップの広い酸化物半導体膜を用いることで、トランジスタのオフ電流を低減することができる。

40

#### 【0064】

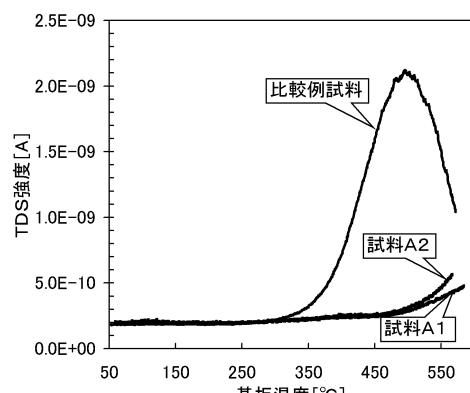

以下では、酸化物半導体膜の構造について説明する。

#### 【0065】

なお、本明細書において、「平行」とは、二つの直線が  $-10^\circ$  以上  $10^\circ$  以下の角度で配置されている状態をいう。従って、 $-5^\circ$  以上  $5^\circ$  以下の場合も含まれる。また、「垂直」とは、二つの直線が  $80^\circ$  以上  $100^\circ$  以下の角度で配置されている状態をいう。従って、 $85^\circ$  以上  $95^\circ$  以下の場合も含まれる。

#### 【0066】

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。

#### 【0067】

50

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、C A A C - O S 膜などをいう。

#### 【0068】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

#### 【0069】

微結晶酸化物半導体膜は、例えば、1 nm以上10 nm未満の大きさの微結晶（ナノ結晶ともいう。）を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。10

#### 【0070】

C A A C - O S 膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が100 nm未満の立方体内に収まる大きさである。従って、C A A C - O S 膜に含まれる結晶部は、一辺が10 nm未満、5 nm未満または3 nm未満の立方体内に収まる大きさの場合も含まれる。C A A C - O S 膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、C A A C - O S 膜について詳細な説明を行う。20

#### 【0071】

C A A C - O S 膜を透過型電子顕微鏡（T E M : T r a n s m i s s i o n E l e c t r o n M i c r o s c o p e ）によって観察すると、結晶部同士の明確な境界、即ち結晶粒界（グレインバウンダリーともいう。）を確認することができない。そのため、C A A C - O S 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。20

#### 【0072】

C A A C - O S 膜を、試料面と概略平行な方向からT E Mによって観察（断面T E M観察）すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C A A C - O S 膜の膜を形成する面（被形成面ともいう。）または上面の凹凸を反映した形状であり、C A A C - O S 膜の被形成面または上面と平行に配列する。30

#### 【0073】

一方、C A A C - O S 膜を、試料面と概略垂直な方向からT E Mによって観察（平面T E M観察）すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。30

#### 【0074】

断面T E M観察および平面T E M観察より、C A A C - O S 膜の結晶部は配向性を有していることがわかる。

#### 【0075】

C A A C - O S 膜に対し、X線回折（X R D : X - R a y D i f f r a c t i o n ）装置を用いて構造解析を行うと、例えばInGaZnO<sub>4</sub>の結晶を有するC A A C - O S 膜のout-of-plane法による解析では、回折角（2θ）が31°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の（009）面に帰属されることから、C A A C - O S 膜の結晶がc軸配向性を有し、c軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。40

#### 【0076】

一方、C A A C - O S 膜に対し、c軸に概略垂直な方向からX線を入射させるin-plane法による解析では、2θが56°近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub>の結晶の（110）面に帰属される。InGaZnO<sub>4</sub>の単結晶酸化物半導体膜であれば、2θを56°近傍に固定し、試料面の法線ベクトルを軸（c軸）として試料を回転させながら分析（スキャン）を行うと、（110）面と等価な結晶面に50

帰属されるピークが 6 本観察される。これに対し、C A A C - O S 膜の場合は、2 を 5 6 ° 近傍に固定して スキャンした場合でも、明瞭なピークが現れない。

#### 【 0 0 7 7 】

以上のことから、C A A C - O S 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 T E M 観察で確認された層状に配列した金属原子の各層は、結晶の a b 面に平行な面である。

#### 【 0 0 7 8 】

なお、結晶部は、C A A C - O S 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、C A A C - O S 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、C A A C - O S 膜の形状をエッチングなどによって変化させた場合、結晶の c 軸が C A A C - O S 膜の被形成面または上面の法線ベクトルと平行にならないこともある。

10

#### 【 0 0 7 9 】

また、C A A C - O S 膜中の結晶化度が均一でなくてもよい。例えば、C A A C - O S 膜の結晶部が、C A A C - O S 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、C A A C - O S 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

#### 【 0 0 8 0 】

20

なお、I n G a Z n O<sub>4</sub> の結晶を有するC A A C - O S 膜の o u t - o f - p l a n e 法による解析では、2 が 3 1 ° 近傍のピークの他に、2 が 3 6 ° 近傍にもピークが現れる場合がある。2 が 3 6 ° 近傍のピークは、C A A C - O S 膜中の一部に、c 軸配向性を有さない結晶が含まれることを示している。C A A C - O S 膜は、2 が 3 1 ° 近傍にピークを示し、2 が 3 6 ° 近傍にピークを示さないことが好みしい。

#### 【 0 0 8 1 】

C A A C - O S 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

#### 【 0 0 8 2 】

30

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、C A A C - O S 膜のうち、二種以上を有する積層膜であってもよい。

#### 【 0 0 8 3 】

また、酸化物半導体膜は、複数の酸化物半導体膜が積層された構造でもよい。例えば、酸化物半導体膜を、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜の積層として、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜に、異なる組成の金属酸化物を用いてもよい。例えば、第 1 の酸化物半導体膜に二元系金属酸化物乃至四元系金属酸化物の一を用い、第 2 の酸化物半導体膜に第 1 の酸化物半導体膜と異なる二元系金属酸化物乃至四元系金属酸化物を用いてもよい。

#### 【 0 0 8 4 】

40

また、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜の構成元素を同一とし、両者の組成を異ならせててもよい。例えば、第 1 の酸化物半導体膜の原子数比を I n : G a : Z n = 1 : 1 : 1 とし、第 2 の酸化物半導体膜の原子数比を I n : G a : Z n = 3 : 1 : 2 としてもよい。また、第 1 の酸化物半導体膜の原子数比を I n : G a : Z n = 1 : 3 : 2 とし、第 2 の酸化物半導体膜の原子数比を I n : G a : Z n = 2 : 1 : 3 としてもよい。

#### 【 0 0 8 5 】

この時、第 1 の酸化物半導体膜と第 2 の酸化物半導体膜のうち、後に設けるゲート電極層 4 0 1 に近い側（チャネル側）の酸化物半導体膜の I n と G a の含有率を I n > G a とするとよい。またゲート電極層 4 0 1 から遠い側（バックチャネル側）の酸化物半導体膜の I n と G a の含有率を I n = G a とするとい。

#### 【 0 0 8 6 】

50

また、酸化物半導体膜を3層構造とし、第1の酸化物半導体膜～第3の酸化物半導体膜の構成元素を同一とし、かつそれぞれの組成を異ならせててもよい。例えば、第1の酸化物半導体膜の原子数比をIn : Ga : Zn = 1 : 3 : 2とし、第2の酸化物半導体膜の原子数比をIn : Ga : Zn = 3 : 1 : 2とし、第3の酸化物半導体膜の原子数比をIn : Ga : Zn = 1 : 1 : 1としてもよい。

#### 【0087】

GaおよびZnよりInの原子数比が小さい酸化物半導体膜、代表的には原子数比がIn : Ga : Zn = 1 : 3 : 2である第1の酸化物半導体膜は、GaおよびZnよりInの原子数比が大きい酸化物半導体膜、代表的には第2の酸化物半導体膜、ならびにGa、ZnおよびInの原子数比が同じ酸化物半導体膜、代表的には第3の酸化物半導体膜と比較して、絶縁性が高い。このため、第1の酸化物半導体膜をゲート電極層401に近い側に設け、ゲート絶縁膜として機能させてもよい。なお、原子数比がIn : Ga : Zn = 1 : 3 : 2である第1の酸化物半導体膜が非晶質構造であってもよい。

10

#### 【0088】

また、第1の酸化物半導体膜～第3の酸化物半導体膜の構成元素は同一であるため、第1の酸化物半導体膜は、第2の酸化物半導体膜との界面におけるトラップ準位が少ない。このため、酸化物半導体膜を上記構造とすることで、トランジスタの経時変化や光BTストレス試験によるしきい値電圧の変動量を低減することができる。

#### 【0089】

酸化物半導体では主として重金属のs軌道がキャリア伝導に寄与しており、Inの含有率を多くすることにより、より多くのs軌道が重なるため、原子数比がIn > Gaとなる酸化物半導体は原子数比がIn-Gaとなる酸化物半導体と比較して高いキャリア移動度を備える。また、GaはInと比較して酸素欠損の形成エネルギーが大きく酸素欠損が生じにくいため、原子数比がIn-Gaとなる酸化物半導体は原子数比がIn > Gaとなる酸化物半導体と比較して安定した特性を備える。

20

#### 【0090】

チャネル側に原子数比がIn > Gaとなる酸化物半導体を適用し、バックチャネル側に原子数比がIn-Gaとなる酸化物半導体を適用することで、トランジスタの電界効果移動度および信頼性をさらに高めることが可能となる。

#### 【0091】

また、酸化物半導体膜409を積層構造とする場合、第1の酸化物半導体膜乃至第3の酸化物半導体膜に、結晶性の異なる酸化物半導体膜を適用してもよい。すなわち、単結晶酸化物半導体膜、多結晶酸化物半導体膜、非晶質酸化物半導体膜、またはCAC-O<sub>2</sub>S膜を適宜組み合わせた構成としてもよい。また、第1の酸化物半導体膜乃至第3の酸化物半導体膜のいずれか一に非晶質酸化物半導体膜を適用すると、酸化物半導体膜の内部応力や外部からの応力を緩和し、トランジスタの特性ばらつきが低減され、また、トランジスタの信頼性をさらに高めることが可能となる。

30

#### 【0092】

酸化物半導体膜の厚さは、1nm以上100nm以下、更に好ましくは1nm以上50nm以下、更に好ましくは1nm以上30nm以下、更に好ましくは3nm以上20nm以下とすることが好ましい。

40

#### 【0093】

酸化物半導体膜において、二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)により得られるアルカリ金属またはアルカリ土類金属の濃度を、 $1 \times 10^{-8}$  atoms/cm<sup>3</sup>以下、さらに好ましくは $2 \times 10^{-6}$  atoms/cm<sup>3</sup>以下であることが望ましい。アルカリ金属およびアルカリ土類金属は、酸化物半導体と結合するとキャリアを生成する場合があり、トランジスタのオフ電流の上昇の原因となるためである。

#### 【0094】

酸化物半導体膜において、二次イオン質量分析法により得られる水素濃度を、 $1 \times 10^{-2}$

50

$^0 \text{ atoms/cm}^3$  未満、好ましくは  $5 \times 10^{19} \text{ atoms/cm}^3$  未満、さらに好ましくは  $1 \times 10^{19} \text{ atoms/cm}^3$  未満、より好ましくは  $5 \times 10^{18} \text{ atoms/cm}^3$  /  $\text{cm}^3$  未満、より好ましくは  $1 \times 10^{18} \text{ atoms/cm}^3$  以下、より好ましくは  $5 \times 10^{17} \text{ atoms/cm}^3$  以下、より好ましくは  $1 \times 10^{16} \text{ atoms/cm}^3$  以下とする。

#### 【0095】

酸化物半導体膜に含まれる水素は、金属原子と結合する酸素と反応して水となると共に、酸素が脱離した格子（または酸素が脱離した部分）には欠損が形成されてしまう。また、水素の一部が酸素と結合することで、キャリアである電子が生じてしまう。酸化物半導体膜の成膜工程において、水素を含む不純物の混入を極めて小さくすることにより、酸化物半導体膜の水素濃度を低減することが可能である。水素をできるだけ除去し、高純度化させた酸化物半導体膜をチャネル形成領域とすることにより、しきい値電圧のマイナスシフトを低減することができる。また、トランジスタのソース - ドレイン間ににおけるチャネル幅  $1 \mu\text{m}$  当たりのリーク電流（オフ電流ともいう）を数  $y \text{ A}/\mu\text{m}$  ~ 数  $z \text{ A}/\mu\text{m}$  にまで低減することが可能となる。従って、高純度化させた酸化物半導体膜を用いることにより、トランジスタの電気特性を向上させることができる。10

#### 【0096】

酸化物半導体膜はスパッタリング法、塗布法、パルスレーザ堆積法、レーザーアブレーション法等により形成する。

#### 【0097】

スパッタリング法で酸化物半導体膜を形成する場合、プラズマを発生させるための電源装置は、RF電源装置、AC電源装置、DC電源装置等を適宜用いることができる。20

#### 【0098】

スパッタリングガスは、希ガス（代表的にはアルゴン）雰囲気、酸素雰囲気、希ガスおよび酸素の混合ガスを適宜用いる。なお、希ガスおよび酸素の混合ガスの場合、希ガスに対して酸素のガス比を高めることが好ましい。

#### 【0099】

また、ターゲットは、形成する酸化物半導体膜の組成にあわせて、適宜選択すればよい。

#### 【0100】

なお、CAC-O<sub>S</sub>膜を形成する際は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa-b面から劈開し、a-b面に平行な面を有する平板状またはペレット状のスパッタ粒子として剥離することがある。この場合、当該平板状のスパッタ粒子が、結晶構造を維持したまま基板に到達することで、CAC-O<sub>S</sub>膜を成膜することができる。30

#### 【0101】

また、CAC-O<sub>S</sub>膜を成膜するために、以下の条件を適用することが好ましい。

#### 【0102】

成膜時の不純物混入を低減することで、不純物によって結晶構造が崩れることを抑制できる。例えば、成膜室内に存在する不純物濃度（水素、水、二酸化炭素および窒素など）を低減すればよい。また、成膜ガス中の不純物濃度を低減すればよい。具体的には、露点が-80以下、好ましくは-100以下である成膜ガスを用いる。40

#### 【0103】

また、成膜時の基板加熱温度を高めることで、基板到達後にスパッタ粒子のマイグレーションが起こる。具体的には、基板加熱温度を100以上740以下、好ましくは200以上500以下として成膜する。成膜時の基板加熱温度を高めることで、平板状のスパッタ粒子が基板に到達した場合、基板上でマイグレーションが起り、スパッタ粒子の平らな面が基板に付着する。

#### 【0104】

また、成膜ガス中の酸素割合を高め、電力を最適化することで成膜時のプラズマダメージ50

を軽減すると好ましい。成膜ガス中の酸素割合は、30 volume%以上、好ましくは100 volume%とする。

【0105】

スパッタリング用ターゲットの一例として、In-Ga-Zn酸化物ターゲットについて以下に示す。

【0106】

InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末を所定のmol数で混合し、加圧処理後、1000以上1500以下の温度で加熱処理をすることで多結晶であるIn-Ga-Zn酸化物ターゲットとする。なお、X、YおよびZは任意の正数である。ここで、所定のmol数比は、例えば、InO<sub>x</sub>粉末、GaO<sub>y</sub>粉末およびZnO<sub>z</sub>粉末が、2:2:1、8:4:3、3:1:1、1:1:1、4:2:3または3:1:2である。なお、粉末の種類、およびその混合するmol数比は、作製するスパッタリング用ターゲットによって適宜変更すればよい。10

【0107】

また、酸化物半導体膜を形成した後、加熱処理を行い、酸化物半導体膜の脱水素化または脱水化をしてもよい。加熱処理の温度は、代表的には、150以上基板歪み点未満、好ましくは250以上450以下、更に好ましくは300以上450以下とする。

【0108】

加熱処理は、ヘリウム、ネオン、アルゴン、キセノン、クリプトン等の希ガス、または窒素を含む不活性ガス雰囲気で行う。または、不活性ガス雰囲気で加熱した後、酸素雰囲気で加熱してもよい。なお、上記不活性雰囲気および酸素雰囲気に水素、水などが含まれないことが好ましい。処理時間は3分～24時間とする。20

【0109】

酸化物半導体膜を形成した後、加熱処理を行うことで、酸化物半導体膜において、水素濃度を $1 \times 10^{20}$ atoms/cm<sup>3</sup>未満、 $5 \times 10^{19}$ atoms/cm<sup>3</sup>未満、 $1 \times 10^{19}$ atoms/cm<sup>3</sup>未満、 $5 \times 10^{18}$ atoms/cm<sup>3</sup>未満、 $1 \times 10^{18}$ atoms/cm<sup>3</sup>以下、 $5 \times 10^{17}$ atoms/cm<sup>3</sup>以下、または $1 \times 10^{16}$ atoms/cm<sup>3</sup>以下とすることができます。

【0110】

なお、下地絶縁膜438として酸化物絶縁膜を用いた場合、酸化物絶縁膜上に酸化物半導体膜が設けられた状態で加熱することによって、酸化物半導体膜に酸素を供給することができ、酸化物半導体膜の酸素欠陥を低減し、半導体特性を良好にすることができる場合がある。酸化物半導体膜および酸化物絶縁膜を少なくとも一部が接した状態で加熱工程を行うことによって、酸化物半導体膜への酸素の供給を行ってもよい。30

【0111】

次に、酸化物半導体膜上にフォトリソグラフィ工程によりマスクを形成した後、該マスクを用いて酸化物半導体膜の一部をエッチングすることで、図2(A)に示すように、酸化物半導体膜409を形成する。この後、マスクを除去する。なお、酸化物半導体膜409に下地絶縁膜438から酸素を供給するための加熱処理は、酸化物半導体膜を島状に加工する前に行ってもよいし、島状に加工した後に行ってもよい。ただし、島状に加工するよりも前に加熱処理を行うことで、下地絶縁膜438から外部に放出される酸素の量を少なくできるため、より多くの酸素を酸化物半導体膜409に供給できる。40

【0112】

なお、酸化物半導体膜の形成方法として印刷法を用いることで、島状の酸化物半導体膜409を直接形成することができる。

【0113】

続いて、酸化物半導体膜409上にゲート絶縁膜402となる絶縁膜を形成する。

【0114】

ゲート絶縁膜402の材料として、酸化シリコン、酸化ガリウム、酸化アルミニウム、酸化窒化シリコン、窒化酸化シリコン、酸化ハフニウム、または酸化タンタルなどの酸化物50

絶縁膜を用いることが好ましい。また、酸化ハフニウム、酸化イットリウム、ハフニウムシリケート ( $HfSi_xO_y$ 、 $x > 0$ 、 $y > 0$ )、窒素が添加されたハフニウムシリケート、ハフニウムアルミネート ( $HfAl_xO_y$ 、 $x > 0$ 、 $y > 0$ )、酸化ランタン、などの  $Hig h - k$  材料を用いることでゲートリーク電流を低減できる。さらに、ゲート絶縁膜は、単層構造としてもよいし、積層構造としてもよい。

#### 【0115】

ゲート絶縁膜 402 の膜厚は、1 nm 以上 100 nm 以下とし、スパッタリング法、MBE 法、CVD 法、PLD 法、ALD 法等を適宜用いて形成することができる。また、ゲート絶縁膜は、スパッタリング用ターゲット表面に対し、略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて成膜してもよい。

10

#### 【0116】

また、ゲート絶縁膜 402 は、下地絶縁膜 438 と同様に酸化物半導体膜と接するため、層中（バルク中）に少なくとも化学量論的組成を超える量の酸素が存在することが好ましい。

#### 【0117】

本実施の形態では、CVD 法により、酸化窒化シリコン膜を 20 nm 成膜する。

#### 【0118】

続いて、ゲート絶縁膜 402 上にゲート電極層 401 を形成し、該ゲート電極層をマスクとしてゲート絶縁膜をエッチングし、酸化物半導体膜を一部露出させる。ここまで、図 2 (A) に示す構造となる。

20

#### 【0119】

ゲート電極層 401 の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料またはこれらのいずれかを主成分とする合金材料を用いて形成することができる。また、ゲート電極層 401 としてリン等の不純物元素を添加した多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。さらに、インジウムスズ酸化物、タングステンインジウム酸化物、タングステンインジウム亜鉛酸化物、チタンインジウム酸化物、チタンインジウムスズ酸化物、インジウム亜鉛酸化物、シリコンインジウムスズ酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることができる。

30

#### 【0120】

また、ゲート絶縁膜 402 と接するゲート電極層 401 の一層として、窒素を含む金属酸化物膜、具体的には窒素を含む  $In - Ga - Zn$  酸化物膜や、窒素を含む  $In - Sn$  酸化物膜や、窒素を含む  $In - Ga$  酸化物膜や、窒素を含む  $In - Zn$  酸化物膜や、窒素を含む  $Sn$  酸化物膜や、窒素を含む  $In$  酸化物膜や、金属窒化膜 ( $InN$ 、 $SnN$  など) を用いることができる。これらの膜は 5 eV 以上、または 5.5 eV 以上の仕事関数を有し、ゲート電極層として用いた場合、トランジスタのしきい値電圧をプラスにすることができ、いわゆるノーマリオフのスイッチング素子を実現できる。

#### 【0121】

ゲート電極層 401 の膜厚は、50 nm 以上 300 nm 以下が好ましい。本実施の形態では、スパッタリング法を用いて、膜厚 30 nm の窒化タンタルと膜厚 200 nm のタングステンの積層を成膜する。

40

#### 【0122】

ゲート電極層 401 の形成後、ゲート電極層 401 をマスクとして、ゲート絶縁膜 402 をエッチングして、酸化物半導体膜 409 の一部を露出させる。

#### 【0123】

続いて、酸化物半導体膜 409、ゲート絶縁膜 402 およびゲート電極層 401 上に、酸化物半導体膜の露出した領域と接するように窒化シリコン膜 407 を形成する。窒化シリコン膜 407 を成膜することで、酸化物半導体膜 409 の窒化シリコン膜 407 と接する領域（ゲート絶縁膜 402 のエッチングによって露出された領域ともいえる）に窒素を添

50

加して低抵抗領域 404a および低抵抗領域 404b を形成する。なお、酸化物半導体膜 409 の露出していない領域（ゲート電極層 401 およびゲート絶縁膜 402 と重畠する領域ともいえる）には窒素が添加されず、チャネル形成領域 403 が形成される。

#### 【0124】

窒化シリコン膜 407 の成膜には、プラズマ CVD 法やスパッタリング法を用いることができる。成膜には、成膜ガスとしてシラン（SiH<sub>4</sub>）および窒素（N<sub>2</sub>）の混合ガスや、シラン（SiH<sub>4</sub>）、窒素（N<sub>2</sub>）およびアンモニア（NH<sub>3</sub>）の混合ガスを用いることができる。

#### 【0125】

窒化シリコン膜 407 からの水素分子の脱離量を低減するためには、成膜ガス中のアンモニアの流量比ができるだけ少ない方がよい。例えば、成膜ガス中の窒素に対するアンモニアの流量比が、0.1倍以下、好ましくは0.05倍以下、より好ましくは0.02倍以下（言い換れば、成膜ガス中のアンモニアの流量比に対して、窒素の流量比が、10倍以上、好ましくは20倍以上、より好ましくは50倍以上）であるとよい。10

#### 【0126】

成膜ガスとしてアンモニアを用いると、成膜時において、シランにおけるシリコン原子と水素原子の結合や、窒素における窒素原⼦どうしの三重結合が、解離したアンモニアによって切断されやすくなる。そのため、成膜時にシランや窒素の分解が促進され、緻密な窒化シリコン膜を形成することができる。緻密な窒化シリコン膜を形成することによって、酸化物半導体膜への外部からの水素、水分等の混入を防止することができる。よって、上記窒化シリコン膜の成膜時における、アンモニアの流量は、シランの分解が促進される程度の量であり、なおかつ、水素分子の脱離量が抑えられる程度の量とすることが、半導体装置の信頼性を高める上で望ましいといえる。20

#### 【0127】

また、成膜時において、基板を窒素プラズマ条件下においてそのまま、成膜ガスを供給しない時間を設けてもよい。基板を窒素プラズマ条件下におくことで、酸化物半導体膜の露出した部分に窒素が添加され、より抵抗を低減することができる場合がある。

#### 【0128】

また、窒化シリコン膜 407 は、水素、水分、水酸基または水素化物（水素化合物ともいう）などの不純物、および酸素の両方に対して膜を通過させないようにする遮断効果を有する。したがって、窒化シリコン膜は作製工程中および作製工程後において、変動要因となる水素、水分などの不純物が酸化物半導体膜へ混入することを防ぐとともに、酸化物半導体膜の主成分材料である酸素の外方拡散を防止する保護膜として機能する。30

#### 【0129】

また、酸化物半導体膜 409 に窒素を添加するために、窒化シリコン膜 407 を設けた後に、加熱処理を行ってもよい。加熱処理を行うことで、窒化シリコン膜 407 から酸化物半導体膜 409 に窒素を添加することができる。

#### 【0130】

続いて、窒化シリコン膜 407 上に層間絶縁膜 411 を形成する。層間絶縁膜 411 は、下地絶縁膜 436 と同様の材料、方法を用いて形成することができる。なお、層間絶縁膜 411 は必ずしも設けなくともよい。40

#### 【0131】

続いて、窒化シリコン膜 407 および層間絶縁膜 411 の低抵抗領域 404a および低抵抗領域 404b と重畠する領域の一部をエッチングし、低抵抗領域 404a および低抵抗領域 404b に達する開口部を形成する。開口部の形成は、マスクなどを用いた選択的なエッチングにより行われる。エッチングはドライエッチングでも、ウェットエッチングでもよく、双方を組み合わせて開口部を形成してもよい。また、該開口部は低抵抗領域 404a および低抵抗領域 404b に達すればよく、形状は特に限定されない。

#### 【0132】

続いて、該開口部に導電材料を成膜することで、ソース電極層 405a およびドレイン電50

極層 405b を形成する(図2(C)参照)。ソース電極層405aおよびドレイン電極層405bには上述したゲート電極層401に用いた材料および方法と同様にして作製することができる。

#### 【0133】

以上の工程でトランジスタ420を作製することができる。

#### 【0134】

本実施の形態に示したトランジスタは、酸化物半導体膜上に設けた窒化シリコン膜の成膜によって、酸化物半導体膜に窒素を添加し、酸化物半導体膜409に低抵抗領域を形成することができる。また、該低抵抗領域において、酸化物半導体膜とソース電極層およびドレイン電極層が電気的に接続するため、酸化物半導体膜とソース電極層およびドレイン電極層とのコンタクト抵抗が低減されている。したがって、オン特性に優れ、電気的特性の良好な半導体装置とすることができる。10

#### 【0135】

また、層間絶縁膜として機能する窒化シリコン膜407の成膜工程において、酸化物半導体膜409に窒素を添加し、低抵抗領域404aおよび低抵抗領域404bを形成することができるため、工程を複雑化させることなくトランジスタ420のオン特性を向上させることができる。

#### 【0136】

また、窒化シリコン膜407は、水素濃度が低減されており、水素分子脱離量の少ない膜である。そのため、窒化シリコン膜407から酸化物半導体膜409に水素、水分といった不純物が混入することを防ぐことができる。また、該窒化シリコン膜は外部からの水素、水分の混入を防止することができるブロッキング性を有する膜である。したがって、外部から水素、水分等の不純物が混入することを防止することができる。そのため、電気的特性の安定した、信頼性の高い半導体装置とすることができます。20

#### 【0137】

低抵抗領域404aおよび低抵抗領域404bの形成は、窒化シリコン膜407の成膜工程における窒素の添加を用いて行うが、組み合わせて酸化物半導体膜を低抵抗化させる不純物元素の添加工程を行ってもよい。不純物元素を添加することによって、低抵抗領域404aおよび低抵抗領域404bの抵抗をより低減することができる。

#### 【0138】

しかし、成膜後の酸化物半導体膜409へ不純物元素を添加すると、添加領域において結晶性が低下する場合がある。例えば、C A A C - O S 膜である酸化物半導体膜409において、成膜時の窒素添加工程と、不純物元素の添加工程を行って低抵抗領域404aおよび低抵抗領域404bを形成する場合、低抵抗領域404aおよび低抵抗領域404bは非晶質構造(または、非晶質構造を多く含む状態)となる場合がある。この場合、酸化物半導体膜409において、チャネル形成領域403はC A A C - O S 膜、低抵抗領域404aおよび低抵抗領域404bは非晶質膜(または、非晶質構造を多く含む膜)となる場合がある。

#### 【0139】

不純物元素の添加方法としては、イオン注入法、イオンドーピング法などを用いることができる。40

#### 【0140】

添加する不純物元素は、リン、ホウ素、窒素、ヒ素、アルゴン、アルミニウム、またはこれらを含む分子イオンなどを用いることができる。これらの元素のドーズ量は、 $1 \times 10^{13} \sim 5 \times 10^{16}$  ions/cm<sup>2</sup>とするのが好ましい。また、不純物元素としてリンを添加する場合、加速電圧を0.5~80kVとするのが好ましい。

#### 【0141】

また、酸化物半導体膜409に不純物元素を添加する処理は、複数回行ってもよい。酸化物半導体膜409に不純物元素を添加する処理を複数回行う場合、不純物元素の種類は複数回の添加処理すべてにおいて同じであってもよいし、1回の処理毎に変えてよい。

## 【0142】

また、不純物元素の添加は、酸化物半導体膜409となる酸化物半導体膜の成膜直後に行ってもよいし、酸化物半導体膜を島状の酸化物半導体膜409に加工した直後に行ってもよい。また、ゲート絶縁膜402となる絶縁膜の成膜後に行ってもよいし、ゲート絶縁膜402を形成して、酸化物半導体膜を一部を露出させた状態で行ってもよい。また、窒化シリコン膜407の成膜後に行ってもよい。ゲート絶縁膜402または窒化シリコン膜407が酸化物半導体膜409を覆っている状態で不純物元素を添加する場合、ゲート絶縁膜402または窒化シリコン膜407を通過させて不純物元素を添加するため、酸化物半導体膜409に与えるダメージが少ない。

## 【0143】

10

なお、非晶質構造の酸化物半導体膜は、CAC-O<sub>x</sub>膜などの結晶性を有する酸化物半導体膜から水素などのドナーとなる不純物を吸収しやすいため、チャネル形成領域403を挟む低抵抗領域が非晶質構造であると、チャネル形成領域403から、不純物を吸収（ゲッタリングとも表現できる）し、トランジスタ420の電気的特性を良好なものとすることができる場合がある。

## 【0144】

また、図示しないが、トランジスタ420上に、さらに絶縁膜を設けてもよい。絶縁膜としては、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、または酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜の単層または積層を用いることができる。

20

## 【0145】

絶縁膜の形成後、さらに加熱工程を行ってもよい。例えば、大気中、100以上200以下、1時間以上30時間以下の加熱工程を行ってもよい。この加熱工程は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回繰り返して行ってもよい。

## 【0146】

また、トランジスタ420起因の表面凹凸を低減するために、平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド樹脂、アクリル樹脂、ベンゾシクロブテン系樹脂等の有機材料を用いることができる。また、上記有機材料の他に、低誘電材料（LOW-K材料）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁膜を形成してもよい。

30

## 【0147】

また、本実施の形態に示すトランジスタは上記の構成に限定されない。例えば、図3に示すトランジスタ430のように、窒化シリコン膜407を形成する前に、酸化物半導体膜409と接するソース電極層405aおよびドレイン電極層405bを形成する構成としてもよい。

## 【0148】

窒化シリコン膜407の形成前にソース電極層405aおよびドレイン電極層405bを形成することによって、ソース電極層405aおよびドレイン電極層405bと重畠する領域の酸化物半導体膜409は、窒化シリコン膜407の成膜時における窒素の添加が行われないため、抵抗が低減されず、チャネル形成領域403と同様の抵抗を有する領域403aおよび領域403bが形成される。

40

## 【0149】

なお、図3に示すトランジスタ430においては、ソース電極層405aおよびドレイン電極層405bと接する酸化物半導体膜409の端部が、低抵抗化されていないため寄生チャネルの発生が低減される。なお、チャネル形成領域403とソース電極層405aおよびドレイン電極層405bとの間には、低抵抗領域404aおよび低抵抗領域404bが形成されているため、チャネル形成領域403とソース電極層405aおよびドレイン電極層405bとの間の抵抗は低減することができ、トランジスタ430の電気的特性を

50

良好とすることができます。

**【0150】**

なお、トランジスタ430のオン特性を重視し、ソース電極層405aおよびドレイン電極層405bと領域403aおよび領域403bの抵抗を低減するためには、ソース電極層405aおよびドレイン電極層405bの形成前に酸化物半導体膜409に不純物元素を添加すればよい。不純物元素を添加することで、ソース電極層405aおよびドレイン電極層405bと重畳する領域403aおよび403bの抵抗を低減させることができる。この場合、低抵抗領域404aおよび低抵抗領域404bにも不純物元素が添加されるため、低抵抗領域404aおよび低抵抗領域404bはより抵抗が低減される。

**【0151】**

本実施の形態は、他の実施の形態と適宜組み合わせることができる。

**【0152】**

(実施の形態2)

本実施の形態では、実施の形態1とは異なる、本発明の一態様のトランジスタについて説明する。なお、本実施の形態では、実施の形態1と同様の箇所については同様の符号を付し、詳細な説明は省略する。

**【0153】**

図4に本実施の形態の一態様のトランジスタ520を示す。図4(A)はトランジスタ520の上面図であり、図4(B)は図4(A)に示す一点鎖線C-Dにおける断面図を示す。

**【0154】**

トランジスタ520は、基板400上の下地絶縁膜436および下地絶縁膜438と、下地絶縁膜438上の酸化物半導体膜509と、酸化物半導体膜509上のゲート絶縁膜402と、ゲート絶縁膜402上のゲート電極層401と、ゲート絶縁膜402およびゲート電極層401の側面と接する側壁絶縁膜413aおよび側壁絶縁膜413bと、酸化物半導体膜509、ゲート電極層401、側壁絶縁膜413aおよび側壁絶縁膜413b上の層間絶縁膜411および層間絶縁膜414と、層間絶縁膜411および層間絶縁膜414に設けられた開口部において酸化物半導体膜509と接するソース電極層405aおよびドレイン電極層405bと、を有する。

**【0155】**

側壁絶縁膜413aおよび側壁絶縁膜413bは実施の形態1に示した窒化シリコン膜407と同様の条件を用いて成膜された窒化シリコン膜を用いることで形成される。

**【0156】**

酸化物半導体膜509は、ゲート電極層401と重畳するチャネル形成領域403と、チャネル形成領域403を挟み、側壁絶縁膜413aおよび側壁絶縁膜413bとそれぞれ重畳する第1の低抵抗領域406aおよび第1の低抵抗領域406bと、第1の低抵抗領域406aおよび第1の低抵抗領域406bを挟み、ソース電極層405aおよびドレイン電極層405bとそれぞれ電気的に接続する第2の低抵抗領域408aおよび第2の低抵抗領域408bと、を有する。

**【0157】**

第1の低抵抗領域406a、第1の低抵抗領域406b、第2の低抵抗領域408aおよび第2の低抵抗領域408bは、側壁絶縁膜413aおよび側壁絶縁膜413bとなる窒化シリコン膜の成膜によって、窒素が添加され、抵抗が低減されている。

**【0158】**

さらに、第2の低抵抗領域408aおよび第2の低抵抗領域408bには、ゲート電極層401および側壁絶縁膜413aおよび側壁絶縁膜413bをマスクとして導電率を低減させる不純物元素が添加されているため、第1の低抵抗領域406a、第1の低抵抗領域406bよりも抵抗が低減されている。

**【0159】**

そのため、第1の低抵抗領域406aおよび第1の低抵抗領域406bは、LDD(Li

10

20

30

40

50

g h t l y D o p e d D r a i n ) 領域として機能する。L D D 領域を設けることにより、オフ電流の低減、またはトランジスタの耐圧向上（信頼性の向上）を図ることができる。

#### 【 0 1 6 0 】

なお、第1の低抵抗領域 4 0 6 a および第1の低抵抗領域 4 0 6 b には、不純物元素 4 2 1 が添加されていないため、第1の低抵抗領域 4 0 6 a および第1の低抵抗領域 4 0 6 b は、結晶性半導体膜、C A A C - O S 膜等の結晶（または、非晶質構造よりも結晶構造が多い）状態を有する膜である。

#### 【 0 1 6 1 】

また、不純物元素の添加によって、第2の低抵抗領域 4 0 8 a および第2の低抵抗領域 4 0 8 b は、チャネル形成領域 4 0 3 、第1の低抵抗領域 4 0 6 a および第1の低抵抗領域 4 0 6 b に比べて、結晶成分よりも非晶質成分の割合が多くなる場合がある。非晶質構造の酸化物半導体膜は、C A A C - O S 膜などの結晶性を有する酸化物半導体膜から水素などのドナーとなる不純物を吸収しやすい場合があるため、チャネル形成領域 4 0 3 、第1の低抵抗領域 4 0 6 a および第1の低抵抗領域 4 0 6 b から、第2の低抵抗領域 4 0 8 a および第2の低抵抗領域 4 0 8 b は、不純物を吸収（ゲッタリングとも表現できる）し、トランジスタ 5 2 0 の電気的特性を良好なものとすることができます。また、不純物元素を吸収し、不純物元素濃度が高くなっている第2の低抵抗領域 4 0 8 a および第2の低抵抗領域 4 0 8 b と、チャネル形成領域 4 0 3 との間に、第1の低抵抗領域 4 0 6 a および第1の低抵抗領域 4 0 6 b が設けられているため、チャネル形成領域 4 0 3 と不純物元素の濃度の高い領域が接していないため、トランジスタ 5 2 0 の信頼性を向上させることができます。10

#### 【 0 1 6 2 】

続いて、トランジスタ 5 2 0 の作製方法について図 5 を用いて説明する。なお、実施の形態 1 と同様の箇所については、詳細な説明を省略する。

#### 【 0 1 6 3 】

図 5 ( A ) に示す半導体装置は、図 2 ( B ) に示す半導体装置に対応する。したがって、図 5 ( A ) に示す半導体装置の作製方法は実施の形態 1 の記載を参照すればよい。なお、この段階では、酸化物半導体膜 4 0 9 は窒化シリコン膜 4 0 7 の成膜時に窒素が添加され、窒化シリコン膜 4 0 7 と接する領域に窒素が添加されることによって抵抗が低減されているため、低抵抗領域 4 0 4 a と、低抵抗領域 4 0 4 b と、低抵抗領域 4 0 4 a および低抵抗領域 4 0 4 b とに挟まれるチャネル形成領域 4 0 3 を有する。20

#### 【 0 1 6 4 】

続いて、窒化シリコン膜 4 0 7 に異方性エッチングを行い、酸化物半導体膜 4 0 9 の一部を露出させる。なお、異方性エッチングはゲート電極層 4 0 1 の上面が露出するまで行えばよい。異方性エッチングによってゲート電極層 4 0 1 が露出した段階では、ゲート電極層 4 0 1 およびゲート絶縁膜 4 0 2 の側部には窒化シリコン膜が残留している。したがって、この段階でエッチングを止めることで、マスクを用いずに自己整合的に側壁絶縁膜 4 1 3 a および側壁絶縁膜 4 1 3 b を形成することができる。マスクを用いずに側壁絶縁膜 4 1 3 a および側壁絶縁膜 4 1 3 b を作製することによって、マスク数を削減し、作製コストを低減することができる。30

#### 【 0 1 6 5 】

続いて、ゲート電極層 4 0 1 、側壁絶縁膜 4 1 3 a および側壁絶縁膜 4 1 3 b をマスクとして、酸化物半導体膜 4 0 9 に不純物元素 4 2 1 の添加を行う。不純物元素 4 2 1 の添加方法としては、イオン注入法、イオンドーピング法などを用いることができる。

#### 【 0 1 6 6 】

添加する不純物元素は、リン、ホウ素、窒素、ヒ素、アルゴン、アルミニウム、またはこれらを含む分子イオンなどを用いることができる。これらの元素のドーズ量は、 $1 \times 1 0^{13} \sim 5 \times 1 0^{16}$  ions / cm<sup>2</sup> とするのが好ましい。また、不純物元素としてリンを添加する場合、加速電圧を 0 . 5 ~ 8 0 k V とするのが好ましい。40

**【 0 1 6 7 】**

また、酸化物半導体膜 4 0 9 に不純物元素を添加する処理は、複数回行ってもよい。酸化物半導体膜 4 0 9 に不純物元素を添加する処理を複数回行う場合、不純物元素の種類は複数回の添加処理すべてにおいて同じであってもよいし、1回の処理毎に変えててもよい。

**【 0 1 6 8 】**

ここで、不純物元素 4 2 1 を添加することによって、低抵抗領域 4 0 4 a および低抵抗領域 4 0 4 b の露出した領域（ゲート電極層 4 0 1 、側壁絶縁膜 4 1 3 a および側壁絶縁膜 4 1 3 b と重畳しない領域）の抵抗を低減する。したがって、ここで酸化物半導体膜 5 0 9 は、チャネル形成領域 4 0 3 と、窒化シリコン膜の成膜時における窒素の添加によって抵抗が低減された第 1 の低抵抗領域 4 0 6 a および第 1 の低抵抗領域 4 0 6 b と、窒化シリコン膜の成膜時における窒素の添加および不純物元素 4 2 1 の添加によって抵抗が低減されている第 2 の低抵抗領域 4 0 8 a および第 2 の低抵抗領域 4 0 8 b と、を含む（図 5 (B) 参照）。

**【 0 1 6 9 】**

第 1 の低抵抗領域 4 0 6 a 、第 1 の低抵抗領域 4 0 6 b 、第 2 の低抵抗領域 4 0 8 a および第 2 の低抵抗領域 4 0 8 b は窒化シリコン膜 4 0 7 の成膜時に窒素が添加され、抵抗が低減された領域である。さらに、第 2 の低抵抗領域 4 0 8 a および第 2 の低抵抗領域 4 0 8 b は、不純物元素 4 2 1 が添加されることによって、第 1 の低抵抗領域 4 0 6 a および第 1 の低抵抗領域 4 0 6 b よりも抵抗が低減され、抵抗が低い領域である。

**【 0 1 7 0 】**

なお、不純物元素 4 2 1 の添加時に、酸化物半導体膜 5 0 9 の側壁絶縁膜 4 1 3 a および側壁絶縁膜 4 1 3 b と重畳する領域（第 1 の低抵抗領域 4 0 6 a および第 1 の低抵抗領域 4 0 6 b ）に、側壁絶縁膜 4 1 3 a および側壁絶縁膜 4 1 3 b を通過して不純物元素が添加されるように、不純物元素の加速電圧を調整してもよい。第 1 の低抵抗領域 4 0 6 a および第 1 の低抵抗領域 4 0 6 b にも不純物元素が添加されることによって、さらに第 1 の低抵抗領域 4 0 6 a および第 1 の低抵抗領域 4 0 6 b の抵抗を低減することができる。なお、第 1 の低抵抗領域 4 0 6 a および第 1 の低抵抗領域 4 0 6 b にも不純物元素が添加される場合、第 2 の低抵抗領域 4 0 8 a および第 2 の低抵抗領域 4 0 8 b には、第 1 の低抵抗領域 4 0 6 a および第 1 の低抵抗領域 4 0 6 b よりも多くの不純物元素が添加されていてよい。

**【 0 1 7 1 】**

続いて、酸化物半導体膜 5 0 9 、側壁絶縁膜 4 1 3 a 、側壁絶縁膜 4 1 3 b およびゲート電極層 4 0 1 上に層間絶縁膜 4 1 1 および層間絶縁膜 4 1 4 を形成する。層間絶縁膜 4 1 1 および層間絶縁膜 4 1 4 は、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、または酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などの無機絶縁膜の単層または積層を用いることができる。層間絶縁膜 4 1 1 および層間絶縁膜 4 1 4 は異なる膜であってもよいし、同一の膜であってもよい。ここでは、層間絶縁膜 4 1 1 を酸化物半導体膜 5 0 9 に対して酸素を供給するため、化学量論的組成よりも酸素が過剰に添加された酸化シリコン膜とし、層間絶縁膜 4 1 4 を、酸化物半導体膜に対する外部からの水素、水等の不純物の混入を防止するブロッキング性を有する窒化シリコン膜とする。

**【 0 1 7 2 】**

続いて、層間絶縁膜 4 1 1 および層間絶縁膜 4 1 4 に第 2 の低抵抗領域 4 0 8 a および第 2 の低抵抗領域 4 0 8 b にそれぞれ達する開口部を形成し、該開口部に導電材料を用いてソース電極層 4 0 5 a およびドレイン電極層 4 0 5 b を形成する（図 5 (C) 参照）。

**【 0 1 7 3 】**

ソース電極層 4 0 5 a およびドレイン電極層 4 0 5 b は第 2 の低抵抗領域 4 0 8 a および第 2 の低抵抗領域 4 0 8 b において、酸化物半導体膜 5 0 9 と接しているため、酸化物半導体膜 5 0 9 とソース電極層 4 0 5 a およびドレイン電極層 4 0 5 b とのコンタクト抵抗を低減することができる。

10

20

30

40

50

**【 0 1 7 4 】**

また、ここで、第1の低抵抗領域406aおよび第1の低抵抗領域406bはLDD領域として機能するため、オフ電流の低減、またはトランジスタの耐圧向上（信頼性の向上）を図ることができる。

**【 0 1 7 5 】**

以上の工程でトランジスタ520を作製することができる。

**【 0 1 7 6 】**

本実施の形態に示すトランジスタは、酸化物半導体膜、ゲート絶縁膜およびゲート電極層上の窒化シリコン膜を形成することで、酸化物半導体膜の窒化シリコン膜と接する領域に窒素を拡散して、低抵抗領域を形成する。該低抵抗領域において、酸化物半導体膜はソース電極層およびドレイン電極層と電気的に接続するため、ソース電極層およびドレイン電極層と酸化物半導体膜とのコンタクト抵抗を低減することができる。10

**【 0 1 7 7 】**

また、該窒化シリコン膜は、水素濃度が低減されており、水素分子脱離量の少ない膜である。そのため、窒化シリコン膜から酸化物半導体膜に対して酸化物半導体膜の劣化要因となる水素、水分といった不純物が混入することを防ぐことができる。また、該窒化シリコン膜は外部からの水素、水分の混入を防止することができるプロッキング性を有する膜である。したがって、外部から水素、水分等の不純物が混入することを防止することができる。そのため、電気的特性の安定した、信頼性の高い半導体装置とすることができます。

**【 0 1 7 8 】**

さらに、本実施の形態に示す半導体装置はゲート電極層および側壁絶縁膜をマスクとして不純物元素を添加することで自己整合的にLDD領域を形成することができる。LDD領域を設けることによって、トランジスタのオフ電流の低減、またはトランジスタの耐圧向上（信頼性の向上）を図ることができる。20

**【 0 1 7 9 】**

また、本実施の形態に示すトランジスタは上記の構成に限らない。例えば、図6(A)に示すトランジスタ530のように、酸化物半導体膜509とソース電極層405aおよびドレイン電極層405bとが層間絶縁膜411に設けられた開口部を介さずに接する構成としてもよい。また、ゲート電極層401上に絶縁膜412を形成してもよい。

**【 0 1 8 0 】**

トランジスタ530の作製方法としては、まず、酸化物半導体膜を形成し、酸化物半導体膜509上にゲート絶縁膜402およびゲート電極層401を形成した後に窒化シリコン膜の成膜によって酸化物半導体膜509に窒素を添加して抵抗を低減し、該窒化シリコン膜を異方性エッチングすることで、側壁絶縁膜413aおよび側壁絶縁膜413bを形成する。その後、ソース電極層405aおよびドレイン電極層405bを形成し、ゲート電極層401、側壁絶縁膜413a、側壁絶縁膜413b、ソース電極層405aおよびドレイン電極層405bをマスクとして酸化物半導体膜509に不純物元素を添加する。30

**【 0 1 8 1 】**

そのため、トランジスタ530の酸化物半導体膜509は、ゲート電極層401と重畠するチャネル形成領域403と、チャネル形成領域403を挟み、側壁絶縁膜413aおよび側壁絶縁膜413bと重畠する第1の低抵抗領域406aおよび第1の低抵抗領域406bと、第1の低抵抗領域406aおよび第1の低抵抗領域406bをはさみ、不純物元素の添加処理によって、第1の低抵抗領域406aおよび第1の低抵抗領域406bよりも抵抗が低減されている第2の低抵抗領域408aおよび第2の低抵抗領域408bと、第2の低抵抗領域408aおよび第2の低抵抗領域408bを挟んで、ソース電極層405aおよびドレイン電極層405bと接する第3の低抵抗領域410aおよび第3の低抵抗領域410bと、を有する。40

**【 0 1 8 2 】**

トランジスタ530は、ソース電極層405aおよびドレイン電極層405bと電気的に接続する酸化物半導体膜509の端部が、低抵抗化されていないため寄生チャネルの発生50

が低減される。なお、トランジスタ 530 のオン特性を重視する場合は、ソース電極層 405a およびドレイン電極層 405b の形成の前に不純物元素を添加することで、ソース電極層 405a およびドレイン電極層 405b と重畠する、第 3 の低抵抗領域 410a および第 3 の低抵抗領域 410b にも不純物元素を添加してもよい。

**【0183】**

また、本実施の形態の他の一様の半導体装置は、図 6 (B) に示すトランジスタ 540 のように、ゲート電極層 401 上の絶縁膜 412 を有し、ソース電極層 405a およびドレイン電極層 405b が側壁絶縁膜 413a および側壁絶縁膜 413b の側面と接し、酸化物半導体膜 409 を覆うように形成された構成としてもよい。

**【0184】**

トランジスタ 540 の作製方法としては、トランジスタ 520 と同様の方法を用いて側壁絶縁膜 413a および側壁絶縁膜 413b を形成した後、酸化物半導体膜 509、ゲート電極層 401、側壁絶縁膜 413a および側壁絶縁膜 413b 上に、ソース電極層 405a およびドレイン電極層 405b となる導電膜、層間絶縁膜 411 となる絶縁膜を形成する。該導電膜および絶縁膜のゲート電極層 401 と重畠する領域を除去することによって、該導電膜を分断し、自己整合的にソース電極層 405a およびドレイン電極層 405b を形成することができる。

**【0185】**

導電膜および絶縁膜の除去には化学的機械的研磨処理、異方性エッティング等を用いることができる。

**【0186】**

ゲート電極層 401 上に設けた絶縁膜 412 によって、ゲート電極層 401 と、ソース電極層 405a およびドレイン電極層 405b との絶縁性を確保することができる。

**【0187】**

本実施の形態は他の実施の形態と適宜組み合わせて利用することができる。

**【0188】**

(実施の形態 3)

本実施の形態では、実施の形態 1 および実施の形態 2 に示すトランジスタを使用した半導体装置の一例について図 7 および図 8 を用いて説明する。

**【0189】**

図 7 は、本実施の形態に示す半導体装置の断面図の一部を示す。なお、図 7 に示す断面図は一例であり、本実施の形態に示す半導体装置の構造はこれに限らない。

**【0190】**

図 7 に示す半導体装置は、下部に第 1 の半導体材料を用いたトランジスタ 160 を有し、上部に第 2 の半導体材料を用いたトランジスタ 162 を有するものである。トランジスタ 162 は、実施の形態 1 および実施の形態 2 に示したトランジスタと同様の構成とすることができます。ここでは、トランジスタ 162 として実施の形態 1 に示すトランジスタを用いる。

**【0191】**

ここで、第 1 の半導体材料と第 2 の半導体材料は異なるエネルギー・ギャップを持つ材料とすることが望ましい。例えば、第 1 の半導体材料を酸化物半導体以外の半導体材料（シリコンなど）とし、第 2 の半導体材料を酸化物半導体とすることができます。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とし、消費電力を低減することができます。

**【0192】**

図 7 におけるトランジスタ 160 は、半導体材料（例えば、シリコンなど）を含む基板 100 に設けられた下地絶縁膜 102 と、下地絶縁膜 102 上の半導体層 116 と、半導体層 116 上のゲート絶縁膜 108 と、ゲート絶縁膜 108 上のゲート電極層 110 と、ゲート絶縁膜 108 上の、ゲート電極層 110 の側面と接する側壁絶縁膜 120a および側

10

20

30

40

50

壁絶縁膜 120b と、半導体層 116、ゲート絶縁膜 108、ゲート電極層 110、側壁絶縁膜 120a および側壁絶縁膜 120b を覆う絶縁膜 125、絶縁膜 131、および絶縁膜 133 の積層と、絶縁膜 125、絶縁膜 131、および絶縁膜 133 に設けられた開口部を介して半導体層 116 に接するソース電極層 124a およびドレイン電極層 124b と、を有する。

#### 【0193】

なお、高集積化を実現するためには、トランジスタ 160 が側壁絶縁膜 120a および側壁絶縁膜 120b を有しない構成とすることが望ましい。一方で、トランジスタ 160 の特性を重視する場合には、図 7 に示すように、側壁絶縁膜 120a および側壁絶縁膜 120b を設けるとよい。

10

#### 【0194】

トランジスタ 160 上には、絶縁膜 135 が設けられている。絶縁膜 135 上には絶縁膜 137 が設けられており、絶縁膜 137 に導電層 141a および導電層 141b が設けられている。導電層 141a は、絶縁膜 135 に設けられた開口部においてトランジスタ 160 のドレイン電極層 124b と電気的に接続している。

20

#### 【0195】

絶縁膜 137 上には絶縁膜 151、絶縁膜 153、絶縁膜 155 が設けられている。絶縁膜 151 および絶縁膜 153 はトランジスタ 162 に対して、トランジスタ 160 起因の不純物が添加されないよう、プロッキング性を有する膜を用いることが好ましい。例えば絶縁膜 151 に酸化シリコンを含む膜を用い、絶縁膜 153 に窒化シリコンを含む膜を用いる構成としてもよい。絶縁膜 155 は、後に形成される酸化物半導体膜 144 の平坦性を向上させ、酸化物半導体膜に酸素を供給する膜である。したがって、絶縁膜 155 として、化学量論的組成を超えた酸素が含まれる酸化シリコン膜等を用い、CMP 处理等によって平坦性を向上させた膜とするよ。

#### 【0196】

絶縁膜 155 上には、トランジスタ 162 が形成されている。トランジスタ 162 は、実施の形態 1 に示す酸化物半導体を用いたトランジスタである。トランジスタ 162 が有する酸化物半導体膜 144 は、ゲート電極層 148 をマスクとした不純物元素の添加処理と酸化物半導体膜 144 上に設けられた窒化シリコン膜 143 の成膜によって低抵抗化されている。よって、酸化物半導体膜 144 は低抵抗領域 144a、低抵抗領域 144b、低抵抗領域 144c、低抵抗領域 144d およびチャネル形成領域 144e を含む。なお、不純物元素の添加処理は、ゲート電極層 148 の形成後、窒化シリコン膜 143 の成膜前に行われている。

30

#### 【0197】

低抵抗領域 144a 乃至低抵抗領域 144d には、ゲート電極層 148 をマスクとした不純物元素の添加が行われている。したがって、低抵抗領域 144a 乃至低抵抗領域 144d は、チャネル形成領域 144e よりも不純物元素の濃度が高い。不純物元素の濃度を高くすることによって酸化物半導体膜 144 中のキャリア密度が増加するため、配線層と酸化物半導体膜の間で良好なオーミックコンタクトをとることができ、トランジスタのオン電流や電界効果移動度が向上する。

40

#### 【0198】

加えて、低抵抗領域 144c および低抵抗領域 144d は、酸化物半導体膜 144 上に形成された窒化シリコン膜 143 の成膜によって窒素が添加されて、抵抗が低減されている。したがって、低抵抗領域 144a および低抵抗領域 144b よりも抵抗が低い。

#### 【0199】

トランジスタ 162 は、酸化物半導体膜に窒化シリコン膜を接して成膜することによって、酸化物半導体膜に窒素を添加し、酸化物半導体膜 144 に低抵抗領域 144c および低抵抗領域 144d を形成することができる。したがって、オン特性に優れ、電気的特性の良好なトランジスタとすることができます、半導体装置の高速応答、高速動作を可能とする。

#### 【0200】

50

また、該窒化シリコン膜は、水素濃度が低減されており、外部からの水素、水分の混入を防止することができるブロッキング性を有する膜である。したがって、酸化物半導体膜の劣化要因となる、水、水素等の不純物が混入することを防止し、電気的特性の安定した、信頼性の高い半導体装置とすることができる。

#### 【0201】

トランジスタ162は、上述の酸化物半導体膜144と、酸化物半導体膜144上のゲート絶縁膜146と、ゲート絶縁膜146上のゲート電極層148と、酸化物半導体膜144の低抵抗領域144aおよび低抵抗領域144bとそれぞれ接するソース電極層142aおよびドレイン電極層142bと、酸化物半導体膜144、ソース電極層142a、ドレイン電極層142b、ゲート絶縁膜146およびゲート電極層148を覆う窒化シリコン膜143と、を有する。なお、ソース電極層142aは、絶縁膜151、絶縁膜153および絶縁膜155に設けられた開口部において導電層141aと電気的に接続している。

。

10

#### 【0202】

トランジスタ162上には、絶縁膜147および絶縁膜149の積層が設けられている。絶縁膜147および絶縁膜149には、酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、酸化窒化アルミニウム膜、酸化ハフニウム膜、または酸化ガリウム膜、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜等の無機絶縁膜を用いればよい。絶縁膜147および絶縁膜149は同一の膜であってもよいし、異なる膜であってもよい。

。

20

#### 【0203】

絶縁膜147および絶縁膜149上には、絶縁膜147および絶縁膜149に設けられた開口部においてソース電極層142aと電気的に接続する配線層145が設けられている。配線層145上には絶縁膜157が設けられ、絶縁膜157上に、絶縁膜157に設けられた開口部において配線層145と電気的に接続する配線層159が設けられている。

#### 【0204】

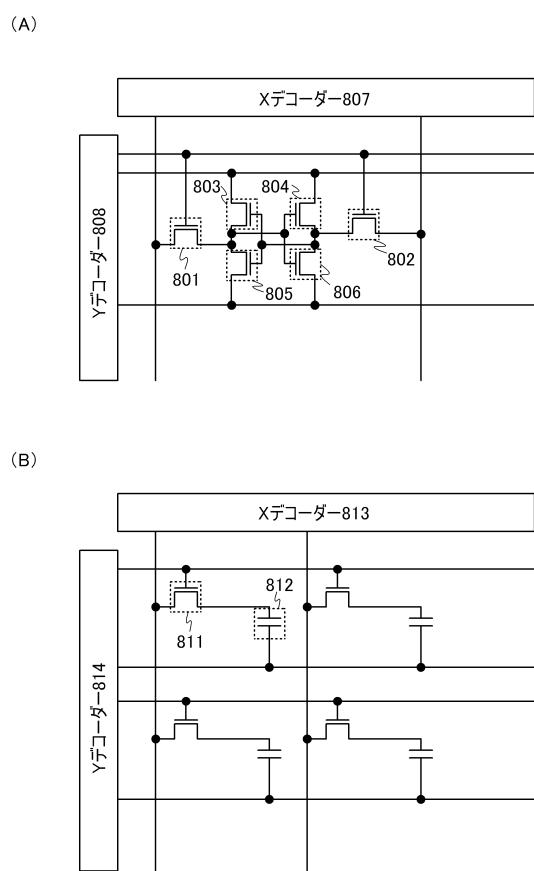

本明細書に示すトランジスタを使用した半導体装置の例として、論理回路であるNOR型回路、およびNAND型回路を図8(A)および図8(B)に示す。図8(A)はNOR型回路であり、図8(B)はNAND型回路である。

#### 【0205】

30

図8(A)および図8(B)に示すNOR型回路およびNAND型回路では、トランジスタ201、202、211、214は、pチャネル型トランジスタであり、図7に示すトランジスタ160と同様な構造を有するトランジスタである。トランジスタ203、204、212、213は、nチャネル型トランジスタであり、図7に示すトランジスタ162または実施の形態1および実施の形態2に示すトランジスタと同様な構造を有するトランジスタである。

#### 【0206】

本実施の形態に示す半導体装置では、トランジスタ162としてチャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、消費電力を十分に低減することができる。また、実施の形態1および実施の形態2に示すトランジスタを用いることで、酸化物半導体膜とソース電極層およびドレイン電極層とのコンタクト抵抗が低減され、オン特性に優れているため、半導体装置の高速応答、高速動作が可能となる。

。

40

#### 【0207】

また、異なる半導体材料を用いた半導体素子を積層することにより、微細化および高集積化を実現し、かつ安定で高い電気的特性を付与された半導体装置、および該半導体装置の作製方法を提供することができる。

#### 【0208】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

50

**【0209】**

(実施の形態4)

本実施の形態では、本明細書に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置（記憶装置）の一例を、図面を用いて説明する。

**【0210】**

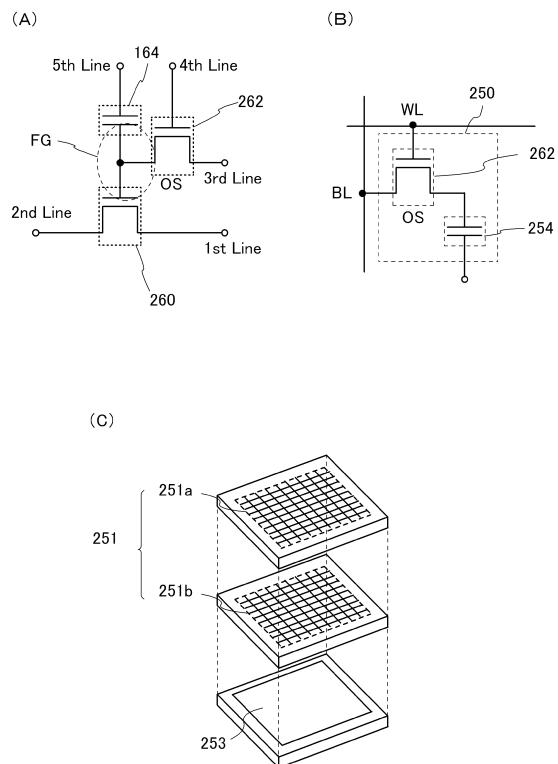

図9(A)は、本実施の形態の半導体装置を示す回路図である。

**【0211】**

図9(A)に示すトランジスタ260は、図7に示すトランジスタ160と同様の構造を適用することができ、高速動作が容易である。また、トランジスタ262には図7に示すトランジスタ162、実施の形態1または実施の形態2に示すトランジスタと同様の構造を適用することができ、その特性により長時間の電荷保持を可能とする。10

**【0212】**

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、本実施の形態に示す半導体装置に用いるトランジスタとしては、pチャネル型トランジスタを用いることもできる。

**【0213】**

図9(A)において、第1の配線(1st Line)とトランジスタ260のソース電極層とは、電気的に接続され、第2の配線(2nd Line)とトランジスタ260のドレイン電極層とは、電気的に接続されている。また、第3の配線(3rd Line)とトランジスタ262のソース電極層またはドレイン電極層の一方とは、電気的に接続され、第4の配線(4th Line)と、トランジスタ262のゲート電極層とは、電気的に接続されている。そして、トランジスタ260のゲート電極層と、トランジスタ262のソース電極層またはドレイン電極層の他方は、容量素子164の電極の一方と電気的に接続され、第5の配線(5th Line)と、容量素子164の電極の他方は電気的に接続されている。20

**【0214】**

図9(A)に示す半導体装置では、トランジスタ260のゲート電極層の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。30

**【0215】**

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ262がオン状態となる電位にして、トランジスタ262をオン状態とする。これにより、第3の配線の電位が、トランジスタ260のゲート電極層、および容量素子164に与えられる。すなわち、トランジスタ260のゲート電極層には、所定の電荷が与えられる（書き込み）。ここでは、異なる二つの電位レベルを与える電荷（以下Lowレベルに相当する電荷、Highレベルに相当する電荷という）のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ262がオフ状態となる電位にして、トランジスタ262をオフ状態とすることにより、トランジスタ260のゲート電極層に与えられた電荷が保持される（保持）。40

**【0216】**

トランジスタ262のオフ電流は極めて小さいため、トランジスタ260のゲート電極層の電荷は長時間にわたって保持される。

**【0217】**

次に情報の読み出しについて説明する。第1の配線に所定の電位（定電位）を与えた状態で、第5の配線に適切な電位（読み出し電位）を与えると、トランジスタ260のゲート電極層に保持された電荷量に応じて、第2の配線は異なる電位をとる。一般に、トランジスタ260をnチャネル型とすると、トランジスタ260のゲート電極層にHighレベルに相当する電荷が与えられている場合の見かけのしきい値 $V_{th\_H}$ は、トランジスタ260のゲート電極層にLowレベルに相当する電荷が与えられている場合の見かけのし

きい値  $V_{th\_L}$  より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ 260 を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を  $V_{th\_H}$  と  $V_{th\_L}$  の間の電位  $V_0$  とすることにより、トランジスタ 260 のゲート電極層に与えられた電荷を判別できる。例えば、書き込みにおいて、High レベルに相当する電荷が与えられていた場合には、第5の配線の電位が  $V_0$  ( $> V_{th\_H}$ ) となれば、トランジスタ 260 は「オン状態」となる。Low レベルに相当する電荷が与えられていた場合には、第5の配線の電位が  $V_0$  ( $< V_{th\_L}$ ) となっても、トランジスタ 260 は「オフ状態」のままである。このため、第2の配線の電位から、保持されている情報を読み出すことができる。

## 【0218】

10

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極層の状態にかかわらずトランジスタ 260 が「オフ状態」となるような電位、つまり、 $V_{th\_H}$  より小さい電位を第5の配線に与えればよい。または、ゲート電極層の状態にかかわらずトランジスタ 260 が「オン状態」となるような電位、つまり、 $V_{th\_L}$  より大きい電位を第5の配線に与えればよい。

## 【0219】

図9(B)に図9(A)とは異なる記憶装置の構造の一形態の例を示す。図9(B)は、半導体装置の回路構成の一例を示し、図9(C)は半導体装置の一例を示す概念図である。まず、図9(B)に示す半導体装置について説明を行い、続けて図9(C)に示す半導体装置について、以下説明を行う。

20

## 【0220】

図9(B)に示す半導体装置において、ビット線 BL とトランジスタ 262 のソース電極層またはドレイン電極層とは電気的に接続され、ワード線 WL とトランジスタ 262 のゲート電極層とは電気的に接続され、トランジスタ 262 のソース電極層またはドレイン電極層と容量素子 254 の第1の端子とは電気的に接続されている。

## 【0221】

酸化物半導体を用いたトランジスタ 262 は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ 262 をオフ状態とすることで、容量素子 254 の第1の端子の電位(または、容量素子 254 に蓄積された電荷)を極めて長時間にわたって保持することが可能である。

30

## 【0222】

次に、図9(B)に示す半導体装置(メモリセル 250)に、情報の書き込みおよび保持を行う場合について説明する。

## 【0223】

まず、ワード線 WL の電位を、トランジスタ 262 がオン状態となる電位として、トランジスタ 262 をオン状態とする。これにより、ビット線 BL の電位が、容量素子 254 の第1の端子に与えられる(書き込み)。その後、ワード線 WL の電位を、トランジスタ 262 がオフ状態となる電位として、トランジスタ 262 をオフ状態とすることにより、容量素子 254 の第1の端子の電位が保持される(保持)。

40

## 【0224】

トランジスタ 262 のオフ電流は極めて小さいから、容量素子 254 の第1の端子の電位(または容量素子に蓄積された電荷)を長時間にわたって保持することができる。

## 【0225】

次に、情報の読み出しについて説明する。トランジスタ 262 がオン状態となると、浮遊状態であるビット線 BL と容量素子 254 とが導通し、ビット線 BL と容量素子 254 の間に電荷が再分配される。その結果、ビット線 BL の電位が変化する。ビット線 BL の電位の変化量は、容量素子 254 の第1の端子の電位(または容量素子 254 に蓄積された電荷)によって、異なる値をとる。

## 【0226】

50

例えば、容量素子 254 の第 1 の端子の電位を V、容量素子 254 の容量を C、ビット線 BL が有する容量成分（以下、ビット線容量とも呼ぶ）を CB、電荷が再分配される前のビット線 BL の電位を VBO とすると、電荷が再分配された後のビット線 BL の電位は、 $(CB \cdot VBO + C \cdot V) / (CB + C)$  となる。従って、メモリセル 250 の状態として、容量素子 254 の第 1 の端子の電位が V1 と V0 ( $V1 > V0$ ) の 2 状態をとるとすると、電位 V1 を保持している場合のビット線 BL の電位 ( $= CB \cdot VBO + C \cdot V1$ ) / ( $CB + C$ ) は、電位 V0 を保持している場合のビット線 BL の電位 ( $= CB \cdot VBO + C \cdot V0$ ) / ( $CB + C$ ) よりも高くなることがわかる。

#### 【0227】

そして、ビット線 BL の電位を所定の電位と比較することで、情報を読み出すことができる。10

#### 【0228】

このように、図 9 (B) に示す半導体装置は、トランジスタ 262 のオフ電流が極めて小さいという特徴から、容量素子 254 に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、または、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することができる。

#### 【0229】

次に、図 9 (C) に示す半導体装置について、説明を行う。20

#### 【0230】

図 9 (C) に示す半導体装置は、上部に記憶回路として図 9 (B) に示したメモリセル 250 を複数有するメモリセルアレイ 251a およびメモリセルアレイ 251b を有し、下部に、メモリセルアレイ 251 (メモリセルアレイ 251a およびメモリセルアレイ 251b) を動作させるために必要な周辺回路 253 を有する。なお、周辺回路 253 は、メモリセルアレイ 251 と電気的に接続されている。

#### 【0231】

図 9 (C) に示した構成とすることにより、周辺回路 253 をメモリセルアレイ 251 (メモリセルアレイ 251a およびメモリセルアレイ 251b) の直下に設けることができるため半導体装置の小型化を図ることができる。30

#### 【0232】

周辺回路 253 に設けられるトランジスタは、トランジスタ 262 とは異なる半導体材料を用いるのがより好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、またはガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、前記トランジスタにより、高速動作が要求される各種回路（論理回路、駆動回路など）を好適に実現することが可能である。

#### 【0233】

なお、図 9 (C) に示した半導体装置では、2 つのメモリセルアレイ 251 (メモリセルアレイ 251a と、メモリセルアレイ 251b) が積層された構成を例示したが、積層するメモリセルアレイの数はこれに限定されない。3 つ以上のメモリセルアレイを積層する構成としてもよい。

#### 【0234】

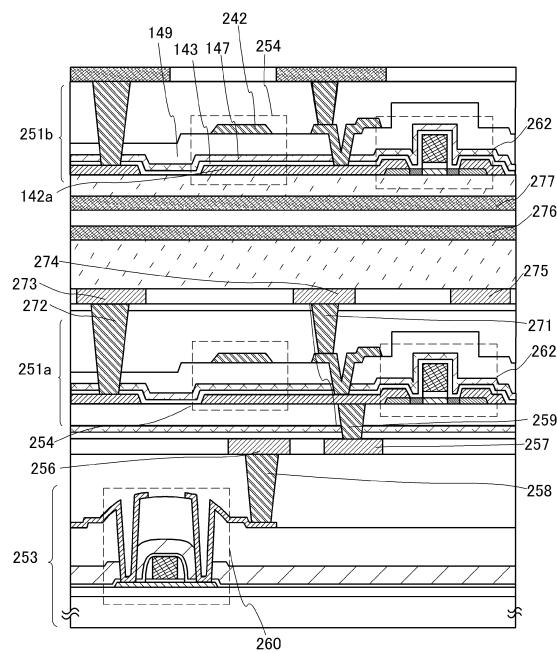

図 10 に、図 9 (C) に示す半導体装置の断面図の一例を示す。図 10 に示す断面図は、周辺回路 253 に含まれるトランジスタ 260 と、メモリセルアレイ 251a およびメモリセルアレイ 251b に含まれるトランジスタ 262 および容量素子 254 を示している。

#### 【0235】

なお、トランジスタ 260 およびトランジスタ 262 は、図 7 に示すトランジスタ 160 50

およびトランジスタ 162 と同様の構成のトランジスタをそれぞれ適用することができるため、詳細な説明は省略する。

**【0236】**

メモリセルアレイ 251a およびメモリセルアレイ 251b が有する容量素子 254 はトランジスタ 262 のソース電極層 142a、窒化シリコン膜 143、絶縁膜 147、絶縁膜 149 および導電層 242 を有する。つまり、トランジスタ 262 のソース電極層 142a は容量素子 254 の一方の電極として機能し、窒化シリコン膜 143、絶縁膜 147、および絶縁膜 149 は容量素子 254 の誘電体として機能し、導電層 242 は容量素子 254 の他方の電極として機能する。

**【0237】**

周辺回路 253 とメモリセルアレイ 251aとの間には、周辺回路 253 およびメモリセルアレイ 251a を電気的に接続するための配線層が設けられている。配線層 258 は、周辺回路 253 が有するトランジスタ 260 のドレイン電極層と導電層 256 とを電気的に接続し、導電層 256 と同一工程で形成された導電層 257 は、配線層 259 を介して、メモリセルアレイ 251a が有するトランジスタ 262 のソース電極層と電気的に接続している。

**【0238】**

メモリセルアレイ 251a およびメモリセルアレイ 251b の間にも同様に、メモリセルアレイ 251a およびメモリセルアレイ 251b を電気的に接続するための配線層が設けられている。詳細な説明は省略するが、配線層 271、配線層 272、導電層 273、導電層 274、導電層 275、導電層 276 および導電層 277 を介してメモリセルアレイ 251a およびメモリセルアレイ 251b は電気的に接続している。

**【0239】**

トランジスタ 262 として、酸化物半導体をチャネル形成領域に用いるトランジスタを適用することによって、長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、または、リフレッシュ動作の頻度が極めて少ない半導体装置とすることが可能となるため、消費電力を十分に低減することができる。

**【0240】**

また、トランジスタ 262 として実施の形態 1 および実施の形態 2 に示すトランジスタを用いることができる。トランジスタ 262 は、酸化物半導体膜上に窒化シリコン膜を接して成膜することによって、酸化物半導体膜に窒素を添加し、酸化物半導体膜 144 に低抵抗領域を形成することができる。したがって、オン特性に優れ、電気的特性の良好なトランジスタとすることができます、半導体装置の高速応答、高速動作を可能とする。

**【0241】**

(実施の形態 5 )

本実施の形態では、先の実施の形態で示した半導体装置を携帯電話、スマートフォン、電子書籍などの電子機器に応用した場合の例を図 11 乃至図 14 を用いて説明する。

**【0242】**

携帯電話、スマートフォン、電子書籍などの電子機器においては、画像データの一時記憶などに S R A M または D R A M が使用されている。S R A M または D R A M が使用される理由としてはフラッシュメモリでは応答が遅く、画像処理には不向きであるためである。一方で、S R A M または D R A M を画像データの一時記憶に用いた場合、以下の特徴がある。

**【0243】**

通常の S R A M は、図 11 (A) に示すように 1 つのメモリセルがトランジスタ 801 ~ 806 の 6 個のトランジスタで構成されており、それを X デコーダー 807、Y デコーダー 808 にて駆動している。トランジスタ 803 とトランジスタ 805、トランジスタ 804 とトランジスタ 806 はインバータを構成し、高速駆動を可能としている。しかし 1 つのメモリセルが 6 トランジスタで構成されているため、セル面積が大きいという欠点がある。デザインルールの最小寸法を F としたときに S R A M のメモリセル面積は通常 10

10

20

30

40

50

$0 \sim 150\text{F}^2$  である。このため S R A M はビットあたりの単価が各種メモリの中でも高い。

#### 【0244】

それに対して、D R A M はメモリセルが図 11 (B) に示すようにトランジスタ 811、保持容量 812 によって構成され、それを X デコーダー 813、Y デコーダー 814 にて駆動している。1つのセルが 1トランジスタ、1容量の構成になっており、面積が小さい。D R A M のメモリセル面積は通常  $10\text{F}^2$  以下である。ただし、D R A M は常にリフレッシュが必要であり、書き換えを行わない場合でも電力を消費する。

#### 【0245】

しかし、先の実施の形態で説明した半導体装置のメモリセル面積は、 $10\text{F}^2$  前後であり、かつ頻繁なリフレッシュは不要である。したがって、メモリセル面積が縮小され、かつ消費電力を低減することができる。また、先の実施の形態に示した半導体装置を用いることによって、外部からの水素、水等の混入による影響を受けにくい、信頼性の高い半導体装置とすることができます。

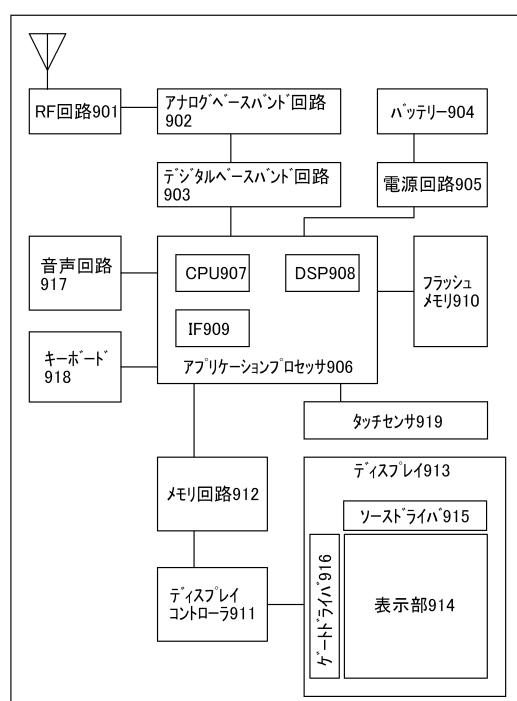

#### 【0246】

図 12 に電子機器のブロック図を示す。図 12 に示す電子機器は R F 回路 901、アナログベースバンド回路 902、デジタルベースバンド回路 903、バッテリー 904、電源回路 905、アプリケーションプロセッサ 906、フラッシュメモリ 910、ディスプレイコントローラ 911、メモリ回路 912、ディスプレイ 913、タッチセンサ 919、音声回路 917、キーボード 918 などより構成されている。ディスプレイ 913 は表示部 914、ソースドライバ 915、ゲートドライバ 916 によって構成されている。アプリケーションプロセッサ 906 は C P U 907、D S P 908、インターフェイス (I F) 909 を有している。一般にメモリ回路 912 は S R A M または D R A M で構成されており、この部分に先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、かつ消費電力が十分に低減された信頼性の高い電子機器を提供することができる。

#### 【0247】

図 13 に、ディスプレイのメモリ回路 950 に先の実施の形態で説明した半導体装置を使用した例を示す。図 13 に示すメモリ回路 950 は、メモリ 952、メモリ 953、スイッチ 954、スイッチ 955 およびメモリコントローラ 951 により構成されている。また、メモリ回路は、信号線から入力された画像データ（入力画像データ）、メモリ 952 およびメモリ 953 に記憶されたデータ（記憶画像データ）を読み出し、および制御を行うディスプレイコントローラ 956 と、ディスプレイコントローラ 956 からの信号により表示するディスプレイ 957 が接続されている。

#### 【0248】

まず、ある画像データがアプリケーションプロセッサ（図示しない）によって、形成される（入力画像データ A）。入力画像データ A は、スイッチ 954 を介してメモリ 952 に記憶される。そしてメモリ 952 に記憶された画像データ（記憶画像データ A）は、スイッチ 955、およびディスプレイコントローラ 956 を介してディスプレイ 957 に送られ、表示される。

#### 【0249】

入力画像データ A に変更が無い場合、記憶画像データ A は、通常  $30 \sim 60\text{Hz}$  程度の周期でメモリ 952 からスイッチ 955 を介して、ディスプレイコントローラ 956 から読み出される。

#### 【0250】

次に、例えばユーザーが画面を書き換える操作をしたとき（すなわち、入力画像データ A に変更が有る場合）、アプリケーションプロセッサは新たな画像データ（入力画像データ B）を形成する。入力画像データ B はスイッチ 954 を介してメモリ 953 に記憶される。この間も定期的にメモリ 952 からスイッチ 955 を介して記憶画像データ A は読み出されている。メモリ 953 に新たな画像データ（記憶画像データ B）が記憶し終わると、

10

20

30

40

50

ディスプレイ 957 の次のフレームより、記憶画像データ B は読み出され、スイッチ 955、およびディスプレイコントローラ 956 を介して、ディスプレイ 957 に記憶画像データ B が送られ、表示がおこなわれる。この読み出しはさらに次に新たな画像データがメモリ 952 に記憶されるまで継続される。

#### 【0251】

このようにメモリ 952 およびメモリ 953 は交互に画像データの書き込みと、画像データの読み出しを行うことによって、ディスプレイ 957 の表示をおこなう。なお、メモリ 952 およびメモリ 953 はそれぞれ別のメモリには限定されず、1つのメモリを分割して使用してもよい。先の実施の形態で説明した半導体装置をメモリ 952 およびメモリ 953 に採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、かつ消費電力を十分に低減することができる。また、外部からの水、水分等の混入の影響を受けにくい信頼性の高い半導体装置とすることができる。10

#### 【0252】

図 14 に電子書籍のブロック図を示す。図 14 はバッテリー 1001、電源回路 1002、マイクロプロセッサ 1003、フラッシュメモリ 1004、音声回路 1005、キーボード 1006、メモリ回路 1007、タッチパネル 1008、ディスプレイ 1009、ディスプレイコントローラ 1010 によって構成される。

#### 【0253】

ここでは、図 14 のメモリ回路 1007 に先の実施の形態で説明した半導体装置を使用することができる。メモリ回路 1007 は書籍の内容を一時的に保持する機能を持つ。例えば、ユーザーがハイライト機能を使用する場合、メモリ回路 1007 は、ユーザーが指定した箇所の情報を記憶し、保持する。なおハイライト機能とは、ユーザーが電子書籍を読んでいるときに、特定の箇所にマーキング、例えば、表示の色を変える、アンダーラインを引く、文字を太くする、文字の書体を変えるなどによってマーキングして周囲との違いを示すことである。メモリ回路 1007 は短期的な情報の記憶に用い、長期的な情報の保存にはフラッシュメモリ 1004 に、メモリ回路 1007 が保持しているデータをコピーしてもよい。このような場合においても、先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、かつ消費電力を十分に低減することができる。また、外部からの水、水分等の混入の影響を受けにくい信頼性の高い半導体装置とすることができる。20

#### 【0254】

図 15 に電子機器の具体例を示す。図 15 (A) および図 15 (B) は、2つ折り可能なタブレット型端末である。図 15 (A) は、開いた状態であり、タブレット型端末は、筐体 9630、表示部 9631a、表示部 9631b、表示モード切り替えスイッチ 9034、電源スイッチ 9035、省電力モード切り替えスイッチ 9036、留め具 9033、操作スイッチ 9038 を有する。

#### 【0255】

実施の形態 1 または実施の形態 2 に示す半導体装置は、表示部 9631a、表示部 9631b に用いることが可能であり、信頼性の高いタブレット型端末とすることが可能となる。また、先の実施の形態に示す記憶装置を本実施の形態の半導体装置に適用してもよい。40

#### 【0256】

表示部 9631a は、一部をタッチパネルの領域 9632a とすることができます、表示された操作キー 9638 にふれることでデータ入力をすることができる。なお、表示部 9631a においては、一例として半分の領域が表示のみの機能を有する構成、もう半分の領域がタッチパネルの機能を有する構成を示しているが、該構成に限定されない。表示部 9631a の全面をキーボードボタン表示させてタッチパネルとし、表示部 9631b を表示画面として用いることができる。

#### 【0257】

また、表示部 9631b においても表示部 9631a と同様に、表示部 9631b の一部をタッチパネルの領域 9632b とすることができます。また、タッチパネルのキーボード

10

20

30

40

50

表示切り替えボタン 9 6 3 9 が表示されている位置に指やスタイルスなどでふれることで表示部 9 6 3 1 b にキーボードボタン表示することができる。

【 0 2 5 8 】

また、タッチパネルの領域 9 6 3 2 a とタッチパネルの領域 9 6 3 2 b に対して同時にタッチ入力することもできる。

【 0 2 5 9 】

また、表示モード切り替えスイッチ 9 0 3 4 は、縦表示または横表示などの表示の向きを切り替え、白黒表示やカラー表示の切り替えなどを選択できる。省電力モード切り替えスイッチ 9 0 3 6 は、タブレット型端末に内蔵している光センサで検出される使用時の外光の光量に応じて表示の輝度を最適なものとすることができます。タブレット型端末は光センサだけでなく、ジャイロ、加速度センサ等の傾きを検出するセンサなどの他の検出装置を内蔵させてもよい。10

【 0 2 6 0 】

また、図 15 ( A ) では表示部 9 6 3 1 b と表示部 9 6 3 1 a の表示面積が同じ例を示しているが特に限定されず、一方のサイズともう一方のサイズが異なっていてもよく、表示の品質も異なっていてもよい。例えば一方が他方よりも高精細な表示を行える表示パネルとしてもよい。

【 0 2 6 1 】

図 15 ( B ) は、閉じた状態であり、タブレット型端末は、筐体 9 6 3 0 、太陽電池 9 6 3 3 、充放電制御回路 9 6 3 4 、バッテリー 9 6 3 5 、DCDC コンバータ 9 6 3 6 を有する。なお、図 15 ( B ) では充放電制御回路 9 6 3 4 の一例としてバッテリー 9 6 3 5 、DCDC コンバータ 9 6 3 6 を有する構成について示している。20

【 0 2 6 2 】

なお、タブレット型端末は 2 つ折り可能なため、未使用時に筐体 9 6 3 0 を閉じた状態にすることができる。従って、表示部 9 6 3 1 a 、表示部 9 6 3 1 b を保護できるため、耐久性に優れ、長期使用の観点からも信頼性の優れたタブレット型端末を提供できる。

【 0 2 6 3 】

また、この他にも図 15 ( A ) および図 15 ( B ) に示したタブレット型端末は、様々な情報（静止画、動画、テキスト画像など）を表示する機能、カレンダー、日付または時刻などを表示部に表示する機能、表示部に表示した情報をタッチ入力操作または編集するタッチ入力機能、様々なソフトウェア（プログラム）によって処理を制御する機能、等を有することができる。30

【 0 2 6 4 】

タブレット型端末の表面に装着された太陽電池 9 6 3 3 によって、電力をタッチパネル、表示部、または映像信号処理部等に供給することができる。なお、太陽電池 9 6 3 3 は、筐体 9 6 3 0 の片面または両面に設けることができ、バッテリー 9 6 3 5 の充電を効率的に行う構成とすることができる。なおバッテリー 9 6 3 5 としては、リチウムイオン電池を用いると、小型化を図れる等の利点がある。

【 0 2 6 5 】

また、図 15 ( B ) に示す充放電制御回路 9 6 3 4 の構成、および動作について図 15 ( C ) にブロック図を示し説明する。図 15 ( C ) には、太陽電池 9 6 3 3 、バッテリー 9 6 3 5 、DCDC コンバータ 9 6 3 6 、コンバータ 9 6 3 7 、スイッチ SW 1 乃至 SW 3 、表示部 9 6 3 1 について示しており、バッテリー 9 6 3 5 、DCDC コンバータ 9 6 3 6 、コンバータ 9 6 3 7 、スイッチ SW 1 乃至 SW 3 が、図 15 ( B ) に示す充放電制御回路 9 6 3 4 に対応する箇所となる。40

【 0 2 6 6 】

まず外光により太陽電池 9 6 3 3 により発電がされる場合の動作の例について説明する。太陽電池で発電した電力は、バッテリー 9 6 3 5 を充電するための電圧となるよう DCDC コンバータ 9 6 3 6 で昇圧または降圧がなされる。そして、表示部 9 6 3 1 の動作に太陽電池 9 6 3 3 からの電力が用いられる際にはスイッチ SW 1 をオンにし、コンバータ 950

637で表示部9631に必要な電圧に昇圧または降圧をすることとなる。また、表示部9631での表示を行わない際には、SW1をオフにし、SW2をオンにしてバッテリー9635の充電を行う構成とすればよい。

#### 【0267】

なお太陽電池9633については、発電手段の一例として示したが、特に限定されず、圧電素子（ピエゾ素子）や熱電変換素子（ペルティ工素子）などの他の発電手段によるバッテリー9635の充電を行う構成であってもよい。例えば、無線（非接触）で電力を送受信して充電する無接点電力伝送モジュールや、また他の充電手段を組み合わせて行う構成としてもよい。

#### 【0268】

以上のように、本実施の形態に示す電子機器には、先の実施の形態に係る半導体装置が搭載されている。このため、読み出しが高速で、長期間の記憶保持が可能で、かつ消費電力を低減した電子機器が実現される。また、外部からの水、水分等の混入の影響を受けにくい信頼性の高い半導体装置とすることができる。

#### 【0269】

本実施の形態に示す構成、方法などは、他の実施の形態に示す構成、方法などと適宜組み合わせて用いることができる。

#### 【実施例1】

#### 【0270】

本実施例では、本発明の一態様の半導体装置に適用できる窒化シリコン膜の評価結果について説明する。詳細には、TDS、SIMS、RBSによる結果を示す。

#### 【0271】

本実施例において評価した試料の作製方法について説明する。

#### 【0272】

試料A1として、シリコンウェハ上に厚さ300nmの窒化シリコン膜を成膜した。窒化シリコン膜の成膜はシリコンウェハをプラズマCVD装置の処理室内に設置し、処理室内的圧力を100Paに制御し、27.12MHzの高周波電源で2000Wの電力を供給した。なお、該プラズマCVD装置は電極面積が6000cm<sup>2</sup>である平行平板型のプラズマCVD装置であり、電力密度は $3.2 \times 10^{-1} W/cm^2$ となる。また、基板温度は350とした。供給ガスをシランと窒素の混合ガス(SiH<sub>4</sub>流量200sccm:N<sub>2</sub>流量5000sccm)とした。

#### 【0273】

試料A2として、シリコンウェハ上に厚さ300nmの窒化シリコン膜を成膜した。窒化シリコン膜の成膜はシリコンウェハをプラズマCVD装置の処理室内に設置し、処理室内的圧力を100Paに制御し、27.12MHzの高周波電源で2000W(電力密度としては $3.2 \times 10^{-1} W/cm^2$ )の電力を供給した。また、基板温度は350とした。供給ガスはシランと窒素とアンモニアの混合ガス(SiH<sub>4</sub>流量200sccm:N<sub>2</sub>流量2000sccm:NH<sub>3</sub>流量100sccm)とした。

#### 【0274】

また、比較例試料として、シリコンウェハ上に厚さ300nmの窒化シリコン膜を成膜した。窒化シリコン膜の成膜はシリコンウェハをプラズマCVD装置の処理室内に設置し、処理室内的圧力を100Paに制御し、27.12MHzの高周波電源で2000Wの電力(電力密度としては $3.2 \times 10^{-1} W/cm^2$ )を供給した。また、基板温度は350とした。供給ガスはシランと窒素とアンモニアの混合ガス(SiH<sub>4</sub>流量200sccm:N<sub>2</sub>流量2000sccm:NH<sub>3</sub>流量2000sccm)とした。

#### 【0275】

試料A1および試料A2は、本発明の一態様の半導体装置に用いる窒化シリコン膜として適する、供給ガス中の窒素に対するアンモニアの流量比が0.1倍以下を満たす条件で成膜された窒化シリコン膜である。一方比較例試料は、本発明の一態様の半導体装置に用いる窒化シリコン膜としては適さない条件で成膜された窒化シリコン膜である。

10

20

30

40

50

**【0276】**

試料A1、試料A2および比較例試料に対して、TDS測定を行った。図16に各試料の基板温度に対する水素分子脱離量を示す。図16において、横軸は基板温度を示し、縦軸は水素分子脱離量に相当するTDS強度を示している。

**【0277】**

TDSの結果を示す曲線におけるピークは、分析した試料（本実施例では試料A1、試料A2、比較例試料）に含まれる原子または分子が外部に脱離されることで現れるピークである。なお、外部に脱離される原子または分子の総量は、各曲線の積分値に比例する。それゆえ、当該ピーク強度の高低によって窒化シリコン膜に含まれる原子または分子の総量を比較できる。なお、本実施例では、50から570の範囲における水素分子の脱離量を定量値として取得した。10

**【0278】**

図16より、比較例試料は加熱処理によって基板温度350付近から水素分子が脱離はじめ、500付近にその水素分子脱離量のピークを有していることが確認された。一方で、試料A1および試料A2には、500以下では水素分子脱離量のピークが見られなかった。

**【0279】**

試料A1、試料A2、比較例試料におけるそれぞれの水素分子脱離量の定量値は、試料A1が $7.35 \times 10^{19}$ 個/cm<sup>3</sup>であり、試料A2が $9.00 \times 10^{19}$ 個/cm<sup>3</sup>であり、比較例試料が $7.75 \times 10^{20}$ 個/cm<sup>3</sup>であった。20

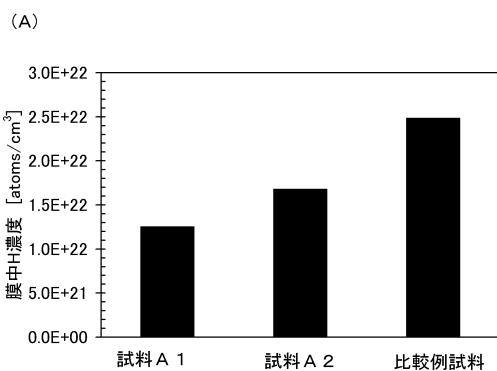

**【0280】**

続いて、試料A1、試料A2、比較例試料におけるSIMSを行い窒化シリコン膜中の水素濃度を測定した。図17(A)にSIMS結果を示す。

**【0281】**

試料A1に含まれる水素濃度は、 $1.25 \times 10^{22}$ atoms/cm<sup>3</sup>であり、試料A2に含まれる水素濃度は、 $1.67 \times 10^{22}$ atoms/cm<sup>3</sup>であり、比較例試料に含まれる水素濃度は $2.48 \times 10^{22}$ atoms/cm<sup>3</sup>であった。したがって、試料A1および試料A2には比較例試料に対して膜中に含まれる水素濃度が低減されていることが確認できた。30

**【0282】**

続いて、試料A1、試料A2、比較例試料の組成をRBSによって測定した。図17(B)にRBS分析の定量値を示す。

**【0283】**

図17(B)の縦軸は、各試料が含有するシリコン(Si)、窒素(N)、水素(H)の割合(atOMIC%)の値である。試料A1には、シリコンが39.5atOMIC%、窒素が50.6atOMIC%、水素が9.9atOMIC%含有されていることが確認された。試料A2には、シリコンが36.2atOMIC%、窒素が50.3atOMIC%、水素が13.5atOMIC%含有されていることが確認された。比較例試料にはシリコンが31.6atOMIC%、窒素が47.6atOMIC%、水素が20.8atOMIC%含有されていることが確認された。したがって、試料A1および試料A2は比較例試料に比べて、水素の割合が低減されていることが確認された。40

**【0284】**

本実施例において作製された膜は、水素分子の脱離量が少なく、かつ膜中の水素濃度も低減されている。よって当該膜は、本発明の一態様の半導体装置に適用される膜として好適である。

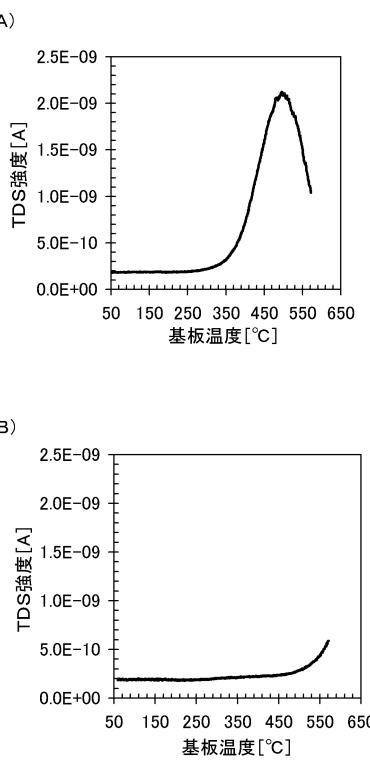

**【実施例2】****【0285】**

本実施例では、本発明の一態様の半導体装置に用いる窒化シリコン膜の水素のプロッキング性について評価を行った。評価方法としては、TDSを行った。

**【0286】**1020304050

まず、シリコンウェハ上に、窒化シリコン膜B1を膜厚275nmで成膜した。窒化シリコン膜B1としては、実施例1に示した比較例試料と同一の条件を用いて成膜した。

#### 【0287】

図18(A)に、窒化シリコン膜B1のTDS結果を示す。図18(A)の横軸は基板温度を示し、縦軸は基板温度に対する水素分子の脱離量を示している。窒化シリコン膜B1は、TDSによる加熱によって、350付近から水素分子が脱離しあり、500付近において、水素分子脱離量のピークが検出された。また、図18(A)に示すTDSにおける水素分子脱離量の定量値は $7.75 \times 10^{20}$ 個/cm<sup>3</sup>である。

#### 【0288】

続いて、窒化シリコン膜B1の上に、実施例1で示したように、本発明の一態様の半導体装置に適用することができる窒化シリコン膜B2を膜厚50nmで積層し、試料Cを作製した。窒化シリコン膜B2は、実施例1に示した試料A1に用いた窒化シリコン膜と同一の条件を用いて形成した。

#### 【0289】

図18(B)に、試料Cの基板温度に対する水素分子脱離量を示す。

#### 【0290】

図18(B)に示すように、試料Cでは、550以下において、水素分子脱離量のピークが見られなかった。また、試料Cにおける水素分子脱離量の定量値は、 $1.10 \times 10^{20}$ 個/cm<sup>3</sup>である。従って、窒化シリコン膜B1膜上に、本発明の一態様の半導体装置に用いる窒化シリコン膜B2を積層して設けることによって、窒化シリコン膜B1単膜の場合に見られた水素分子の脱離を抑制できることが確認された。

#### 【0291】

したがって、本発明の一態様の半導体装置に適用することができる窒化シリコン膜は、水素に対するブロッキング性を有することが確認された。

#### 【符号の説明】

#### 【0292】

|       |         |    |

|-------|---------|----|

| 100   | 基板      |    |

| 102   | 下地絶縁膜   |    |

| 108   | ゲート絶縁膜  |    |

| 110   | ゲート電極層  | 30 |

| 116   | 半導体層    |    |

| 120 a | 側壁絶縁膜   |    |

| 120 b | 側壁絶縁膜   |    |

| 124 a | ソース電極層  |    |

| 124 b | ドレイン電極層 |    |

| 125   | 絶縁膜     |    |

| 131   | 絶縁膜     |    |

| 133   | 絶縁膜     |    |

| 135   | 絶縁膜     |    |

| 137   | 絶縁膜     | 40 |

| 141 a | 導電層     |    |

| 141 b | 導電層     |    |

| 142 a | ソース電極層  |    |

| 142 b | ドレイン電極層 |    |

| 143   | 窒化シリコン膜 |    |

| 144   | 酸化物半導体膜 |    |

| 144 a | 低抵抗領域   |    |

| 144 b | 低抵抗領域   |    |

| 144 c | 低抵抗領域   |    |

| 144 d | 低抵抗領域   | 50 |

|         |          |    |

|---------|----------|----|

| 1 4 4 e | チャネル形成領域 |    |

| 1 4 5   | 配線層      |    |

| 1 4 6   | ゲート絶縁膜   |    |

| 1 4 7   | 絶縁膜      |    |

| 1 4 8   | ゲート電極層   |    |

| 1 4 9   | 絶縁膜      |    |

| 1 5 1   | 絶縁膜      |    |

| 1 5 3   | 絶縁膜      |    |

| 1 5 5   | 絶縁膜      |    |

| 1 5 7   | 絶縁膜      | 10 |

| 1 5 9   | 配線層      |    |

| 1 6 0   | トランジスタ   |    |

| 1 6 2   | トランジスタ   |    |

| 1 6 4   | 容量素子     |    |

| 2 0 1   | トランジスタ   |    |

| 2 0 2   | トランジスタ   |    |

| 2 0 3   | トランジスタ   |    |

| 2 0 4   | トランジスタ   |    |

| 2 1 1   | トランジスタ   |    |

| 2 1 2   | トランジスタ   | 20 |

| 2 1 3   | トランジスタ   |    |

| 2 1 4   | トランジスタ   |    |

| 2 4 2   | 導電層      |    |

| 2 5 0   | メモリセル    |    |

| 2 5 1   | メモリセルアレイ |    |

| 2 5 1 a | メモリセルアレイ |    |

| 2 5 1 b | メモリセルアレイ |    |

| 2 5 3   | 周辺回路     |    |

| 2 5 4   | 容量素子     |    |

| 2 5 6   | 導電層      | 30 |

| 2 5 7   | 導電層      |    |

| 2 5 8   | 配線層      |    |

| 2 5 9   | 配線層      |    |

| 2 6 0   | トランジスタ   |    |

| 2 6 2   | トランジスタ   |    |

| 2 7 1   | 配線層      |    |

| 2 7 2   | 配線層      |    |

| 2 7 3   | 導電層      |    |

| 2 7 4   | 導電層      |    |

| 2 7 5   | 導電層      | 40 |

| 2 7 6   | 導電層      |    |

| 2 7 7   | 導電層      |    |

| 4 0 0   | 基板       |    |

| 4 0 1   | ゲート電極層   |    |

| 4 0 2   | ゲート絶縁膜   |    |

| 4 0 3   | チャネル形成領域 |    |

| 4 0 3 a | 領域       |    |

| 4 0 3 b | 領域       |    |

| 4 0 4 a | 低抵抗領域    |    |

| 4 0 4 b | 低抵抗領域    | 50 |

|         |               |    |

|---------|---------------|----|

| 4 0 5 a | ソース電極層        |    |

| 4 0 5 b | ドレイン電極層       |    |

| 4 0 6 a | 低抵抗領域         |    |

| 4 0 6 b | 低抵抗領域         |    |

| 4 0 7   | 窒化シリコン膜       |    |

| 4 0 8 a | 低抵抗領域         |    |

| 4 0 8 b | 低抵抗領域         |    |

| 4 0 9   | 酸化物半導体膜       |    |

| 4 1 0 a | 低抵抗領域         | 10 |

| 4 1 0 b | 低抵抗領域         |    |

| 4 1 1   | 層間絶縁膜         |    |

| 4 1 2   | 絶縁膜           |    |

| 4 1 3 a | 側壁絶縁膜         |    |

| 4 1 3 b | 側壁絶縁膜         |    |

| 4 1 4   | 層間絶縁膜         |    |

| 4 2 0   | トランジスタ        |    |

| 4 2 1   | 不純物元素         |    |

| 4 3 0   | トランジスタ        |    |

| 4 3 6   | 下地絶縁膜         |    |

| 4 3 8   | 下地絶縁膜         | 20 |

| 5 0 9   | 酸化物半導体膜       |    |

| 5 2 0   | トランジスタ        |    |

| 5 3 0   | トランジスタ        |    |

| 5 4 0   | トランジスタ        |    |

| 8 0 1   | トランジスタ        |    |

| 8 0 3   | トランジスタ        |    |

| 8 0 4   | トランジスタ        |    |

| 8 0 5   | トランジスタ        |    |

| 8 0 6   | トランジスタ        |    |

| 8 0 7   | X デコーダー       | 30 |

| 8 0 8   | Y デコーダー       |    |

| 8 1 1   | トランジスタ        |    |

| 8 1 2   | 保持容量          |    |

| 8 1 3   | X デコーダー       |    |

| 8 1 4   | Y デコーダー       |    |

| 9 0 1   | R F 回路        |    |

| 9 0 2   | アナログベースバンド回路  |    |

| 9 0 3   | デジタルベースバンド回路  |    |

| 9 0 4   | バッテリー         |    |

| 9 0 5   | 電源回路          | 40 |

| 9 0 6   | アプリケーションプロセッサ |    |

| 9 0 7   | C P U         |    |

| 9 0 8   | D S P         |    |

| 9 1 0   | フラッシュメモリ      |    |

| 9 1 1   | ディスプレイコントローラ  |    |

| 9 1 2   | メモリ回路         |    |

| 9 1 3   | ディスプレイ        |    |

| 9 1 4   | 表示部           |    |

| 9 1 5   | ソースドライバ       |    |

| 9 1 6   | ゲートドライバ       | 50 |

|           |               |    |

|-----------|---------------|----|

| 9 1 7     | 音声回路          |    |

| 9 1 8     | キー ボード        |    |

| 9 1 9     | タッチセンサ        |    |

| 9 5 0     | メモリ回路         |    |

| 9 5 1     | メモリコントローラ     |    |

| 9 5 2     | メモリ           |    |

| 9 5 3     | メモリ           |    |

| 9 5 4     | スイッチ          |    |

| 9 5 5     | スイッチ          |    |

| 9 5 6     | ディスプレイコントローラ  | 10 |

| 9 5 7     | ディスプレイ        |    |

| 1 0 0 1   | バッテリー         |    |

| 1 0 0 2   | 電源回路          |    |

| 1 0 0 3   | マイクロプロセッサ     |    |

| 1 0 0 4   | フラッシュメモリ      |    |

| 1 0 0 5   | 音声回路          |    |

| 1 0 0 6   | キー ボード        |    |

| 1 0 0 7   | メモリ回路         |    |

| 1 0 0 8   | タッチパネル        |    |

| 1 0 0 9   | ディスプレイ        | 20 |

| 1 0 1 0   | ディスプレイコントローラ  |    |

| 9 0 3 3   | 留め具           |    |

| 9 0 3 4   | スイッチ          |    |

| 9 0 3 5   | 電源スイッチ        |    |

| 9 0 3 6   | スイッチ          |    |

| 9 0 3 8   | 操作スイッチ        |    |

| 9 6 3 0   | 筐体            |    |

| 9 6 3 1   | 表示部           |    |

| 9 6 3 1 a | 表示部           |    |

| 9 6 3 1 b | 表示部           | 30 |

| 9 6 3 2 a | 領域            |    |

| 9 6 3 2 b | 領域            |    |

| 9 6 3 3   | 太陽電池          |    |

| 9 6 3 4   | 充放電制御回路       |    |

| 9 6 3 5   | バッテリー         |    |

| 9 6 3 6   | D C D C コンバータ |    |

| 9 6 3 7   | コンバータ         |    |

| 9 6 3 8   | 操作キー          |    |

| 9 6 3 9   | ボタン           |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【 四 6 】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

## フロントページの続き

|         |         |           | F I     |        |         |

|---------|---------|-----------|---------|--------|---------|

| H 0 1 L | 27/11   | (2006.01) | H 0 1 L | 29/50  | M       |

| H 0 1 L | 21/8242 | (2006.01) | H 0 1 L | 27/10  | 3 8 1   |

| H 0 1 L | 27/108  | (2006.01) | H 0 1 L | 27/10  | 3 2 1   |

| H 0 1 L | 27/115  | (2017.01) | H 0 1 L | 27/10  | 6 1 5   |

| H 0 1 L | 29/788  | (2006.01) | H 0 1 L | 27/10  | 6 7 1 C |

| H 0 1 L | 29/792  | (2006.01) | H 0 1 L | 27/10  | 6 7 1 Z |

| H 0 1 L | 21/8234 | (2006.01) | H 0 1 L | 27/10  | 4 3 4   |

| H 0 1 L | 27/088  | (2006.01) | H 0 1 L | 29/78  | 3 7 1   |

| G 0 2 F | 1/1368  | (2006.01) | H 0 1 L | 27/08  | 1 0 2 E |

|         |         |           | G 0 2 F | 1/1368 |         |

(72)発明者 佐々木 俊成

栃木県栃木市都賀町升塚161-2 アドバンスト フィルム ディバイス インク株式会社内

審査官 岩本 勉

(56)参考文献 特開2009-141002(JP,A)

米国特許出願公開第2010/0283049(US,A1)

特開2008-141119(JP,A)

特開2010-135462(JP,A)

特開2011-146694(JP,A)

特開2012-023352(JP,A)

特開2011-071503(JP,A)

特開2012-054544(JP,A)

特開2008-283046(JP,A)

特開2012-033836(JP,A)

特開2011-119706(JP,A)

特開2011-109646(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 0 1 L 2 1 / 3 3 6

G 0 2 F 1 / 1 3 6 8

H 0 1 L 2 1 / 2 8

H 0 1 L 2 1 / 8 2 3 4

H 0 1 L 2 1 / 8 2 4 2

H 0 1 L 2 1 / 8 2 4 4

H 0 1 L 2 7 / 0 8 8

H 0 1 L 2 7 / 1 0 8

H 0 1 L 2 7 / 1 1

H 0 1 L 2 7 / 1 1 5

H 0 1 L 2 9 / 4 1 7

H 0 1 L 2 9 / 7 8 6

H 0 1 L 2 9 / 7 8 8

H 0 1 L 2 9 / 7 9 2