(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

C09K 3/14 (2006.01)

(45) 공고일자

2007년08월07일

(11) 등록번호

10-0746883

(24) 등록일자

2007년08월01일

(21) 출원번호 10-2000-0047456

(22) 출원일자 2000년08월17일

심사청구일자 2005년08월02일

(65) 공개번호 10-2001-0067081

(43) 공개일자 2001년07월12일

(30) 우선권주장 1999-368640 1999년12월27일 일본(JP)

(73) 특허권자 가부시키가이샤 히타치세이사쿠쇼

일본국 도쿄토 치요다쿠 마루노우치 1초메 6반 6고

(72) 발명자 곤도세이이찌

일본도쿄도고꾸분지시미나미조2-18-13페밀고꾸분지1408

후지모리마사아끼

일본사이다마깽히끼궁하또야마마찌아까누마2527-311

사구마노리유끼

일본도쿄도하찌오우지시아까쓰끼조1-47-3에프203

홈마요시오

일본도쿄도니시따마궁히노데마찌히라이2196-58

(74) 대리인 구영창

장수길

(56) 선행기술조사문헌

JP07070767 A JP11195628 A

심사관 : 오세주

전체 청구항 수 : 총 21 항

(54) 반도체 장치의 제조 방법

(57) 요약

스크래치나 박리, 디싱, 침식을 억제하고, 또한 빠른 연마 속도로 연마하는 기술을 제공한다.

산화성 물질과, 인산과, 보호막 형성제를 포함하는 연마액으로 연마한다.

대표도

도 3

### 특허청구의 범위

#### 청구항 1.

반도체 기판 표면에 형성된 요철을 갖는 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 금속막을, 상기 금속막 표면을 산화성 물질에 의해 산화시키고, 상기 산화된 금속막 표면의 금속 산화막을 인산에 의해 수용화시켜 금속 이온화함으로써 볼록부를 연마하여 상기 요철을 평탄화하는 반도체 장치의 제조방법으로서, 보호막 형성제를 상기 요철을 갖는 금속막에 형성함으로써 볼록부를 선택적으로 연마하고, 오목부는 연마를 억제하면서 평탄화하는 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 청구항 2.

제1항에 있어서,

상기 산화성 물질은 과산화수소이고, 상기 인산은 오르토인산, 혹은 아인산인 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 청구항 3.

제1항 또는 제2항에 있어서,

상기 보호막 형성제는 벤조트리아졸인 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 청구항 4.

제1항 또는 제2항에 있어서,

상기 보호막 형성제는 카르복실기를 갖는 폴리머인 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 청구항 5.

제1항 또는 제2항에 있어서,

상기 보호막 형성제는 폴리아크릴산, 또는 폴리아크릴산암모늄염, 또는 폴리아크릴산아민염, 혹은 이들의 가교물인 것을 특징으로 하는 반도체 장치의 제조 방법.

#### 청구항 6.

반도체 기판 표면에 형성된 요철을 갖는 금속막 표면을 산화성 물질로 산화하고, 상기 산화된 금속막 표면의 금속 산화막을 인산으로 수용화시켜 금속 이온화함으로써, 볼록부를 연마하여 상기 요철을 평탄화하는 반도체 장치의 제조방법으로서, 벤조트리아졸 및 폴리머를 포함하는 보호막 형성제를 상기 요철을 갖는 금속막에 형성함으로써 볼록부를 선택적으로 연마하고, 오목부는 연마를 억제하면서 평탄화하는 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 7.

제6항에 있어서,

상기 산화성 물질은 과산화수소이고, 상기 인산은 오르토인산 또는 아인산이고, 상기 폴리머는 폴리아크릴산, 또는 폴리아크릴산암모늄염, 또는 폴리아크릴산아민염, 혹은 이들의 가교물인 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 8.

제6항 또는 제7항에 있어서,

상기 금속막은 배리어 금속으로 이루어지는 제1 금속막 및 그 위에 형성된 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 제2 금속막인 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 9.

반도체 기판 표면의 요철을 갖는 절연막 상에 형성된 배리어 금속으로 이루어지는 제1 금속막과, 상기 제1 금속막의 표면에 형성된 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 제2 금속막을 연마하여 볼록 부분의 상기 제1 금속막과 제2 금속막을 제거하여, 오목 부분에 상기 제1 금속막과 제2 금속막을 매립하는 반도체 장치의 제조 방법으로서,

상기 제2 금속막 표면을 산화하는 산화성 물질과, 상기 산화된 제2 금속막 표면의 제2 금속 산화막을 인산에 의해 수용화시켜 금속 이온화함으로써 상기 볼록부의 제2 금속막을 연마함과 함께, 보호막 형성제에 의해 보호막을 상기 요철을 갖는 상기 제2 금속 표면에 형성함으로써 볼록부를 선택적으로 연마하고, 오목부는 연마를 억제하면서 상기 제2 금속막 표면을 평탄화하는 지립 프리의 제1 연마액에 의한 제1 연마 공정과, 그 후, 상기 제1 연마액에 지립을 가하여 이루어지는 제2 연마액을 이용하여 상기 제1 금속막을 연마하는 제2 연마 공정으로 이루어지는 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 10.

제9항에 있어서,

상기 산화성 물질은 과산화수소이고, 상기 인산은 오르토인산 또는 아인산이며, 상기 보호막 형성제는 벤조트리아졸인 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 11.

제9항에 있어서,

상기 산화성 물질은 과산화수소이고, 상기 인산은 오르토인산 또는 아인산이고, 상기 보호막 형성제는 카르복실기를 갖는 폴리머인 것을 특징으로 하는 반도체 장치의 제조 방법.

## 청구항 12.

제9항에 있어서,

상기 산화성 물질은 과산화수소이고, 상기 인산은 오르토인산 또는 아인산이고, 상기 보호막 형성제는 폴리아크릴산, 또는 폴리아크릴산암모늄염, 또는 폴리아크릴산아민염, 혹은 이들의 가교물인 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 13.

반도체 영역의 상부에 개구부를 갖는 절연막을 형성하고, 상기 절연막 상 및 상기 개구부 내에 배리어 금속으로 이루어지는 제1 금속막과 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 제2 금속막을 피착시켜 상기 개구부 내를 상기 피착 금속막으로 충전하고,

상기 제2 금속막 표면을 산화하는 산화성 물질과, 상기 산화된 제2 금속막 표면의 제2 금속 산화막을 인산으로 수용화하여 금속 이온화함으로써 상기 절연막 상의 제2 금속막을 연마함과 함께, 보호막 형성제로 보호막을 상기 제2 금속 표면에 형성함으로써 상기 절연막 상의 제2 금속막을 선택적으로 연마하고, 상기 개구부 내는 연마를 억제하면서 상기 제2 금속막 표면을 연마하는 지립 프리의 제1 연마액을 이용한 제1 연마 공정에 의해, 상기 절연막 상의 상기 제2 금속막을 제거하여 상기 제1 금속막 표면 및 상기 개구부 내의 상기 제2 금속막 표면을 노출시키는 공정과, 그 후, 지립을 포함하는 제2 연마액을 이용하여 상기 절연막 상에 노출된 상기 제1 금속막을 제2 연마공정에 의해 제거하는 공정을 포함하는 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 14.

제13항에 있어서,

상기 제2 연마액의 상기 지립을 제외한 조성은 상기 제1 연마액과 동일한 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 15.

제13항에 있어서,

상기 제2 연마액은 상기 제1 연마액보다도 보호막 형성제의 함유량이 많게 되어 있는 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 16.

반도체 영역의 상부에 개구부를 갖는 절연막을 형성하고, 상기 절연막 상 및 상기 개구부 내에 배리어 금속으로 이루어지는 제1 금속막과 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 제2 금속막을 피착시켜 상기 개구부 내를 상기 피착 금속막으로 충전하고, 상기 제2 금속막 표면을 산화하는 과산화수소와, 인산에 의해 상기 제2 금속 산화막을 수용화시켜 금속 이온화함으로써 상기 절연막 상의 제2 금속막을 연마함과 함께, 벤조트리아졸, 폴리아크릴산 또는 그의 염 또는 그의 가교물을 포함하는 보호막 형성제에 의해 보호막을 상기 제2 금속 표면에 형성함으로써 상기 절연막 상의 제2 금속막을 선택적으로 연마하고, 상기 개구부 내는 연마를 억제하면서 상기 제2 금속막 표면을 연마하는 지립 프리의 제1 연마액을 이용한 화학 기계 연마에 의해서 상기 절연막 상의 상기 제2 금속막을 제거하여 상기 제1 금속막 표면 및 상기 개구부 내의 상기 제2 금속막 표면을 노출시키고, 그 후, 지립을 포함하는 제2 연마액을 이용하여 상기 절연막 상에 노출된 상기 제1 금속막을 화학 기계 연마에 의해서 제거하는 것을 특징으로 하는 반도체 장치의 제조 방법.

### 청구항 17.

제16항에 있어서,

상기 제2 연마액의 상기 지립을 제외한 조성은 상기 제1 연마액과 동일한 것을 특징으로 하는 반도체 장치의 제조 방법.

**청구항 18.**

제16항에 있어서,

상기 제2 연마액은 상기 제1 연마액보다도 벤조트리아졸, 혹은 폴리아크릴산 또는 그의 염 또는 그 가교물의 함유량이 많게 되어 있는 것을 특징으로 하는 반도체 장치의 제조 방법.

**청구항 19.**

반도체 기판 표면의 요철을 갖는 절연막 상에 형성된 배리어 금속으로 이루어지는 제1 금속막과, 상기 제1 금속막의 표면에 형성된 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 제2 금속막을 연마하여, 볼록 부분의 상기 제1 금속막과 제2 금속막을 제거하여 오목 부분에 상기 제1 금속막과 제2 금속막을 매립하는 반도체 장치의 제조 방법으로서,

상기 제2 금속막 표면을 산화시키는 산화성 물질과, 상기 산화된 제2 금속막 표면의 제2 금속 산화막을 인산으로 수용화시켜 금속 이온화함으로써 상기 볼록부의 제2 금속막을 연마함과 함께, 보호막 형성제에 의해 보호막을 상기 요철을 갖는 상기 제2 금속 표면에 형성함으로써 볼록부를 선택적으로 연마하고, 오목부는 연마를 억제하면서 상기 제2 금속막 표면을 평탄화하는 지립 프리의 제1 연마액에 의한 연마공정과, 그 후, 드라이 에칭법에 의해서 상기 제1 금속막을 제거하는 제2 공정을 갖는 것을 특징으로 하는 반도체 장치의 제조 방법.

**청구항 20.**

반도체 영역의 상부에 설치된 제1 배선층 상에 상기 제1 배선층에 도달하는 흄을 갖는 절연층을 형성하고, 상기 절연층의 상부 및 상기 흄 내에 배리어 금속으로 이루어지는 제1 금속막과 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 제2 금속막과의 적층막을 상기 흄 내를 충전하도록 피착시켜, 상기 제2 금속막 표면을 산화시키는 산화성 물질과, 상기 산화된 제2 금속막 표면의 제2 금속 산화막을 인산으로 수용화시켜 금속 이온화함으로써 상기 볼록부의 제2 금속막을 연마함과 함께, 보호막 형성제에 의해 보호막을 상기 요철을 갖는 상기 제2 금속 표면에 형성함으로써 볼록부를 선택적으로 연마하고, 오목부는 연마를 억제하면서 상기 제2 금속막 표면을 평탄화하는 지립 프리의 제1 연마액에 의한 연마 공정과, 그 후, 지립을 포함하는 제2 연마액을 이용하여 상기 절연막 상에 노출된 상기 제1 금속막을 화학 기계 연마하여 제거하는 공정에 의해 상기 절연층 상의 상기 제2 금속막 및 제1 금속막을 제거하여 상기 흄 내에 매립된 상기 제2 금속막을 노출시키고, 상기 노출된 제2 금속막의 표면을 환원성 분위기의 플라즈마로 처리하고, 이러한 후, 상기 제2 금속막의 상부에 제2 배선층을 피착시키는 것을 특징으로 하는 반도체 장치의 제조 방법.

**청구항 21.**

제19항 또는 제20항에 있어서,

상기 산화성 물질은 과산화수소이며, 상기 인산은 오르토인산 또는 아인산이고, 상기 보호막 형성제는 벤조트리아졸 및 또는 카르복실기를 갖는 폴리머인 것을 특징으로 하는 반도체 장치의 제조 방법.

**청구항 22.**

삭제

**청구항 23.**

삭제

명세서

## 발명의 상세한 설명

### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 금속막의 연마 기술에 관한 것으로, 특히 반도체 장치 등의 전자 회로 장치의 다층 배선 형성에 사용되는 연마 방법에 관한 것이다.

최근, 반도체 집적 회로 장치 (이하 LSI라고 적는다)의 고집적화, 고성능화에 따라 새로운 미세 가공 기술이 개발되어 있다. 화학 기계 연마법 [이하 CMP(Chemical Mechanical Polishing)라고 적는다]도 그 하나이며, LSI 제조 공정, 특히 다층 배선 형성 공정에서의 충간 절연막의 평탄화, 금속 플러그 형성, 매립 배선 형성에 있어서 빈번히 이용되는 기술이다. 이 기술은, 예를 들면 미국 특허 No.4944836에 개시되어 있다.

또한, 최근은 LSI의 고속 성능화를 달성하기 위해, 배선 재료를 종래의 알루미늄(a1) 합금으로부터 저저항의 구리(Cu) 합금을 이용하려고 하는 것이 시도되고 있다. 그러나, Cu 합금은 Al 합금 배선의 형성에서 빈번히 이용된 드라이 에칭법에 의한 미세 가공이 곤란하다.

그래서, 홈 가공이 실시된 절연막 상에 Cu 합금 박막을 피착하고, 홈 내에 매립된 부분 이외의 Cu 합금 박막을 CMP에 의해 제거하여 매립 배선을 형성하는, 소위 다마신(damascene)법이 주로 채용되어 있다.

이 기술은 예를 들면 특개평2-278822호 공보에 개시되어 있고, Cu 합금막과 절연막 사이에는 접착성 향상과 Cu 확산 배리어의 목적으로부터, 수 10nm 정도 두께의 질화 티탄(TiN)막이나 탄탈(Ta)막 혹은 질화 탄탈(TaN)막 등의 배리어 금속막을 삽입하는 것이 일반적으로 되어 있다.

종래, 배선에 이용되는 Cu 합금 등의 금속막의 CMP에 이용되는 연마액은, 연마 지립과 산화성 물질 (산화제라고 부르는 경우도 있다)을 주성분으로 하는 것이 일반적이다.

산화성 물질의 산화 작용으로 금속막 표면을 산화하면서, 연마 지립에 의해 그 산화물을 기계적으로 제거하는 것이 기본적인 CMP의 메카니즘이다. 이것에 대해서는, 일본 주식회사 사이언스 포럼 발행, 柚木正弘 편집 「CMP의 사이언스」 1997년 8월 20일 발행의 제299페이지에 개시되어 있다.

연마 지립으로서는, 수 10 내지 수 100nm의 입자 직경을 갖는 알루미나 지립(砥粒)이나 실리카 지립이 알려져 있지만, 일반적으로 시판되어 있는 메탈 CMP용의 지립의 대부분은 전자이다.

산화성 물질로서는, 과산화수소( $H_2O_2$ ), 질산제2철( $Fe(NO_3)_3$ ), 과요오드산칼륨( $KIO_3$ )이 일반적으로 이용되고 있고, 이들은 예를 들면, 상기한 「CMP의 사이언스」의 제299페이지로부터 제300페이지에 개시되어 있다. 이들 중에서도 과산화수소가 금속 이온을 포함하지 않기 때문에, 최근에는 빈번히 이용되도록 되어 왔다.

그러나, 종래의 메탈 CMP용의 연마 지립을 주성분으로서 포함하는 연마액을 이용하여 매립 배선이나 플러그를 형성하는 경우, 이하의 (1) 내지 (7)에 예를 드는 문제가 있었다.

즉, (1) 디싱(dishing, 배선 부재의 오목부)이나 침식(erosion, 절연막부의 절삭)의 발생, (2) 스크래치 (연마 상처)의 발생, (3) 박리의 발생, (4) CMP 후 세정에 의한 지립 제거의 필요성, (5) 높은 연마제 비용, (6) 연마제 공급 장치, 폐액 처리 설비에 따른 높은 비용, (7) CMP 장치로부터의 크린룸 내에서의 먼지 발생이다.

상기한 문제점은 연마 지립을 포함하는 연마제에 의해 CMP를 행하는 것이 원인으로 되어 있다. 그러나, 종래의 CMP의 방법에서는, 연마 지립은 산화제에 의해서 형성된 산화층을 빠르게 제거하기 위해 기계적 제거 효과를 생기게 하기 위해 필요하고, 연마 지립을 가하지 않으면 실용적인 연마 속도에 도달하지 않았다.

이것에 대하여, 본원 출원인은 지립을 포함하지 않은 연마액에 의해 금속막을 연마하여 매립 배선 구조를 형성하는 방법을 연구하고, 그 기술을 특개평11-135466호 공보에 개시하였다. 그것에 의하면, 산화성 물질과, 산화물을 수용성화하는 물

질로 물과, 필요하면 방식성 물질을 포함하는 연마액을 이용하여, 금속막 표면에 기계적인 마찰을 거는 것에 의해 매립 금속 배선을 형성할 수가 있다. 예를 들면, 과산화수소수와 시트르산과 벤조트리아졸 (이하, BTA라 한다)을 포함하는 지립프리(free) 연마액으로 Cu 배선을 형성하는 방법이 그 일례이다.

상기한 지립 프리연마액을 이용하면 상술한 (1) 내지 (7)의 문제는 해결되지만, 통상의 연마 조건에 있어서의 Cu 등의 금속의 연마 속도가 80~150nm/분이었다. 300g/cm<sup>2</sup> 이상의 높은 연마 하중을 걸더라도 연마 속도가 포화하여 200nm/분을 넘지 않고, 처리량을 이 이상 향상시킬 수 없다고 하는 문제가 있었다. 시판의 알루미나 연마액의 경우에는 높은 연마 하중을 거는 것에 의해 200~400nm/분의 연마 속도까지 도달하지만, 이 경우에는 스크래치나 박리 등의 문제점이 보다 심각하게 되었다.

한편, 지금까지 본 발명에 관계되는 공보가 몇개인가 공개되어 있다. 그 하나로서 특개평7-94455호 공보에 Cu용의 지립 함유 연마액의 하나로서 인산 수용액이 개시되어 있다 (상기 공보의 실시예 4). 농도 3%의 인산을 포함하는 지립 함유 연마액을 이용함으로써 절연막에 대한 Cu의 연마 속도비를 14.5까지 증가할 수 있다고 기재되어 있다 (상기 공보의 도 5; Cu 가 100%의 경우).

그러나, 우리들 실험에서는, 지립과 인산 수용액의 조합 만으로는 실용적인 연마 조건 (연마 하중 500g/cm<sup>2</sup> 이하, 정반 회전 수 90rpm 이하)에 있어서, 50nm/분 이상의 연마 속도는 얻어지지 않고, 지립을 제거하면 20nm/분 이하의 연마 속도였다. 따라서, 이 지립 함유 연마액은 연마 속도비는 높지만, 충분히 많은 처리량으로 정밀도가 높은 (예를 들면, 침식의 발생이 없다) 연마를 행하는 것은 불가능하였다.

이것에 대하여, 본 발명에서 개시하는 연마액의 연마 속도는 500nm/분 이상의 높은 것으로, 상기 공보의 연마액과 비교하면 1자릿수 이상 우수한 것이다.

또한, 특개평10-265766호 공보에 개시되어 있는 텅스텐 CMP용의 지립 함유 연마액에 있어서도, 인산 혹은 유기산을 안정제로서 이용하고 있지만, 이 경우의 안정제는 연마액 중에 첨가하는 촉매 (질산 제2철)와 산화제 (과산화수소)의 반응을 억제하는 약제이다.

우리들의 실험에 의하면, 이 연마액의 Cu의 에칭 속도는 100nm/분 이상이고, Cu막을 연마하는 것은 가능하지만, Cu 배선은 에칭에 의해 소멸되었다. 즉, 이 연마액은 Cu의 CMP에는 적용할 수 없는 것이었다. 이 공보로부터, 지립을 포함하지 않은 연마액에 인산을 첨가하여 Cu의 연마 속도를 증가시킨다고 하는 본 발명의 사고 방식은 예측할 수 없는 것이다.

특개평11-21546호 공보에는 Cu의 CMP용 연마액이 개시되어 있다. 연마액은 연마 지립과 산화제 (예를 들면, 요소-과산화수소수)와 착생성제 (예를 들면 옥살산암모늄)와 막 생성제(BTA)와 계면 활성제로 구성되는 것이다.

상기 공보의 [0025]란 및 [0034]란에, 티탄이나 탄탈과 같은 배리어층의 연마 속도를 촉진하기 위해서 혹은 이 연마액의 pH를 조정하기 위해서, 황산, 인산, 질산 등의 무기산을 가하는 것이 기재되어 있다. 여기서 기재되어 있는 계면 활성제는 연마 지립의 침강, 응집, 분해를 억제하기 위한 것으로, 우리들의 실험에서는, 이 공보에 기재된 연마액으로부터 연마 지립을 제거한 연마액에서는 Cu막을 연마하는 것은 실질적으로 곤란하였다. 즉, 이 연마액은 지립에 의한 Cu 산화물의 기계적 제거 작용을 필수 작용으로 한 연마액이다. 이 공보로부터, 지립을 포함하지 않은 연마액에 계면 활성제나 증점제를 첨가한다고 하는 발명은 예측할 수 없는 것이다.

유리 지립을 이용하지 않은 연마액은, 특개소52-21222호 공보에 카메라 부품 등의 구리 장식품의 화학 연마액으로서 개시되어 있다. 연마액은 계면 활성제와 과산화수소와 황산과 인산으로 구성된 것으로, 지립이 부착된 금강사(金剛砂, emery) 연마지로 구리 표면을 연마하여 광택을 내는 것을 목적으로 하고 있다. 이 계면 활성제는 연마면의 습윤성을 향상시킴으로써 광택을 내는 효과가 있지만, 우리들의 실험에 따르면 이 연마액의 에칭 속도는 1000nm/분 이상이며, 본 발명의 수 100nm 레벨의 매립 Cu 배선을 형성하기 위한 연마액으로서는 이용할 수 없는 것이다.

본 발명의 연마액의 Cu의 에칭 속도는 10nm/분 이하인 것이 필요하다. 그 이유를 이하에 설명한다. 본 발명의 연마액을 적용하는 반도체 장치의 배선층의 두께는 통상 300nm~1000nm이다. 연마 시간이 수분인 것을 고려하면, 예를 들면 100nm 정도의 에칭 속도를 갖는 연마액을 적용한 경우, 배선 부분의 Cu가 수 100nm의 깊이까지 에칭될 가능성이 있다. 즉, 디싱이 수 100nm에 달하는 가능성이 있다. 디싱량을 수 10nm 이하로 억제하기 위해서는, 연마액의 에칭 속도를 10nm 이하로 하지 않으면 안된다. 또한, 오버 연마 시간을 고려하면 1nm/분 이하인 것이 바람직하다.

특개소55-47382호 공보, 및 특개평6-57455호 공보에는 지립을 포함하지 않은 연마액이 개시되어 있다. 전자는 AI제 기계 가공품의 버어 제거 등에 이용하는 화학 연마액으로, 산(인산을 포함한다)과 방향족 AI킬레이트제로 구성되며, 필요에 따라서 계면 활성제와 과산화수소를 첨가한 것이다. 후자는 황동의 도금전 처리용의 화학 연마액으로, 과산화수소와 옥시퀴놀린과 착화제와 계면 활성제로 구성되고, 필요에 따라서 인산이나 황산을 첨가하여 광택이나 체크 무늬의 조절을 행하는 연마액이다. 계면 활성제는 습윤성을 향상하기 위함과, 기포 발생에 의한 미스트를 방지하기 위해 첨가하고 있다. 어느 쪽의 화학 연마액의 에칭 속도도 100nm/분 이상이고, 이들은 에칭 작용에 의해 연마하는(마찰을 걸지 않는다) 연마액이다. 따라서, 본 발명의 매립 Cu 배선을 형성하기 위한 연마액으로서는 이용할 수 없는 것이다. 또한, 본 발명이 대상으로 하고 있는 LSI의 매립 배선용의 연마액은 nm 레벨로 평탄성을 낼 필요가 있어, 이를 공보에 기재된 연마액의 광택 레벨 이상으로 요구되는 평탄성(광택)의 레벨이 높은 것이다.

### 발명이 이루고자 하는 기술적 과제

본 발명은 이러한 점을 감안하여 이루어진 것으로, 매립 금속 배선이나 비어 등의 플러그를 형성하는 연마 공정에 있어서, 상기 (1) 내지 (7)의 문제점을 개선하는 새로운 연마 방법을 제공하는 것이다.

더욱 구체적으로는, Cu, Cu를 주성분으로 하는 합금, Cu 화합물 등의 금속에 대한 에칭 속도가 10nm/분 이하이고, 연마 속도의 고속화(500nm/분 이상)를 실현하는 것이 가능한 개량된 연마 방법이나 반도체 장치의 제조 방법을 제공하는 것을 목적으로 한다.

본원에 있어서 개시되는 발명 중, 대표적이지만 개요를 간단히 설명하면 이하와 같다.

즉, 본 발명의 하나는 Cu 또는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물로 이루어지는 금속막을, 산화성 물질과, 인산과, 보호막 형성제를 포함하는 연마액을 이용한 화학 기계 연마에 의해 제거하는 것이다.

인산(phosphoric acid)은 산화성 물질에 의해서 산화된 금속막 표면의 산화물을 효율적으로 수용성화하는 기능이 있다. 인산으로서는 오르토인산(orthophosphoric acid,  $H_3PO_4$ )이 대표적인 것으로, 본 발명에서는 특별히 언급하지 않는 한 오르토인산을 인산이라 칭한다.

오르토인산 이외에도, 아인산(포스폰산, phosphorous acid,  $H_2PHO_3$ ), 차아인산(포스핀산, hypophosphorous acid,  $HPH_2O_2$ ), 메터인산(metaphosphoric acid,  $HPO_3$ )이나, 폴리인산(polyphosphoric acid, 예를 들면 이인산(피롤린산, pyrophosphoric acid) ), 혹은 인산기를 포함하는 물질을 예로 들 수 있다.

이들 중에서, 오르토인산과 아인산이 가장 연마 속도를 높이는 효과가 있다. 또한, 오르토인산은 화학적 안정성에 뛰어나며, 가격이 가장 싸다고 하는 이점이 있다.

아인산이나 차아인산은 오르토인산과 비교하여, 연마액의 유해성이 낮다고 하는 이점이 있다. 오르토인산과 아인산은 차아인산이나 메터인산과 비교하여 자극성이 낮다고 하는 이점이 있다. 아인산은 오르토인산과 비교하여 연마면의 거칠음이 발생하기 어렵게 된다고 이점이 있다.

금속막의 지나친 산화나 에칭을 억제하는 물질로서는 보호막 형성제가 유효하다. 이를 위한 보호막 형성제로서는, 연마액에 첨가함으로써 연마하는 금속의 에칭 속도를 저감하는 효과가 있는 것이면 좋고, 배선 가공 후에 생기는 디싱(dishing)을 억제할 수가 있다.

본 발명의 연마액에 보호막 형성제를 첨가하기 전의 금속막에 대한 에칭 속도는 50nm/분을 넘는 것이다. 즉, 본질적으로 부식성이 높은 연마액이다. 이 연마액에 보호막 형성제를 첨가함으로써 방식 효과가 얻어져, 본 발명의 CMP용의 연마액으로서 이용할 수 있게 된다. 구체적으로는 10nm/분 이하의 에칭 속도가 되도록 첨가하는 것이 바람직하다.

보호막 형성제로서는 Cu나 Cu 합금에 대한 BTA(benzotriazole)가 대표적인 것이다. 그 외에 실용상 사용할 수 있는 것으로서는, 톨릴트리아졸(tolyltriazole, 이하 TTA라고 적는다), BTA 카르본산(BTA carboxylic acid, 이하 BTA-COOH라고 적는다) 등의 BTA의 유도체나 키날진산(quinaldinic acid)도 있다. 그 중에서도, BTA가 가장 염가이며, 물로의 용해도가 높다(실온에 있어서 순수로의 용해도가 2중량%)고 하는 이점이 있다.

보호막 형성제의 연마액 중에 있어서의 용해도를 높이기 위해서 알콜을 첨가하는 것은 매우 유효하다. 연마액의 온도가 0°C 근처까지 저하한 경우나 첨가물을 가한 경우에는, 보호막 형성제의 연마액으로의 용해도는 순수로의 용해도보다도 밑돌고, 결정화하여 연마액 중에서 석출하는 것이 있기 때문에, 실온에 있어서의 순수에의 용해도의 2배 이상으로 해 놓는 것이 필요하다. 예를 들면, BTA를 보호막 형성제로서 사용하는 경우, 메탄올(methanol)을 1% 정도 연마액에 첨가함으로써 BTA의 용해도는 2배 이상으로 올라간다. 에탄올(ethanol)이나 이소프로필 알콜(isopropyl alcohol)에서도 마찬가지의 효과가 있다.

이 이외의 보호막 형성제로서는, 계면 활성제나 증점제를 들 수 있고, 이들 폴리머가 CMP 중에 연마액과 금속의 계면에 흡착하여, 폴리머의 보호막을 형성함으로써 에칭을 억제하는 효과가 있다. 상기한 BTA와 같이 Cu에 선택적으로 흡착하지 않기 때문에, 범용성이 있다.

이들 폴리머 중에서는 카르복실기를 포함하는 것이 금속의 연마 속도를 향상하는 목적으로부터 바람직하다. 예를 들면, 폴리아크릴산(polyacrylic acid), 폴리메타크릴산(polymethacrylic acid), 및 이들 암모늄염(ammonium salt), 트리에탄올아민염(triethanolamine salt), 모노에탄올아민염, 트리에틸아민염(triethylamine salt), 디이소프로판올아민염(diisopropanolamine salt) 등을 들 수 있다.

또한, 분자량이 높은 폴리머의 보호막 형성 효과는 더욱 높고, 특히 증점 작용이 높은 가교형 폴리머(bridged bond type polymer)는 연마 속도를 더욱 증가시키는 효과가 있다. 예를 들면, 가교형 폴리아크릴산 및 그 염이다.

계면 활성제 중에는 살균, 곰팡이 방지 작용이 있는 폴리머도 있지만, 이것도 연마 특성을 높이는 효과와 함께, 연마액 사용 전의 보관액 중이나 폐액 중에서 곰팡이나 박테리아가 발생하는 문제를 방지할 수 있다. 예를 들면 염화세틸피리디늄(세틸 피리디늄 클로라이드, cetyl pyridinium chloride)이 이 예이다.

보호막 형성제는, 2종류의 물질을 혼합하여 이용함으로써 연마 속도를 개개에 이용한 경우보다도 증가시키는 것이 가능하다. 예를 들면, 방식제와 계면 활성제, 방식제와 증점제가 그 예이며, BTA와 폴리아크릴산암모늄염, BTA와 가교형 폴리아크릴산암모늄염, BTA와 염화세틸 피리디늄의 조합이 그 구체예이다.

또, 계면 활성제를 첨가한 경우의 기포 발생을 방지하기 위해서, 소포제를 더욱 첨가할 수가 있다.

필요에 따라서, 상기한 연마액에 유기산(organic acid) 혹은 그 염을 첨가하는 것도 가능하다. 유기산은 인산과 마찬가지로, 연마하는 금속을 이온(예를 들면 Cu<sup>2+</sup> 이온)화할 때에, 효율적으로 수용성화하는 작용이 있고, 인산계의 산만의 경우 보다도 연마의 웨이퍼 내 균일성을 향상하는 효과와, 연마면의 표면 거칠기를 방지하는 효과가 있다.

유기산 중에서도 수산기나 카르복실기를 포함하는 히드록시산(hydroxy acid), 카르본산(carboxylic acid), 히드록시카르본산은 연마 속도를 높이는 효과가 높다.

예를 들면, 시트르산(citric acid), 말산(malic acid), 말론산(malonic acid), 숙신산(succinic acid), 타르타르산(tartaric acid), 프탈산(phthalic acid), 말레산(maleic acid), 푸마르산(funlaric acid), 젖산(lactic acid), 피메린산(phelic acid), 아디핀산(adipic acid), 글루타르산(glutaric acid), 옥살산(oxalic acid), 살리실산(salicylic acid), 글리콜산(glycollic acid), 트리카르발산(tricarbal1ylic acid), 벤조산(benzoic acid), 포름산(formic acid), 아세트산(acetic acid), 프로피온산(propionic acid), 부티르산(butyric acid), 발레르산(valeric acid) 등의 유기산 및 이들 염을 예로 들 수 있다. 그 밖에 EDTA(etylenediaminetetraacetic acid) 등의 칼레이트제(chelating agent)도 이용할 수 있다.

염은 용해도를 높이는 효과가 있고, 금속 성분을 포함하지 않은 것, 예를 들면 암모늄염, 혹은 반도체 소자에 악영향을 미치지 않는 원소(예를 들면 알루미늄 등)를 포함하는 것이 바람직하다. 또한, 이들 약제는 복수를 조합시켜 이용하여도 좋다.

상기한 산 중, 말론산, 타르타르산, 말산, 시트르산, 숙신산, 말레산, 푸마르산, 글리콜산, 트리카르발산, 젖산이 고연마 속도, 저에칭 속도의 관점으로부터, 본 발명의 연마액에 첨가하는 유기산으로서 바람직하다.

상기한 산 중, 시트르산, 말산, 말론산, 타르타르산은 식품 첨가물로서도 일반적으로 사용되고 있고, 독성이 낮고, 폐액으로서의 해도 적어, 냄새도 없고, 물에의 용해도도 높기 때문에 본 발명의 연마액에 사용하는 유기산으로서 특히 바람직하다.

산화성 물질은 연마하는 금속막의 표면을 산화시키는 작용이 있는 물질이다. 과산화수소가 금속 성분을 포함하지 않기 때문에 가장 적합하다. 또, 질산, 질산제2철, 과요오드산칼륨도 충분한 산화력이 있고, 금속 성분이 장해가 되지 않는 경우에는 이용할 수 있다. 이들 산화성 물질은 복수를 조합시켜 이용하여도 좋다.

연마 지립에 대해서는, 알루미나 지립이나 실리카 지립이 본 발명의 연마액에 포함되어 있으면 연마 속도를 더욱 증가하는 효과를 기대할 수 있다. 단, 상기에 기재한 문제점 (1) 내지 (7)이 발생하기 때문에, 이러한 문제점이 장해가 되지 않는 경우에는 적용할 수 있다. 지립 함유량의 목표로서는, 다음과 같이, 각종 목적에 따라서 다르다. 디싱과 침식을 억제하는 목적이, 상기한 연마 지립의 농도를 0.05 중량% 이하로 함으로써 달성된다.

$\text{SiO}_2$  등의 절연막 표면에 발생하는 스크래치를 저감시키는 목적은, 상기한 연마 지립의 농도를 0.5 중량% 미만으로 함으로써 달성된다.

금속막 표면에 발생하는 스크래치를 저감하는 목적은, 상기한 연마 지립의 농도를 0.1 중량% 이하로 함으로써 달성된다.

박리를 저감시키는 목적은, 상기한 연마 지립의 농도를 0.3 중량% 이하로 함으로써 달성된다.

세정성을 향상시키는 목적은, 상기한 연마 지립의 농도를 0.01 중량% 이하로 함으로써 달성된다.

연마액의 비용을 저감시키는 목적은, 상기한 연마 지립의 농도를 0.001 중량% 이하로 함으로써 달성된다.

연마제 공급 장치, 폐액 처리 설비의 비용 문제를 해결하는 목적은, 상기한 연마 지립의 농도를 0.0001 중량% 이하로 함으로써 달성된다.

크린룸 내의 먼지 발생을 억제하는 목적은, 상기한 연마 지립을 첨가하지 않음으로써 달성된다.

상기한 여러가지 목적에 따른 미량의 지립 함유량 이하의 연마액으로써 「지립 프리 연마액」을 정의하여야 하지만, 본원 발명에서는 디싱, 침식 및 스크래치의 억제가 주 목적이기 때문에, 이 목적을 고려하여 특단의 것이 없는 한 실리카지립 혹은 알루미나 등의 지립이 전혀 포함되고 있지 않은 연마액 또는 0.05 중량% 이하밖에 포함되어 있지 않은 연마액을 「실질적으로 지립을 함유하지 않은 연마액」 혹은 「지립 프리의 연마액」으로 한다.

매립 Cu 배선 또는 비어 등의 플러그를 형성하는 경우, Cu의 연마 (제1스텝)에서는 지립을 실질적으로 포함하지 않은 지립 프리의 연마액을 이용하고, 그 후 배리어 금속의 연마 (제2스텝)에서는 지립을 포함하는 연마액으로 전환하는 2개의 스텝 연마를 행함으로써, 상기한 문제점의 특히 (1), (2), (5), (6)을 크게 개선할 수가 있다.

이 경우, 배리어 금속막을 고속으로 연마할 수 있고, 또한 기초의 오목부에의한 Cu막이나 배리어 금속막의 잔여물 등의 트러블을 회피할 수 있는 이점이 있다.

연마액의 공급 방법으로서는, Cu용 연마 정반과 배리어 금속용 연마 정반의 각각에 개별로 공급하는 방법도 있지만, 하나의 동일한 조성의 지립 프리 연마액을 Cu용 연마 정반과 배리어 금속용 연마 정반의 양쪽에 공급하고, 또한 지립 분산액을 배리어 금속용 연마 정반에 추가하여 공급하는 방법이 편리하다. 이와 같이 지립의 유무 이외에는 동일 조성의 연마액을 사용하는 경우에는, 연마액을 보관하기용이 할뿐만 아니라 액의 성질이나 성능의 관리가 간단하게 된다.

또한, 연마 지립이 매립된 연마 패드를 이용하거나, 지석을 이용하는 것도 가능하다. 이것에 의해 연마 폐액 내의 지립 성분을 저감할 수가 있어, (6)의 폐액 처리의 문제 해결이 용이하게 된다. 지석을 이용하는 경우에는 Cu의 연마로부터 행하여도 평탄성이 향상하는 이점이 있고, 상기한 (1)의 문제를 해결한다.

상기한 2스텝에서 연마하는 경우, 제1 스텝과 제2 스텝에서 연마액의 조성을 바꿀 수 있다. 가장 효과가 있는 것은, 제2 스텝에서 Cu의 연마 속도를 내립으로써, 침식이나 디싱을 적극적으로 억제하는 것이다. 이것을 위해서는 연마액 중의 보호

막 형성제의 농도를 제2스텝으로 증가하여, 배리어 금속막의 연마 속도를 Cu의 연마 속도에 대해 상대적으로 증가시키는 것이다. 예를 들면, BTA 및 또는 폴리머의 첨가 농도를 높게 함으로써, 배리어 금속/Cu 선택비를 2배 이상으로 높일 수 있다. 연마액 중에 첨가하지 않더라도, 연마액과 동시에, 예를 들면 고농도 (1% 정도)의 BTA수를 동시에 연마 정반 상에 흘림으로써 마찬가지의 효과가 얻어진다.

상기한 2스텝 연마를 행하는 대신에, 드라이 에칭법을 조합시킨 배선 형성 방법도 있다. 즉, 제1 스텝을 Cu의 지립 프리 CMP, 제2 스텝을 연마액을 이용하지 않은 드라이 에칭법에 의한 배리어 금속막의 제거로 함으로써, 완전 지립 프리 프로세스로 하는 것이 가능해진다. 이것에 의해, 상기한 (1) 내지 (7)의 문제를 해결한다.

배리어 금속의 드라이 에칭법에 이용하는 가스로서는 6불화유황( $SF_6$ )이 가장 적합하다.  $SF_6$ 은 플라즈마 해리에 의해 많은 F 래디컬을 생성하기 때문에, TiN이나 TaN을 선택적으로 제거하기 위해 유리하고, 또한 Cu와의 반응성이 낮기 때문이다. Cu와 배리어 금속의 에칭 선택비는 3 이상인 것이 바람직하다. 또한 이 드라이 에칭 프로세스의 마진을 넓히기 위해서는 이 선택비가 5 이상인 것이 더 바람직하다.

또, 연마하는 금속막으로서는, Cu, Ti, TiN, Ta, TaN 등에 적용할 수 있다. 특히, Cu는 Cu를 주성분으로 하는 합금 혹은 Cu 화합물의 경우도 포함시켜 지립을 실질적으로 포함하지 않은 지립 프리 연마액을 이용한 경우의 연마 속도가 높고, 본 발명의 대상 금속으로서 가장 적합하다. Ti 및 TiN, Ta 및 TaN에 대해서는 지립을 포함하지 않은 연마액을 이용한 경우의 연마 속도는 Cu만큼 높지 않지만, 지립을 포함하는 연마제를 이용함으로써 적용 가능하다.

산화성 물질과 인산과 보호막 형성제로 구성된 연마액을 이용하여, 예를 들면 Cu의 CMP를 행하면, 우선 Cu막 표면이 보호막 형성제에 의해 회복 보호된다. Cu막 표면의 볼록부는 항상 연마포의 기계적 마찰을 받기 때문에, 보호막 형성제에 의해서 형성된 보호막은 용이하게 제거된다.

연마액에 노출되어진 Cu막 표면은 산화성 물질에 의해서 산화되고, 표면에 얇은 산화층이 형성된다.

다음에 인산이 공급되면 상기 산화층이 수용액으로 되어 용출하여 상기 산화층의 두께가 감소한다. 산화층이 얇아진 부분은 재차 산화성 물질에 노출되어 산화층의 두께가 증가하고, 이 반응을 반복하여 CMP가 진행한다.

따라서, Cu막 표면의 볼록부는 표면의 반응 생성물이 제거되기 쉽고, 또한 국소적으로 가열되기 때문에 반응이 촉진되어, 상기한 산화/수용성화의 반복 반응은 방식성 보호막이 형성된 오목부보다도 빠르게 진행한다. 즉, 볼록부의 연마 속도는 빠르게 되어 평탄화된다.

상기 보호막 형성제는 금속막 표면에 부착하여 오목부의 반응을 억제하고, 최종적으로 디싱의 발생을 저지하는 효과가 있다. BTA 유도체와 같이 일반적으로 방식제로서 이용되고 있는 보호막 형성제는 매우 강고한 보호막을 Cu막 표면에 형성한다. 또한, 폴리아크릴산과 같은 계면 활성 효과를 갖는 폴리머도 연마액과 Cu 표면과의 계면에 폴리머의 막을 형성함으로써 방식제로서의 효과를 발휘한다.

보호막 형성제의 연마액 중으로의 첨가 농도의 목표로서는, 연마 속도를 500 nm/분 이상으로 유지하고, 또한 에칭 속도가 10nm/분 이하이도록 하는 것이 바람직하다 (속도비가 50 이상). 또한, 에칭 속도는 1nm/분 이하 (속도비가 500 이상)이면 더욱 바람직하다. 그 이상의 농도로 첨가하면 CMP 속도가 저하하는 경우가 있다. 그 이하의 농도로 첨가하면 에칭 속도가 높아져서, CMP를 행할 수는 있지만 디싱이 발생하기 용이해진다.

본 발명에 따르면 이러한 연마 특성의 조정을 간단하게 할수 있게 되어, 특히 전극 배선 밀도가 현저하게 다른 미세한 다층 배선을 갖는 LSI나 전자 회로 장치의 실현에 크게 공헌하는 것이다.

### 발명의 구성

이하, 본 발명을 도면을 이용하여 구체적으로 상세히 설명한다.

(실시예 1)

본 실시예에서는 Cu의 CMP를 행함으로써 Cu 배선을 형성하는 방법에 대해 설명한다.

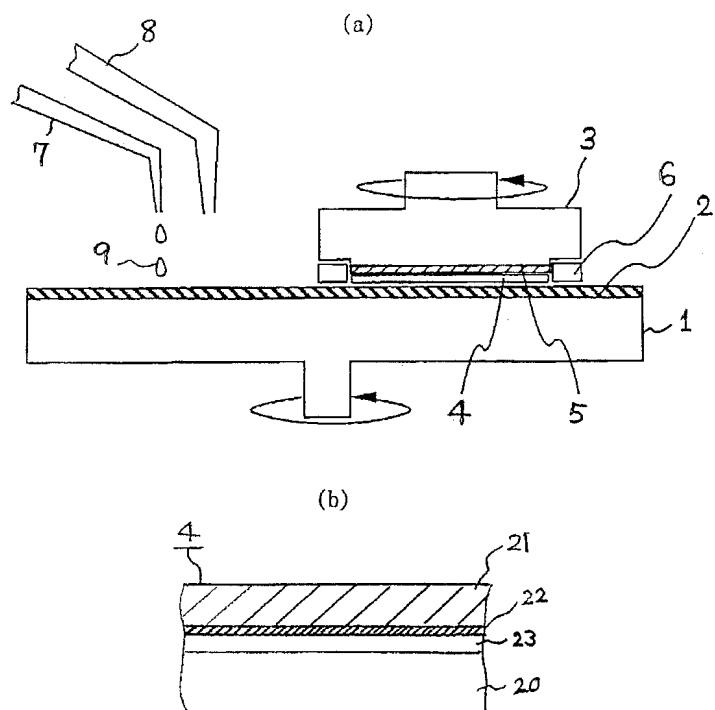

도 1의 (a)는 본 발명의 실시예에 있어서 사용하는 CMP 장치의 주요부를 나타내는 개략 단면도이다. 연마포(2)가 접착된 정반(1)의 상부에 배킹 패드(5)에 의해서 반도체 웨이퍼(4)를 뒤집은 상태에서 지지한 홀더(3)를 배치하고, 정반(1) 및 홀더(3)를 회전시켜 CMP를 행하는 구조로 되어 있다.

CMP 중에 반도체 웨이퍼(4)가 빠지지 않도록 홀더(3)에는 리테이너링(6)이 설치된다. CMP 중에 있어서의 연마 하중은 홀더(3)의 상부에 가하는 하중으로 조절하였다. 표준 연마 하중은 220g/cm<sup>2</sup>, 정반의 회전수는 60rpm, 홀더의 회전수는 20 rpm으로 하였다. 또, 연마 하중이나 회전수는 이것에 한정되는 것은 아니다. 연마포(2)는 로델사 제조의 경질포 IC1000을 이용하였다. 필요에 따라서 연마포(2)에는 홈 가공이 실시된 것을 이용하여도 좋다.

도 2는 이 CMP 장치의 주요부를 위에서부터 본 평면도이다. 연마 정반은 동일 구조의 것이 2개 있고, 제1 정반(1)은 Cu의 연마용, 제2 정반(11)은 배리어 금속의 연마용으로서 이용하였다. 어느 한쪽의 정반에도 도 1과 같이 연마포(2)가 접착되어 있다. 양 정반(1, 11) 사이를 반송 기구(12)가 웨이퍼(4)를 반송함으로써 연속하여 (2스텝으로) 연마하는 것이 가능하다. 또, 간략화를 위해 홀더(3)는 도시되어 있지 않다. 참조 번호(13)는 웨이퍼 로더, 참조 번호(14)는 웨이퍼 언로더이다. 또한, 베프 연마를 행하기 위해서 3개의 정반(도시 생략)을 갖는 것이어도 좋다.

본 발명의 연마액(9)은 도 1의 정반(1) 상부에 설치된 제1 액체 공급구(7)로부터 연마포(2) 상에 약 200cc/분의 속도로 적하하여 CMP를 행한다. CMP가 종료한 단계에서 제1 공급구(7)를 폐쇄하여 연마액(9)의 공급을 정지하고, 제2 액체 공급구(8)로부터 순수를 약 3000cc/분의 속도로 공급하여 린스를 30~60초 동안 행한다. CMP는 실온에서 행한다.

그 후, 웨이퍼(4)를 건조하지 않은 상태에서 유지하고, 브러시 스크립 세정에 의해 연마액을 제거한 후, 웨이퍼를 린서 드라이어 혹은 스피너 등으로 건조시킨다.

우선, 배선 패턴이 형성되어 있지 않은 평탄한 반도체 웨이퍼를 이용하여 본 발명의 연마액의 기초적인 연마 특성을 조사하였다. 시료는 도 1의 (b)에 그 단면도를 도시한 바와 같이, 평탄한 실리콘의 반도체 기판(20) 상에 두께 200nm의 실리콘 산화막(23)을 형성한 후, 접착층으로서 두께 50nm의 TiN막 (배리어 금속막: 22)과 두께 2000nm의 Cu막(21)을 스퍼터링 법에 의해서 진공 중에서 연속 성막한 것이다. 웨이퍼(4)의 직경은 5인치이다.

본 실시예에서 이용한 연마액은 과산화수소수 (시판의 30 중량% H<sub>2</sub>O<sub>2</sub> 수용액)와 오르토인산 (이하, 인산이라 한다)과 BTA와 메탄올로 구성된 수용액이고, 알루미나나 실리카 등의 연마 지립을 실질적으로 포함하지 않은 소위 지립 프리의 연마액이다. 조성은 과산화수소수는 30중량%, 인산은 0.2 중량%, BTA는 0.2 중량%, 메탄올은 1중량%이다. 이 인산계 지립 프리 연마액을 이용하여, Cu막(21)의 연마 속도와 에칭 속도를 측정하였다. 연마 속도 및 에칭 속도는 Cu막(21)의 전기 저항치 변화로부터 환산하여 구하였다. 연마 시간은 2분으로 하였다.

그 결과, Cu막(21)의 연마 속도는 550nm/분이었다. 에칭 속도는 1.0nm/분 이하로 억제되어 있고, 디싱 발생의 문제는 없는 것을 알았다. 또, SiO<sub>2</sub>막(23)의 연마 속도는 0.1nm/분 이하이고, 침식 발생의 문제도 없는 것을 알았다. 이 실험으로부터 알 수 있는 바와 같이, 상기한 특개평11-135466에 개시되어 있는 종래의 유기산계 지립 프리 연마액 (예를 들면, 과산화수소수는 30 중량%, 시트르산은 0.15 중량%, BTA는 0.2 중량%)의 약 5배의 연마 속도가 얻어지고 있는 것이 이해된다.

상기한 연마액에 인산을 가하지 않은 연마액, 혹은 과산화수소수를 가하지 않은 연마액에서는 Cu막(21)은 거의 연마되지 않았다 (연마 속도가 50nm/분 이하). 또한, BTA를 가하지 않은 연마액에서는 Cu막(21)에 대해 200nm/분 정도의 연마 속도가 얻어졌지만, 에칭 속도가 100nm/분으로 매우 높은 값으로 되고, 매립 배선 가공용의 연마액으로서는 적합하지 않은 것을 알았다.

다음에, Cu막(21)을 상기 연마에 의해서 제거하여 배리어 금속막(22)을 노출한 후, 상기한 연마액에 실리카 지립을 1중량% 가한 연마액을 이용하여 배리어 금속인 TiN의 연마를 행하였다. 상기한 Cu막(21)에 대한 것과 마찬가지의 연마 방법에 의해 실험한 결과, TiN막(22)의 연마 속도는 100nm/분의 값이 얻어졌다. 또한, SiO<sub>2</sub>막(23)의 연마 속도는 1nm/분 이하였다.

또, 이 기초 실험에서는 배리어 금속으로서 TiN을 이용하였지만, Ta 및 TaN도 연마 시간을 바꿔 마찬가지의 방법으로 실험한 결과, Ta와 TaN의 연마 속도는 각각 40nm/분, 50nm/분의 값이 얻어졌다.

한편, 인산을 대신해서 아인산, 차아인산, 메터인산을 이용하여 연마액을 제작하고, 상기와 마찬가지로 Cu의 연마 속도를 측정한 결과, 각각 550nm/분, 520 nm/분, 500nm/분이었다. 어느 것이나 예상 속도는 1.0nm/분 이하로 억제되어 있고, 디싱 발생의 문제는 없는 것을 알았다.

또한, 아인산은 인산과 비교하여, 연마면의 표면 거칠기를 억제하는 효과가 있는 것이 연마면의 현미경 관찰로 알았다. 또한, 어느 한쪽의 연마액에 있어서도 TiN의 연마 속도는 100nm/분, Ta와 TaN의 연마 속도는 각각 40nm/분 및 50nm/분이었다. 또,  $\text{SiO}_2$ 의 연마 속도는 0.1nm/분 이하이고, 침식 발생의 문제도 없는 것을 알았다.

다음에, 본 발명에 따른 인산의 연마액을 이용하여 실제로 매립 배선 내지 매립 플러그를 형성한 예를 설명한다. 또, 아인산, 차아인산, 메터인산 등의 다른 인산계 연마액에서도 마찬가지의 방법에 의해 실시할 수 있다.

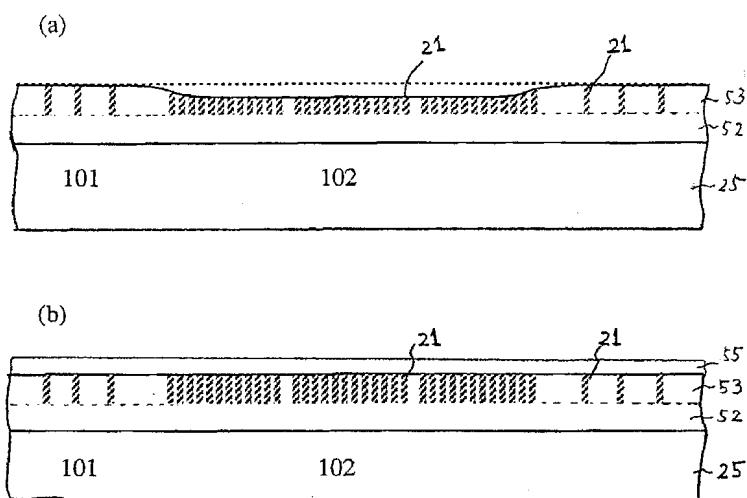

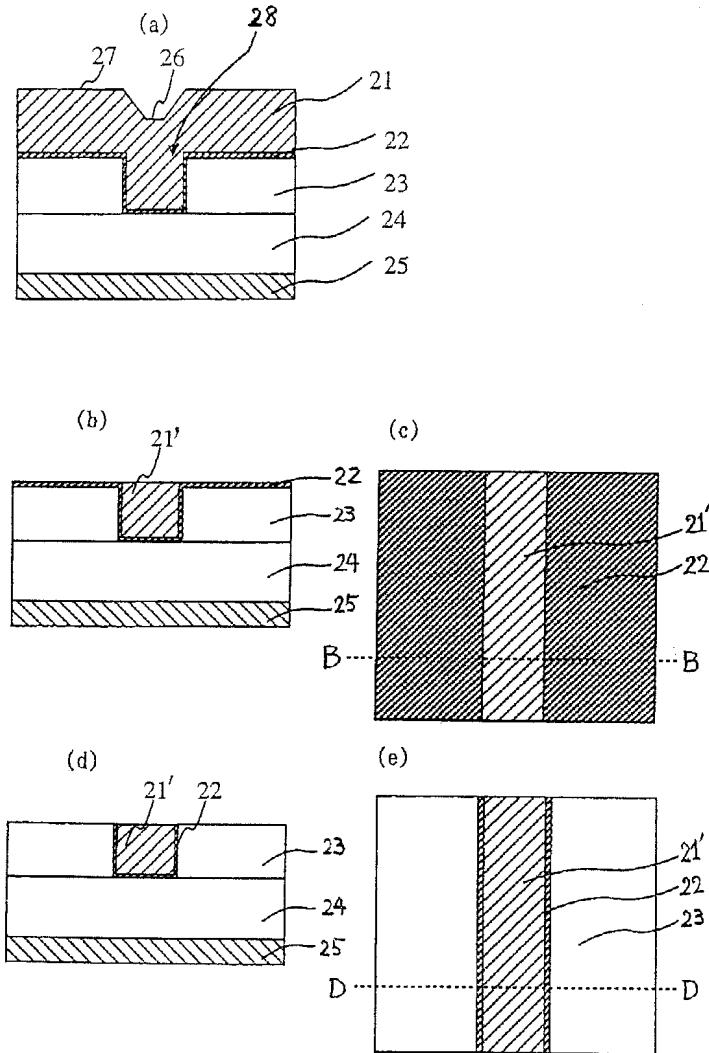

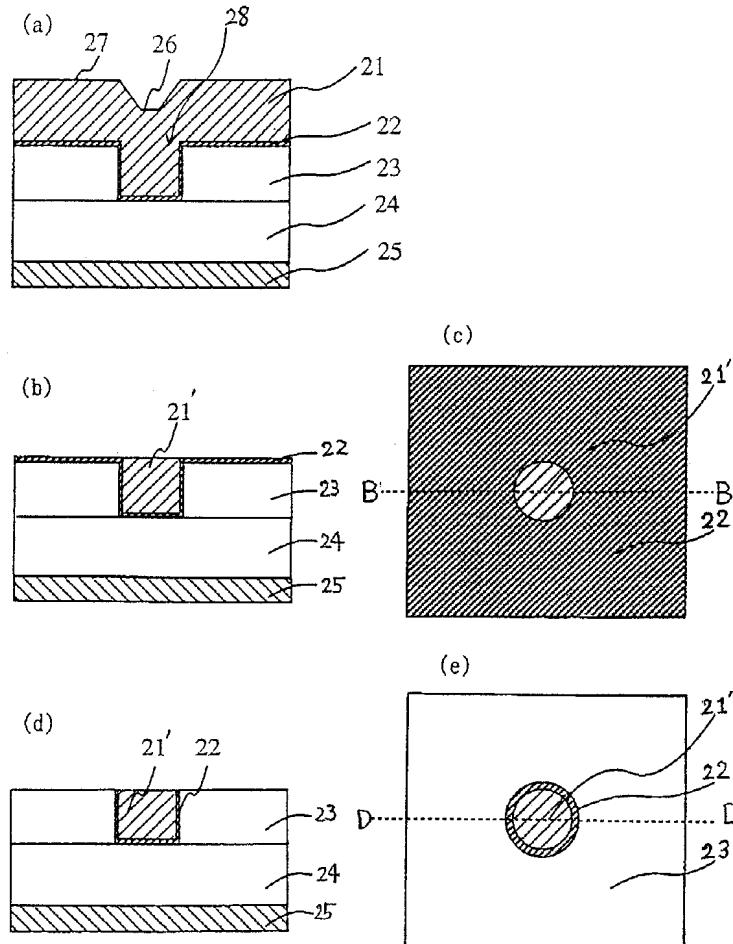

도 3의 (a)에 시료의 연마 전의 반도체 웨이퍼의 단면 구조의 예를 나타낸다. 불순물 도핑층이나 절연막 (도시 생략)이 형성된 실리콘 기판(25) 상에 두께 500nm의 BPSG막 (붕소와 인이 첨가된 실리콘 산화막: 24)과 두께 500nm의 실리콘 산화막(23)을 성막하고, 리소그래피 공정 및 드라이에치 공정에 의해 깊이 500nm의 배선용의 홈 패턴(28)을 실리콘 산화막(23) 내에 형성하였다.

그 홈(28)의 저면부, 측면부 및 실리콘 산화막(23)의 표면 상에 접착층 (베리어 금속층)으로서 두께 50nm의 TiN층(22)을 성막한 후에, 두께 800nm의 Cu 박막(21)을 스퍼터링법에 의해 진공 중에서 연속 성막하였다. 또한 단차 피복성을 좋게 하기 위해서 스퍼터 장치 내에서 450°C에서 3분간의 진공 열 처리를 행하였다.

또, 실리콘 기판(25)의 표면 부분에는 MISFET를 구성하는 소스, 드레인 등의 불순물을 도핑한 반도체 영역이나 게이트 절연막이나 게이트 전극이 형성되어 있지만, 상술한 바와 같이 여기서는 간략화를 위해 도시를 생략하고 있다.

이 시료(4)를, 상술한 인산계 지립 프리 연마액을 이용하여 도 2의 제1 정반(1)에 있어서 CMP를 행하였다. 그 결과, 상측부의 Cu막(21)이 연마에 의해 제거되고, 도 3의 (b)에 그 단면도를 (c)에 평면도를 도시하나 바와 같이, 디싱이나 침식이 약 50nm 이하의 실질적으로 평탄한 표면 형상으로 가공할 수가 있었다. 종래의 유기산계 지립 프리 연마액과 비교하여 약 4분의 1의 시간으로 연마가 종료하였다. 박리나 연마상은 발생하지 않았다. 또, 단면도 (b)는 평면도 (c)에서의 B-B 라인에서의 단면을 나타내고 있다.

계속해서, 상기한 인산계 연마액에 실리카 지립을 1중량% 첨가한 연마액을 이용하여, 절연막 ( $\text{SiO}_2$ 막: 23) 상에 남겨진 TiN막(22)의 연마를 도 2의 제2 정반(11)으로 행하였다. 연마 시간은 40초이다. 그 결과, 절연막 상의 TiN막(22)이 제거되고, 도 3의 (d)에 단면도를 (e)에 평면도를 도시한 바와 같이, 디싱이나 침식이 약 50nm 이하의 실질적으로 거의 평탄한 표면 형상의 매립 배선층(21')에 가공할 수가 있었다. 또, 단면도 (d)는 평면도 (e)에서의 D-D 라인에서의 단면을 나타내고 있다.

하나의 정반으로 Cu와 배리어 금속의 양방의 연마를 행하면, 연마 패드(2)에 잔류한 지립에 의해, 지립 프리 연마 시에 침식이 발생하였다. 이점으로부터, 지립 프리 CMP 전용의 연마 정반 및 패드를 준비하지 않으면 안되는 것을 알았다.

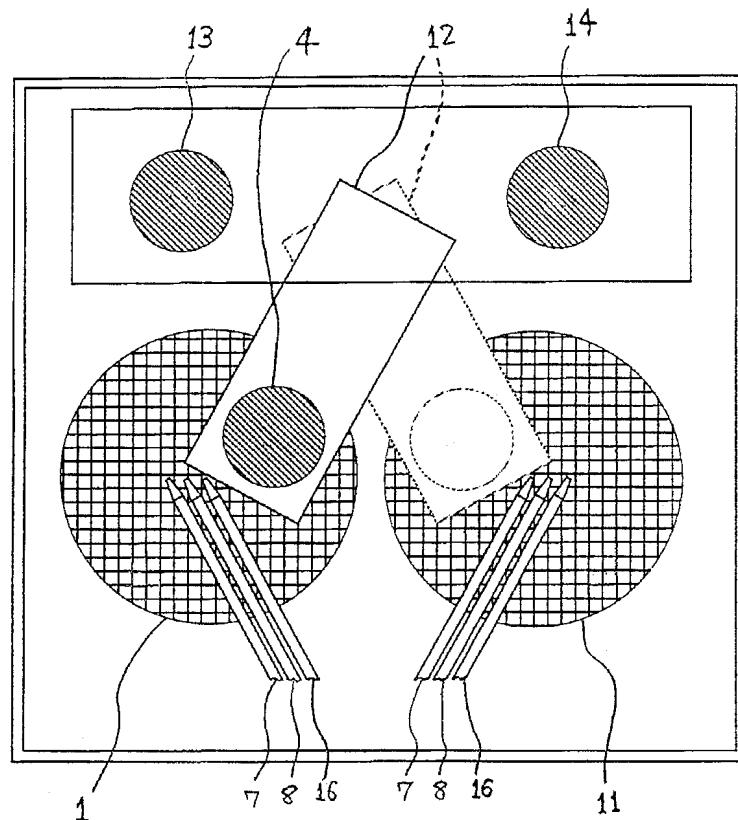

상기한 매립 배선과 마찬가지로 하여, 도 4의 (a)에 단면을 나타내는 시료를 2스텝에서 CMP함으로써, 도 4의 (d)에 단면도를 (e)에 평면도를 나타낸 바와 같이,  $\text{SiO}_2$  등의 절연막에 의해 그 주위가 둘러싸인 Cu의 매립 플러그 구조(21')를 형성할 수가 있었다.

Cu막(21)에 대한 CMP 후의 배리어 금속이 홈 내에 잔존한 상태는 도 3과 마찬가지로 도 4의 (b) 및 (c)에 도시하였다. 어느 한쪽의 단계에서도 디싱이나 침식은 약 50nm 이하가 되는 형상으로 가공할 수가 있었다. 박리나 연마상은 발생하지 않았다. 또, 이 예에서는, 플러그를 형성하는 경우의 Cu의 성막은, 구멍(28) 내로의 Cu의 매립성을 향상시키기 위해 전해 도금법으로 행하였다.

상기한 배리어 금속의 연마로 이용한 연마액의 BTA 농도는 0.2 중량%이고, 이 농도는 Cu 연마에 이용한 연마액의 농도와 동일하다.

배리어 금속용의 연마액으로 Cu의 연마 속도를 저감하여, 디싱을 더욱 억제하기 위해서는 배리어 금속용 연마액의 BTA 농도를 높이는 것이 유효하다. 예를 들면, 배리어 금속을 연마할 때에 BTA를 0.5 중량%로 증가함으로써, Cu의 연마 속도

는 반 정도까지 저하한다. 배리어 금속용의 연마액 중에 이 농도의 BTA를 미리 첨가하여 놓는 방법과, 정반(11)에 Cu 연마액의 공급과 동시에 예를 들면 1% BTA 물을 추가 공급하는 방법이 있다. 도 2의 참조 번호(16)는 그와 같은 연마액의 조성 조정을 가능하게 하기 위한 액체 공급관이다.

도 3의 (d)에서 형성된 매립 Cu 배선(21')의 전기 저항율을 측정한 결과, TiN층의 부분도 포함시켜  $1.9\mu\Omega\text{cm}$ 의 값을 얻었다. 또한, 사행 배선 (배선폭  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)나 빗형 배선 (배선 간격  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)을 이용하여 도통/절연 시험을 행한 결과, 거의 100%의 수율이 얻어졌다.

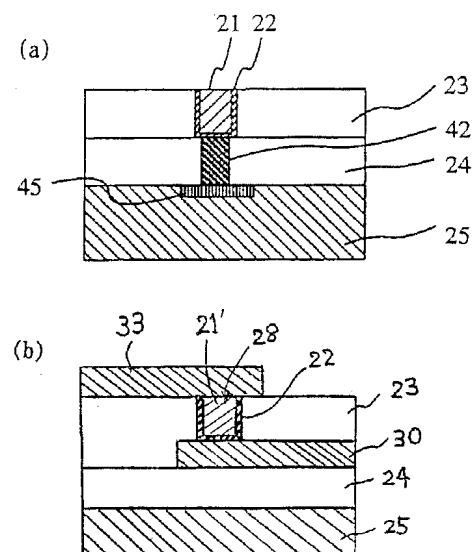

또한, 도 5의 (a)에 단면도를 도시한 바와 같이, 불순물이 도핑된 반도체층(45)으로부터 절연층(24) 내의 홈에 매립된 텅스텐으로 이루어지는 플러그(42)를 갖는 반도체 기판에 대해, 상기 도 4에서 설명한 바와 같이 Cu 플러그(21')를 형성하였다. 그 결과, 텅스텐 플러그(42)를 통해서, 정상적으로 도통이 얻어져, LSI로서의 동작도 정상인 것을 알았다. 이 경우에도, 최상층을 형성하는 절연막(23) 및 그 중에 매립된 배선 플러그(21')의 평탄 특성은, 상기와 마찬가지의 디싱 및 침식이 50nm 이하의 실질적으로 평탄한 주 표면을 나타내고 있는 것을 확인하였다.

또한, 본 발명은 후에 상세히 설명하지만, 기본적으로는 도 5의 (b)에 도시한 바와 같은 다층 배선 구조체의 형성을 위해 매우 유익하다. 즉, 기판(25) 상의 제1 절연층(24) 상에 제1 배선층(30)을 설치하고, 그 위에 제2 절연층(23)을 피착하고, 이 절연층(23)에 관통하는 홈(28)을 설치하고, 이 홈(28) 내부 표면 및 절연막(23)의 표면에 배리어 금속막(22) 및 Cu막(21)을 피착시켜서, 상술한 바와 같이 본 발명의 CMP 기술에 의해 절연막(23) 상의 금속(21 및 22)을 제거하여 매립 배선 또는 플러그(21')를 형성하고, 이러한 통상 방법으로 소정 패턴을 갖는 제2층째의 배선층(33)을 형성한다. 이 때, 제2층째의 배선층은 스퍼터링이나 증착 기술에 의해서 절연층(23)의 전 표면에 피착되고, 그것에 대해 미세한 패턴을 갖는 포토마스크를 이용한 사진 처리 혹은 드라이 에칭 기술에 의해서 소정의 미세한 패턴에 가공되지만, 그 때의 초점 맞추기나 위치 정렬 등의 처리로 절연막(23) 및 배선층(33)의 표면의 평탄 특성은 매우 중요하고, 본 발명이 매우 유익하게 공헌한다.

또, 도 5의 (b)와 같이 본 발명의 CMP 기술을 이용하여 Cu의 매립 배선 혹은 플러그(21)를 형성했을 때에, 상기한 연마액 중의 보호막 형성제 등에 의해서 Cu 표면에 얇은 보호막이 형성되어 있기 때문에, 제2 배선층과의 전기적 접속 특성을 개선하기 위해서 제2 배선층을 피착하기 전에 이 Cu의 표면을 암모니아 플라즈마 등의 환원성 분위기에서의 플라즈마로 처리하여 그 보호막을 제거해 놓는 것은 중요하다. 이 플라즈마 처리의 상세는 본원 출원인이 먼저 특허 출원한 특원평11-226876에 기재되어 있는 바와 같으며, 여기서는 생략한다. 또한, 이하의 각종 적용예에서도 이 플라즈마 처리를 실시하였지만 상세한 설명은 중복을 피하기 위해서 생략하였다.

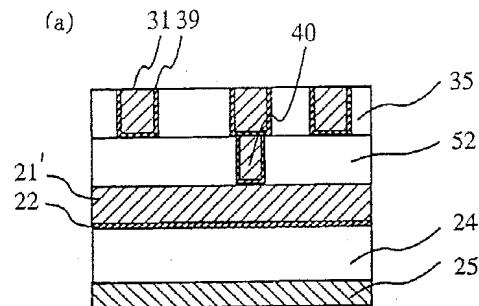

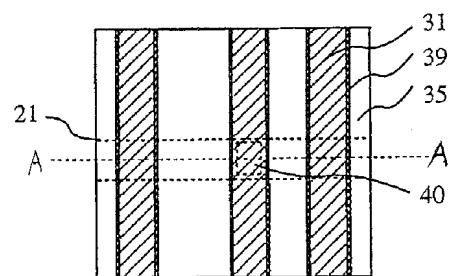

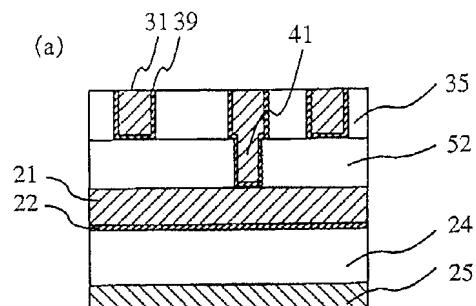

또한, 도 3의 매립 배선 구조와 도 4의 매립 플러그 구조의 제조 프로세스를 반복하여 행함으로써, 도 6과 같은 적층 배선 구조를 형성하는 것도 가능하였다. 도 6의 (b)는 평면도이고, (a)는 그 A-A 라인에서의 단면도를 나타내고 있다. 참조 번호(31)는 매립 Cu 배선이다. 플러그(40)의 도통 수율은 거의 100%의 값이 얻어지고, LSI로서의 정상적인 동작도 확인하였다. 또, 플러그(40)의 재료는 Cu를 이용하여도, 텅스텐을 이용하여도 마찬가지로 도통을 얻을 수 있었다.

텅스텐의 경우에는, CVD에 의한 성막이 매립성의 관점으로부터 유리하고, TiN이나 Ti 등의 접착 금속막은 설치하지 않아도 좋다.

또한, 도 7과 같은 이중 상감에 의해 형성된 플러그(41)를 형성하는 것도 가능하게 되었다. 이에 따라 적층 배선의 공정수를 감소시키는 것이 가능해졌다. 이 방법에서도 LSI로서의 정상적인 동작을 확인하였다. 상기 도면 (b)는 평면도를, (a)는 그 A-A 라인에서의 단면도를 나타내고 있다.

도 6 및 도 7에서 형성된 다층 배선 구조체에 있어서도, 최상층을 형성하는 절연막(35) 및 그 중에 매립된 배선층(21')의 평탄 특성은, 상기 동일 모양 배리어 금속층과 함께 디싱 및 침식이 50nm 이하의 실질적으로 평탄한 공통의 주 표면을 나타내고 있는 것을 확인하였다.

도 6 및 도 7의 배선 형성 방법 및 플러그 형성 방법을 이용함으로써, 배선층이 3층 이상이 되는 LSI의 다층 배선 형성에 적용할 수가 있었다. 특히, 하나의 반도체 칩 상에 전극 배선 밀도가 장소에 의해서 매우 다른 다층 배선을 갖는 시스템 LSI에 적용하여, 그 효과를 확인하였다.

이하, 그점에 대해서 상세히 설명한다.

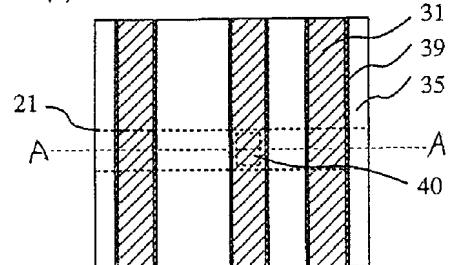

도 8의 (a)는, 침식이나 디싱을 발생시키는 종래의 연마액 내지 연마 방법으로 CMP를 행한 경우의 배선 주요부 단면도이고, 배선부의 표면에  $\text{SiO}_2$  등의 절연막(23)의 부분적 애칭에 의한 오목부, 즉 침식이 발생하고, 또한 Cu 등의 금속부(21)의 부분적 핵물에 의한 오목부, 즉 디싱이 발생하고 있다.

그것에 대하여, 본 발명에 따르면 도 8의 (b)에 도시한 바와 같이, 배선 부재를 매립한 절연막(23) 및 그 배선 부재에 침식이나 디싱을 50nm 이하로 억제한 즉 실질적으로 평탄한 표면을 실현할 수가 있어, 이것이 다층 배선의 형성에 매우 큰 효과를 가져오는 것이다.

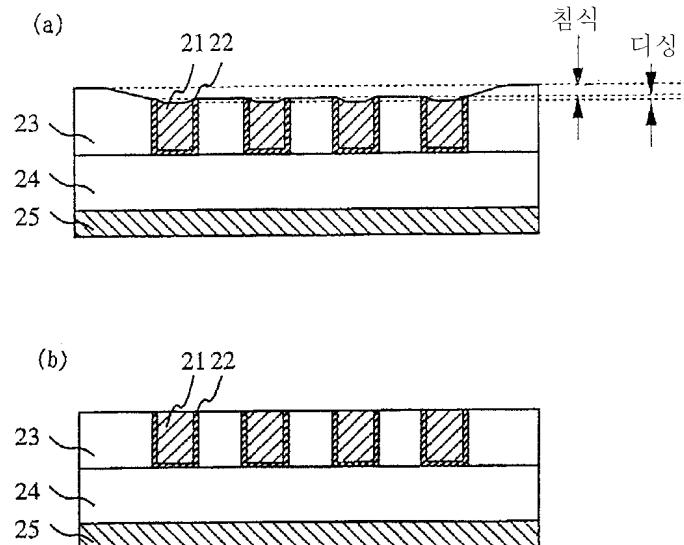

도 9를 기초로, 종래의 CMP 기술에 의해서 다층 배선을 형성한 경우와 본 발명의 연마액 내지 연마 방법을 이용한 CMP에 의해서 다층 배선을 형성한 경우와의 차이를 설명한다. 또, 도 9에서는 간략화를 위해, 층간 절연막 내에 매립된 금속 배선 부재 내지 플러그를 주체로 묘사되어 있고, 이들에 접속된 복수의 다층 배선의 구성은 생략되어 있다. 이들의 구성은 이미 상술한 도 1의 (b) 및 그 설명으로부터 분명하다.

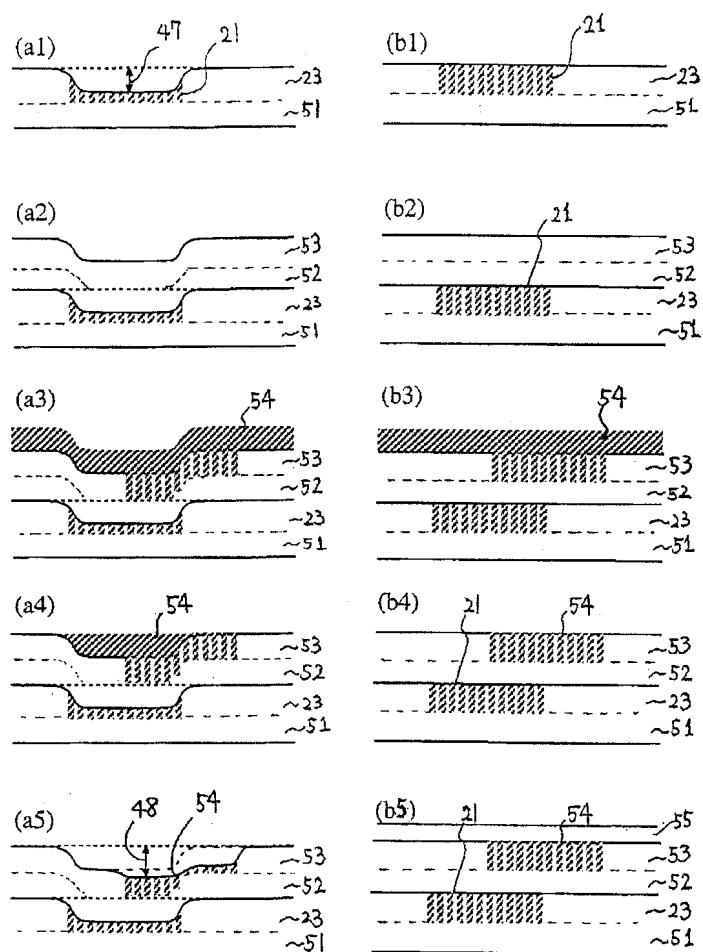

도 9의 (a1) 내지 (a5)는 종래의 연마액을 이용한 CMP에 의해서 다층 배선을 형성한 경우의 다층 배선 주요부의 공정마다의 확대 단면도를 나타낸다. (a1)에 있어서의 참조 번호(21)는 CMP에 의해서 절연막(23) 중에 매립된 Cu 등의 플러그이고, (a2)와 같이 그 위에 소정 패턴의 제2층째의 배선(52)이 설치되고, 그 위에 제3번째의 층간 절연막(53)이 설치된다. (a3)과 같이, 절연막(53) 내에 홈이 설치되고, 그 홈 내부를 매립하도록 절연막(53) 상에 Cu 등의 금속막(54)이 형성된다. 계속해서, (a4)와 같이, 이 금속막(54)에 대하여 2번째의 CMP가 실시된다. 그러나, (a1)의 CMP 공정에서 발생한 오목부(침식 내지 디싱: 47) 중에 금속막(54)이 남게 되기 때문에, 그것을 제거하기 위해 과잉의 CMP를 계속시켜 제2층째의 매립 배선 부재 내지 플러그(54)를 형성하고, (a5)와 같이 오목부(47)보다도 깊이가 깊게 된 오목부(48)를 갖는 다층 배선 구조로 되어 있다.

이와 같이 종래의 연마액으로 CMP를 행하면, 하층에서 발생한 디싱이나 침식의 영향으로 상층이 될수록 연마 잔여물이 발생한다고 하는 문제가 있었다. 도 9의 (a4)에 도시한 연마 잔여물을 제거하기 위해 여분의 오버 CMP 시간이 상층으로 됨 따라서 증가하고, 또한 그것이 디싱이나 침식을 가속시킨다고 하는 문제가 있었다. 즉, 이 여분의 CMP에 의해서 도 9의 (a5)에 도시한 바와 같이 상층이 되면 될수록 디싱이나 침식이 증가하고 있었다.

배선 층수가 3층 이상이 되면 연마 잔여물이 더욱 증대하고, 이것을 완전히 제거하려고 하면 밀집부의 배선 자체가 침식에 의해서 반 이상 소멸한다고 하는 문제가 발생한다. 즉, 종래의 연마 방법에서는 디싱 및 침식을 50nm 이하로 억제하는 것은 곤란하였다. 또한, 7층까지 제작한 경우에도 당연히 100nm 이하로 억제하는 것은 곤란하였다.

한편, 도 9의 (b1) 내지 (b5)는 본 발명의 연마 방법을 이용한 CMP에 의해 다층 배선을 형성한 경우의 마찬가지의 공정 외의 주요부 단면도이고, (b1)에 있어서의 참조 번호(21)는 CMP에 의해서 제2층째의 절연막(23) 중에 매립된 Cu 등의 금속 배선 부재 또는 플러그이고, 그들은 그 아래의 제1번째의 절연층(50) 상의 제1 배선층(51)에 접속되어 있다. 계속해서, (b2)와 같이 그 위에 소정 패턴의 제2층째의 배선층(52)이 설치되고, 그 위에 제3번째의 층간 절연막(53)이 설치된다. 다음에, (b3)와 같이, 제3 절연막(53) 내에 홈이 설치되고, 그 홈 내부를 매립하도록 절연막(53) 상에 Cu 등의 금속막(54)이 형성된다. 계속해서, (b4)와 같이, 이 금속막(54)에 대하여 2번째의 CMP가 실시된다. 이러한 후, (b5)와 같이, 이 제3 절연층(53) 및 제2 배선 부재 또는 플러그(54) 상에 제3 배선층(55)을 설치한다.

본 발명의 CMP 기술에 따르면, 도 9의 (b4)에 도시한 바와 같이 연마 잔여물은 전혀 발생하지 않고, 평탄한 제2번째의 배선 부재 또는 플러그(54) 및 제3 절연층(53)의 공통 주표면을 실현할 수 있었다. 따라서, 도 9의 (b5)에 도시한 바와 같이, 이 제3 절연층 상에 통상의 리소그래피 기술에 의해 미세한 패턴 형상의 제3 배선층(56)을 설치하는 것을 용이하게 할 수 있었다.

마찬가지의 공정을 반복하여 행하고 제4층까지 금속 배선을 제작하여도 디싱 및 침식이 50nm 이하로 억제하는 것이 가능해졌다.

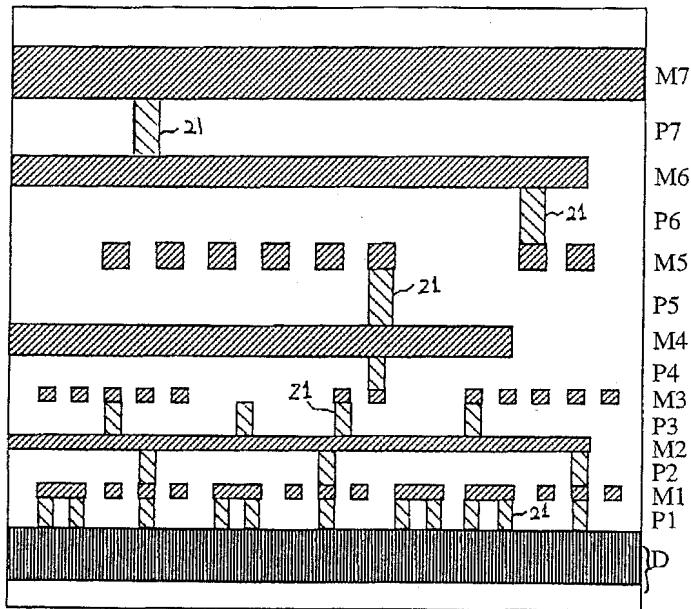

또한, 도 10에 도시한 바와 같이 제7층까지 본 발명의 CMP를 사용하여 금속 배선을 제작하여도 최상층의 디싱 및 침식을 80nm 이하로 억제하는 것이 가능해졌다. 도 10은 시작한 전자 회로 장치의 주요부 단면도이고, D는 베이스가 되는 반도체 등의 기판, P1~P7은 절연막 내에 매립된 Cu의 금속 배선 부재 내지 플러그(이러한 플러그를 비어라고도 칭한다) 등의 배선 부재이고, M1~M7은 이들 금속 배선 부재 내지 플러그와 전기적으로 접속된 배선층이다.

이 도 10은 단일 상감을 채용한 경우이며, 충간 절연층 내에 매설된 배선 부재 또는 플러그 형성도 포함시켜 14회의 CMP (M1~M7, P1~P7)를 반복하여 완성시킨 것이다. 이것을 이중 상감으로 형성한 경우에서도 마찬가지로 디싱 및 침식을 80 nm 이하로 억제할 수가 있었다.

이 종류의 다층 배선 구조체를 갖는 전자 회로 장치에서는, 그 용도에 따라서도 다르지만, 대체적으로 제10층째 정도의 배선층에서 하층부에 비교하여 비교적 조밀하지 않은 패턴으로 배선이 형성되어 있기 때문에, 도 10에 도시한 바와 같이 적어도 상측의 제7층째의 배선 M7을 그 위에 형성하는 제7번째의 매립 배선 부재 또는 플러그 및 그것을 매립하는 충간 절연막 P7 (즉, 화학 기계 연마 처리가 실시되어 형성되는 최상부의 절연층)이 형성하는 주 표면 레벨을 상기한 바와 같이 평탄하게 하는 것이 바람직하다. 본 발명에서는 상기한 바와 같이, 그 중에서 매설된 상기 배선 부재 또는 플러그가 침식 80 nm 이하, 디싱 80nm 이하가 실질적으로 평탄한 주 표면 레벨을 갖고 있는 (즉, 기복 또는 요철의 고저차가 80nm 이하의 실질적으로 평탄하다) 최상층 절연막을 얻을 수 있었다. 더구나, 이 평탄한 공통 주 표면이 대부분 기판 상부의 넓은 영역에 걸쳐 얻을 수 있어, 그 위의 피착 절연막의 평탄도도 80nm 이하로 할 수 있었다.

또한, 도 11은 LSI 칩 내에서의 메모리 어레이부(102)와 논리 등의 주변 회로부(101) 상에 다층 배선을 형성한 경우의 주요부 단면도를 도시한 것이다. 메모리 어레이부(102)를 구성하는 반도체 기판(칩)의 영역에는 DRAM, SRAM, 플래시 메모리 등과 같이 다수의 반도체 회로 소자(도시 생략)가 주변 회로부(101)를 구성하는 반도체 기판의 영역보다도 훨씬 고밀도로 그 중에 집적되어 있고, 따라서, 반도체 기판(25)의 표면 상부의 전극 배선이 밀집하고 있고, 주변 회로부와 비교하여 전극 배선 밀도가 30% 이상의 비율로 현저히 높다.

따라서, 메모리 어레이부(102)와 주변 회로부(101)에서는 전극 배선 밀도의 소밀차가 크고, 종래의 연마 방법에서는 메모리 어레이부(102)의 상부의 다층 금속 배선 형성 시의 오버 CMP 시간이 길어져서, 도 11의 (a)에 도시한 바와 같이 논리부(101)와 비교하여 침식 및 디싱이 증대한다. 이것을 다층화하면 도 9의 (a1) 내지 (a5)에서 설명한 문제가 발생하고, 3층 이상 적층하면 배선 저항이 대폭 증대한다고 하는 문제가 발생하였다.

이 대책 방법으로서, 외견 상의 전극 배선 밀도를 균등하게 하기 위해서, 전기적으로 어디에도 접속되어 있지 않은 더미 배선이나 1미크론오더의 더미 플러그를 미리 다수 설치하고 그 위에 피착한 절연층이나 금속막을 연마하는 것도 생각되지만, 불필요한 기생 배선 용량이 발생하는 등의 우려가 있다.

이것에 대해, 본 발명의 연마 방법은 오버 CMP에 대한 내성이 높기 때문에, 이러한 전극 배선의 소밀차가 큰 부분이 동일 칩 내에 공존하는 LSI에서도, 본 발명에 따른 CMP를 반복하여 행함으로써, 도 11의 (b)에 도시한 바와 같이 디싱 및 침식을 50nm 이하로 억제할 수가 있었다. 특히, 이와 같이 전극 배선 밀도가 극단적으로 큰 메모리 매트를 칩 내에 내장하는 LSI에 본 발명을 적용함으로써, 상측의 제3층째의 적층 배선(55)을 상기한 바와 같이 실질적으로 평탄한 (즉, 기복 또는 요철의 고저차가 50nm 이하의) 제3번째의 플러그 및 충간 절연막(53)의 공통 주 표면 상에 형성할 수가 있었다. 또한, 이 평탄한 주 표면이 소자 형성 밀도 내지 배선 밀도가 다른 이격한 반도체 영역에 걸쳐 1장의 반도체 웨이퍼 상부에 형성할 수 있던 것은, 이점으로부터의 더욱 대규모인 LSI로 전개하기 위해 매우 공헌하는 것이다.

또한, 이와 같이 형성된 제3층 배선 상에 배선층을 더욱 적층하더라도 배선 저항의 증대 없이 평탄한 배선층을 형성할 수가 있다.

상기 도 9 내지 11로부터도 알 수 있는 바와 같이, 본 발명에 따르면 화학 기계 연마를 다수회 (적어도 3회) 반복하여 다층 배선 구조체를 형성하여도, 침식이나 디싱이 매우 적은 실질적으로 평탄한 최상층을 실현할 수가 있다. 그것에 따라, LSI나 전자 회로 장치를 제조하기 위해 예를 들면 다음과 같은 여러가지의 효과를 발휘하는 것이다. (1) Cu 배선 저항을 LSI의 설계 규격대로 낮은 값으로 제작할 수 있고, (2) 오버 CMP를 하지 않고도 웨이퍼면 내에서의 배선 저항의 변동을 감소할 수 있다. 또한, (3) 그 상층에 대한 리소그래피 공정으로 광학적 초점 맞추기도 하기 용이해져서 정밀도 높게 가공할 수 있고, 그것에 따라 (4) 상부에 상감 배선을 형성하는 경우에는 연마 잔여물을 방지할 수가 있다. (5) 쓸데 없는 더미 배선이나 플러그(비어)를 설치할 필요가 없다.

(실시예 2)

본 실시예에서 이용한 Cu용의 지립 프리 연마액은 과산화수소수 (시판의 30%  $H_2O_2$  수용액)와 인산과 폴리아크릴산 암모늄염으로 구성된 수용액이다. 조성은, 과산화수소수는 30 중량%, 인산은 0.2 중량%, 폴리아크릴산암모늄염은 0.1 중량%이다. 이 연마액을 이용하여, Cu막의 연마 속도와 에칭 속도를 측정하였다. 연마 특성의 평가는 실시예 1과 마찬가지로 행하였다.

베리어 금속막의 연마용에는 상기한 연마액에 실리카 지립을 1% 첨가한 것을 이용하였다.

그 결과, Cu의 연마 속도는 500nm/분, 에칭 속도는 1.0nm/분 이하로 억제되어 있고, 디싱 발생의 문제는 없는 것을 알았다. 상기한 종래의 유기산계 지립 프리 연마액의 약 5배의 연마 속도가 얻어졌다. 또,  $SiO_2$ 의 연마 속도는 0.1nm/분 이하이고, 침식 발생의 문제도 없는 것을 알았다.

실리카 지립을 1% 첨가한 연마액에 의한 베리어 메탈 TiN의 연마 속도는 100 nm/분이었다. 본 실시예에서는 TiN을 이용하였지만, Ta와 TaN도 연마 시간을 바꿔 마찬가지로 실시할 수 있다. Ta와 TaN의 연마 속도는 각각 40nm/분, 50nm/분이었다. 또,  $SiO_2$ 의 연마 속도는 1nm/분 이하였다.

매립 배선을 형성하는 시료를, 상술한 연마액으로 2스텝에서 CMP를 행한 결과, 도 3의 (d) 및 (e)와 같이, 디싱이나 침식이 약 50nm이하가 되는 형상으로 가공할 수가 있었다. 종래의 유기산계 지립 프리 연마액과 비교하여 약 5분의 1의 시간으로 Cu 연마가 종료하였다. 박리나 연마상도 발생하지 않았다.

플러그 구조도 도 4의 (d) 및 (e)와 같이, 디싱이나 침식이 약 50nm 이하가 되는 형상으로 가공할 수가 있었다.

형성된 Cu 배선의 전기 저항율을 측정한 결과, TiN층의 부분도 포함시켜  $1.9\mu\Omega\text{cm}$ 의 값을 얻었다. 또한, 사행 배선 (배선 폭  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)나 빗형 배선 (배선 간격  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)을 이용하여 도통/절연 시험을 행한 결과, 거의 100%의 수율이 얻어졌다.

도 5, 도 6 및 도 7과 같은 적층 배선 구조를 제작하는 것도 가능하였다. LSI의 동작도 정상인 것을 알았다. 또한, 도 10 및 도 11의 (b)와 같은 다층 배선을 갖는 전자 회로 시스템 및 LSI에도 적용한 결과, 실시예 1에서 설명한 것과 거의 동일 효과가 얻어지는 것도 확인하였다.

본 실시예 2에서는 폴리아크릴산 암모늄염을 이용하였지만, 대신에 동일 농도의 염화세틸페리듐을 첨가함으로써, 상기한 연마 속도를 달성하고, 또한 연마액 보관 시나 폐액 중에 있어서의 곰팡이 및 박테리아의 발생을 방지할 수가 있었다.

또한, 본 실시예 2에서 이용한 폴리아크릴산암모늄염의 분자량은 1만 정도의 것이지만, 분자량 10만 정도의 것을 이용함으로써 Cu의 연마 속도를 20% 증가시키는 것이 가능하였다. 또, 분자량 100만을 넘는 가교형 폴리아크릴산 암모늄염을 이용함으로써 Cu의 연마 속도를 30% 증가시키는 것이 가능하였다.

본 실시예 2에서 이용한 연마액에, 제2 보호막 형성제로서 또한 BTA를 0.2 중량% 첨가함으로써 Cu의 연마 속도를 50% 증가시키는 것이 가능하였다.

(실시예 3)

본 실시예에서 이용한 연마액은 과산화수소수 (시판의 30%  $H_2O_2$  수용액)와 인산과 BTA와 메탄올로 구성된 수용액이다. 조성은 과산화수소수는 30 중량%, 인산은 0.2 중량%, BTA는 0.2 중량%, 메탄올은 1중량%이다. 또한, 이 연마액에 실리카 지립을 1% 첨가한 것도 준비하였다. 이들 2종류의 연마액을 이용하여, Cu막의 연마 속도와 에칭 속도를 측정하였다. 연마 특성의 평가는 실시예 1과 마찬가지로 행하였다.

그 결과, 실리카 지립이 들어간 연마액의 Cu의 연마 속도는 800 nm/분이며, 에칭 속도는 1.0nm/분 이하로 억제되어 있고, 디싱 발생의 문제는 없는 것을 알았다. 실리카 지립을 포함하지 않은 연마액의 Cu의 연마 속도는 실시예 1과 마찬가지로 550nm/분이었다.

또한, 실리카 지립이 들어간 연마액의 TiN의 연마 속도는 100nm/분, 실리카지립을 포함하지 않은 연마액의 TiN의 연마 속도는 20nm/분이었다. Ta의 연마 속도는 각각 40nm/분 (지립 있음), 10nm/분 (지립 없음)이고, TaN의 연마 속도는 각각 50nm/분 (지립 있음), 15nm/분 (지립 없음)의 값이 얻어졌다. 이하의 실험에서는, TiN을 배리어 금속막으로서 이용한 예를 나타낸다. Ta와 TaN도 연마 시간을 바꿔 마찬가지의 방법으로 실시할 수 있다.

도 3의 (a)에 도시한 매립 Cu 배선을 형성하는 시료를, 실리카 지립이 들어간 연마액으로 1스텝에서 [즉, Cu막과 TiN막을 계속하여 도 2의 제2 정반(11)으로] CMP를 행한 결과와 실시예 1과 마찬가지로 2스텝에서 연마한 경우에 Cu 배선의 가공 형상을 비교하였다. 1스텝에서 연마한 경우에는 도 8의 (a)와 같은 형상으로 가공되고, 50nm 이상의 침식이 발생하였다. 디싱에 대해서는 50nm 이하로 억제되어 있다. 한편, 2스텝에서 CMP한 시료의 동일 배선 구조의 부분을 관찰한 결과는 도 8의 (b)에 도시한 바와 같이 실질적으로 평탄한 표면이 얻어지는 것을 알았다. 지립의 유무에 따른 침식 크기의 차이를 보여진다.

또한, 연마상을 표면 결합 검사 장치로 조사하면, 1스텝의 경우에는 웨이퍼당 수 10 내지 수 100개의 연마상이 발생하고 있는 것을 알 수 있다.

이러한 문제가 있지만, 상기한 1스텝 CMP는 2스텝 CMP의 경우와 비교하여, TiN의 연마 시간까지 포함시키면 약 3분의 1의 시간으로 연마가 종료하였기 때문에, 처리량 향상의 관점으로부터는 장점이 있다.

1스텝 CMP에서 형성된 Cu 배선의 전기 저항율을 측정한 결과, TiN층의 부분도 포함시키고  $1.9\mu\Omega\text{cm}$ 의 값을 얻었다 (막 두께 감소분을 고려). 단, 배선 저항치는 2스텝에서 얻은 값과 비교하여 10% 정도 높은 값으로 되었다. 이것은 침식이 크기 때문이라고 생각된다. 또한, 사행 배선 (배선 폭  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40 mm)이나 빗형 배선 (배선 간격  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)을 이용하여 도통/ 절연 시험을 행한 결과, 거의 100%의 수율이 얻어졌다.

또한, 실시예 1과 마찬가지로, 도 5, 6, 7, 10 및 11과 같이 적층 배선을 형성하여 LSI를 시작한 결과 거의 마찬가지의 효과가 얻어지고, 또는 LSI의 회로 동작을 조사한 결과, 정상적으로 동작하는 것도 확인하였다.

(실시예 4)

본 실시예 4에서는, 지립 프리의 연마액으로 Cu를 연마한 후 드라이 에칭법에 의해서 배리어 금속을 제거한 완전 지립 프리 프로세스에 대한 예를 진술한다.

드라이 에칭에는  $\text{SF}_6$ (육불화유황) 가스를 이용하였다. 가스 유량은 25cc/분, 처리 압력은 5mmTorr, 플라즈마용 고주파 출력은 600W, 바이어스용 고주파 출력은 0 내지 100W이다.

이 조건으로 배리어 금속막과  $\text{SiO}_2$ 막의 에칭 선택비를 조사한 결과, 바이어스 전력이 높아질수록 에칭 속도가 증가하지만, 바이어스 전력을 인가하지 않은 경우에 가장 선택비가 높아졌다. 바이어스 전력 0으로,  $\text{TiN}/\text{SiO}_2$  선택비가 15,  $\text{TaN}/\text{SiO}_2$  선택비가 11이었다.

$\text{TiN}$ 이나  $\text{TaN}$ 은 F 래디컬에 의한 에칭 효과가 큰 데 대해,  $\text{SiO}_2$ 는 F 래디컬만에 따라서는 에칭되기 어려워, 바이어스 전력 인가에 의한 이온의 가속 효과를 필요로 하기 때문에, 바이어스 전력을 인가하지 않는 쪽이 선택비가 커졌다고 생각된다.

또, Cu는 이 조건에서는 전혀 에칭되지 않은 것도 확인하였다.

드라이 에칭 속도는  $\text{TiN}$ 의 경우에 320nm/분,  $\text{TaN}$ 의 경우에 240nm/분이었다.

이하에 상기한 드라이 에칭법을 이용하여 Cu 배선 내지 플러그를 형성하는 방법을 보다 상세히 설명한다. 배리어 금속은  $\text{TaN}$ 을 이용하였다.  $\text{TiN}$ 의 경우에도 완전히 동일하다.

도 3이나 도 4의 (a)에 도시한 시료를 준비하고, Cu의 CMP에 대해서는, 다른 실시예에 기재한 인산계 지립 프리 연마액을 이용하여 마찬가지로 실시하였다. 그 후, 웨이퍼를 브러시 스크립 세정하여 건조 후, 드라이 에칭 장치로 상기한 조건으로  $\text{TaN}$ 막의 제거를 행한 결과, 도 3의 (d) 및 (e)와 같이 디싱이나 침식이 약 50nm 이하가 되는 형상으로 가공할 수가 있었다.

또한, 플러그에 대해서도 도 4의 (d) 및 (e)와 같은 평탄 구조를 형성할 수가 있었다. 이 경우, Cu의 성막은 매립성을 향상시키기 위해 공지의 전해 도금법으로 행하였다. 이 경우에도, 디싱이나 침식은 약 50nm 이하가 되는 형상으로 가공할 수가 있었다. 박리나 연마상은 발생하지 않았다.

상기 방법으로 형성된 Cu 배선의 전기 저항율을 측정한 결과, TiN층의 부분도 포함시켜  $1.9\mu\Omega\text{cm}$ 의 값을 얻었다. 또한, 사행 배선(배선 폭  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)이나 빗형 배선(배선 간격  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)을 이용하여 도통/절연 시험을 행한 결과, 거의 100%의 수율이 얻어졌다.

또한, 도 5와 같이 불순물 도핑층(45)으로부터 텅스텐 플러그(42)를 통해서 정상적으로 도통이 얻어져, LSI의 동작도 정상인 것을 확인하였다.

도 3의 배선 구조와 도 4의 플러그 구조의 제조 프로세스를 반복하여 행함으로써 도 6과 같은 적층 배선 구조를 형성하는 것도 가능하였다. 플러그의 도통 수율은 거의 100%의 값이 얻어지고, LSI의 정상적인 동작도 확인하였다.

또, 플러그의 재료는 Cu를 이용하여도, 텅스텐을 이용하여도 마찬가지로 도통을 얻을 수 있었다. 텅스텐의 경우에는 CVD에 의한 성막이 매립성의 관점으로부터 유리하며, 접착 금속막은 없어도 좋다. 또한, 이 경우에는 텅스텐의 CMP를 행하였다.

또한, 도 7과 같은 이중 상감에 의해 형성된 플러그(41)를 형성하는 것도 가능하였다. 이에 따라 적층 배선의 공정수를 감소시키는 것이 가능해졌다. 이 방법에서도 LSI의 정상적인 동작을 확인하였다.

또한, 실시예 1과 마찬가지로, 도 5, 6, 7, 10 및 11과 같이 적층 배선을 형성하여 LSI를 시작한 결과 거의 마찬가지의 효과가 얻어지고, 또는 LSI의 회로 동작을 조사한 결과 정상적으로 동작하는 것도 확인하였다.

(실시예 5)

본 실시예 5에서 이용한 연마액은 과산화수소수(시판의 30%  $\text{H}_2\text{O}_2$  수용액)와 인산과 BTA와 메탄올과 말론산으로 구성된 수용액이다. 조성은 과산화수소수는 30중량%, 인산은 0.2 중량%, BTA는 0.2 중량%, 메탄올은 1중량%, 말론산은 0.1 중량%이다. 이 연마액을 이용하여, Cu막의 연마 속도와 에칭 속도를 측정하였다. 연마 특성의 평가는 실시예 1과 마찬가지로 행하였다.

그 결과, 연마 속도는 600nm/분이며, 에칭 속도는 1.0nm/분 이하로 억제되어 있고, 디싱 발생의 문제는 없는 것을 알 수 있다. 실시예 1의 연마액과 비교하여, 연마 속도가 50nm/분 빠르고, Cu의 연마면의 원활함이 향상하고 있는 것이 주사 전자 현미경(SEM) 관찰로 알 수 있다.

도 3의 (a)에 도시한 매립 배선을 형성하는 시료를, 상술한 연마액으로 CMP를 행한 결과, 도 3의 (d) 및 (e)와 같이, 디싱이나 침식이 약 50nm 이하로 되는 형상으로 가공할 수가 있었다. 종래의 유기산계 지립 프리 연마액과 비교하여 약 6분의 1의 시간으로 연마가 종료하였다. 박리나 연마상도 발생하지 않았다.

플러그 구조도 도 4의 (d) 및 (e)와 같이, 디싱이나 침식이 약 50nm 이하가 되는 형상으로 가공할 수가 있었다.

형성된 Cu 배선의 전기 저항율을 측정한 결과, TiN층의 부분도 포함시켜  $1.9\mu\Omega\text{cm}$ 의 값을 얻었다. 또한, 사행 배선(배선 폭  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)이나 빗형 배선(배선 간격  $0.3\mu\text{m}$  내지  $3\mu\text{m}$ , 길이 40mm)을 이용하여 도통/절연 시험을 행한 결과, 거의 100%의 수율이 얻어졌다.

도 5, 도 6과 같은 적층 배선 구조를 제작하는 것도 가능하게 되어, LSI의 동작도 정상인 것을 알 수 있었다.

또한, 실시예 1과 마찬가지로, 도 5, 6, 7, 10 및 11과 같이 적층 배선을 형성하여 LSI를 시작한 결과 거의 마찬가지의 효과가 얻어지거나, 또는 LSI의 회로 동작을 조사한 결과, 정상적으로 동작하는 것도 확인하였다.

### 발명의 효과

본 발명의 인산을 포함하는 연마액으로 CMP를 행하는 방법은, 종래의 연마액으로 CMP를 행하는 방법과 비교하여, 스크래치나 박리, 디싱, 침식을 억제하고, 또한 높은 연마 속도로 연마를 행할 수 있다.

### 도면의 간단한 설명

도 1은 CMP 장치의 개략을 나타내는 단면도.

도 2는 CMP 장치의 개략을 나타내는 평면도.

도 3은 CMP 공정을 설명하기 위한 배선 주요부의 구조도.

도 4는 CMP 공정을 설명하기 위한 다른 배선 주요부의 구조도.

도 5는 CMP에 의해서 형성된 배선 주요부의 구조도.

도 6은 CMP에 의해서 형성된 다른 배선 주요부의 구조도.

도 7은 CMP에 의해서 형성된 또 다른 배선 주요부의 구조도.

도 8은 본 발명의 효과를 설명하기 위한 배선 주요부의 구조도.

도 9는 본 발명의 다른 효과를 설명하기 위한 배선 주요부의 구조도.

도 10은 본 발명에 따른 다른 배선을 갖는 전자 회로 장치의 주요부 단면도.

도 11은 본 발명의 또 다른 효과를 설명하기 위한 배선 주요부의 구조도.

〈도면의 주요 부분에 대한 부호의 설명〉

21 : Cu 등의 금속막

21' : 절연층 내에 매립된 금속 배선부 내지 플러그

22 : 배리어 금속막

23 : 1층째의 배선층 부분의  $\text{SiO}_2$ 막

24 : BPSG막

25 : 불순물 도핑층이나 절연막이 형성된 Si 기판

26 : 금속막 표면의 오목부

27 : 금속막 표면의 볼록부

28 : 절연막에 설치된 홈

31 : 2층째의 Cu 배선

35 : 2층째의  $\text{SiO}_2$ 막

39 : 2층째의 배리어 금속막

40 : 플러그

41 : 이중 상감에 의해서 형성된 플러그

42 : 텅스텐

45 : 불순물 도핑층

52 : 1층째의 배선층과 2층째의 배선층 사이의 층간 절연층

도면

도면1

도면2

## 도면3

도면4

도면5

도면6

(b)

도면7

(b)

도면8

도면9

도면10

도면11