# (19) United States

# (12) Patent Application Publication Lim et al.

(10) Pub. No.: US 2015/0287673 A1 Oct. 8, 2015 (43) Pub. Date:

# (54) SEMICONDUCTOR PACKAGE

Applicant: ADVANPACK SOLUTIONS PTE LTD., Singapore (SG)

Inventors: **Shoa-Siong Lim**, Singapore (SG);

Kian-Hock Lim, Singapore (SG)

Appl. No.: 14/731,774

Jun. 5, 2015 (22) Filed:

# Related U.S. Application Data

(62) Division of application No. 13/127,061, filed on May 2, 2011, filed as application No. PCT/SG2009/000408 on Nov. 3, 2009, which is a division of application No. 61/112,207, filed on Nov. 7, 2008.

# **Publication Classification**

(51) **Int. Cl.**

H01L 23/498 (2006.01)H01L 23/31 (2006.01)H01L 23/00 (2006.01)

# (52) U.S. Cl.

CPC .... H01L 23/49861 (2013.01); H01L 23/49827 (2013.01); H01L 24/06 (2013.01); H01L 23/3107 (2013.01); H01L 2924/1532 (2013.01)

#### ABSTRACT (57)

A semiconductor package includes a trace molding compound layer and a chip molding compound layer. The trace molding compound layer has a first surface and a second surface, wherein the trace molding compound layer encapsulates a plurality of traces and studs between the first and second surface. The chip molding compound layer has a first surface and a second surface, wherein the chip molding compound layer encapsulates a semiconductor chip between the first and second surface of the chip molding compound layer. The chip molding compound layer is disposed on the trace molding compound layer, the second surface of the chip molding compound layer adheres to the first surface of the trace molding compound layer, and the chip molding compound layer and the trace molding compound layer comprise substantially the same molding compound material.

FIG. 1(PRIOR ART)

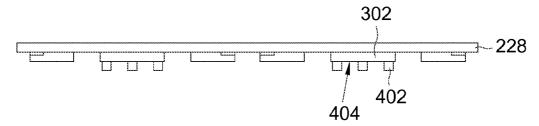

FIG. 9

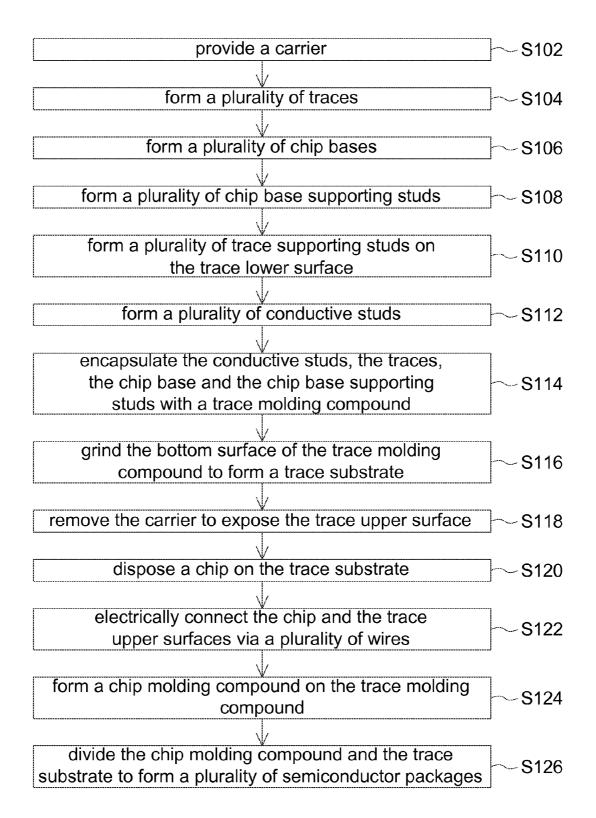

FIG. 10

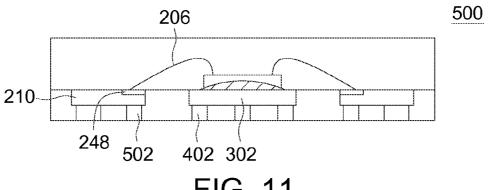

FIG. 11

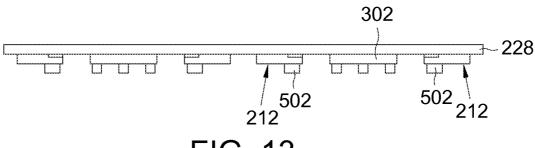

FIG. 12

FIG. 13

FIG. 15

FIG. 16

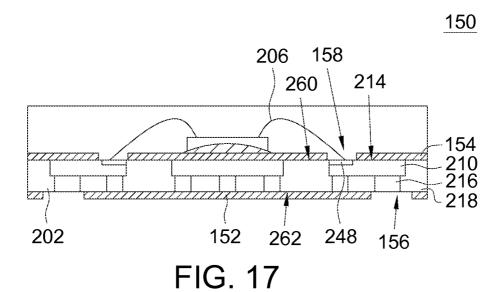

| form a plurality of traces  form a plurality of chip bases  form a plurality of chip base supporting studs  form a plurality of trace supporting studs  form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  form a plurality of conductive studs  supporting a plurality of conductive studs  form a plurality of conductive studs  supporting a plurality of conductive studs  supporting a plurality of conductive studs  form a plurality of trace supporting studs on the trace supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  supporting studs and the trace upper surface  supporting studs and the trace of the trace substrate  \$1816  \$1816  \$1820  \$1820  Gispose a chip on the trace substrate  \$1822  S1824  form a chip molding compound on the trace molding compound  S1826  Givide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                            | _            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------|

| form a plurality of chip bases  form a plurality of chip base supporting studs  form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  form a plurality of conductive studs  supporting studs with a traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  S1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound and the trace divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | provide a carrier                                          | ~S1802       |

| form a plurality of chip bases  form a plurality of chip base supporting studs  form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  form a plurality of conductive studs  supporting studs with a traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  S1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound and the trace divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                            | -            |

| form a plurality of chip base supporting studs  form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  form a plurality of conductive studs  studs, the traces, the chip base, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace upper surface  stage  stag | form a plurality of traces                                 | ~S1804       |

| form a plurality of chip base supporting studs  form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  form a plurality of conductive studs  studs, the traces, the chip base, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace upper surface  stage  stag | \/                                                         |              |

| form a plurality of chip base supporting studs  form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  form a plurality of conductive studs  studs, the traces, the chip base, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace upper surface  stage  stag | form a plurality of chip bases                             | ~S1806       |

| form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  encapsulate the conductive studs, the traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  S1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                            | <u>.</u>     |

| form a plurality of trace supporting studs on the trace lower surface  form a plurality of conductive studs  form a plurality of conductive studs  encapsulate the conductive studs, the traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  S1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | form a plurality of chip base supporting studs             | L S1808      |

| form a plurality of conductive studs  encapsulate the conductive studs, the traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound  grind the bottom surface of the trace molding compound  supporting studs with a trace molding compound  Grind the bottom surface of the trace substrate  supporting studs with a trace molding compound  S1816  Fremove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  S1822  electrically connect the chip and the trace upper surface via a plurality of wires  form a chip molding compound on the trace molding compound  S1826  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ionn a planality of omp bace supporting stade              | ] = 31000    |

| form a plurality of conductive studs  encapsulate the conductive studs, the traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound  grind the bottom surface of the trace molding compound  supporting studs with a trace molding compound  Grind the bottom surface of the trace substrate  supporting studs with a trace molding compound  S1816  Fremove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  S1822  electrically connect the chip and the trace upper surface supper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1826  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | form a plurality of trace supporting stude on              | 1 0.0.0      |

| form a plurality of conductive studs  encapsulate the conductive studs, the traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  electrically connect the chip and the trace upper surface supper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                            | ~S1810       |

| encapsulate the conductive studs, the traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  s1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | \//                                                        | _1           |

| encapsulate the conductive studs, the traces, the chip base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  s1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | form a plurality of conductive studs                       | ~S1812       |

| base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  s1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | , ,                                                        | J 01012      |

| base, the chip base supporting studs and the trace supporting studs with a trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  s1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ancapsulate the conductive stude, the traces, the chip     | 7            |

| grind the bottom surface of the trace molding compound  grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  stage of the trace substrate  stage of the trace substrate  S1820  dispose a chip on the trace substrate  stage of the trace upper surface  S1822  dispose a chip on the trace substrate  stage of the trace upper surface  S1822  dispose a chip on the trace molding compound  S1824  form a chip molding compound on the trace molding compound  S1826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                            | ~ S1914      |

| grind the bottom surface of the trace molding compound to form a trace substrate  remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  S1822  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1826                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                            | 031014       |

| remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  stage of the trace upper surface  dispose a chip on the trace substrate  stage of the trace upper surface   | capporting state than a face moraling compound             |              |

| remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  stage of the trace upper surface  dispose a chip on the trace substrate  stage of the trace upper surface   | grind the bottom surface of the trace molding              | 1            |

| remove the carrier to expose the trace upper surface  form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  stage of the trace substrate  |                                                            | ~S1816       |

| form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  state of the trace substrate  dispose a chip on the trace substrate  state of the trace upper surface  state of the trace upper surface of the trace upper surface  state of the trace upper surface of the trace upper surface upper surface  state of the trace upper surface of the trace upper surface upper surface upper surface  state of the trace upper surface of the trace upper surface upp | \/                                                         | <u>ا</u> ـــ |

| form an insulation layer on the lower surface of the trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  state of the trace substrate  dispose a chip on the trace substrate  state of the trace upper surface  state of the trace upper surface of the trace upper surface  state of the trace upper surface of the trace upper surface upper surface  state of the trace upper surface of the trace upper surface upper surface upper surface  state of the trace upper surface of the trace upper surface upp | remove the carrier to expose the trace upper surface       | ~S1818       |

| trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  sleetrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | \/                                                         | J 01010      |

| trace substrate which exposes the conductive studs, and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  sleetrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | form an insulation layer on the lower surface of the       | 1            |

| and form insulation layer on the upper surface of the trace substrate which exposes the trace upper surface  dispose a chip on the trace substrate  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | · ·                                                        |              |

| dispose a chip on the trace substrate  electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                            | ~S1820       |

| electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1824                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | trace substrate which exposes the trace upper surface      |              |

| electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1824                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\bigvee$                                                  | _            |

| electrically connect the chip and the trace upper surfaces via a plurality of wires  form a chip molding compound on the trace molding compound  S1824  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | dispose a chip on the trace substrate                      | S1822        |

| form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                            | _1           |

| form a chip molding compound on the trace molding compound  divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | electrically connect the chip and the trace                | 04004        |

| divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | upper surfaces via a plurality of wires                    | S1824        |

| divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\bigvee$                                                  |              |

| divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | form a chip molding compound on the trace molding compound | ~S1826       |

| divide the chip molding compound and the trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                            | 1            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | divide the chip molding compound and the trace             | 04000        |

| substrate to form a plurality of semiconductor packages \$1828                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | substrate to form a plurality of semiconductor packages    | <u></u>      |

FIG. 18

FIG. 19

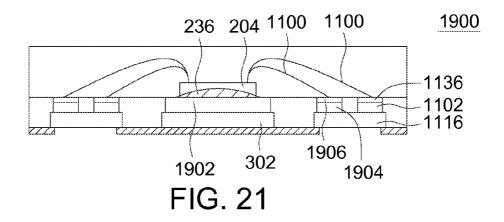

FIG. 20

FIG. 23

FIG. 24

FIG. 25

#### SEMICONDUCTOR PACKAGE

[0001] This is a divisional application of U.S. application Ser. No. 13/127,061, filed May 2, 2011, now in a state of allowability. This application claims the benefit of U.S. provisional application Ser. No. 61/112,207, filed Nov. 7, 2008, and claims the benefit of a Patent Cooperation Treaty application Serial No. PCT/SG2009/000408, filed Nov. 6, 2009, the contents of which are incorporated herein by reference.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

[0003] The invention relates in general to a semiconductor package, and more particularly to a semiconductor package with enhanced routing design flexibility.

[0004] 2. Description of the Related Art

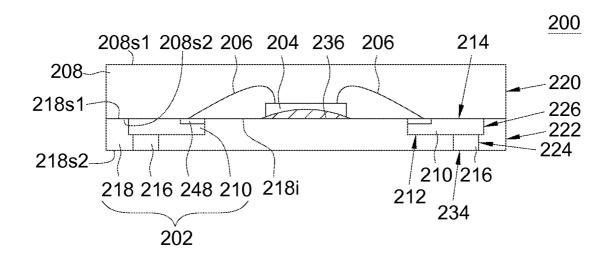

[0005] Referring to FIG. 1, a conventional Quad-Flat Pack (QFN) semiconductor package is shown. The semiconductor package 10 includes a chip 12, a lead frame 14, a plurality of wires 16, a chip base 18, a chip supporting studs 20 and an adhesive 24. The lead frame 14 located on the peripheral of the semiconductor package 10 is exposed from the bottom surface of the semiconductor package 10 to be used as an I/O contact of the semiconductor package 10. The chip 12 is disposed on the chip base 18. The chip base supporting stud 20 supports the chip base 18 to enhance the structural strength of the semiconductor package 10.

[0006] However, the wires 16, extended around the semi-conductor package 10, are too long and exposed to the risk of short-circuiting. Besides, the lead frame 14, being used as an I/O contact, can only be disposed on the peripheral of the semiconductor package 10, hence limiting the number of the I/O contacts of the semiconductor package 10. Consequently, increasing the number of I/O contacts substantially increases the size of the semiconductor package. Moreover, the lead frame 14 being used as an I/O contact is exposed in the air, and is susceptible to the erosion by the environment.

# SUMMARY OF THE INVENTION

[0007] The invention is directed to a semiconductor package and a method for manufacturing the semiconductor package and a trace substrate and a method for manufacturing the trace substrate. The semiconductor package includes a plurality of trace pads, a plurality of wires, a plurality of conductive studs and a molding compound. The trace pads can be disposed near the chip, so that the wire connects the chip and the trace pad via a shortest distance to reduce the risk of wire-crossing and short-circuiting. Besides, the trace pads of the semiconductor package are not limited to be disposed on the peripheral of the semiconductor package, so the number of the I/O contacts of the semiconductor package can be greatly increased. Moreover, the trace pads and the conductive studs are protected inside the molding compound, and will not be eroded easily.

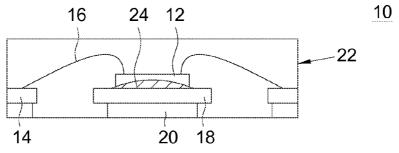

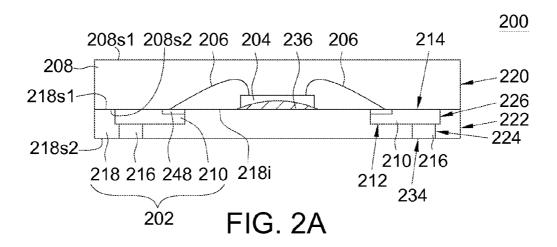

[0008] According to a first aspect of the present invention, a semiconductor package is provided. The semiconductor package includes a trace substrate, a chip, a plurality of wires and a chip molding compound. The trace substrate includes a plurality of traces, a plurality of conductive studs, a plurality of traces pads and a trace molding compound. The trace pads are disposed on the trace. The conductive studs correspondingly are formed on the traces, the trace pads and their corresponding conductive studs are separated by a distance and arranged along an extending direction of the trace. The trace

molding compound encapsulates the conductive studs and the trace, and exposes a conductive stud surface of each conductive stud and a trace surface of each trace. The chip is disposed on the surface of the trace substrate which exposes the trace upper surface. The wires electrically connect the chip and the trace pads. The chip molding compound is disposed on the trace substrate. The chip molding compound encapsulates the chip and the wire.

[0009] According to a second aspect of the present invention, a trace substrate is provided. The trace substrate is for disposing a chip. The trace substrate includes a plurality of traces, a plurality of conductive studs, a plurality of traces pads and a trace molding compound. The conductive studs correspondingly are formed on the traces. The trace pads are correspondingly disposed on the traces, wherein the trace pads and their corresponding conductive studs are separated by a distance along an extending direction of the traces. The trace molding compound encapsulates the conductive studs and the traces, and exposes a conductive stud surface of each conductive stud and a trace surface of each trace.

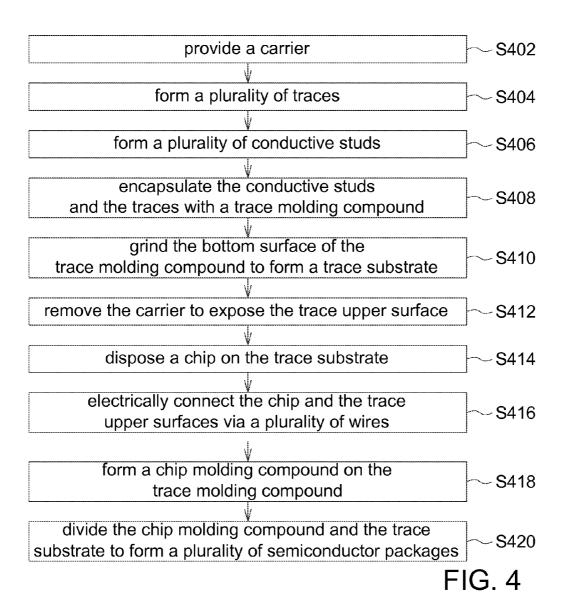

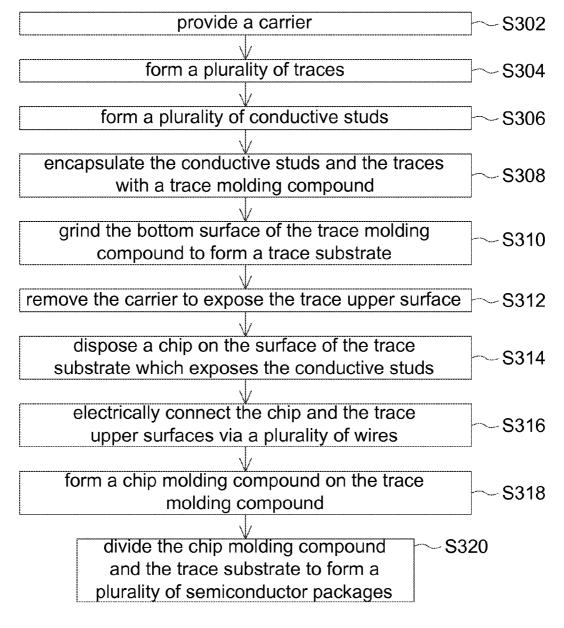

[0010] According to a third aspect of the present invention, a method for manufacturing semiconductor package is provided. The manufacturing method includes the following steps. A carrier is provided. A plurality of traces is formed on a lower surface of the carrier. A plurality of traces pads is formed on the traces. A plurality of conductive studs is formed on the trace, wherein the trace pads and their corresponding conductive studs are separated by a distance along an extending direction of the trace. The conductive studs and the traces are encapsulated by a trace molding compound. The bottom surface of the trace molding compound is grinded to expose a conductive stud surface of each conductive stud. The carrier is removed to expose a trace surface of each trace so that conductive studs, the trace and the trace molding compound together form a trace substrate. A chip is disposed on the surface of the trace substrate which exposes the trace upper surface. The chip and the trace upper surface are electrically connected by a plurality of wires. A chip molding compound is formed on the trace substrate, wherein the chip molding compound encapsulates the chip and the wire.

[0011] According to a fourth aspect of the present invention, a method for manufacturing trace substrate is provided. The manufacturing method includes the following steps. A carrier is provided. A plurality of traces is formed on a lower surface of the carrier. A plurality of conductive studs is formed on the traces. A plurality of traces pads is formed on the trace, wherein the trace pads and their corresponding conductive studs are separated by a distance along an extending direction of the trace. The conductive studs and the trace are encapsulated by a trace molding compound. The bottom surface of the trace molding compound is grinded to expose a conductive stud surface of each conductive stud. The carrier is removed to expose a trace surface of each trace.

[0012] The invention will become apparent from the following detailed description of the preferred but non-limiting embodiments. The following description is made with reference to the accompanying drawings.

### BRIEF DESCRIPTION OF THE DRAWINGS

[0013] FIG. 1 shows a generally known semiconductor package;

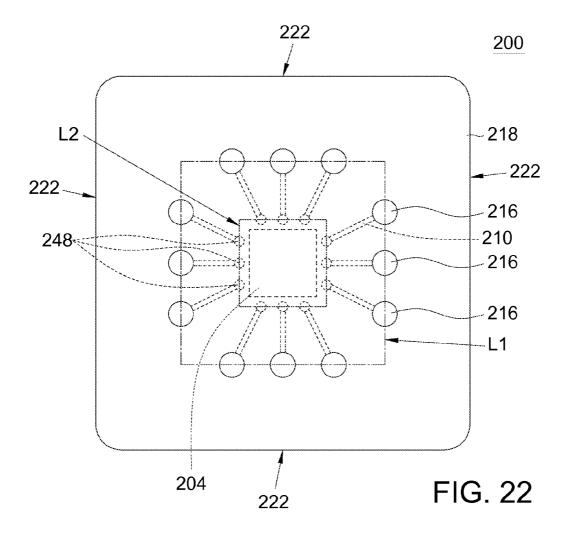

[0014] FIG. 2A shows a semiconductor package according to a first embodiment of the invention;

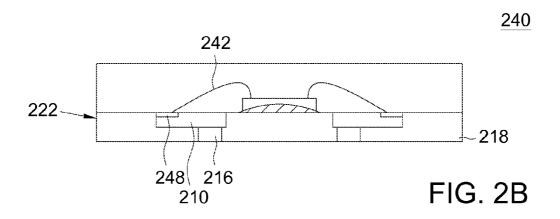

[0015] FIG. 2B shows a semiconductor package according to another embodiment of the invention;

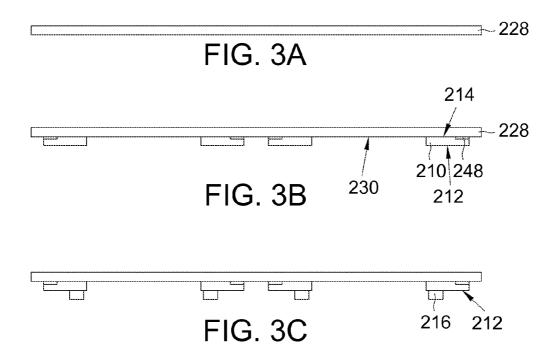

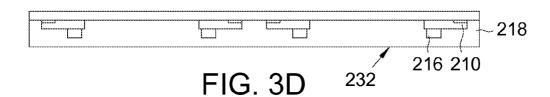

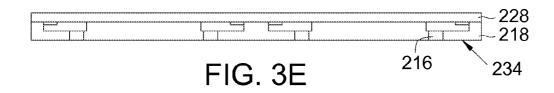

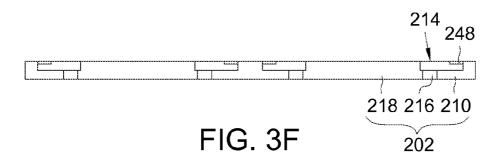

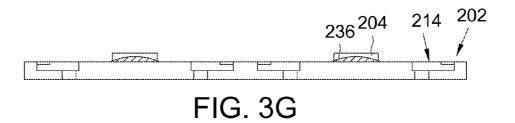

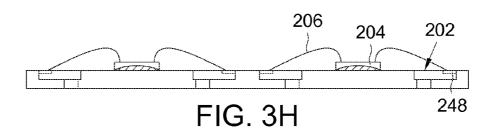

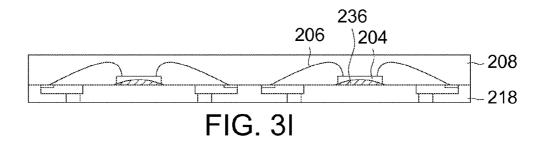

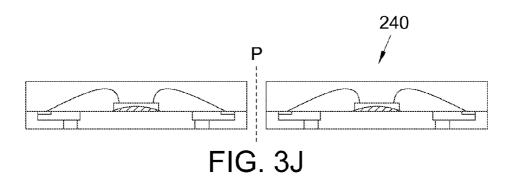

[0016] FIGS. 3A-3J show processes for manufacturing the semiconductor package of FIG. 2A;

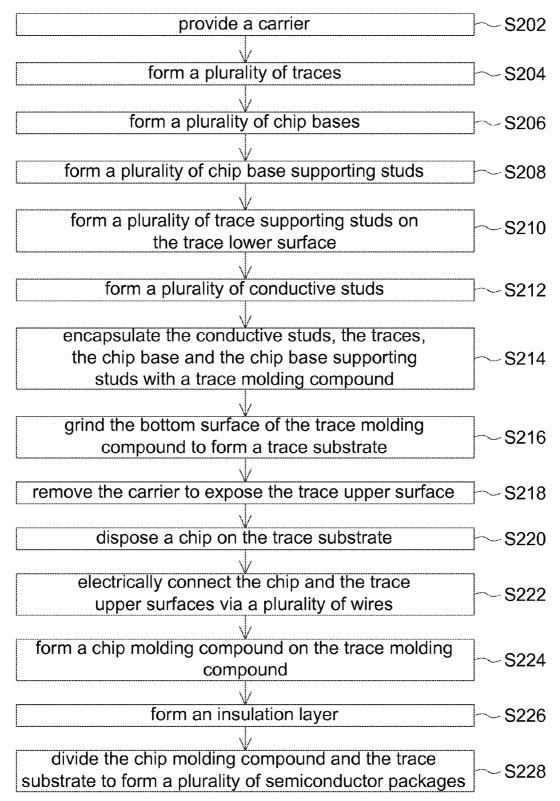

[0017] FIG. 4 shows a method flowchart for manufacturing semiconductor package according to a first embodiment of the invention;

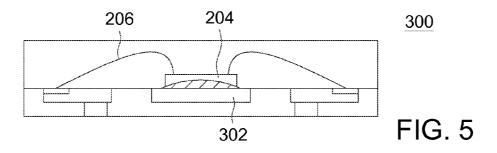

[0018] FIG. 5 shows a semiconductor package according to a second embodiment of the invention;

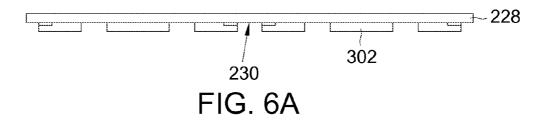

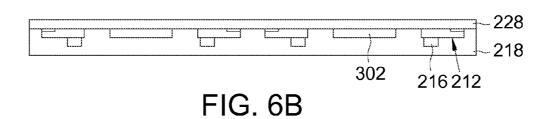

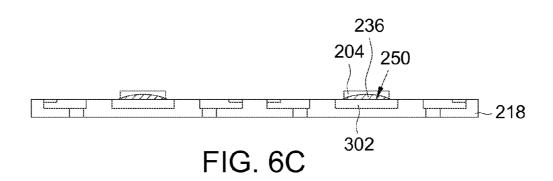

[0019] FIGS. 6A-6C show processes for manufacturing the semiconductor package of FIG. 5;

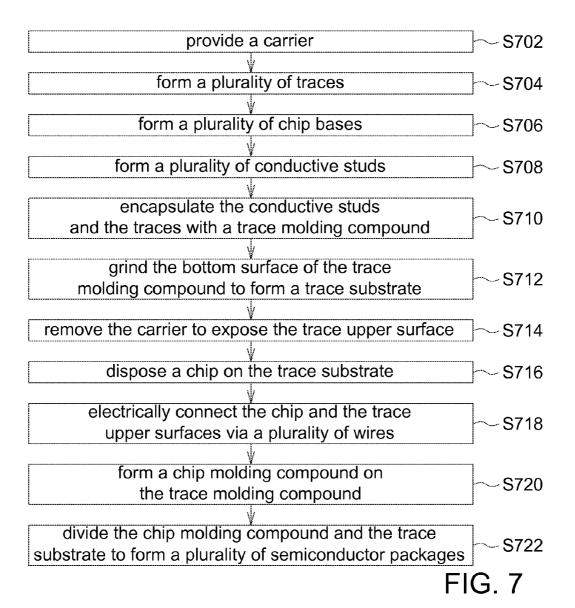

[0020] FIG. 7 shows a method flowchart for manufacturing semiconductor package according to a second embodiment of the invention;

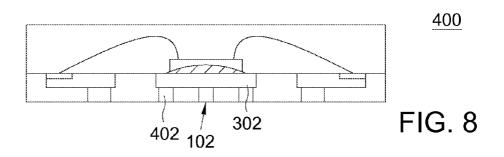

[0021] FIG. 8 shows a semiconductor package according to a third embodiment of the invention;

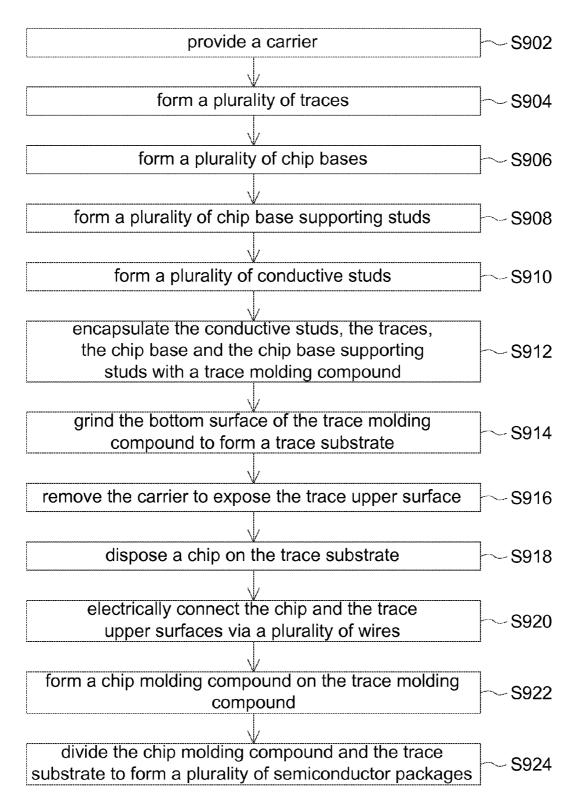

[0022] FIG. 9 shows a method flowchart for manufacturing semiconductor package according to a third embodiment of the invention;

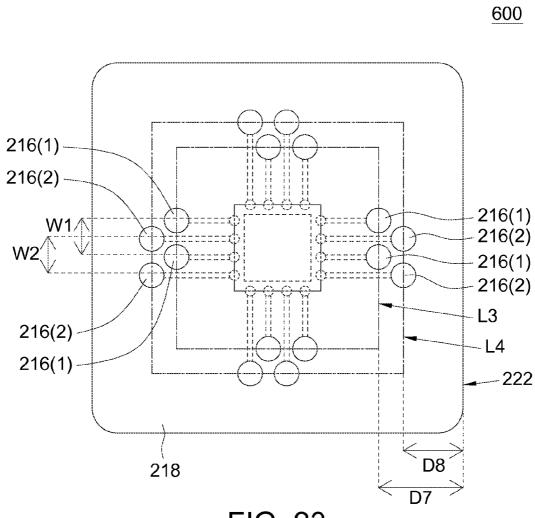

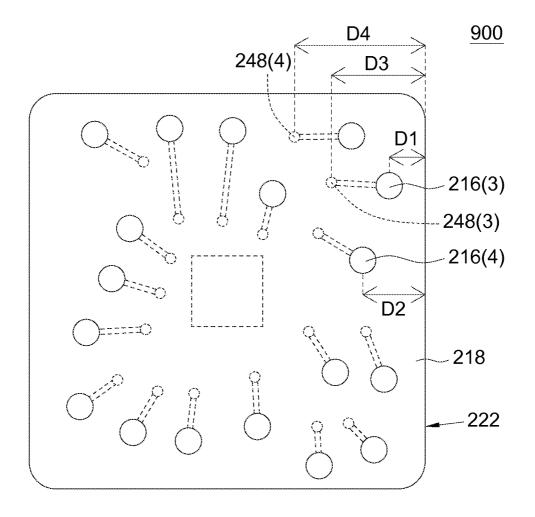

[0023] FIG. 10 shows a semiconductor package of the third embodiment with a chip base supporting stud;

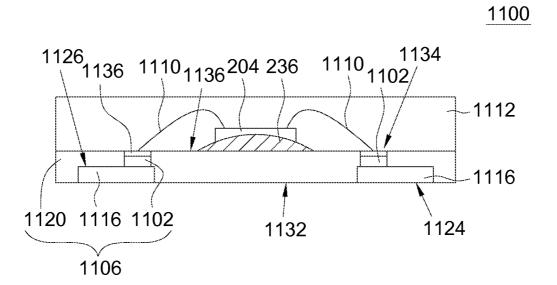

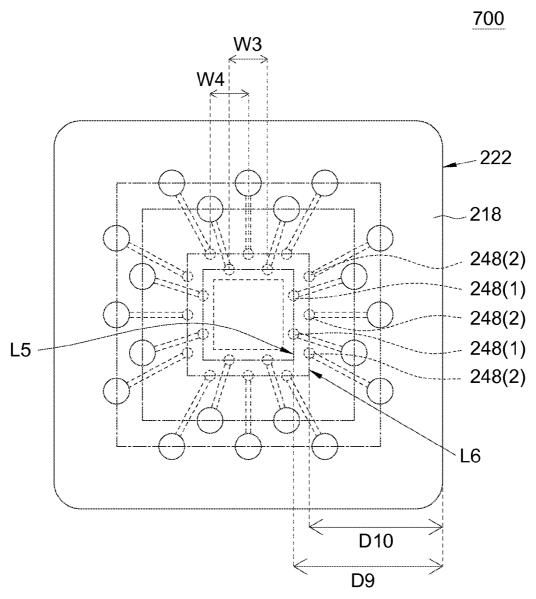

[0024] FIG. 11 shows a semiconductor package according to a fourth embodiment of the invention;

[0025] FIG. 12 shows a method flowchart for manufacturing semiconductor package according to a fourth embodiment of the invention;

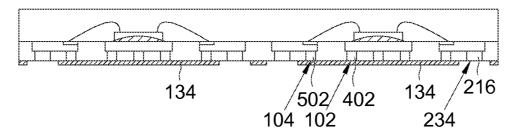

[0026] FIG. 13 shows a semiconductor package of the present embodiment of the invention with a plurality of trace supporting studs;

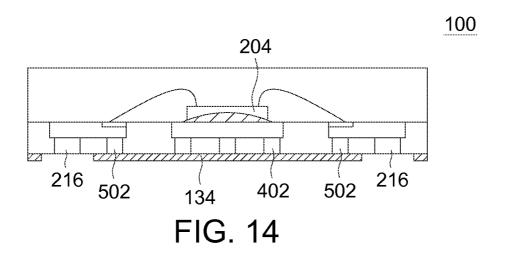

[0027] FIG. 14 shows a semiconductor package according to a fifth embodiment of the invention;