(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2016-510461

(P2016-510461A)

(43) 公表日 平成28年4月7日(2016.4.7)

|                      |            |             |

|----------------------|------------|-------------|

| (51) Int.Cl.         | F 1        | テーマコード (参考) |

| GO6F 9/315 (2006.01) | GO6F 9/30  | 340D 5B033  |

| GO6F 17/16 (2006.01) | GO6F 17/16 | D 5B056     |

|                      | GO6F 17/16 | E           |

審査請求 未請求 予備審査請求 未請求 (全 49 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2015-553179 (P2015-553179) |

| (86) (22) 出願日 | 平成25年11月21日 (2013.11.21)     |

| (85) 翻訳文提出日   | 平成27年6月24日 (2015.6.24)       |

| (86) 國際出願番号   | PCT/IB2013/060309            |

| (87) 國際公開番号   | W02014/114997                |

| (87) 國際公開日    | 平成26年7月31日 (2014.7.31)       |

| (31) 優先権主張番号  | 13/748,543                   |

| (32) 優先日      | 平成25年1月23日 (2013.1.23)       |

| (33) 優先権主張国   | 米国(US)                       |

|          |                                                                                                                                                                                                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (71) 出願人 | 390009531<br>インターナショナル・ビジネス・マシーンズ・コーポレーション<br>INTERNATIONAL BUSINESS MACHINES CORPORATION<br>アメリカ合衆国10504 ニューヨーク<br>州 アーモンク ニュー オーチャード<br>ロード<br>New Orchard Road, Armonk, New York 10504, United States of America |

| (74) 代理人 | 100108501<br>弁理士 上野 剛史                                                                                                                                                                                              |

最終頁に続く

(54) 【発明の名称】 VECTORELEMENT ROTATE AND INSERT UNDER MASK 命令を処理するためのコンピュータ・プログラム、コンピュータ・システム及び方法

## (57) 【要約】

【課題】 中央演算処理ユニットにおいてマシン命令を実行するためのコンピュータ・プログラム、コンピュータ・システム及び方法を提供する。

【解決手段】 Vector Element Rotate and Insert Under Mask 命令である。命令の第2のオペランドの各要素が、指定されたビット数だけ指定された方向にローテートされる。1に設定された命令の第3のオペランド内の各ビットについて、第2のオペランド内のローテートされた要素の対応するビットが、命令の第1のオペランド内の対応するビットに置き換わる。

【選択図】 図20

FIG. 8B

**【特許請求の範囲】****【請求項 1】**

中央演算処理ユニットにおいてマシン命令を実行するためのコンピュータ・プログラムであって、前記コンピュータ・プログラムは、方法を実施するための命令を含み、

前記方法は、

プロセッサにより、実行のためのマシン命令を取得することであって、前記マシン命令は、コンピュータ・アーキテクチャに従ったコンピュータ実行のために定められ、

Vector Element Rotate And Insert Under Mask 操作を識別するオペコードを与えるための少なくとも 1 つのオペコード・フィールドと、

第 1 のオペラントを含む第 1 のレジスタを指定するのに用いられる第 1 のレジスタ・フィールドと、

第 2 のオペラントを含む第 2 のレジスタを指定するのに用いられる第 2 のレジスタ・フィールドと、

第 3 のオペラントを含む第 3 のレジスタを指定するのに用いられる第 3 のレジスタ・フィールドと、

を含む、取得することと、

前記マシン命令を実行することと、

を含み、

前記実行することは、

前記第 2 のオペラントの 1 つ又は複数の要素を、指定されたローテート量だけ選択された方向にローテートさせることと、

特定の値を有する 1 つ又は複数のデータ単位に関して前記第 3 のオペラントをチェックすることと、

前記特定の値をもつ前記 1 つ又は複数のデータ単位を有する前記第 3 のオペラントに基づいて、前記第 1 のオペラント内の対応するデータ単位の 1 つ又は複数の値を、ローテートされた前記第 2 のオペラント内の対応するデータ単位の 1 つ又は複数の値に置き換えることと、

を含む、コンピュータ・プログラム。

**【請求項 2】**

前記選択された方向は左方向を含み、前記指定されたローテート量は指定されたビット数を含む、請求項 1 に記載のコンピュータ・プログラム。

**【請求項 3】**

前記ローテートさせることは、前記第 2 のオペラントの各要素を前記指定されたビット数だけ左ヘローテートさせることを含み、要素の左端ビット位置から外にシフトされた各ビットは、前記要素の右端ビット位置に再び入る、請求項 2 に記載のコンピュータ・プログラム。

**【請求項 4】**

前記第 3 のオペラントは複数の要素を含み、前記複数の要素は複数のマスクを含み、前記複数のマスクのうちの 1 つのマスクは複数のビットを含む、請求項 1 に記載のコンピュータ・プログラム。

**【請求項 5】**

前記 1 つ又は複数のデータ単位は 1 つ又は複数のビットを含み、前記特定の値は 1 を含み、前記置き換えることは、1 に設定された前記第 3 のオペラント内の各ビットについて、前記第 1 のオペラント内の対応するビットの値を、ローテートされた前記第 2 のオペラント内の対応するビットの値に置き換えることを含む、請求項 4 に記載のコンピュータ・プログラム。

**【請求項 6】**

前記第 2 のオペラントは複数の要素を含み、前記指定されたローテート量は、前記マシン命令の第 4 のオペラント内に含まれ、前記第 4 のオペラントは、前記第 2 のオペラント

10

20

30

40

50

の各要素をローテートするためのビット数を指定する符号なし2進整数を含み、

前記方法は、

前記符号なし2進整数が選択されたオペランドの要素のビット数より大きいかどうか

を判断することと、

前記符号なし2進整数が前記選択されたオペランドの前記要素の前記ビット数より大

きいことに基づいて、前記符号なし2進整数を法として前記選択されたオペランドの前記

要素の前記ビット数だけ減らすことをさらに含む、請求項1に記載のコンピュータ・プロ

グラム。

#### 【請求項7】

前記方法は、前記マシン命令のマスク・フィールドを用いて、前記選択されたオペラン

ドの前記要素の前記ビット数を求めるることをさらに含み、前記マスク・フィールドは、前

記マシン命令の1つ又は複数のオペランドの要素のサイズを示すための要素サイズ制御を

含む、請求項6に記載のコンピュータ・プログラム。 10

#### 【請求項8】

前記マシン命令は、1つ又は複数のレジスタを指定するのに用いられる拡張フィールド

をさらに含み、前記第1のレジスタ・フィールドと前記拡張フィールドの第1の部分とが

組み合わされて前記第1のレジスタが指定され、前記第2のレジスタ・フィールドと前記

拡張フィールドの第2の部分とが組み合わされて前記第2のレジスタが指定され、前記第

3のレジスタ・フィールドと前記拡張フィールドの第3の部分とが組み合わされて前記第

3のレジスタが指定される、請求項1に記載のコンピュータ・プログラム。 20

#### 【請求項9】

前記第2のオペランドは1つ又は複数の第2のオペランド要素を含み、前記選択された

方向は左方向であり、前記データ単位はビットを含み、前記指定されたローテート量は指

定されたビット数を含み、前記第3のオペランドは1つ又は複数の第3のオペランド要素

を含み、各々の第3のオペランド要素は複数のビットを有するマスクを含み、

前記ローテートさせることは、前記第2のオペランドの各要素を前記指定されたビット

数だけ左ヘローテートさせることを含み、要素の左端ビット位置から外にシフトされた各

ビットは、前記要素の右端ビット位置に再び入り、

前記置き換えることは、1に設定された前記第3のオペランド内の各ビットについて、

前記第1のオペランド内の対応するビットの値を、ローテートされた前記第2のオペラン

ドの対応するビットの値に置き換えることを含む、請求項1に記載のコンピュータ・プロ

グラム。 30

#### 【請求項10】

前記マシン命令はマスク・フィールドをさらに含み、前記マスク・フィールドは、前記

第1のオペランド、前記第2のオペランド及び前記第3のオペランドのうちの1つ又は複

数の要素のサイズを示すための要素サイズ制御を含む、請求項1に記載のコンピュータ・

プログラム。

#### 【請求項11】

中央演算処理ユニットにおいてマシン命令を実行するためのコンピュータ・システムで

あって、前記コンピュータ・システムは、 40

メモリと、

前記メモリと通信を行うプロセッサと、

を含み、方法を実施するように構成され、

前記方法は、

プロセッサにより、実行のためのマシン命令を取得することであって、前記マシン命令

は、コンピュータ・アーキテクチャに従ったコンピュータ実行のために定められ、

Vector Element Rotate And Insert Under

Mask 操作を識別するオペコードを与えるための少なくとも1つのオペコード・フィ

ールドと、

第1のオペランドを含む第1のレジスタを指定するのに用いられる第1のレジスタ・

フィールドと、

第2のオペランドを含む第2のレジスタを指定するのに用いられる第2のレジスタ・フィールドと、

第3のオペランドを含む第3のレジスタを指定するのに用いられる第3のレジスタ・フィールドと、

を含む、取得することと、

前記マシン命令を実行することと、

を含み、

前記実行することは、

前記第2のオペランドの1つ又は複数の要素を、指定されたローテート量だけ選択された方向にローテートさせることと、

特定の値を有する1つ又は複数のデータ単位に関して前記第3のオペランドをチェックすることと、

前記特定の値をもつ前記1つ又は複数のデータ単位を有する前記第3のオペランドに基づいて、前記第1のオペランド内の対応するデータ単位の1つ又は複数の値を、ローテートされた前記第2のオペランド内の対応するデータ単位の1つ又は複数の値に置き換えることと、

を含む、コンピュータ・システム。

#### 【請求項12】

前記選択された方向は左方向を含み、前記指定されたローテート量は指定されたビット数を含み、前記ローテートさせることは、前記第2のオペランドの各要素を前記指定されたビット数だけ左ヘローテートさせることを含み、要素の左端ビット位置から外にシフトされた各ビットは、前記要素の右端ビット位置に再び入る、請求項11に記載のコンピュータ・システム。

#### 【請求項13】

前記第3のオペランドは複数の要素を含み、前記複数の要素は複数のマスクを含み、前記複数のマスクのうちの1つのマスクは複数のビットを含み、前記1つ又は複数のデータ単位は1つ又は複数のビットを含み、前記特定の値は1を含み、前記置き換えることは、1に設定された前記第3のオペランド内の各ビットについて、前記第1のオペランド内の対応するビットの値を、ローテートされた前記第2のオペランド内の対応するビットの値に置き換えることを含む、請求項11に記載のコンピュータ・システム。

#### 【請求項14】

前記第2のオペランドは複数の要素を含み、前記指定されたローテート量は、前記マシン命令の第4のオペランド内に含まれ、前記第4のオペランドは、前記第2のオペランドの各要素をローテートするためのビット数を指定する符号なし2進整数を含み、

前記方法は、

前記符号なし2進整数が選択されたオペランドの要素のビット数より大きいかどうかを判断することと、

前記符号なし2進整数が前記選択されたオペランドの前記要素の前記ビット数より大きいことに基づいて、前記符号なし2進整数を法として前記選択されたオペランドの前記要素の前記ビット数だけ減らすことをさらに含む、請求項11に記載のコンピュータ・システム。

#### 【請求項15】

前記マシン命令は、1つ又は複数のレジスタを指定するのに用いられる拡張フィールドをさらに含み、前記第1のレジスタ・フィールドと前記拡張フィールドの第1の部分とが組み合わされて前記第1のレジスタが指定され、前記第2のレジスタ・フィールドと前記拡張フィールドの第2の部分とが組み合わされて前記第2のレジスタが指定され、前記第3のレジスタ・フィールドと前記拡張フィールドの第3の部分とが組み合わされて前記第3のレジスタが指定される、請求項11に記載のコンピュータ・システム。

#### 【請求項16】

10

20

30

40

50

前記第2のオペランドは1つ又は複数の第2のオペランド要素を含み、前記選択された方向は左方向であり、前記データ単位はビットを含み、前記指定されたローテート量は指定されたビット数を含み、前記第3のオペランドは1つ又は複数の第3のオペランド要素を含み、各々の第3のオペランド要素は複数のビットを有するマスクを含み、

前記ローテートさせることは、前記第2のオペランドの各要素を前記指定されたビット数だけ左ヘローテートさせることを含み、要素の左端ビット位置から外にシフトされた各ビットは、前記要素の右端ビット位置に再び入り、

前記置き換えることは、1に設定された前記第3のオペランド内の各ビットについて、前記第1のオペランド内の対応するビットの値を、ローテートされた前記第2のオペランドの前記対応するビットの値に置き換えることを含む、請求項11に記載のコンピュータ・システム。 10

#### 【請求項17】

前記マシン命令はマスク・フィールドをさらに含み、前記マスク・フィールドは、前記第1のオペランド、前記第2のオペランド及び前記第3のオペランドの要素のサイズを示すための要素サイズ制御を含む、請求項11に記載のコンピュータ・システム。

#### 【請求項18】

中央演算処理ユニットにおいてマシン命令を実行する方法であって、

プロセッサにより、実行のためのマシン命令を取得することであって、前記マシン命令は、コンピュータ・アーキテクチャに従ったコンピュータ実行のために定められ、

Vector Element Rotate And Insert Under Mask 操作を識別するオペコードを与えるための少なくとも1つのオペコード・フィールドと、 20

第1のオペランドを含む第1のレジスタを指定するのに用いられる第1のレジスタ・フィールドと、

第2のオペランドを含む第2のレジスタを指定するのに用いられる第2のレジスタ・フィールドと、

第3のオペランドを含む第3のレジスタを指定するのに用いられる第3のレジスタ・フィールドと、

を含む、取得することと、

前記マシン命令を実行することと、 30

を含み、

前記実行することは、

前記第2のオペランドの1つ又は複数の要素を、指定されたローテート量だけ選択された方向にローテートさせることと、

特定の値を有する1つ又は複数のデータ単位に関して前記第3のオペランドをチェックすることと、

前記特定の値をもつ前記1つ又は複数のデータ単位を有する前記第3のオペランドに基づいて、前記第1のオペランド内の対応するデータ単位の1つ又は複数の値を、ローテートされた前記第2のオペランド内の対応するデータ単位の1つ又は複数の値に置き換えることと、 40

を含む、方法。

#### 【請求項19】

前記第2のオペランドは1つ又は複数の第2のオペランド要素を含み、前記選択された方向は左方向であり、前記データ単位はビットを含み、前記指定されたローテート量は指定されたビット数を含み、前記第3のオペランドは1つ又は複数の第3のオペランド要素を含み、各々の第3のオペランド要素は複数のビットを有するマスクを含み、

前記ローテートさせることは、前記第2のオペランドの各要素を前記指定されたビット数だけ左ヘローテートさせることを含み、要素の左端ビット位置から外にシフトされた各ビットは、前記要素の右端ビット位置に再び入り、

前記置き換えることは、1に設定された前記第3のオペランド内の各ビットについて、 50

前記第1のオペランド内の対応するビットの値を、ローテートされた前記第2のオペランド内の対応するビットの値に置き換えることを含む、請求項18に記載の方法。

【請求項20】

前記マシン命令はマスク・フィールドをさらに含み、前記マスク・フィールドは、前記第1のオペランド、前記第2のオペランド及び前記第3のオペランドの要素のサイズを示すための要素サイズ制御を含む、請求項18に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

1つ又は複数の態様は、一般に、コンピューティング環境内での処理に関し、特定的に

10 は、こうした環境内でのベクトル処理に関する。

【背景技術】

【0002】

コンピューティング環境内での処理は、1つ又は複数の中央演算処理ユニット(CPU)の動作を制御することを含む。通常、中央演算処理ユニットの動作は、ストレージ内の命令によって制御される。命令は、異なる形式を有し、多くの場合、種々の動作の実施に用いられるレジスタを指定することができる。

【0003】

中央演算処理ユニットのアーキテクチャによって、例えば、例を挙げると汎用レジスタ、専用レジスタ、浮動小数点レジスタ、及び/又はベクトル・レジスタを含む種々のタイプのレジスタを使用することができる。異なるタイプのレジスタを、異なるタイプの命令と共に使用することができる。例として、浮動小数点レジスタは、浮動小数点命令により用いられる浮動小数点数を格納し、ベクトル・レジスタは、ベクトル命令を含む、Single Instruction、Multiple Data(SIMD)命令によって実施されるベクトル処理のためのデータを保持する。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】米国特許第5,551,013号明細書

【特許文献2】米国特許第6,009,261号明細書

【特許文献3】米国特許第5,574,873号明細書

【特許文献4】米国特許第6,308,255号明細書

【特許文献5】米国特許第6,463,582号明細書

【特許文献6】米国特許第5,790,825号明細書

【非特許文献】

【0005】

【非特許文献1】IBM(登録商標)、「z/Architecture Principles of Operations」、IBM(登録商標)出版番号SA22-7832-09、第10版、2012年9月

【非特許文献2】インターナショナル・ビジネス・マシーンズ・コーポレーション、「Power ISA(商標) Version 2.06 改定B」、2010年7月23日

【非特許文献3】「Intel(登録商標) 64 and IA-32 Architectures Developer's Manual: Vol. 2B, Instructions Set Reference, A-L」、注文番号253666-045US、2013年1月

【非特許文献4】「Intel(登録商標) 64 and IA-32 Architectures Developer's Manual: Vol. 2B, Instructions Set Reference, M-Z」、注文番号253667-045US、2013年1月

10

20

30

40

50

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

中央演算処理ユニットにおいてマシン命令を実行するためのコンピュータ・プログラム、コンピュータ・システム及び方法を提供する。

**【課題を解決するための手段】****【0007】**

マシン命令を実行するためのコンピュータ・プログラム製品を提供することにより、従来技術の欠点が克服され、利点がもたらされる。このコンピュータ・プログラム製品は、処理回路により読み出し可能であり、且つ、方法を実施するための、処理回路による実行される命令を格納するコンピュータ可読ストレージ媒体を含む。この方法は、例えば、プロセッサにより、実行のためのマシン命令を取得することであって、マシン命令は、コンピュータ・アーキテクチャに従ったコンピュータ実行のために定められ、且つ、Vector Element Rotate And Insert Under Mask 操作を識別するオペコードを与えるための少なくとも1つのオペコード・フィールドと、第1のオペランドを含む第1のレジスタを指定するのに用いられる第1のレジスタ・フィールドと、第2のオペランドを含む第2のレジスタを指定するのに用いられる第2のレジスタ・フィールドと、第3のオペランドを含む第3のレジスタを指定するのに用いられる第3のレジスタ・フィールドとを含む、取得することと、マシン命令を実行することとを含み、実行することは、第2のオペランドの1つ又は複数の要素を、指定されたローテート量だけ選択された方向にローテートさせることと、特定の値を有する1つ又は複数のデータ単位について第3のオペランドをチェックすることと、特定の値をもつ1つ又は複数のデータ単位を有する第3のオペランドに基づいて、第1のオペランド内の対応するデータ単位の1つ又は複数の値を、ローテートされた第2のオペランド内の対応するデータ単位の1つ又は複数の値に置き換えることと、を含む。

10

**【0008】**

1つ又は複数の態様に関する方法及びシステムも、本明細書で説明され、特許請求される。さらに、1つ又は複数の態様に関するサービスも、本明細書で説明され、特許請求され得る。

20

1つ又は複数の態様の技術を通じて、付加的な特徴及び利点が実現される。他の実施形態及び態様は、本明細書で詳細に説明され、特許請求の範囲の一部と見なされる。

30

**【0009】**

1つ又は複数の態様が、本明細書の最後にある特許請求の範囲において、例として具体的に示され、明確に特許請求されている。上記及び他の目的、特徴、並びに利点は、添付図面と関連して用いられる以下の詳細な説明から明らかである。

**【図面の簡単な説明】****【0010】**

【図1】1つ又は複数の態様を組み込み、用いるためのコンピューティング環境の一例を示す。

40

【図2】1つ又は複数の態様を組み込み、用いるためのコンピューティング環境の別の例を示す。

**【図3】図2のメモリの更なる詳細を示す。****【図4】レジスタ・ファイルの一例を示す。**

【図5】Vector Floating Point Test Data Class Immediate 命令の形式の一例を示す。

40

【図6】図5のVector Floating Point Test Data Class Immediate 命令の第3のオペランドのビット値の一例を示す。

【図7】図5のVector Floating Point Test Data Class Immediate 命令と関連付けられた論理の一実施形態を示す。

**【図8】図5のVector Floating Point Test Data C**

50

lass Immediate 命令の実行のブロック図の一例を示す。

【図 9】2進浮動小数点データの種々のクラスの定義の一例を示す。

【図 10】Vector Checksum 命令の形式の一例を示す。

【図 11】図 10 の Vector Checksum 命令と関連付けられた論理の一実施形態を示す。

【図 12】図 10 の Vector Checksum 命令の実行のブロック図の一例を示す。

【図 13】Vector Galois Field Multiply Sum and Accumulate 命令の形式の一例を示す。

【図 14】図 13 の Vector Galois Field Multiply Sum and Accumulate 命令と関連付けられた論理の一実施形態を示す 10

【図 15】図 13 の Vector Galois Field Multiply Sum and Accumulate 命令の実行のブロック図の一例を示す。

【図 16】Vector Generate Mask 命令の形式の一例を示す。

【図 17】図 16 の Vector Generate Mask 命令と関連付けられた論理の一実施形態を示す。

【図 18】図 16 の Vector Generate Mask 命令の実行のブロック図の一例を示す。

【図 19】Vector Element Rotate and Insert Under Mask 命令の形式の一例を示す。 20

【図 20】図 19 の Vector Element Rotate and Insert Under Mask 命令と関連付けられた論理の一実施形態を示す

【図 21】図 19 の Vector Element Rotate and Insert Under Mask 命令の実行のブロック図の一例を示す。

【図 22】ベクトル例外コード (Vector Exception Code) の一例を示す。

【図 23】図 22 のベクトル例外コードを設定するための論理の一実施形態を示す。

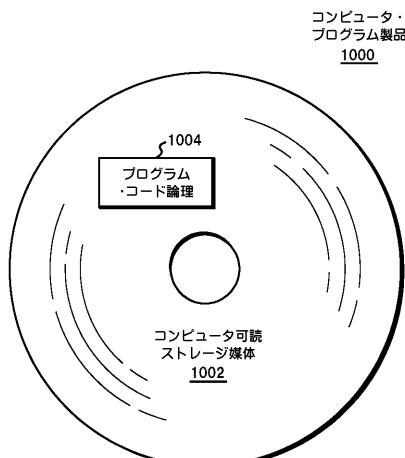

【図 24】1つ又は複数の態様を組み込むコンピュータ・プログラム製品の一実施形態を示す。

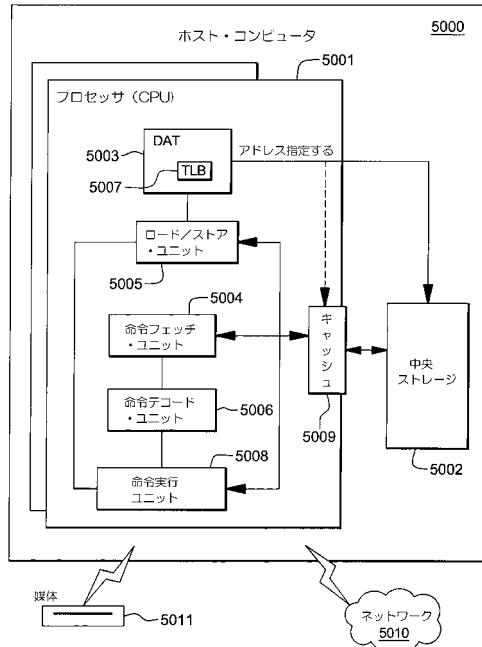

【図 25】ホスト・コンピュータ・システムの一実施形態を示す。 30

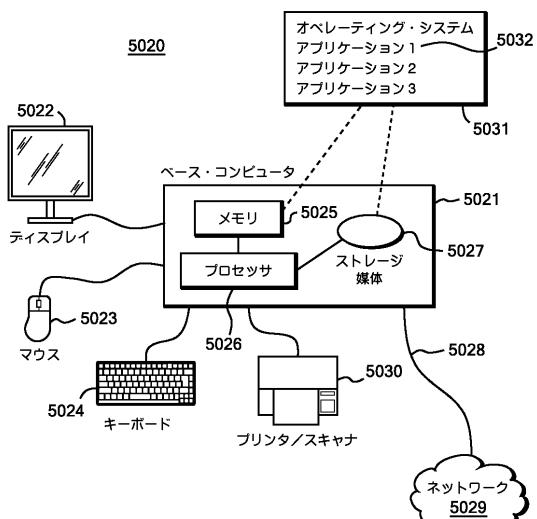

【図 26】コンピュータ・システムの更に別の例を示す。

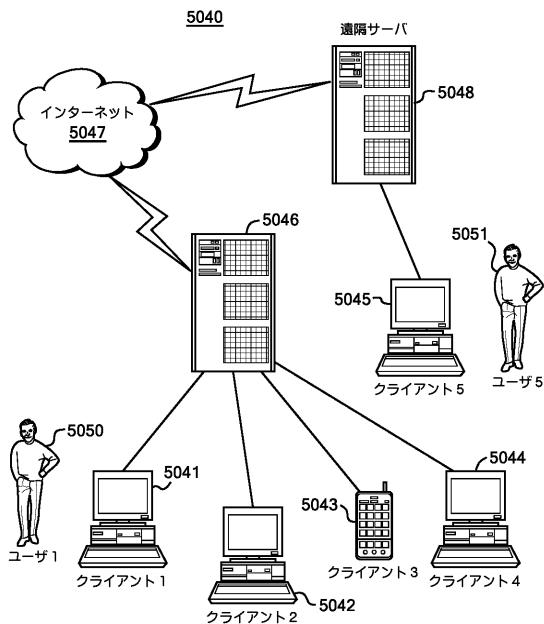

【図 27】コンピュータ・ネットワークを含むコンピュータ・システムの別の例を示す。

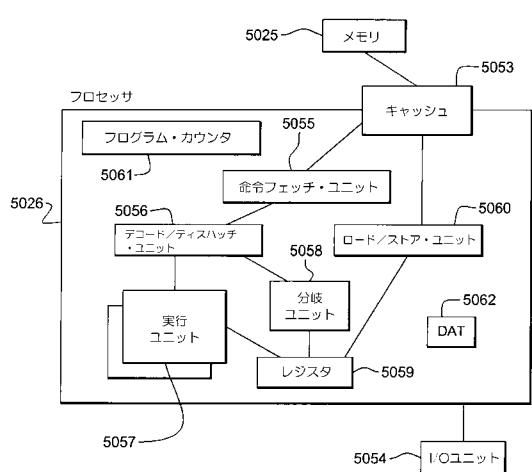

【図 28】コンピュータ・システムの種々の要素の一実施形態を示す。

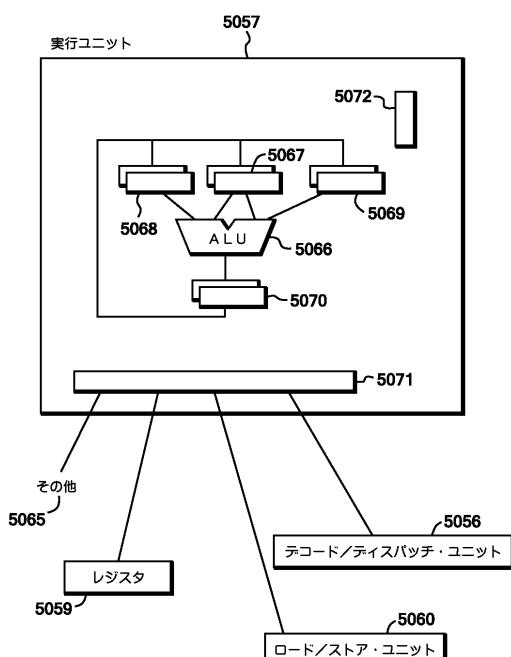

【図 29】図 28 のコンピュータ・システムの実行ユニットの一実施形態を示す。

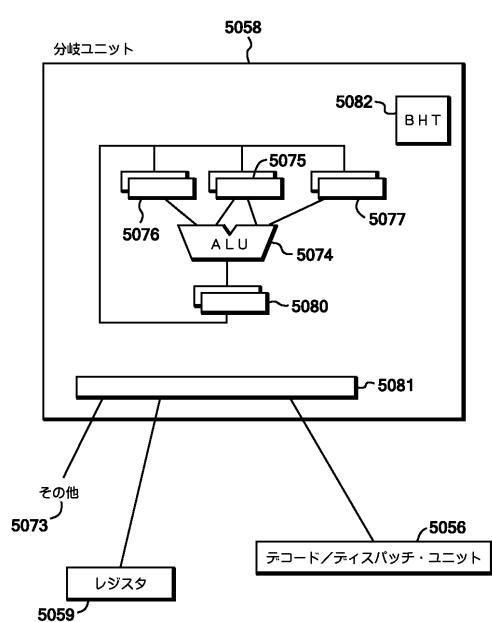

【図 30】図 28 のコンピュータ・システムの分岐ユニットの一実施形態を示す。

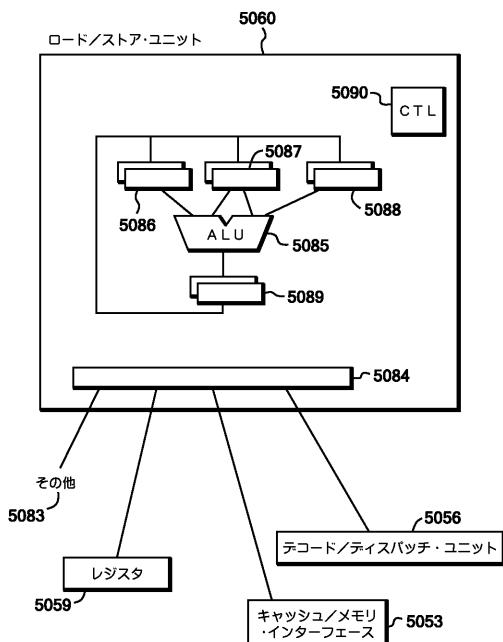

【図 31】図 28 のコンピュータ・システムのロード/ストア・ユニットの一実施形態を示す。

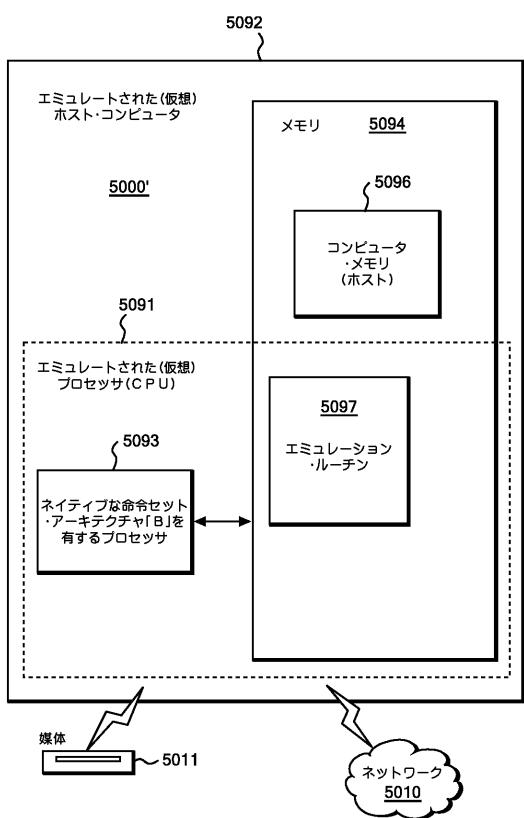

【図 32】エミュレートされたホスト・コンピュータ・システムの一実施形態を示す。

【発明を実施するための形態】

【0011】

1つ又は複数の態様によると、種々のベクトル命令、並びにベクトル例外処理を含むベクトル・ファシリティが提供される。本明細書で説明される命令の各々は、1つ又は複数のベクトル・レジスタ（本明細書では、ベクトルとも呼ばれる）を用いる Single Instruction Multiple Data (SIMD) 命令である。ベクトル・レジスタは、例えば、中央演算処理ユニット (CPU) 又は他のプロセッサの一部として利用可能な小容量のストレージである（例えば、主メモリではない）プロセッサ・レジスタ（ハードウェア・レジスタとも呼ばれる）である。各ベクトル・レジスタは、1つ又は複数の要素を有するベクトル・オペランドを含み、要素の長さは、例えば、1バイト、2バイト、4バイト、又は8バイトである。他の実施形態において、要素は他のサイズのものとすることができます、また、ベクトル命令は SIMD 命令である必要はない。

40

50

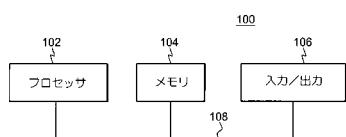

**【0012】**

1つ又は複数の態様を組み込み、用いるためのコンピューティング環境の一実施形態が、図1を参照して説明される。コンピューティング環境100は、例えば1つ又は複数のバス108及び／又は他の接続を介して互いに結合された、例えばプロセッサ102（例えば中央演算処理ユニット）、メモリ104（例えば主メモリ）、並びに1つ又は複数の入力／出力（I/O）デバイス及び／又はインターフェース106を含む。

**【0013】**

一例において、プロセッサ102は、インターナショナル・ビジネス・マシーンズ・コーポレーションにより提供されるz/Architectureに基づいており、同じくインターナショナル・ビジネス・マシーンズ・コーポレーションにより提供され、z/Architectureを実装する、System zサーバなどのサーバの一部である。z/Architectureの一実施形態は、IBM（登録商標）の刊行物である非特許文献1に記載されている。一例において、プロセッサは、同じくインターナショナル・ビジネス・マシーンズ・コーポレーションにより提供される、z/OSなどのオペレーティング・システムを実行する。IBM（登録商標）、z/Architecture（登録商標）、及びz/OS（登録商標）は、米国ニューヨーク州アーモンク所在のインターナショナル・ビジネス・マシーンズ・コーポレーションの登録商標である。本明細書で使用される他の名称は、インターナショナル・ビジネス・マシーンズ・コーポレーション又は他の会社の登録商標、商標、又は製品名である場合がある。10

**【0014】**

さらに別の実施形態において、プロセッサ102は、インターナショナル・ビジネス・マシーンズ・コーポレーションにより提供されるPower Architectureに基づいている。Power Architectureの一実施形態は、非特許文献2に記載されている。Power Architecture（登録商標）は、インターナショナル・ビジネス・マシーンズ・コーポレーションの登録商標である。20

**【0015】**

さらに別の実施形態において、プロセッサ102は、Intel Corporationにより提供されるIntelアーキテクチャに基づいている。Intelアーキテクチャの一実施形態は、非特許文献3及び非特許文献4に記載されている。Intel（登録商標）は、カリフォルニア州サンタクララ所在のIntel Corporationの登録商標である。30

**【0016】**

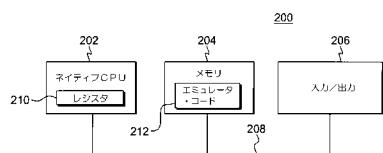

1つ又は複数の態様を組み込み、用いるためのコンピューティング環境の別の実施形態が、図2を参照して説明される。この例において、コンピューティング環境200は、例えば1つ又は複数のバス208及び／又は他の接続を介して互いに結合された、例えばネイティブ中央演算処理プロセッサ202、メモリ204、並びに1つ又は複数の入力／出力（I/O）デバイス及び／又はインターフェース206を含む。例として、コンピューティング環境200は、ニューヨーク州アーモンク所在のインターナショナル・ビジネス・マシーンズ・コーポレーションにより提供されるPowerPCプロセッサ、pSeriesサーバ、又はxSeriesサーバ、及びカリフォルニア州Palo Alto所在のHewlett Packard Co.,により提供される、Intel Itanium IIプロセッサを搭載するHP Superdome、及び／又はインターナショナル・ビジネス・マシーンズ・コーポレーション、Hewlett Packard、Intel、Oracle、又はその他により提供されるアーキテクチャに基づく他のマシンを含むことができる。40

**【0017】**

ネイティブ中央演算処理ユニット202は、環境内での処理の際に用いられる、1つ又は複数の汎用レジスタ及び／又は1つ又は複数の専用レジスタなどの1つ又は複数のネイティブ・レジスタ210を含む。これらのレジスタは、任意の特定の時点での環境の状態を表す情報を含む。50

## 【0018】

さらに、ネイティブ中央演算処理ユニット202は、メモリ204に格納された命令及びコードを実行する。1つの具体的な例においては、中央演算処理ユニットは、メモリ204に格納されたエミュレータ・コード212を実行する。このコードにより、1つのアーキテクチャで構成された処理環境が、別のアーキテクチャをエミュレートすることが可能になる。例えば、エミュレータ・コード212は、PowerPCプロセッサ、pSeriesサーバ、xSeriesサーバ、HP Superdomeサーバなどのような、z/Architecture以外のアーキテクチャに基づくマシンが、z/Architectureをエミュレートし、z/Architectureに基づき開発されたソフトウェア及び命令を実行することを可能にする。

10

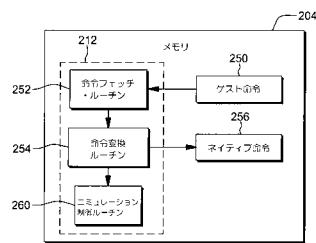

## 【0019】

エミュレータ・コード212に関する更なる詳細が、図3を参照して説明される。メモリ204に格納されたゲスト命令250が、ネイティブCPU202のもの以外のアーキテクチャで実行されるように開発されたソフトウェア命令（例えば、マシン命令に関する）を含む。例えば、ゲスト命令250は、z/Architectureプロセッサ102上で実行されるように設計されているが、代わりに、例えばIntel Itanium IIプロセッサとすることができるネイティブCPU202上でエミュレートされてもよい。一例において、エミュレータ・コード212は、メモリ204から1つ又は複数のゲスト命令250を取得し、取得した命令のためのローカル・バッファリングを随意的に提供するための命令フェッチ・ルーチン252を含む。エミュレータ・コード212はまた、取得したゲスト命令のタイプを判断し、ゲスト命令を1つ又は複数の対応するネイティブ命令256に変換するための命令変換ルーチン254も含む。この変換は、例えば、ゲスト命令により実施される機能を識別すること、及びその機能を実施するためのネイティブ命令を選択することを含む。

20

## 【0020】

さらに、エミュレータ212は、ネイティブ命令を実行させるためのエミュレーション制御ルーチン260を含む。エミュレーション制御ルーチン260は、ネイティブCPU202に、既に取得した1つ又は複数のゲスト命令をエミュレートするネイティブ命令のルーチンを実行させ、こうした実行の最後に、制御を命令フェッチ・ルーチンに戻して、次のゲスト命令又はゲスト命令のグループの取得をエミュレートすることができる。ネイティブ命令256の実行は、データをメモリ204からレジスタにロードすること、データをレジスタから再びメモリに格納すること、又は変換ルーチンによって求められるような何らかのタイプの算術演算又は論理演算を実施することを含むことができる。

30

## 【0021】

各ルーチンは、例えば、メモリに格納され、ネイティブ中央演算処理ユニット202によって実行される、ソフトウェアの形で実装される。他の例においては、ルーチン又は演算は、ファームウェア、ハードウェア、ソフトウェア、又はそれらの何らかの組み合わせの形で実装される。エミュレートされるプロセッサのレジスタは、ネイティブCPUのレジスタ210又はメモリ204内の位置を使用して、エミュレートすることができる。実施形態において、ゲスト命令250、ネイティブ命令256、及びエミュレータ・コード212は、同一のメモリ内にあっても、又は異なるメモリ・デバイス間に分散されてもよい。

40

## 【0022】

本明細書で用いられるファームウェアは、例えば、プロセッサのマイクロコード、ミリコード、及び／又はマクロコードを含む。ファームウェアは、例えば、上位レベルのマシン・コードの実装に用いられるハードウェア・レベルの命令及び／又はデータ構造体を含む。一実施形態において、ファームウェアは、例えば、典型的には、信頼できるソフトウェアを含むマイクロコード、又は基礎をなすハードウェアに特有のマイクロコードとして配信される独自のコードを含み、システム・ハードウェアへのオペレーティング・システムのアクセスを制御する。

50

**【 0 0 2 3 】**

一例において、取得され、変換され、実行されるゲスト命令 250 は、本明細書で説明される 1 つの命令である。1 つのアーキテクチャ（例えば、z / Architecture のものであるこの命令が、メモリからフェッチされ、変換され、別のアーキテクチャ（例えば、PowerPC、pSeries、xSeries、Intel 等）のネイティブ命令 256 のシーケンスとして表される。次に、これらのネイティブ命令が実行される。

**【 0 0 2 4 】**

一実施形態において、本明細書で説明される命令は、ベクトル・ファシリティの一部であるベクトル命令である。ベクトル・ファシリティは、例えば、1 つの要素から 16 の要素までの範囲の固定サイズのベクトルを提供する。各ベクトルは、ファシリティ内で定められたベクトル命令により操作されるデータを含む。一実施形態において、ベクトルが複数の要素で構成される場合、各要素は、他の要素と共に並行処理される。全ての要素の処理が完了するまで、命令は完了しない。他の実施形態において、要素は部分的に並行処理され、及び／又は逐次的に処理される。10

**【 0 0 2 5 】**

ベクトル命令は、z / Architecture、Power、x86、IA-32、IA-64 等を含むがこれらに限定されるものではない、種々のアーキテクチャの一部として実装することができる。本明細書で説明される実施形態は z / Architecture に関するものであるが、本明細書で説明されるベクトル命令及び 1 つ又は複数の他の形態は、他の多数のアーキテクチャに基づくものであってもよい。z / Architecture は一例にすぎない。20

**【 0 0 2 6 】**

ベクトル・ファシリティが z / Architecture の一部として実装される一実施形態において、ベクトル・レジスタ及び命令を使用するために、指定された制御レジスタ（例えば、制御レジスタ 0）におけるベクトル・イネーブルメント制御（vector enablement control）及びレジスタ制御が、例えば 1 に設定される。ベクトル・ファシリティがインストールされており、ベクトル命令がイネーブルメント制御の設定なしに実行される場合、データ例外が認識される。ベクトル・ファシリティがインストールされておらず、ベクトル命令が実行される場合、演算例外が認識される。30

**【 0 0 2 7 】**

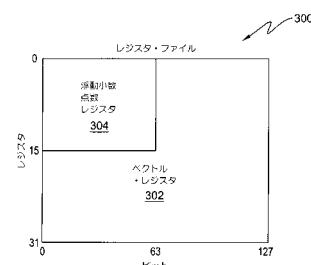

一実施形態においては、32 のベクトル・レジスタが存在し、他のタイプのレジスタは、ベクトル・レジスタの象限にマッピングすることができる。例えば、図 4 に示すように、レジスタ・ファイル 300 は 32 のベクトル・レジスタ 302 を含み、各レジスタの長さは 128 ビットである。長さが 64 ビットである 16 の浮動小数点レジスタ 304 は、ベクトル・レジスタに重ね合わせができる。従って、一例として、浮動小数点レジスタ 304 が修正されると、ベクトル・レジスタ 302 も修正される。他のタイプのレジスタに対する他のマッピングも可能である。

**【 0 0 2 8 】**

ベクトル・データは、ストレージにおいて、例えば、他のデータ形式と同じ左から右への順序で現れる。0 - 7 の番号が付けられたデータ形式のビットは、ストレージ内の左端の（最小番号を付された）バイト位置のバイトを構成し、ビット 8 - 15 は、次の順次位置のバイトを形成し、以下同様である。さらに別の例において、ベクトル・データは、ストレージにおいて、右から左などの別の順序で現れることがある。40

**【 0 0 2 9 】**

本明細書で説明されるベクトル命令の各々は複数のフィールドを有し、フィールドの 1 つ又は複数は、それに付随する下付き数字を有する。命令フィールドに付随する下付き数字は、そのフィールドが適用されるオペランドを示す。例えば、ベクトル・レジスタ V<sub>1</sub> に付随する下付き数字 1 は、V<sub>1</sub> のレジスタが第 1 のオペランドを含むことを示し、以下同様である。レジスタ・オペランドは、長さが 1 レジスタであり、これは例えば 128 ビ50

ットである。

#### 【0030】

さらに、ベクトル・ファシリティが与えられるベクトル命令の多くは、指定ビットのフィールドを有する。レジスタ拡張ビット(`register extension bit`)又はRXBと呼ばれるこのフィールドは、ベクトル・レジスタ指定のオペランドの各々についての最上位ビットを含む。命令によって指定されないレジスタ指示のためのビットは、予約され、ゼロに設定される。最上位ビットは、例えば、4ビットのレジスタ指示の左に連結されて、5ビットのベクトル・レジスタ指示を作成する。

#### 【0031】

一例において、RXBフィールドは4ビット(例えば、ビット0-3)を含み、これらのビットは、以下のように定義される。:

0 - 命令の第1のベクトル・レジスタ指定(例えば、ビット8-11内)のための最上位ビット。

1 - もしあれば、命令の第2のベクトル・レジスタ指定(例えば、ビット12-15内)のための最上位ビット。

2 - もしあれば、命令の第3のベクトル・レジスタ指定(例えば、ビット16-19内)のための最上位ビット。

3 - もしあれば、命令の第4のベクトル・レジスタ指定(例えば、ビット32-35内)のための最上位ビット。

#### 【0032】

各ビットは、例えば、レジスタ番号に応じて、アセンブラーによりゼロ又は1に設定される。例えば、レジスタ0-15に対してビットは0に設定され、レジスタ16-31に対してビットは1に設定される、などである。

#### 【0033】

一実施形態において、各RXBビットは、1つ又は複数のベクトル・レジスタを含む命令における特定の位置のための拡張ビットである。例えば、1つ又は複数のベクトル命令において、RXBのビット0は、位置8-11のための拡張ビットであり、これが例えば $V_1$ に割り当てられ、RXBのビット1は、位置12-15のための拡張ビットであり、これが例えば $V_2$ に割り当てられ、以下同様である。さらに別の実施形態において、RXBフィールドは付加的なビットを含み、1つより多くのビットが、各ベクトル又は位置のための拡張として用いられる。

#### 【0034】

RXBフィールドを含む、一態様に従って提供される1つの命令が、`Vector Floating Point Test Data Class Immediate (VFTCI)`命令であり、その一例を図5に示す。一例において、`Vector Floating Point Test Data Class Immediate`命令400は、`Vector Floating Point Test Data Class Immediate`操作を指示するオペコード・フィールド402a(例えば、ビット0-7)、402b(例えば、ビット40-47)と、第1のベクトル・レジスタ( $V_1$ )を指示するのに用いられる第1のベクトル・レジスタ・フィールド404(例えば、ビット8-11)と、第2のベクトル・レジスタ( $V_2$ )を指示するのに用いられる第2のベクトル・レジスタ・フィールド406(例えば、ビット12-15)と、ビットマスクを含むための即値フィールド( $I_3$ )408(例えば、ビット16-27)と、第1のマスク・フィールド( $M_5$ )410(例えば、ビット28-31)と、第2のマスク・フィールド( $M_4$ )412(例えば、ビット32-35)と、RXBフィールド414(例えば、ビット36-39)とを含む。フィールド404-414の各々は、一例においては、オペコード・フィールドから分離し、独立している。さらに、一実施形態において、これらのフィールド404-414は互いに分離し、独立しているが、他の実施形態においては、1つより多くのフィールドを組み合わせてもよい。これらのフィールドの使用に関する更なる情報を以下に説明する。

10

20

30

40

50

**【0035】**

一例において、オペコード・フィールド 402a により指示されるオペコードの選択されたビット（例えば、最初の 2 ビット）は、命令の長さを指定する。この特定の例において、選択されたビットは、長さが 3 ハーフワード（halfword）であることを示す。さらに、命令の形式は、拡張されたオペコード・フィールドを伴うベクトル・レジスタ・アンド即値操作（vector register-and-immediate）操作である。ベクトル（V）フィールドの各々は、RXB によって指定されたその対応する拡張ビットと共に、ベクトル・レジスタを指示する。特に、ベクトル・レジスタについては、オペランドを含むレジスタが、例えば、その対応するレジスタ拡張ビット（RXB）を最上位ビットとして付加したレジスタ・フィールドの 4 ビット・フィールドを用いて指定される。例えば、4 ビット・フィールドが 0110 であり、拡張ビットが 0 である場合、5 ビット・フィールド 00110 はレジスタ番号 6 を示す。

10

**【0036】**

さらに、VFTCI 命令の一実施形態において、V<sub>1</sub>404 及び V<sub>2</sub>406 は、それぞれ、命令のための第 1 のオペランド及び第 2 のオペランドを含むベクトル・レジスタを指定する。付加的に、以下でさらに詳細に説明されるように、I<sub>3</sub>408 は複数のビットを有するビットマスクを含み、各ビットは 2 進浮動小数点要素のクラス及び符号（正又は負）を表すのに用いられる。

20

**【0037】**

さらに別の実施形態において、ビットマスクは、例として、汎用レジスタ、メモリ、（要素ごとに異なる）ベクトル・レジスタの要素において、又はアドレス計算から、提供することができる。ビットマスクは、命令の明示的オペランドとして含ませてもよく、又は暗黙オペランド若しくは入力として含ませてもよい。

20

**【0038】**

M<sub>5</sub> フィールド 410 は、例えば、4 ビット（0 - 3）を有し、例えばビット 0 における单一要素制御（S）を指定する。ビット 0 が 1 に設定される場合、操作は、ベクトル内のゼロ・インデックス付の要素に対してのみ行われる。第 1 のオペランド・ベクトル内の他の全ての要素のビット位置は、予測不能である。ビット 0 がゼロに設定される場合、操作は、ベクトル内の全ての要素に対して行われる。

30

**【0039】**

M<sub>4</sub> フィールド 412 は、例えば、命令の第 2 のオペランド内の浮動小数点数のサイズを指定するのに用いられる。一例において、このフィールドは、倍精度 2 進浮動小数点数を示す 3 に設定される。他の例も可能である。

30

**【0040】**

Vector Floating Point Test Data Class Immediate 命令の一実施形態の実行において、第 3 のオペランドから 1 つ又は複数のビットを選択するために、第 2 のオペランドの浮動小数点要素のクラス及び符号を検査する。選択されたビットが設定された場合、第 1 のオペランド内の対応する要素の全てのビット位置が 1 に設定され、そうでなければ、これらはゼロに設定される。つまり、第 2 のオペランドの要素内に含まれる浮動小数点数のクラス / 符号が、第 3 のオペランド内の設定されたビット（即ち、例えば 1 に設定されたビット）と一致した場合、第 2 のオペランドの要素に対応する第 1 のオペランドの要素は、1 に設定される。一例において、全てのオペランド要素は、長形式（long format）の BFP（2 進浮動小数点）数を含む。

40

**【0041】**

本明細書で示されるように、第 3 のオペランドの 12 ビット、すなわち命令テキストのビット 16 - 27 を用いて、BFP データのクラス及び符号の 12 の組み合わせを指定する。一例において、図 6 に示されるように、BFP オペランド要素は、6 つのクラス 430：即ち、ゼロ、正規数、非正規数、無限大、クワイエット（quiet）NaN（NaN：Not-a-Number（非数））、及びシグナリング（signaling）N

50

a N に分けられ、各クラスは、これと関連付けられた符号 4 3 2 ( 正又は負のいずれか ) を有する。従って、例えば、I<sub>3</sub> のビット 0 は正符号を有するゼロ・クラスを指定し、ビット 1 は負符号を有するゼロ・クラスを指定する等である。

#### 【 0 0 4 2 】

第 3 のオペランドの 1 つ又は複数のビットを 1 に設定することができる。さらに、一実施形態において、命令は、同時に 1 つ又は複数の要素を操作することができる。

I E E E 例外を引き起こすことなく、S N a N ( シグナリング N a N ) 及び Q N a N ( クワイエット N a N ) を含むオペランド要素が検査される。

#### 【 0 0 4 3 】

全ての要素に対する結果のサマリ条件コード :

- 0 全ての要素について、選択されたビットは 1 である ( 一致 )

- 1 全ての要素ではないが、少なくとも 1 つの要素について、選択されたビットは 1 である ( S ビットがゼロである場合 )

- 2 - -

- 3 全ての要素について、選択されたビットは 0 である ( 非一致 )

#### 【 0 0 4 4 】

I E E E 例外 : なし

プログラム例外 :

- \* ベクトル・ファシリティがイネーブルにされていないことを示す、データ例外コード ( D X C ) F E を伴うデータ、ベクトル命令

- \* 演算 ( z / A r c h i t e c t u r e のためのベクトル・ファシリティがインストールされていない場合 )

- \* 指定

- \* トランザクション制限

#### 【 0 0 4 5 】

プログラミング上の注意 :

1 . この命令は、例外のリスクなしに又は I E E E フラグを設定せずにオペランド要素をテストする方法を提供する。

2 . S ビットが設定された場合、1 の条件コードは使用されない。

#### 【 0 0 4 6 】

V e c t o r F l o a t i n g P o i n t T e s t D a t a C l a s s I m m e d i a t e 命令の一実施形態に関する更なる詳細が、図 7 及び図 8 を参照して説明される。特に、図 7 は、プロセッサ ( 例えば、C P U ) によって実施される V e c t o r F l o a t i n g P o i n t T e s t D a t a C l a s s I m m e d i a t e 命令と関連付けられた論理の一実施形態を示し、図 8 は、V e c t o r F l o a t i n g P o i n t T e s t D a t a C l a s s I m m e d i a t e 命令の実行を図示するブロック図の一例を示す。

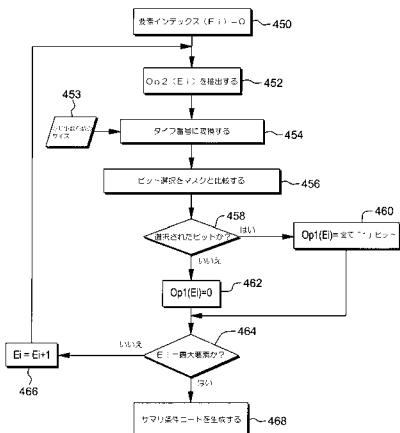

#### 【 0 0 4 7 】

図 7 を参照すると、最初に、要素インデックス ( E i ) と呼ばれる変数をゼロに初期化する ( ステップ 4 5 0 ) 。次に、この場合は要素 0 である要素 E i の値を、命令の第 2 のオペランドから ( 例えば、V<sub>2</sub> によって指示されるレジスタに格納されたオペランドから ) 抽出する ( ステップ 4 5 2 ) 。以下で説明されるように、長形式の 2 進浮動小数点の値であるこの値をタイプ番号に変換し、第 2 のオペランドの浮動小数点要素についてのクラス及び符号を取得する ( ステップ 4 5 4 ) 。一例において、浮動小数点数のサイズ 4 5 3 を変換論理に入力する。図 6 を参照して説明されるように、取得したクラス及び符号を特定のクラス / 符号ビットと関連付ける。例えば、浮動小数点数が正の正規数であることが変換により示される場合、ビット 2 をその浮動小数点数と関連付ける。

#### 【 0 0 4 8 】

変換に続いて、変換に基づいて決定された特定のビットに対応する第 3 のオペランド内のビット ( 選択されたビットと呼ばれる ) をチェックする ( ステップ 4 5 6 ) 。選択され

10

20

30

40

50

たビットが設定された場合（問い合わせ 458）、要素（E<sub>i</sub>）に対応する第1のオペラント内の要素を全て1に等しくなるように設定し（ステップ460）、そうでなければ、第1のオペラント内の要素をゼロと等しくなるように設定する（ステップ462）。例えば、要素0内の浮動小数点数の変換が正の正規数を示す場合、ビット2をその数と関連付ける。従って、第3のオペラントのビット2をチェックし、これが1に設定された場合、第1のオペラントの要素0を全て1に設定する。

#### 【0049】

その後、E<sub>i</sub>が第2のオペラントの要素の最大数に等しいかどうかについての判断を行う（問い合わせ464）。等しくない場合、E<sub>i</sub>を例えば1だけインクリメントし（ステップ466）、処理はステップ452を続行する。そうではなく、E<sub>i</sub>が要素の最大数に等しい場合、サマリ条件コードを生成する（ステップ468）。サマリ条件コードは、第2のオペラントの全ての要素についての処理を要約する。例えば、全ての要素について、選択されたビットが1である場合（一致）、結果の条件コードはゼロである。一方、要素の全てではないが少なくとも1つについて、選択されたビットが1である場合（Sビットがゼロでない場合）、条件コードは1であり、要素の全てについて選択されたビットが0である場合（非一致）、条件コードは3である。

10

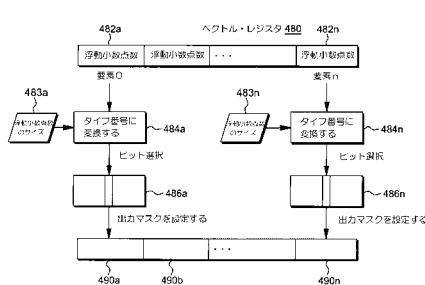

#### 【0050】

上記の処理は、図8のブロック図に示される。示されるように、ベクトル・レジスタ480は、各々が浮動小数点数を含む、複数の要素482a - 482nを含む。浮動小数点数483a - 483nの各々の浮動小数点数及びサイズは、タイプ番号への変換（convert-to-type number）論理484a - 484nに入力され、その出力は、その浮動小数点数についてのクラス／符号を表す特定のビットである。次に、特定のビットの各々に対応する各マスク486a - 486n内の選択されたビットをチェックする。選択されたビットが設定されているかどうかに応じて、ベクトル・レジスタ480内の第1のオペラントが設定される。例えば、第2のオペラントの要素0に対して、選択されたビットが設定されている場合、第1のオペラントの要素490aは全て1に設定される。同様に、第2のオペラントの要素1に対する選択されたビットが設定されていない（例えば、ゼロに設定されている）場合、第1のオペラントの要素490bは全てゼロに設定される。

20

#### 【0051】

ここで、タイプ番号への変換論理の一実施形態の更なる詳細を説明する。最初に、標準的なIEEE2進浮動小数点数である浮動小数点数を、既知のように、3つの部分：即ち符号部、指数部（8ビット）+127、及び仮数部（23ビット）に変換する。次に、図9に示されるように、3つの部分全ての値をチェックして、クラス及び符号を判断する。例えば、符号は符号部の値であり、クラス（図9では、エンティティとしても知られる）は、指数部及び仮数部の値に基づいている（図9の単位ビットは、仮数部の暗黙ビットである）。一例として、指数部及び仮数部（単位ビットを含む）の値がゼロの場合、クラスはゼロであり、符号部が正の場合、符号は正である。従って、ビット0（図6）は、この浮動小数点数のクラス／符号を表す。

30

#### 【0052】

上述したのは、ベクトル内の要素の浮動小数点クラスをテストし、結果のビットマスクを設定するための命令の一実施形態である。Vector Floating Point Test Data Class Immediate命令は、検出するための浮動小数点数のクラスを各ビットが表す即値フィールドを有する。入力ベクトルの各浮動小数点の要素をテストして、値が、命令によって指定されるクラスのいずれかの中にあるかどうかを確認する。浮動小数点要素がクラスの1つの中にある場合、出力ベクトルの対応する要素のビット位置は1に設定される。これは、いかなる例外又は割り込みも引き起こすことなく、2進浮動小数点数に関する何らかの特性（例えば、クラス及び符号）を判断するための技術を提供する。

40

#### 【0053】

50

さらに別の実施形態において、第3のオペランドのどのビットが（例えば1に）設定されているかをチェックし、次いで、第2のオペランドの1つ又は複数の要素のクラス／符号が設定されたビットの1つと同じであるかどうかを判断することにより、テストを行うことができる。次いで、比較に基づいて第1のオペランドを設定する。

#### 【0054】

さらに別の態様において、`Vector Checksum`命令が提供され、その一例が図10に示される。一例において、`Vector Checksum`命令500は、`Vector Checksum`操作を示すオペコード・フィールド502a（例えば、ビット0-7）、502b（例えば、ビット40-47）と、第1のベクトル・レジスタ（ $V_1$ ）を指示するのに用いられる第1のベクトル・レジスタ・フィールド504（例えば、ビット8-11）と、第2のベクトル・レジスタ（ $V_2$ ）を指示するのに用いられる第2のベクトル・レジスタ・フィールド506（例えば、ビット12-15）と、第3のベクトル・レジスタ（ $V_3$ ）を指示するのに用いられる第3のベクトル・レジスタ・フィールド508（例えば、ビット16-19）と、`RXB`フィールド510（例えば、ビット36-39）とを含む。フィールド504乃至510の各々は、一例において、オペコード・フィールドから分離され、独立している。さらに、一実施形態において、これらのフィールド504乃至510は互いに分離し、独立しているが、他の実施形態においては、1つより多くのフィールドを組み合わせてもよい。

10

#### 【0055】

さらに別の実施形態において、第3のベクトル・レジスタ・フィールドは、命令の明示的オペランドとしては含まれず、代わりに、暗黙オペランド又は入力である。さらに、オペランドにおいて提供される値を、例えば汎用レジスタで、メモリで、アドレス計算としてなど、他の手法で提供することもできる。

20

#### 【0056】

さらに別の実施形態において、第3のオペランドは、明示的であれ又は暗黙的であれ、全く提供されない。

#### 【0057】

一例において、オペコード・フィールド502aにより指示されるオペコードの選択されたビット（例えば、最初の2ビット）は、命令の長さを指定する。この特定の例において、選択されたビットは、長さが3ハーフワードであることを示す。さらに、命令の形式は、拡張されたオペコード・フィールドを伴うベクトル・レジスタ・アンド・レジスタ（`vector register-and-register`）操作である。ベクトル（ $V$ ）フィールドの各々は、`RXB`によって指定されたその対応する拡張ビットと共に、ベクトル・レジスタを指示する。特に、ベクトル・レジスタについては、オペランドを含むレジスタは、例えば、その対応するレジスタ拡張ビット（`RXB`）を最上位ビットとして付加したレジスタ・フィールドの4ビット・フィールドを用いて指定される。

30

#### 【0058】

`Vector Checksum`命令の一実施形態の実行において、例えばワード（`word`）サイズである第2のオペランドからの要素が、第3のオペランドの選択された要素、例えば第3のオペランドのワード1内の要素と共に、1つずつ加算される。（別の実施形態においては、第3のオペランドの選択された要素の加算は任意である。）和は、第1のオペランドの選択された位置、例えばワード1に入れられる。第1のオペランドの他のワード要素、例えばワード要素0及び2-3に、ゼロが入れられる。ワード・サイズ要素は、全て32ビットの符号なし2進整数として扱われる。要素のそれぞれの加算後、例えば和のビット位置0のキャリー出力を、例えば、第1のオペランドのワード要素1における結果のビット位置31に加算する。

40

#### 【0059】

条件コード：コードは変更されないままである。

#### 【0060】

プログラム例外：

50

\* ベクトル・ファシリティがイネーブルにされていないことを示す、データ例外コード(DXC)FEを伴うデータ、ベクトル命令

\* 演算(z/Architectureのためのベクトル・ファシリティがインストールされていない場合)

\* トランザクション制限

#### 【0061】

プログラミング上の注意：

1. 第3のオペランドのコンテンツは、チェックサム計算アルゴリズムの開始時にゼロを含むことになる。

2. 16ビット・チェックサムは、例えば、TCP/IPアプリケーションにおいて用いられる。32ビット・チェックサムを計算した後、以下のプログラムを実行することができる。

#### 【表1】

VERLLF V2,V1,16(0) (VERLLF - Vector Element Rotate Left)

Logical – 4-byte value)

VAF V2,V1,V2 (VAF – Vector Add – 4 byte value)

10

要素2内のハーフワードは、16ビット・チェックサムを含む。

#### 【0062】

Vector Checksum命令に関する更なる詳細が、図11及び図12を参照して説明される。一例において、図11は、Vector Checksum命令の実行においてプロセッサにより実施される論理の一実施形態を示し、図12は、Vector Checksum命令の実行の一例のブロック図を示す。

#### 【0063】

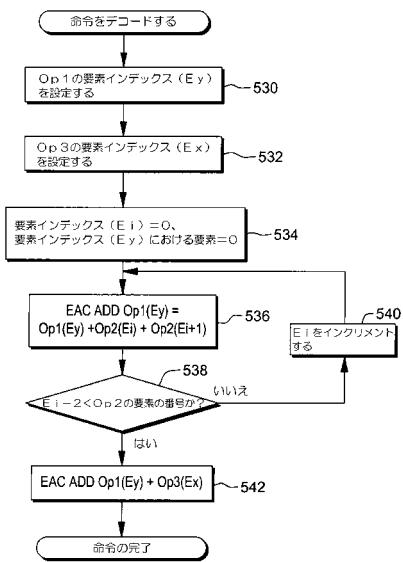

図11を参照すると、最初に、第1のオペランド(OP1)の要素インデックス(Ey)を、例えば第1のオペランドの要素1を示す1に設定する(ステップ530)。同様に、第3のオペランド(OP3)の要素インデックス(Ex)を、例えば第3のオペランドの要素1を示す1に設定する(ステップ532)。次に、要素インデックス(Ei)を0と等しくなるように設定し、要素インデックス(Ey)における要素、即ちこの例では要素1をゼロに初期化する(ステップ534)。さらに別の実施形態において、Ex及びEyは、任意の有効な要素インデックスに設定することができる。

30

#### 【0064】

$OP1(Ey) = OP1(Ey) + OP2(Ei) + OP2(Ei+1)$ である、エンド・アラウンド・キャリー(EAC)加算を行う(ステップ536)。従って、出力ベクトル(OP1)の要素1を、その要素のコンテンツに第2のオペランド(OP2)の要素0内の値及び第2のオペランドの要素1内の値を加算したものと等しくなるように、設定する。エンド・アラウンド・キャリー加算を用いて、加算演算を行い、加算からのあらゆるキャリー出力を和に戻し、新しい和を生成する。

40

#### 【0065】

さらに別の実施形態においては、上述のように加算する代わりに、以下を実施する。すなわち、一時的アキュムレータ値を定め、ゼロに初期化し、次に、一度に1つの要素を加算する。さらに別の実施形態として、全てのワードを並列に加算し、一時的アキュムレータは存在しない。他の変形も可能である。

#### 【0066】

その後、第2のオペランド内に加算すべき付加的な要素があるかどうかについての判断を行う(問い合わせ538)。例えば、Ei-2 < 第2のオペランドの要素の番号であるか。加算すべき第2のオペランドの要素がさらにある場合、Eiを、例えば2だけイン

50

クリメントし(ステップ540)、処理はステップ536を続行する。

#### 【0067】

第2のオペランドにわたって要素を加算した後、結果を第3のオペランド内の値に加算する。例えば、第1のオペランドの要素(Ey)(これは、全ての第2のオペランドの要素にわたるEAC加算の和である)と第3のオペランド(OP3)の要素(Ex)内の値とのエンド・アラウンド・キャリー加算を行う(即ち、EAC ADD OP1(Ey)+OP3(Ex))(ステップ542)。これは、図12に示される。

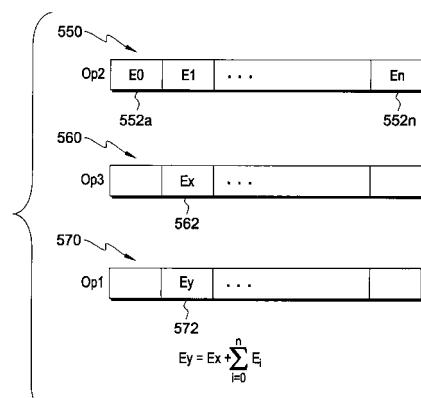

#### 【0068】

図12に示されるように、第2のオペランド550は複数の要素552a-552nを含み、これらの要素が、第3のオペランド560のワード1内の要素(562)と共に1つずつ加算される。結果は、第1のオペランド570の要素1(572)に入れられる。これは、式 $Ey = Ex + E_i$ の総和、により数学的に表され、ここで、iは0乃至nであり、加算はエンド・アラウンド・キャリー加算である。

10

#### 【0069】

上述したのは、レーン(lane)算術計算を行う代わりに、ベクトル・レジスタの要素にわたってチェックサムを行うVector Checksum命令の一実施形態である。一実施形態において、Vector Checksum命令は、エンド・アラウンド・キャリー加算によりsum-acrossを実施することにより、チェックサムを行う。一例において、Vector Checksum命令は、ベクトル・レジスタから4つの4バイト整数要素を取り出し、これらを加算する。加算からのあらゆるキャリー(桁上げ、carry)が戻されて加えられる。4バイトの和を別のオペランド内の4バイト要素に加算し、次に、さらに別のベクトル・レジスタに保存する(例えば、ベクトル・レジスタの下位4バイト要素が、ベクトル・レジスタの上位要素内に格納される)。

20

#### 【0070】

さらに別の実施形態において、値を保存するためにさらに別のベクトル・レジスタ又は別のレジスタが使用されず、代わりに、他のレジスタ(即ち、オペランド)の1つがアクチューメータとして使用される。

#### 【0071】

与えられるチェックサムを用いて、データの完全性を保つことができる。受信したデータが正しいことを検証するために、チェックサムが、データに適用され、ノイズのあるチャネル上で送られることが多い。この例では、本明細書で説明されるように、連続する4バイト整数を加算することによって、チェックサムが計算される。整数算術演算のキャリー出力がある場合、キャリー及び付加的な1が、累積和に加算される。

30

#### 【0072】

本明細書ではチェックサムが説明されるが、類似の技術を他のエンド・アラウンド・キャリー加算に対して用いることができる。

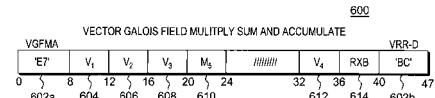

#### 【0073】

一様に従って提供されるさらに別の命令は、Vector Galois Field Multiply Sum and Accumulate(VGFMA)命令であり、その一例を図13に示す。一例において、Vector Galois Field Multiply Sum and Accumulate命令600は、Vector Galois Field Multiply Sum and Accumulate操作を示す、オペコード・フィールド602a(例えば、ビット0-7)、602b(例えば、ビット40-47)と、第1のベクトル・レジスタ(V<sub>1</sub>)を指示するのに用いられる第1のベクトル・レジスタ・フィールド604(例えば、ビット8-11)と、第2のベクトル・レジスタ(V<sub>2</sub>)を指示するのに用いられる第2のベクトル・レジスタ・フィールド606(例えば、ビット12-15)と、第3のベクトル・レジスタ(V<sub>3</sub>)を指示するのに用いられる第3のベクトル・レジスタ・フィールド608(例えば、ビット16-19)と、マスク・フィールド(M<sub>5</sub>)610(例えば、ビット20-23)と、第4のベクトル・レジスタ(V<sub>4</sub>)を指示するのに用いられる第4のベクトル・レジ

40

50

スタ・フィールド 612（例えば、ビット 32 - 35）と、RXB フィールド 614（例えば、ビット 36 - 39）とを含む。フィールド 604 - 614 の各々は、一例において、オペコード・フィールドから分離し、独立している。さらに、一実施形態においては、これらのフィールド 604 - 614 は互いに分離し、独立しているが、他の実施形態においては、1つより多くのフィールドを組み合わせてもよい。

#### 【0074】

一例において、オペコード・フィールド 602a により指示されるオペコードの選択されたビット（例えば、最初の 2 ビット）は、命令の長さを指定する。この特定の例において、選択されたビットは、長さが 3 ハーフワードであることを示す。さらに、命令の形式は、拡張されたオペコード・フィールドを伴うベクトル・レジスタ・アンド・レジスタ操作である。ベクトル（V）フィールドの各々は、RXB によって指定されたその対応する拡張ビットと共に、ベクトル・レジスタを指示する。特に、ベクトル・レジスタについては、例えば、その対応するレジスタ拡張ビット（RXB）を最上位ビットとして付加したレジスタ・フィールドの 4 ビット・フィールドを用いて、オペラントを含むレジスタが指定される。

10

#### 【0075】

$M_5$  フィールド 610 は、例えば 4 ビット（0 - 3）を含み、要素サイズ（ES）制御を指定する。要素サイズ制御は、ベクトル・レジスタ・オペランド 2 及び 3 内の要素のサイズを指定し、第 1 のオペランド及び第 4 のオペランド内の要素は、ES 制御によって指定されるものの 2 倍のサイズである。例えば、 $M_5$  における 0 の値はバイト・サイズの要素を示し、例として、1 はハーフワードを示し、2 はワードを示し、3 はダブルワード（doubleword）を示す。

20

#### 【0076】

Vector Galois Field Multiply Sum and Accumulate 命令の一実施形態の実行においては、ガロア体（Galois field）（即ち、有限数の要素を有する有限フィールド）において、第 2 のオペランドの各要素に、第 3 のオペランドの対応する要素を乗算する。つまり、キャリーレス（桁上げなし、carryless）乗算を用いて、第 2 のオペランドの各要素に、対応する第 3 のオペランドの要素を乗算する。一例において、ガロア体は、2 の位数を有する。この乗算は、標準的な 2 進乗算に類似しているが、シフトされる被乗数を加算する代わりに、排他的論理和演算（XOR）される。例えば、ダブル要素サイズの積の結果として得られる偶数 - 奇数の対を互いに排他的論理和演算し、第 4 のオペランドの、例えばダブルワイド要素などの対応する要素と排他的論理和演算する。結果は、例えば、第 1 のオペランドのダブルワイド要素に入れられる。

30

#### 【0077】

条件コード：コードは変更されないままである。

#### 【0078】

プログラム例外：

\* ベクトル・ファシリティがイネーブルにされていないことを示す、データ例外コード（DXC）FE を伴うデータ、ベクトル命令

40

\* 演算（z / Architecture のためのベクトル・ファシリティがインストールされていない場合）

\* 指定

\* トランザクション制限

#### 【0079】

さらに別の実施形態において、命令は、1つ又は複数のより少ない数のオペランドを含むことができる。例えば、第 4 のオペランドの代わりに、排他的論理和演算されるべき値は第 1 のオペランド内にあり、この値は結果も含む。他の変形も可能である。

#### 【0080】

Vector Galois Field Multiply Sum and Acc

50

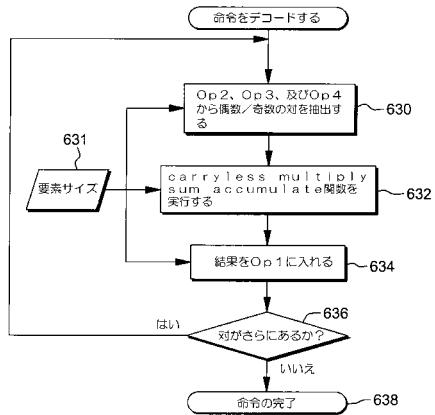

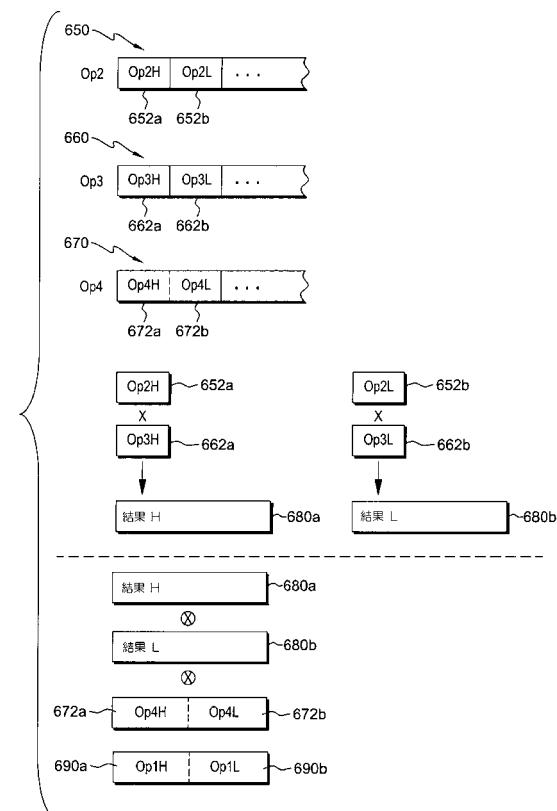

cumulate命令の実行の一実施形態に関する更なる詳細が、図14及び図15を参照して説明される。一例において、図14は、Vector Galois Field Multiply Sum and Accumulate命令を実行するためにプロセッサによって実施される論理の一実施形態を示し、図15は、その論理の実行を示すブロック図の一例を示す。

#### 【0081】

図14を参照すると、最初に、第2のオペランド(OP2)、第3のオペランド(OP3)、及び第4のオペランド(OP4)から、偶数／奇数の対を抽出し(ステップ630)、carryless multiply sum accumulate関数を実施する(ステップ632)。例えば、2の累乗のガロア体において動作する場合、キャリーレス乗算はシフト・アンドXOR(排他的OR)であり、これはあらゆるキャリーを事实上無視する。結果は、第1のオペランド(OP1)に入れられ(ステップ634)、抽出されるべき対がさらにあるかどうかについての判断が行われる(問い合わせ636)。対がさらにある場合、処理はステップ630を続行し、他の場合には、処理は完了する(ステップ638)。一例において、要素サイズ631は、ステップ630-634への入力である。

10

#### 【0082】

ステップ632のcarryless multiply sum accumulate関数の更なる詳細が、図15を参照して説明される。示されるように、オペランドの対OP2H 652a、OP2L 652bが、第2のオペランド650から抽出される。さらに、オペランドの対OP3H 662a、OP3L 662bが、第3のオペランド660から抽出され、オペランドの対OP4H 672a及びOP4L 672bが、第4のオペランド670から抽出される。キャリーレス乗算によって、オペランドOP2H 652aに、オペランドOP3H 662aを乗算して、結果H 680aが与えられる。同様に、キャリーレス乗算によって、オペランドOP2L 652bに、オペランドOP3L 662bを乗算して、結果L 680bが与えられる。次に、結果H 680aを結果L 680bと排他的論理和演算し、その結果をオペランドOPH 672a及びオペランドOP4L 672bと排他的論理和演算し、結果を、OP1H 690a、OP1L 690bに入れる。

20

#### 【0083】

本明細書で説明されたのは、キャリーレス乗算演算を行い、次に最終的な排他的論理和演算を行って累積和を生成するベクトル命令である。この技術は、2の位数を有する有限体で演算を行うエラー検出コード及び暗号化の種々の態様と共に使用することができる。

30

#### 【0084】

一例において、命令は、ベクトル・レジスタの複数の要素に対して、キャリーレス乗算演算を行って和を得る。さらに、命令は、和に対して最終的な排他的論理和演算を行って累積和を生成する。命令は、実行されると、ガロア体において第2のベクトル及び第3のベクトルの対応する要素を乗算し、シフトされた被乗数を排他的論理和演算する。各々のダブルワイドの積を互いに排他的論理和演算し、結果を、第1のベクトルの対応するダブルワイド要素と排他的論理和演算する。結果は、第1のベクトル・レジスタに格納される。ダブルワード要素が上述されているが、他の要素サイズのワード・サイズ要素を用いてもよい。命令は、多数の異なる要素サイズで動作することができる。

40

#### 【0085】

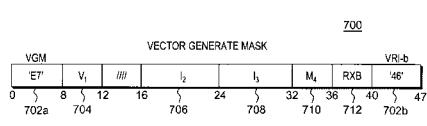

一態様に従って提供されるさらに別の命令は、Vector Generate Mask(VGM)命令であり、その一例が図16を参照して説明される。一例において、Vector Generate Mask命令700は、Vector Generate Mask操作を示すオペコード・フィールド702a(例えば、ビット0-7)、702b(例えば、ビット40-47)と、第1のベクトル・レジスタ(V<sub>1</sub>)を指示するのに用いられる第1のベクトル・レジスタ・フィールド704(例えば、ビット8-11)と、第1の値を指定するのに用いられる第1の即値フィールドI<sub>2</sub>706(例えば、ビ

50

ビット 16 - 24) と、第 2 の値を指定するのに用いられる第 2 の即値フィールド (I<sub>3</sub>) 708 (例えば、ビット 24 - 32) と、マスク・フィールド (M<sub>4</sub>) 710 (例えば、ビット 32 - 35) と、R X B フィールド 712 (例えば、ビット 36 - 39) とを含む。フィールド 704 - 712 の各々は、一例においては、オペコード・フィールドから分離し、独立している。さらに、一実施形態において、これらのフィールド 704 - 712 は互いに分離し、独立しているが、他の実施形態においては、1つより多くのフィールドを組み合わせてもよい。

#### 【0086】

さらに別の実施形態において、第 1 の値及び / 又は第 2 の値は、例として、汎用レジスタ、メモリ、(要素ごとに異なる)ベクトル・レジスタの要素において、又は、アドレス計算から、提供することができる。値は、命令の明示的オペランドとして含ませてもよく、又は暗黙オペランド若しくは入力として含ませてもよい。

10

#### 【0087】

一例において、オペコード・フィールド 702a により指示されるオペコードの選択されたビット (例えば、最初の 2 ビット) は、命令の長さを指定する。この特定の例において、選択されたビットは、長さが 3 ハーフワードであることを示す。さらに、命令の形式は、拡張されたオペコード・フィールドを伴うベクトル・レジスタ・アンド即値操作である。ベクトル (V) フィールドの各々は、R X B によって指定されたその対応する拡張ビットと共に、ベクトル・レジスタを指示する。特に、ベクトル・レジスタについては、オペランドを含むレジスタが、例えば、その対応するレジスタ拡張ビット (R X B) を最上位ビットとして付加したレジスタ・フィールドの 4 ビット・フィールドを用いて指定される。

20

#### 【0088】

M<sub>4</sub> フィールドは、例えば、要素サイズ制御 (E S) を指定する。要素サイズ制御は、ベクトル・レジスタ・オペランド内の要素のサイズを指定する。一例において、M<sub>4</sub> フィールドのビット 0 は 1 バイトを指定し、ビット 1 はハーフワード (例えば 2 バイト) を指定し、ビット 2 はワード (例えば 4 バイト、別名フルワード) を指定し、ビット 3 はダブルワードを指定する。

#### 【0089】

Vector Generate Mask 命令の一実施形態の実行において、第 1 のオペランド内の各要素について、ビットマスクが生成される。マスクは、例えば I<sub>2</sub> 内の符号なし整数値が指定するビット位置から開始して、例えば I<sub>3</sub> 内の符号なし整数値が指定するビット位置で終了する、1 に設定されたビットを含む。他の全てのビット位置はゼロに設定される。一例において、指定された要素サイズのビット位置の全てを表すのに必要なビット数のみが、I<sub>2</sub> フィールド及び I<sub>3</sub> フィールドから使用され、他のビットは無視される。I<sub>2</sub> フィールド内のビット位置が I<sub>3</sub> フィールド内のビット位置より大きい場合、ビット範囲は、指定された要素サイズの最大ビット位置でラップする。例えば、バイト・サイズの要素を仮定すると、I<sub>2</sub> = 1 及び I<sub>3</sub> = 6 であれば、結果のマスクは、X 7 E、又は B 0 1 1 1 1 1 1 0 である。しかしながら、I<sub>2</sub> = 6 及び I<sub>3</sub> = 1 であれば、結果のマスクは、X 8 1、又は b 1 0 0 0 0 0 1 である。

30

#### 【0090】

条件コード：コードは変更されないままである。

#### 【0091】

プログラム例外：

- \* ベクトル・ファシリティがイネーブルにされていないことを示す、データ例外コード (D X C) F E を伴うデータ、ベクトル命令

40

- \* 演算 (z / A r c h i t e c t u r e のためのベクトル・ファシリティがインストールされていない場合)

- \* 指定

- \* トランザクション制限

50

## 【0092】

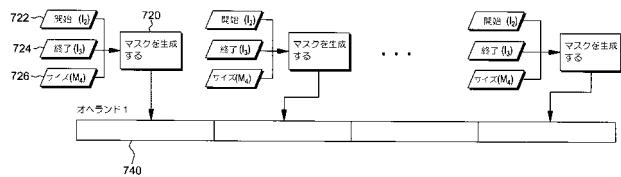

Vector Generate Mask命令の一実施形態に関する更なる詳細が、図17及び図18を参照して説明される。特に、図17は、プロセッサによって実施されるVector Generate Mask命令と関連付けられた論理の一実施形態を示し、図18は、Vector Generate Mask命令の実行の一実施形態を図示するプロック図の一例を示す。

## 【0093】

図17を参照すると、最初に、第1のオペランド内の各要素について、マスクを生成する(ステップ720)。このステップは、第2のオペランド・フィールド内で開始位置(722)として指定された値と、第3のオペランド・フィールド内で終了位置(724)として指定された値と、M<sub>4</sub>フィールド内で指定された要素サイズ(726)とを含む種々の入力を用いる。これらの入力は、マスクを生成し、第1のオペランド(Op1)の、例えば要素0などの選択された要素の位置を埋める(ステップ730)のに用いられる。例えば、第1のオペランド(Op1)の要素0は、複数の位置(例えば、ビット位置)を含み、I<sub>2</sub>内の符号なし整数値が指定する位置で開始し、I<sub>3</sub>内の符号なし整数値が指定する位置で終了し、第1のオペランドの要素0の位置(例えば、ビット)は、1に設定される。他のビット位置は0に設定される。その後、第1のオペランド内に要素があるかどうかについての判断を行う(問い合わせ734)。要素がある場合、処理はステップ720を続行する。他の場合には、処理は完了する(ステップ736)。

## 【0094】

マスクを生成すること及び第1のオペランドを埋めることが、図18に示される。示されるように、入力(例えば、722 - 726)を用いて、第1のオペランドの各要素についてのマスクが生成され(720)、マスクを生成した結果は、第1のオペランドの要素740内に格納される。

## 【0095】

上記で詳細に説明されるのは、ベクトルの各要素についてビットマスクを生成するための命令である。一実施形態において、命令は、開始ビット位置及び終了ビット位置を利用してビットマスクを生成し、このビットマスクは各要素について複製される。命令は、ビット範囲を指定し、範囲内の各ビットは、ベクトル・レジスタの各要素について1に設定されるが、他のビットはゼロに設定される。

## 【0096】

一実施形態において、ビットマスクを生成するための命令を用いることにより、例えば、命令ストリームのキャッシュ・フットプリントを増大させ、必要なマスク数に応じて重要ループにおける待ち時間を増大させる場合があるメモリからビットマスクをロードすることに勝る利点が提供される。

## 【0097】

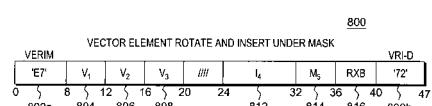

1つの態様に従って提供されるさらに別の命令は、Vector Element Rotate and Insert Under Mask(VERIM)命令であり、その一例が図19に示される。一例において、Vector Element Rotate and Insert Under Mask命令800は、Vector Element Rotate and Insert Under Mask操作を示すオペコード・フィールド802a(例えば、ビット0 - 7)、802b(例えば、ビット40 - 47)と、第1のベクトル・レジスタ(V<sub>1</sub>)を指示するのに用いられる第1のベクトル・レジスタ・フィールド804(例えば、ビット8 - 11)と、第2のベクトル・レジスタ(V<sub>2</sub>)を指示するのに用いられる第2のベクトル・レジスタ・フィールド806(例えば、ビット12 - 15)と、第3のベクトル・レジスタ(V<sub>3</sub>)を指示するのに用いられる第3のベクトル・レジスタ・フィールド808(例えば、ビット16 - 19)と、例えば各要素をローテートするためのビット数を指定する符号なし2進整数を含む即値フィールド(I<sub>4</sub>)812(例えば、ビット24 - 31)と、マスク・フィールド(M<sub>5</sub>)814(例えば、ビット32 - 35)と、RXBフィールド816(例えば、ビット3

10

20

30

40

50

6 - 3 9 )とを含む。フィールド 8 0 4 - 8 1 6 の各々は、一例において、オペコード・フィールドから分離し、独立している。さらに、一実施形態において、これらのフィールド 8 0 4 - 8 1 6 は互いに分離し、独立しているが、他の実施形態においては、1つより多くのフィールドを組み合わせてもよい。

#### 【0098】

一例において、オペコード・フィールド 8 0 2 a により指示されるオペコードの選択されたビット（例えば、最初の 2 ビット）は、命令の長さを指定する。この特定の例において、選択されたビットは、長さが 3 ハーフワードであることを示す。さらに、命令の形式は、拡張されたオペコード・フィールドを伴うベクトル・レジスタ・アンド即値操作である。ベクトル（V）フィールドの各々は、R X B によって指定されたその対応する拡張ビットと共に、ベクトル・レジスタを指示する。特に、ベクトル・レジスタについては、オペランドを含むレジスタが、例えば、対応するレジスタ拡張ビット（R X B）を最上位ビットとして付加したレジスタ・フィールドの 4 ビット・フィールドを用いて指定される。

10

#### 【0099】

M<sub>5</sub> フィールドは、要素サイズ制御（E S）を指定する。要素サイズ制御は、ベクトル・レジスタ・オペランド内の要素のサイズを指定する。一例において、M<sub>5</sub> フィールドのビット 0 はバイトを指定し、ビット 1 はハーフワード（例えば、2 バイト）を指定し、ビット 2 はワード（例えば、4 バイト、別名フルワード）を指定し、ビット 3 はダブルワードを指定する。

20

#### 【0100】

**V e c t o r E l e m e n t R o t a t e a n d I n s e r t U n d e r M a s k** 命令の一実施形態の実行において、第 2 のオペランドの各要素は、第 4 のオペランドによって指定されたビット数だけ左にローテートされる。要素の左端のビット位置から外にシフトされた各ビットは、要素の右端のビット位置に再び入る。第 3 のオペランドは、各要素内にマスクを含む。第 3 のオペランド内の 1 である各ビットについて、第 2 のオペランド内のローテートされた要素の対応するビットが、第 1 のオペランド内の対応するビットに置き換わる。つまり、ローテートされた要素の対応するビットの値が、第 1 のオペランド内の対応するビットの値に置き換わる。第 3 のオペランド内の 0 である各ビットについて、第 1 のオペランドの対応するビットは変更されないままである。第 1 のオペランドが第 2 のオペランド又は第 3 のオペランドのいずれかと同一である場合を除いて、第 2 のオペランド及び第 3 のオペランドは変更されないままである。

30

#### 【0101】

第 4 のオペランドは、例えば、第 2 のオペランド内の各要素をローテートするビット数を指定する、符号なし 2 進整数である。この値が指定された要素サイズのビット数より大きい場合、要素内のビット数を法として、値が減らされる。

#### 【0102】

一例において、第 3 のオペランドに含まれるマスクは、本明細書で説明される V G M 命令を用いて生成される。

#### 【0103】

条件コード：コードは変更されないままである。

40

#### 【0104】

プログラム例外：

- \* ベクトル・ファシリティがイネーブルにされていないことを示す、データ例外コード（D X C）F E を伴うデータ、ベクトル命令

- \* 演算（z / A r c h i t e c t u r e のためのベクトル・ファシリティがインストールされていない場合）

- \* 指定

- \* トランザクション制限

#### 【0105】

プログラミング上の注意：

50

1. V E R I MとV G Mとの組み合わせを用いて、R o t a t e a n d I n s e r t S e l e c t e d B i t s命令の完全な機能を達成することができる。

2. I<sub>4</sub>フィールドのビットは、各要素を左にローテートするためのビット数を指定する符号なし2進整数を含むように定義されるが、右へのローテート量を効果的に指定する負の数をコード化してもよい。

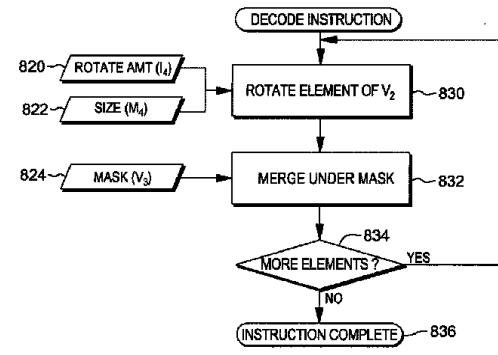

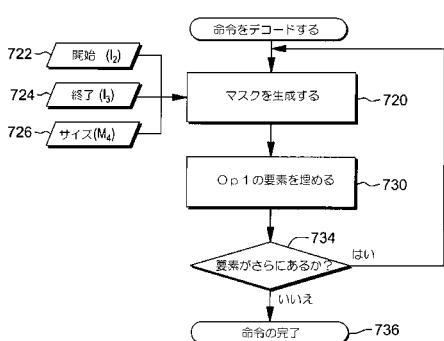

#### 【0106】

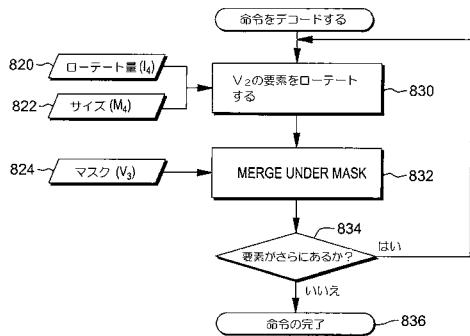

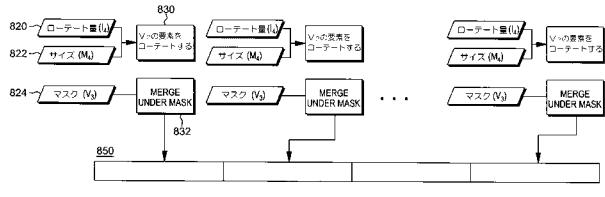

V e c t o r E l e m e n t R o t a t e a n d I n s e r t U n d e r M a s k命令の実行に関する更なる詳細が、図20及び図21を参照して説明される。特に、図20は、プロセッサによって実施されるV e c t o r E l e m e n t R o t a t e a n d I n s e r t U n d e r M a s k命令と関連付けられた論理の一実施形態を示し、図21は、V e c t o r E l e m e n t R o t a t e a n d I n s e r t U n d e r M a s k命令の実行の一例を図形的に示す。10

#### 【0107】

図20を参照すると、第2のオペランドの選択された要素が、第4のオペランドで指定された量(820)だけローテートされる(ステップ830)。第4のオペランドで指定された値が要素サイズ(822)で指定されたビット数より大きい場合、その値は要素内のビット数を法として減らされる。

#### 【0108】

要素のビットをローテートさせた後、m e r g e u n d e r m a s kを実施する(ステップ832)。例えば、第3のオペランド内の1である各ビット(824)について、第2のオペランド内のローテートされた要素の対応するビットが、第1のオペランド内の対応するビットに置き換わる。20

#### 【0109】

その後、ローテートされるべき要素がさらにあるかどうかについての判断が行われる(問い合わせ834)。ローテートされるべき要素がさらにある場合、処理はステップ830を続行する。そうでない場合には、処理は完了する(ステップ836)。

#### 【0110】

図21を参照すると、示されるように、第2のオペランドの要素は、入力820及び822に基づいてローテートされる(830)。さらに、入力824を用いて、m e r g e u n d e r m a s k(832)を実施する。出力は、第1のオペランド850に与えられる。30

#### 【0111】

上述したのは、V e c t o r E l e m e n t R o t a t e a n d I n s e r t U n d e r M a s k命令の一例である。この命令は、定められたビット数だけ、選択されたオペランド内の要素をローテートするのに用いられる。ビットが指定されるが、さらに別の実施形態においては、位置の数だけ要素をローテートさせることができ、位置は、ビット以外であってもよい。さらに、命令は、異なる要素サイズと共に用いることができる。

#### 【0112】

一例として、こうした命令は、テーブル・ルックアップの数から特定のビット範囲を選択するために用いられる。40

#### 【0113】

特定のベクトル命令又は他のS I M D操作の実行の際、例外が発生することがある。S I M D操作において例外が発生した場合、通常、ベクトル・レジスタのどの要素が例外を引き起こしたのかは未知である。どの要素が例外を引き起こしたのかを判断するために、ソフトウェア割り込みハンドラは、各要素を抽出し、スカラー・モードで計算をやり直さなければならない。しかしながら、一様によれば、マシン(例えば、プロセッサ)がベクトル演算に起因するプログラム割り込みを処理するとき、例えば、例外を引き起こしたベクトル内の最小インデックス付き要素を示す要素インデックスが報告される。そして、ソフトウェア割り込みハンドラは、即座に当該要素にスキップし、いずれかの必要な又は50

所望のアクションを実施することができる。

#### 【0114】

例えば、一実施形態において、ベクトル・データ例外がプログラム割り込みを発生させた場合、ベクトル例外コード（VXC）が、例えば実メモリ位置（例えば、位置147（X 93））に格納され、ゼロが、実メモリ位置144 - 146（X 90 - X 92）に格納される。さらに別の実施形態において、指定された制御レジスタ（例えば、CR0）の指定されたビット（例えば、ビット45）が1である場合、VXCは、浮動小数点制御レジスタのデータ例外コード（DXC）フィールドにも入れられる。制御レジスタ0のビット45が0であり、制御レジスタ0のビット46が1である場合、FPCレジスタのDXC、及び、位置147（X 93）におけるストレージのコンテンツは予測不能である。10

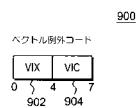

#### 【0115】

一実施形態において、VXCは、種々のタイプのベクトル浮動小数点例外を区別して、どの要素が例外を引き起こしたのかを示す。一例において、図22に示されるように、ベクトル例外コード900が、ベクトル・インデックス（VIX）902と、ベクトル割り込みコード（VIC）904とを含む。一例において、ベクトル・インデックスは、ベクトル例外コードのビット0 - 3を含み、その値は、例外を認識した選択されたベクトル・レジスタの左端の要素のインデックスである。さらに、ベクトル割り込みコードは、ベクトル例外コードのビット4 - 7に含まれ、例として以下の値を有する。

|         |                 |

|---------|-----------------|

| 0 0 0 1 | I E E E 無効操作    |

| 0 0 1 0 | I E E E ゼロ除算    |

| 0 0 1 1 | I E E E オーバーフロー |

| 0 1 0 0 | I E E E アンダーフロー |

| 0 1 0 1 | I E E E 不正確     |

#### 【0116】

さらに別の実施形態において、VXCは、例外を引き起こした要素のベクトル・インデックス又は他の位置インジケータのみを含む。

#### 【0117】

一実施形態において、VXCは、例えば以下の命令を含む多数の命令：即ち、例として、Vector Floating Point (FP) Add、Vector FP Compare Scalar、Vector FP Compare Equal、Vector FP Compare High or Equal、Vector FP Convert From Fixed 64-Bit、Vector FP Convert From Logical 64-Bit、Vector FP Convert to Fixed 64-Bit、Vector FP Convert to Logical 64-Bit、Vector FP Divide、Vector Load FP Integer、Vector FP Load Lengthened、Vector FP Load Rounded、Vector FP Multiply、Vector FP Multiply and Add、Vector FP Multiple and Subtract、Vector FP Square Root、及びVector FP Subtract、並びに他のタイプのベクトル浮動小数点命令及び/又は他の命令によって設定することができる。3040

#### 【0118】

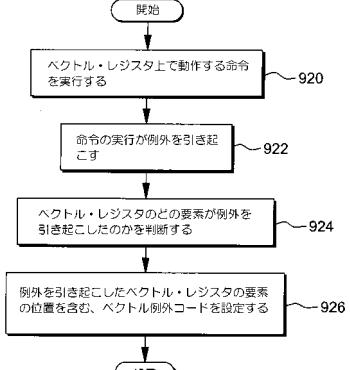

ベクトル例外コードの設定に関する更なる詳細が、図23を参照して説明される。一実施形態において、コンピューティング環境のプロセッサがこの論理を実施する。

#### 【0119】

図23を参照すると、最初に、上に列挙した命令の1つ又は別の命令などの、ベクトル・レジスタ上で動作する命令が実行される（ステップ920）。命令の実行の際、例外条件が引き起こされる（ステップ922）。一例において、例外条件は割り込みを発生させる。ベクトル・レジスタのどの要素が例外を引き起こしたかについての判断が行われる（50

ステップ924)。例えば、ベクトル・レジスタの1つ又は複数の要素の計算を実施しているプロセッサの1つ又は複数のハードウェア・ユニットが例外を判断し、信号を出す。例えば、複数のハードウェア・ユニットがベクトル・レジスタの複数の要素の計算を並行して実施し、要素の1つ又は複数の処理中に例外が引き起こされた場合、例外を引き起こした処理を実施しているハードウェア・ユニットは、例外条件、並びに処理していた要素の表示を信号で送る。さらに別の実施形態においては、ベクトルの要素が逐次的に処理され、要素の処理中に例外に遭遇した場合、ハードウェアは、例外が発生したときにシーケンス内のどの要素にとりかかっていたかを示す。

#### 【0120】

例外の信号送信に基づいて、ベクトル例外コードが設定される(ステップ926)。これは、例えば、例外を引き起こしたベクトル・レジスタ内の要素の位置、並びに割り込みコードを示すことを含む。

#### 【0121】

上記で詳細に説明したのは、効率的なベクトル例外処理を提供するベクトル例外コードである。一例において、マシンがベクトル演算に起因するプログラム割り込みを処理する際、例外を引き起こしたベクトル・レジスタ内の最小インデックス付き要素を示す要素インデックスが報告される。特定の例として、ベクトル加算(`vector add`)が実施されており、ベクトル・レジスタ毎に、 $A_0 + B_0$ 及び $A_1 + B_1$ を与える2つの要素があり、且つ、 $A_1 + B_1$ ではなく $A_0 + B_0$ に関する不正確の結果を受信した場合、`VIX`は0に設定され、`VIC`は0101に等しくなるように設定される。さらに別の例においては、 $A_0 + B_0$ は例外を受信しないが、 $A_1 + B_1$ は例外を受信した場合、`VIX`は1に等しくなるように設定される(`VIC = 0101`)。両方とも例外を引き起した場合、それが左端インデックス付き位置であるので、`VIX`は0に設定され、`VIC = 0101`である。

#### 【0122】

上記で詳細に説明したのは、種々のベクトル命令、並びに、ベクトル・レジスタ内の例外の位置を示すベクトル例外コードである。与えられたフロー図では、幾つかの処理は逐次的に見えることがあるが、1つ又は複数の実施形態においては、要素は並行処理され、従って、例えば、処理されるべき要素がさらにあるかどうかをチェックする必要がないことがある。他の多くの変形も可能である。

#### 【0123】

付加的に、さらに別の実施形態において、命令の1つ又は複数のフィールドのコンテンツを、例として、汎用レジスタ、メモリ、(要素ごとに異なる)ベクトル・レジスタの要素内に、又は、アドレス計算から提供することができる。コンテンツは、命令の明示的オペランドとして、又は、暗黙オペランド若しくは入力として含ませることができる。さらに、1つ又は複数の命令がより少ない数のオペランド又は入力を用いることがあり、代わりに、1つ又は複数のオペランドを複数の操作又はステップに用いることもある。

#### 【0124】

さらに、本明細書で説明されたように、命令のフィールドに要素サイズ制御を含む代わりに、要素サイズ制御を他の手法で提供することができる。付加的に、要素サイズはオペコードによって指示することができる。例えば、命令の特定のオペコードは、操作、並びに要素サイズ等を指示する。

#### 【0125】

本明細書において、メモリ、主メモリ、ストレージ、及び主ストレージは、明示的に又は文脈によって特に断りのない限り、交換可能に使用される。

#### 【0126】

当業者であれば理解するように、態様は、システム、方法又はコンピュータ・プログラムとして具体化することができる。従って、態様は、完全にハードウェアの実施形態、完全にソフトウェアの実施形態(ファームウェア、常駐ソフトウェア、マイクロコード等を含む)、又はソフトウェアの態様とハードウェアの態様とを組み合わせた実施形態の形態

10

20

30

40

50

をとることができ、本明細書においては、これらは全て、一般的に「回路」、「モジュール」又は「システム」と呼ぶことがある。さらに、態様は、媒体内に具体化されたコンピュータ可読プログラム・コードを有する、1つ又は複数のコンピュータ可読媒体内に具体化されたコンピュータ・プログラムの形態をとることができる。

#### 【0127】

1つ又は複数のコンピュータ可読媒体のいずれかの組み合わせを用いることもできる。コンピュータ可読媒体は、コンピュータ可読ストレージ媒体とすることができます。コンピュータ可読ストレージ媒体は、例えば、これらに限定されるものではないが、電子、磁気、光学、電磁気、赤外線若しくは半導体のシステム、装置若しくはデバイス、又はこれらのいずれかの適切な組み合わせとすることができます。コンピュータ可読ストレージ媒体のより具体的な例（非網羅的なリスト）として、以下のもの、即ち、1つ又は複数の配線を有する電気的接続、ポータブル・コンピュータ・ディスクケット、ハード・ディスク、ランダム・アクセス・メモリ（RAM）、読み出し専用メモリ（ROM）、消去可能なプログラム可能読み出し専用メモリ（EPROM又はフラッシュ・メモリ）、光ファイバ、ポータブル・コンパクト・ディスク型読み出し専用メモリ（CD-ROM）、光記憶装置、磁気記憶装置、又は上記のいずれかの適切な組み合わせが挙げられる。本明細書の文脈においては、コンピュータ可読ストレージ媒体は、命令実行システム、装置若しくはデバイスによって又はそれらと関連して用いるためのプログラムを収容又は格納することが可能な、任意の有形媒体とすることができます。

10

#### 【0128】

図24を参照すると、一例において、コンピュータ・プログラム製品1000は、例えば、本発明の1つ又は複数の態様を提供し、容易にするように、その上にコンピュータ可読プログラム・コード手段又は論理1004を格納するための、1つ又は複数の一時的でないコンピュータ可読ストレージ媒体1002を含む。

20

#### 【0129】

コンピュータ可読媒体上に具体化されたプログラム・コードは、これらに限定されるものではないが、無線、有線、光ファイバ・ケーブル、RF等、又はこれらの任意の適切な組み合わせを含む、適切な媒体を用いて伝送することができる。

#### 【0130】

態様のための動作を実行するためのコンピュータ・プログラム・コードは、Java、Smalltalk（登録商標）、C++などのオブジェクト指向型プログラミング言語、及び、「C」プログラミング言語などの従来の手続き型プログラミング言語、アセンブラ、又は類似のプログラミング言語を含む、1つ又は複数のプログラミング言語の任意の組み合わせで記述することができる。プログラム・コードは、全体をユーザのコンピュータ上で実行することができ、独立型ソフトウェア・パッケージとして部分的にユーザのコンピュータ上で実行することができ、一部をユーザのコンピュータ上で実行し、一部を遠隔コンピュータ上で実行することができ、又は全体を遠隔コンピュータ若しくはサーバ上で実行することができる。後者のシナリオにおいては、遠隔コンピュータは、ローカル・エリア・ネットワーク（LAN）若しくは広域ネットワーク（WAN）を含むいずれかのタイプのネットワークを通じてユーザのコンピュータに接続されるか、又は、若しくはコンバージド・ネットワークを含むがこれらに限定されるものではない、いずれかのタイプのネットワーク若しくは通信システムを通じてユーザのコンピュータに接続することができ、又は（例えば、インターネット・サービス・プロバイダを用いたインターネットを通じて）外部コンピュータへの接続をなすことができる。

30

40

#### 【0131】

態様は、本明細書において、1つ又は複数の実施形態による方法、装置（システム）及びコンピュータ・プログラムのフローチャート図及び/又はブロック図を参照して説明される。フローチャート図及び/又はブロック図の各ブロック、並びにフローチャート図及び/又はブロック図におけるブロックの組み合わせは、コンピュータ・プログラム命令によって実装できることが理解されるであろう。これらのコンピュータ・プログラム命令を

50

、汎用コンピュータ、専用コンピュータ、又は他のプログラム可能データ処理装置のプロセッサに与えて、マシンを製造し、その結果、コンピュータ又は他のプログラム可能データ処理装置のプロセッサによって実行される命令が、フローチャート及び／又はブロック図の1つ又は複数のブロックにおいて指定された機能／動作を実装するための手段を生成するようにすることができる。

#### 【0132】

これらのコンピュータ・プログラム命令を、コンピュータ、他のプログラム可能データ処理装置、又は他のデバイスを特定の方式で機能せしめるように指示することができるコンピュータ可読媒体内に格納し、その結果、そのコンピュータ可読媒体内に格納された命令が、フローチャート及び／又はブロック図の1つ又は複数のブロックにおいて指定された機能／動作を実装する命令を含む製品を製造するようにすることもできる。10

#### 【0133】

コンピュータ・プログラム命令を、コンピュータ、他のプログラム可能データ処理装置、又は他のデバイス上にロードして、そのコンピュータ、他のプログラム可能装置、又は他のデバイス上で一連の動作ステップを行わせてコンピュータ実装プロセスを生成し、それにより、そのコンピュータ又は他のプログラム可能装置上で実行される命令が、フローチャート及び／又はブロック図の1つ又は複数のブロックにおいて指定された機能／動作を実施するためのプロセスを提供するようにすることもできる。

#### 【0134】

画面内のフローチャート及びブロック図は、種々の実施形態による、システム、方法及びコンピュータ・プログラムの可能な実装のアーキテクチャ、機能及び動作を示す。この点に関して、フローチャート又はブロック図内の各ブロックは、指定された論理機能を実行するための1つ又は複数の実行可能な命令を含む、モジュール、セグメント又はコードの一部を表すことができる。幾つかの代替的な実施において、ブロック内に記された機能は、図面内に記された順序とは異なる順序で行われることがあることにも留意すべきである。例えば、連続して示された2つのブロックは、関与する機能に応じて、実際には実質的に同時に実行されることもあり、又はこれらのブロックは、ときには逆の順序で実行されることもある。ブロック図及び／又はフローチャート図の各ブロック、並びにブロック図及び／又はフローチャート図内のブロックの組み合わせは、指定された機能又は動作を行う専用ハードウェアベースのシステム、又は専用ハードウェアとコンピュータ命令との組み合わせによって実装することができることにも留意されたい。20

#### 【0135】

上記に加えて、1つ又は複数の態様は、顧客環境の管理を提供するサービス・プロバイダによって供与、提供、配置、管理、サービス等を行うことができる。例えば、サービス・プロバイダは、1又は複数の顧客のために1つ又は複数の態様を実施するコンピュータ・コード及び／又はコンピュータ・インフラストラクチャの作成、保守、サポート等を行うことができる。見返りに、サービス・プロバイダは、例として、予約申し込み及び／又は報酬契約の下で顧客から支払いを受けることができる。付加的に又は代替的に、サービス・プロバイダは、1又は複数の第三者に対する広告コンテンツの販売から支払いを受けることができる。30

#### 【0136】

1つの態様において、1つ又は複数の態様を実施するために、アプリケーションを配置することができる。一例として、アプリケーションの配置は、1つ又は複数の態様を実施するように動作可能なコンピュータ・インフラストラクチャを提供することを含む。

#### 【0137】

更に別の態様として、コンピュータ可読コードをコンピュータ・システムに統合することを含む、コンピュータ・インフラストラクチャを配置することができ、そこでは、コードは、コンピューティング・システムと協働して、1つ又は複数の態様を実施することができる。

#### 【0138】

10

20

30

40

50

更に別の態様として、コンピュータ可読コードをコンピュータ・システムに統合することを含む、プロセスを提供することができる。コンピュータ・システムは、コンピュータ可読媒体を含み、ここで、コンピュータ媒体は、1つ又は複数の態様を含む。コードは、コンピュータ・システムと協働して、1つ又は複数の態様を実施することができる。

#### 【0139】

種々の実施形態が上述されたが、これらは例にすぎない。例えば、他のアーキテクチャのコンピューティング環境は、1つ又は複数の態様を組み込み、使用することができる。さらに、他のサイズのベクトルを使用することができ、1つ又は複数の態様から逸脱することなく、命令への変更をなすことができる。加えて、他の実施形態においては、ベクトル・オペランドは、ベクトル・レジスタの代わりに、メモリ位置とすることができます。他の変形も可能である。

10

#### 【0140】

さらに、他のタイプのコンピューティング環境は、1つ又は複数の態様から利益を得ることができる。一例として、プログラム・コードを格納及び／又は実行するのに適しており、システム・バスを介してメモリ要素に直接又は間接的に結合された少なくとも2つのプロセッサを含む、データ処理システムを使用することができる。メモリ要素は、例えば、プログラム・コードの実際の実行中に用いられるローカル・メモリ、大容量記憶装置、及び実行中に大容量記憶装置からコードを取り出さなければならない回数を減らすために少なくとも幾つかのプログラム・コードの一時的なストレージを提供するキャッシュ・メモリを含む。

20

#### 【0141】

入力／出力即ちI／Oデバイス（これらに限定されるものではないが、キーボード、ディスプレイ、ポインティング・デバイス、D A S D、テープ、C D、D V D、サムドライブ及び他のメモリ媒体等）は、直接システムに結合することもでき、又は介在するI／Oコントローラを介してシステムに結合することができる。ネットワーク・アダプタをシステムに結合させて、データ処理システムが、介在する私的ネットワーク又は公衆ネットワークを通じて他のデータ処理システム又は遠隔プリンタ若しくはストレージ・デバイスに結合できるようにすることもできる。モデム、ケーブル・モデム及びイーサネット・カードは、ネットワーク・アダプタの利用可能なタイプのうちのほんの数例である。

30

#### 【0142】

図25を参照すると、1つ又は複数の態様を実装するためのホスト・コンピュータ・システム5000の代表的なコンポーネントが描かれる。代表的なホスト・コンピュータ5000は、コンピュータ・メモリ（即ち、中央ストレージ）5002と通信する1つ又は複数のC P U 5001と、他のコンピュータ若しくはS A Nなどとの通信のためのストレージ媒体デバイス5011及びネットワーク5010に対するI／Oインターフェースとを含む。C P U 5001は、アーキテクチャ化命令セット及びアーキテクチャ化機能を有するアーキテクチャに準拠している。C P U 5001は、プログラム・アドレス（仮想アドレス）をメモリの実アドレスに変換するための動的アドレス変換（D A T）5003を有することができる。D A Tは、典型的には、変換をキャッシュに入れるための変換ルックアサイド・バッファ（T L B）5007を含み、後でコンピュータ・メモリ5002のロックにアクセスしたときにアドレス変換による遅延を必要とせずに済むように変換をキャッシュに入れるための、変換ルックアサイド・バッファ（T L B）5007を含む。典型的には、キャッシュ5009は、コンピュータ・メモリ5002とプロセッサ5001との間で用いられる。キャッシュ5009は、1つより多くのC P Uが利用できる大型キャッシュと、大型キャッシュと各C P Uとの間のより小型で高速な（下位レベルの）キャッシュとを有する階層構造とすることができます。幾つかの実施において、下位レベルのキャッシュは、命令フェッチ及びデータ・アクセスのための個別の下位レベル・キャッシュを提供するように分割される。一実施形態において、命令は、命令フェッチ・ユニット5004によりメモリ5002からキャッシュ5009を介してフェッチされる。命令は、命令デコード・ユニット5006内でデコードされ（幾つかの実施形態においては他の

40

50

命令と共に)、命令実行ユニット 5008 にディスパッチされる。典型的には、幾つかの実行ユニット 5008、例えば、算術演算実行ユニット、浮動小数点実行ユニット及び分岐命令実行ユニットが用いられる。命令は、実行ユニットにより、必要に応じて命令が指定するレジスタ又はメモリからのオペランドにアクセスすることにより実行される。オペラントがメモリ 5002 からアクセスされる(ロードされる又はストアされる)場合には、典型的には、ロード/ストア・ユニット 5005 が、実行されている命令の制御下でアクセスを取り扱う。命令は、ハードウェア回路若しくは内部マイクロコード(ファームウェア)、又はこの両方の組み合わせにより実行することができる。

#### 【0143】

既述のように、コンピュータ・システムは、ローカル(又は、主)ストレージ内の情報、並びにアドレス指定、保護、並びに参照及び変更記録を含む。アドレス指定の幾つかの様態は、アドレスの形式、アドレス空間の概念、アドレスの種々のタイプ及び1つのタイプのアドレスが別のタイプのアドレスに変換される方法を含む。主ストレージの一部は、恒久的に割り当てられたストレージ位置を含む。主ストレージは、システムに、直接アドレス可能なデータの高速アクセス・ストレージを提供する。データ及びプログラムの両方とも、これらが処理される前に(入力デバイスから)主ストレージにロードされる。

#### 【0144】

主ストレージは、キャッシュと呼ばれることがある、1つ又は複数のより小型の高速アクセス・バッファ・ストレージを含むことができる。キャッシュは、典型的には、CPU 又は I/O プロセッサと物理的に関連付けられる。物理的構造の、性能を除いた効果及び別個のストレージ媒体の使用は、一般に、プログラムにより観察することができない。

#### 【0145】

命令及びデータ・オペラントに対して、別個のキャッシュを維持することができる。キャッシュ内の情報は、キャッシュ・ブロック又はキャッシュ・ライン(又は、簡単に言えばライン)と呼ばれる整数境界上の連続バイトで維持される。モデルは、キャッシュ・ラインのサイズをバイト単位で戻す EXTRACT CACHE ATTRIBUTE 命令を提供することができる。モデルはまた、データ又は命令キャッシュへのストレージの prefetch 又はキャッシュからのデータの解放を行う PREFETCH DATA 及び PREFETCH DATA RELATIVE LONG 命令も提供することができる。

#### 【0146】

ストレージは、ビットの水平の長い文字列として見ることができる。殆どの操作では、ストレージへのアクセスは、左から右への順で進行する。ビットの文字列は、8ビット単位で細分される。この8ビットの単位はバイトと呼ばれ、これは全ての情報形式の基本構成単位である。ストレージ内の各々のバイト位置は、負でない固有の整数により識別され、この整数がバイト位置のアドレス、即ち、簡単にバイト・アドレスである。隣接するバイト位置は連続するアドレスを有し、左端の 0 から始まって左から右へ順に進行する。アドレスは、符号なしの2進整数であり、24ビット、31ビット又は64ビットである。

#### 【0147】

情報は、ストレージと CPU 又はチャネル・サブシステムとの間で、一度に1バイトずつ、又は1グループ分のバイトで伝送される。特に断りのない限り、例えば z / Architectureにおいて、ストレージ内のバイト・グループは、グループの左端のバイトによりアドレス指定される。グループ内のバイト数は、実行される操作により暗黙的に決定される場合、又は明示的に決定される場合がある。CPU 操作に使用される場合、バイト・グループはフィールドと呼ばれる。各々のバイト・グループ内において、例えば z / Architectureにおいて、ビットは、左から右の順に番号付けされる。z / アーキテクチャにおいて、左端のビットを「最上位」ビットと呼び、右端のビットを「最下位」ビットと呼ぶことがある。しかしながら、ビット番号はストレージ・アドレスではない。アドレス指定できるのはバイトだけである。ストレージ内の1つのバイトの個々のビットに対して操作を行うためには、そのバイト全体にアクセスされる。1バイトの中のビットには、(z / Architectureにおいて)左から右に 0 から 7 までの番号

10

20

30

40

50

が付けられる。1つのアドレスの中のビットには、24ビット・アドレスの場合は、8-31若しくは40-63の番号が付けられ、又は31ビット・アドレスの場合は、1-31若しくは33-63の番号が付けられ、又は64ビット・アドレスの場合は、0-63の番号が付けられる。複数バイトの任意の他の固定長形式において、形式を構成するビットは、0から始まって連續的に番号が付けられる。エラー検出のため、また好ましくは訂正のため、各々のバイト又はバイト・グループと共に1又は複数の検査ビットを伝送することができる。こうした検査ビットは、マシンにより自動的に生成され、プログラムにより直接制御することはできない。ストレージ容量は、バイト数で表現される。ストレージ・オペランド・フィールドの長さが命令のオペコードで暗黙指定される場合、そのフィールドは固定長を有するといわれ、この長さは1バイト、2バイト、4バイト、8バイト又は16バイトとすることができます。幾つかの命令に対しては、より大きいフィールドが暗黙指定される。ストレージ・オペランドの長さが暗黙指定されず、明示的に指定される場合は、そのフィールドは可変長を有するといわれる。可変長オペランドは、1バイトのインクリメント(又は幾つかの命令では、2バイトの倍数又は他の倍数で)で長さが変化し得る。情報がストレージ内に配置されると、ストレージへの物理的バスの幅が格納されるフィールドの長さより大きい場合であっても、指定したフィールドに含まれているバイト位置のコンテンツのみが置き換えられる。

10

#### 【0148】

情報の特定の単位は、ストレージ内の整数境界上にあるべきである。境界は、そのストレージ・アドレスがバイトでの単位の長さの倍数である場合に、情報の単位に対して整数であると呼ばれる。整数境界上にある2バイト、4バイト、8バイト、及び16バイトのフィールドには、特別な名称が与えられる。ハーフワードは、2バイト境界上にある2個の連続したバイトのグループであり、これは命令の基本構成単位である。ワードは、4バイト境界上にある4個の連続したバイトのグループである。ダブルワードは、8バイト境界上にある8個の連続したバイトのグループである。クワッドワードは、16バイト境界上にある16個の連続したバイトのグループである。ストレージ・アドレスが、ハーフワード、ワード、ダブルワード、及びクワッドワードを指定するとき、そのアドレスの2進表現では、それぞれ1個、2個、3個、又は4個の右端の0ビットを含む。命令は、2バイト整数境界上にあるべきである。殆どの命令のストレージ・オペランドは、境界位置合わせ要件を有さない。

20

#### 【0149】

命令及びデータ・オペランドに対して別個のキャッシュを実装するデバイスにおいては、ストアが後にフェッチされる命令を変更するかどうかに関係なく、プログラムが、後にフェッチされるキャッシュ・ラインに格納される場合、著しい遅延が生じ得る。

30

#### 【0150】

一実施形態において、本発明は、ソフトウェア(ライセンス内部コード、ファームウェア、マイクロコード、ミリコード、ピココードなどとも呼ばれる場合があるが、そのいずれも1つ又は複数の態様と整合性がある)により実施することができる。図25を参照すると、1つ又は複数の態様を具体化するソフトウェア・プログラム・コードは、CD-ROMドライブ、テープドライブ、又はハードドライブといった長期ストレージ媒体デバイス5011から、ホスト・システム5000のプロセッサ5001によりアクセスすることができる。ソフトウェア・プログラム・コードは、ディスクケット、ハードドライブ、又はCD-ROMのようなデータ処理システムと共に使用するための種々の周知の媒体のいずれかの上で具体化することができる。コードは、こうした媒体上に分散させても、又はコンピュータ・メモリ5002からユーザに分散させても、又はこうした他のシステムのユーザが使用するために、ネットワーク5010上の1つのコンピュータ・システムのストレージから他のコンピュータ・システムに分散させてもよい。

40

#### 【0151】

ソフトウェア・プログラム・コードは、種々のコンピュータ・コンポーネント及び1つ又は複数のアプリケーション・プログラムの機能及び相互作用を制御するオペレーティン

50

グ・システムを含む。プログラム・コードは、通常、ストレージ媒体デバイス 5011 から相対的により高速のコンピュータ・ストレージ 5002 にページングされ、そこでプロセッサ 5001 による処理のために利用可能になる。ソフトウェア・プログラム・コードをメモリ内、物理的媒体上で具体化し、及び / 又は、ネットワークを介してソフトウェア・コードを配布する技術及び方法は周知であり、ここではこれ以上論じない。プログラム・コードは、有形の媒体（これらに限定されるものではないが、電子メモリ・モジュール（RAM）、フラッシュ・メモリ、コンパクト・ディスク（CD）、DVD、磁気テープ等）上に作成され格納されたとき、「コンピュータ・プログラム」と呼ばれることが多い。コンピュータ・プログラム媒体は、典型的には、処理回路による実行のために、好ましくはコンピュータ・システム内の処理回路によって読み取り可能である。

10

#### 【0152】

図 26 は、1つ又は複数の態様を実施できる代表的なワークステーション又はサーバ・ハードウェア・システムを示す。図 26 のシステム 5020 は、随意的な周辺機器を含む、パーソナル・コンピュータ、ワークステーション、又はサーバなどの代表的なベース・コンピュータ・システム 5021 を含む。ベース・コンピュータ・システム 5021 は、1つ又は複数のプロセッサ 5026 と、周知の技術に従ってプロセッサ 5026 とシステム 5021 の他のコンポーネントを接続し、これらの間の通信を可能にするために用いられるバスとを含む。バスは、プロセッサ 5026 を、ハードドライブ（例えば、磁気媒体、CD、DVD 及びフラッシュ・メモリのいずれかを含む）又はテープドライブを含むことができる、メモリ 5025 及び長期ストレージ 5027 に接続する。システム 5021 はまた、バスを介して、マイクロプロセッサ 5026 を、キーボード 5024、マウス 5023、プリンタ / スキャナ 5030、及び / 又はタッチ・センシティブ・スクリーン、デジタル化された入力パッド等のいずれかのユーザ・インターフェース機器と接続することができる他のインターフェース機器といった、1つ又は複数のインターフェース機器に接続する、ユーザ・インターフェース・アダプタを含むこともできる。バスはまた、ディスプレイ・アダプタを介して、LCD スクリーン又はモニタなどのディスプレイ装置 5022 をマイクロプロセッサ 5026 にも接続する。

20

#### 【0153】

システム 5021 は、ネットワーク 5029 と通信する 5028 ことができるネットワーク・アダプタを介して、他のコンピュータ又はコンピュータ・ネットワークと通信することができる。例示的なネットワーク・アダプタは、通信チャネル、トーカン・リング、イーサネット又はモデムである。代替的に、システム 5021 は、CDPD（セルラー・デジタル・パケット・データ）カードのような無線インターフェースを用いて通信することもできる。システム 5021 は、ローカル・エリア・ネットワーク（LAN）又は広域ネットワーク（WAN）又はシステム 5021 内のこうした他のコンピュータと関連付けることができ、又は、別のコンピュータ等とのクライアント / サーバ構成におけるクライアントとすることができる。これら構成の全て、並びに、適切な通信ハードウェア及びソフトウェアは、当技術分野において周知である。

30

#### 【0154】

図 27 は、1つ又は複数の態様を実施することができるデータ処理ネットワーク 5040 を示す。データ処理ネットワーク 5040 は、各々が複数の個々のワークステーション 5041、5042、5043、5044 を含むことができる、無線ネットワーク及び有線ネットワークのような複数の個々のネットワークを含むことができる。さらに、当業者であれば理解するように、1つ又は複数の LAN を含ませることができ、そこで、LAN は、ホスト・プロセッサに結合された複数のインテリジェント・ワークステーションを含むことができる。

40

#### 【0155】

さらに図 27 を参照すると、ネットワークはまた、ゲートウェイ・コンピュータ（クライアント・サーバ 5046）、又はアプリケーション・サーバ（データ・リポジトリにアクセスすることができ、且つ、ワークステーション 5045 から直接アクセスすることも

50

できる遠隔サーバ 5048) のような、メインフレーム・コンピュータ又はサーバを含むこともできる。ゲートウェイ・コンピュータ 5046 は、各々の個々のネットワークへの入力点のとして働く。ゲートウェイは、1つのネットワーク・プロトコルを別のものに接続するときに必要とされる。ゲートウェイ 5046 は、通信リンクによって別のネットワーク(例えば、インターネット 5047)に結合できることが好ましい。ゲートウェイ 5046 はまた、通信リンクを用いて、1つ又は複数のワークステーション 5041、5042、5043、5044 に直接結合することもできる。ゲートウェイ・コンピュータは、インターナショナル・ビジネス・マシンズ・コーポレーションから入手可能な IBM eServer System z サーバを用いて実装することができる。

## 【0156】

10

図 26 及び図 27 を同時に参照すると、本発明の1つ又は複数の態様を具体化することができるソフトウェア・プログラム・コードには、一般的に、CD-ROM ドライブ又はハードドライブといった長期ストレージ媒体 5027 から、システム 5020 のプロセッサ 5026 によってアクセスすることができる。ソフトウェア・プログラム・コードは、ディスクケット、ハードドライブ、又は CD-ROM といった、データ処理システムと共に用いるための種々の周知の媒体のいずれかの上で具体化することができる。コードは、そのような媒体上で分散させても、又はメモリからユーザ 5050、5051 に分散させても、又は、こうした他のシステムのユーザが用いるために、ネットワーク上の1つのコンピュータ・システムのメモリ若しくはストレージから他のコンピュータ・システムに分散させてもよい。

20

## 【0157】

代替的に、プログラム・コードをメモリ 5025 内で具体化し、プロセッサ・バスを用いてプロセッサ 5026 によってプログラム・コードにアクセスすることができる。このようなプログラム・コードは、種々のコンピュータ・コンポーネント及び1つ又は複数のアプリケーション・プログラム 5032 の機能及び相互作用を制御するオペレーティング・システムを含む。プログラム・コードは、通常、ストレージ媒体 5027 から高速メモリ 5025 にページングされ、そこでプロセッサ 5026 による処理のために利用可能になる。ソフトウェア・プログラム・コードをメモリ内、物理的媒体上で具体化し、及び/又は、ネットワークを介してソフトウェア・コードを配布する技術及び方法は周知であり、ここではこれ以上論じない。プログラム・コードは、有形の媒体(これらに限定されるものではないが、電子メモリ・モジュール(RAM)、フラッシュ・メモリ、コンパクト・ディスク(CD)、DVD、磁気テープなどを含む)に格納されたとき、「コンピュータ・プログラム」と呼ばれることが多い。コンピュータ・プログラム媒体は、典型的には、処理回路による実行のために、好ましくはコンピュータ・システム内の処理回路によって読み取り可能である。

30

## 【0158】

プロセッサが最も容易に利用できるキャッシュ(通常、プロセッサの他のキャッシュよりも高速で小さい)は、最下位(L1 又はレベル1)のキャッシュであり、主ストア(主メモリ)は、最上位レベルのキャッシュ(3つのレベルがある場合には L3)である。最下位レベルのキャッシュは、実行されるマシン命令を保持する命令キャッシュ(I-キャッシュ)と、データ・オペランドを保持するデータ・キャッシュ(D-キャッシュ)とに分割されることが多い。

40

## 【0159】

図 28 を参照すると、プロセッサ 5026 についての例示的なプロセッサの実施形態が示される。典型的には、メモリ・ロックをバッファに入れてプロセッサ性能を向上させるために、1つ又は複数のレベルのキャッシュ 5053 が用いられる。キャッシュ 5053 は、用いられる可能性が高いメモリ・データのキャッシュ・ラインを保持する高速バッファである。典型的なキャッシュ・ラインは、64 バイト、128 バイト、又は 256 バイトのメモリ・データである。データをキャッシュに入れるのではなく、命令をキャッシュに入れるために、別個のキャッシュが用いられることが多い。キャッシュ・コヒーレン

50

ス（メモリ及びキャッシュ内のラインのコピーの同期）は、多くの場合、当技術分野において周知の種々の「スヌープ」アルゴリズムによって与えられる。プロセッサ・システムの主メモリ・ストレージ5025は、キャッシュと呼ばれることが多い。4つのレベルのキャッシュ5053を有するプロセッサ・システムにおいて、主ストレージ5025は、典型的にはより高速であり、且つ、コンピュータ・システムが利用できる不揮発性ストレージ（DASD、テープ等）の一部だけを保持するので、レベル5（L5）のキャッシュと呼ばれることがある。主ストレージ5025は、オペレーティング・システムによって主ストレージ5025との間でページングされるデータのページを「キャッシュに入れる」。

#### 【0160】

プログラム・カウンタ（命令カウンタ）5061は、実行される現行の命令のアドレスを常時監視している。z/Architectureプロセッサのプログラム・カウンタは64ビットであり、従来のアドレッシング制限をサポートするために、31ビット又は24ビットに切り捨てることができる。プログラム・カウンタは、典型的には、コンテキスト・スイッチの際に持続するように、コンピュータのPSW（プログラム状況ワード）内で具体化される。従って、例えば、オペレーティング・システムにより、プログラム・カウンタ値を有する進行中のプログラムに割り込みをかけることが可能である（プログラム環境からオペレーティング・システム環境へのコンテキスト・スイッチ）。プログラムのPSWは、プログラムがアクティブでない間、プログラム・カウンタ値を保持し、オペレーティング・システムが実行されている間、オペレーティング・システムの（PSW内の）プログラム・カウンタが用いられる。典型的には、プログラム・カウンタは、現行の命令のバイト数に等しい量だけインクリメントされる。RISC命令は、典型的には固定長であり、CISC命令は、典型的には可変長である。IBM z/Architectureの命令は、2バイト、4バイト、又は6バイトの長さを有するCISC命令である。例えば、コンテキスト・スイッチ操作又は分岐命令の分岐成立操作により、プログラム・カウンタ5061が変更される。コンテキスト・スイッチ操作において、現行のプログラム・カウンタ値は、実行されるプログラムについての他の状態情報（条件コードのような）と共にプログラム状況ワード内に保存され、実行される新しいプログラム・モジュールの命令を指示する新しいプログラム・カウンタ値がロードされる。分岐成立操作を行い、分岐命令の結果をプログラム・カウンタ5061にロードすることにより、プログラムが判断を下すこと又はプログラム内でループすることを可能にする。

#### 【0161】

典型的には、プロセッサ5026の代わりに命令をフェッチするために、命令フェッチ・ユニット5055が用いられる。フェッチ・ユニットは、「次の順次命令」、分岐成立命令のターゲット命令、又はコンテキスト・スイッチの後のプログラムの最初の命令のいずれかをフェッチする。今日の命令フェッチ・ユニットは、プリフェッチされた命令を用いることができる可能性に基づいて、命令を投機的にプリフェッチするプリフェッチ技術を用いることが多い。例えば、フェッチ・ユニットは、次の順次命令を含む16バイトの命令と、付加的なバイトの更なる順次命令とをフェッチすることができる。

#### 【0162】

次いで、フェッチされた命令が、プロセッサ5026によって実行される。一実施形態において、フェッチされた命令は、フェッチ・ユニットのディスパッチ・ユニット5056に渡される。ディスパッチ・ユニットは命令をデコードし、デコードされた命令についての情報を適切なユニット5057、5058、5060に転送する。実行ユニット5057は、典型的には、命令フェッチ・ユニット5055からデコードされた算術命令についての情報を受け取り、命令のオペコードに従ってオペランドに関する算術演算を行う。オペランドは、好ましくは、メモリ5025、アーキテクチャ化レジスタ5059、又は実行される命令の即値フィールドのいずれかから、実行ユニット5057に与えられる。実行の結果は、格納された場合には、メモリ5025、レジスタ5059、又は他のマシン・ハードウェア（制御レジスタ、PSWレジスタなどのような）内に格納される。

10

20

30

40

50

## 【0163】

プロセッサ 5026 は、典型的には、命令の機能を実行するための 1 つ又は複数の実行ユニット 5057、5058、5060 を有する。図 29 を参照すると、実行ユニット 5057 は、インターフェース論理 5071 を介して、アーキテクチャ化された汎用レジスタ 5059、デコード / ディスパッチ・ユニット 5056、ロード・ストア・ユニット 5060、及び他のプロセッサ・ユニット 5065 と通信することができる。実行ユニット 5057 は、幾つかのレジスタ回路 5067、5068、5069 を用いて、算術論理演算ユニット (ALU) 5066 が動作する情報を保持することができる。ALU は、加算、減算、乗算、及び除算などの算術演算、並びに、論理積、論理和、及び排他的論理和、ローテート及びシフトのような論理関数を実行する。ALU は、設計に依存する専用の演算をサポートすることが好ましい。他の回路は、例えば条件コード及び回復サポート論理を含む、他のアーキテクチャ化ファシリティ 5072 を提供することができる。典型的には、ALU 演算の結果は、出力レジスタ回路 5070 に保持され、この出力レジスタ回路 5070 が、結果を種々の他の処理機能に転送することができる。多数のプロセッサ・ユニットの構成が存在し、本説明は、一実施形態の代表的な理解を与えることのみを意図している。

10

## 【0164】

例えば ADD 命令は、算術及び論理機能を有する実行ユニット 5057 で実行され、一方、例えば浮動小数点命令は、特化された浮動小数点能力を有する浮動小数点実行部で実行される。実行ユニットは、オペランドに対してオペコードが定めた関数を行うことにより、命令が特定したオペランドに対して動作することが好ましい。例えば、ADD 命令は、命令のレジスタ・フィールドによって特定された 2 つのレジスタ 5059 内に見出されるオペランドに対して、実行ユニット 5057 により実行することができる。

20

## 【0165】

実行ユニット 5057 は、2 つのオペランドに対して算術加算を実行し、結果を第 3 オペランドに格納し、ここで第 3 オペランドは、第 3 のレジスタであっても又は 2 つのソース・レジスタのいずれかであってもよい。実行ユニットは、シフト、ローテート、論理積、論理和、及び排他的論理和のような種々の論理関数、並びに、加算、減算、乗算、除法のいずれかを含む、種々の代数関数を実行することができる算術論理演算ユニット (ALU) 5066 を用いることが好ましい。スカラー演算のために設計された ALU 5066 もあり、浮動小数点のために設計されたもの ALU 5066 もある。データは、アーキテクチャに応じて、ビッグ・エンディアン（最下位のバイトが最も高いバイト・アドレスである）、又はリトル・エンディアン（最下位のバイトが最も低いバイト・アドレスである）とすることができます。IBM z / Architecture は、ビッグ・エンディアンである。符号付きフィールドは、アーキテクチャに応じて、符号及び大きさ、1 の補数、又は 2 の補数とすることができます。2 の補数における負の値又は正の値は、ALU 内で加法しか必要としないため、ALU が減算能力を設計する必要がないという点で、2 の補数は有利である。数値は、通常、省略表現で記述され、12 ビット・フィールドは、4,096 バイトブロックのアドレスを定め、通常、例えば 4K バイト（キロバイト）ブロックのように記述される。

30

## 【0166】

図 30 を参照すると、分岐命令を実行するための分岐命令情報が、典型的には、分岐ユニット 5058 に送られ、この分岐ユニット 5058 は、多くの場合、分岐履歴テーブル 5082 のような分岐予測アルゴリズムを用いて、他の条件付き演算が完了する前に分岐の結果を予測する。条件付き演算が完了する前に、現行の分岐命令のターゲットがフェッチされ、投機的に実行される。条件付き演算が完了すると、投機的に実行された分岐命令は、条件付き演算の条件及び投機された結果に基づいて、完了されるか又は破棄される。典型的な分岐命令は、条件コードをテストし、条件コードが分岐命令の分岐要件を満たす場合、ターゲット・アドレスに分岐することができ、ターゲット・アドレスは、例えば、命令のレジスタ・フィールド又は即値フィールド内に見出されるものを含む幾つかの数に

40

50

基づいて計算することができる。分岐ユニット 5058 は、複数の入力レジスタ回路 5075、5076、5077 と、出力レジスタ回路 5080 を有する ALU5074 を用いることができる。分岐ユニット 5058 は、例えば、汎用レジスタ 5059、デコード・ディスパッチ・ユニット 5056、又は他の回路 5073 と通信することができる。

#### 【0167】

例えば、オペレーティング・システムによって開始されるコンテキスト・スイッチ、コンテキスト・スイッチを発生させるプログラム例外又はエラー、コンテキスト・スイッチを発生させる I/O 割り込み信号、又は（マルチスレッド環境における）複数のプログラムのマルチスレッド活動を含む様々な理由により、命令のグループの実行に割り込みがかけられることがある。コンテキスト・スイッチ動作は、現在実行中のプログラムについての状態情報を保存し、次いで、起動される別のプログラムについての状態情報をロードすることが好ましい。状態情報は、例えば、ハードウェア・レジスタ又はメモリ内に保存することができる。状態情報は、実行される次の命令を指示するプログラム・カウンタ値と、条件コードと、メモリ変換情報と、アーキテクチャ化されたレジスタのコンテンツとを含むことが好ましい。コンテキスト・スイッチの活動は、ハードウェア回路、アプリケーション・プログラム、オペレーティング・システム・プログラム、又はファームウェア・コード（マイクロコード、ピココード、又はライセンス内部コード（LIC））単独で又はその組み合わせで実施することができる。

10

#### 【0168】

プロセッサは、命令により定義された方法に従ってオペランドにアクセスする。命令は、命令の一部の値を用いて即値オペランドを与えることができ、汎用レジスタ又は専用レジスタ（例えば、浮動小数点レジスタ）のいずれかを明示的に指示する 1 つ又は複数のレジスタ・フィールドを与えることができる。命令は、オペコード・フィールドによって、オペランドとして識別されるインプライド・レジスタを用いることができる。命令は、オペランドのためのメモリ位置を用いることができる。z/Architecture の長変位ファシリティにより例示されるように、オペランドのメモリ位置を、レジスタ、即値フィールド、又はレジスタと即値フィールドの組み合わせによって与えることができ、命令は、ベース・レジスタ、索引レジスタ、及び即値フィールド（変位フィールド）を定め、これらが、例えば互いに加算されてメモリ内のオペランドのアドレスをもたらす。ここでの位置は、典型的には、特に断りのない限り、主メモリ（主ストレージ）内の記憶位置を意味する。

20

#### 【0169】

図 31 を参照すると、プロセッサは、ロード / ストア・ユニット 5060 を用いて、ストレージにアクセスする。ロード / ストア・ユニット 5060 は、メモリ 5025 内のターゲット・オペランドのアドレスを取得し、オペランドをレジスタ 5059 又は別のメモリ 5025 の記憶位置にロードすることによってロード操作を行うことができ、或いは、メモリ 5025 内のターゲット・オペランドのアドレスを取得し、レジスタ 5059 又は別のメモリ 5025 の記憶位置から取得したデータをメモリ 5025 内のターゲット・オペランドの記憶位置に格納することによって、ストア操作を行うことができる。ロード / ストア・ユニット 5060 は、投機的なものであってもよく、命令シーケンスに対してアウト・オブ・オーダー 式の順序でメモリにアクセスすることができるが、プログラムに対して、命令がインオーダー 式に実行されたという外観を維持することになる。ロード / ストア・ユニット 5060 は、汎用レジスタ 5059、デコード / ディスパッチ・ユニット 5056、キャッシュ / メモリ・インターフェース 5053、又は他の要素 5083 と通信することができ、ストレージ・アドレスを計算し、且つ、パイプライン処理を順に行つて操作をインオーダー 式に保持するための、種々のレジスタ回路、ALU5085、及び制御論理 5090 を含む。一部の動作は、アウト・オブ・オーダー 式とすることができるが、ロード / ストア・ユニットは、アウト・オブ・オーダー 式動作が、プログラムに対して、当技術分野において周知のようなインオーダー 式に実行されたように見えるようにする機能を提供する。

30

40

50

## 【0170】

好ましくは、アプリケーション・プログラムが「見ている」アドレスは、仮想アドレスと呼ばれることが多い。仮想アドレスは、「論理アドレス」及び「実効アドレス」と呼ばれることがある。これらの仮想アドレスは、これらに限定されるものではないが、単に仮想アドレスをオフセット値にプリフィックス付加すること、1つ又は複数の変換テーブルを介して仮想アドレスを変換することを含む、種々の動的アドレス変換(DAT)技術の1つによって、物理的メモリ位置にリダイレクトされるという点で仮想のものであり、変換テーブルは、少なくともセグメント・テーブル及びページ・テーブルを単独で又は組み合わせて含むことが好ましく、セグメント・テーブルは、ページ・テーブルを指示するエントリを有することが好ましい。*z/Architecture*では、領域第1テーブル、領域第2テーブル、領域第3テーブル、セグメント・テーブル、及び随意的なページ・テーブルを含む、変換の階層構成が提供される。アドレス変換の性能は、仮想アドレスを関連した物理的メモリ位置にマッピングするエントリを含む変換ルックアサイド・バッファ(TLB)を用いることにより改善されることが多い。DATが変換テーブルを用いて仮想アドレスを変換したときに、エントリが作成される。次いで、後に仮想アドレスを用いることで、低速の順次変換テーブル・アクセスではなく、高速のTLBのエントリを用いることが可能になる。TLBのコンテンツは、LRUを含む種々の置換アルゴリズムによって管理することができる。

10

## 【0171】

プロセッサがマルチプロセッサ・システムのプロセッサである場合には、各プロセッサは、コヒーレンシのために、I/O、キャッシュ、TLB、及びメモリといった共有リソースをインターロック状態に保持する責任を負う。キャッシュ・コヒーレンシを保持する際に、一般的には「スヌープ」技術が用いられる。スヌープ環境においては、共有を容易にするために、各キャッシュ・ラインを、共有状態、排他的状態、変更状態、無効状態等のいずれか1つの状態にあるものとしてマーク付けすることができる。

20

## 【0172】

I/Oユニット5054(図28)は、プロセッサに、例えば、テープ、ディスク、プリンタ、ディスプレイ、及びネットワークを含む周辺機器に取り付けるための手段を与える。I/Oユニットは、ソフトウェア・ドライバによってコンピュータ・プログラムに提示されることが多い。IBMによるSystem zのようなメインフレームにおいては、チャネル・アダプタ及びオープン・システム・アダプタが、オペレーティング・システムと周辺機器との間に通信をもたらすメインフレームのI/Oユニットである。

30

## 【0173】

さらに、他のタイプのコンピューティング環境が、1つ又は複数の態様から利益を得ることができる。一例として、環境は、特定のアーキテクチャ(例えば、命令実行、アドレス変換などのアーキテクチャ化された機能、及びアーキテクチャ化されたレジスタを含む)又はそのサブセットをエミュレートする(例えば、プロセッサ及びメモリを有するネイティブ・コンピュータ・システム上で)エミュレータ(例えば、ソフトウェア又は他のエミュレーション機構)を含むことができる。このような環境においては、エミュレータを実行しているコンピュータが、エミュレートされる機能とは異なるアーキテクチャを有することができたとしても、エミュレータの1つ又は複数のエミュレーション機能は、本発明の1つ又は複数の態様を実施することができる。一例として、エミュレーション・モードにおいては、エミュレートされる特定の命令又は操作がデコードされ、適切なエミュレーション機能が構築され、個々の命令又は操作を実施する。

40

## 【0174】

エミュレーション環境においては、ホスト・コンピュータは、例えば、命令及びデータを格納するためのメモリと、メモリから命令をフェッチし、随意的に、フェッチされた命令のためのローカル・バッファリングを提供するための命令フェッチ・ユニットと、フェッチされた命令を受信し、フェッチされた命令のタイプを判断するための命令デコード・ユニットと、命令を実行するための命令実行ユニットとを含む。実行は、データをメモリ

50

からレジスタ内にロードすること、データをレジスタから再びメモリに格納すること、又はデコード・ユニットにより判断されるように、何らかのタイプの算術演算又は論理演算を実行することを含むことができる。一例においては、各ユニットは、ソフトウェアで実装される。例えば、ユニットが実行する演算は、エミュレータ・ソフトウェア内の1つ又は複数のサブルーチンとして実装される。

#### 【0175】

より具体的には、メインフレームにおいて、アーキテクチャ化されたマシン命令は、通常、プログラマによって、多くの場合コンパイラ・アプリケーションを介して、今日では「C」プログラマによって用いられる。ストレージ媒体内に格納されたこれらの命令は、z/ArchitectureのIBMサーバにおいて、又は代替的に他のアーキテクチャを実行するマシンにおいて、ネイティブに実行することができる。これらの命令は、既存の及び将来のIBMメインフレーム・サーバにおいて、及び、IBMの他のマシン（例えば、Power Systemsサーバ及びSystem x（登録商標）サーバ）上で、エミュレートすることができる。これらの命令は、IBM（登録商標）社、Intel（登録商標）社、AMD（商標）社などによって製造されたハードウェアを用いて種々のマシン上でLinux（登録商標）を実行しているマシンにおいて実行することができる。Z/Architecture下でそのハードウェア上で実行することに加えて、Linuxを用いること、並びに、一般に実行がエミュレーション・モードにあるHercules、UMX、又はFSI（Fundamental Software, Inc）によるエミュレーションを用いるマシンを用いることもできる。エミュレーション・モードにおいては、ネイティブ・プロセッサによって、エミュレーション・ソフトウェアが実行され、エミュレートされたプロセッサのアーキテクチャをエミュレートする。

10

20

30

40

#### 【0176】

ネイティブ・プロセッサは、一般的に、エミュレートされたプロセッサのエミュレーションを実行するためにファームウェア又はネイティブ・オペレーティング・システムのいずれかを含むエミュレーション・ソフトウェアを実行する。エミュレーション・ソフトウェアは、エミュレートされたプロセッサ・アーキテクチャの命令のフェッチと実行を担当する。エミュレーション・ソフトウェアは、エミュレートされたプログラム・カウンタを維持し、命令境界を常時監視している。エミュレーション・ソフトウェアは、一度に1つ又は複数のエミュレートされたマシン命令をフェッチし、ネイティブ・プロセッサにより実行するために、その1つ又は複数のエミュレートされたマシン命令を、対応するネイティブマシン命令のグループに変換することができる。これらの変換された命令は、より速い変換を達成できるようにキャッシュに入れることができる。それにも関わらず、エミュレーション・ソフトウェアは、エミュレートされたプロセッサ・アーキテクチャのアーキテクチャ規則を維持して、オペレーティング・システム及びエミュレートされたプロセッサのために書かれたアプリケーションが正確に動作することを保証しなければならない。さらに、エミュレーション・ソフトウェアは、これらに限定されるものではないが、制御レジスタ、汎用レジスタ、浮動小数点レジスタ、例えばセグメント・テーブル及びページ・テーブルを含む動的アドレス変換機能、割り込み機構、コンテキスト・スイッチ機構、時刻（TOD）クロック、及びI/Oサブシステムへのアーキテクチャ化インターフェースを含む、エミュレートされたプロセッサのアーキテクチャによって識別されるリソースを提供し、オペレーティング・システム又はエミュレートされたプロセッサ上で実行するように設計されたアプリケーション・プログラムが、エミュレーション・ソフトウェアを有するネイティブ・プロセッサ上で実行することができる。

#### 【0177】

エミュレートされた特定の命令がデコードされ、個々の命令の機能を実行するためのサブルーチンが呼び出される。エミュレートされたプロセッサの機能をエミュレートするエミュレーション・ソフトウェア機能は、例えば、「C」サブルーチン若しくはドライバにおいて、又は1つ又は複数の実施形態の説明を理解した後で当業者の技術の範囲内にあるような特定のハードウェアのためにドライバを提供する他の何らかの方法で実装される。

50

Beausoleil 他による「Multiprocessor for Hardware Emulation」という名称の特許文献1、Scalzi 他による「Preprocessing of Stored Target Routines for Emulating Incompatible Instructions on a Target Processor」という名称の特許文献2、Davidian 他による「Decoding Guest Instruction to Directly Access Emulation Routines that Emulate the Guest Instructions」という名称の特許文献3、Gorishek 他による「Symmetrical Multiprocessing Bus and Chipset Used for Coprocessor Support Allowing Non-Native Code to Run in a System」という名称の特許文献4、Lethin 他による「Dynamic Optimizing Object Code Translator for Architecture Emulation and Dynamic Optimizing Object Code Translation Method」という名称の特許文献5、Eric Traut による「Method for Emulating Guest Instructions on a Host Computer Through Dynamic Recompilation of Host Instructions」という名称の特許文献6 及び他の多くを含むがこれらに限定されない、種々のソフトウェア及びハードウェア・エミュレーションの特許は、当業者が利用可能なターゲット・マシンのための異なるマシン用に設計された命令形式のエミュレーションを達成する様々な既知の方法を示す。

10

20

20

#### 【0178】

図32において、ホスト・アーキテクチャのホスト・コンピュータ・システム5000'をエミュレートする、エミュレートされたホスト・コンピュータ・システム5092の一例が提供される。エミュレートされたホスト・コンピュータ・システム5092では、ホスト・プロセッサ(CPU)5091は、エミュレートされたホスト・プロセッサ(又は、仮想ホスト・プロセッサ)であり、且つ、ホスト・コンピュータ5000'のプロセッサ5091のものとは異なるネイティブな命令セット・アーキテクチャを有するエミュレーション・プロセッサ5093を含む。エミュレートされたホスト・コンピュータ・システム5092は、エミュレーション・プロセッサ5093がアクセス可能なメモリ5094を有する。例示的な実施形態において、メモリ5094は、ホスト・コンピュータ・メモリ5096の部分と、エミュレーション・ルーチン5097の部分とにパーティション化される。ホスト・コンピュータ・メモリ5096は、ホスト・コンピュータ・アーキテクチャに従い、エミュレートされたホスト・コンピュータ・システム5092のプログラムに利用可能である。エミュレーション・プロセッサ5093は、エミュレートされたプロセッサ5091のもの以外のアーキテクチャのアーキテクチャ化された命令セットのネイティブ命令を実行し、このネイティブ命令はエミュレーション・ルーチン・メモリ5097から取得されたものであり、且つ、エミュレーション・プロセッサ5093は、シーケンス及びアクセス/デコード・ルーチンにおいて取得される1つ又は複数の命令を用いることにより、ホスト・コンピュータ・メモリ5096の中のプログラム由来の実行のためのホスト命令にアクセスすることができ、このシーケンス及びアクセス/デコード・ルーチンは、アクセスされたホスト命令をデコードして、アクセスされたホスト命令の機能をエミュレートするためのネイティブ命令実行ルーチンを判断することができる。ホスト・コンピュータ・システム5000'のアーキテクチャのために定められた、例えば、汎用レジスタ、制御レジスタ、動的アドレス変換、及びI/Oサブシステムのサポート、並びにプロセッサ・キャッシュといったファシリティを含む他のファシリティを、アーキテクチャ化ファシリティ・ルーチンによってエミュレートすることができる。エミュレーション・ルーチンは、エミュレーション・ルーチンの性能を高めるために、エミュレーション・プロセッサ5093において利用可能な(汎用レジスタ、及び仮想アドレスの動的

30

40

40

50

変換といった)機能を利用することができる。ホスト・コンピュータ5000'の機能をエミュレートする際にプロセッサ5093を補助するために、専用のハードウェア及びオフ・ロード・エンジンを設けることもできる。

#### 【0179】

本明細書で用いられる用語は、特定の実施形態を説明する目的のものにすぎず、本発明の限定であることを意図したものではない。本明細書で用いられる場合、単数形「1つの(a)」、「1つの(an)」及び「その(the)」は、文脈が特に明示しない限り、複数形も同様に含むことを意図したものである。「含む(comprise)」及び/又は「含んでいる(comprising)」という用語は、本明細書で用いられる場合、記述された特徴、整数、ステップ、動作、要素、及び/又はコンポーネントの存在を指示するが、1つ又は複数の他の特徴、整数、ステップ、動作、要素、コンポーネント、及び/又はそれらのグループの存在又は追加を排除するものではないこともさらに理解されるであろう。10

#### 【0180】

以下の特許請求の範囲に存在する場合、「手段又はステップと機能との組み合わせ(ミーンズ又はステップ・プラス・ファンクション)」要素の対応する構造、材料、動作及び均等物は、明確に特許請求された他の請求要素と共に機能を実行するための任意の構造体、材料、又は行為を含むことを意図したものである。1つ又は複数の態様の説明は、例証及び説明のためだけに提示されたものであり、網羅的であること又は本発明を開示した形態に限定することを意図したものではない。1つ又は複数の態様の範囲から逸脱することなく、当業者には、多くの修正及び変形が明らかとなるであろう。実施形態は、1つ又は複数の態様の原理及び実際の用途を最もよく説明するため、及び、当業者が、企図した特定の用途に適するように種々の修正を有する種々の実施形態に関して1つ又は複数の態様を理解することができるよう、選択され記述された。20

#### 【符号の説明】

#### 【0181】

100、200 : コンピューティング環境

102、5026 : プロセッサ

104、204、5025 : メモリ

106、206 : 入力/出力デバイス及び/又はインターフェース

108、208 : バス

202 : ネイティブ中央演算処理ユニット(CPU)

210 : ネイティブ・レジスタ

212 : エミュレータ・コード

250 : ゲスト命令

252 : 命令フェッチ・ユニット

254 : 命令変換ルーチン

256 : ネイティブ命令

260 : エミュレーション制御ルーチン

300 : レジスタ・ファイル

302、480 : ベクトル・レジスタ

304 : 浮動小数点レジスタ

400 : Vector Floating Point Test Data Class Immediate 命令

500 : Vector Checksum 命令

600 : Vector Galois Field Multiply Sum and

700 : Vector Generate Mask 命令

800 : Vector Element Rotate and Insert Under Mask 命令

900 : ベクトル例外コード

902 : ベクトル・インデックス4050

904 : ベクトル割り込みコード

1000 : コンピュータ・プログラム製品

【図1】

【図2】

【図3】

【図4】

【図5】

| VECTOR FLOATING POINT TEST DATA CLASS IMMEDIATE |                |                |                |                |                |     |       |

|-------------------------------------------------|----------------|----------------|----------------|----------------|----------------|-----|-------|

| VFTCI                                           | V <sub>1</sub> | V <sub>2</sub> | I <sub>2</sub> | M <sub>5</sub> | M <sub>6</sub> | RXB | VRI-E |

| E7                                              | 402a           | 404            | 406            | 408            | 410            | 412 | 402b  |

| 0                                               | 8              | 12             | 16             | 28             | 32             | 36  | 40    |

|                                                 |                |                |                |                |                |     |       |

【図6】

| ビット番号クラス  |    | 各ビットでの値に付属されるビット |  |

|-----------|----|------------------|--|

| +         | -  |                  |  |

| ゼロ        | 0  | 1                |  |

| 止境数       | 2  | 3                |  |

| サブ正規数     | 4  | 5                |  |

| 無限大       | 6  | 7                |  |

| クワイエットNaN | 8  | 9                |  |

| シグナリングNaN | 10 | 11               |  |

〔 四 7 〕

【 四 8 】

| エンティティ      | 属性 | ハイアス花数            | 仙山ヒット | 枚数      |

|-------------|----|-------------------|-------|---------|

| 島の内         | 土  | 0                 | 0     | 0       |

| 非正規化数       | 土  | 0*                | 0     | 件〇      |

| 正規化数        | 土  | 既定で<br>なければ<br>ない | 1     | 件悪      |

| 測定式         | 土  | 全て1               | -     | 0       |

| クォンタフィックNaN | 土  | 全て1               | -     | F#01+件良 |

| シグナリングNaN   | 土  | 全て1               | -     | F#00+件良 |

【 図 1 0 】

【 四 1 1 】

【 义 1 3 】

【図 1 4】

【図 1 5】

【図 1 6】

【図 1 8】

【図 1 7】

【図 1 9】

【図20】

【図22】

【図23】

【図21】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図31】

【図32】

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                      | International application No.<br>PCT/IB2013/060309     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>Int.Cl. G06F9/305(2006.01)i, G06F9/315(2006.01)i, G06F15/80(2006.01)i,<br>G06F17/16(2006.01)i<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                      |                                                        |