(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6234054号

(P6234054)

(45) 発行日 平成29年11月22日(2017.11.22)

(24) 登録日 平成29年11月2日(2017.11.2)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/341 (2011.01)  | HO4N 5/341     |

| HO4N 5/3745 (2011.01) | HO4N 5/3745    |

| HO4N 5/232 (2006.01)  | HO4N 5/232 120 |

| HO1L 27/146 (2006.01) | HO1L 27/146 A  |

| GO3B 13/36 (2006.01)  | HO1L 27/146 D  |

請求項の数 16 (全 11 頁) 最終頁に続く

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2013-93051 (P2013-93051)    |

| (22) 出願日  | 平成25年4月25日 (2013.4.25)        |

| (65) 公開番号 | 特開2014-216866 (P2014-216866A) |

| (43) 公開日  | 平成26年11月17日 (2014.11.17)      |

| 審査請求日     | 平成28年4月22日 (2016.4.22)        |

|           |                                            |

|-----------|--------------------------------------------|

| (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (74) 代理人  | 100076428<br>弁理士 大塚 康徳                     |

| (74) 代理人  | 100112508<br>弁理士 高柳 司郎                     |

| (74) 代理人  | 100115071<br>弁理士 大塚 康弘                     |

| (74) 代理人  | 100116894<br>弁理士 木村 秀二                     |

| (74) 代理人  | 100130409<br>弁理士 下山 治                      |

| (74) 代理人  | 100134175<br>弁理士 永川 行光                     |

最終頁に続く

(54) 【発明の名称】撮像装置および撮像装置の制御方法

## (57) 【特許請求の範囲】

## 【請求項 1】

各々が複数の光電変換手段を備える複数の単位画素が行列状に配置された画素配列と、前記画素配列の列毎に設けられた第1の容量と、前記画素配列の列毎に設けられた第2の容量と、

各単位画素が備える前記複数の光電変換手段の一部から第1の信号を読み出して前記第1の容量に書き込む第1の書き込み処理と、各単位画素が備える前記複数の光電変換手段の全てから第2の信号を読み出して前記第2の容量に書き込む第2の書き込み処理とを実行する駆動手段と、

前記第1の信号と、前記第2の信号と前記第1の信号の差分信号とを用いて焦点検出を行う焦点検出手段と、

前記第2の信号から撮影画像データを生成する撮影画像データ生成手段と、

前記駆動手段、前記焦点検出手段および前記撮影画像データ生成手段を制御する制御手段と、を有し、

前記第1の書き込み処理の時間が前記第2の書き込み処理の時間よりも短く設定されることを特徴とする撮像装置。

## 【請求項 2】

さらに前記撮影画像データを記憶する記憶手段を有することを特徴とする請求項1に記載の撮像装置。

## 【請求項 3】

10

20

さらに前記撮影画像データを表示する表示手段を有することを特徴とする請求項1または2に記載の撮像装置。

【請求項4】

前記単位画素の各々は、前記複数の光電変換手段により共有される電荷電圧変換手段と、前記複数の光電変換手段によって生成された電荷と、を前記電荷電圧変換手段に転送する転送手段とを備えることを特徴とする請求項1乃至3のいずれか1項に記載の撮像装置。

【請求項5】

前記単位画素の各々は、1つのマイクロレンズを備えることを特徴とする請求項1乃至4のいずれか1項に記載の撮像装置。

10

【請求項6】

前記第2の信号は前記単位画素の全ての光電変換手段からの信号を混合することにより得られることを特徴とする請求項1乃至5のいずれか1項に記載の撮像装置。

【請求項7】

前記複数の単位画素の各々は2つの光電変換部を備えることを特徴とする請求項1乃至6のいずれか1項に記載の撮像装置。

【請求項8】

さらに前記複数の単位画素上に光学像を形成する撮影レンズを有することを特徴とする請求項1乃至7のいずれか1項に記載の撮像装置。

【請求項9】

各々が複数の光電変換手段を備える複数の単位画素が行列状に配置された画素配列と、前記画素配列の列毎に設けられた第1の容量と、前記画素配列の列毎に設けられた第2の容量とを備えた撮像装置の制御方法であって、

駆動手段が、各単位画素が備える前記複数の光電変換手段の一部から第1の信号を読み出して前記第1の容量に書き込む第1の書き込み処理と、各単位画素が備える前記複数の光電変換手段の全てから第2の信号を読み出して前記第2の容量に書き込む第2の書き込み処理とを実行する工程と、

焦点検出手段が、前記第1の信号と、前記第2の信号と前記第1の信号の差分信号とを用いて焦点検出を行う工程と、

撮影画像データ生成手段が、前記第2の信号から撮影画像データを生成する工程と、を有し、

20

前記第1の書き込み処理の時間が前記第2の書き込み処理の時間よりも短く設定されることを特徴とする撮像装置の制御方法。

【請求項10】

さらに、記憶手段が前記撮影画像データを記憶する工程を有することを特徴とする請求項9に記載の撮像装置の制御方法。

【請求項11】

さらに、表示手段が前記撮影画像データを表示する工程を有することを特徴とする請求項9又は10に記載の撮像装置の制御方法。

【請求項12】

前記単位画素の各々は、前記複数の光電変換手段により共有される電荷電圧変換手段と、前記複数の光電変換手段によって生成された電荷と、を前記電荷電圧変換手段に転送する転送手段とを備えることを特徴とする請求項9乃至11のいずれか1項に記載の撮像装置の制御方法。

30

【請求項13】

前記単位画素の各々は、1つのマイクロレンズを備えることを特徴とする請求項9乃至12のいずれか1項に記載の撮像装置の制御方法。

【請求項14】

前記第2の信号は前記単位画素の全ての光電変換手段からの信号を混合することにより得られることを特徴とする請求項9乃至13のいずれか1項に記載の撮像装置の制御方法

40

50

。【請求項 15】

前記複数の単位画素の各々は 2 つの光電変換部を備えることを特徴とする請求項 9 乃至 14 のいずれか 1 項に記載の撮像装置の制御方法。

【請求項 16】

さらに前記複数の単位画素上に光学像を形成する撮影レンズを有することを特徴とする請求項 9 乃至 15 のいずれか 1 項に記載の撮像装置の制御方法。

【発明の詳細な説明】

【技術分野】

【0001】

10

本発明は、撮像装置および撮像装置の制御方法に関するものである。

【背景技術】

【0002】

デジタルスチルカメラやデジタルビデオカメラなどの撮像装置に用いられる撮像素子は、その多機能が進んでおり、例えば焦点検出機能を有するものも知られている。具体的には、撮像素子の 1 つの画素に 2 つのフォトダイオードと 1 つのマイクロレンズを設ける。そして、各フォトダイオードが撮影レンズの異なる瞳を通過した光を受光するよう構成することで、各フォトダイオードの出力信号を用いた位相差検出方式の焦点検出が可能となる。また、同じ画素に設けられた 2 つのフォトダイオードの出力信号を加算することで、画像出力を得ることができる（特許文献 1）。

20

【先行技術文献】

【特許文献】

【0003】

【特許文献 1】特開 2001-124984 号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

特許文献 1 の構成では、1 画素あたり 2 つのフォトダイオードから信号を取得する必要がある。そのため、1 つの画素に 1 つのフォトダイオードを有する従来の構成に対して、読み出す時間が 2 倍に増えてしまうという問題がある。しかし、所定のフレームレートでの読み出しを達成するには読み出し時間の短縮が必要である。

30

【0005】

本発明はこのような課題に鑑み、位相差検出方式の焦点検出が可能な撮像素子を用いた撮像装置において、信号読み出し時間の短縮が可能な撮像装置を提供することを目的とする。

【課題を解決するための手段】

【0006】

本発明の撮像装置は、各々が複数の光電変換手段を備える複数の単位画素が行列状に配置された画素配列と、前記画素配列の列毎に設けられた第 1 の容量と、前記画素配列の列毎に設けられた第 2 の容量と、各単位画素が備える前記複数の光電変換手段の一部から第 1 の信号を読み出して前記第 1 の容量に書き込む第 1 の書き込み処理と、各単位画素が備える前記複数の光電変換手段の全てから第 2 の信号を読み出して前記第 2 の容量に書き込む第 2 の書き込み処理とを実行する駆動手段と、前記第 1 の信号と、前記第 2 の信号と前記第 1 の信号の差分信号とを用いて焦点検出を行う焦点検出手段と、前記第 2 の信号から撮影画像データを生成する撮影画像データ生成手段と、前記駆動手段、前記焦点検出手段および前記撮影画像データ生成手段を制御する制御手段と、を有し、前記第 1 の書き込み処理の時間が前記第 2 の書き込み処理の時間よりも短く設定されることを特徴とする。

40

【発明の効果】

【0007】

本発明によれば、位相差検出方式の焦点検出が可能な撮像素子を用いた撮像装置におい

50

て、信号読み出し時間を短縮することができる。

【図面の簡単な説明】

【0008】

【図1】本発明にかかる撮像装置の撮影レンズの射出瞳から出た光束が単位画素に入射する概念図

【図2】撮像装置の全体ブロック図

【図3】実施形態1の像素子の全体図

【図4】実施形態1の像素子の単位画素の回路図

【図5】実施形態1の像素子の読み出し回路の回路図

【図6】実施形態1の像素子の駆動タイミングチャート

10

【発明を実施するための形態】

【0009】

以下、図面を参照して本発明の実施形態を詳細に説明する。

【実施形態1】

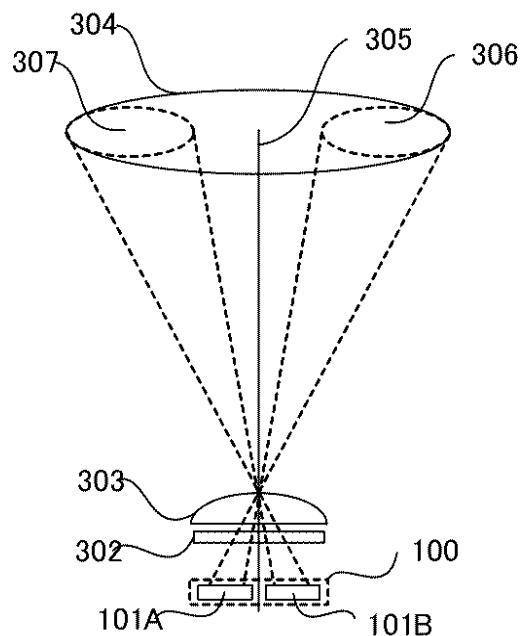

はじめに、通常の被写体撮像用の像素子で位相差検出方式の焦点検出を実現する原理を説明する。図1は、撮影レンズの射出瞳から出た光束が、像素子が有する単位画素の1つに入射する状態を模式的に示した図である。単位画素100は、第1のフォトダイオード101Aおよび第2のフォトダイオード101Bを有する。また、単位画素100に対応して、カラーフィルタ302およびマイクロレンズ303が設けられている。

【0010】

20

マイクロレンズ303を有する画素に対して、撮影レンズの射出瞳304から出た光束の中心を光軸305とする。射出瞳304を通過した光は、光軸305を中心として単位画素100に入射する。瞳領域306、307は撮影レンズの射出瞳の一部領域である。図1に示すように、瞳領域306を通過する光束は、マイクロレンズ303を通してフォトダイオード101Aで受光され、瞳領域307を通過する光束は、マイクロレンズ303を通してフォトダイオード101Bで受光される。このように、フォトダイオード101Aと101Bが、それぞれ撮影レンズの射出瞳304の別々の瞳領域306、307の光を受光するため、フォトダイオード101Aと101Bの信号の位相差に基づく焦点検出が可能である。

【0011】

30

ここで、フォトダイオード101Aから得られる信号をA像信号、フォトダイオード101Bから得られる信号をB像信号とする。A像信号とB像信号を加算した(A+B)像信号は、単位画像100の撮像信号として用いることができる。

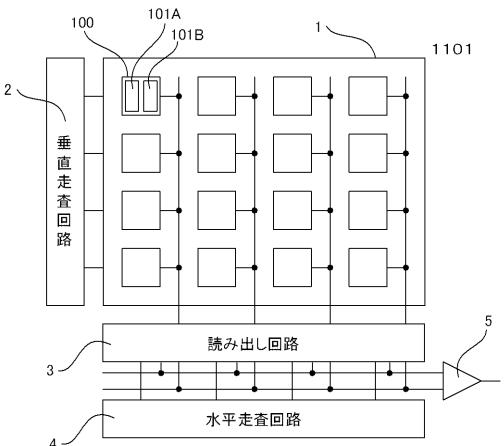

【0012】

図2は、本実施形態の像素子を用いた撮像装置の機能構成例を示すブロック図である。撮像装置の光学系は、被写体の光学像を像素子1101に結像させる撮影レンズ1110などを含み、レンズ駆動回路1109によってズーム制御、フォーカス制御、絞り制御などが行われる。像素子1101には、複数の単位画素100が行列状に配置されている。像素子1101に結像された被写体の像は、電気的な画像信号として像素子1101から出力される。信号処理回路1103は、像素子1101から出力される画像信号に各種の補正を行ったり、圧縮したりする。信号処理回路1103では、像素子1101で取得したA像信号と(A+B)像信号の差分信号としてB像信号の生成を行ってもよい。タイミング発生回路1102は、像素子1101を駆動するタイミング信号を出力する。全体制御・演算回路1104は、各種演算を行うとともに、像素子1101の動作を含む撮像装置全体の動作を制御する。全体制御・演算回路1104は、A像信号およびB像信号を用いた位相差検出方式の焦点検出動作も行う。信号処理回路1103が出力する画像データは、メモリ回路1105に一時的に記憶される。表示回路1106は、各種情報や撮影した画像を表示する。記録回路1107は、画像データの記録または読み出しを行う。記録回路1107は、例えば半導体メモリ等の着脱可能な記録媒体を読み書きする回路である。操作回路1108は、スイッチ、ボタン、タッチパネルなどを代表

40

50

とする入力デバイス群を含み、撮像装置に対するユーザ指示を受け付ける。

【0013】

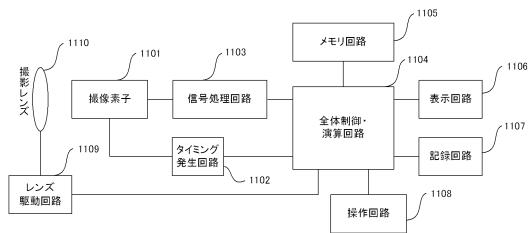

つぎに、撮像素子 1101 の構成例を図 3～5 を用いて説明する。図 3 は、撮像素子 1101 の全体構成例を示す図である。撮像素子 1101 は、画素領域 1、垂直走査回路 2、読み出し回路 3、水平走査回路 4、出力アンプ 5 から構成される。画素領域 1 には、複数の単位画素 100 が行列状に配置されている。ここでは、説明を簡単にするために  $4 \times 4$  の 16 画素の配列を示してあるが、実際には数 100 万以上の単位画素が行列状に配置される。図 1 で説明したように、各単位画素 100 は、第 1 のフォトダイオード 101A および第 2 のフォトダイオード 101B を備える。本実施形態では、垂直走査回路 2 は、画素領域 1 の画素を 1 行単位で選択し、選択行の画素に対して駆動信号を送出する。読み出し回路 3 は、列毎に列読み出し回路を備え、単位画素 100 からの出力信号を増幅し、その出力信号をサンプルホールドする。水平走査回路 4 は、読み出し回路 3 でサンプルホールドされた信号を列毎に順次出力アンプ 5 に出力するための信号を送出する。出力アンプ 5 は、水平走査回路 4 の動作により、読み出し回路 3 から出力された信号を信号処理回路 1103 に出力する。垂直走査回路 2、読み出し回路 3、水平走査回路 4 は、タイミング発生回路 1102 からのタイミング信号により駆動される。

【0014】

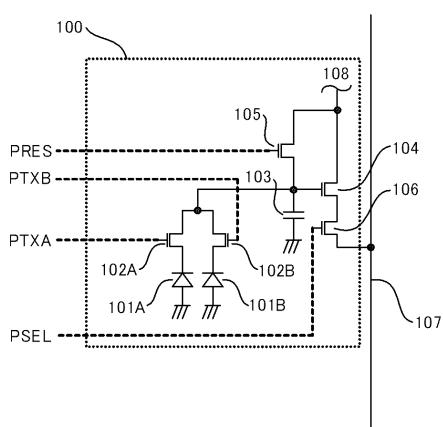

図 4 は、単位画素 100 の構成例を示す回路図である。第 1 のフォトダイオード 101A、第 2 のフォトダイオード 101B には、第 1 の転送スイッチ 102A、第 2 の転送スイッチ 102B がそれぞれ接続されている。また、第 1 および第 2 の転送スイッチ 102A、102B の出力は、フローティングディフュージョン領域 103 を通じて増幅部 104 に接続されている。フローティングディフュージョン領域 103 にはリセットスイッチ 105 が接続され、増幅部 104 には選択スイッチ 106 が接続される。

【0015】

フォトダイオード 101A、101B は、同一のマイクロレンズを通過した光を受光し、その受光量に応じた信号電荷を生成する光電変換部として機能する。転送スイッチ 102A、102B は、それぞれフォトダイオード 101A、101B で発生した電荷を共通のフローティングディフュージョン領域 103 に転送する転送部として機能する。転送スイッチ 102A、102B は、それぞれ垂直走査回路 2 からの転送パルス信号 P T X A、P T X B によって制御される。フローティングディフュージョン領域 103 は、フォトダイオード 101A および 101B から転送された電荷を一時的に保持するとともに、保持した電荷を電圧信号に変換する電荷電圧変換部として機能する。増幅部 104 は、ソースフォロワ MOS トランジスタであり、フローティングディフュージョン領域 103 により変換された電圧信号を増幅して、画素信号として出力する。リセットスイッチ 105 は、垂直走査回路 2 からのリセットパルス信号 P R E S によって制御され、フローティングディフュージョン領域 103 の電位を基準電位 V D D 108 にリセットする。選択スイッチ 106 は、垂直走査回路 2 からの垂直選択パルス信号 P S E L によって制御され、増幅部 104 で増幅された電圧信号を垂直出力線 107 に画素信号として出力する。

【0016】

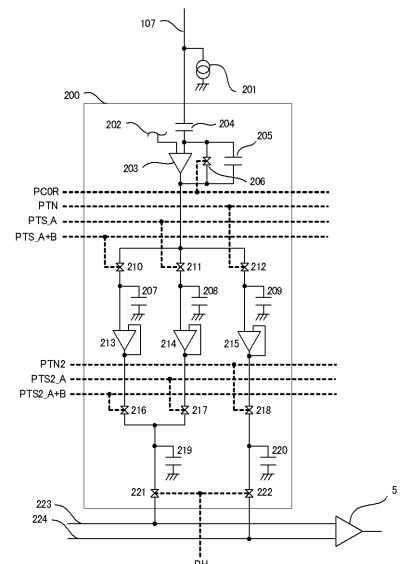

図 5 は、図 3 の読み出し回路 3 に含まれる列読み出し回路 200 の構成例を示す回路図である。読み出し回路 3 は、列毎に列読み出し回路 200 を備えるが、各列の構成は共通であるので、ここでは 1 列のみ示してある。垂直出力線 107 上の信号電圧はオペアンプ 203 により増幅される。オペアンプ 203 には基準電圧 V R E F が供給される。オペアンプ 203 の入力にはクランプ容量 C 0204 が接続され、入出力間にはフィードバック容量 C f 205 が接続される。また、フィードバック容量 C f 205 の両端には、両端をショートさせるためのスイッチ 206 が設けられている。スイッチ 206 は、読み出し回路 3 の P C O R 信号で制御される。垂直出力線 107 には定電流源 201 が接続されている。

【0017】

C T S \_ A + B 207、C T S \_ A 208、C T N 209 は、オペアンプ 203 からの

10

20

30

40

50

信号電圧を保持するための容量である。スイッチ 210、211、212 は、それぞれ CTS\_A + B 207、CTS\_A 208、CTN 209 への書き込みを制御するスイッチである。スイッチ 210 は、読み出し回路 3 の PTS\_A + B 信号で制御され、スイッチ 211 は、読み出し回路 3 の PTS\_A 信号で制御される。スイッチ 212 は、読み出し回路の PTN 信号で制御される。CTS\_2 219、CTN\_2 220 は、CTS\_A + B 207、CTS\_A 208、CTN 209 からの信号電圧を保持するための容量である。スイッチ 216、217、218 は、CTS\_2 219、CTN\_2 220 への書き込みを制御するスイッチである。スイッチ 216 は、CTS\_A + B 207 の信号を CTS\_2 219 に書き込むためのもので、読み出し回路の PTS\_2\_A + B 信号で制御される。スイッチ 217 は、CTS\_A 208 の信号を CTS\_2 219 に書き込むためのもので、読み出し回路の PTS\_2\_A 信号で制御される。スイッチ 218 は、CTN 209 の信号を CTN\_2 220 に書き込むためのもので、読み出し回路の PTN 2 信号で制御される。10

#### 【0018】

また、CTS\_2 219、CTN\_2 220 の直前には、バッファとしてのボルテージフォロワ回路 213、214、215 を設けている。ボルテージフォロワ回路 213、214、215 は、CTS\_A + B 207、CTS\_A 208、CTN 209 のそれぞれに蓄積された電位と等しい電位を、容量分割によらず CTS\_2 219、CTN\_2 220 に伝達する。

#### 【0019】

スイッチ 221、222 は、水平走査回路 4 からの PH 信号で制御され、CTS\_2 219 に書き込まれた信号は共通出力線 223 を介して、CTN\_2 220 に書き込まれた信号は共通出力線 224 を介して、それぞれ出力アンプ 5 に出力される。CTS\_A + B 207、CTS\_A 208、CTN 209 への信号書き込みと CTS\_2 219、CTN\_2 220 からの水平走査による信号読み出しは、並行して行われる。20

#### 【0020】

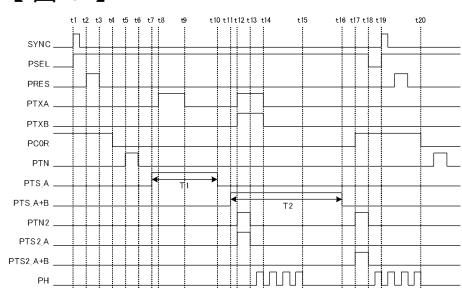

図 6 に、本実施形態に係る撮像素子 1101 の駆動方法を実現するためのタイミングチャートを示す。図 6 は、垂直走査回路 2 がある行を選択した際の駆動タイミングを表す。時刻 t1 において、水平同期信号 SYNC が立ち上がるとともに、選択された行の垂直選択パルス信号 PSEL が L → H となる。これにより選択された行の選択スイッチ 106 ( 図 4 ) がオンし、選択された行の画素信号を垂直出力線 107 に出力することが可能となる。30

#### 【0021】

時刻 t2 には、リセットパルス信号 PRES が L → H となり、リセットスイッチ 105 がオンし、フローティングディフュージョン領域 103 の電位が電源 VDD にリセットされる。時刻 t3 には、リセットパルス信号 PRES が H → L となり、リセットスイッチ 105 がオフし、フローティングディフュージョン領域 103 のリセットが解除される。このときのフローティングディフュージョン領域 103 の電位は、垂直出力線 107 に増幅部 104 を介してリセット信号レベルとして読み出され、列読み出し回路 200 に入力される。列読み出し回路 200 では、PCOR 信号が H でスイッチ 206 ( 図 5 ) がオンになっており、オペアンプ 203 が基準電圧 Vref の出力をバッファする状態でリセット信号レベルがクランプ容量 C0204 に入力される。40

#### 【0022】

その後、時刻 t4 で PCOR 信号を H → L とし、時刻 t5 で PTN 信号を H にしてスイッチ 212 をオンして、そのときのオペアンプ 203 の出力をリセット電圧として容量 CTN 209 へ書き込む。その後、時刻 t6 で PTN 信号を L として、スイッチ 212 をオフして CTN 209 へのリセット電圧の書き込みを終了する。

#### 【0023】

時刻 t7 で PTS\_A 信号を H とし、スイッチ 211 をオンにし、容量 CTS\_A 208 に信号を書き込み可能な状態とする。続いて、時刻 t8 で転送パルス信号 PTXA を H として、フォトダイオード 101A の電荷をフローティングディフュージョン領域 103

へ転送し、時刻  $t_9$  で転送パルス信号  $PTXA$  を  $L$  とする。この動作により、フォトダイオード  $101A$  に蓄積された電荷がフローティングディフュージョン領域  $103$  へ読み出される。そして、フローティングディフュージョン領域  $103$  で電荷が電圧に変換されて、その電圧が増幅部  $104$  および垂直出力線  $107$  を介して読み出し回路  $200$  へ供給される。

#### 【0024】

列読み出し回路  $200$  では、オペアンプ  $203$  がクランプ容量  $C0204$  とフィードバック容量  $Cf205$  の比率に応じた利得で垂直出力線  $107$  から供給された電圧を増幅して出力する。このフォトダイオード  $101A$  から提供された信号電圧は、容量  $CTS\_A208$  に書き込まれる。時刻  $t_{10}$  で  $PTS\_A$  信号を  $H-L$  と切り替え、スイッチ  $211$  をオフし、容量  $CTS\_A208$  への書き込みを終了する。この容量  $CTS\_A208$  への信号書き込み期間（時刻  $t_7 \sim t_{10}$ ）を  $T_1$  とする。

10

#### 【0025】

時刻  $t_{11}$  で  $PTS\_A+B$  信号を  $H$  とし、スイッチ  $210$  をオンにし、容量  $CTS\_A+B207$  に信号を書き込み可能な状態とする。続いて、時刻  $t_{12}$  で再び転送パルス信号  $PTXA$  を  $H$  とすると同時に転送パルス信号  $PTXB$  も  $H$  とする。この動作により、フォトダイオード  $101A$  と  $101B$  の双方の電荷を同時にフローティングディフュージョン領域  $103$  へ読み出すことができる。そして、時刻  $t_{14}$  で転送パルス信号  $PTXA$  および  $PTXB$  を  $L$  とする。読み出された電荷は、電圧に変換されて読み出し回路  $200$  へ供給され、オペアンプ  $203$  で増幅される。オペアンプ  $203$  により増幅された信号は容量  $CTS\_A+B207$  に書き込まれる。時刻  $t_{16}$  で  $PTS\_A+B$  信号を  $H-L$  に切り替え、スイッチ  $207$  をオフし、容量  $CTS\_A+B207$  への書き込みを終了する。この容量  $CTS\_A+B207$  への信号書き込み期間（時刻  $t_{11} \sim t_{16}$ ）を  $T_2$  とする。

20

#### 【0026】

なお、時刻  $t_{12}$  では転送パルス信号  $PTXA$  および  $PTXB$  を同時に  $H$  としたが、転送パルス信号  $PTXB$  だけを  $H$  としてフォトダイオード  $101B$  の電荷をフローティングディフュージョン領域  $103$  へ転送してもよい。この場合、フォトダイオード  $101A$  の電荷がすでにフローティングディフュージョン領域  $103$  へ転送されているので、フォトダイオード  $101A$  および  $101B$  の電荷を加算した出力を得ることができる。以上の動作により、容量  $CTSN209$ 、 $CTS\_A208$ 、 $CTS\_A+B207$  への信号書き込みが完了する。

30

#### 【0027】

ここで、容量  $CTS\_A+B207$  と容量  $CTN209$  に保持された信号の差分から、フォトダイオード  $101A$  および  $101B$  からの出力信号の和である  $(A+B)$  像信号が得られる。この  $(A+B)$  像信号は画像信号となる。また、容量  $CTS\_A208$  と容量  $CTN209$  に保持された信号の差分から、フォトダイオード  $101A$  からの出力信号である  $A$  像信号が得られる。この  $A$  像信号から撮影レンズの瞳の一部を透過する光束の情報が得られ、さらに  $(A+B)$  像信号と  $A$  像信号の差分をとることにより、フォトダイオード  $101B$  からの出力信号である  $B$  像信号が得られる。この  $B$  像信号からは、 $A$  像信号とは異なる瞳領域を透過する光束の情報が得られる。したがって、これら  $A$  像信号と  $B$  像信号との 2 つの光束の情報から焦点情報や距離情報を得ることができる。

40

#### 【0028】

画素部の信号を容量  $CTS\_A208$ 、 $CTS\_A+B207$  に書き込むには、垂直出力線での伝送遅延やオペアンプ  $203$  の静定時間を考慮して比較的長い時間が必要となる。静定時間が短い場合、信号にシェーディング等の固定パターンノイズが生じてしまう。この固定パターンノイズを低減する要求は、焦点検出用信号（ $A$  像信号および  $B$  像信号）に比べ、撮像画像用信号（ $(A+B)$  像信号）では極めて高い。換言すれば、焦点検出用信号については、撮像画像用信号ほどは固定パターンノイズを低減しなくてもよい。また、本実施形態では、容量  $CTS\_A208$  に書き込む信号が焦点検出用に用いられ、容量

50

CTS\_A + B 207 に書き込む信号が撮像画像に用いられるが、焦点検出用の A 像信号は撮像画像用の (A + B) 像信号よりも電圧が低い。そこで、焦点検出用の信号である A 像信号用の信号を容量 CTS\_A 208 に書き込む期間 T1 を、撮像画像用信号である (A + B) 像信号用の信号を容量 CTS\_A + B 207 に書き込む期間 T2 よりも短く設定する。これにより、撮像画像のノイズを抑えつつ、読み出し時間の短縮が可能となる。

#### 【0029】

ここで、容量 CTS\_A 208 に信号を書き込むために、PTS\_A 信号を H にするタイミング (時刻 t7) は、本実施形態では転送パルス信号 PTXA を H とする前に設定したが、転送パルス信号 PTXA を H とした後でもよい。この場合、容量 CTS\_A 208 に書き込む期間 T1 は、転送パルス信号 PTXA を H (時刻 t8) としてから PTS\_A 信号を L (時刻 t10) とするまでとして定義してもよい。同様に、容量 CTS\_A + B 207 に信号を書き込むために、PTS\_A + B 信号を H にするタイミング (時刻 t11) を転送パルス信号 PTXA および PTXB を H にするタイミング (時刻 t12) よりも後に設定してもよい。この場合は、容量 CTS\_A + B 207 に書き込む期間 T2 は、転送パルス信号 PTXA および PTXB を H (時刻 t12) としてから PTS\_A + B 信号を L (時刻 t16) とするまでとして定義してもよい。

#### 【0030】

図 6 の説明に戻り、時刻 t17 では PCOR 信号を再び H とし、スイッチ 206 がオンし、読み出し回路 200 では、オペアンプ 203 が基準電圧 Vref の出力をバッファする状態に戻る。そして時刻 t18 で垂直選択パルス信号 PSEL を L とし、選択されていた行の画素からの信号の読み出しは終了し、選択されていた行は垂直出力線から切り離される。その後、t19 で水平同期信号 SYNC が再び立ち上がり、同時に次行の垂直選択パルス信号 PSEL が H となり、次行の画素の選択が開始される。

#### 【0031】

時刻 t12 に戻り、(A + B) 像信号の容量 CTS\_A + B 207 への書き込みと同時に PTS2\_A 信号と PTN2 信号を L H とし、スイッチ 217 及びスイッチ 218 をオンする。容量 CTN209 に保持された信号はボルテージフォロワ回路 215 を介して、容量 CTN220 へ書き込まれ、容量 CTS\_A 208 に保持された信号はボルテージフォロワ回路 214 を介して容量 CTS2219 に書き込まれる。そして、時刻 t13 で PTN2 信号および PTS2\_A + B 信号が同時に H L となり、容量 CTN220 及び容量 CTS2219 への書き込みが終了する。

#### 【0032】

その後、t13 ~ t15 の間に、水平走査回路 4 の駆動パルス PH が各列の読み出し回路毎に順次 L H L となる。それに伴い、列毎にスイッチ 221、222 がオフ オン オフとなり、水平走査が行われる。スイッチ 221、222 がオフ オン オフとなつたときに各列の容量 CTS220、CTN2219 に保持された信号は共通出力線 223、224 へそれぞれ読み出され、出力アンプ 221 で共通出力線の信号の差電圧として出力される。この差電圧が A 像信号となる。なお、共通出力線 223、224 は各列の信号を読み出す毎に不図示のリセットスイッチにより基準電位にリセットされる。

#### 【0033】

ここで、A 像信号の水平走査は、(A + B) 像信号の容量 CTS\_A + B 207 への書き込み中 (T2 の期間) に行われる。この水平走査期間は、容量 CTS\_A + B 207 への書き込みが終わる時刻 t16 までに完了する。(A + B) 像信号の容量 CTS\_A + B 207 への書き込みが終わった後、(A + B) 像信号の容量 CTS2219 の書き込みおよび水平走査が行われる。これらの動作は次行のフローティングディフュージョン領域 103 のリセット、容量 CTN209 及び CTS\_A 208 への書き込みと並行して行われる。時刻 t17 では、PTN2 信号および PTS2\_A + B 信号を同時に L H することで、スイッチ 216 および 218 がオンする。容量 CTN209 に保持された信号はボルテージフォロワ 215 を介して、容量 CTN220 へ書き込まれる。さらに、容量 CTS\_A + B 207 に保持された信号はボルテージフォロワ 213 を介して、容量 CTS

10

20

30

40

50

<sub>2</sub> 2 1 9 に書き込まれる。そして、時刻  $t_{18}$  で P T N 2 信号および P T S 2 \_ A + B 信号が同時に H L となり、書き込みが終了する。

【 0 0 3 4 】

その後、図 6 の例では容量 C T N <sub>2</sub> 2 2 0 、 C T S <sub>2</sub> 2 1 9 に保持された信号は  $t_{18}$  ~  $t_{20}$  の間に、水平走査回路 4 の駆動パルス P H が順次 L H L となり水平走査が行われる。駆動パルス P H により各列のスイッチ 2 2 1 、 2 2 2 が駆動されてオフ オン オフする。スイッチ 2 2 1 、 2 2 2 により列毎の容量 C T S <sub>2</sub> 2 2 0 、 C T N <sub>2</sub> 2 1 9 に保持された信号は共通出力線 2 2 3 、 2 2 4 へそれぞれ読み出され、出力アンプ 2 2 1 で共通出力線 2 2 3 、 2 2 4 の差電圧として出力される。この差電圧が ( A + B ) 像信号となる。

10

【 0 0 3 5 】

ここで、 ( A + B ) 像信号の水平走査は、次行のフロー ティングディ フュージョン領域 1 0 3 のリセットおよび、容量 C T N 2 0 9 、 C T S \_ A 2 0 8 への書き込みと並行して行われる。並行して行うことにより処理時間を短縮できる。この水平走査期間は、次行の容量 C T S \_ A 2 0 8 への書き込みが終わる次の時刻  $t_{10}$  までに完了できる。

【 0 0 3 6 】

以上、述べたように、本実施形態では、撮像信号に用いる信号を容量に書き込む時間よりも焦点検出用の信号を容量へ書き込む時間を短くすることにより、撮像信号に影響を与えることなく、1フレームの読み出しに要する時間の短縮が可能となる。

【 0 0 3 7 】

なお、本実施形態では単位画素内に 2 つのフォトダイオードを備える構成であったが、単位画素内のフォトダイオードの数はこれに限定されず複数であればよい。例えば、単位画素内に 4 つのフォトダイオードを備え、焦点検出用として、単位画素内の 2 つの光電変換部の信号を読み出し、撮像用として単位画素内のすべての光電変換部の信号を読み出す構成であってもよい。

20

【 0 0 3 8 】

[ 実施形態 2 ]

次に、本発明に係る撮像素子を撮像装置に応用する場合の回路ブロックの例を図 2 により説明する。操作回路 1 1 0 8 からの操作に応じて、全体制御・演算回路 1 1 0 4 からの信号がタイミング発生回路 1 1 0 2 に与えられる。被写体の像は、光学系の撮影レンズ 1 1 1 0 や絞り等により撮像素子 1 1 0 1 に結像される。タイミング発生回路 1 1 0 2 は、撮像素子にタイミング信号を供給して撮像素子を制御する。撮像素子に結像された被写体の像は、タイミング信号に駆動される撮像素子により電気信号に変換されて、撮像素子 1 1 0 1 から出力される。なお、撮像素子に結像されたアナログ信号をデジタル信号に変換する機能は撮像素子 1 1 0 1 に持たせることもできるが、信号処理回路 1 1 0 3 で行ってもよい。撮像素子 1 1 0 1 からの出力信号は、信号処理回路 1 1 0 3 で補正や圧縮処理される。処理された画像信号は全体制御・演算回路 1 1 0 4 の制御によりメモリ回路 1 1 0 5 に一時的に蓄積されたり、操作回路 1 1 0 8 の操作に応じて表示回路 1 1 0 6 により表示されたりする。また、全体制御・演算回路 1 1 0 4 は信号処理回路 1 1 0 3 からの画像信号を記録回路 1 1 0 7 へ転送して記憶する。記録回路 1 1 0 7 は着脱可能な半導体メモリとすることができる。

30

【 0 0 3 9 】

以上、本発明の実施形態について説明したが、本発明はこれらの実施形態に限定されるものではない。

40

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

---

フロントページの続き

| (51)Int.Cl. |                | F I    |       |

|-------------|----------------|--------|-------|

| G 02 B      | 7/28 (2006.01) | G 03 B | 13/36 |

| G 02 B      | 7/34 (2006.01) | G 02 B | 7/28  |

|             |                | G 02 B | 7/34  |

(72)発明者 池戸 秀樹

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 鈴木 明

(56)参考文献 特開2010-181751(JP, A)

特開2009-089144(JP, A)

特開2001-305415(JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |                    |

|--------|--------------------|

| H 04 N | 5 / 30 - 5 / 378   |

| H 04 N | 5 / 222 - 5 / 257  |

| G 02 B | 7 / 28             |

| G 02 B | 7 / 34             |

| G 03 B | 13 / 36            |

| H 01 L | 27 / 14 - 27 / 148 |