(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3553946号

(P3553946)

(45) 発行日 平成16年8月11日(2004.8.11)

(24) 登録日 平成16年5月14日(2004.5.14)

(51) Int.C1.<sup>7</sup>

F 1

G06F 9/38

G06F 9/38 380B

G06F 9/34

G06F 9/34 380

請求項の数 9 (全 9 頁)

(21) 出願番号 特願平7-509618

(86) (22) 出願日 平成6年8月16日(1994.8.16)

(65) 公表番号 特表平9-503876

(43) 公表日 平成9年4月15日(1997.4.15)

(86) 国際出願番号 PCT/GB1994/001793

(87) 国際公開番号 WO1995/008801

(87) 国際公開日 平成7年3月30日(1995.3.30)

審査請求日 平成13年8月15日(2001.8.15)

(31) 優先権主張番号 9319662.4

(32) 優先日 平成5年9月23日(1993.9.23)

(33) 優先権主張国 英国(GB)

(73) 特許権者

エイアールエム リミテッド

イギリス国シービー1 9エヌジェイ ケ

ンブリッジ、チェリー ヒントン、フルバ

ーン ロード 110

(74) 代理人 弁理士 浅村 皓

(74) 代理人 弁理士 浅村 肇

(74) 代理人 弁理士 林 銘三

(74) 代理人 弁理士 清水 邦明

最終頁に続く

(54) 【発明の名称】データ処理命令の実行

## (57) 【特許請求の範囲】

## 【請求項1】

連続したデータ処理命令がパイプライン方式で実行されるデータ処理装置(100、110、120)であって、

1つまたはそれ以上の前記命令に対応して、データメモリにアクセスするメモリアクセス手段(110)であって、各メモリアクセスが無効か否かを検出する手段を含む前記モリアクセス手段(110)と、

前に実行された命令により発生する、前記装置の処理状態に対応しつつ各命令の実行中に動作して、その命令を実行すべきか否かを検出する条件テスト手段(200)と、

を含み、

前記メモリアクセス手段(110)が、先行命令によって開始されたメモリアクセスが無効であることを検出するか、あるいは前記条件テスト手段(200)が現在の命令を実行すべきではないことを検出するか、のいずれかの場合、前記メモリアクセス手段(110)と前記条件テスト手段(200)とに応答して、現在の命令の完全実行を防止する条件付き制御手段(230、240)、

を含むことを特徴とするデータ処理装置。

## 【請求項2】

請求項1において、

前記データ処理装置は自己の現在の処理状態を示すデータを格納する1つまたはそれ以上の処理フラグ(NZCV)を含み、

各命令は、実行すべきその命令に必要な前記処理フラグの状態を定義する条件コード（ビット28からビット31）を含み、

前記条件テスト手段（200）は、各命令の条件コードによって定義される処理フラグの必要な状態を、前記処理フラグの現在の状態と比較する、

データ処理装置。

**【請求項3】**

請求項2において、

- （i）前記装置の先行データ処理動作により負の結果（N）が発生したか否か、

- （ii）前記装置の先行データ処理動作によりゼロの結果（Z）が発生したか否か、

- （iii）前記装置の先行データ処理動作により桁上げビットがセットされた（C）か否か 10

- 、

- （iv）前記装置の先行データ処理動作中に算術演算のオーバーフローが発生した（V）か否か、

を表す4個の処理フラグを含む、データ処理装置。

**【請求項4】**

請求項1から請求項3のいずれか1つにおいて、前記メモリアクセス手段（110）は、メモリアドレスを前記データメモリ（120）に送信する手段と、

引き続きデータを前記データメモリに送信する手段、あるいは引き続きデータを前記データメモリから受信する手段と、

を含む、データ処理装置。 20

**【請求項5】**

請求項1から請求項4のいずれか1つにおいて、

前記メモリアクセス手段（110）は、異常終了制御信号（150）を発生させて、メモリアクセスが無効であることを示し、

前記条件テスト手段（200）は、条件不良制御信号（220）を発生させて、前記現在の命令を実行すべきではないことを示し、

前記装置は、前記条件制御手段（240）に供給する組合わせ制御信号を発生するため前記異常終了制御信号と前記条件不良制御信号とを組合せる手段（230）を含む、データ処理装置。

**【請求項6】**

請求項5において、前記組合わせる手段（230）は、論理和ゲートを含む、データ処理装置。 30

**【請求項7】**

請求項1から請求項6のいずれか1つにおいて、装置のデータ処理動作は、クロック信号によって制御される、データ処理装置。

**【請求項8】**

請求項1から請求項7のいずれか1つに記載の装置を含む集積回路。

**【請求項9】**

連続するデータ処理命令が、パイプライン方式で実行されるデータ処理方法であって、

1つまたはそれ以上の前記命令に対応してデータメモリにアクセスするステップ（110）と、 40

各メモリアクセスが無効か否かを検出するステップ（110）と、

各命令の実行中に、前に実行した命令によって発生する前記装置の処理状態に依存して、その命令を実行すべきか否かを検出するステップ（200）と、

を含み、

先行命令によって開始されたメモリアクセスが無効であること、あるいは現在の命令を実行すべきではないこと、のいずれかが検出された場合、現在の命令の完全実行を防止するステップ（230、240）、

を含む、データ処理方法。

**【発明の詳細な説明】**

## 発明の背景

## 発明の分野

本発明はデータ処理命令の実行に関する。

## 従来技術の説明

ある種のデータプロセッサには中央処理装置（CPU）が含まれてあり、CPUは現在実行中のデータ処理命令の制御のもとに、中間のメモリ管理ユニットを介して、ランダムアクセスメモリ（RAM）の中に格納されているデータにアクセスすることができる。かかるデータプロセッサについて以前に提案した例は、1993年にアドバンスト・リスク・マシンズ社（Advanced RISC Machines Limited）が発行したARM6データシートに説明されているARM6プロセッサである。

メモリアクセス中にメモリ管理ユニットは、現在のメモリアクセスを完了できないことを示す、異常終了（abort）信号を発生させることができる。異常終了信号はいろいろな理由で発生する。一例を挙げると、メモリアクセスの異常終了は、仮想記憶メモリを使用しているデータ処理システムで発生することがあるが、かかるデータ処理システムにおいては、RAMと低速のディスク記憶装置との間でデータが交換されるので、アドレス指定できるメモリ空間が、実装されているRAMの量より大きいという錯覚が起こる。このようなシステムにおいて、要求された仮想アドレスに対応するデータが、現在、RAMではなくディスク記憶装置に保持されていると、これらのデータにアクセスできるまでに遅延時間が発生するが、この遅延時間中にそのデータをディスク記憶装置からRAMに転送しなければならない。この場合、現在のメモリアクセスは異常終了し、それらのデータに対するアクセスは後で試行される。

メモリ管理ユニットから供給される異常終了信号は、失敗したメモリアクセスを開始した命令の実行を中止するにはあまりにも遅れて発生するが、次のデータ処理命令の実行、すなわち、失敗したメモリアクセスを開始した命令の後のデータ処理命令の実行を解除するためには使用できる。このことは有用である。その理由は、後続の命令は正常動作中のメモリアクセスに依存できるからである。

失敗したメモリアクセスを開始した命令の直後の命令の実行を解除するために異常終了信号を使用すると、異常終了信号のタイミングに厳しい条件が要求される。これに替る方法として、直後の命令の実行が完了した後その命令の実行結果を「元に戻す（undo）」複雑なメカニズムを備えなくてはならない。

添付図面の第1図は、以前に提案し、上に引用したデータプロセッサによるデータ書き込み動作中（本動作中にデータがRAMに書き込まれる）の、異常終了信号のタイミング条件の概略を示すタイムチャートである。

第1図を参照すると、クロック信号は、データプロセッサによるデータ処理命令の実行を制御している。データ書き込み動作が開始されると、データプロセッサは、メモリ管理ユニットにメモリアドレス20を供給するとともに、クロック信号の半サイクル後で、そのアドレスに書き込まれるデータ30を出力する。

（たとえば、そのアドレスに対応するデータは仮想メモリシステムのディスク記憶装置の中に保持されているため）メモリアドレス20が無効であることをメモリ管理ユニットが検出すると、メモリ管理ユニットは異常終了信号40を発生させ、この信号をデータプロセッサに供給する。

（通常）書き込むべきデータがデータバスに載せられてしまった後は、メモリ管理ユニットからの応答を待つ必要がないから、データ書き込み命令の次の命令は直ちに実行される。したがって、直後の命令を解除するのに間に合うように異常終了信号が到着するには、以前に提案し、上に引用したデータプロセッサは、書き込むべきデータを出力するよりもクロック信号の半サイクル前に、異常終了信号が有効でなければならない。

このタイミングの制約を実現させることは実際には困難なので、（メモリ管理ユニットの電力消費を大きくして）メモリ管理ユニットを非常に速く動作させなければならない。

また、以前に提案し、上に引用したデータプロセッサは、このデータプロセッサの全命令セットを条件付きで実行する。これは、最大4つの処理フラグの現在の状態を、各命令に

10

20

30

40

50

含まれている条件コードによって定義される各状態と比較することにより達成される。この比較は命令の実行と並行して行われる。条件コードによって指定された条件と処理フラグの状態が一致しないと、命令の完全実行を防止する。

この形式のプロセッサを説明する別の文献には、論文、「ARM6:高性能低消費電力マクロセル (ARM6:High Performance Low Power Consumption Macrocell)」M.Muller、COMPICON、1993年春期号、頁80から頁87、がある。本論文には、上に引用したARM6のメモリ異常終了機能と条件付き命令実行機能が説明されている。

#### 発明の要約

本発明は、連続するデータ処理命令がパイプライン方式によって実行されるデータ処理装置を提供する。このデータ処理装置は、1つまたはそれ以上の命令に対応してデータメモリにアクセスするとともに、各メモリアクセスが無効か否かを検出する手段を含むメモリアクセス手段と、前に実行した命令によって発生する装置の処理状態に対応しつつ各命令の実行中に動作して、その命令を実行すべきか否かを検出する条件テスト手段とを含み、メモリアクセス手段と条件テスト手段とに応答して、メモリアクセス手段が、先行命令によって開始されたメモリアクセスが無効であることを検出するか、あるいは条件テスト手段が、現在の命令を実行すべきではないことを検出するか、のいずれかの場合、現在の命令の完全実行を防止する条件付き制御手段を含むことを特徴としている。

本発明によるデータ処理装置においては、完全条件付きの命令セットが使用されており、各命令の完全実行を条件付きで防止するメカニズムは、メモリ異常終了を処理するためにも使用されている。したがって、各命令の実行中に、その命令を実行すべきか否かを条件テスト手段が検出すると同時に、先行命令によって開始されたメモリアクセスに関係するメモリ異常終了信号を受信してよい。これにより、各命令に対するメモリ異常終了を、以前に提案し上に引用したデータプロセッサに考慮されていた時間よりも後で処理してよいことになる。

好適実施例において、本装置は、データ処理装置の現在の処理状態を示すデータを格納する1つまたはそれ以上の処理フラグを含み、各命令には、実行すべきその命令に必要な処理フラグの状態を定義する条件コードが含まれており、条件テスト手段は、各命令の条件コードによって定義される処理フラグの必要な状態を処理フラグの現在の状態と比較する。条件コードは、特定の処理フラグを特定の論理状態にセットすべきこと、あるいはその処理フラグの状態が、現在の命令を実行すべきか否かに影響を与えないことを指定することができる。極端な場合、条件コードは、どの処理フラグの状態にも無関係に、特定の命令を実行すべきことを指定することができる。

処理フラグは、本装置の処理状態に関する各種機能を指定することができる。好適実施例において、本装置には、

- (i) 装置の先行データ処理動作により負の結果が発生したか否か、

- (ii) 装置の先行データ処理動作によりゼロの結果が発生したか否か、

- (iii) 装置の先行データ処理動作により桁上げビットがセットされたか否か、

- (iv) 装置の先行データ処理動作中に算術演算のオーバーフローが発生したか否か、

- を表す4つの処理フラグが含まれている。

望ましくは、メモリアクセス手段は、メモリアドレスをデータメモリに送信する手段と、引き続きデータをデータメモリに転送する手段あるいは引き続きデータメモリからデータを受信する手段とを含んでいる。

条件付き制御手段がメモリアクセス手段と条件テスト手段との両方に対して好都合に応答するようになるためには、メモリアクセス手段は異常終了信号を発生させてメモリアクセスが無効であることを示すこと、条件テスト手段は条件不良制御信号 (condition failure control signal) を発生させて現在の命令を実行すべきではないことを示すこと、および本装置は条件制御手段に供給する組合せ制御信号を発生するため異常終了制御信号と条件不良制御信号とを組合せる手段を備えることが望ましい。

簡潔で有利な実施例においては、組合わせる手段は論理和ゲートを含んでいる。

便利な実施例においては、装置のデータ処理動作はクロック信号によって制御される。

10

20

30

40

50

第2の側面から見ると、本発明は上に定義した装置を含む集積回路を提供する。

第3の側面から見ると、本発明はデータ処理方法を提供する。このデータ処理方法においては、連続するデータ処理命令はパイプライン方式で実行され、1つまたはそれ以上の命令に応答してデータメモリにアクセスするステップと、各メモリアクセスが無効か否かを検出するステップと、各命令の実行中に、前に実行した命令によって発生する装置の処理状態に依存して、その命令を実行すべきか否かを検出するステップとを含み、先行命令によって開始されたメモリアクセスが無効であること、あるいは現在の命令を実行すべきではないこと、のいずれかが検出された場合、現在の命令の完全実行を防止するステップを含むことを特徴としている。

#### 【図面の簡単な説明】

10

添付の図面を参照して例を示すという方法で本発明を説明する。なお全図面について、同じ部分は同じ参照符号で示されている。

第1図は、以前に提案したデータプロセッサによるデータ書き込み動作中の異常終了信号のタイミング条件の概略を示すタイムチャートである。

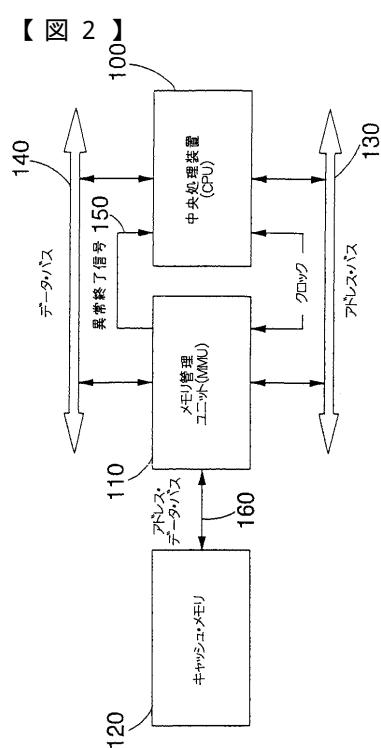

第2図は、本発明の実施例によるデータ処理装置の概略を示すブロック図である。

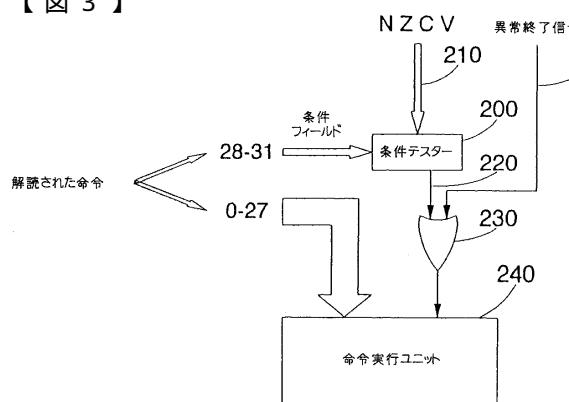

第3図は、中央処理装置の概略を示すブロック図である。

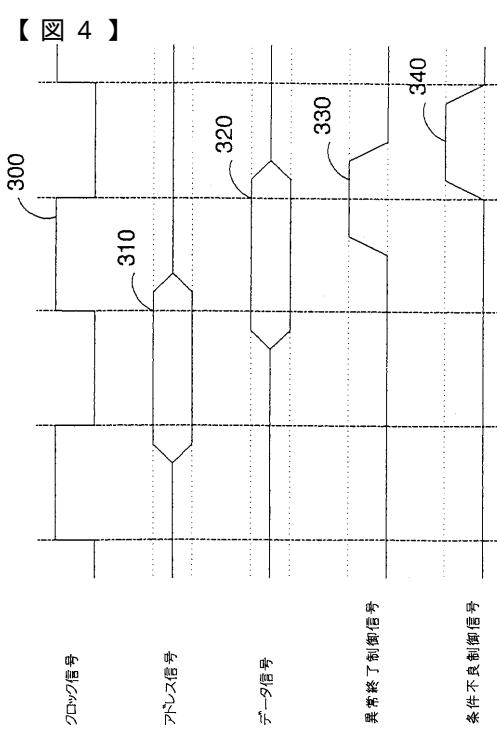

第4図は、第2図のデータ処理装置によるデータ書き込み動作中の異常終了信号のタイミング条件の概略を示すタイムチャートである。

#### 好適実施例の説明

つぎに第2図を参照すると、本発明の実施例によるデータ処理装置の概略を示すブロック図が示されている。本装置は中央処理装置(CPU)100、メモリ管理ユニット(MMU)110、ランダムアクセスメモリ(RAM)120を含んでいる。CPU100とMMU110とは、メモリアドレスを交換するアドレスバス130とデータを交換するデータバス140で接続されている。また、失敗したメモリアクセスあるいは無効なメモリアクセスを示す異常終了信号を運ぶ異常終了制御ライン150も、MMU110からCPU100に用意されている。

20

クロック信号はCPU100とMMU110に供給され、両ユニットの動作を制御する。各データ処理命令は、(その命令の性質に依存する)クロック信号の特定数のサイクル中にCPU100によって実行され、MMU110によるメモリアクセスはクロック信号に同期して実行される。

MMU110はCPU100とクロック信号の制御のもとに動作して、RAM120に格納されているデータにアクセスする。したがって、MMUは複数のアドレス・データ・ライン160によりRAMに接続される。

30

第3図は、中央処理装置100の一部の概略を示すブロック図である。CPU100は、処理動作およびメモリ動作が実質的に連続して実行されることを可能にする命令パイプライン方式(instruction pipelining)を使用している。普通、1つのデータ処理命令が実行されている間に、その命令の次の命令は解読中であり、第3の命令はメモリからフェッチされている。この装置は、3段パイプライン(three-stage execution pipeline)と呼ばれている。

CPU100の第3図に示す部分において、メモリからフェッチされて解読されているデータ処理命令が転送されて実行される。データ処理命令は32ビットのデータ語であり、その内のビット28からビット31は4ビットの条件フィールド(condition field)を形成する。残りのビット(ビット0からビット27)は、その命令に対応して実行される演算を定義し、ある場合には、演算が実行されるオペランドを定義する。

40

条件フィールド(ビット28からビット31)が条件テスト200に送られると、条件テスト200は、この条件フィールドのビットを所定の16個の条件コードと比較する。この16個の条件コードは、Nフラグ、Zフラグ、Cフラグ、Vフラグと呼ばれ、4個のプロセッサフラグ210の1つまたはそれ以上のフラグの状態を定義する。これらのフラグは、前に実行した命令により発生するCPU100の処理状態を表す。

Nフラグは、前に実行したCPU100の算術演算の負の結果を表し、Zフラグは、前に実行したCPU100の演算のゼロ(等しい)結果を表し、Cフラグは、前に実行したCPU100の演算中に桁上げビットがセットされたか否かを表し、Vフラグは、前に実行したCPU100の演算中

50

に算術演算のオーバーフローが発生したことを示す。

条件フィールドの4ビットの間の関係と、Nフラグ、Zフラグ、Cフラグ、Vフラグに適用される条件とを下表に示す。

0 0 0 0 = EQ - Zセット (等しい)

0 0 0 1 = NE - Zクリア (等しくない)

0 0 1 0 = CS - Cセット (符号なしの、より大きいか同じ)

0 0 1 1 = CC - Cクリア (符号なしの、より小さい)

0 1 0 0 = MI - Nセット (負)

10

0 1 0 1 = PL - Nクリア (正あるいはゼロ)

0 1 1 0 = VS - Vセット (オーバーフロー発生)

0 1 1 1 = VC - Vクリア (オーバーフローは発生しない)

1 0 0 0 = HI - CセットでかつZクリア (符号なしの、より大きい)

1 0 0 1 = LS - CクリアあるいはZセット (符号なしの、より小さいか同じ)

20

1 0 1 0 = GE - NセットでかつVセットあるいはNクリアでかつVクリア (より大きいか等しい)

1 0 1 1 = LT - NセットでかつVクリアあるいはNクリアでかつVセット (より小さい)

1 1 0 0 = GT - Zクリアでかつ、NセットとVセットとのいずれか、あるいはNクリアでかつVセット (より大きい)

30

1 1 0 1 = LE - Zセット、あるいはNセットでかつVクリア、あるいはNクリアでかつVセット (より小さいか等しい)

1 1 1 0 = AL - 常に成立する

1 1 1 1 = NV - 常に成立しない

条件テスタ200は、現在の命令の条件フィールドのどのビットがセットされているかに依存して、上に示したフラグの状態をテストする。この比較は、現在の命令の実行中に行われる。適切なフラグが、条件フィールドが指定した状態にセットされているときにかぎり、現在の命令の実行を完了することが可能になる。

40

AL (常に成立する) 条件が指定されると、フラグに関係なく命令が実行される。NV (常に成立しない) 条件コードは、フラグ210の状態に関係なく命令の実行を防止する。

条件テスタ200は、現在の命令を完全に実行すべきか否かを示す出力信号220を発生させる。出力信号220は、異常終了制御ライン150を介し、ORゲート230を使用して、MMU110からCPU100に供給される異常終了信号と組合わされる。したがって、条件テスタ200が現在の命令を完全に実行すべきではないことを示しているか、あるいはMMU110が異常終了信号を立ち上げているかのいずれかの場合、ORゲート230の出力がセットされる。

命令実行ユニット240は、各命令の実行すべき演算を定義するビット0からビット27と、ある場合には、演算が実行されるオペランドを受信する。現在の命令の実行中に(つまり

50

、条件テスタ200とORゲート230の伝搬遅延と処理遅延の後で)、現在の命令を完全に実行すべきか否かを示すORゲート230の出力を受信する。ORゲート230が現在の命令を完全に実行すべきではないことを示している場合、装置に付随するレジスタの場所やメモリの場所をどれも変更せずに、この命令は解除される。

条件テスタ200と命令実行ユニット240は、以前に提案し、上に引用したARM6プロセッサの対応する構成部品と同じ形式にすることができる。

第3図の装置を使用した結果、異常終了信号に対する厳しいタイミングは大幅に緩和されるので、先行命令によって開始されたメモリアクセスに関する異常終了信号は、各命令の実行中、後の段階でセットすることができる。

命令フェッチ動作が失敗した結果として異常終了信号が受信された場合、その命令は、上に述べた3段階命令パイプラインの後の段階で廃棄されるだけである。 10

メモリから読出されたデータが適切なプロセッサレジスタにロードされるための時間を与えるために、データ読出し動作の後にはメモリをアクセスしない(内部)プロセッササイクルが続く。したがって、データ読出し動作が失敗した結果として異常終了信号が受信された場合、読出し動作の後に続く内部サイクルは、MMU110がメモリから供給したいかなるデータ(このデータには殆んどエラーがある)も無視し、(たとえばプロセッサレジスタなど)意図していた場所に格納しないようにするため時間を与える。

命令の実行とデータ書込み動作に対する異常終了信号の受信とのタイミング関係が、第4図に示されているが、本図中にはアドレスバス130とデータバス140の状態とともに、CPU100による命令の実行を制御するクロック信号300が示されている。 20

データ書込み動作を開始するため、CPU100はアドレスバスにアドレス310を載せる。クロック信号300の半サイクル後に、CPU100はデータバスにデータ320を載せる。この状態になると、CPU100は、クロック信号300の次のサイクル中に次の命令を実行することができる。

(第4図に330で示すように)異常終了信号が受信された場合、あるいは条件テスタ200が、次の命令を実行すべきではないと決定した場合(データがデータバスに載せられていて、340で示される後の半サイクル中に、条件テスタ200がこれを決定する)、データ320がデータバスに載せられると同時に、次の命令の実行は中止される。

添付の図面を参照して、本発明の判りやすい実施例を詳細に説明してきたが、本発明はこれらの詳細な実施例に限定されるものではないこと、さらには当業者ならば、添付の請求の範囲に定義される本発明の範囲から逸脱せずに、各種の変更や修正ができる。 30

【図3】

【図1】

【図2】

【図4】

---

フロントページの続き

(72)発明者 ジャガー, デビッド ビビアン

イギリス国シービー 1 4ティーエヌ ケンブリッジ, チェリー ヒントン, マンドリル クロー

ス 48

審査官 後藤 彰

(56)参考文献 特開平5-81016(JP, A)

特開昭57-196356(JP, A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

G06F 9/30-9/38