(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7039237号**

**(P7039237)**

(45)発行日 令和4年3月22日(2022.3.22)

(24)登録日 令和4年3月11日(2022.3.11)

(51)国際特許分類

|         |                  |     |         |        |       |

|---------|------------------|-----|---------|--------|-------|

| H 0 4 N | 9/07 (2006.01)   | F I | H 0 4 N | 9/07   | A     |

| H 0 1 L | 27/146 (2006.01) |     | H 0 1 L | 27/146 | A     |

| H 0 4 N | 5/374(2011.01)   |     | H 0 4 N | 5/374  |       |

| H 0 4 N | 5/3745(2011.01)  |     | H 0 4 N | 5/3745 | 7 0 0 |

| H 0 4 N | 5/378(2011.01)   |     | H 0 4 N | 5/378  |       |

請求項の数 14 (全22頁)

(21)出願番号 特願2017-192057(P2017-192057)

(22)出願日 平成29年9月29日(2017.9.29)

(65)公開番号 特開2019-68271(P2019-68271A)

(43)公開日 平成31年4月25日(2019.4.25)

審査請求日 令和2年9月25日(2020.9.25)

(73)特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74)代理人 100126240

弁理士 阿部 琢磨

100124442

弁理士 黒岩 創吾

(72)発明者 波多野 雄一朗

東京都大田区下丸子3丁目30番2号キ

ヤノン株式会社内

櫻井 克仁

東京都大田区下丸子3丁目30番2号キ

ヤノン株式会社内

古林 篤

東京都大田区下丸子3丁目30番2号キ

最終頁に続く

(54)【発明の名称】 撮像装置、撮像システム、移動体、回路チップ

**(57)【特許請求の範囲】****【請求項1】**

第1色のカラーフィルタを備える、複数行および複数列に渡って配され、画素信号を出力する複数の第1画素を有する第1画素群と、

前記第1色とは別の色である第2色のカラーフィルタを備える、複数行および複数列に渡って配され、画素信号を出力する複数の第2画素を有する第2画素群と、

前記第1画素群のうち、前記複数列のうちの第1列に配される第1画素が接続された第1信号線と、

前記第2画素群のうち、前記第1列に配される第2画素が接続された第2信号線と、

前記第1画素群のうち、前記第1列に配される別の第1画素が接続された第3信号線と、

前記第2画素群のうち、前記第1列に配される別の第2画素が接続された第4信号線と、

前記第1信号線が接続される第1接続部と、

前記第2信号線が接続される第2接続部と、

前記第3信号線が接続される第3接続部と、

前記第4信号線が接続される第4接続部とを有する第1チップと、

第1A/D変換部と、

第2A/D変換部と、

前記第1A/D変換部にそれぞれ接続される、第5接続部および第6接続部と、

前記第2A/D変換部にそれぞれ接続される、第7接続部および第8接続部と、

を有する第2チップとを有し、

前記第1チップと前記第2チップは積層され、

前記第1接続部と前記第5接続部が接続され、

前記第3接続部と前記第6接続部が接続され、

前記第2接続部と前記第7接続部が接続され、

前記第4接続部と前記第8接続部が接続され、

前記第7接続部および前記第8接続部は接続されず、かつ前記第5接続部と前記第6接続部が接続される入力部および前記第1A/D変換部に接続される出力部を有する第1選択部と、前記第5接続部および前記第6接続部は接続されず、かつ前記第7接続部、前記第8接続部が接続される入力部および前記第2A/D変換部に接続される出力部を有する第2選択部とを前記第2チップが有し、

前記第1信号線から前記第1選択部の前記入力部に前記第1画素から前記画素信号が出力される期間に、前記第2信号線から前記第2選択部の前記入力部に前記第2画素から前記画素信号が出力されることを特徴とする撮像装置。

**【請求項2】**

平面視において、前記第1接続部、前記第5接続部は前記第1A/D変換部と重なっており、平面視において、前記第2接続部、前記第7接続部は前記第2A/D変換部と重なっていることを特徴とする請求項1に記載の撮像装置。

**【請求項3】**

前記第1信号線と、前記第1接続部とを各々が備える複数の第1組と、前記第2信号線と、前記第2接続部とを各々が備える複数の第2組とを前記第1チップが有することを特徴とする請求項1または2に記載の撮像装置。

**【請求項4】**

前記第1選択部と前記第2選択部の各々が、マルチプレックス回路であることを特徴とする請求項1～3のいずれか1項に記載の撮像装置。

**【請求項5】**

平面視において、前記第1画素と前記第2画素とが前記第1A/D変換部と重なることを特徴とする請求項1～4のいずれか1項に記載の撮像装置。

**【請求項6】**

前記第1A/D変換部と、前記第2A/D変換部のそれぞれが、逐次比較型のA/D変換器であることを特徴とする請求項1～5のいずれか1項に記載の撮像装置。

**【請求項7】**

前記第1A/D変換部と、前記第2A/D変換部のそれぞれが、ランプ信号と前記画素信号とを比較する比較器を備えることを特徴とする請求項1～5のいずれか1項に記載の撮像装置。

**【請求項8】**

前記第1色のカラーフィルタと、前記第2色のカラーフィルタとの透過率のピーク波長が異なることを特徴とする請求項1～7のいずれか1項に記載の撮像装置。

**【請求項9】**

前記第1画素群と前記第2画素群のそれぞれの画素は、光電変換部と、前記光電変換部の電荷に基づく信号を出力する増幅トランジスタとを有し、

第1チップは、前記複数の第1画素と前記複数の第2画素のそれぞれが接続される第1配線を有し、

第2チップは、電流源と前記電流源に接続される第2配線を有し、

前記電流源は、前記第2配線、前記第1配線を介して前記増幅トランジスタに電流を供給することを特徴とする請求項1～8のいずれか1項に記載の撮像装置。

**【請求項10】**

請求項1～9のいずれか1項に記載の撮像装置と、

前記撮像装置が出力する信号を処理することによって画像を生成する信号処理部とを有することを特徴とする撮像システム。

**【請求項11】**

10

20

30

40

50

請求項 1 ~ 9 のいずれか 1 項に記載の撮像装置と、

前記撮像装置からの信号に基づく視差画像から、対象物までの距離情報を取得する距離情報取得手段と、を有する移動体であって、

前記距離情報に基づいて前記移動体を制御する制御手段をさらに有することを特徴とする移動体。

【請求項 1 2】

画素チップと回路チップとを積層した撮像装置のための回路チップであって、

前記画素チップは、

第 1 色のカラーフィルタを備える、複数行および複数列に渡って配され、画素信号を出力する複数の第 1 画素を有する第 1 画素群と、

10

前記第 1 色とは別の色である第 2 色のカラーフィルタを備える、複数行および複数列に渡って配され、画素信号を出力する複数の第 2 画素を有する第 2 画素群と、

前記第 1 画素群のうち、前記複数列のうちの第 1 列に配される第 1 画素が接続された第 1 信号線と、

前記第 2 画素群のうち、前記第 1 列に配される第 2 画素が接続された第 2 信号線と、

前記第 1 画素群のうち、前記第 1 列に配される別の第 1 画素が接続された第 3 信号線と、

前記第 2 画素群のうち、前記第 1 列に配される別の第 2 画素が接続された第 4 信号線と、

前記第 1 信号線が接続される第 1 接続部と、

前記第 2 信号線が接続される第 2 接続部と、

前記第 3 信号線が接続される第 3 接続部と、

20

前記第 4 信号線が接続される第 4 接続部とを備えた構成であり、

前記回路チップは、

第 1 A D 変換部と、

第 2 A D 変換部と、

前記第 1 A D 変換部にそれぞれ接続される、第 5 接続部および第 6 接続部と、

前記第 2 A D 変換部にそれぞれ接続される、第 7 接続部および第 8 接続部と、

を有し、

前記第 5 接続部は前記第 1 接続部と接続するための接続部であり、

前記第 6 接続部は前記第 3 接続部と接続するための接続部であり、

前記第 7 接続部は前記第 2 接続部と接続するための接続部であり、

30

前記第 8 接続部は前記第 4 接続部と接続するための接続部であり、

前記第 7 接続部および前記第 8 接続部は接続されず、かつ前記第 5 接続部と前記第 6 接続部が接続される入力部および前記第 1 A D 変換部に接続される出力部を有する第 1 選択部と、前記第 5 接続部および前記第 6 接続部は接続されず、かつ前記第 7 接続部、前記第 8 接続部が接続される入力部および前記第 2 A D 変換部に接続される出力部を有する第 2 選択部とを前記回路チップが有し、

前記第 5 接続部から前記第 1 選択部の前記入力部に前記第 1 画素から前記画素信号が出力される期間に、前記第 7 接続部から前記第 2 選択部の前記入力部に前記第 2 画素から前記画素信号が出力されることを特徴とする回路チップ。

【請求項 1 3】

さらに第 1 選択部と第 2 選択部を備え、

前記第 1 選択部は、前記第 5 接続部と前記第 6 接続部の一方を選択して前記第 1 A D 変換部に接続し、

前記第 2 選択部は、前記第 7 接続部と前記第 8 接続部の一方を選択して前記第 2 A D 変換部に接続することを特徴とする請求項 1\_2 に記載の回路チップ。

【請求項 1 4】

前記第 1 選択部と前記第 2 選択部の各々が、マルチプレックス回路であることを特徴とする請求項 1\_3 に記載の回路チップ。

【発明の詳細な説明】

【技術分野】

40

50

**【 0 0 0 1 】**

本発明は、撮像装置、撮像システム、移動体に関する。

**【背景技術】****【 0 0 0 2 】**

複数の画素が複数行、複数列に渡って配された撮像装置が知られている。この撮像装置の一例として、特許文献1にあるように、複数の画素が配された第1チップと、画素が出力する信号をA/D変換するA/D変換部が配された第2チップとが積層された撮像装置が知られている。

**【先行技術文献】****【特許文献】****【 0 0 0 3 】**

**【文献】特開2015-126043号公報**

10

**【発明の概要】****【発明が解決しようとする課題】****【 0 0 0 4 】**

特許文献1に記載の撮像装置は、画素とA/D変換部との好適な接続関係について、検討が為されていない。複数の第1画素に第1色のカラーフィルタが配され、複数の第2画素に第2色のカラーフィルタが配される場合における、画素とA/D変換部との好適な接続関係について検討されていない。例えば、1つのA/D変換部が第1色のカラーフィルタが配された第1画素と、第2色のカラーフィルタが配された第2画素のそれぞれが出力する信号をA/D変換する場合、第1色、第2色のそれぞれに応じた処理を要することがある。このような場合には、A/D変換、あるいはA/D変換後の信号処理が複雑になるという課題がある。

20

**【 0 0 0 5 】**

本発明は、複数の第1画素に第1色のカラーフィルタが配され、複数の第2画素に第2色のカラーフィルタが配される場合における、画素とA/D変換部との好適な接続関係を備える撮像装置を提供する。

**【課題を解決するための手段】****【 0 0 0 6 】**

本発明は上記の課題を鑑みて為されたものであり、一の態様は、第1色のカラーフィルタを備える、複数行および複数列に渡って配され、画素信号を出力する複数の第1画素を有する第1画素群と、前記第1色とは別の色である第2色のカラーフィルタを備える、複数行および複数列に渡って配され、画素信号を出力する複数の第2画素を有する第2画素群と、前記第1画素群のうち、前記複数列のうちの第1列に配される第1画素が接続された第1信号線と、前記第2画素群のうち、前記第1列に配される第2画素が接続された第2信号線と、前記第1画素群のうち、前記第1列に配される別の第1画素が接続された第3信号線と、前記第2画素群のうち、前記第1列に配される別の第2画素が接続された第4信号線と、前記第1信号線が接続される第1接続部と、前記第2信号線が接続される第2接続部と、前記第3信号線が接続される第3接続部と、前記第4信号線が接続される第4接続部とを有する第1チップと、第1A/D変換部と、第2A/D変換部と、前記第1A/D変換部にそれぞれ接続される、第5接続部および第6接続部と、前記第2A/D変換部にそれぞれ接続される、第7接続部および第8接続部と、を有する第2チップとを有し、前記第1チップと前記第2チップは積層され、前記第1接続部と前記第5接続部が接続され、前記第3接続部と前記第6接続部が接続され、前記第2接続部と前記第7接続部が接続され、前記第4接続部と前記第8接続部が接続され、前記第7接続部および前記第8接続部は接続されず、かつ前記第5接続部と前記第6接続部が接続される入力部および前記第1A/D変換部に接続される出力部を有する第1選択部と、前記第5接続部および前記第6接続部は接続されず、かつ前記第7接続部、前記第8接続部が接続される入力部および前記第2A/D変換部に接続される出力部を有する第2選択部とを前記第2チップが有し、前記第1信号線から前記第1選択部の前記入力部に前記第1画素から前記画素信号が出力される

30

40

50

期間に、前記第2信号線から前記第2選択部の前記入力部に前記第2画素から前記画素信号が出力されることを特徴とする撮像装置である。

【発明の効果】

【0007】

本発明により、複数の第1画素に第1色のカラーフィルタが配され、複数の第2画素に第2色のカラーフィルタが配される場合における、画素とA/D変換部との好適な接続関係を備える撮像装置が提供される。

【図面の簡単な説明】

【0008】

【図1】撮像装置の構成を示す図

10

【図2】平面視における撮像装置の画素と信号処理回路の配置を示す図

【図3】画素と信号処理回路を示す図

【図4】画素と信号処理回路の接続を示す図

【図5】画素と信号処理回路の接続を示す図

【図6】画素の等価回路を示す図

【図7】撮像装置の動作を示す図

【図8】画素と信号処理回路の接続を示す図

【図9】A/D変換回路の等価回路を示す図

【図10】A/D変換回路の動作を示す図

【図11】撮像システムの構成を示す図

20

【図12】移動体の構成を示す図

【図13】撮像システムの動作を示す図

【発明を実施するための形態】

【0009】

以下、図面を参照しながら各実施例を説明する。なお、以下の説明では、特に断りの無い限り、トランジスタはN型トランジスタであるものとする。しかし、以下に述べる実施例はN型トランジスタに限定されるものではなく、P型トランジスタを適宜用いてもよい。その場合には、トランジスタのゲート、ソース、ドレインの電位を、実施例中の説明に対し適宜変更することができる。例えば、スイッチとして動作させるトランジスタであれば、ゲートに供給する電位のローレベルとハイレベルとを、実施例中の説明に対し逆転させるようにすればよい。

30

【0010】

(実施例1)

(撮像装置の全体構成)

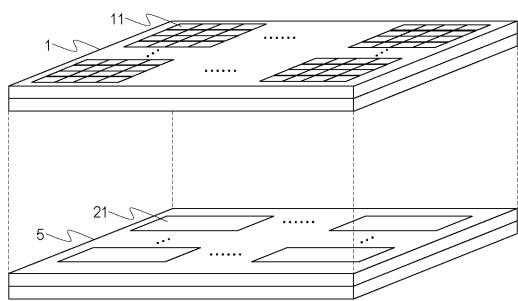

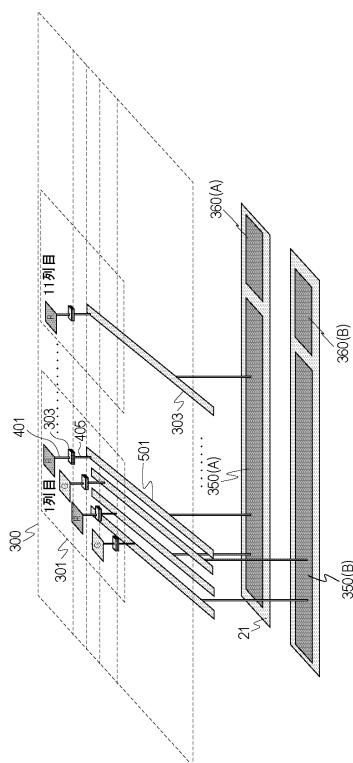

図1は、本実施例の撮像装置が備える、第1チップ1、第2チップ5を示した図である。第1チップ1は、複数行および複数列に渡って画素11が配された画素チップである。また、第2チップ5は、複数行および複数列に渡って、信号処理回路21が配された回路チップである。なお、ここでは画素11と信号処理回路21のみを図示しているが、他に画素11を制御する制御線、画素11が出力する信号を伝送する信号線が適宜、第1チップ1に配される。また、垂直走査回路、タイミングジェネレータ等の駆動回路が適宜、第1チップ1あるいは第2チップ5に配される。

40

【0011】

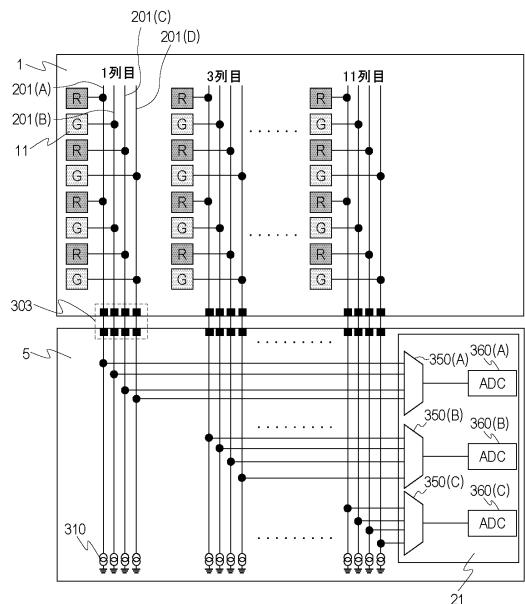

(平面視における、画素と信号処理回路の配置関係)

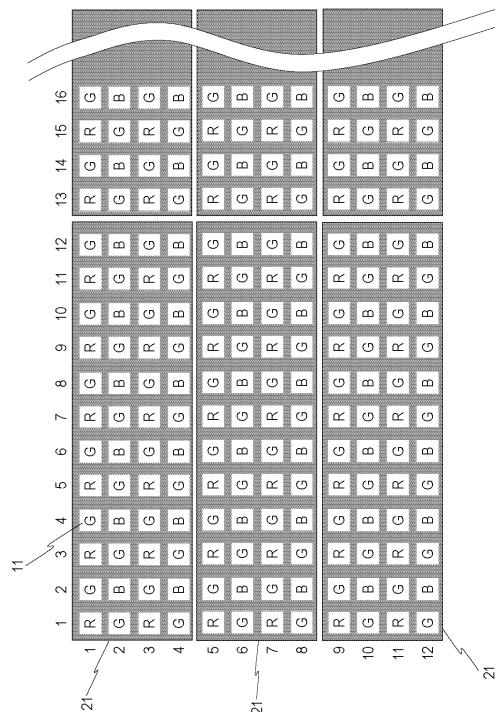

図2は、平面視における、第1チップ1が備える画素11と、第2チップ5が備える信号処理回路21のレイアウトを示した図である。図2では、画素11が備えるカラーフィルタの色も合わせて示している。図2に示したRは、画素11が赤(R)のカラーフィルタを備えることを示している。以下、同じくG、Bはそれぞれ、画素11が緑(G)、青(B)のカラーフィルタを備えることを示している。

【0012】

別の言い方をすれば、第1色に対応する波長の光が入射する画素と、第2色に対応する波

50

長の光が入射する画素とを備えるとも言える。

**【 0 0 1 3 】**

典型的には、赤色に対応する波長は 600 ~ 830 nm である。また、緑色に対応する波長は、500 ~ 600 nm である。また、青色に対応する波長は 360 ~ 500 nm である。

**【 0 0 1 4 】**

また、カラーフィルタの色は、カラーフィルタの透過率がピークとなるピーク波長で区別してもよい。典型的には、青色のカラーフィルタの透過率のピーク波長は約 450 nm である。また、緑色のカラーフィルタの透過率のピーク波長は約 540 nm である。また、赤色のカラーフィルタの透過率のピーク波長は約 630 nm である。

10

**【 0 0 1 5 】**

1つの画素 11 のカラーフィルタは、単一のカラーフィルタ部材によって構成されていてもよい。また、1つの画素 11 のカラーフィルタは、カラーフィルタが設けられる領域の一部と他の一部とで、実質的に同一色とみなせる範囲で、互いに組成が異なるカラーフィルタ部材が設けられた例であってもよい。

**【 0 0 1 6 】**

1つの信号処理回路 21 は、複数行および複数列に渡って配された画素 11 と重なるように配置されている。ここでは、1つの信号処理回路 21 は、4 行 12 列の画素 11 に重なるように配置されている。後述するが、信号処理回路 21 は、マルチプレックス回路、A/D 変換回路を有する。したがって、1つの信号処理回路 21 のマルチプレックス回路と A/D 変換回路の一方、あるいは両方が、画素 11 に重なるように配置されていると言える。

20

**【 0 0 1 7 】**

また、後述するが、1つの信号処理回路 21 の A/D 変換回路は、第 1 色のカラーフィルタを備える画素 11 が出力する信号を A/D 変換し、第 2 色のカラーフィルタを備える画素 11 が出力する信号の A/D 変換を行わない。したがって、1つの信号処理回路 21 の A/D 変換回路とマルチプレックス回路の一方あるいは両方は、A/D 変換を行う対象の画素 11 と、A/D 変換を行わない対象の画素 11 との双方に対し、平面視において重なる関係となっている。

**【 0 0 1 8 】**

なお、この配置は一例であって、本実施例では、1つの信号処理回路 21 に対し、複数行、複数列の画素 11 が配されている形態を採用することができる。

30

**【 0 0 1 9 】**

(撮像装置の等価回路)

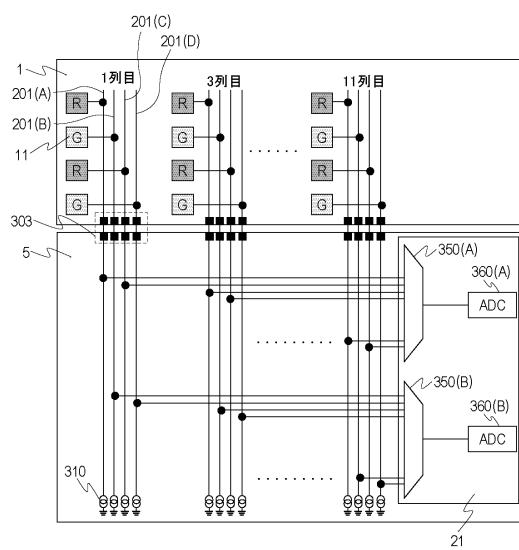

図 3 は、図 1、図 2 に示した撮像装置のブロック図を示している。図 3 では、図 2 に示した画素 11 のうち、奇数列の画素 11 のみを示している。第 1 チップ 1 の画素 11 は、1 列の画素 11 に対し、4 本の信号線 201 (A) ~ (D) を有する。なお、以下では信号線 201 (A) ~ (D) を区別なく表記する場合には、単に信号線 201 と表記する。1 行目の画素 11 は信号線 201 (A) に接続されている。以下、同様に 2 ~ 4 行目の画素 11 は、順に信号線 201 (B) ~ (D) に接続されている。信号線 201 (A) ~ (D) は、他の列においても、1 列目の画素 11 と同じように配されている。

40

**【 0 0 2 0 】**

信号線 201 (A)、201 (C) のそれぞれは、接続部 303 を介して、信号処理回路 21 が備えるマルチプレックス回路（以下、MPX 回路と表記する）350 (A) に接続されている。また、信号処理回路 21 は、A/D 変換回路（以下、明細書および図面にて ADC と表記する）360 (A)、360 (B) を有する。MPX 回路 350 (A) は、信号線 201 (A)、201 (C) に接続される入力部と、ADC 360 (A) に接続される出力部とを備える第 1 選択部である。

**【 0 0 2 1 】**

信号線 201 (B)、201 (D) のそれぞれは、接続部 303 を介して、信号処理回路 21 が備える MPX 回路 350 (B) に接続されている。MPX 回路 350 (B) は、信

50

号線 201(B)、201(D)に接続される入力部と、ADC360(B)に接続される出力部とを備える第2選択部である。

#### 【0022】

図3に示しているように、ADC360(A)に接続される画素11は全て、Rのカラーフィルタを備える画素11である。一方、ADC360(B)に接続される画素11は全て、Gのカラーフィルタを備える画素11である。このように、各々が第1色(R)のカラーフィルタを備える複数の第1画素11は、第2AD変換部であるADC360(B)に接続されずに第1AD変換部であるADC360(A)に接続される。また、各々が第2色(G)のカラーフィルタを備える複数の第1画素11は、第1AD変換部であるADC360(A)に接続されずに第2AD変換部であるADC360(B)に接続される。

10

#### 【0023】

また、図3に示したように、第2チップ5は電流源310を有する。電流源310は、接続部303を介して、各列の信号線201に電流を供給する。

#### 【0024】

##### (撮像装置の接続部周りの断面構造)

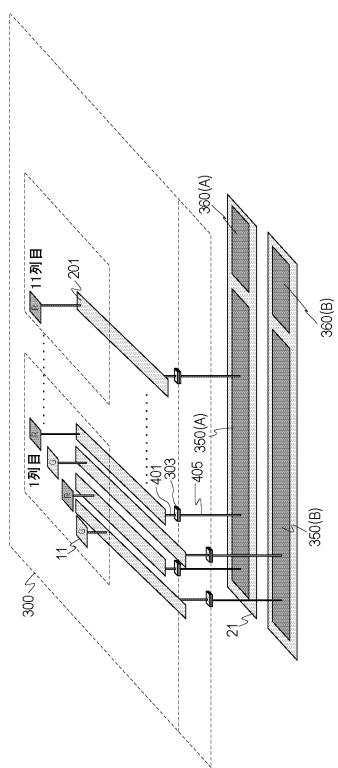

図4は、図3に示した撮像装置の斜視図である。図4では、4行1列に配された画素11と、1行目11列目の画素11を中心記載している。図1に示した第1チップ1と第2チップ5は、接合面300で接合されている。

#### 【0025】

本実施例の撮像装置は、裏面照射型の撮像装置である。画素11は、不図示の光電変換部を備える。この光電変換部と、接合面300との間に信号線201が設けられている。信号線201は、画素11の所定の方向(図では列に沿った方向)に延在している。信号線201は、接続配線401を介して接続部303に接続される。また、MPX回路350(A)は、接続配線405を介して接続部303に接続される。接続配線401、接続配線405、接続部303は、平面視において重なるように配置されている。信号処理回路21と信号線201との接続は、接続配線405に対して、平面視において重なる位置に接続配線401を形成することによって行うことができるとも言える。そして、所定の方向に沿って延在する信号線201と接続配線401とを接続することによって、信号線201と、MPX回路350とを接続することができる。信号線201が所定の方向に延在していることにより、接続配線401と信号線201との接続を容易にすることができます。他の例として、図5に示すように、第1チップ1ではなく第2チップ5に、所定の方向に延在する信号線501を設けることが考えられる。この場合においても、画素11とMPX回路350(A)を接続することができる。しかしながら、図5に比べて、図4に示した、第1チップ1に、所定の方向に延在する信号線を設けることが好ましい。これは、画素11が備わる第1チップ1よりも、信号処理回路21が備わる第2チップ5の方が、配線層が多くなることに由来する。配線層の多い第2チップ5に、図5のように信号線501を設けるよりも、配線層の少ない第1チップ1に、図4のように信号線201を設ける方が、設計の自由度が高いためである。接続配線401、接続配線405は典型的にはビアとして形成される。

20

30

#### 【0026】

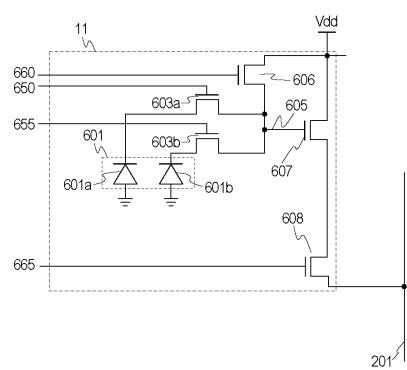

##### (画素の等価回路)

図6は、本実施例の画素11の等価回路図である。画素11は、光電変換部であるフォトダイオード601a、601bを有する。フォトダイオード601a、601bには、不図示の1つのマイクロレンズと、図2に示した配列に従って設けられたカラーフィルタを透過した光が入射する。つまり、フォトダイオード601aに入射する光と、フォトダイオード601bに入射する光の波長は実質的に同じである。

40

#### 【0027】

フォトダイオード601aは、転送トランジスタ603aを介して、フローティングディフージョン部(以下、FD部)605に接続されている。また、転送トランジスタ603aのゲートは、制御線650を介して、不図示の垂直走査回路に接続されている。

50

**【0028】**

フォトダイオード 601b は、転送トランジスタ 603b を介して、フローティングディフージョン部（以下、FD 部）605 に接続されている。また、転送トランジスタ 603b のゲートは、制御線 655 を介して、不図示の垂直走査回路に接続されている。

**【0029】**

FD 部 605 は、増幅トランジスタ 607 のゲートと、リセットトランジスタ 606 に接続されている。

**【0030】**

リセットトランジスタ 606 および増幅トランジスタ 607 は、電源電圧 Vdd が供給される。リセットトランジスタ 606 のゲートは、制御線 660 を介して、不図示の垂直走査回路に接続されている。10

**【0031】**

増幅トランジスタ 607 は、選択トランジスタ 608 に接続されている。選択トランジスタ 608 のゲートは、制御線 665 を介して、不図示の垂直走査回路に接続されている。

**【0032】**

選択トランジスタ 608 は、信号線 201 に接続されている。

**【0033】**

## (撮像装置の動作)

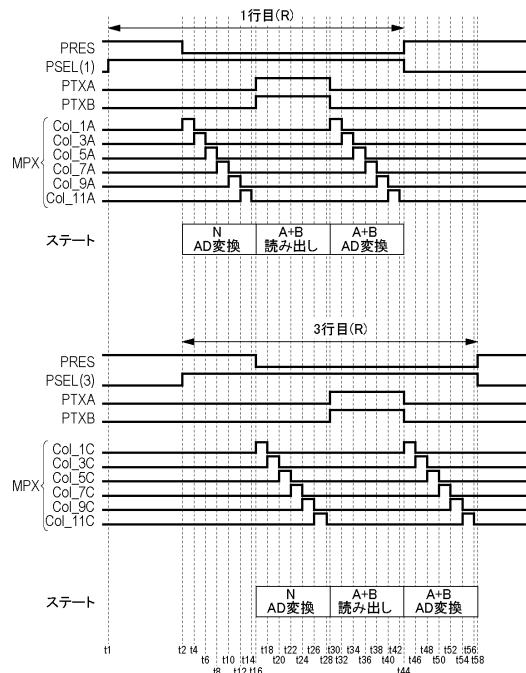

図 7 は、図 6 に示した画素 11 を備える撮像装置の動作を示した図である。

**【0034】**

図 7 の信号 PRES は、図 6 の制御線 660 を介して垂直走査回路からリセットトランジスタ 606 のゲートに供給される信号を示している。同じく、信号 PSEL は、制御線 665 を介して垂直走査回路から N 行目の画素 11 の選択トランジスタ 608 のゲートに供給される信号を示している。なお、信号 PSEL については、出力される画素 11 の行位置を末尾に合わせて示している。つまり、信号 PSEL (1) は、1 行目の画素 11 に出力される信号 PSEL であることを示している。信号 PTXA は、制御線 650 を介して垂直走査回路から転送トランジスタ 603a のゲートに供給される信号を示している。信号 PTXB は、制御線 655 を介して垂直走査回路から転送トランジスタ 603b のゲートに供給される信号を示している。20

**【0035】**

図 7 では、MPX 回路 350 (A)、ADC360 (A) に関わる動作を示している。この MPX 回路 350 (A)、ADC360 (A) には、図 3 で示したように、R のカラー フィルタを備える、1 行目および 3 行目であって、1 ~ 12 列のうちの奇数列に位置する画素 11 の信号が入力される。したがって、図 7 では、1 行目、3 行目であって、1 ~ 12 列のうちの奇数列に位置する画素 11 の動作に関わる動作を示している。30

**【0036】**

また、図 7 に示した信号 MPX は、不図示のタイミングジェネレータが、MPX 回路 350 (A) に出力する信号を示している。信号 MPX の信号値の変化によって、MPX 回路 350 (A) は、ADC360 (A) に出力する信号を、1 ~ 12 列のうち、奇数列の画素 11 に対応する信号線 201 の中から順次変更する。40

**【0037】**

図 7 では、MPX 回路 350 (A) が、ADC360 (A) に信号を出力する列としてどの列を選択しているかを、Col\_nm として示している。この nm の表記を説明する。n は画素 11 の列番号を示している。また、m は、1 列の画素 11 に対応して配される信号線 201 (A) ~ (D) のアルファベットを示している。つまり、Col\_1A であれば、1 列目の画素 11 に対応された信号線 201 (A) を示している。

**【0038】**

時刻 t1において、垂直走査回路は、1 行目および 3 行目の画素 11 に出力する信号 PRES を High レベルとしている。これにより、1 行目の画素 11 のリセットトランジスタ 606 がオンしている。よって、FD 部 605 は、電源電圧 Vdd に対応する電位にリ50

セットされている。また、時刻  $t_1$ において垂直走査回路は、信号 P S E L (1) を H i g h レベルとしている。これにより、1行目の画素 11 の選択トランジスタ 608 がオンする。よって、図 3 に示した電流源 310 が供給する電流が、1行目の画素 11 の選択トランジスタ 608 を介して増幅トランジスタ 607 に供給される。これにより、電源電圧 V d d 、増幅トランジスタ 607 、電流源 310 によるソースフォロワ回路が形成される。つまり、増幅トランジスタ 607 は、F D 部 605 の電位に対応する信号を、選択トランジスタ 608 を介して信号線 201 に出力するソースフォロワ動作を行う。

#### 【 0039 】

(動作：1行目の画素 11 に対応する N 信号の読み出し)

時刻  $t_2$  に、垂直走査回路は、1行目の画素 11 に出力する信号 P R E S を L o w レベルとする。これにより、1行目の画素 11 のリセットトランジスタ 606 がオフする。よって、F D 部 605 のリセットが解除される。増幅トランジスタ 607 は、リセットが解除された F D 部 605 の電位に基づく信号を、図 3 に示した信号線 201 (A) に出力する。この信号を、N 信号（ノイズ信号）と表記する。これにより、各列の信号線 201 (A) には、画素 11 から N 信号が出力されている。

10

#### 【 0040 】

(動作：1行目の画素 11 に対応する N 信号の A D 変換)

時刻  $t_2$  以降、M P X 回路 350 (A) は、タイミングジェネレータから供給される信号 M P X によって、1 ~ 12 列のうち奇数列の画素 11 に対応する信号線 201 (A) を、順次 A D C 360 (A) に接続する。

20

#### 【 0041 】

A D C 360 (A) は、M P X 回路 350 (A) から出力される、1列目の信号線 201 (A) のノイズ信号をデジタル信号に A D 変換する。その後、順次、1 ~ 12 列のうちの奇数列の画素 11 に対応する信号線 201 (A) に出力されているノイズ信号をデジタル信号に A D 変換する。

#### 【 0042 】

(動作：3行目の画素 11 に対応する N 信号の読み出し)

時刻  $t_{16}$  に、垂直走査回路は、3行目の画素 11 に出力する信号を L o w レベルとする。これにより、3行目の画素 11 のリセットトランジスタ 606 がオフする。よって、F D 部 605 のリセットが解除される。増幅トランジスタ 607 は、リセットが解除された F D 部 605 の電位に基づく信号である N 信号を、図 3 に示した信号線 201 (C) に出力する。これにより、各列の信号線 201 (C) には、画素 11 からノイズ信号が出力されている。

30

#### 【 0043 】

(動作：3行目の画素 11 に対応する N 信号の A D 変換)

時刻  $t_{16}$  以降、M P X 回路 350 (A) は、タイミングジェネレータから供給される信号 M P X によって、1 ~ 12 列のうち奇数列の画素 11 に対応する信号線 201 (C) を、順次 A D C 360 (A) に接続する。

30

#### 【 0044 】

A D C 360 (A) は、M P X 回路 350 (A) から出力される、1列目の信号線 201 (C) の N 信号をデジタル信号に A D 変換する。その後、順次、1 ~ 12 列のうちの奇数列の画素 11 に対応する信号線 201 (C) に出力されている N 信号をデジタル信号に A D 変換する。

40

#### 【 0045 】

(動作：1行目の画素 11 に対応する A + B 信号の読み出し)

時刻  $t_{16}$  に、垂直走査回路は、1行目の画素 11 に出力する信号 P T X A 、 P T X B を H i g h レベルとする。これにより、フォトダイオード 601a 、 601b が蓄積した電荷（本実施例では電子である）が、転送トランジスタ 603a 、 603b を介して F D 部 605 に転送される。F D 部 605 では、フォトダイオード 601a 、 601b のそれぞれの電荷が加算される。これにより、F D 部 605 は、フォトダイオード 601a 、 601b の合計電荷を出力する。

50

1 b のそれぞれの電荷を加算した電荷に対応する電位となる。仮に、フォトダイオード 601 a のみの電荷による F D 部 605 の電位に基づいて増幅トランジスタ 607 が出力する信号を A 信号とする。また、仮に、フォトダイオード 601 b のみの電荷による F D 部 605 の電位に基づいて増幅トランジスタ 607 が出力する信号を B 信号とする。この表記に従うと、フォトダイオード 601 a、601 b のそれぞれの電荷を加算した電荷に対応する F D 部 605 の電位に基づいて増幅トランジスタ 607 が出力する信号は A 信号と B 信号を加算した A + B 信号とみなすことができる。各列の信号線 201 (A) には、1 行目の画素 11 の A + B 信号が出力されている。

#### 【0046】

(1行目の画素11に対応するA+B信号のAD変換)

時刻 t30 以降、MPX 回路 350 (A) は、タイミングジェネレータから供給される信号 MPX によって、1 ~ 12 列のうち奇数列の画素 11 に対応する信号線 201 (A) を、順次 ADC360 (A) に接続する。

#### 【0047】

ADC360 (A) は、MPX 回路 350 (A) から出力される、1 列目の信号線 201 (A) の A + B 信号をデジタル信号に AD 变換する。その後、順次、1 ~ 12 列のうちの奇数列の画素 11 に対応する信号線 201 (A) に出力されている A + B 信号をデジタル信号に AD 变換する。

#### 【0048】

(動作：3行目の画素11に対応するA+B信号の読み出し)

時刻 t30 に、垂直走査回路は、3 行目の画素 11 に出力する信号 P TX A、P TX B を High レベルとする。これにより、各列の信号線 201 (C) には、3 行目の画素 11 の A + B 信号が出力されている。

#### 【0049】

(動作：3行目の画素11に対応するA+B信号のAD変換)

時刻 t44 以降、MPX 回路 350 (A) は、タイミングジェネレータから供給される信号 MPX によって、1 ~ 12 列のうち奇数列の画素 11 に対応する信号線 201 (C) を、順次 ADC360 (A) に接続する。

#### 【0050】

ADC360 (A) は、MPX 回路 350 (A) から出力される、1 列目の信号線 201 (C) の A + B 信号をデジタル信号に AD 变換する。その後、順次、1 ~ 12 列のうちの奇数列の画素 11 に対応する信号線 201 (C) に出力されている A + B 信号をデジタル信号に AD 变換する。

#### 【0051】

(撮像装置が行う並行動作)

図 7 に示した動作では、以下のように、複数の動作を並行して行っている。

(1) 1 行目の画素 11 に対応する N 信号の AD 变換と、3 行目の画素 11 に対応する N 信号の読み出しとの並行動作

(2) 3 行目の画素 11 に対応する N 信号の AD 变換と、1 行目の画素 11 に対応する A + B 信号の読み出しとの並行動作

(3) 1 行目の画素 11 に対応する A + B 信号の AD 变換と、3 行目の画素 11 に対応する A + B 信号の読み出しとの並行動作

この並行動作により、ADC360 (A) が 1 度の AD 变換を終えてから、次の AD 变換を行うまでの待機期間を短縮することができる。これにより、全ての画素 11 が出力する信号の AD 变換に要する時間を短縮することができる。よって、撮像装置の高フレームレート化を進展させることができる。

#### 【0052】

(本実施例の効果)

本実施例の撮像装置では、前述したように、1 つの ADC360 (A) に接続される画素 11 は全て、R のカラーフィルタを備える画素 11 である。一方、ADC360 (B) に

10

20

30

40

50

接続される画素 1 1 は全て、G のカラーフィルタを備える画素 1 1 である。このように、各々が第 1 色 (R) のカラーフィルタを備える複数の第 1 画素 1 1 は、第 2 A D 変換部である A D C 3 6 0 (B) に接続されずに第 1 A D 変換部である A D C 3 6 0 (A) に接続される。また、各々が第 2 色 (G) のカラーフィルタを備える複数の第 1 画素 1 1 は、第 1 A D 変換部である A D C 3 6 0 (A) に接続されずに第 2 A D 変換部である A D C 3 6 0 (B) に接続される。

#### 【 0 0 5 3 】

この構成を備えることにより、1 つの A D C が A D 変換する信号に対応する光の色を 1 色のみとすることができる。複数の A D C を備える撮像装置においては、A D C ごとの A D 変換特性のばらつきに対応するため、A D 変換の補正処理、あるいは A D 変換後の補正処理が必要になることがある。A D 変換の補正処理は、例えば A D C が使用する基準信号の補正がある。また、A D 変換後の補正処理は、例えばデジタル信号の補正がある。1 つの A D C が A D 変換する信号に対応する光の色を複数とすると、複数の色のそれぞれに応じた補正パラメータを用意する必要が生じる。このため、A D 変換の補正、A D 変換後の補正が煩雑になるという課題が有る。

10

#### 【 0 0 5 4 】

一方、本実施例の撮像装置は、1 つの A D C が A D 変換する信号に対応する光の色を 1 色のみとしている。これにより、本実施例の撮像装置は A D 変換の補正、A D 変換後の補正を簡略にすることができるという効果を有する。

20

#### 【 0 0 5 5 】

このように、本実施例の撮像装置は、複数の第 1 画素に第 1 色のカラーフィルタが配され、複数の第 2 画素に第 2 色のカラーフィルタが配される場合における、画素と A D 変換部との好適な接続関係を備える撮像装置を提供することができる。

#### 【 0 0 5 6 】

##### (他の形態)

本実施例では、第 1 色のカラーフィルタが配された画素 1 1 が接続され、第 2 色のカラーフィルタが配された画素 1 1 が接続されていない信号線 2 0 1 が、A D C 3 6 0 に接続される例を説明した。この例では、当該 A D C 3 6 0 と第 2 色のカラーフィルタが配された画素 1 1 とが接続される接続部が設けられない形態となる。

30

#### 【 0 0 5 7 】

本実施例は、この例に限定されるものでは無い。例えば、図 8 に示したように、1 列の画素 1 1 に対し、複数の信号線が配され、この複数の信号線が M P X 回路 3 5 0 によって、選択的に A D C 3 6 0 に接続される例にも適用することが可能である。この例の場合には、1 フレーム期間において、第 1 色のカラーフィルタが配された画素 1 1 と接続され、第 2 色のカラーフィルタが配された画素 1 1 とは接続されないようにすればよい。1 列目の画素 1 1 に注目して説明すると、M P X 回路 3 5 0 (A) は、第 1 色である R のカラーフィルタを有する画素 1 1 が接続された信号線 2 0 1 (A)、2 0 1 (C) を A D C 3 6 0 (A) に接続する。一方、当該 1 フレーム期間において、M P X 回路 3 5 0 (A) は、第 2 色である G のカラーフィルタを有する画素 1 1 が接続された信号線 2 0 1 (B)、2 0 1 (D) を A D C 3 6 0 (A) に接続しない。この構成においても、上記した A D 変換の補正、A D 変換後の補正を簡略にすることができるという効果を得ることができる。

40

#### 【 0 0 5 8 】

##### (実施例 2)

本実施例について、実施例 1 と異なる点を中心に説明する。本実施例の撮像装置は、実施例 1 の A D C 3 6 0 (A)、A D C 3 6 0 (B) として、逐次比較型の A D 変換器を用いた例である。その他の構成は、実施例 1 の撮像装置の構成と同じとすることができる。

#### 【 0 0 5 9 】

##### (逐次比較型 A D C の等価回路)

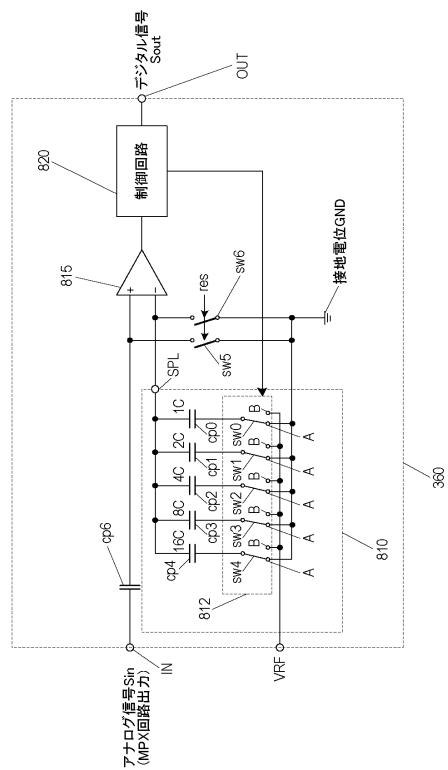

図 9 は、本実施例の A D C 3 6 0 の等価回路図である。

#### 【 0 0 6 0 】

50

A D C 3 6 0 は入力端子 I N 及び出力端子 O U T を有し、入力端子 I N から入力されたアナログ信号 S i n ( M P X 回路 3 5 0 の出力) をデジタル信号 S o u t に変換して出力端子 O U T から出力する。このアナログ信号 S i n は、実施例 1 で説明した、 N 信号と S 信号の一方あるいは両方とすることができる。A D C 3 6 0 は M P X 回路出力を 5 ビットの分解能でデジタル信号 S o u t に変換する。

#### 【 0 0 6 1 】

A D C 3 6 0 はアナログ信号 S i n との比較に用いられる比較信号を生成する生成回路 8 1 0 を更に有する。生成回路 8 1 0 はバイナリウェイトの容量値を有する複数の容量素子 c p 0 ~ c p 4 と、容量素子 c p 0 ~ c p 4 に接続された複数のスイッチ s w 0 ~ s w 4 とを有する。複数のスイッチ s w 0 ~ s w 4 によって、容量素子 c p 0 ~ c p 4 のうちの 1 つ以上を選択するスイッチ回路が構成される。バイナリウェイトとは、公比 2 の等比数列をなす重み(容量値)の集合のことである。図 9 の例では、容量素子 c p 0 ~ c p 4 は順に、 1 C 、 2 C 、 4 C 、 8 C 、 16 C の容量値を有する。容量素子 c p 0 ~ c p 4 の一方の電極は生成回路 8 1 0 の供給端子 S P L に接続され、他方の電極はそれぞれスイッチ s w 0 ~ s w 4 に接続される。スイッチ s w 0 ~ s w 4 はそれぞれ、一端が容量素子 c p 0 ~ c p 4 に接続され、他端が端子 A と端子 B との間をトグルする。端子 A には接地電位 G N D が供給され、端子 B には基準電圧 V R F が供給される。基準電圧 V R F は A D C 3 6 0 の外部から供給される定電圧であり、接地電位 G N D よりも大きな値である。スイッチ s w 0 が端子 A にトグルすると、容量素子 c p 0 に接地電位 G N D が供給され、スイッチ s w 0 が端子 B にトグルすると、容量素子 c p 0 に基準電圧 V R F が供給される。他のスイッチ s w 1 ~ s w 4 についても同様である。スイッチ s w 0 ~ s w 4 が切り替わることによって、供給端子 S P L と基準電圧 V R F との間に接続される容量素子の合成容量値が変化し、その結果として供給端子 S P L から出力される比較信号 V c m p の値が変化する。

#### 【 0 0 6 2 】

A D C 3 6 0 は比較器 8 1 5 を更に有する。比較器 8 1 5 はアナログ信号 S i n の値と比較信号 V c m p の値とを比較して、比較結果に応じた信号を出力する。比較器 8 1 5 の非反転端子には容量素子 c p 6 を介してアナログ信号 S i n が供給され、比較器 8 1 5 の反転端子には生成回路 8 1 0 の供給端子 S P L から比較信号 V c m p が供給される。それにより、アナログ信号 S i n の値が比較信号 V c m p の値以上の場合に H i g h が出力され、アナログ信号 S i n の値が比較信号 V c m p の値未満の場合に L o w が出力される。この例ではアナログ信号 S i n の値と比較信号 V c m p の値が等しい場合に H i g h を出力しているが、 L o w を出力してもよい。容量素子 c p 6 はアナログ信号 S i n の値を比較信号 V c m p との比較が可能な範囲に調整する。本実施形態では、説明を簡単にするために、アナログ信号 S i n の値は接地電位 G N D 以上、基準電圧 V R F 以下であり、アナログ信号 S i n と同じ大きさの信号が比較器 8 1 5 の非反転端子に供給される場合を扱う。

#### 【 0 0 6 3 】

図 9 の例ではアナログ信号 S i n を比較器 8 1 5 の非反転端子に供給し、比較信号 V c m p を比較器 8 1 5 の反転端子に供給するが、アナログ信号 S i n の値と比較信号 V c m p の値との大小関係を判定できれば他の構成も取りうる。例えば、アナログ信号 S i n と比較信号 V c m p との差分を比較器 8 1 5 の非反転端子に供給し、接地電位 G N D を比較器 8 1 5 の反転端子に供給してもよい。

#### 【 0 0 6 4 】

A D C 3 6 0 はスイッチ s w 5 、 s w 6 を更に有する。これらのスイッチ s w 5 、 s w 6 が導通状態になると、比較器 8 1 5 の非反転端子、反転端子に接地電位 G N D が供給され、比較器 8 1 5 がリセットされる。

#### 【 0 0 6 5 】

A D C 3 6 0 は、制御回路 8 2 0 を更に備える。制御回路 8 2 0 には比較器 8 1 5 から比較結果が供給され、制御回路 8 2 0 はこの比較結果に基づいてデジタル信号 S o u t を生成し、出力端子 O U T から出力する。制御回路 8 2 0 はまた、各スイッチ s w 0 ~ s w 6

10

20

30

40

50

に制御信号を送信してその状態を切り替える。ADC360(A)は、ADC360(B)が備える比較器815、生成回路810とは別の比較器815、生成回路810を備える。第1AD変換部と第2AD変換部は、別々の比較器と、別々の生成回路とを備えると言える。

#### 【0066】

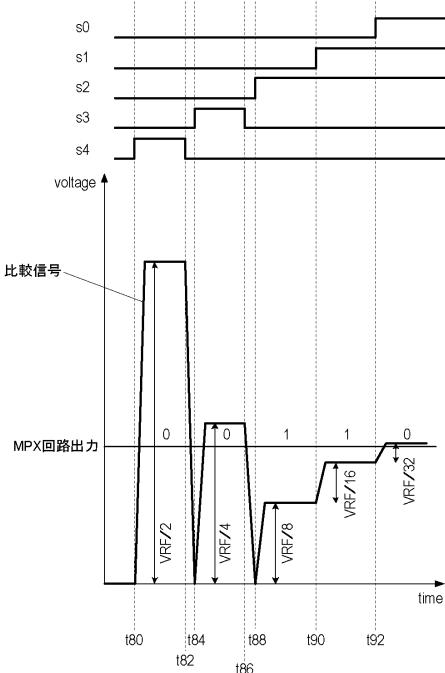

(逐次比較型ADCの動作)

図10において、sw0～sw6は制御回路820からスイッチsw0～sw6に供給される制御信号の値を示す。スイッチsw0～sw4は、供給される制御信号がHighである場合に端子Bへトグルし、制御信号がLowである場合に端子Aへトグルする。スイッチsw5、sw6は、供給される制御信号がHighである場合に導通状態となり、制御信号がLowである場合に非導通状態となる。図10の下側にはアナログ信号Sin及び比較信号Vcmpが示される。図10では、アナログ信号Sinの値が2進数で00110に相当する場合を例として扱う。

10

#### 【0067】

続いて、AD変換器100のAD変換動作を時系列に沿って説明する。制御回路820は準備期間において、スイッチsw0～sw4に供給される制御信号をLowにし、スイッチsw5、sw6に供給される制御信号をHighにする。これにより、比較器815の非反転端子及び反転端子が接地電位GNDにリセットされるとともに、比較信号Vcmpの値が接地電位GNDに等しくなる。その後、制御回路820はスイッチsw5、sw6に供給される制御信号をLowにする。以降の動作において、比較器815の非反転端子にはアナログ信号Sinが供給され続ける。

20

#### 【0068】

次に、逐次比較期間が始まると、制御回路820はスイッチsw4に供給される制御信号をHighに変更する。これにより、スイッチsw4は端子Bにトグルし、バイナリウェイトの中で1番目に大きな容量値を有するキャパシタcp4を介して生成回路810の供給端子SPLに基準電圧VRFが印加される。その結果、比較信号VcmpがVRF/2だけ増加し、比較信号Vcmpの値はVRF/2に等しくなる。制御回路820は、比較器815からの比較結果に基づいて、アナログ信号Sinの値が比較信号Vcmpの値(VRF/2)よりも小さいと判定し、スイッチsw4に供給される制御信号をLowに戻す。それにより、比較信号Vcmpの値は接地電位GNDに戻る。この比較結果は、デジタル信号Soutの値のMSB( LSBを1ビット目とした場合に5ビット目)が0であることを意味する。

30

#### 【0069】

次に、制御回路820はスイッチsw3に供給される制御信号をHighに変更する。これにより、バイナリウェイトの中で2番目に大きな容量値を有するキャパシタcp3を介して生成回路810の供給端子SPLに基準電圧VRFが印加される。その結果、比較信号VcmpがVRF/4だけ増加し、比較信号Vcmpの値はVRF/4に等しくなる。制御回路820は、比較器815からの比較結果に基づいて、アナログ信号Sinの値が比較信号Vcmpの値(VRF/4)よりも小さいと判定し、スイッチsw3に供給される制御信号をLowに戻す。それにより、比較信号Vcmpの値は接地電位GNDに戻る。この比較結果は、デジタル信号Soutの値の4ビット目が0であることを意味する。

40

#### 【0070】

次に、制御回路820はスイッチsw2に供給される制御信号をHighに変更する。これにより、バイナリウェイトの中で3番目に大きな容量値を有するキャパシタcp2を介して生成回路810の供給端子SPLに基準電圧VRFが印加される。その結果、比較信号VcmpがVRF/8だけ増加し、比較信号Vcmpの値はVRF/8に等しくなる。制御回路820は、比較器815からの比較結果に基づいて、アナログ信号Sinの値が比較信号Vcmpの値(VRF/8)よりも大きいと判定し、スイッチsw2に供給される制御信号をHighのままにする。それにより、比較信号Vcmpの値はVRF/8に維持される。この比較結果は、デジタル信号Soutの値の3ビット目が1であることを

50

意味する。

#### 【0071】

次に、制御回路820はスイッチsw1に供給される制御信号をHighに変更する。これにより、バイナリウェイトの中で4番目に大きな容量値を有するキャパシタcp1と、キャパシタcp2とを介して生成回路810の供給端子SPLに基準電圧VRFが印加される。その結果、比較信号VcmpがVRF/16だけ増加し、比較信号Vcmpの値は $VRF * 3 / 16$ に等しくなる。なお、本明細書で用いる「\*」は乗算を意味している。制御回路820は、比較器815からの比較結果に基づいて、アナログ信号Sinの値が比較信号Vcmpの値( $VRF * 3 / 16$ )よりも大きいと判定し、スイッチsw1に供給される制御信号をHighのままにする。それにより、比較信号Vcmpの値は $VRF * 3 / 16$ に維持される。この比較結果は、デジタル信号Soutの値の2ビット目が1であることを意味する。

#### 【0072】

最後に、制御回路820はスイッチsw0に供給される制御信号をHighに変更する。これにより、バイナリウェイトの中で5番目に大きな容量値を有するキャパシタcp0と、cp1、cp2とを介して生成回路810の供給端子SPLに基準電圧VRFが印加される。その結果、比較信号VcmpがVRF/32だけ増加し、比較信号Vcmpの値は $VRF * 7 / 32$ に等しくなる。制御回路820は、比較器815からの比較結果に基づいて、アナログ信号Sinの値が比較信号Vcmpの値( $VRF * 7 / 32$ )よりも小さいと判定し、スイッチsw0に供給される制御信号をLowに戻す。それにより、比較信号Vcmpの値は $VRF * 3 / 16$ に戻る。この比較結果は、デジタル信号Soutの値の1ビット目が0であることを意味する。

#### 【0073】

以上の逐次比較により、制御回路820はアナログ信号に対応するデジタル信号Soutが00110であると決定する。

#### 【0074】

このようにして、ADC360は、入力されるアナログ信号に対応するデジタル信号を生成するAD変換を行うことができる。

#### 【0075】

(他のAD変換形式)

実施例2では、ADC360として、逐次比較型のAD変換器を用いた例を説明した。ADC360は、この逐次比較型のAD変換器に限定されるものでは無い。例えば、他のAD変換器として、ランプ信号比較型、デルタシグマ型、パイプライン型、フラッシュ型等の種々のAD変換器を用いることができる。

#### 【0076】

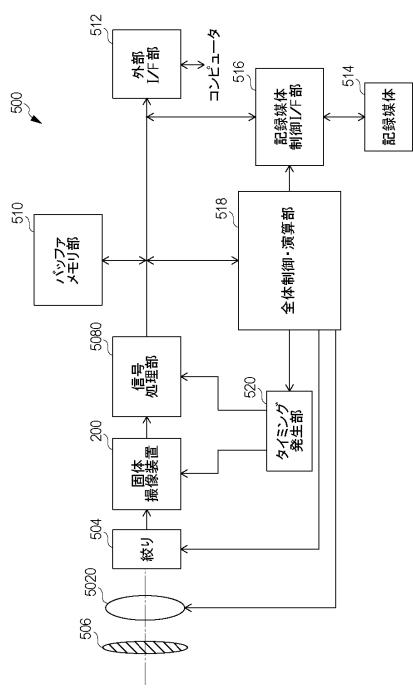

(実施例3)

図11は、本実施例による撮像システム500の構成を示すブロック図である。本実施例の撮像システム500は、上述の各実施例で述べた撮像装置のいずれかの構成を適用した撮像装置200を含む。撮像システム500の具体例としては、デジタルスチルカメラ、デジタルカムコーダー、監視カメラ等が挙げられる。図11に、上述の各実施例のいずれかの撮像装置を撮像装置200として適用したデジタルスチルカメラの構成例を示す。

#### 【0077】

図11に例示した撮像システム500は、撮像装置200、被写体の光学像を撮像装置200に結像させるレンズ5020、レンズ5020を通過する光量を可変にするための絞り504、レンズ5020の保護のためのバリア506を有する。レンズ5020及び絞り504は、撮像装置200に光を集光する光学系である。

#### 【0078】

撮像システム500は、また、撮像装置200から出力される出力信号の処理を行う信号処理部5080を有する。信号処理部5080は、必要に応じて入力信号に対して各種の補正、圧縮を行って出力する信号処理の動作を行う。信号処理部5080は、撮像装置2

10

20

30

40

50

00より出力される出力信号に対してA/D変換処理を実施する機能を備えていてもよい。この場合、撮像装置200の内部には、必ずしもA/D変換回路を有する必要はない。

#### 【0079】

撮像システム500は、更に、画像データを一時的に記憶するためのバッファメモリ部510、外部コンピュータ等と通信するための外部インターフェース部（外部I/F部）512を有する。更に撮像システム500は、撮像データの記録又は読み出しを行うための半導体メモリ等の記録媒体514、記録媒体514に記録又は読み出しを行うための記録媒体制御インターフェース部（記録媒体制御I/F部）516を有する。なお、記録媒体514は、撮像システム500に内蔵されていてもよく、着脱可能であってもよい。

#### 【0080】

更に撮像システム500は、各種演算を行うとともにデジタルスチルカメラ全体を制御する全体制御・演算部518、撮像装置200と信号処理部5080に各種タイミング信号を出力するタイミング発生部520を有する。ここで、タイミング信号などは外部から入力されてもよく、撮像システム500は、少なくとも撮像装置200と、撮像装置200から出力された出力信号を処理する信号処理部5080とを有すればよい。全体制御・演算部518及びタイミング発生部520は、撮像装置200の制御機能の一部又は全部を実施するように構成してもよい。

10

#### 【0081】

撮像装置200は、画像用信号を信号処理部5080に出力する。信号処理部5080は、撮像装置200から出力される画像用信号に対して所定の信号処理を実施し、画像データを出力する。また、信号処理部5080は、画像用信号を用いて、画像を生成する。

20

#### 【0082】

上述した各実施例の撮像装置による撮像装置を用いて撮像システムを構成することにより、より良質の画像が取得可能な撮像システムを実現することができる。

#### 【0083】

##### （実施例4）

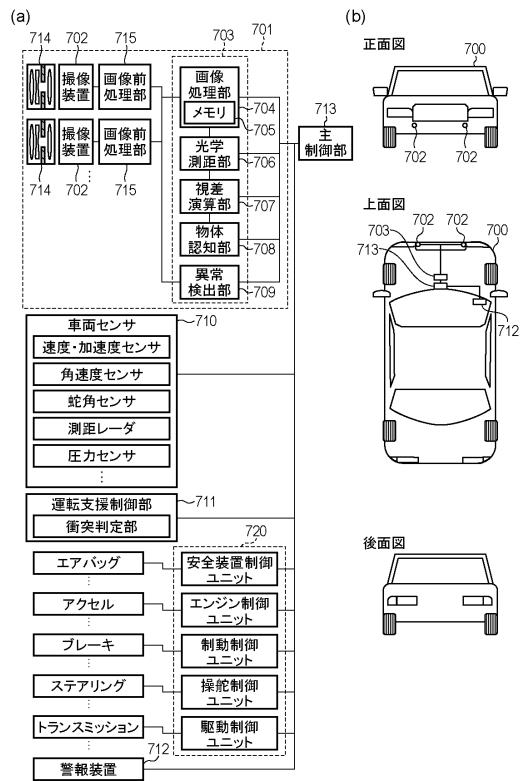

本実施例の撮像システム及び移動体について、図12及び図13を用いて説明する。

#### 【0084】

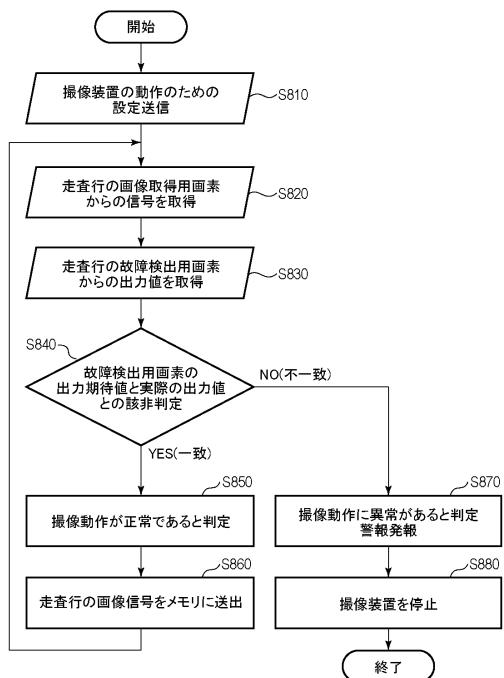

図12は、本実施例による撮像システム及び移動体の構成例を示す概略図である。図13は、本実施例による撮像システムの動作を示すフロー図である。

30

#### 【0085】

本実施例では、車載カメラに関する撮像システムの一例を示す。図12は、車両システムと共に搭載される撮像システムの一例を示したものである。撮像システム701は、撮像装置702、画像前処理部715、集積回路703、光学系714を含む。光学系714は、撮像装置702に被写体の光学像を結像する。撮像装置702は、光学系714により結像された被写体の光学像を電気信号に変換する。撮像装置702は、上述の各実施例のいずれかの撮像装置である。画像前処理部715は、撮像装置702から出力された信号に対して所定の信号処理を行う。画像前処理部715の機能は、撮像装置702内に組み込まれていてもよい。撮像システム701には、光学系714、撮像装置702及び画像前処理部715が、少なくとも2組設けられており、各組の画像前処理部715からの出力が集積回路703に入力されるようになっている。

40

#### 【0086】

集積回路703は、撮像システム用途向けの集積回路であり、メモリ705を含む画像処理部704、光学測距部706、視差演算部707、物体認知部708、異常検出部709を含む。画像処理部704は、画像前処理部715の出力信号に対して、現像処理や欠陥補正等の画像処理を行う。メモリ705は、撮像画像の一次記憶、撮像画素の欠陥位置を格納する。光学測距部706は、被写体の合焦や、測距を行う。視差演算部707は、複数の撮像装置702により取得された複数の画像データから視差（視差画像の位相差）の算出を行う。物体認知部708は、車、道、標識、人等の被写体の認知を行う。異常検出部709は、撮像装置702の異常を検出すると、主制御部713に異常を発報する。

50

**【 0 0 8 7 】**

集積回路 703 は、専用に設計されたハードウェアによって実現されてもよいし、ソフトウェアモジュールによって実現されてもよいし、これらの組合せによって実現されてもよい。また、FPGA (Field Programmable Gate Array) や ASIC (Application Specific Integrated Circuit) 等によって実現されてもよいし、これらの組合せによって実現されてもよい。

**【 0 0 8 8 】**

主制御部 713 は、撮像システム 701、車両センサ 710、制御ユニット 720 等の動作を統括・制御する。なお、主制御部 713 を持たず、撮像システム 701、車両センサ 710、制御ユニット 720 が個別に通信インターフェースを有して、それぞれが通信ネットワークを介して制御信号の送受を行う（例えば CAN 規格）方法も取りうる。

10

**【 0 0 8 9 】**

集積回路 703 は、主制御部 713 からの制御信号を受け或いは自身の制御部によって、撮像装置 702 へ制御信号や設定値を送信する機能を有する。例えば、集積回路 703 は、撮像装置 702 内の電圧スイッチ 13 をパルス駆動させるための設定や、フレーム毎に電圧スイッチ 13 を切り替える設定等を送信する。

**【 0 0 9 0 】**

撮像システム 701 は、車両センサ 710 に接続されており、車速、ヨーレート、舵角などの自車両走行状態及び自車外環境や他車・障害物の状態を検出することができる。車両センサ 710 は、視差画像から対象物までの距離情報を取得する距離情報取得手段もある。また、撮像システム 701 は、自動操舵、自動巡航、衝突防止機能等の種々の運転支援を行う運転支援制御部 711 に接続されている。特に、衝突判定機能に関しては、撮像システム 701 や車両センサ 710 の検出結果を基に他車・障害物との衝突推定・衝突有無を判定する。これにより、衝突が推定される場合の回避制御、衝突時の安全装置起動を行う。

20

**【 0 0 9 1 】**

また、撮像システム 701 は、衝突判定部での判定結果に基づいて、ドライバーに警報を発する警報装置 712 にも接続されている。例えば、衝突判定部の判定結果として衝突可能性が高い場合、主制御部 713 は、ブレーキをかける、アクセルを戻す、エンジン出力を抑制するなどして、衝突を回避、被害を軽減する車両制御を行う。警報装置 712 は、音等の警報を鳴らす、カーナビゲーションシステムやメーターパネルなどの表示部画面に警報情報を表示する、シートベルトやステアリングに振動を与えるなどしてユーザに警告を行う。

30

**【 0 0 9 2 】**

本実施例では、車両の周囲、例えば前方又は後方を撮像システム 701 で撮影する。図 1 2 (b) に、車両前方を撮像システム 701 で撮像する場合の撮像システム 701 の配置例を示す。

**【 0 0 9 3 】**

2つの撮像装置 702 は、車両 700 の前方に配置される。具体的には、車両 700 の進退方位又は外形（例えば車幅）に対する中心線を対称軸に見立て、その対称軸に対して 2 つの撮像装置 702 が線対称に配置されると、車両 700 と被写対象物との間の距離情報の取得や衝突可能性の判定を行う上で好ましい。また、撮像装置 702 は、運転者が運転席から車両 700 の外の状況を視認する際に運転者の視野を妨げない配置が好ましい。警報装置 712 は、運転者の視野に入りやすい配置が好ましい。

40

**【 0 0 9 4 】**

次に、撮像システム 701 における撮像装置 702 の故障検出動作について、図 1 3 を用いて説明する。撮像装置 702 の故障検出動作は、図 1 3 に示すステップ S810 ~ S880 に従って実施される。

**【 0 0 9 5 】**

ステップ S810 は、撮像装置 702 のスタートアップ時の設定を行うステップである。

50

すなわち、撮像システム 701 の外部（例えば主制御部 713）又は撮像システム 701 の内部から、撮像装置 702 の動作のための設定を送信し、撮像装置 702 の撮像動作及び故障検出動作を開始する。

#### 【0096】

次いで、ステップ S820において、有効画素から画素信号を取得する。また、ステップ S830において、故障検出用に設けた故障検出画素からの出力値を取得する。この故障検出画素は、有効画素と同じく光電変換部を備える。この光電変換部には、所定の電圧が書き込まれる。故障検出用画素は、この光電変換部に書き込まれた電圧に対応する信号を出力する。なお、ステップ S820 とステップ S830 とは逆でもよい。

#### 【0097】

次いで、ステップ S840において、故障検出画素の出力期待値と、実際の故障検出画素からの出力値との該非判定を行う。

#### 【0098】

ステップ S840における該非判定の結果、出力期待値と実際の出力値とが一致している場合は、ステップ S850に移行し、撮像動作が正常に行われていると判定し、処理ステップがステップ S860へと移行する。ステップ S860では、走査行の画素信号をメモリ 705 に送信して一次保存する。そののち、ステップ S820に戻り、故障検出動作を継続する。

#### 【0099】

一方、ステップ S840における該非判定の結果、出力期待値と実際の出力値とが一致していない場合は、処理ステップはステップ S870に移行する。ステップ S870において、撮像動作に異常があると判定し、主制御部 713、又は警報装置 712 に警報を発報する。警報装置 712 は、表示部に異常が検出されたことを表示させる。その後、ステップ S880において撮像装置 702 を停止し、撮像システム 701 の動作を終了する。

#### 【0100】

なお、本実施例では、1行毎にフローチャートをループさせる例を例示したが、複数行毎にフローチャートをループさせてもよいし、1フレーム毎に故障検出動作を行ってもよい。

#### 【0101】

なお、ステップ S870 の警報の発報は、無線ネットワークを介して、車両の外部に通知するようにしてもよい。

#### 【0102】

また、本実施例では、他の車両と衝突しない制御を説明したが、他の車両に追従して自動運転する制御や、車線からはみ出さないように自動運転する制御などにも適用可能である。さらに、撮像システム 701 は、自車両等の車両に限らず、例えば、船舶、航空機或いは産業用ロボットなどの移動体（移動装置）に適用することができる。加えて、移動体に限らず、高度道路交通システム（ITS）等、広く物体認識を利用する機器に適用することができる。

#### 【0103】

##### [変形実施例]

本発明は、上記実施例に限らず種々の変形が可能である。

#### 【0104】

例えば、いずれかの実施例の一部の構成を他の実施例に追加した例や、他の実施例の一部の構成と置換した例も、本発明の実施例である。

#### 【0105】

また、上述の実施例は、いずれも本発明を実施するにあたっての具体化の例を示したものに過ぎず、これらの例示によって本発明の技術的範囲が限定的に解釈されてはならない。すなわち、本発明はその技術思想、又はその主要な特徴から逸脱することなく、様々な態様で実施することができる。

#### 【符号の説明】

#### 【0106】

10

20

30

40

50

1 第1チップ

5 第2チップ

11 画素

21 信号処理回路

303 接続部

310 電流源

350 マルチプレックス回路 (MPX回路)

360 A/D変換回路 (ADC)

【図面】

【図1】

【図2】

10

20

30

40

50

【図 3】

【図 4】

10

20

【図 5】

【図 6】

30

40

50

【図 7】

【図 8】

10

20

【図 9】

【図 10】

30

40

50

【図 1 1】

【図 1 2】

10

20

30

40

【図 1 3】

50

---

フロントページの続き

ヤノン株式会社内

審査官 大室 秀明

- (56)参考文献

- 特開2011-130032(JP,A)

- 特開2013-255035(JP,A)

- 特開2015-126043(JP,A)

- 特開2013-232717(JP,A)

- 特開2017-103752(JP,A)

(58)調査した分野 (Int.Cl., DB名)

- H01L21/339

- H01L27/14-27/148

- H01L27/30

- H01L29/762

- H04N5/222-5/257

- H04N5/30-5/378

- H04N9/04-9/11