(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5650217号

(P5650217)

(45) 発行日 平成27年1月7日(2015.1.7)

(24) 登録日 平成26年11月21日(2014.11.21)

(51) Int.Cl.

F 1

|                   |                  |            |      |

|-------------------|------------------|------------|------|

| <b>G06F 11/00</b> | <b>(2006.01)</b> | G06F 11/00 | 350M |

| <b>G06F 15/78</b> | <b>(2006.01)</b> | G06F 15/78 | 510P |

| <b>G06F 1/32</b>  | <b>(2006.01)</b> | G06F 1/00  | 332B |

請求項の数 11 (全 16 頁)

(21) 出願番号 特願2012-522124 (P2012-522124)

(86) (22) 出願日 平成22年7月23日 (2010.7.23)

(65) 公表番号 特表2013-500528 (P2013-500528A)

(43) 公表日 平成25年1月7日 (2013.1.7)

(86) 國際出願番号 PCT/EP2010/060755

(87) 國際公開番号 WO2011/012558

(87) 國際公開日 平成23年2月3日 (2011.2.3)

審査請求日 平成25年7月23日 (2013.7.23)

(31) 優先権主張番号 0955284

(32) 優先日 平成21年7月28日 (2009.7.28)

(33) 優先権主張国 フランス (FR)

(73) 特許権者 510000633

エスティー・エリクソン、ソシエテ、アノニム

スイス国プラン-レ-ズアト、シュマン、デュ、シャン-デ-フィーユ、39

(74) 代理人 100117787

弁理士 勝沼 宏仁

(74) 代理人 100082991

弁理士 佐藤 泰和

(74) 代理人 100103263

弁理士 川崎 康

(74) 代理人 100107582

弁理士 関根 賀

(74) 代理人 100118843

弁理士 赤岡 明

最終頁に続く

(54) 【発明の名称】 トランザクション終端装置

## (57) 【特許請求の範囲】

## 【請求項 1】

中央演算装置(10)と、

相互接続バス(1)と、

別個のパワードメインの一部であり、前記バスを介して、相互に通信することができおよび前記中央演算装置と通信することができ、あるいは、相互に通信することができまたは前記中央演算装置と通信することができる複数の機能モジュール(11～15、21)であって、トランザクションは、マスタ機能モジュールによる要求メッセージの送信、および、スレーブ機能モジュールによる応答メッセージの返信を含む、複数の機能モジュールと、

スレーブモードでのみ動作でき、前記パワードメインの1つと関連付けられ、前記パワードメインへの電源及び前記スレーブ機能モジュールへの電源が前記中央演算装置によってオフにされるときに前記パワードメインのスレーブ機能モジュール(21)を引き継ぐとともに、電源がオフにされる瞬間に、前記スレーブ機能モジュールとマスタ機能モジュールとの間で進行中のトランザクションの任意の要求に応答してエラーを知らせるように構成された少なくとも1つの終端モジュール(22)と、

を備え、

前記スレーブ機能モジュール(21)が前記相互接続バス(1)に接続されると、前記終端モジュール(22)は、前記相互接続バス(1)から切り離され、

前記終端モジュール(22)が前記相互接続バス(1)に接続されると、前記スレーブ

機能モジュール(21)は、前記相互接続バス(1)から切り離されるシステム。

**【請求項2】**

前記終端モジュール(22)は、前記スレーブ機能モジュールへの電源がオフにされる瞬間に読み出し動作が進行中である場合にエラーを知らせる応答を生成し、前記マスタ機能モジュールによって期待される読み出し応答の全持続時間にわたって前記エラーを知らせる応答を生成するように構成された第1の論理ユニット(221)を備える請求項1に記載のシステム。

**【請求項3】**

前記終端モジュール(22)は、前記スレーブ機能モジュールへの電源がオフにされる瞬間に書き込み動作が進行中である場合にエラーを知らせる応答を生成し、現在のトランザクションの間のどんな瞬間に、スレーブ機能モジュールへの電源がオフにされるかにかかわらず、書き込み要求の受信の終了時に前記エラーを知らせる応答を生成するように構成された第2の論理ユニット(222)を備える請求項1または2に記載のシステム。10

**【請求項4】**

前記相互接続バスは、組み合わせ通信プロトコルをサポートし、前記エラーが前記プロトコルに準拠したエラー信号の活性化によって知らされる請求項1から3のいずれか一項に記載のシステム。

**【請求項5】**

前記相互接続ネットワークは、順次通信プロトコルをサポートし、前記エラーが前記プロトコルに準拠したエラーメッセージの形式で知らされる請求項1から3のいずれか一項に記載のシステム。20

**【請求項6】**

中央演算装置(10)と、

相互接続バス(1)と、

別個のパワードメインの一部であるとともに、前記バスを介して、相互に通信することができますおよび前記中央演算装置と通信することができ、あるいは、相互に通信することができますまたは前記中央演算装置と通信することができる複数の機能モジュール(11～15、21)であって、トランザクションは、マスタ機能モジュールによる要求メッセージの送信、および、スレーブ機能モジュールによる応答メッセージの返信を含む、複数の機能モジュールと、を備えるシステムのための電源管理プロセスの方法であって、30

前記中央演算装置によって前記パワードメインへの電源及び前記スレーブ機能モジュールへの電源がオフにされるときに、スレーブモードでのみ動作でき、前記パワードメインの1つと関連付けられた終端モジュール(22)が前記パワードメインのスレーブ機能モジュール(21)を引き継ぎ、この引き継ぎは、前記終端モジュール(22)を前記相互接続バス(1)に接続することを含み、

電源がオフにされる瞬間に、前記スレーブ機能モジュールとマスタ機能モジュールとの間で進行中のトランザクションの任意の要求に応答してエラーを知らせ、

前記スレーブ機能モジュール(21)が前記相互接続バス(1)に接続されると、前記終端モジュール(22)は、前記相互接続バス(1)から切り離され、

前記終端モジュール(22)が前記相互接続バス(1)に接続されると、前記スレーブ機能モジュール(21)は、前記相互接続バス(1)から切り離される、方法。40

**【請求項7】**

前記終端モジュールは、前記スレーブ機能モジュールへの電源がオフにされる瞬間に読み出し動作が進行中である場合にエラーを知らせる応答を生成し、前記マスタ機能モジュールによって期待される読み出し応答の全持続時間にわたって前記エラーを知らせる応答を生成する請求項6に記載のプロセスの方法。

**【請求項8】**

前記終端モジュールは、前記スレーブ機能モジュールへの電源がオフにされる瞬間に書き込み動作が進行中である場合にエラーを知らせる応答を生成し、現在のトランザクションの間のどんな瞬間に、スレーブ機能モジュールへの電源がオフにされるかにかかわらず50

、書き込み要求の受信の終了時に前記エラーを知らせる応答を生成する請求項 6 または 7 のいずれかに記載のプロセスの方法。

【請求項 9】

前記相互接続バスが組み合わせ通信プロトコルをサポートする際に、前記エラーが前記プロトコルに準拠したエラー信号の活性化によって知らされる請求項 6 から 8 のいずれか一項に記載のプロセスの方法。

【請求項 10】

前記相互接続ネットワークが順次通信プロトコルをサポートする際に、前記エラーが前記プロトコルに準拠したエラーメッセージの形式で知らされる請求項 6 から 8 のいずれか一項に記載のプロセスの方法。

10

【請求項 11】

請求項 1 から 5 のいずれか一項に記載のシステムを備える電子機器。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、システム・オン・チップすなわち S o C といった集積回路システムの分野に関する。より詳細には、本発明は、そのようなシステムにおいてパワードメインへの電源が切断されるときの進行中のトランザクションの終結に関する。

【0002】

本発明は、電池式であり、機器の自律性を高めるために効率のよい電源管理が望ましい、携帯電話といった携帯用電子機器に特に応用することができる。

20

【背景技術】

【0003】

特にシステム・オン・チップにおいては、もっぱらシステムのある特定の機能を処理するための機能モジュールが、相互接続バスを介して相互に、および / または中央演算装置 (C P U) に接続されている。このバスは、決定されたプロトコルを使った、C P U と機能モジュールとの間の、および / または機能モジュール間の直接の制御情報およびデータのやりとりを確実に行わせる。このプロトコルは、順次的なものとすることも、組み合わせによるものとすることもできる。順次的である場合、マスタモジュールとスレーブモジュールとの間のトランザクションは、要求および応答と呼ばれるメッセージを交換することにより行われる。2 番目の場合、トランザクションは論理信号を使用して行われ、論理信号は、アドホック論理ゲートを使って論理ユニットによりハイまたはロウに設定される。

30

【0004】

総電力消費を低減するシステムのための電源管理を実装するために、システムは、別々の独立のパワードメインへと編成される。そのようなドメインに供給される電力は、したがって、その他のドメインから独立にオフにすることができます。各パワードメインは少なくとも 1 つの機能モジュールを含む。所与のパワードメインに含まれる機能モジュールの数に制限はないが、柔軟な電源管理を可能にするためのシステムの機能モジュールの総数と比べて小さい。

40

【0005】

例えば、携帯電話では、セルラネットワークによって送信されるビーコン無線周波数信号に聞き耳を立てる (listening) ための専用の機能モジュールが、ほとんど常時、電力を受け取る。逆に、M P 3 形式のオーディオデータを読み出し、復号するための専用の機能モジュールは、対応する機能がユーザによって要求されないときには、大部分の時間、電源がオフにされ得る。これによりチップの静的電力消費 (これには漏れ電流も寄与する) が低減され、電池電力が節約され、機器の自律性が高まる。

【0006】

所与のドメインへの電源をオフにすることは C P U によって決定される。機能モジュールへの電源が切断される瞬間に、モジュールが、C P U に知られることなく別の機能モジ

50

ュールとのトランザクションに関与している可能性もある。これは、マスタモジュールからの要求に直接応答するスレーブモジュールについて特に当てはまる。

#### 【0007】

機能モジュールの電源がオフにされると、他方の機能モジュールが決して送られることのない応答を待ち続ける状況が生じ得る。これは、通信プロトコルがそのような状況に対してロバストでない場合、システムを停止させ、完全再起動が必要になる可能性がある。

#### 【0008】

米国特許第6,590,907号明細書には、（同明細書で「パケットルータ」と呼ばれる）相互接続バスに位置し、別のモジュールが接続されているとマスタモジュールが期待する拡張ポートに上記別のモジュールが存在していないときに、上記別のモジュールに対してマスタモジュールによってアドレス指定された要求に応答する経路指定および調停(arbitration)の論理の使用が記載されている。応答は、エラーメッセージを発行することからなる。

#### 【0009】

この解決策は、システムのある特定の用途における別の機能モジュールの接続の可能性のための拡張ポートの存在を可能にし、要求が存在しない機能モジュールと関連付けられたパケット・ルータ・ポートに対してアドレス指定されるときに、システムが停止することを回避する。この解決策は、本発明が解決することを目指す問題とは異なる問題への解決策を提供すると同時に、多数のパワードメインを用いて実施されるときには難題も提示する。

10

20

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0010】

したがって、進行中のトランザクションを、その電源を切断させる機能モジュールを用いて、進行中のトランザクションを満足に終了させるためのより有効な解決策が求められている。

#### 【課題を解決するための手段】

#### 【0011】

本発明の第1の態様において、いくつかの実施形態は、

中央演算装置と、

相互接続バスと、

別個のパワードメインに対応し、バスを介して相互に、および／または、中央演算装置と通信できる複数の機能モジュールと、

30

パワードメインの1つと関連付けられ、前記パワードメインへの電源が中央演算装置によってオフにされるときに上記パワードメインのスレーブ機能モジュールの代わりになるとともに、電源がオフにされる瞬間に、スレーブ機能モジュールとマスタ機能モジュールとの間で進行中のトランザクションの任意の要求に応答してエラーを知らせるように構成された上記パワードメインと関連付けられた少なくとも1つのスレーブモジュールとを備えるシステムを提案する。

#### 【0012】

40

このように、たとえスレーブ機能モジュールへの電源が、このモジュールとマスタ機能モジュールとの間で進行中のトランザクションの処理の間にオフにされる場合でさえも、マスタモジュールはエラーメッセージを受け取り、これにより、マスタモジュールはスレーブモジュールが利用できないことから生じる状況を処理することができる。したがって、システムは応答を待つ間に停止しなくなる。

#### 【0013】

システムは、複数の集積回路にまたがって分散されていてもよい。しかし典型的には、システムは、システム・オン・チップ(SoC)として実現される。

#### 【0014】

一実施形態では、関連付けられたスレーブモジュールは、電源がオフにされる瞬間に読

50

み出し動作が進行中である場合にエラーを知らせる応答を生成するための第1の論理ユニットを備え、マスタ機能モジュールによって期待される読み出し応答の全期間にわたって、エラーを知らせる応答を生成する。

#### 【0015】

プロトコルから見た場合、これはすべて、マスタ機能モジュールにとって、あたかも、スレーブ機能モジュールの電源が依然としてオンであり、読み出しデータの代わりに、すなわち、マスタ機能モジュールによって期待される読み出し応答の全期間にわたってエラーを知らせているかのように見える。

#### 【0016】

加えて、または代替として、関連付けられたスレーブモジュールは、電源がオフにされる瞬間に書き込み動作が進行中である場合にエラーを知らせる応答を生成するための第2の論理ユニットを備え、第2の論理ユニットは、スレーブ機能モジュールへの電源が現在のトランザクションの間にオフにされる瞬間にかかわらず、書き込み要求の受信の終了時にエラーを知らせる。

10

#### 【0017】

プロトコルから見た場合、これはすべて、マスタ機能モジュールにとって、あたかも、スレーブ機能モジュールの電源が依然としてオンのままであり、書き込み要求を受け取った直後にエラーを知らせているかのように見える。

#### 【0018】

相互接続バスは、組み合わせ通信プロトコルをサポートすることができ、この場合にエラーは、上記プロトコルに準拠したエラー信号の活性化によって知らせることができる。

20

#### 【0019】

相互接続ネットワークが順次通信プロトコルをサポートする場合、エラーは、上記プロトコルに準拠したエラーメッセージの形式で知らせることができる。

#### 【0020】

本発明の第2の態様は、中央演算装置と、相互接続バスと、別個のパワードメインに対応し、バスを介して相互に、および／または中央演算装置とやりとりすることができる複数の機能モジュールとを備え、パワードメインの1つと関連付けられたスレーブモジュールが、上記パワードメインへの電源が中央演算装置によってオフにされるときに上記パワードメインのスレーブ機能モジュールの代わりに使用され、電源がオフにされる瞬間にスレーブ機能モジュールとマスタ機能モジュールとの間で進行中のトランザクションの要求に応答してエラーを知らせるシステム・オン・チップのための電源管理プロセスの方法を提案する。

30

#### 【0021】

また、本発明の第3の態様も、第1の態様によるシステム・オン・チップを備える電子機器に関するものである。典型的には、これは、電源のエネルギーが電源管理によって節約されなければならない携帯電話または他の任意の電池式機器とすることができる。

#### 【発明の効果】

#### 【0022】

有利には、本発明の実施形態は、システムにおいてパワードメインの数が増加する際に複雑さを増大させない。言い換えると、提案する解決策は、多数のパワードメインとの適合性を有する。

40

#### 【0023】

また、提案する解決策は、パワードメインの数を増加させることを伴う新しい用途の必要を満たすために所与のバージョンがアップグレードされるときに、例えば、既存のチップに機能を追加するときなどに、回路の設計において大きな変更を必要としない。

#### 【0024】

最後に、提案する解決策は、まだこの解決策を実装していない既存の回路を、回路の内部アーキテクチャをほとんど変更せずに更新するのに使用することができる。

#### 【0025】

50

本発明の他の特徴および利点は、以下の詳細な説明を読めば明らかになるであろう。この説明は、単なる例示にすぎず、添付の図面を参照して読むべきものである。

**【図面の簡単な説明】**

**【0026】**

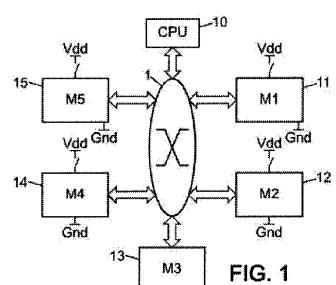

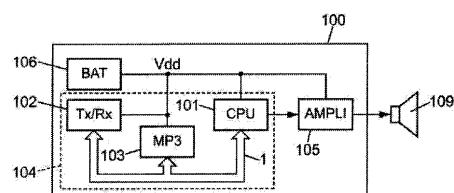

【図1】システム・オン・チップを示すブロック図である。

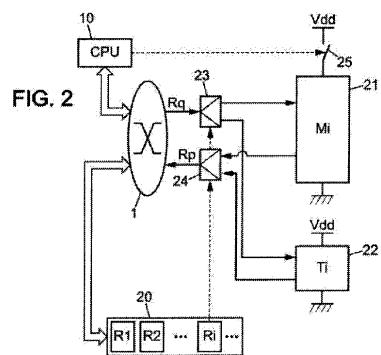

【図2】スレーブ機能モジュールおよびそれに関連付けられた終端装置モジュールのシステムバスへの選択的結合を示すブロック図である。

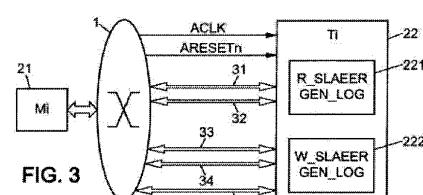

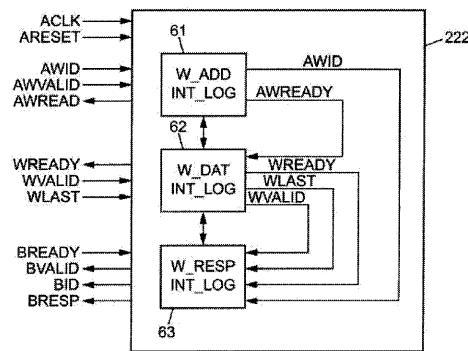

【図3】終端装置モジュールによってバス上で送られ、または受け取られる信号をより詳細に示す、上記終端装置モジュールの簡略化されたブロック図である。

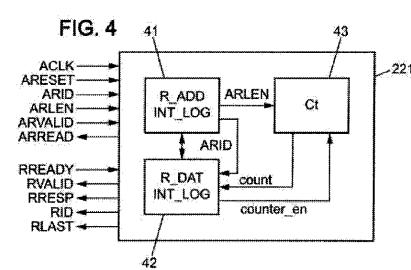

【図4】終端装置モジュールにおいて実装される第1の論理ユニットを示すブロック図である。10

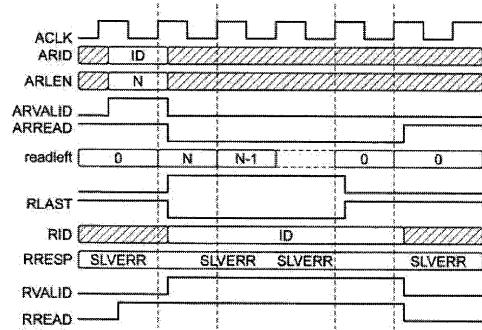

【図5】バスと終端装置モジュールの第1の論理ユニットとの間で交換される信号を示すタイミングチャートである。

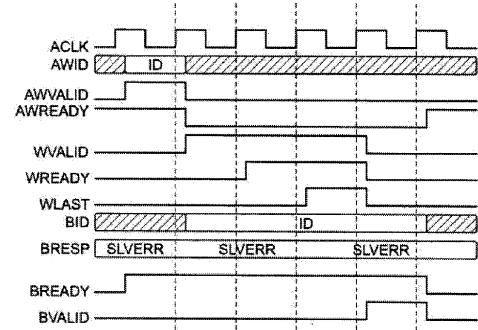

【図6】終端装置モジュールにおいて実装される第2の論理ユニットを示すブロック図である。

【図7】バスと終端装置モジュールの第2の論理ユニットとの間で交換される信号を示すタイミングチャートである。

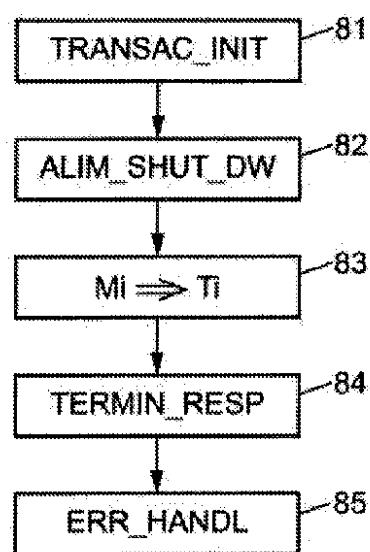

【図8】第2の態様による方法を示すステップ図である。

【図9】第1の態様によるシステムを組み込んだ第3の態様による機器を示すブロック図である。20

**【発明を実施するための形態】**

**【0027】**

次に、本発明の実施形態を、AXI（登録商標）と呼ばれる順次通信プロトコルを使用する例示的システム・オン・チップにおいて、添付の図面を参照して説明する。このプロトコルの仕様は、ARM Limitedという企業によって提案されたものであり、以下でAXI仕様と呼び、「AMBA Advanced extensible Interface (AXI) Protocol Specification」、バージョン1.0、B版、2004年3月19日付、という名称の公開標準文書において自由に入手することができ、読者は同文書を必要なだけ参照されたい。

**【0028】**

本例は限定するものではない。本発明の実施形態は、STMicroelectronicsのSTBus（登録商標）といった他の順次プロトコルに適用することもでき、ARM LimitedのAMBA（登録商標）アーキテクチャ（Advanced Microcontroller Bus Architecture）の別のプロトコルであるAPB（登録商標）（Advanced Peripheral Bus）やAHB（登録商標）（Advanced High-performance Bus）といった組み合わせプロトコル、あるいは別の例として、NoC（Network on Chip）プロトコルに適用することもできる。30

**【0029】**

本明細書で説明するシステムは、（ハードウェアでは）45nmCMOS技術および（ソフトウェアでは）Verilog（登録商標）記述言語を使って実現することができる。40

**【0030】**

図1にシステム・オン・チップのアーキテクチャを示す。

**【0031】**

システムは、それぞれシステムの一機能と関連付けられた機能モジュール11、12、13、14、および15を備える。これらのモジュールは、例えば、内部記憶、外部記憶管理部、オーディオデータを読み出すためのMP3復号器、ビデオデータを読み出すためのMPEG復号器、USBインターフェース管理部、ディスプレイ管理部などとすることができます。これらのモジュールは、マスタモジュールとともに、スレーブモジュール50

とすることも、コンテキストに応じてどちらか1つとすることもできる。例えばMP3復号器は、復号されるべきデータを読み出すために、スレーブモードで動作している内部記憶にマスター mode でアクセスできる。

#### 【0032】

またシステムは、システム全体を管理する中央演算装置10、すなわちCPUも備える。

#### 【0033】

これらの異なる要素は相互接続バス1によってやりとりし、各要素はそれぞれ適切なインターフェース（不図示）を介して相互接続バス1に結合されている。各トランザクションは、マスタモジュールによる要求メッセージの送信、およびスレーブモジュールによる応答メッセージの返信を含む。これらのメッセージは、引数として、送信元識別子および宛先識別子、すなわちアドレスを含む。これらは、トランザクションに関与するマスタモジュールおよびスレーブモジュールのそれぞれのインターフェース間でバス1を介してメッセージを経路指定するのに使用される。10

#### 【0034】

以下の説明を簡略化するために、各機能モジュールを、1つの特定のパワードメインに対応するものとみなす。言い換えると、この場合のパワードメインは1つの機能モジュールだけを含む。当然ながら、説明する原理を変更せずに、複数の機能モジュールをパワードメインの一部とすることもできることが理解される。

#### 【0035】

シリコンチップを実装するために、モジュールに電源電圧Vddを選択的に提供するオンチップ電源グリッドが定義される。接地面がすべての機能モジュールを接地電位Gnd、すなわち共通接地に接続する。

#### 【0036】

電池電力を節約するために、ここでは詳述する必要のない所与の基準に基づいて特定のドメインへの電源をいつオフにすべきか決定するのはCPUである。

#### 【0037】

システムのパワードメインの少なくとも1つについて、システムは、上記パワードメインと関連付けられた、「終端装置」モジュールと呼ばれる特定のモジュールを備える。この終端装置モジュールは、関連するパワードメイン内の機能モジュールの代わりに使用されるように配置および構成されるとともに、上記機能モジュールを用いて、電源がオフにされる瞬間に処理中である可能性のある任意のトランザクションを終了させるように配置および構成されている。終端装置モジュールはスレーブモードだけで動作する。トランザクションの終了は、ここで考察する例では、トランザクションを開始したマスタモジュールに（AXI仕様の第7.2.3節に定義されているように）エラーメッセージSOLVERRを送信することを含む。このエラーメッセージを提供することにより、マスタモジュールは、スレーブ機能モジュールが利用できないことを考慮に入れて、そのプロセスを完全に従来通りに実行し続けることができる。30

#### 【0038】

好ましくは、システムは、少なくとも1つのスレーブ機能モジュールが存在するパワードメインごとに終端装置を備える。これによりシステムが応答を待っている間に決して停止しなくなることが保証される。しかし本発明の利点は、システムの少なくとも1つのパワードメインが終端装置によって保護されるときにすでに達成されている。

#### 【0039】

また好ましくは、終端装置はパワードメインと排他的に関連付けられる。言い換えると、終端装置は、多くても1つのパワードメインについて提供される。これによりパワードメインの設計が簡略化される。

#### 【0040】

例えば、終端装置T1は機能モジュールM1と関連付けられ、終端装置T2は機能モジュールM2と関連付けられ、...終端装置Tiは機能モジュールMiと関連付けられ、...、50

ここで、 $i$  はシステムの機能モジュールに対応するパワードメインの 1 つを指定する指数である。

#### 【0041】

終端装置の設計および動作をより詳細に説明する前に、まず、終端装置および終端装置が関連付けられるパワードメインの機能モジュールがどのようにして一緒に配置されるか説明する。

#### 【0042】

図 2において、終端装置モジュール 22 (T<sub>i</sub>) は、その電源が C P U 10 によって選択的にオフにされ得る機能モジュール 21 (M<sub>i</sub>) と関連付けられている。これは、C P U 10 とモジュール 21 への電源電圧 V<sub>dd</sub> を制御するスイッチとの間の点線で表される制御信号によって示されている。

#### 【0043】

相互接続バス 1 へのモジュール 21 の結合の表現を簡略化するために、このモジュールはスレーブモードでのみ動作し得るものと仮定する。しかし、以下の説明は、このモジュール 21 がマスター モードで動作する場合にも完全に適合する。後者の場合には、バス 1 への結合は、その他の追加される要素が終端装置 22 の接続に関与することなく、単に後に続くものだけに対して完了されなければならない。

#### 【0044】

この例では、モジュール 21 は、要求メッセージ R<sub>q</sub> を受け取るためにデマルチプレクサ 23 を介して、および、応答メッセージ R<sub>p</sub> を返すためにマルチプレクサ 24 を介してバス 1 に結合されている。また終端装置 22 も、デマルチプレクサによってモジュール 21 の代わりにメッセージ R<sub>q</sub> を受け取るように知らされるときに、モジュール 21 の代わりにメッセージ R<sub>q</sub> を受け取るために、デマルチプレクサ 23 に結合されている。同様に、終端装置 22 は、マルチプレクサによってモジュール 21 の代わりにバス 1 に応答メッセージ R<sub>p</sub> を送るように知らされるときに、モジュール 21 の代わりにバス 1 に応答メッセージ R<sub>p</sub> を送るためにマルチプレクサ 24 にも結合されている。

#### 【0045】

より詳細には、デマルチプレクサ 23 は、バス 1 に結合された 1 つの入力、および、モジュール 21 と終端装置 22 とにそれぞれ結合された 2 つの出力を有する論理ゲートの組み合わせである。マルチプレクサ 24 は、モジュール 21 と終端装置 22 とにそれぞれ結合された 2 つの入力、および、バス 1 に結合された 1 つの出力を有する論理ゲートの組み合わせである。バス 1 への結合は、正しい電力レベルが供給されるようにするインターフェース（図 2 には表されていない）を介して行われ得る。

#### 【0046】

またシステムはレジスタの配列 20 も備え、配列 20 にはパワードメインごとに 1 つのレジスタがある。したがって、レジスタ R<sub>1</sub>、R<sub>2</sub>、…、R<sub>i</sub>、…などがある。例えば、書き込み要求を開始することにより、バス 1 を介してレジスタの配列 20 への書き込みアクセスを獲得することなどによって、C P U はこれらのレジスタに記憶される値を書き込むことができる。例えば、N 個のパワードメインがあって、レジスタの配列 20 に N 個のレジスタがある場合、書き込まれるべき値は、各ビットがそれぞれパワードメインと関連付けられた N ビットの値である。一変形では、C P U がバスを使用せずにレジスタの配列に直接書き込むことを可能にする制御プレーン接続が存在する場合には、C P U はレジスタの配列に直接書き込むことができる。

#### 【0047】

図 2 に 21 で表す機能モジュール M<sub>i</sub> と関連付けられたレジスタ R<sub>i</sub> に記憶された 2 進値は、デマルチプレクサ 23 およびマルチプレクサ 24 からの信号を制御する。例えば、このビットの論理値が 1 である場合、バス 1 に結合されるのはモジュール 21 であり、このビットの論理値が 0 である場合、バス 1 に結合されるのは終端装置 22 である。

#### 【0048】

C P U がモジュール 21 への電源をオフにするとき、C P U はスイッチ 25 に開くよう

10

20

30

40

50

指図し、また、レジスタの配列 2 0 に記憶された値を、レジスタ R i のビットが 1 から 0 に変化するように変更する。C P U がオンになるとき、または、C P U がモジュール 2 1 への電源を復元するときには、逆の動作が実行される。

#### 【 0 0 4 9 】

次に、機能モジュール 2 1 と関連付けられる終端装置モジュール 2 2 の一般的な構造およびレイアウトを、図 3 の図を参照して説明する。

#### 【 0 0 5 0 】

終端装置 2 2 はスレーブモジュールである。終端装置 2 2 は、それが関連付けられる機能モジュール 2 1 と同様に、A X I 仕様に記載されている以下の 5 つのチャネルを介してバス 1 に結合されている。

10

#### 【 0 0 5 1 】

- アドレス読み出しチャネル 3 1

- データ読み出しチャネル 3 2

- アドレス書き込みチャネル 3 3

- データ書き込みチャネル 3 4

- 書き込み応答チャネル 3 5

#### 【 0 0 5 2 】

加えて、終端装置 2 2 は、バス 1 から、クロック信号 A C L K および非同期リセット信号 A R E S E T n ( 小文字の n は、この信号がロウ論理状態でアクティブであることを示す ) も受け取る。

20

#### 【 0 0 5 3 】

この信号のセットは、データチャネルのサイズに応じて、約 4 0 0 ラインを表す。詳細は前述の A X I 仕様において入手することができる。

#### 【 0 0 5 4 】

終端装置はデータを処理しないため、データチャネルは「ドント・ケア ( d o n ' t c a r e ) 」状態にある。同じことは、データのサイズを示す A X I プロトコルの信号、およびバーストの種類を示す A X I プロトコルの信号 ( バーストとは、要求に応答して送られるデータの単位であり、整数のクロック信号周期に対応する ) についても当てはまる。

#### 【 0 0 5 5 】

30

A X I プロトコルにおける信号の中には、終端装置によって使用されないものもある。使用される信号を以下の表 1 に示す。

【表 1】

| Name of Signal                | Size | Type | Description                                 |

|-------------------------------|------|------|---------------------------------------------|

| <b>Clock and Reset</b>        |      |      |                                             |

| ACLK                          | 1    | IN   | AXI clock                                   |

| ARESETn                       | 1    | IN   | Asynchronous reset, active in the low state |

| <b>Write address channel</b>  |      |      |                                             |

| AWID                          | 4    | IN   | Write address ID                            |

| AWVALID                       | 1    | IN   | Write address valid                         |

| AWREADY                       | 1    | OUT  | Write address ready                         |

| <b>Write Data Channel</b>     |      |      |                                             |

| WVALID                        | 1    | IN   | Write valid                                 |

| WLAST                         | 1    | IN   | Last write transfer                         |

| WREADY                        | 1    | OUT  | Write ready                                 |

| <b>Write Response Channel</b> |      |      |                                             |

| BID                           | 4    | OUT  | Write response ID                           |

| BRESP                         | 2    | OUT  | Write response                              |

| BVALID                        | 1    | OUT  | Write response valid                        |

| BREADY                        | 1    | IN   | Write response ready                        |

| <b>Read Address Channel</b>   |      |      |                                             |

| ARID                          | 4    | IN   | Read address ID                             |

| ARLEN                         | 4    | IN   | Burst length                                |

| ARVALID                       | 1    | IN   | Read address valid                          |

10

| Name of Signal           | Size | Type | Description        |

|--------------------------|------|------|--------------------|

| ARREADY                  | 1    | OUT  | Read address ready |

| <b>Read Data Channel</b> |      |      |                    |

| RID                      | 4    | OUT  | Read ID            |

| RRESP                    | 2    | OUT  | Read response      |

| RVALID                   | 1    | OUT  | Read valid         |

| RLAST                    | 1    | OUT  | Last read transfer |

| RREADY                   | 1    | IN   | Read ready         |

20

30

## 【0056】

この表では、(AXI仕様を参照する)信号の名前が第1列に示され、信号のバイト単位の長さが第2列に示され、その種類(入ってくる信号には「IN」、出て行く信号には「OUT」)が第3列に示され、信号の説明が第4列に示されている。

## 【0057】

信号ARID、AWID、RID、WIDおよびBIDの2進数の長さは、テンプレートおよびパラメータを使って構成することができ、これについての詳述は不要である。単に、ユーザがバス上のIDラベルのバイト単位の長さを定義するパラメータID\_WIDTHの値を選択できることを記すだけにとどめる。デフォルト値は1バイトである。パラメータID\_MAXの値は、バス上のIDラベルについての(バイト単位の)長さの上限を定義し、ユーザによって定義されるパラメータID\_WIDTHに基づいて自動的に計算される。

40

## 【0058】

図3に示すように、終端装置は、それが返すエラーメッセージSLVERRについて、読み出し動作が進行中である場合にエラー信号を生成するための論理ユニット221と、書き込み動作が進行中である場合にエラー信号を生成するために論理ユニット221の2つのソースを備える。これら2つの別個の事例は電源がオフにされる瞬間に進行中のトランザクションを指し、このトランザクションは終端装置によるメッセージSLVERRの

50

送信を求める。論理ユニット221は、したがって、機能モジュール21がスレーブモードで読み出し動作に関与している間に、機能モジュール21への電源がオフにされるときに活性化される。逆に、論理ユニット222は、機能モジュール21がスレーブモードで書き込み動作に関与している間に、機能モジュール21への電源がオフにされるときに活性化される。

#### 【0059】

図4に、読み出し動作が進行中である場合にエラーメッセージ応答を生成するための論理ユニット221のブロック図を示す。この図には、論理ユニット221によって送信され、または受信される信号が、受信される信号についての入ってくる矢印および送信される信号についての出て行く矢印と共に、左側に表されている。10

#### 【0060】

論理ユニット221は、アドレス読み出しチャネルおよびデータ読み出しチャネルの動作を担当する。論理ユニット221は、例えば、アドレス読み出しつェース論理ブロック41、データ読み出しつェース論理ブロック42、およびカウンタ43（実際にはダウンカウンタ）を備える。

#### 【0061】

ブロック41は、アドレス読み出しチャネル31およびデータ読み出しチャネル32の動作を担当する。

#### 【0062】

ブロック41は、アドレス読み出しチャネル上にある情報をロードし、信号ARREA

DYを活性化し、カウンタ43の初期値を再初期設定する。例えば、この再初期設定は、カウンタ43の現在値を、信号ARLENにおいて受け取られる非ゼロの整数である値Nに設定する。ブロック41はこのためにカウンタ43に信号ARLENを送る。20

#### 【0063】

また、ブロック42がトランザクションを初期設定したマスタモジュールの識別子IDを、上記識別子が信号ARIDにおいて受け取られる際に知るように、ブロック41はブロック42に信号ARIDを送る。

#### 【0064】

ブロック42は、応答信号RRESPを、エラーメッセージSLVERRを示すように設定する。このエラーメッセージは、スレーブモードが利用できないことを示すことに対応する。またブロック42は、カウンタ43から受け取る「readleft」で表されるカウンタ43のカウント値に基づいて、信号RVALIDおよび信号RLASTを生成する。例示的実施形態では、この機能に対応するVerilogコードは以下とすることができます。

#### 【0065】

```

assign iLAST = (readleft == 4'b0000) ? 1'b1

: 1'b0;

assign RLAST = iLAST;

```

#### 【0066】

ブロック42は、カウンタ活性化信号であるcounter\_enで表される、論理ユニット221にとっての内部の信号を生成する。この信号は、例えば、信号RVALID、信号RRREADY、およびカウンタのカウント値readleftが0ではないという追加条件の間の論理AND演算の結果などである。信号counter\_enがハイ状態にあるとき、値readleftは、提示されるクロック信号ACLKの各立ち上がりエッジにおいて1単位減分される。40

#### 【0067】

図5のタイミングチャートに、論理ユニット221の動作に関与し、および/または論理ユニット221の動作によって変更される種々の信号のタイミングを示す。このタイミングチャートでは、適切な場合に信号によって搬送される応答メッセージおよび値が示されている。50

**【0068】**

図示のように、論理ユニット221は、機能モジュール21の電源がオフにされる瞬間に機能モジュール21において読み出し動作が進行中であるときに、終端装置22が、マスタモジュールによって期待される応答バーストの全持続時間にわたって、すなわち、Nサイクルのクロック信号ACKにわたって（Nは信号ARLENにおいて受け取られる値である）データ読み出しチャネル上で応答SLVERRを返すように構成されている。

**【0069】**

言い換えると、これは、すべて、読み出しトランザクションの間にスレーブモジュール21への電源がオフにされる瞬間にかかわらず、トランザクションを開始したマスタモジュールに対して透過的（transparent）であるように行われる。終端装置は、起動モジュールにとって、すべてが、あたかも機能モジュール21がまだ電力を受け取っており、読み出しデータの代わりに、すなわち、マスタ機能モジュールによって期待される読み出し応答の全持続時間にわたって、エラーメッセージSLVERRを送っているかのように続行されるように動作する。10

**【0070】**

図6に、書き込み動作が進行中である場合にエラーメッセージを生成するための論理ユニット222のブロック図を示す。この図には、論理ユニット222によって送信され、または受信される信号が、受信される信号についての入ってくる矢印および送信される信号についての出て行く矢印と共に左側に表されている。

**【0071】**

論理手段222は、アドレス書き込みチャネル34、データ書き込みチャネル35、および書き込み応答チャネル33の動作を担当する。論理手段222は、アドレス書き込みインターフェース論理プロック61、データ書き込みインターフェース論理プロック62、および書き込み応答インターフェース論理プロック63を備える。20

**【0072】**

書き込みおよびデータアドレスは重要ではない。というのは、書き込み動作は完了されず、エラーメッセージSLVERRを含む応答信号BRESPを送ることにより終了されるからである。

**【0073】**

プロック61およびプロック62はそれぞれ、相互に独立に、アドレス書き込みチャネル信号34およびデータ書き込みチャネル信号35を処理する。プロック61は信号AWREADYをプロック62に提供し、信号AWIDをプロック63に提供する。30

**【0074】**

プロック62は信号WREADY、信号WLAST、および信号WVALIDをプロック63に提供する。そこで、これら3つの信号をサンプリングすることにより、書き込み応答確認信号BVALIDが生成される。これらの信号が同時にハイ論理状態にあるとき、信号BVALIDはハイ論理状態に設定される。これは、現在の書き込みトランザクションが終了されること示す。

**【0075】**

図7のタイミングチャートに、論理ユニット222の動作に関与し、および／または論理ユニット222の動作によって変更される異なる種々のタイミングを示す。このタイミングチャートでは、適切な場合に信号によって搬送される応答メッセージおよび値が示されている。40

**【0076】**

第1の信号が第2の信号において受け取られる識別子IDの値を含むという意味において、送られる信号BIDは受け取られる信号AWIDから導出されることに留意されたい。

**【0077】**

加えて、信号AWREADYがロウ状態に移るときに、信号WREADYは1サイクルの遅延でハイ状態に移る。信号WREADYは、信号WVALIDおよび信号WLAST50

が同時にロウ状態であるときにハイ状態に戻る。

**【0078】**

言い換えると、これは、すべて、現在のトランザクションの間にスレーブモジュール21への電源がオフにされる瞬間にかかわらず、トランザクションを開始したマスタモジュールに対して透過的であるように行われる。終端装置は、起動モジュールにとって、すべてが、あたかも機能モジュール21がまだ電力を受け取っており、機能モジュール21自分が、書き込まれるべき2進データを受け取った後で、すなわち書き込み要求の受信の終了時にエラーメッセージS L V E R Rを送っているかのように動作する。

**【0079】**

本発明の実施形態によるプロセスのステップが図8に示されている。

10

**【0080】**

ステップ81で、マスタ機能モジュールが、前述のように、システム・オン・チップのスレーブ機能モジュールとのトランザクションを開始する。これは読み出し要求でもよいし、書き込み要求でもよい。

**【0081】**

ステップ82で、システム・オン・チップのCPUは、この機能モジュールがまだ進行中のトランザクションに関与していることを知ることなく、エネルギーを節約するために、スレーブ機能モジュールへの電源をオフにする。

**【0082】**

ステップ83で、スレーブ機能モジュールMiと関連付けられた終端装置モジュールTiが、スレーブ機能モジュールMiの役割を引き継ぐ。前述のように、これは、スレーブ機能モジュールをバスから切り離し、関連付けられた終端装置モジュールを上記バスに結合することによって行われる。

20

**【0083】**

ステップ84で、終端装置モジュールは現在処理されている要求への応答を生成し、送る。この応答はエラーメッセージに対応するものである。

**【0084】**

ステップ85で、要求を送ることによりトランザクションを開始したマスタモジュールは、エラーメッセージを受け取り、処理する。受け取られるエラーメッセージの原因を従来のように特定し、しかるべき反応することは、このマスタモジュールに実装されているソフトウェア次第である。

30

**【0085】**

図9のブロック図に、前述のシステム・オン・チップを組み込んだ機器の要素を示す。そのような機器は、携帯電話でもよいし他の電子機器でもよく、他の電子機器は通信機器であってもよいしなくてもよい。この機器は、典型的には、電池で動作し、したがって、電池電力を節約するための電源管理が望ましい。

**【0086】**

機器100は、中央演算装置101と、外部から、特に、無線周波数搬送波の変調によって情報を送信および受信するための通信部102とを備える。また機器100は、音楽といった（例えば、図示されないメモリなどに記憶された）MP3形式のファイルを読み出すための装置103も備える。装置101は、通信バス1を介して装置102および装置103とやりとりする。これらの要素はそれぞれ電池106によって送られる電源電圧Vddにより電力供給される。

40

**【0087】**

実施形態によっては、制御部101はCPUであり、装置102および装置103は、前述のようなシステム・オン・チップ104の機能モジュールである。システム104は、増幅器105による増幅の後で、例えばスピーカ109などを介してユーザのために再生されるオーディオ信号を生成する。

**【0088】**

これらの実施形態を実装すれば、システム・オン・チップ104の要素によって消費さ

50

れる電流が低減され、したがって、機器 100 の自律性、すなわち、2 回の電池充電 106 の間に使用され得る時間の長さが延長される。有利には、この電力節約は、トランザクションに関与するスレーブ機能モジュールの電源がオフにされる瞬間にスレーブ機能モジュールからの応答がないため、システムが停止するリスクを伴わずに達成される。

#### 【 0 0 8 9 】

以上本発明を特定の実施形態を参照して説明した。当然ながら、技術的に実現可能な任意の変形は本願のコンテキストの範囲内に入ることが理解される。特に、本発明はシステム・オン・チップ (S o C) の状況において説明したが、システムは複数の集積回路において、すなわち、複数のチップにおいて各要素を含むこともできることが理解される。この場合、相互接続バスは、異なる集積回路を相互接続するバスを備えることができる。

10

【 図 1 】

FIG. 1

【 図 2 】

【 図 3 】

【 図 4 】

【図5】

FIG. 5

【図7】

FIG. 7

【図6】

FIG. 6

【図8】

FIG. 8

【図9】

FIG. 9

---

フロントページの続き

(74)代理人 100167933

弁理士 松野 知紘

(72)発明者 ベルナール、ラマナダン

フランス国クロル、リュ、ギヨーム、アポリネール、39

(72)発明者 メン、テッダー

中華人民共和国上海、ミンハン、ディストリクト、ジング、イースト、ロード、エヌ. 99

(72)発明者 ワン、ウェイ、タオ

中華人民共和国上海、ツォンシャン、ウエスト、ロード、1410、ナンバー12、ルーム、30

2

(72)発明者 チェン、ロバート、サンシン

中華人民共和国上海、シフェン、ロード、レーン、626、ナンバー33、ルーム、602

(72)発明者 ガブリエル、ダフィー

フランス国グルノーブル、ブルバール、クレマンソー、35

審査官 高 橋 正 徳

(56)参考文献 特開2002-014939 (JP, A)

特開2005-267595 (JP, A)

特開2001-168917 (JP, A)

特開平10-124191 (JP, A)

特表昭62-501252 (JP, A)

米国特許第04955075 (US, A)

特開2003-308257 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 06 F 11/00 ,

G 06 F 1/32 ,

G 06 F 15/78 ,

G 06 F 9/46 - 9/54 ,

G 06 F 1/26