(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-523368

(P2007-523368A)

(43) 公表日 平成19年8月16日(2007.8.16)

|                             |                                     |                      |

|-----------------------------|-------------------------------------|----------------------|

| (51) Int.C1.                | F 1                                 | テーマコード (参考)          |

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J                         | 3K107                |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 624B                      | 5C080                |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 670A                      |                      |

| <b>H05B 33/10</b> (2006.01) | G09G 3/20 641D                      |                      |

|                             | HO5B 33/14 A                        |                      |

|                             | 審査請求 未請求 予備審査請求 未請求 (全 20 頁) 最終頁に続く |                      |

| (21) 出願番号                   | 特願2006-552140 (P2006-552140)        | (71) 出願人 590000846   |

| (86) (22) 出願日               | 平成17年1月21日 (2005.1.21)              | イーストマン コダック カンパニー    |

| (85) 翻訳文提出日                 | 平成18年8月3日 (2006.8.3)                | アメリカ合衆国、ニューヨーク14650  |

| (86) 國際出願番号                 | PCT/US2005/001990                   | , ロチェスター、ステイト ストリート3 |

| (87) 國際公開番号                 | W02005/078691                       | 43                   |

| (87) 國際公開日                  | 平成17年8月25日 (2005.8.25)              | (74) 代理人 100070150   |

| (31) 優先権主張番号                | 10/773,509                          | 弁理士 伊東 忠彦            |

| (32) 優先日                    | 平成16年2月6日 (2004.2.6)                | (74) 代理人 100091214   |

| (33) 優先権主張国                 | 米国(US)                              | 弁理士 大貫 進介            |

|                             |                                     | (74) 代理人 100107766   |

|                             |                                     | 弁理士 伊東 忠重            |

|                             |                                     | (74) 代理人 100145377   |

|                             |                                     | 弁理士 杉山 公一            |

|                             |                                     | 最終頁に続く               |

(54) 【発明の名称】 改善された耐故障性を有するOLED装置

## (57) 【要約】

複数の列電極、及び複数の行の個々にアドレス可能なOLED画素を有するアレイは、各々の行が一般に共有される共有電極を含み、各々の行の少なくとも1つのOLED画素が電流制限素子、及び有機エレクトロルミネッセント・ダイオードを有し、少なくとも1つのOLED画素が共有電極と複数の列電極の1つとの間に電流を通電するためにそれらの間に接続されており；且つ有機エレクトロルミネッセント・ダイオードが電流制限素子と直列に接続されている。

**【特許請求の範囲】****【請求項 1】**

複数の列電極、及び複数の行の個々にアドレス可能なOLED画素を有するアレイであって、各々の行が一般に共有される共有電極を含み：

a) 各々の行の少なくとも1つのOLED画素が電流制限素子、及び有機エレクトロルミネッセント・ダイオードを有し、且つ前記少なくとも1つのOLED画素が前記共有電極と前記複数の列電極の1つとの間に電流を通電するためにそれらの間に接続されており；且つ

b) 前記有機エレクトロルミネッセント・ダイオードが前記電流制限素子と直列に接続されている；

ことを特徴とするアレイ。

**【請求項 2】**

前記電流制限素子が少なくとも1つのダイオードを含むことを特徴とする請求項1に記載の複数の行のOLED画素を有するアレイ。

**【請求項 3】**

前記電流制限素子が少なくとも1つのエレクトロルミネッセント・ダイオードを含むことを特徴とする請求項1に記載の複数の行のOLED画素を有するアレイ。

**【請求項 4】**

前記電流制限素子が溶断部材であることを特徴とする請求項1に記載の複数の行のOLED画素を有するアレイ。

**【請求項 5】**

前記電流制限素子が抵抗であることを特徴とする請求項1に記載の複数の行のOLED画素を有するアレイ。

**【請求項 6】**

複数の列電極、複数の行電極、及び個々にアドレス可能なOLED画素を有するアレイであって、各々の画素が複数のサブピクセルを有し、且つ各々の行のOLED画素が一般に共有される共有電極を含み：

a) 前記サブピクセルが行電極と列電極との間に並列に接続されており、且つ前記サブピクセルがさらにエレクトロルミネッセント・ダイオード及び電流制限素子を有し；且つ

b) 前記エレクトロルミネッセント・ダイオードが前記電流制限素子と直列に接続されている；

ことを特徴とするアレイ。

**【請求項 7】**

前記電流制限素子が抵抗、溶断部材、又はダイオードであることを特徴とする請求項6に記載の複数の行のOLED画素を有するアレイ。

**【請求項 8】**

前記列電極が、前記共有電極に重なっているとともに、各分割片と前記共有電極との間に前記エレクトロルミネッセント・ダイオードを形成するように分割されており、それにより各分割片に並列ダイオードを形成していることを特徴とする請求項6に記載のアレイ。

**【請求項 9】**

前記各分割片が前記列電極の材料から成るストリップであることを特徴とする請求項8に記載の複数の行のOLED画素を有するアレイ。

**【請求項 10】**

OLEDセルの1つ以上のバンクとして配置されたOLEDセルのアレイを有するエリア照明装置であって：

a) 前記OLEDセルの各々が、溶断部材と直列接続されたエレクトロルミネッセント・ダイオードを有し；

b) 各バンクが、並列接続された複数の前記OLEDセルを含み；且つ

c) 前記OLEDセルの1つ以上のバンクが、互いに直列又は並列に接続されている；

10

20

30

40

50

ことを特徴とするエリア照明装置。

【請求項 1 1】

前記 O L E D セルの 1 つ以上のバンクが交流電源に接続されていることを特徴とする請求項 1 0 に記載のエリア照明装置。

【請求項 1 2】

前記 O L E D セルの 1 つ以上のバンクが直流電源に接続されていることを特徴とする請求項 1 0 に記載のエリア照明装置。

【請求項 1 3】

個々にアドレス可能な O L E D 画素のアレイをリペアする方法であって：

a ) 複数の行の有機エレクトロルミネッセント・ダイオードとしてアレイを形成する形成ステップであり、各行の各ダイオードが、各行の一般に共有される共有電極と複数の列電極の 1 つとの間に接続され、且つ各行の各ダイオードが溶断部材と直列に接続される、ところの形成ステップ；

b ) 短絡したダイオードに直列の溶断部材を飛ばすために 1 つの行及び 1 つの列電極の間に逆電圧を印加するステップ；

を有する方法。

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、耐故障性のある O L E D 装置に関する。

20

【背景技術】

【0 0 0 2】

有機発光ダイオード (O L E D) 技術は広範囲のアプリケーションに適したディスプレー技術として大いに期待されている。自己発光の O L E D ディスプレーは、高輝度、高品質の色合い、及び比較的広視野角をもたらし、他のディスプレー技術より有利である。O L E D ディスプレーコンポーネントは薄く、軽量であり、特に掌サイズのコンポーネントでの使用に適応可能である。掌サイズのコンポーネントとは例えばカメラ、携帯電話、携帯情報端末 (P D A) 及びラップトップ計算機器等である。

【0 0 0 3】

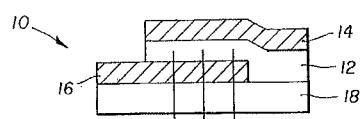

基本的な底面発光 O L E D 画素 10 は図 1 に示されるように構成される。有機層 12 は一般的に複数の有機薄膜の積層体として組み立てられ、カソード 14 と透明アノード 16 との間に挟まれてガラス基板 18 上に構築される。有機層 12 は、アノード 16 とカソード 14 との間に適当な電圧が印加されたときに明るくなるエレクトロルミネッセント層を含んでいる。画素 10 はカソード 14 とアノード 16 との間の重なり部分に形成される。O L E D ディスプレーは、一連の行及び列のアレイとして配置された個々にアドレス可能な O L E D 画素 10 から成る規則的な空間配置から形成される。

30

【0 0 0 4】

O L E D アレイにはパッシブマトリックス型とアクティブマトリックス型という 2 つの基本型式がある。アクティブマトリックス型 O L E D ディスプレーは電流制御回路をディスプレー自体の内部に一体化しており、高リフレッシュ速度で高解像度カラー画像を作り出すため、基板上の個々の画素それぞれに別個の制御回路が専用化されている。他方、パッシブマトリックス型 O L E D ディスプレーは、ディスプレー自体の外部のみに電流制御回路を有する。従って、パッシブマトリックス型 O L E D ディスプレーはアクティブマトリックス型ディスプレーより単純な構成をしており、より簡易で低コストの製造技術を用いることができる。

40

【0 0 0 5】

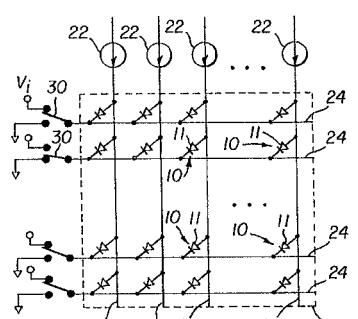

図 2 a は、パッシブマトリックス型 O L E D アレイ 20 の基本配置の概略図を示している。アレイ 20 内にて、各々の個々にアドレス可能な O L E D 画素 10 はアノードライン 26 (列) とカソードライン 24 (行) との間に接続されたエレクトロルミネッセント (E L) ダイオード 11 を有する。各アノードライン 26 は電流源 22 を有し、画像データに従って各列の画

50

素を明るくするために、電流源22がアノードライン26に対してオンに切り替えられる。カソードライン24は一般に行内の各ELダイオード11に共有されている。各カソードライン24のスイッチ30は、行スキャンシーケンスを用いて連続する各行の画素を明るくするよう1度に1行ずつグラウンドに切り替わる。ELダイオード11はその電流源22がオンに切り替えられ、且つその対応する行スイッチ30がグラウンドに切り替わると明るくなる。そもそもなければ、カソードライン24は一般的に中間電圧Viに切り替えられる。ELダイオード11は、そのカソード電位がViであるときは明るくならない。そのカソードライン24を中間電圧Viにすることにより、スキャンされていない如何なる行の画素10もターンオフされるが、その行の電位は維持される。これにより、各々の行がアドレスされたときにその行の寄生キャパシタンスを充電するのに必要な電力量が削減される。この単純な配置を用いることで、パッシブマトリックス型OLEDアレイ20は、行及び列のマトリックス状に編成された数千個の画素10を有するように構成され得る。ディスプレー機器（図示せず）の制御ロジックが、ディスプレーコンポーネント技術で周知の制御及びタイミング技術を用いて、各々の列の電流源22、及び各々の行のスイッチ30の制御を実現し、各OLED画素10を個々にアドレス可能にする。

#### 【0006】

なお、上記記載及び図2aの概略図は、パッシブマトリックス型OLEDアレイ20の制御機構及び構成要素を簡略化して説明するものであることを強調しておく。従来のパッシブマトリックス型OLEDアレイ及びアレイドライバの対処策に関するさらに詳細な事項は、例えば特許文献1及び特許文献2に記載されている。

#### 【0007】

対角線で数インチの小型OLEDディスプレーは構築に成功してきたものの、今もなお、製造欠陥が大面積のパッシブマトリックス型OLEDディスプレー開発の障害となっている。例えば、製造中のダストや汚染、電極表面による凹凸、ピンホール、及び有機層厚さの不均一性が欠陥原因となり得る。

#### 【0008】

ディスプレー動作に特に関係があるのは、ELダイオード11の短絡に起因する欠陥である。図2aから分かるように、画素10の短絡ELダイオード11は事実上、対応する行がスキャンされるとき電流源22をグラウンドに直接的に接続する。他の行がスキャンされるときには、短絡ELダイオード11は事実上、中間電位Viをアノードライン26に設定する。このため、画素10の列全体がディスプレー動作時に真っ暗になってしまう。ある程度の数の故障画素10は見た目の画像では許容されるが、一般に、列全体に影響を及ぼす欠陥は受け入れられない。故に、実際には、OLEDアレイ20の全面積での短絡画素欠陥に関する許容度はゼロである。

#### 【0009】

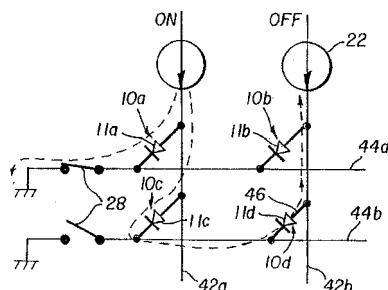

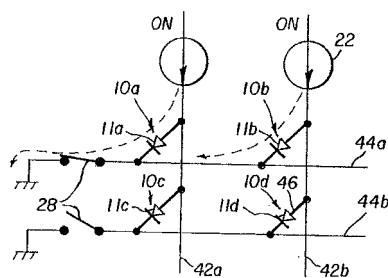

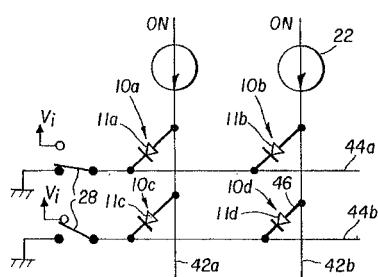

図2b、2c、2d及び2eは、ダイオードが短絡した状態で種々のOLEDアレイ20構成がどのように動作するかを示している。図2b、2c及び2dは、中間電圧Viへの接続がなく、スイッチ群28が（グラウンドに対して）開いているか閉じているかの何れかであるOLEDアレイ20を示している。図2bには、行44a及び44b並びに列42a及び42bの配置内の個々にアドレス可能な画素10a、10b、10c及び10dに、それぞれ、ELダイオード11a、11b、11c及び11dを有するOLEDアレイ20の微小部分が示されている。図2bの例では、短絡46で図示されるようにELダイオード11dが短絡している。行のスキャン中に、それぞれのスイッチ28にて示されるように、行44aは使用可能にされ、隣接する行44bは使用不可能にされている。列42aの電流源22は、列42aと行44aとの交点にある画素10aを（ELダイオード11aに電流を与えることにより）明るくするようにオンにされている。しかしながら、短絡46が隣の行44bの列42bの画素10dにある。故に、短絡46がELダイオード11cを介して列42bに望ましくない電流経路を提供する。短絡46を流れる電流量によっては、ELダイオード11cは明るくなることができ、それによりアレイ20の全ての行44のスキャン中ずっとオンになってしまふ。ELダイオード11cの照度が薄暗く一定であっても望ましくはない。図2cに示されるように、双方の電流源22がオンのとき、画素10cは望ま

しい状態となる。図 2 d に示されるように、行 44b がスキャンされ、且つ E L ダイオード 1 1c がオンであるとき、短絡 46 は事実上バイパスされる。

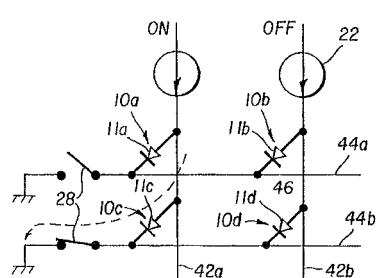

#### 【 0 0 1 0 】

図 2 e は、行 44b がスキャンされるまでスイッチ 28 が中間電圧 Vi にある O L E D アレイ 2 0 の配置を示している。短絡 46 が図示の位置にあり、行 44b のスイッチ 28 が遊休 (idle) 電圧 Vi に接続し、且つ行 44a がスキャンされるとき、又は行 44b 以外の何れかの行がスキャンされるとき、列 42b は Vi に拘束される。このため、列 42b は事実上、使用不可能である。電流源 22 が同時に唯一の E L ダイオード 11 への電流しか提供できないように設計され、一方で中間電圧 Vi が全ての行 44a、44b に印加される場合について述べておくことは有益であるが、短絡 46 によって生じる状態を補償するように各々の列 42a、42b の電流源 22 の容量を決めるることは実用的ではない。10

#### 【 0 0 1 1 】

ディスプレーが大面積化するにつれ、製造欠陥の可能性は劇的に増加する。アレイ 20 全体での欠陥密度がポアソン分布の特徴を示すと仮定すると、アレイ 20 が 1 つも欠陥を有さない確率が歩留まり Y であり、数式 1 :  $Y = \exp(-DA)$  で表される。ここで、D は面積当たりの短絡ダイオード 11 の短絡欠陥密度であり、A はアレイ 20 の全面積である。

#### 【 0 0 1 2 】

欠陥密度 D 及び面積 A の影響が指数関数的に増大することは特に重大である。例えば、妥当な欠陥密度である  $D = 0.01/cm^2$ 、 $A = 0.5m^2$  では、歩留まりは  $Y = 2 \times 10^{-22}$  となる。換言すれば、非常に大きなパッシブマトリックス型 O L E D ディスプレーで、良品のディスプレーが生産される見込みは事実上皆無に等しい。数式 1 の指数の因子 D 及び A の劇的な低減のみが O L E D アレイの妥当な歩留まりを可能にする。20

#### 【 0 0 1 3 】

アクティブマトリックス型 O L E D 設計は、この欠陥関連の性能問題に対する 1 つの解決策を提供するものである。アクティブマトリックス型 O L E D アレイにおいては、薄膜トランジスタ (TFT) 及び蓄積キャパシタのアレイを用いて、個々の O L E D 画素 10 の各々が独立してアクセス可能である。アクティブマトリックス型ディスプレー回路は、例えば特許文献 3 及び特許文献 4 に開示されている。アクティブマトリックス型の構成では、何れの O L E D 画素 10 での短絡ダイオード欠陥も、その他の O L E D 画素 10 には影響を及ぼさない。しかしながら、上述のように、アクティブマトリックス型 O L E D アレイの設計はかなり複雑であり、各 O L E D 画素 10 に多数の追加支援素子を必要とする。30

#### 【 0 0 1 4 】

アレイが、O L E D 画素 10 の欠陥を補償するように、選択的にアクティブ又は非アクティブにされる部分群を有する新しいパッシブマトリックス型手法が特許文献 5 に開示されている。この O L E D アレイでは、各々の列が 2 つの別個の部分を含み、短絡ダイオードの場合にはそれらの何れかがアクティブ又は非アクティブにされる。この手法は、欠陥問題を軽減することはできるものの、アレイはかなりの数の追加素子を必要とする。また、その追加素子の多くは使用されないものである。さらに、製造及び試験後に生じた欠陥は依然としてディスプレー性能に悪影響を与える。

#### 【 0 0 1 5 】

アドレス可能な画像ディスプレーに用いられる O L E D アレイのためのものでないことは明らかであるが、部屋照明や標識応用に用いられる大型 O L E D セル又はモジュール用に提案された解決策が幾らか興味深い（特許文献 6 参照）。そこには、複数の大面積 O L E D モジュールを交流電源に直接的に直列接続することが開示されている。各 O L E D セル又はモジュールは単一のダイオードであり、少なくとも数  $cm^2$  の面積の放出表面を有する。O L E D セル群は直列に接続されており、例えば、1 つの O L E D セルのアノードがその前の O L E D セルのカソードに接続される。有利には、特許文献 6 に記載されている照明及び標識文字の用途では、この解決策により、O L E D 装置はライン電圧の交流電流（定格 120VAC、60Hz）で使用可能になるため、別個の直流電源が不要になる。直列接続された O L E D セルは交流電流の半周期の各々で明るくなるように整えられている。非特許4050

文献1に、照明応用に向けた大面積OLEDセルのこの種の直列接続が開示されており、さらに、直列接続された他のOLED装置への故障の影響に関して議論されている。驚くことではないが、直列にされた短絡OLEDセルダイオードに対応して、同じ直列内の他のOLEDセルの輝度が増大される。しかしながら、上述の単純な直列接続は、より複雑な故障反応機構よりも有利である。

#### 【0016】

従って、故障OLEDのその他の近接OLEDへの影響を抑制又は最小化するために幾つかの解決策が提案されているものの、各OLEDのELダイオード11が個々にアドレス可能な、画像を形成する画素10として機能する画像ディスプレー応用で用いられるパッシブマトリックス型OLEDアレイでの利用に特に適した解決策はない。特許文献3及び4で開示されたアクティブマトリックス型設計は、特許文献5で開示された二重列解法がそうであるように、かなりの複雑性を付加するものである。特許文献6で提案された解決策は、大型照明のバンクとして用いられるモジュール化された個別OLED照明装置に適用されるものであり、個々にアドレス可能な各OLEDのELダイオード11が画像を形成する1画素として機能するOLEDアレイに適用されるものではない。実用的な解決策を考えると、パッシブマトリックス型OLEDアレイ設計の、低成本であることと、図2の概略図で示されるように比較的単純であることを維持することに利点があると認識される。

#### 【0017】

従って、個々にアドレス可能な複数の画素を備えるOLEDアレイ装置に対するニーズ、及び、製造の複雑さを実質的に増すことなく、あるいは複雑な支援回路を必要とすることなく短絡状態への一定の許容度をもたらす方法へのニーズが存在すると考えることができる。

【特許文献1】米国特許第5844368号明細書

【特許文献2】米国特許第6594606号明細書

【特許文献3】米国特許第6392617号明細書

【特許文献4】米国特許第6433485号明細書

【特許文献5】米国特許第6605903号明細書

【特許文献6】米国特許出願公開第2002/0190661号明細書

【非特許文献1】「Fault-tolerant, scalable organic light-emitting device architecture」、Applied Physics Letters Vol.82 No.16、2003年4月21日

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0018】

本発明は、耐故障性が向上されたOLEDアレイを提供することを目的とする。

##### 【課題を解決するための手段】

#### 【0019】

本発明によって提供される複数の列電極、及び複数の行の個々にアドレス可能なOLED画素を有するアレイは、各々の行が一般に共有される共有電極を含み：

a) 各々の行の少なくとも1つのOLED画素が電流制限素子、及び有機エレクトロルミネッセント・ダイオードを有し、且つ前記少なくとも1つのOLED画素が前記共有電極と前記複数の列電極の1つとの間に電流を通電するためにそれらの間に接続されており；且つ

b) 前記有機エレクトロルミネッセント・ダイオードが前記電流制限素子と直列に接続されている。

#### 【0020】

本発明の特徴は、電流制限素子と直列にされたエレクトロルミネッセント・ダイオードを有する画素を設けることである。

#### 【0021】

本発明の利点は、各々の画素又は画素の行に、例えばスイッチングトランジスタ等の能

動素子を必要とするのではなく、エレクトロルミネッセント・ダイオードと直列に受動素子を用いることである。本発明に係る解決策は、ディスプレーにおけるOLEDの暗い線欠陥の可能性を低減したOLEDアレイの製造を低成本で実現するものである。

#### 【0022】

本発明のさらなる利点は、単一画素の短絡によって線が脱落してしまう1つの原因を抑制することによって、OLEDアレイの製造歩留まりを改善することが可能になることがある。

#### 【0023】

本発明のさらなる利点は、短絡した画素によるOLEDアレイ性能への影響を最小化するように短絡画素を分離する製造方法を実現できることである。

10

#### 【0024】

本発明のこれら及び他の目的、特徴、及び利点は、以下の詳細な説明を、本発明の例示的な実施形態が示された図面とともに読むことにより当業者に明らかとなるところである。

#### 【発明を実施するための最良の形態】

#### 【0025】

ここでの記載は、特に、本発明に従った装置に対して、その部分を形成する、あるいはより直接的に協働する素子を対象にしている。特に示されたり記載されたりしていない素子は、当業者に広く知られた様々な形態を取り得る。

20

#### 【0026】

本発明は、OLEDセル画素10内のエレクトロルミネッセンス(EL)ダイオード11と直列に電流制限素子を導入することにより、短絡ダイオードからの保護の問題を解決するものである。以下の実施形態の各々に対して述べられるように、種々の異なる型式の電流制限素子が単独で、或いは組み合わせて用いられ得る。

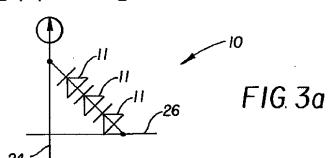

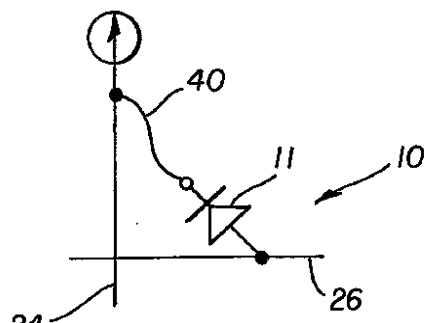

#### 【0027】

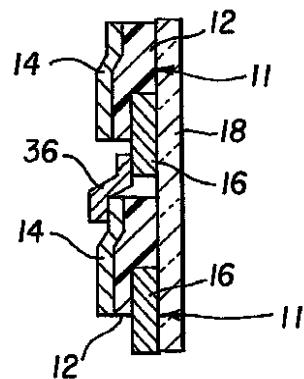

図3aは、単一のOLED画素10の各々の内部に複数のELダイオード11が直列に接続された本発明の第1実施形態を示している。この上面発光構成では、カソードは透明である。この配置で1つのELダイオード11が短絡することは、単に、OLED画素10内で直列接続されたその他のELダイオード11の電流負荷を増大させることになる。ELダイオード11はそれ自体が電流制限素子となり、その場合、OLED画素10内の各ダイオード11は放出光全体の幾らかの部分を提供する。あるいは、直列接続ダイオード群の内の1つ以上は、光を放出せずに単に電流制限素子として機能するダイオードとされること也可能である。

30

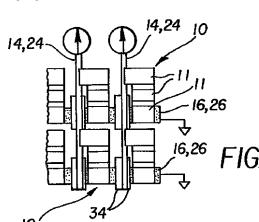

#### 【0028】

図3bは、この第1実施形態のOLED画素10内に置かれた構成要素の平面図を示している。ELダイオード11は好適にドープされたOLED材料から形成され、1つのELダイオード11のカソードが隣のダイオード11のアノードに接続するよう、直列に配置されている。図3cの側面図に示されるように、ジャンパ36がカソード14とアノード16との間のこの接続を形成している。各ELダイオード11の位置に、アノードライン26をカソードライン24から分離するための絶縁体34が設けられている。

40

#### 【0029】

この第1のディスプレーの実施形態には多数の代替配置が認められる。例えば、直列ELダイオード11の数は、ドライバ特性などの要因に基づいて変更され得る。OLED画素10内で直列接続されるELダイオード11の数が多いほど、短絡状態に関する相対的な影響の受けにくさが増大する。しかしながら、同時に、直列接続ELダイオード11数の増加に伴って、画素10を駆動するために必要な電圧も高くなる。

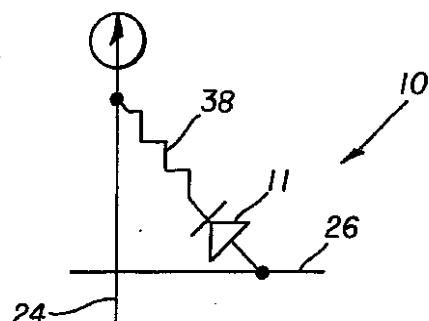

#### 【0030】

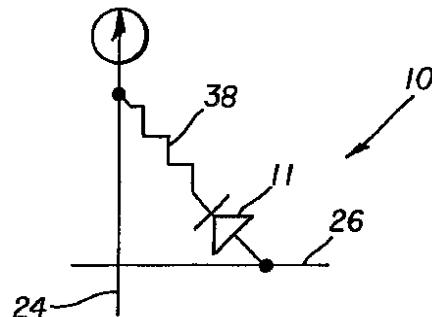

図4aは第2実施形態の概略を示しており、OLED画素10は電流制限のための直列抵抗38を用いている。直列抵抗38の抵抗値は、ELダイオード11が短絡した場合に電流を制限するのに適した値に選定される。図4bは、この第2実施形態のOLED画素10内に置

50

かれた構成要素の平面図を示している。図示の実施形態では、直列抵抗38はELダイオード11のカソードに接続されている。しかしながら、抵抗38をアノードに直列接続しても等しく電流制限保護をもたらす。

#### 【0031】

この第2のディスプレーの実施形態にも同様に、他の実施形態との組み合わせを含め、多数の代替配置が認められる。例えば、直列抵抗38は2つ以上のELダイオード11を含むOLED画素10で用いられてもよい。

#### 【0032】

図5aは第3実施形態の概略を示しており、OLED画素10は電流制限のためのヒューズ40を用いている。ELダイオード11が短絡することで生じた過電流状態によってヒューズ40が飛ばされ、このOLED画素10が効果的に開放される。単一の暗画素が生じるが、他のOLED画素10から成るその他の画素はこの故障の影響を受けない。図5bは、ヒューズ40がELダイオード11のカソードとカソードライン24との間に接続された、この第3のディスプレーの実施形態のOLED画素10内に置かれ得る構成要素の平面図を示している。ヒューズ40はELダイオード11のアノードとアノードライン26との間、又はELダイオード11のカソードとカソードライン24との間の何れに接続されてもよい。図5a及び5bに示される実施形態に代わる変形例には、ヒューズ40と複数のELダイオード11、又は他の電流制限素子との直列結合が含まれる。

10

#### 【0033】

ヒューズ40は多数ある材料及び技術の何れを用いて製造されてもよい。ヒューズを形成するのに有用な材料は、一般に、比較的低い融点を有する合金である。特に、元素Bi、In、Pb、Sn、及びCdから選択された二元、三元、四元及び五元合金が好ましい。限定ではなく例として、ヒューズ40の材料は以下の何れかを含むことができる：

20

- a ) 融点が47 である五元共晶合金 Bi(44.7%)Pb(22.6%)In(19.1%)Sn(8.3%)Cd(5.3%)；

- b ) 融点が70 である四元ウッド合金 (Bi(50.0%)Pb(25.0%)Sn(12.5%)Cd(12.5%))；

- c ) 融点が95 である三元共晶Bi(52.5%)Pb(32.0%)Sn(15.5%)；

- d ) 融点が183 である二元共晶はんだ (Sn(63%)Pb(37%))。

#### 【0034】

これら又は他の元素から成る他の多くの共晶及び非共晶合金が、本発明に従ったヒューズ40を形成するために有用であることが認識される。

30

#### 【0035】

ヒューズ40はOLEDアレイ20の組立中にさらなる利点を有する。何れかの画素10のELダイオード11が短絡された場合、ヒューズ40は回路接続を選択的に開放するのに有利であり、その位置の画素10を効率的に分離し、使用不可能にする。アレイ20に高い逆バイアス電圧を印加すると、大きなレベルの電流が短絡画素10のみで導通される。十分な値の逆バイアス電圧を印加することにより、短絡ELダイオード11を有する画素10のみのヒューズ40が飛ばされることになる。これは高い歩留まりを可能にする。先述の歩留まり方程式（式1）に関し、面積Aは事実上、单一画素10の領域サイズまで大いに低減される。

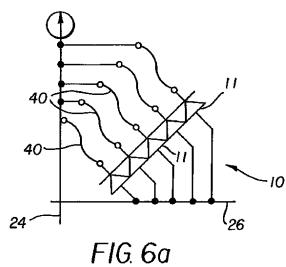

#### 【0036】

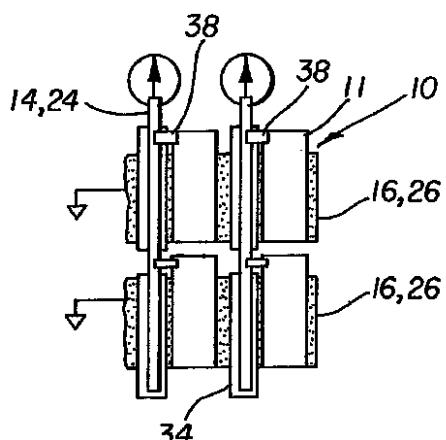

図6aは第4実施形態の概略を示している。この実施形態では、单一のOLED画素10に対して複数のELダイオード11がアノードライン26とカソードライン24との間に電気的に並列に置かれており、各ELダイオード11が別個の直列ヒューズ40を有している。この配置では、单一のELダイオードが短絡すると、それに対応するヒューズ40が飛ばされて回路のこの部分が開放されるが、並列接続された他のELダイオード11を介して電流の継続通電が可能になる。しかしながら、第3のディスプレーの実施形態の配置と異なり、ヒューズ40を組み立てるために別個の部材が用いられる必要はない。代わりに、OLED材料自体の電流通電容量、又はその隣のカソード若しくはアノード支援構造の電流通電容量が事実上、この実施形態での溶断部材をもたらしてもよい。過電流状態はELダイオード11を形成する導電体を溶融又は焼失させ、回路をその位置で開放することになる。

40

#### 【0037】

50

図 6 b は、この第 4 のディスプレーの実施形態の OLED 画素 10 内に置かれる構成要素の平面図を示している。5 個の OLED 画素 10 が示されている。OLED 画素 10 内の並列 EL ダイオード 11 の各々は、カソード 14 部材の薄ストリップ 48 とその下にあるアノード 16 部材との間に位置する発光有機材料によって形成されている。このようにカソード 14 を、EL ダイオード群 11 が形成するカソード 14 とアノード 16 との重なり領域内で空間的に離された、平行な薄ストリップ群 48 にパターン化することにより、複数の EL ダイオード 11 が画素 10 についての並列サブピクセル素子の組として製造されることが可能になる。ダイオード形成領域の外側の電極部材は導電性であり、限られた電流通電容量を有する。特に、図 6 b に表されるようにカソードライン 24 とアノードライン 26 との重なり領域には直接的 10 ない領域であるヒューズ領域 41 の OLED 材料は、過電流に晒されると損傷され、電気的開放状態を形成することが多い。しかしながら、カソード 14 は薄ストリップ群 48 に分割されているので、過電流状態によって、EL ダイオード 11 が短絡された位置の薄ストリップ 48 の長手方向の何処かで溶融が引き起こされることもあり得る。故に、全ての薄ストリップ 48 が溶断機構として機能する。アノード 16 も同様に、ヒューズ動作をもたらすストリップ群の部分を用いて形成されてもよい。熱的な考慮を行うと、ストリップ 48 は、基板と直接接触していない電極上に形成されると最も良く機能する。基板は、ヒューズを開放する原因となる熱に対し望ましくない熱放散をもたらすからである。

#### 【 0 0 3 8 】

図 6 a の実施形態を実施するためにヒューズ 40 の機能を果たす別個の溶断部材を付加することは 1 つの変形例となる。しかしながら、図 6 b の全体的な配置は、別個の型式の溶断部材を OLED アレイ 20 の製造プロセスに導入する必要がないため、製造しやすさの点で有利である。 20

#### 【 0 0 3 9 】

OLED 材料の局所的な過熱、アノード 16 若しくはカソード 14 の分割片の過熱、又は第 3 のディスプレーの実施形態に関連して述べられたようなヒューズ部材の使用、の組み合わせて用いる複合型配置も同様に可能である。また、この第 4 実施形態の配置の変形例は、1 つ以上のヒューズ 40 を対応する直列抵抗 38 で置換することを含む。他の変形例として、1 つ以上の並列回路は、各々の回路内に直列接続された複数の EL ダイオード 11 を備える配置を用いてもよい。 30

#### 【 0 0 4 0 】

エリア照明応用は OLED セルが個々にアドレスされるのではなく同時に動作させられるものであるが、アレイ 20 状の個々にアドレス可能な OLED 画素 10 に提供される耐故障性の解決策はまた、エリア照明に用いられる大型 OLED セルにも適用され得る。特に、図 5 a 及び 6 a の概略図で示される第 3 及び第 4 のディスプレーの実施形態によって提供される解決策は、部屋照明又は他のエリア照明装置に用いられる大面積 OLED においても格別な実用性を有する。背景技術にて述べられたように、照明応用で複数の OLED セルを含む機器を交流ライン電流に直接接続可能にする目的で、大型 OLED セル又はモジュールの直列接続が提案されている。特許文献 6 で述べられているように、これらの装置の直列接続はまた、短絡事象における一定の耐故障性を個々の OLED セルにもたらすものである。 40

#### 【 0 0 4 1 】

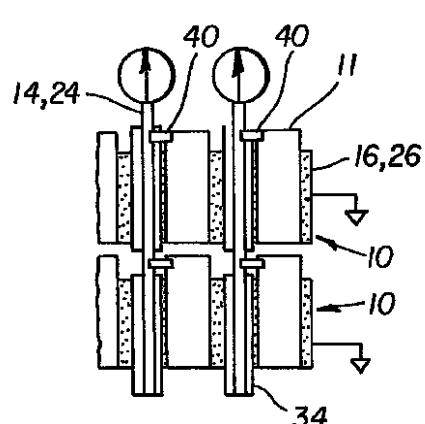

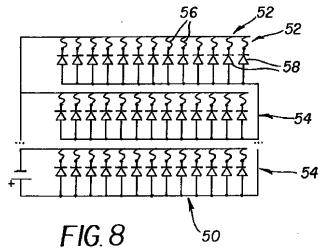

図 7 は、大型 OLED セル 52 のアレイを有するエリア照明装置 50 を示している。各 OLED セル 52 は、単一の大型 OLED ダイオード 58 をヒューズ 56 と直列に接続することによって形成されている。そして、OLED セル 52 のバンク 54 は複数の OLED セル 52 を並列に接続することによって形成されている。バンク 54 は使用可能なエリア照明装置又はモジュールを提供し得るが、より実用的には図 7 に示されるように、OLED セル 52 の連続するバンク 54 が直列に接続される。この耐故障性配置を用いると、OLED セル 52 内の大型 OLED ダイオード 58 の何れかの短絡により、それに対応するヒューズ 56 が飛ばされるが、OLED セル 52 の同一バンク 54 内の隣接 OLED セル 52 が機能することを可能にする。図 7 の配置は、特に直列接続されたバンク 54 を用いるとき、交流電力応用に適している。 50

しかしながら、図7の配置では、OLEDセル52は交流の半周期の間だけ明るくなる。一部のOLEDセル52の向きを逆にすることによって、OLEDセル52の互い違いになったグループが交流電流の各々の半周期に明るくなる。

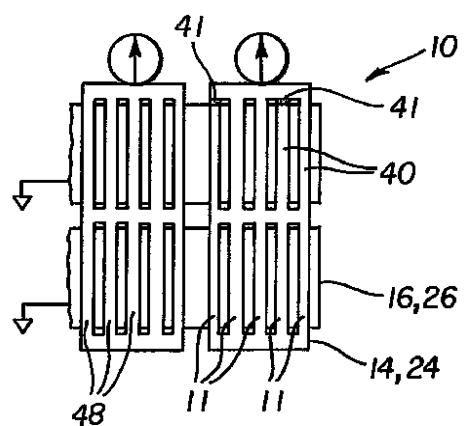

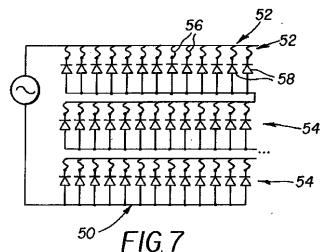

#### 【0042】

図8は、直流電源を用いるエリア照明装置50の実施形態におけるOLEDセル52のバンク54の配置を示している。ここでは、OLEDセル52のバンク54は、図7の実施形態と同様に形成されているが、直流源の両端間に並列に接続されている。この照明配置は、電池電流又は他の直流源を使用する車載応用及びその他の環境に特に適したものである。

#### 【0043】

トランジスタスイッチ及びそれらに必要な支援素子を用いるアクティブマトリックス型OLEDアレイと異なり、図3a、3b、3c、4a、4b、5a、5b、6a及び6bのディスプレーの実施形態での全体的な手法は、例えば追加のELダイオード11、受動抵抗38、又はヒューズ40等の、ELダイオード11と直列に配置された単純な電流制限素子を使用する。

#### 【0044】

図3a、3b、3c、4a、4b、5a、5b、6a及び6bのディスプレーの実施形態を用いると、製造歩留まりはコストに有意な影響を与えることなく改善されることになる。背景技術で述べた数式1に関しては、この方法を用いると、実効面積Aはディスプレー全体の面積Aではなく、画素10の面積まで縮小される。

#### 【0045】

本発明について、特定の好ましい実施形態を具体的に参照しながら詳細に説明した。しかしながら、当業者に理解されるところであるが、本発明の範囲を逸脱することなく様々な変形及び変更が為され得る。例えば、上述の実施形態の様々な電流制限の解決策は、有利な素子配置を実現するように互いに組み合わせられ得る。行及び列の電極、並びにデバイスの極性の指定は、実際にはここで開示された一部の実施形態を実施するに際して逆にされ得る。本発明の意図において、直列接続された電流制限素子は、製造しやすさに応じて、ELダイオード11のアノード端子又はカソード端子の何れにも接続され得る。本発明は上面発光及び底面発光の双方のOLED構造に適用可能である。

#### 【図面の簡単な説明】

#### 【0046】

【図1】従来のOLED画素の基本素子を示す断面側面図である。

【図2a】従来のパッシブマトリックス型OLEDアレイの基本配置を示す概略図である。

【図2b】或る電流源及び行スキャン条件での、短絡を有する従来のパッシブマトリックス型OLEDアレイの一部分を示す概略図である。

【図2c】或る電流源及び行スキャン条件での、短絡を有する従来のパッシブマトリックス型OLEDアレイの一部分を示す概略図である。

【図2d】或る電流源及び行スキャン条件での、短絡を有する従来のパッシブマトリックス型OLEDアレイの一部分を示す概略図である。

【図2e】或る電流源及び行スキャン条件での、短絡を有する従来のパッシブマトリックス型OLEDアレイの一部分を示す概略図である。

【図3a】本発明の第1実施形態に係るOLED画素配置を示す概略図である。

【図3b】図3aに示される第1実施形態におけるOLEDの構成要素を示す平面図である。

【図3c】第1実施形態におけるOLED画素の構成要素を示す断面側面図である。

【図4a】本発明の第2実施形態に係るOLED画素配置を示す概略図である。

【図4b】図4aに示される第2実施形態におけるOLEDの構成要素を示す平面図である。

【図5a】本発明の第3実施形態に係るOLED画素配置を示す概略図である。

【図5b】図5aに示される第3実施形態におけるOLEDの構成要素を示す平面図であ

10

20

30

40

50

る。

【図 6 a】本発明の第 4 実施形態に係る O L E D 画素配置を示す概略図である。

【図 6 b】図 6 a に示される第 4 実施形態における O L E D の構成要素を示す平面図である。

【図 7】本発明に係る技術を用いたエリア照明装置の実施形態における O L E D セルの配置を示す概略図である。

【図 8】本発明に係る技術を用いた、直流電源を用いるエリア照明装置の実施形態における O L E D セルの代替配置を示す概略図である。

【符号の説明】

【 0 0 4 7 】

|                                          |    |

|------------------------------------------|----|

| 10... O L E D 画素                         | 10 |

| 10a、 10b、 10c、 10d... 画素                 |    |

| 11... エレクトロルミネッセント・ダイオード                 |    |

| 11a、 11b、 11c、 11d... エレクトロルミネッセント・ダイオード |    |

| 12... 有機層                                |    |

| 14... カソード                               |    |

| 16... アノード                               |    |

| 18... 基板                                 |    |

| 20... パッシブマトリックス型 O L E D アレイ            |    |

| 22... 電流源                                | 20 |

| 24... カソードライン                            |    |

| 26... アノードライン                            |    |

| 28、 30... スイッチ                           |    |

| 34... 絶縁体                                |    |

| 36... ジャンパ                               |    |

| 38... 抵抗                                 |    |

| 40... ヒューズ                               |    |

| 41... ヒューズ領域                             |    |

| 42a、 42b... 列                            |    |

| 44a、 44b... 行                            | 30 |

| 46... 短絡                                 |    |

| 48... ストリップ                              |    |

| 50... エリア照明装置                            |    |

| 52... O L E D セル                         |    |

| 54... バンク                                |    |

| 56... ヒューズ                               |    |

| 58... 大型 O L E D ダイオード                   |    |

【図1】

図1

(従来技術)

【図2 a】

図2a

(従来技術)

【図2 b】

図2b

(従来技術)

【図2 c】

図2c

(従来技術)

【図2 d】

図2d

(従来技術)

【図3 a】

FIG. 3a

【図3 b】

FIG. 3b

【図2 e】

図2e

(従来技術)

【図 3 c】

FIG. 3c

【図 4 a】

FIG. 4a

【図 4 b】

FIG. 4b

【図 5 a】

FIG. 5a

【図 5 b】

FIG. 5b

【図 6 a】

FIG. 6a

【図 6 b】

FIG. 6b

【図 8】

FIG. 8

【図 7】

FIG. 7

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US2005/001990

A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 G09G3/32

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 G09G H01L

Documentation searched other than minimum documentation to the extent that such documents are included In the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                              | Relevant to claim No. |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X        | WO 03/060865 A (KONINKLIJKE PHILIPS ELECTRONICS N.V; SEMPEL, ADRIANUS; GIRALDO, ANDREA) 24 July 2003 (2003-07-24)<br>page 1, lines 11-15; figure 2<br>page 2, lines 4-22                        | 1-3                   |

| Y        | US 5 828 181 A (OKUDA ET AL)<br>27 October 1998 (1998-10-27)<br>abstract; figures 1,5<br>column 1, lines 15-23<br>column 3, line 58 - column 4, line 13<br>column 5, line 7 - column 6, line 25 | 6,7                   |

| X        | US 5 828 181 A (OKUDA ET AL)<br>27 October 1998 (1998-10-27)<br>abstract; figures 1,5<br>column 1, lines 15-23<br>column 3, line 58 - column 4, line 13<br>column 5, line 7 - column 6, line 25 | 1,2                   |

| Y        | WO 03/012869 A (THOMSON LICENSING S.A;<br>DAGOIS, JEAN-PAUL; HAAS, GUNTHER)<br>13 February 2003 (2003-02-13)<br>abstract<br>page 13, lines 4-19; figure 14                                      | 6,7                   |

|          |                                                                                                                                                                                                 | -/-                   |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents :

- "A" document defining the general state of the art which is not considered to be of particular relevance

- "E" earlier document but published on or after the international filing date

- "L" document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- "O" document referring to an oral disclosure, use, exhibition or other means

- "P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art

"&" document member of the same patent family

Date of the actual completion of the international search

13 May 2005

Date of mailing of the International search report

10.11.2005

Name and mailing address of the ISA

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040, Tx. 31 851 epo nl,

Fax: (+31-70) 340-3018

Authorized officer

Fulcheri, A

**INTERNATIONAL SEARCH REPORT**

|                                                   |

|---------------------------------------------------|

| International Application No<br>PCT/US2005/001990 |

|---------------------------------------------------|

| C(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                        |                       |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category *                                          | Citation of document, with indication, where appropriate, of the relevant passages                                                                     | Relevant to claim No. |

| X                                                   | US 2003/010985 A1 (SHEN ZILAN)<br>16 January 2003 (2003-01-16)<br>abstract; figures 1-4<br>paragraphs [0001] - [0007], [0015] -<br>[0022]<br>-----     | 1,4                   |

| Y                                                   | DE 29 42 777 A1 (SIEMENS AG; SIEMENS AG,<br>1000 BERLIN UMD 8000 MUENCHEN, DE)<br>7 May 1981 (1981-05-07)<br>page 5, lines 21-29; figures 1,4<br>----- | 6,7                   |

| Y                                                   | US 2003/107537 A1 (OCHI HIDEO ET AL)<br>12 June 2003 (2003-06-12)<br>paragraphs [0004], [0005], [0022];<br>figures 1,7<br>-----                        | 6,7                   |

**INTERNATIONAL SEARCH REPORT**

International application No.

PCT/US2005/001990

**Box II Observations where certain claims were found unsearchable (Continuation of item 2 of first sheet)**

This International Search Report has not been established in respect of certain claims under Article 17(2)(a) for the following reasons:

1.  Claims Nos.: because they relate to subject matter not required to be searched by this Authority, namely:

2.  Claims Nos.: because they relate to parts of the International Application that do not comply with the prescribed requirements to such an extent that no meaningful International Search can be carried out, specifically:

3.  Claims Nos.: because they are dependent claims and are not drafted in accordance with the second and third sentences of Rule 6.4(a).

**Box III Observations where unity of invention is lacking (Continuation of item 3 of first sheet)**

This International Searching Authority found multiple Inventions in this international application, as follows:

**see additional sheet**

1.  As all required additional search fees were timely paid by the applicant, this International Search Report covers all searchable claims.

2.  As all searchable claims could be searched without effort justifying an additional fee, this Authority did not invite payment of any additional fee.

3.  As only some of the required additional search fees were timely paid by the applicant, this International Search Report covers only those claims for which fees were paid, specifically claims Nos.:

4.  No required additional search fees were timely paid by the applicant. Consequently, this International Search Report is restricted to the invention first mentioned in the claims; it is covered by claims Nos.:

1-9

**Remark on Protest**

- The additional search fees were accompanied by the applicant's protest.

No protest accompanied the payment of additional search fees.

International Application No. PCT/US2005/001990

FURTHER INFORMATION CONTINUED FROM PCT/ISA/ 210

This International Searching Authority found multiple (groups of) inventions in this international application, as follows:

1. claims: 1-9

The first concept relates to an OLED display device having a current limiting component connected in series with the light emitting element.

---

2. claims: 10-12

The second concept relates to an area lighting apparatus comprising an array of OLED cells arranged in banks, said banks comprising a plurality of OLED cells connected in parallel and the banks being connected to each other in series or in parallel

---

3. claim: 13

The third concepts relates to a method of repairing an array of OLED pixels by applying a reverse voltage between a row electrode and a column electrode, so as to blow a fuse which is connected in series with a shorted diode

---

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/US2005/001990

| Patent document cited in search report |    | Publication date |                   | Patent family member(s)                                                            | Publication date                                                                 |

|----------------------------------------|----|------------------|-------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| WO 03060865                            | A  | 24-07-2003       | AU CN JP TW US    | 2003201064 A1<br>1615505 A<br>2005515503 T<br>584299 Y<br>2005093848 A1            | 30-07-2003<br>11-05-2005<br>26-05-2005<br>11-04-2004<br>05-05-2005               |

| US 5828181                             | A  | 27-10-1998       | JP                | 8330070 A                                                                          | 13-12-1996                                                                       |

| WO 03012869                            | A  | 13-02-2003       | CN EP FR JP TW US | 1533614 A<br>1419541 A2<br>2827991 A1<br>2004537832 T<br>558698 B<br>2004233138 A1 | 29-09-2004<br>19-05-2004<br>31-01-2003<br>16-12-2004<br>21-10-2003<br>25-11-2004 |

| US 2003010985                          | A1 | 16-01-2003       | US                | 2004262711 A1                                                                      | 30-12-2004                                                                       |

| DE 2942777                             | A1 | 07-05-1981       | NONE              |                                                                                    |                                                                                  |

| US 2003107537                          | A1 | 12-06-2003       | JP                | 2003077663 A                                                                       | 14-03-2003                                                                       |

---

フロントページの続き

(51)Int.Cl.

F I

テーマコード(参考)

H 05 B 33/10

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,L,U,LV,MA,MD,MG,MK,MN,MW,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW

(72)発明者 アゴスティネリ,ジョン アルフォンセ

アメリカ合衆国 ニューヨーク州 14612 ロチェスター ベットウッド・レーン 60

(72)発明者 コワーツ,マレック ウロジミエーツ

アメリカ合衆国 ニューヨーク州 14467 ヘンリエッタ ポートフィーノ・サークル 3

(72)発明者 クロスデール,フィツロイ ヒュー

アメリカ合衆国 ニューヨーク州 14624 ロチェスター ロイヤリスト・アヴェニュー 3

4

F ターム(参考) 3K107 AA01 BB02 CC21 CC45 EE02 EE09 GG57 HH00 HH03

5C080 AA06 BB05 DD19 FF12 JJ02 JJ03 JJ06