(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6620112号

(P6620112)

(45) 発行日 令和1年12月11日(2019.12.11)

(24) 登録日 令和1年11月22日(2019.11.22)

(51) Int.Cl.

H01L 21/768 (2006.01)

H01L 23/532 (2006.01)

F 1

H01L 21/90

N

請求項の数 11 (全 17 頁)

|                    |                               |

|--------------------|-------------------------------|

| (21) 出願番号          | 特願2016-559150 (P2016-559150)  |

| (86) (22) 出願日      | 平成26年12月3日 (2014.12.3)        |

| (65) 公表番号          | 特表2017-501591 (P2017-501591A) |

| (43) 公表日           | 平成29年1月12日 (2017.1.12)        |

| (86) 國際出願番号        | PCT/US2014/068344             |

| (87) 國際公開番号        | W02015/094667                 |

| (87) 國際公開日         | 平成27年6月25日 (2015.6.25)        |

| 審査請求日              | 平成29年12月1日 (2017.12.1)        |

| (31) 優先権主張番号       | 61/916,726                    |

| (32) 優先日           | 平成25年12月16日 (2013.12.16)      |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

| (31) 優先権主張番号       | 14/523,523                    |

| (32) 優先日           | 平成26年10月24日 (2014.10.24)      |

| (33) 優先権主張国・地域又は機関 | 米国(US)                        |

|           |                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 390040660<br>アプライド マテリアルズ インコーポレイテッド<br>APPPLIED MATERIALS, INCORPORATED<br>アメリカ合衆国 カリフォルニア 95054, サンタクララ, バウアーズ<br>アヴェニュー 3050 |

| (74) 代理人  | 110002077<br>園田・小林特許業務法人                                                                                                        |

| (72) 発明者  | ナイク, メフル ピー.<br>アメリカ合衆国 カリフォルニア 95148, サンノゼ, バリーウッド コート 3088                                                                    |

最終頁に続く

(54) 【発明の名称】処理システムを使用した空隙構造の組込

## (57) 【特許請求の範囲】

## 【請求項1】

一体型層スタック内に空隙構造を形成する方法であって、

真空下の処理システムにおいて前記一体型層スタック上に配置されたモールド層をドライエッチング処理するステップであって、前記モールド層は一ないし複数の銅配線の間に配置され、前記モールド層のドライエッチング処理は前記一ないし複数の銅配線の少なくとも一部を露出させる、ステップと、

前記ドライエッチング処理によって露出された前記一ないし複数の銅配線の露出部分の上にコンフォーマルなライナー層を堆積するステップであって、前記ドライエッチング処理と前記コンフォーマルなライナー層の堆積とが前記処理システムにおいて真空を遮断せずに実行される、ステップと、

前記処理システムにおいて真空を遮断せずに、真空下で前記一ないし複数の銅配線の上に、犠牲膜層及び一ないし複数の流動性低誘電率材料層を含む層スタックを堆積するステップと、

前記層スタックを硬化し、前記犠牲膜層を取り除いて空隙構造を形成するステップと、を含む、方法。

## 【請求項2】

前記モールド層は、シリコンベース酸化物又は低誘電率材料である、請求項1に記載の方法。

## 【請求項3】

10

20

前記コンフォーマルなライナー層は、炭化物及び窒化物からなるグループから選択される誘電体材料を含む、請求項1に記載の方法。

**【請求項4】**

前記一ないし複数の流動性低誘電率材料層は、炭素がドープされた酸化物、フッ素化炭素、ナノクラスターリングシリカ、又はメソポーラス酸化物を含む、請求項1に記載の方法。

**【請求項5】**

前記犠牲膜層は、炭素又は高分子炭素・水素材料を含む、請求項1に記載の方法。

**【請求項6】**

一体型層スタック内に空隙構造を形成する方法であって、

10

真空下の処理システムにおいて第1処理チャンバの前記一体型層スタック上に配置された酸化物モールド層をドライエッチング処理するステップであって、前記酸化物モールド層は一ないし複数の銅配線の間に配置され、前記酸化物モールド層の前記ドライエッチング処理は一ないし複数の前記銅配線の少なくとも一部を露出させる、ステップと、

真空下で前記処理システム内の第2処理チャンバの前記一ないし複数の銅配線の露出部分の上に約2ナノメートル未満の厚みを有する低誘電率材料ライナー層をコンフォーマルに堆積することによって、前記一ないし複数の銅配線に堆積されたコンフォーマルな低誘電率材料ライナー層を形成するステップであって、前記ドライエッチング処理と前記低誘電率材料ライナー層の堆積とが前記処理システムにおいて真空を遮断せずに実行される、ステップと、

20

前記処理システムにおいて真空を遮断することなく、真空下で前記一ないし複数の銅配線の上に、犠牲膜層及び一ないし複数の流動性低誘電率材料層を含む層スタックを堆積するステップと、

前記層スタックを硬化し、前記犠牲膜層を取り除いて空隙構造を形成するステップと、を含む、方法。

**【請求項7】**

前記低誘電率材料ライナー層は炭窒化ケイ素(SiCN)を含み、前記犠牲膜層は炭素を含む、請求項6に記載の方法。

**【請求項8】**

前記銅配線の上部を露出するため、前記一ないし複数の流動性低誘電率材料層の一部及び前記低誘電率材料ライナー層を研磨するステップを更に含む、請求項6に記載の方法。

30

**【請求項9】**

前記ドライエッチングは、約2mTorr～約20mTorrの圧力で、NF<sub>3</sub>、NH<sub>3</sub>又はC<sub>x</sub>F<sub>y</sub>ガスを使用する、請求項6に記載の方法。

**【請求項10】**

処理システム内で基板上に誘電体構造を形成する方法であって、

真空下で第1処理チャンバの前記基板上にモールド層をドライエッチング処理するステップであって、前記モールド層は一ないし複数の銅配線の間に配置され、前記モールド層の前記ドライエッチング処理は前記一ないし複数の銅配線の少なくとも一部を露出させるステップと、

40

真空下で前記第1処理チャンバから、一ないし複数の第2処理チャンバまで前記基板を移送するステップと、

真空下で前記一ないし複数の第2処理チャンバの前記基板上の前記一ないし複数の銅配線の露出部分の上にコンフォーマルにライナー層を堆積することによって、前記一ないし複数の銅配線に堆積されたコンフォーマルなライナー層を形成するステップと、

真空下で前記一ないし複数の第2処理チャンバの前記基板上に形成される前記ライナー層の上に一ないし複数の誘電体層及び犠牲層を堆積するステップと、

前記一ないし複数の誘電体層及び前記犠牲層を硬化し、前記犠牲層を取り除いて空隙構造を形成するステップと、

を含む方法。

50

**【請求項 11】**

ライナー層の堆積と一ないし複数の誘電体層の堆積は、別々の第2処理チャンバにおいて実行される、請求項10に記載の方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

[0001] 本開示の実施形態は概して、一体型処理システムを使用した空隙構造を有する誘電体層構造の形成に関する。 10

**【背景技術】****【0002】**

[0002] 今日、集積回路は、單一チップ上に数百万個もの構成要素（例えば、トランジスタ、コンデンサ及び抵抗）が搭載される複雑なデバイスへと進化を遂げている。回路の高密度化に伴い、集積回路構成要素の寸法を小さくすること、例えばサブミクロンまで寸法を低減することが求められるほか、高速で電気性能の優れたデバイスの実現に向けて、デバイス製造の原材料として、たとえば、金属ラインの形成には高導電率の材料、絶縁層には低誘電率（低k）の材料など、様々な材料を使用することが必要となってくる。集積回路製造の場合、銅及びアルミニウムの配線などの低抵抗の金属配線は、集積回路素子上で集積回路構成要素間の導電性経路となる。一般的に、金属配線は誘電体バルク絶縁材料によって互いに電気絶縁される。サブミクロンの寸法では、隣接する金属配線間で容量性結合が起こる場合があり、これがクロストークや抵抗・容量（RC）遅延の要因となって集積回路全体の性能が低下する可能性がある。 20

**【0003】**

[0003] 集積回路構成要素に対して垂直及び水平の配線を形成する方法として、ダマシン法、デュアルダマシン法がある。典型的に、ダマシン構造は、上下に積み上げられた低誘電率材料と導電性銅層などのように、誘電体バルク絶縁層と導電性金属層を有する。垂直な配線（すなわちビア）と水平な配線（すなわちトレーニング）は、誘電体バルク絶縁層内にエッチングされる。その後、導電性金属層がビア及び／又はトレーニングに満たされ、導電性金属材料だけがビア及び／又はトレーニング内に残るように、化学的機械平坦化プロセス（CMP）などによって平坦化される。ダマシンアプローチでは、一連のハードマスク、低誘電率誘電体、エッチング停止層、空隙などを含む、かなり複雑な誘電体膜スタックが求められる。このようなスタックを得るには、ビアとトレーニングを導電性金属材料で満たす前に、一般に、ビア／トレーニングリソグラフィ、パターニング、及び湿式洗浄プロセスが必要である。 30

**【0004】**

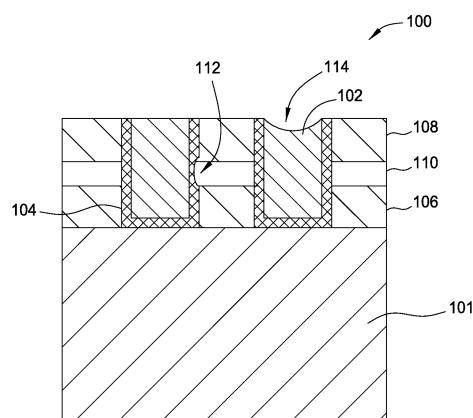

[0004] 図1は、従来の酸化物又は低誘電率材料のモールド湿式エッチング除去技術によって製造された一体型層スタック100を示したもので、この技術により、半導体基板101の表面上に配線構造の少なくとも一部が形成されている。一体型層スタック100は、基板101の上に配置された低誘電率誘電体材料の上に堆積されたプランケットモールド膜（図示せず）によって製造される。モールド膜は、そこにトレーニングを形成するため、モールド膜層の一部を選択的に取り除くようにパターニングされる。バリア層104はパターニングされた低誘電率誘電体材料106の上に堆積され、導電性材料102はバリア層104の上のトレーニング内に堆積される。バリア層104は、導電性材料102と隣接する流動性低誘電率誘電体材料106との間の拡散を防止するように構成される。次に、化学的機械平坦化プロセスは、導電性材料102の上面を露出するため、モールド酸化物とバリア層104を研磨しなおすように実行される。湿式エッチング技術では残存モールド膜を取り除いて、図1に示す一体型層スタック100を形成する。その結果、空隙構造110が、第1の流動性低誘電率材料106と第2の流動性低誘電率材料108との間に形成される。 40

**【0005】**

10

20

30

40

50

[ 0 0 0 5 ] しかしながら、従来の湿式エッティング技術は、フッ化水素酸( H F )又は希釈 H F など、モールド層( 図示せず )の除去に使用されるエッチャントが、領域 1 1 2 に示したようにバリア層 1 0 4 を損傷しうるため問題がある。しかも、湿式エッティングは、領域 1 1 4 に示したように、導電性材料 1 0 2 を過剰にエッティングし、或いは侵すことがあり、この例では導電性材料 1 0 2 はくぼんでいる。

#### 【 0 0 0 6 】

[ 0 0 0 6 ] 加えて、モールド湿式エッティングステップと、空隙形成などのその後の処理との間の周囲条件で長い待ち時間があるため、バリア層 1 0 4 及び導電性材料 1 0 2 が酸化することがある。したがって、導電性材料 1 0 2 及びバリア層 1 0 4 をエッティングすることや物理的に損傷することなく、形成処理中に導電性材料 1 0 2 及びバリア層 1 0 4 の酸化を更に防止するように、配線形成処理を改善する必要がある。

10

#### 【発明の概要】

#### 【 0 0 0 7 】

[ 0 0 0 7 ] 一実施形態では、一体型層スタックに空隙構造を形成する方法は、真空下の処理システム内の一体型層スタック上に配置されたモールド層をドライエッティングするステップを含む。モールド層は一ないし複数の配線の間に配置され、モールド層のドライエッティング処理は、一ないし複数の配線の少なくとも一部を露出させる。本方法は更に、一ないし複数の配線の露出部分の上にライナー層を堆積するステップを含む。本書で開示の方法は一般的に、処理システムにおいて真空を遮断せずに実行される。

#### 【 0 0 0 8 】

[ 0 0 0 8 ] 別の実施形態では、一体型層スタックに空隙構造を形成する方法は、真空下の処理システム内の第 1 処理チャンバの一体型層スタック上に配置されたモールド層をドライエッティングするステップを含む。モールド層は一ないし複数の銅配線の間に配置され、モールド層のドライエッティング処理は、一ないし複数の配線の少なくとも一部を露出させる。本方法は更に、真空下の処理システム内の第 2 処理チャンバの一ないし複数の配線の露出部分の上に、約 2 ナノメートル未満の厚みを有する低誘電率材料ライナー層を堆積するステップを含む。本方法は、処理システムにおいて真空を遮断せずに実行される。

20

#### 【 0 0 0 9 】

[ 0 0 0 9 ] 更に別の実施形態では、処理システム内の基板上に誘電体構造を形成するための方法は、真空下で第 1 処理チャンバの基板上にモールド層をドライエッティングするステップを含む。モールド層は一ないし複数の銅配線の間に配置され、モールド層のドライエッティング処理は、一ないし複数の配線の少なくとも一部を露出させる。本方法は更に、真空下で基板を第 1 処理チャンバから第 2 処理チャンバまで移送するステップを含む。本方法は更に、真空下で第 2 処理チャンバの基板上のーないし複数の配線の露出部分の上にライナー層を堆積するステップを含む。本方法はまた、真空下で第 2 処理チャンバの基板上に形成されたライナー層の上に、ーないし複数の誘電体層及び犠牲層を堆積するステップを含む。

30

#### 【 0 0 1 0 】

[ 0 0 1 0 ] かくして、本開示の特徴が詳細にわたり理解されるように、上記で要約した本開示について、以下、実施形態の詳細な説明をする。その際に参照する実施形態一部は添付図面に示される。もとより、本開示は他の等しく有効な実施形態も包含しうることから、添付図面は本開示の典型的な実施形態を例示しているのにすぎず、本発明の範囲を限定するものではないことは勿論である。

40

#### 【図面の簡単な説明】

#### 【 0 0 1 1 】

【図 1】一体型層スタックの概略断面図である。

【図 2】処理チャンバの概略断面図である。

【図 3】処理チャンバの概略断面図である。

【図 4】空隙構造を含む配線構造を形成するための方法のフロー図である。

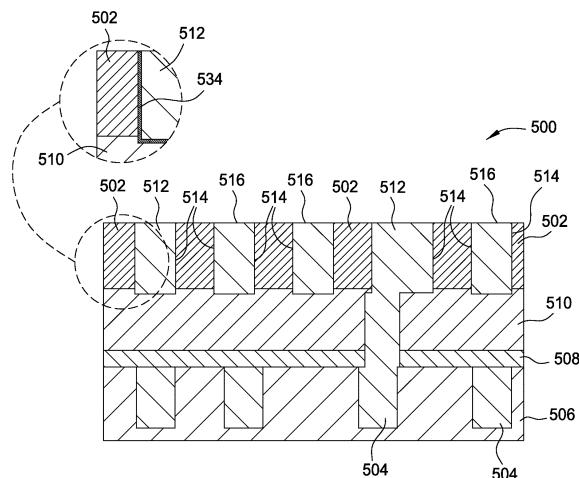

【図 5 A】配線構造形成処理の異なるフェーズでの概略断面図である。

50

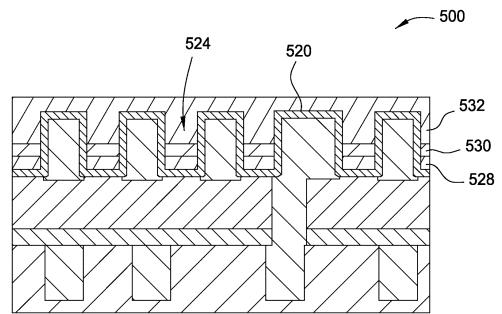

- 【図 5 B】配線構造形成処理の異なるフェーズでの概略断面図である。

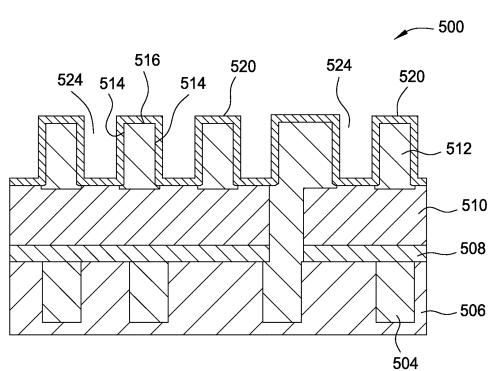

- 【図 5 C】配線構造形成処理の異なるフェーズでの概略断面図である。

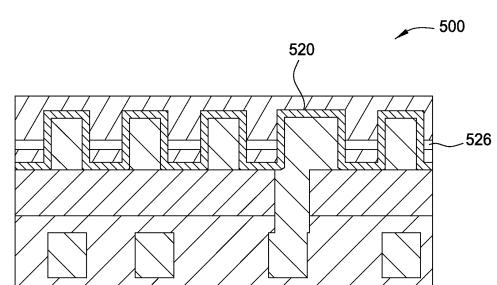

- 【図 5 D】配線構造形成処理の異なるフェーズでの概略断面図である。

- 【図 6 A】配線構造形成処理の異なるフェーズでの概略断面図である。

- 【図 6 B】配線構造形成処理の異なるフェーズでの概略断面図である。

- 【図 7】一体型層スタックの概略断面図である。

- 【図 8】処理システムの平面図である。

#### 【0012】

理解を容易にするため、可能な限り、図面に共通する同一の要素を示すのに同一の参照番号を使用した。一実施形態の要素および特徴は、特記しない限り、他の実施形態にも有益に組み込むことができる。10

#### 【発明を実施するための形態】

##### 【0013】

【0018】以下の説明では、便宜上、本開示の実施形態の完全な理解を促すために、詳細にわたって記載されている。ただし、場合によっては、本開示の実施形態が不明確にならぬようするため、周知の構造や装置については詳細には立ち入らずに、ブロック図の形態で示してある。これらの実施形態は、当業者が本開示の実施形態を実施することができるよう詳細に説明されているが、他の実施形態も使用することができる、また、本開示の範囲を逸脱することなく、論理的、機械的、電気的、その他の変更を行いうることは明らかである。20

##### 【0014】

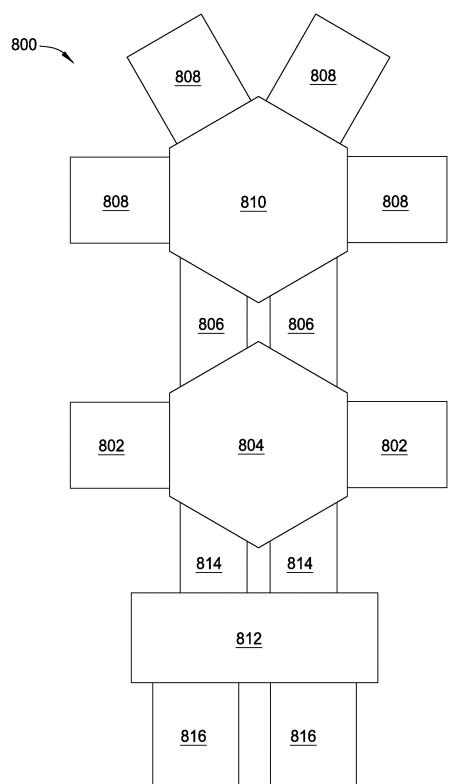

【0019】本明細書に記載の実施形態は概して、処理システムを使用する空隙構造の組込方法に関する。具体的には、本開示の実施形態は、改善された空隙構造形成処理に対して処理システム内で一体化されるモールド層エッティング処理及びライナー堆積処理に関する。本開示の実施形態は概して、一ないし複数の処理チャンバ200、300を有する処理システム800を使用する空隙構造を含む、誘電体含有層構造の形成に関する。処理システムは好都合なことに、処理システム800内で「真空を破る」ことなく誘電体含有層構造を形成し、その結果、誘電体含有層構造内の物質は形成処理中に酸化又は損傷されることはないと想定される。処理システム800及び処理チャンバ200、300の詳細は、以下で更に説明される。30

##### 【0015】

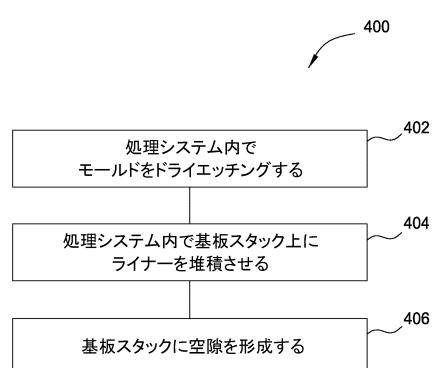

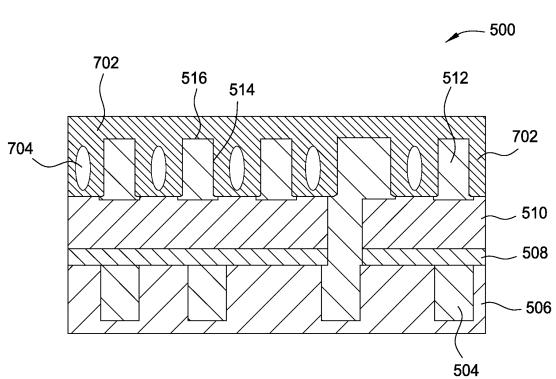

【0020】図4は、本開示の一実施形態による空隙構造形成の方法400のフロー図を示している。図5A～図5Dは、本開示の一実施形態による一体型層スタック500の概略的な断面図である。

##### 【0016】

【0021】図4及び図5A～図5Dを参照するに、本方法400は、ブロック402で、一体型層スタック500からモールド層502をドライエッティングすること又は除去することによって開始される。図5Aに示すように、一体型層スタック500は、第1低誘電率誘電体材料506に配置された導電性材料504を含むダマシン構造である。一実施形態では、導電性材料504は銅などの金属であり、第1低誘電率誘電体材料506は、炭素がドープされた酸化物又はその変形物、例えば、フッ素化炭素、ナノクラスタリングシリカ(NCS)、メソポーラス酸化物、又は有機「スピンドル」材料、カリフォルニア州サンタクララのアプライドマテリアルズ社から入手可能なBD1、BDII及びBD3などのBLACK DIAMOND(登録商標)膜層を含みうる。他の好適な低誘電率誘電体材料、例えば、約1.5～約5の誘電率を有する材料も、本明細書に記載の実施形態により使用されうることが企図されている。40

##### 【0017】

【0022】第1低誘電率誘電体材料506は、スピンドル技術、プラズマ化学気相堆積(PECVD)、高密度プラズマCVD、ハイブリッド物理CVD(HPCVD)、中性ビーム化学気相堆積(NBECVD)、マイクロ波支援化学気相堆積(CVD)、又は

10

20

30

40

50

他の任意の好適な低誘電率誘電体材料堆積技術によって堆積されうる。第1バリア層508は、導電性材料504の拡散を防止するため、第1低誘電率誘電体材料506の上に配置される。第1バリア層508は、窒化ケイ素、炭窒化ケイ素(SiCN)、又はSiOCNを含みうる。一実施形態では、バリア層508は、エッチング停止物質、例えば、窒化アルミニウム(AlN)、及び窒化ケイ素、炭窒化ケイ素(SiCN)又はSiOCNの組み合わせを含みうる。更に別の実施形態では、バリア層508は、選択的な金属キャップ、例えば、窒化ケイ素、炭窒化ケイ素(SiCN)又はSiOCNを含有するコバルト(Co)含みうる。

#### 【0018】

【0023】 第2低誘電率誘電体材料510は、バリア層508の上に配置される。一実施形態では、第2低誘電率誘電体材料510は、第1低誘電率誘電体材料510に対して既に列挙した任意の材料又は材料の組み合わせを含みうる。加えて、第2低誘電率誘電体材料510は、第1低誘電率誘電体材料510に対して既に列挙した任意の技術によって堆積されうる。導電性材料504は、第2低誘電率誘電体材料510の上に配置される一ないし複数の配線512を形成する。一実施形態では、第2バリア層534は、配線512と隣接する第2低誘電率誘電体材料510及びモールド層502との間に配置される。図5Aに示した第2バリア層534は、第1バリア層508又はバリア材料と同じ材料を含みうる。タンタル又は窒化タンタルなど、或いは他の任意の好適な材料、例えば、マンガン(Mn)、窒化マンガン(MnN)、タングステン(W)、又はこれらの組み合わせから形成される任意の材料は、銅に対するバリアとなりうる。一実施形態では、配線512は側壁514及び上面壁516を含む。10

#### 【0019】

【0024】 図5Bに示したように、配線512(図5A)の間に配置された、パターン形成されたモールド層502は、選択的にエッチングされ、第1低誘電率誘電体材料506内に開放トレンチ524を形成する。一実施形態では、モールド層502は、二酸化ケイ素(SiO<sub>2</sub>) (オルトケイ酸テトラエチル(TEOS)前駆体から形成される)、シラン(SiH<sub>4</sub>)、又は、例えば有機前駆体から形成される他の任意のケイ素系酸化物などの犠牲酸化物である。別の実施形態では、モールド層は、炭素、カリフォルニア州サンタクララのアプライドマテリアルズ社から入手可能なBD1、BDII及びBD3などのBLACK DIAMOND(登録商標)膜層など、超低誘電率材料である。他の好適な低誘電率誘電体材料、例えば、約1.5～約3の誘電率を有する材料も、本明細書に記載の実施形態により使用されうることが企図されている。20

#### 【0020】

【0025】 一実施例では、ドライエッチング処理は、約2mTorrから約20mTorrの処理圧力、摂氏約10度から約80度の温度、及び約0.2kWから約2.0kWの出力を有する13.56MHzのRF電力で、NF<sub>3</sub>、NH<sub>3</sub>又はC<sub>x</sub>F<sub>y</sub>ガスを使用して、モールド層502を取り除くために実行される。従来の湿式エッチングと比較して、モールド層502のドライエッチングは等方的にエッチングするのではないため、隣接する構造を損傷する。すなわち、導電性材料504を過剰にエッチングする、或いは侵すため、第2バリア層534を損傷する。したがって、形成された隣接する膜への導電性材料504の拡散は低減又は防止され、一体型層スタック500の電気特性及び完全性は維持される。図5A～図5Dには単層ビアが示されているが、一実施形態では、その後の次の層ビアに隣接する空隙形成を防止するため、モールド層502をドライエッチングする前にエクスクルージョンマスクが使用される。30

#### 【0021】

【0026】 本明細書では特定の一体型層スタック構造が説明されているが、ブロック402で、その後の空隙構造形成に適した任意の一体型層スタック上でモールド層502のドライエッチングが実行されうることが企図されている。当業者であれば、ブロック402で使用されるエッチング化学物質が、モールド層502の組成及び厚みに基づいて選択され、調整されることが理解されよう。一般的に、モールド層502のエッチングに使40

用されるドライエッチング処理は、配線 512 の形成に使用される材料のエッチング又は酸化を実質的に低減又は防止し、配線 512 の完全性及び構造を維持するのに役立つよう に、選択される。

#### 【0022】

##### ドライエッチング処理チャンバの例

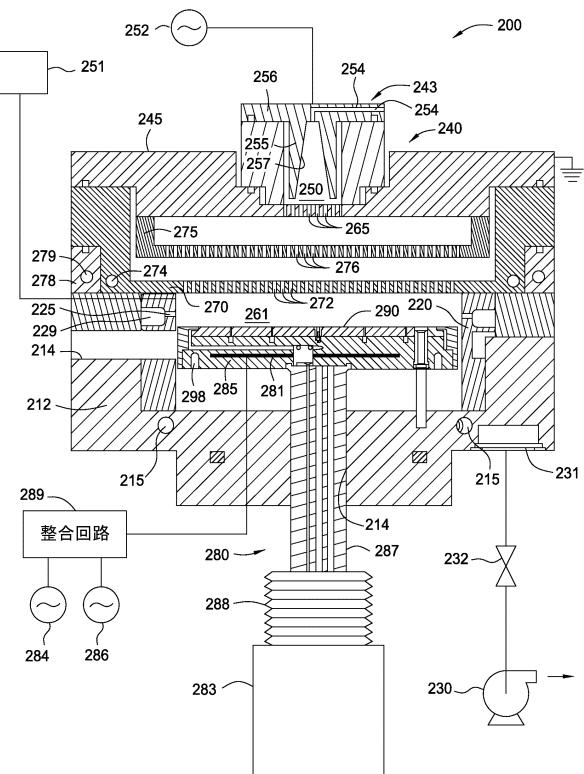

[0027] ブロック 402 で実施されるドライエッチング処理は、処理システム 800 のチャンバ 200 内で実行されうる（図 8 参照）。図 2 は、一体型層スタックから材料をドライエッチング又は除去するように構成された、例示的な処理チャンバ 200 の断面図である。ドライエッチングは、異方的エッチング、等方性エッチング、又はこれらの任意の組み合わせを含みうる。チャンバ 200 は、モールド層 502 のドライエッチングに特に適している。一ないし複数の実施形態の実行に適した処理チャンバ 200 は、限定するものではないが、FRONTIER（商標）処理チャンバ及び SiCONi（商標）処理チャンバを含みうる。どちらもカリフォルニア州サンタクララのアプライドマテリアルズ社から入手可能である。他の製造業者から入手可能な他の真空処理チャンバも、本実施形態を実行するように適合されうることに留意されたい。10

#### 【0023】

[0028] 処理チャンバ 200 は、真空を破ることなく、基板表面の熱処理とプラズマ処理の双方を提供する。一実施形態では、処理チャンバ 200 は、チャンバ本体 212、リッドアセンブリ 240、及び支持体アセンブリ 280 を含む。リッドアセンブリ 240 はチャンバ本体 212 の上端部に配置され、支持体アセンブリ 280 はチャンバ本体 212 内で少なくとも部分的に配置される。20

#### 【0024】

[0029] チャンバ本体 212 は、処理チャンバ 200 の内部へのアクセスを可能にするため、その側壁に形成されたスリットバルブ開口部 214 を含む。スリットバルブ開口部 214 は、外部の基板ハンドリングロボット（図示せず）によって、チャンバ本体 212 内部へのアクセスを可能にするため、選択的に開閉される。

#### 【0025】

[0030] 一ないし複数の実施形態では、チャンバ本体 212 は、伝熱流体を中に流すために形成されたチャネル 215 を含む。伝熱流体は、加熱流体又は冷却材であってもよく、処理中にチャンバ本体 212 の温度を制御するために使用される。30

#### 【0026】

[0031] チャンバ本体 212 は更に、支持体アセンブリ 280 を取り囲むライナー 220 を含む。ライナー 220 は、修理及び洗浄のために着脱可能である。ライナー 220 は、アルミニウムなどの金属、セラミック材料、又は他の任意の処理互換材料から作られる。一ないし複数の実施形態では、ライナー 220 は、一ないし複数の開口 225 及び真空ポート 231 と流体連通するように形成されたポンピングチャネル 229 を含む。開口 225 は、ポンピングチャネル 229 へのガス流路を設け、これによって、処理チャンバ 200 内のガスの真空ポート 231 への出口を提供する。

#### 【0027】

[0032] 真空ポンプ 230 及びスロットルバルブ 232 を含む真空システムは、処理チャンバ 200 を通るガス流を調整するため、真空ポート 231 に連結されている。真空ポンプ 230 は、チャンバ本体 212 内に配置された真空ポート 231 に連結されており、その結果、ライナー 220 内に形成されたポンピングチャネル 229 と流体連通している。40

#### 【0028】

[0033] リッドアセンブリ 240 は、少なくとも 2 つの積み重ねられた構成要素を含み、両者の間にプラズマ容積又は空洞を形成するように構成されている。一実施形態では、リッドアセンブリ 240 は、第 2 電極 245（「下方電極」）の上方に垂直に配置された第 1 電極 243（「上方電極」）を含み、両者の間にプラズマ容積又は空洞 250 を閉じ込める。第 1 電極 243 は RF 電源などの電源 252 に接続され、第 2 電極 245 は50

アース端子に接続され、2つの電極243、245の間にキャパシタンスを形成する。

**【0029】**

[0034] 一実施形態では、リッドアセンブリ240は、第1電極243の上部内に少なくとも部分的に形成される、一ないし複数のガス注入口254（1つのみを示す）を含む。ガス注入口254は、第1端部でプラズマ空洞250と流体連通されており、第2端部で一ないし複数の上流ガス源及び／又はガスミキサなどの他のガス供給構成要素に連結されている。

**【0030】**

[0035] 一ないし複数の実施形態では、第1電極243は、プラズマ空洞250と境界を接する拡張部分255を有する。一ないし複数の実施形態では、拡張部分255は環状の部材である。一ないし複数の実施形態では、拡張部分255は倒立させた切頭円錐又は「漏斗」に似ている。一ないし複数の実施形態では、拡張部分255の内面257は、拡張部分255の上部から下部へ徐々に傾斜している。プラズマ空洞250内で生成されるプラズマは、支持体アセンブリ280上方の処理領域261に入る前にリッドアセンブリ240内で画定されるため、基板（図示せず）は処理中にそこに配置される。プラズマは処理領域261から離れたところで生成されるため、リッドアセンブリ240は遠隔プラズマ源とみなされうる。一ないし複数の実施形態では、様々な処理ガス／キャリアガスが、ガス源251を経由して処理領域261に供給されうる。処理ガス／キャリアガスはプラズマを形成するため励起されず、ガス源251を経由して処理領域261に導入されうる。

10

**【0031】**

[0036] 拡張部分255はガス注入口254と流体連通しており、プラズマ空洞250内のガスの混合を支援する旋回流量パターンすなわち「渦」流を拡張部分255内に作り出すため、2つのガス注入口254は拡張部分255の反対側に配置されうる。

**【0032】**

[0037] リッドアセンブリ240は更に、分配プレート270及び第2電極245に隣接する遮蔽板275を含むことができる。第2電極245、分配プレート270及び遮蔽板275は、チャンバ本体212に接続されたリッドリム278上に積み重ねられ、配置される。リッドリム278は、伝熱媒体を循環させるための埋め込みチャネル又は通路279を含むことができる。

20

**【0033】**

[0038] 一ないし複数の実施形態では、第2電極又は上部プレート245は、プラズマ空洞250からガスを流すことを可能にするため、プラズマ空洞250の下に形成される複数のガス通路又は開口265を含むことができる。分配プレート270はほぼ円板形状で、そこを通るガスの流れを分散するため、複数の開口272又は通路を含む。

**【0034】**

[0039] 一ないし複数の実施形態では、分配プレート270は、リッドアセンブリ240の温度制御を行うため、ヒータ又は加熱流体を収容するための一ないし複数の埋め込みチャネル又は通路274を含む。

**【0035】**

[0040] 遮蔽板275は、オプションにより、第2電極245と分配プレート270との間に配置されうる。遮蔽板275は、第2電極245の下面に着脱可能に取り付けられる。遮蔽板275は、第2電極245と熱的及び電気的に良好に接しうる。一ないし複数の実施形態では、遮蔽板275は、ボルト又は同様な締め具を使用して、第2電極245に連結されうる。遮蔽板275はまた、第2電極245の外径上にねじ込み又はねじ止め可能である。遮蔽板275は、第2電極245から分配プレート270まで複数のガス通路を提供するため、複数の開口276を含む。

30

**【0036】**

[0041] 支持体アセンブリ280は、チャンバ本体212での処理のために基板を支える支持部材285を含むことができる。支持部材285は、チャンバ本体212の

40

50

底面に形成された中心に位置する開口部 214 を経由して延在するシャフト 287 を通つて昇降機構 283 に連結されうる。昇降機構 283 は、シャフト 287 周囲からの真空漏れを防止するベローズ 288 によって、チャンバ本体 212 に柔軟に密閉されうる。昇降機構 283 により、支持部材 285 はチャンバ本体 212 内で処理位置と下方移送位置との間を垂直に移動することができる。一実施形態では、支持部材 285 は、基板の裏面汚染を低減するため、例えば、シリコン又はセラミック材料からなる着脱可能な上部プレート 290 を含む。

#### 【0037】

【0042】 一ないし複数の実施形態では、基板（図示せず）は、真空チャック又は静電チャックを利用して、支持部材 285 に固定されうる。静電チャックは典型的に、支持部材 285 の上に配置される、又は支持部材 285 の一体化された部分として形成される、電極 281 を取り囲む少なくとも誘電体材料を含む。一実施形態では、電極 281 は複数の RF バイアス電源 284、286 に連結されている。デュアル RF バイアス電源 284、286 は、整合回路 289 を経由して電極 281 に連結されている。RF バイアス電源 284、286 は一般的に、約 50 kHz から約 200 MHz までの周波数と約 0 ワットから約 5000 ワットまでの電力を有する RF 信号を生成することができる。必要に応じて、プラズマの特性を制御するため、付加的なバイアス電源が電極 281 に連結されうる。

#### 【0038】

【0043】 支持体アセンブリ 280 の温度は、支持部材 285 の本体内に埋め込まれた流体チャネル 298 を通って循環される流体によって制御可能である。

#### 【0039】

【0044】 システムコントローラ（図示せず）は、処理チャンバ 200 の動作を調整するための使用可能である。システムコントローラは、コンピュータのメモリ上に保存されたコンピュータプログラムの制御下で動作可能である。コンピュータプログラムは、後述の処理を処理チャンバ 200 内で実行することを可能にする命令を含みうる。例えば、コンピュータプログラムは、処理順序及びタイミング、ガス混合、チャンバ圧力、RF 電力レベル、サセプタ位置決め、スリットバルブ開閉、基板冷却及び特定の処理の他のパラメータを命令することができる。

#### 【0040】

【0045】 図 4 及び図 5A ~ 図 5D を振り返ると、ブロック 404 では、方法 400 は、処理システム 800 のチャンバ 300 内の配線 512 上にライナー 520 を堆積することを含む。ライナー 520 は、原子層堆積（ALD）、CVD、HPCVD、高密度プラズマ CVD、遠隔プラズマ CVD、マイクロ波支援 CVD、NBECVD 又はプラズマ原子層堆積（PEALD）によって堆積されてもよく、ここで、ALD、CVD、HPCVD、NBECVD、PEALD という用語は、基板構造の上に層を堆積するための反応物質又は前駆体の順次導入、又は他の任意の好適な堆積処理を示している。図 5B に示した実施形態では、ライナー 520 は、配線 512 の側壁 514 及び上面壁 516 の上に堆積されるコンフォーマルライナーである。

#### 【0041】

【0046】 一実施形態では、ライナー 520 は、配線 512 の酸化を防止し、隣接する配線 512（例えば、ダマシントレース）間の容量性結合を最小化するように構成されている誘電体ライナーである。一実施形態では、配線 512 間の所望のキャパシタンスは、低誘電率のライナー材料を選択することによって実現される。例えば、ライナーは、炭化物、窒化物及び炭窒化ケイ素（SiCN）などのシラン、又はこれらの任意の好適な組み合わせ、及び / 又は他の有用な低誘電率材料を含む、誘電体材料から選択される。一実施例では、ブロック 404 で実行されるライナー堆積処理は、SiCN 材料を約 20 オンストローム（Å）堆積するため、約 3.7 Torr の処理圧力で、摂氏約 350 度の温度で、13.56 MHz の RF 電力の約 700 W の出力で、約 10 秒間、トリメチルシランを供給することを含む。なお、低誘電率材料ライナー層は、約 2 ナノメートル未満の厚

10

20

30

40

50

みを有するように堆積されてもよい。

【0042】

[0047] 別の実施形態では、所望のキャパシタンスは、より大きな従来の誘電率を有するライナー520を、約4ナノメートル未満の厚みで、例えば、約2ナノメートル未満で、或いは約1ナノメートル未満で、但し、少なくとも単一層よりは大きな厚みで堆積することによって実現される。一実施形態では、ライナー520は、窒化ケイ素(SiN)又は窒化アルミニウム(AlN)などの従来の誘電体材料、或いはこれらの他の任意の好適な組み合わせ、及び/又は他の有用な誘電体材料から選択される。一実施例では、ブロック404で実行されるライナー堆積処理は、SiN材料を約20オングストローム(A)堆積するため、約3.5Torrの処理圧力で、摂氏約350度の温度で、13.56MHzのRF電力の約75Wの出力で、約5秒間、SiH<sub>4</sub>又はNH<sub>3</sub>ガスを供給することを含む。更に別の実施形態では、所望のキャパシタンスは、最適なライナー材料と厚みを組わせることによって、実現されうる。10

【0043】

ライナー堆積チャンバの例

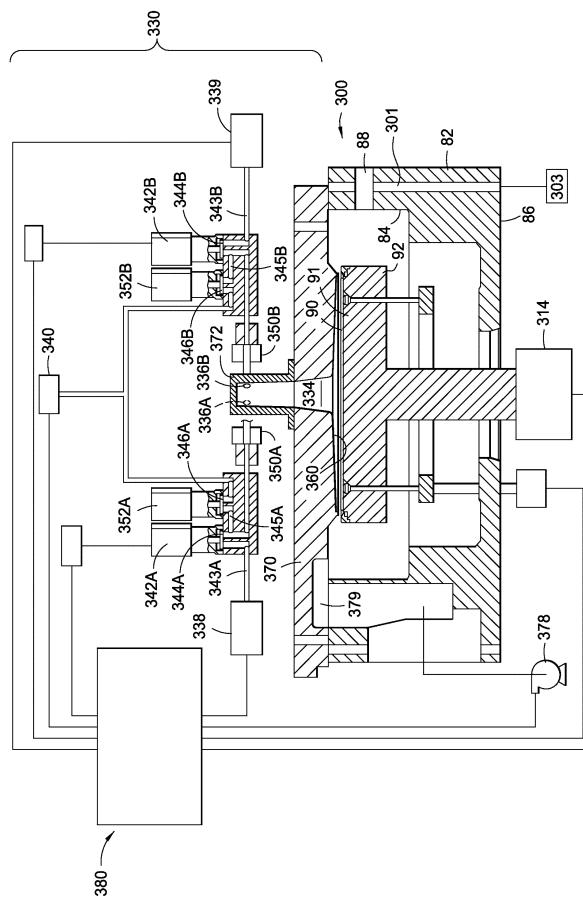

[0048] ブロック404で実行されるライナー堆積処理は、図3に示されるチャンバ300と同様のチャンバ内で実施されうる(図3参照)。一般的に、チャンバ300は、一体型層スタック上にライナーを堆積することに適しており、ALD、CVD、HPCVD、PEALD、PECVD、マイクロ波支援CVD又はNBECVDなど、循環堆積に適合されたガス供給装置330を含む。所望の厚みでコンフォーマル層を形成するためには、複数の薄層を堆積するため、前駆体の順次導入が反復されうる。20

【0044】

[0049] 処理チャンバ300は、側壁84及び底部86を有するチャンバ本体82を含む。側壁84は、側壁を加熱及び冷却するための流体源303に連結された流体チャネル301を含みうる。処理チャンバ300のスリットバルブ88は、ロボット(図示せず)が基板90を供給し、処理チャンバ300から基板90を回収できるよう、アクセスを可能にしている。

【0045】

[0050] 基板支持体92は、処理チャンバ300内の基板受容面91上で基板90を支持する。基板支持体92は、基板支持体92及びその上に配置された基板90を上げ下げするための昇降モータ314に取り付けられている。基板支持体92は、その上に配置された基板90の温度を上げるために、加熱されうる。ガス供給装置330は、処理ガス及び/又はバージガスなどのガスをチャンバ80に供給するため、チャンバ本体82の上部に配置されている。真空システム378は、任意の所望のガスを処理チャンバ300から排気し、処理チャンバ300内を所望の圧力に維持するよう支援するためのポンピングチャネル379と連通している。30

【0046】

[0051] 一実施形態では、処理チャンバ300によって、処理ガス及び/又はバージガスは、ガス供給装置330を介して、基板90の平面に対して垂直に(すなわち、90度で)処理チャンバ300に入ることができる。したがって、基板90の表面はガスに対して対称に露出され、基板上での均一な膜形成を可能にする。40

【0047】

[0052] 一実施形態では、ガス供給装置330は処理チャンバリッド370を備える。チャンバリッド370は、チャンバリッド370の中心部分から延在する拡張チャネル334、及び拡張チャネル334からチャンバリッド370の周辺部分まで延在する底面360を含む。拡張チャネル334は、2つの同様なバルブ対342A/352A、342B/352Bからガス流を供給するガス注入口336A、336Bを有する。

【0048】

[0053] 1つの構成では、バルブ342A、342Bは別々の前駆体ガス源に連結されているが、同一のバージガス源に連結されてもよい。例えば、バルブ342Aは第150

前駆体ガス源 338 に連結されており、バルブ 342B は第2前駆体ガス源 339 に連結されており、両バルブ 342A、342B はバージガス源 340 に連結されている。各バルブ 342A、342B は、バルブシートアセンブリ 344A、344B を有する供給ライン 343A、343B を含み、各バルブ 352A、352B は、バルブシートアセンブリ 346A、346B を有するバージライン 345A、345B を含む。供給ライン 343A、343B は、第1前駆体ガス源 338、及び第2前駆体ガス源 339 と連通しており、拡張チャネル 334 のガス注入口 336A、336B と連通している。供給ライン 343A、343B のバルブシートアセンブリ 344A、344B は、前駆体ガス源 338、339 から拡張チャネル 334 までの前駆体ガスの流れを制御する。バージライン 345A、345B はバージガス源 340 と連通しており、バルブ 342A、342B のバルブシートアセンブリ 344A、344B 下流の供給ライン 343A、343B と交差する。バージライン 343A、343B のバルブシートアセンブリ 344A、344B は、バージガス源 340 から供給ライン 343A、343B までのバージガスの流れを制御する。バルブ 342A、342B の供給ライン 343A、343B は、ガス導管 350A、350B を経由してガス注入口 336A、336B に連結されうる。ガス導管 350A、350B は、バルブ 342A、342B と一体化されてもよく、或いはバルブ 342A、342B から分離されてもよい。

## 【0049】

【0054】 拡張チャネル 334 は、キャップ 372 の上部から処理チャンバリッド 370 の底面 360 に隣接する拡張チャネル 334 の下部まで、増大する直径を有するチャネルを備える。一般的に、ガス流を増やすには、拡張チャネルの直径を大きくすることが必要になる。

## 【0050】

【0055】 上述の処理チャンバ 300 は、コントローラ 380 などのプロセッサベースのシステムコントローラによって制御可能である。コントローラ 380 は、コンピュータのメモリ上に保存されたコンピュータプログラムの制御下で動作可能である。コンピュータプログラムは、処理チャンバ 300 内で実行される後述の処理を可能にする命令を含みうる。

## 【0051】

【0056】 図4及び図5A～図5Dを振り返ると、ブロック 406 では、方法 400 は、一体型層スタック 500 内で形成されるライナー 520 の上に空隙構造 526 を形成することを含む。一実施形態では、空隙構造 526 は、一ないし複数の流動性 CVD 处理を用いることによって、第1の流動性低誘電率材料 528、犠牲膜 530、及び第2の流動性低誘電率材料 532 を含む層スタックを、ライナー 520 及びブロック 402 で形成されるトレンチ 524 内に堆積することによって形成される。一実施形態では、第1の流動性低誘電率材料 528 及び第2の流動性低誘電率材料 532 は、炭素がドープされた酸化物又はこれらの変形物、例えば、フッ素化炭素、NCS、メソポーラス酸化物、又は有機「スピノン」材料、及び炭素(C)又は高分子炭素-水素膜を含む犠牲膜 530 である。一実施形態では、ライナー 520 は、好都合なことに、犠牲炭素膜 530 から銅配線 512 を保護する。一実施形態では、空隙構造 526 は、一ないし複数の流動性 CVD 处理を用いることによって、犠牲膜 530 及び第2の流動性低誘電率材料 532 のみを含む層スタックを、ライナー 520 及びブロック 402 で形成されるトレンチ 524 内に堆積することによって形成される。

## 【0052】

【0057】 一実施形態では、次に、犠牲膜 530 を取り除き、これによって空隙構造 526 を形成するため、第1の流動性低誘電率材料 528 及び第2の流動性低誘電率材料 532、並びに犠牲膜 530 がUV処理又は熱処理によって硬化される。しかしながら、層スタックが犠牲膜 530 及び第2の流動性低誘電率材料 532 のみを含む実施形態では、犠牲膜 530 を取り除き、これによって空隙構造 526 を形成するため、犠牲膜 530 及び第2の流動性低誘電率材料 532 のみがUV処理又は熱処理によって硬化される。-

実施形態では、第1の流動性低誘電率材料528及び第2の流動性低誘電率材料532、並びに犠牲膜530は、He又はArなどの不活性ガスを使用して、UV光の下で摂氏約400度未満の温度で硬化されうる。

#### 【0053】

【0058】一実施形態では、ライナー520の一部を研磨して、配線512の上面壁516を露出するため、第2の流動性低誘電率材料532は、例えば、化学機械研磨処理によって研磨しなおされる。バリア層(図示せず)は、その後の処理、例えば、プランケット低誘電率材料堆積を実行する前に、上面壁516の上に堆積されうる。別の実施形態では、その後の処理、例えば、プランケット低誘電率材料堆積を実行する前に、流動性低誘電率材料532のみが部分的に研磨しなおされ、ライナー520は研磨されない。したがって、上面壁516の上の研磨されていないライナー520は、配線512とプランケット低誘電率材料との間の拡散を防止するバリア層として使用可能である。10

#### 【0054】

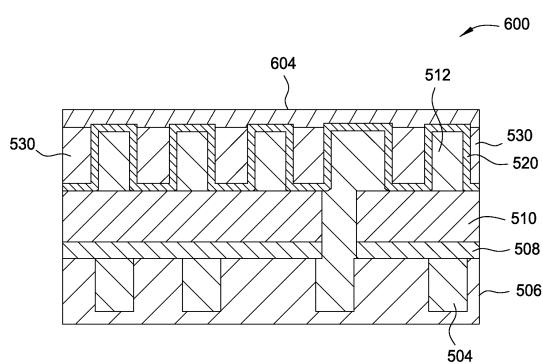

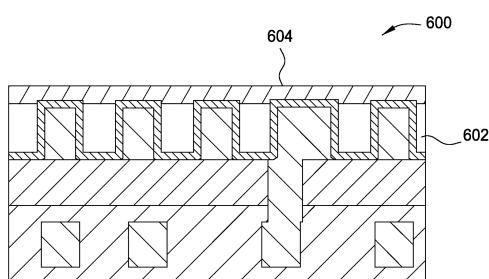

【0059】図6A～図6Bは、本明細書に記載の別の実施形態による一体型層スタック600の概略的な断面図である。一体型層スタック600は、一体型層スタック500に類似している。一体型層スタック600を形成する処理は、上述のように操作402～404を実行することを含む。しかしながら、本方法400のこの実施形態では、ブロック406は、一体型層スタック600に空隙構造602を形成することを含む。空隙構造602は、犠牲膜530及びキャッピング層604を含む層スタックを堆積することによって形成される。層スタックは、CVDプロセス、例えば、PECVD(プラズマ化学気相堆積)によって、ライナー520の上及びトレンチ524内に犠牲膜530を堆積することによって、形成される。犠牲膜530は、一体型層スタック500を参照して上述されたように、材料を含みうる。その後、キャッピング層604は、CVDプロセス、例えば、PECVD(プラズマ化学気相堆積)によって、犠牲膜530の上に堆積される。一実施形態では、キャッピング層はSiOCHなどの多孔性材料である。次に、犠牲膜530を取り除き、これによって空隙構造602を形成するため、キャッピング層604及び犠牲膜530はUV処理又は熱処理によって硬化される。20

#### 【0055】

【0060】図7は、別の実施形態による一体型層スタック700の概略的な断面図である。一体型層スタック700は一体型層スタック500と同様であるが、ブロック402でモールド層502のドライエッティング後、非コンフォーマルライナー702はブロック404でトレンチ524内に配置される。非コンフォーマルライナー702は、材料はライナー520と同様であるが、非コンフォーマルライナー702は、ライナー702内に無効な空隙構造704を形成するように堆積される。無効な空隙構造704は、上面壁516近くでは高速で、また、配線512の側壁514近くでは低速で、ライナー702を堆積すること、並びにトレンチ524が満たされる前に上面壁516近くで堆積を「摘み取る」ことによって、従来の技術で形成される。30

#### 【0056】

##### 処理システムの例

【0061】図8は処理システム800の平面図を示している。一実施形態では、ブロック402及び404、並びに方法400のブロック406の少なくとも一部は、処理システム800内で実行される。処理システム800は、チャンバ200及び300を含む一体型クラスタツールである。一実施形態では、処理システム800は、第1移送チャンバ804に連結された複数の第1処理チャンバ802を含む。一実施形態では、第1処理チャンバ802はチャンバ200すなわちドライエッティングのためのもので、方法400のブロック402におけるドライエッティングはチャンバ200内で実行される。第1移送チャンバ804はまた、一ないし複数のロードロックチャンバ806に連結されている。第1移送チャンバ804は、処理チャンバ802と第1ロードロックチャンバ806との間で基板を移送するための、中央に配置された移送口ボット(図示せず)を有する。処理システム800はまた、第2移送チャンバ810に連結された複数の第2処理チャンバ84050

08を含む。一実施形態では、第2処理チャンバ808は、チャンバ300などのライナー堆積のためのチャンバを含み、ブロック404で実行されるライナー520の堆積、及びブロック406で実行される層スタック堆積処理は、チャンバ300内で実施される。このような好適なチャンバの1つは、カリフォルニア州サンタクララのアプライドマテリアルズ社のCENTINEL(商標)チャンバであってもよい。

#### 【0057】

[0062] 第2の処理チャンバ808はまた、層スタック堆積のためのチャンバを含む。例えば、第1の流動性低誘電率材料528及び第2の流動性低誘電率材料532は第1処理チャンバ802内で堆積され、犠牲膜530は第2処理チャンバ808内で堆積される。別の実施形態では、キャッピング層604及び犠牲膜530は、同一処理チャンバ808内で堆積される。このような好適なチャンバの1つは、カリフォルニア州サンタクララのアプライドマテリアルズ社のETERNA(商標)チャンバであってもよい。第2移送チャンバ810はまた、処理チャンバ808と第1ロードロックチャンバ806との間で基板を移送するための、中央に配置された移送ロボット(図示せず)を有する。ファクトリインターフェース812は、第2ロードロックチャンバ814によって、第1移送チャンバ804に接続されている。ファクトリインターフェース812は、第2ロードロックチャンバ814の反対側で、一ないし複数のポッド816に連結されている。ポッド816は典型的に、洗浄室側からアクセス可能な前方開口型統一ポッド(FOUP)である。第1処理チャンバ802はチャンバ200のように示されており、第2処理チャンバ808はチャンバ300のように示されているが、最小の待ち時間で基板のスループットを最大にするように、チャンバの任意の組み合わせが使用されうるように企図されている。

。

#### 【0058】

[0063] 一実施形態では、処理システム800はCENTURA(登録商標)又はENDURA(登録商標)プラットフォームで、どちらもカリフォルニア州サンタクララのアプライドマテリアルズ社から入手可能である。他の製造業者から入手可能な他の処理システムも、本明細書に記載の一ないし複数の実施形態を実行するように適合されうることに留意されたい。

#### 【0059】

[0064] ブロック402及び404でのドライエッティング及びライナー堆積処理、並びにブロック406での層スタック堆積処理は、「真空を破ることなく」処理システム800内で実行される。本明細書で使用されているように、「真空を破ることなく」という表現は、1つのチャンバ、例えばチャンバ200の真空環境と、第2のチャンバ、例えばチャンバ300の真空環境との間で、真空圧を維持しつつ、一体型層スタック500を周囲環境に曝露することなく、一体型層スタック500を移送する処理について言及している。周囲環境では、一体型層スタック500は、粒子、湿気、酸素などのように、製造される誘電体層構造を損傷しうる、また、場合によっては望ましくない界面層、例えば、移送中の各層間の自然酸化物を形成しうる、機械的及び化学的汚染物質に曝露されることがある。したがって、真空を破ることなく、処理システム800内で方法400を実行することは、好都合なことに、(i)一体型層スタック500に対する待ち時間を最小限にし、また、(ii)ブロック402でのドライエッティングとブロック404でのライナー520堆積との間の配線512の酸化を防止し、更に、ブロック404でのライナー堆積とブロック406での空隙構造形成における層スタックの堆積との間のライナー520の酸化を防止する。

。

#### 【0060】

[0065] 上述事項は、本開示の実施形態を対象としているが、本開示の基本的な範囲から逸脱せずに他の更なる実施形態を考案することができ、本開示の範囲は下記の特許請求の範囲によって規定される。

【図1】

【図2】

【図3】

【図4】

【図 5 A】

【図 5 C】

【図 5 B】

【図 5 D】

【図 6 A】

【図 7】

【図 6 B】

【図8】

---

フロントページの続き

(72)発明者 レン，ホー

アメリカ合衆国 カリフォルニア 95130, サンノゼ, ラサルウェイ 2658

(72)発明者 ツイ，ジェンジアン

アメリカ合衆国 カリフォルニア 95129, サンノゼ, ボリンジャー ロード 6670

審査官 早川 朋一

(56)参考文献 特開2010-165864(JP,A)

特開2013-165147(JP,A)

特開2004-103971(JP,A)

米国特許出願公開第2010/0051578(US,A1)

特開2009-094519(JP,A)

特開2011-165876(JP,A)

特開2004-266244(JP,A)

特開2010-153859(JP,A)

特開2014-053612(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/3205 - 21/3215

H01L 21/768

H01L 23/52

H01L 23/522 - 23/532