(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5743066号

(P5743066)

(45) 発行日 平成27年7月1日(2015.7.1)

(24) 登録日 平成27年5月15日(2015.5.15)

(51) Int.Cl.

G01J 1/44 (2006.01)

G09G 3/30 (2006.01)

F 1

G01J 1/44

G09G 3/30N

K

請求項の数 5 (全 21 頁)

(21) 出願番号 特願2011-48320 (P2011-48320)

(22) 出願日 平成23年3月4日 (2011.3.4)

(65) 公開番号 特開2012-186313 (P2012-186313A)

(43) 公開日 平成24年9月27日 (2012.9.27)

審査請求日 平成26年2月14日 (2014.2.14)

(73) 特許権者 514188173

株式会社 J O L E D

東京都千代田区神田錦町三丁目23番地

(74) 代理人 110001357

特許業務法人つばさ国際特許事務所

(72) 発明者 山本 哲郎

東京都港区港南1丁目7番1号 ソニー株

式会社内

(72) 発明者 内野 勝秀

東京都港区港南1丁目7番1号 ソニー株

式会社内

審査官 ▲高▼場 正光

最終頁に続く

(54) 【発明の名称】光検出回路、光検出方法、表示パネルおよび表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

表示パネルと、

前記表示パネルを駆動する駆動回路と

を備え、

前記表示パネルは、

自発光素子を含む複数の画素と、

前記画素から発せられた光を検出する複数の光検出回路と

を有し、

前記光検出回路は、

固定電源線と光検出線との間に設けられたトランジスタと、

前記トランジスタのゲートと制御線との間に設けられるとともに、カソードが前記制御

線側を向くように配置されたフォトダイオードと

を有し、

前記駆動回路は、前記フォトダイオードに順バイアスを印加するとともに前記トランジ

スタをオフ状態とする第1電圧と、前記フォトダイオードに逆バイアスを印加するととも

に前記トランジスタをオフ状態とする第2電圧(前記第2電圧 > 前記第1電圧)と、前記

フォトダイオードに逆バイアスを印加するとともに前記トランジスタをオン状態とする第

3電圧(前記第3電圧 > 前記第2電圧)とを順次、前記制御線に出力する電源を有する

表示装置。

## 【請求項 2】

前記駆動回路は、前記光検出線に接続された受光信号処理回路をさらに有し、

前記受光信号処理回路は、

前記光検出線の電圧を検出する電圧検出部と、

前記光検出線の電圧を第4電圧（前記第4電圧 > 前記第1電圧）で初期化する初期化部と

を有する

請求項1に記載の表示装置。

## 【請求項 3】

前記駆動回路は、前記電圧検出部で検出された電圧の大きさに応じて映像信号を補正する信号処理回路をさらに有する

請求項2に記載の表示装置。

## 【請求項 4】

固定電源線と光検出線との間に設けられたトランジスタと、前記トランジスタのゲートと制御線との間に設けられると共にカソードが前記制御線側を向くように配置されたフォトダイオードとを備えた光検出回路を用いて、入射光を検出する光検出方法であって、

前記制御線の電圧を、前記フォトダイオードに順バイアスを印加するとともに前記トランジスタをオフ状態とする第1電圧に設定するとともに、前記光検出線の電圧を初期化する第1ステップと、

前記制御線の電圧を、前記フォトダイオードに逆バイアスを印加するとともに前記トランジスタをオフ状態とする第2電圧（前記第2電圧 > 前記第1電圧）に設定する第2ステップと、

前記制御線の電圧を、前記フォトダイオードに逆バイアスを印加するとともに前記トランジスタをオン状態とする第3電圧（前記第3電圧 > 前記第2電圧）に設定する第3ステップと

を含む

光検出方法。

## 【請求項 5】

前記第2ステップと前記第3ステップとの間に、前記光検出線の電圧を再度、初期化する第4ステップを含む

請求項4に記載の光検出方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、光検出回路を含む表示パネルを備えた表示装置と、この光検出回路を用いた光検出方法とにに関する。

## 【背景技術】

## 【0002】

近年、画像表示を行う表示装置の分野では、画素の発光素子として、流れる電流値に応じて発光輝度が変化する電流駆動型の光学素子、例えば有機EL（electro luminescence）素子を用いた表示装置が開発され、商品化が進められている。有機EL素子は、液晶素子などと異なり自発光素子である。そのため、有機EL素子を用いた表示装置（有機EL表示装置）では、光源（バックライト）が必要ないので、光源を必要とする液晶表示装置と比べて、薄型化、高輝度化することができる。特に、駆動方式としてアクティブマトリクス方式を用いた場合には、各画素をホールド点灯させることができ、低消費電力化することもできる。そのため、有機EL表示装置は、次世代のフラットパネルディスプレイの主流になると期待されている。

## 【0003】

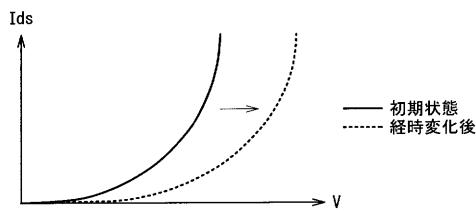

しかし、有機EL素子では、通電する電流量に応じて素子が劣化し、発光効率が低下するという問題がある（図21参照）。そのため、有機EL素子を表示装置の画素として用

10

20

30

40

50

いた場合には、画素ごとに劣化の状況が異なることがある。例えば、時刻や表示チャンネルなどの情報が長時間、同じ場所に高輝度で表示されていた場合には、その部分の画素だけ劣化が早まる。その結果、劣化の早まった画素を含む部分に高輝度の映像が表示された場合には、劣化の早まった画素の部分だけが暗く表示される焼き付きという現象が生じてしまう。この焼き付きは非可逆性であることから、一旦、焼き付きが生じると、焼き付きが消えることはない。

#### 【0004】

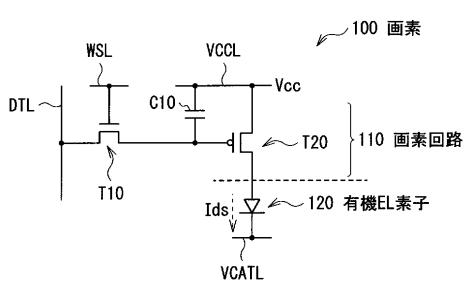

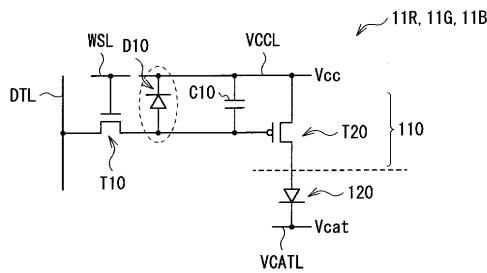

有機EL素子に流す電流量を補正することにより、焼き付きを改善する手法が、今までに多数提案されている。例えば、画素回路内にフォトダイオードを設けることが提案されている。具体的には、図22に示したように、トランジスタT10、トランジスタT20および保持容量C10を含む画素回路110と、有機EL素子120とからなる従来タイプの画素100(図20参照)に対して、トランジスタT20のゲートと電源線VCCLとの間にフォトダイオードD10設けることが開示されている。これにより、白表示時、フォトダイオードは有機EL素子の発光を検出して固定電源線からトランジスタのゲートへ電流を流す。この時、トランジスタのゲート-ソース間電圧は小さくなり、有機EL素子に流れる電流は小さくなる。次に、白表示のまま、一定時間経過後に有機EL素子の発光効率の低下等によって発光輝度が低下した場合を考える。この時、発光輝度の低下によってフォトダイオードに入射する光量は低下し、固定電源線からトランジスタのゲートへ流入する電流値は小さくなる。これにより、トランジスタのゲート-ソース間電圧は大きくなり、有機EL素子に流れる電流は大きくなる。このように、EL素子に流れる電流量をフォトダイオードで調整することで、有機EL素子の効率変化に起因する焼き付きを軽減することが可能である。

10

20

30

#### 【0005】

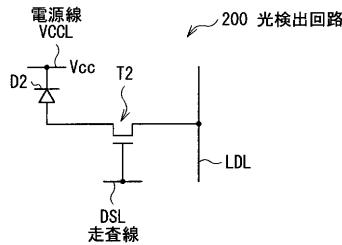

また、例えば、画素回路に隣接して光検出回路を設けるとともに、光検出回路の出力に基づいて信号線の電圧を補正する信号処理回路を設けることが提案されている(特許文献1参照)。具体的には、図23に示したように、光検出線LDLと、電源線VCCLとの間に、互いに直列に接続されたフォトダイオードD2およびスイッチングトランジスタT2を有する光検出回路200を設けるとともに、図示しないが、この光検出回路200の出力に基づいて信号線DTLの電圧を補正する信号処理回路を設けることが開示されている。これにより、輝度劣化量を考慮した電圧を信号線DTLに出力することができるので、有機EL素子の効率変化に起因する焼き付きを軽減することが可能である。また、画像表示期間とは異なる期間(例えば、表示装置の電源をオフした直後やオンした直後)に光検出を行うことにより、表示画像の輝度に依存せずに光検出を行うことが可能である。

#### 【先行技術文献】

#### 【特許文献】

#### 【0006】

【特許文献1】特開2010-286814号公報

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0007】

ところで、特許文献1に記載の方策では、電流変化を的確に検知するために、電流変化の大きなオフ領域(印加電圧:負で0V付近)を用いるのが望ましい。ところが、このときの電流値は大きくなっているとはいっても、オン電流と比較すると非常に小さい。そのため、輝度変化の検出精度が十分に得られないという問題があった。

40

#### 【0008】

本発明はかかる問題点に鑑みてなされたものであり、その目的は、焼き付きを低減しつつ、高い検出精度を得ることの可能な光検出回路を備えた表示装置と、焼き付きを低減しつつ、高い検出精度を得ることの可能な光検出方法とを提供することにある。

#### 【課題を解決するための手段】

#### 【0009】

50

参考例の第1の光検出回路は、入射光を検出する回路である。この光検出回路は、固定電源線と光検出線との間に設けられたトランジスタと、トランジスタのゲートと制御線との間に設けられるとともに、カソードが制御線側を向くように配置されたフォトダイオードを備えている。この光検出回路は、さらに、フォトダイオードと並列接続された第1容量素子と、トランジスタのゲートと固定電源線との間に設けられた第2容量素子とを備えている。

【0010】

参考例の第1の表示パネルは、自発光素子を含む複数の画素と、画素から発せられた光を検出する複数の光検出回路とを備えている。この表示パネルに含まれる光検出回路は、上記の第1の光検出回路と同一の構成要素を有している。参考例の第1の表示装置は、表示パネルと、表示パネルを駆動する駆動回路とを備えている。この表示装置に含まれる表示パネルは、上記の第1の表示パネルと同一の構成要素を有している。

10

【0011】

参考例の第1の光検出回路、第1の表示パネルおよび第1の表示装置では、カソードが制御線側を向くようにフォトダイオードが配置されると共に、フォトダイオードに並列に第1容量素子が設けられている。これにより、1本の制御線に制御パルスを印加するだけで、光検出線に接続されたトランジスタのゲートに、画素から発せられた光の光量の大きさに応じた電圧をオン電圧として印加することが可能となる。

【0012】

参考例の第2の光検出回路は、入射光を検出する回路である。この光検出回路は、固定電源線と光検出線との間に設けられたトランジスタと、トランジスタのゲートと制御線との間に設けられるとともに、カソードが制御線側を向くように配置されたフォトダイオードを備えている。上記の制御線は、第1電圧、第2電圧および第3電圧の計3値を順次、出力する電源に接続される配線である。ここで、第1電圧は、フォトダイオードに順バイアスを印加するとともにトランジスタをオフ状態とする電圧である。第2電圧は、フォトダイオードに逆バイアスを印加するとともにトランジスタをオフ状態とする電圧である。第3電圧は、フォトダイオードに逆バイアスを印加するとともにトランジスタをオン状態とする電圧である。

20

【0013】

参考例の第2の表示パネルは、自発光素子を含む複数の画素と、画素から発せられた光を検出する複数の光検出回路とを備えている。この表示パネルに含まれる光検出回路は、上記の第2の光検出回路と同一の構成要素を有している。本発明の第2の表示装置は、表示パネルと、表示パネルを駆動する駆動回路とを備えている。この表示装置に含まれる表示パネルは、上記の第2の表示パネルと同一の構成要素を有している。また、この表示装置に含まれる駆動回路は、上述の第1電圧、第2電圧（前記第2電圧 > 前記第1電圧）および第3電圧（前記第3電圧 > 前記第2電圧）の計3値を順次、出力する電源を有している。

30

【0014】

参考例の第2の光検出回路、参考例の第2の表示パネルおよび本発明の第2の表示装置では、カソードが制御線側を向くようにフォトダイオードが配置されている。これにより、1本の制御線に制御パルスを印加するだけで、光検出線に接続されたトランジスタのゲートに、画素から発せられた光の光量の大きさに応じた電圧をオン電圧として印加することが可能となる。

40

【0015】

本発明の光検出方法は、固定電源線と光検出線との間に設けられたトランジスタと、トランジスタのゲートと制御線との間に設けられると共にカソードが制御線側を向くように配置されたフォトダイオードとを備えた光検出回路を用いて、入射光を検出する方法である。この光検出方法は、以下の3つのステップを含むものである。

（A）制御線の電圧を、フォトダイオードに順バイアスを印加するとともにトランジスタをオフ状態とする第1電圧に設定するとともに、光検出線の電圧を初期化する第1ステッ

50

プ

(B) 制御線の電圧を、フォトダイオードに逆バイアスを印加するとともにトランジスタをオフ状態とする第2電圧(前記第2電圧>前記第1電圧)に設定する第2ステップ

(C) 制御線の電圧を、フォトダイオードに逆バイアスを印加するとともにトランジスタをオン状態とする第3電圧(前記第3電圧>前記第2電圧)に設定する第3ステップ

【0016】

本発明の光検出方法において、さらに、第2ステップと第3ステップとの間に、光検出線の電圧を再度、初期化する第4ステップを含んでいてもよい。

【0017】

本発明の光検出方法では、カソードが制御線側を向くように配置されたフォトダイオードを含む光検出回路を用いて、1本の制御線に、3種類の電圧を含む制御パルスを印加するだけで、光検出線に接続されたトランジスタのゲートに、画素から発せられた光の光量の大きさに応じた電圧をオン電圧として印加することが可能である。 10

【発明の効果】

【0018】

参考例の第1および第2の光検出回路、参考例の第1および第2の表示パネル、参考例の第1の表示装置、本発明の第2の表示装置ならびに本発明の光検出方法によれば、光検出線に接続されたトランジスタのゲートに、画素から発せられた光の光量の大きさに応じた電圧をオン電圧として印加することができるようとしたので、焼き付きを低減しつつ、高い検出精度を得ることができる。 20

【図面の簡単な説明】

【0019】

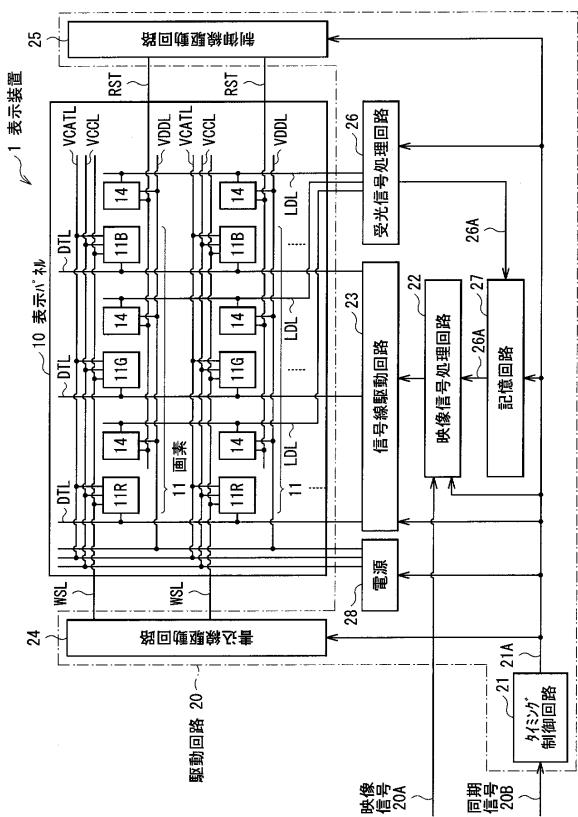

【図1】本発明の一実施の形態に係る表示装置の概略構成図である。

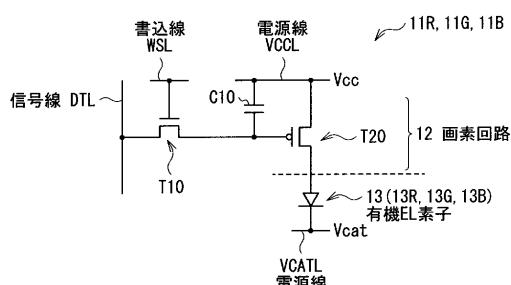

【図2】図1の画素の回路図である。

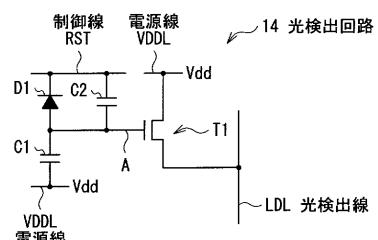

【図3】図1の光検出回路の回路図である。

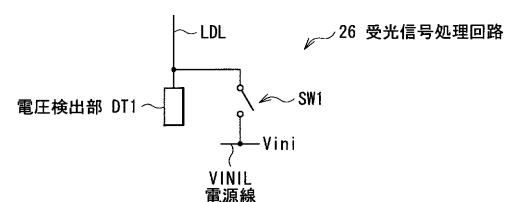

【図4】図1の受光信号処理回路の回路図である。

【図5】図1の表示装置における光検出に関する動作を表す図である。

【図6】図1の表示装置における光検出時の光検出線とA点(光検出線に接続されたトランジスタのゲート)の電位の変化を表す図である。

【図7】図1の表示装置における光検出に関する動作の一例を表す回路図である。 30

【図8】図7に続く動作を表す回路図である。

【図9】図8に続く動作を表す回路図である。

【図10】図9に続く動作を表す回路図である。

【図11】図10に続く動作を表す回路図である。

【図12】図11に続く動作を表す回路図である。

【図13】図3の光検出回路の一変形例の回路図である。

【図14】図13の光検出回路を含む表示装置における光検出に関する動作を表す図である。

【図15】図13の光検出回路の第1変形例の回路図である。

【図16】図13の光検出回路の第2変形例の回路図である。 40

【図17】図13の光検出回路の第3変形例の回路図である。

【図18】参考例に係る入力装置の概略構成図である。

【図19】図18の入力装置に情報を入力する様子を表す図である。

【図20】従来の表示装置の画素の回路図である。

【図21】有機EL素子のV-Ids特性の経年変化を表す図である。

【図22】図20の画素に改良を加えたものの回路図である。

【図23】従来の光検出回路の回路図である。

【図24】図23の光検出回路に改良を加えたものの回路図と、改良の加えられた光検出回路の出力を検出する受光信号処理回路の回路図である。

【図25】図24の光検出回路および受光信号処理回路を含む表示装置における光検出に 50

に関する動作を表す図である。

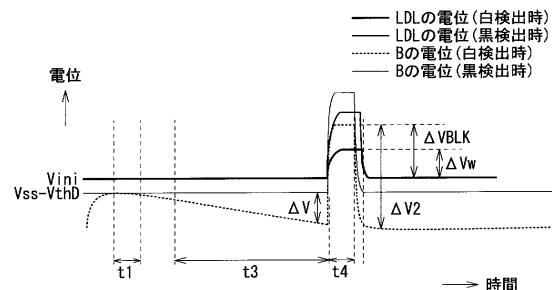

【図26】図24の光検出回路および受光信号処理回路を含む表示装置における光検出時の光検出線とB点(光検出線に接続されたトランジスタのゲート)の電位の変化を表す図である。

【図27】図24の光検出回路および受光信号処理回路を含む表示装置における光検出に関する動作の一例を表す回路図である。

【図28】図27に続く動作を表す回路図である。

【図29】図28に続く動作を表す回路図である。

【図30】図29に続く動作を表す回路図である。

【図31】図30に続く動作を表す回路図である。

10

【発明を実施するための形態】

【0020】

以下、発明を実施するための形態について、図面を参照して詳細に説明する。なお、説明は以下の順序で行う。

### 1. 実施の形態(表示装置)

光検出回路においてトランジスタのドレインとフォトダイオードのアノードとが互いに異なる配線に接続されている例

### 2. 変形例(表示装置)

光検出回路においてトランジスタのドレインとフォトダイオードのアノードとが共通の配線に接続されている例

20

### 3. 参考例(入力装置)

【0021】

<1. 実施の形態>

【構成】

図1は、本発明の一実施の形態に係る表示装置1の全体構成の一例を表したものである。この表示装置1は、表示パネル10と、表示パネル10の周辺に形成された駆動回路20とを備えている。

【0022】

(表示パネル10)

30

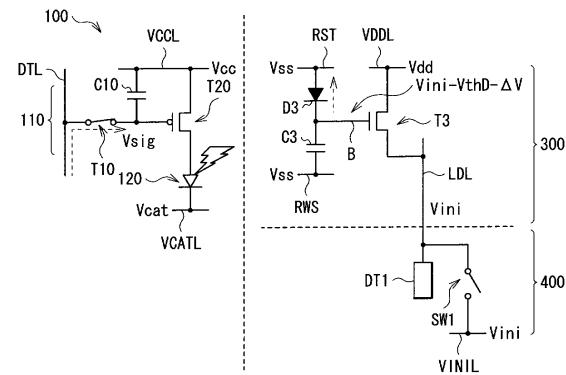

表示パネル10は、複数の画素11を表示パネル10の全面に渡って2次元配置したものである。表示パネル10は、各画素11をアクティブマトリクス駆動することにより、外部から入力された映像信号20Aに基づく画像を表示するものである。各画素11は、例えば、赤色用の画素11Rと、緑色用の画素11Gと、青色用の画素11Bとを含んでいる。

【0023】

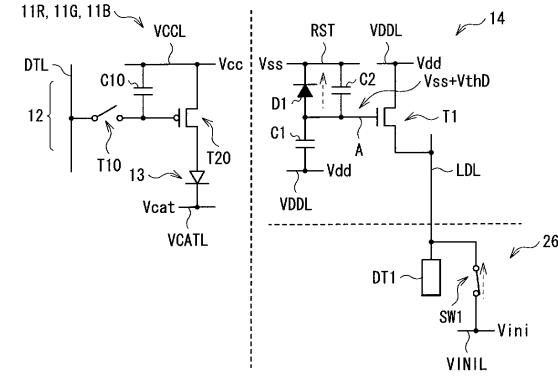

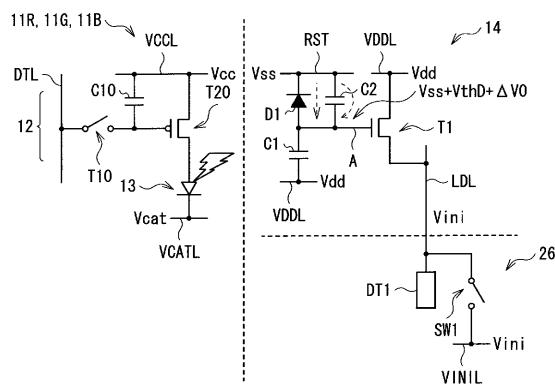

図2は、画素11R, 11G, 11Bの内部構成の一例を表したものである。画素11R, 11G, 11Bは、例えば、図2に示したように、画素回路12と、有機EL素子13R, 13G, 13Bとを有している。有機EL素子13Rは赤色光を発する有機EL素子であり、有機EL素子13Gは緑色光を発する有機EL素子であり、有機EL素子13Bは青色光を発する有機EL素子である。以下では、有機EL素子13R, 13G, 13Bの総称として「有機EL素子13」を用いるものとする。なお、有機EL素子13R, 13G, 13Bは、本発明の「自発光素子」の一具体例に相当する。

40

【0024】

有機EL素子13は、例えば、図示しないが、陽極(アノード)、有機層および陰極(カソード)が順に積層された構成を有している。有機層は、例えば、陽極の側から順に、正孔注入効率を高める正孔注入層と、発光層への正孔輸送効率を高める正孔輸送層と、電子と正孔との再結合による発光を生じさせる発光層と、発光層への電子輸送効率を高める電子輸送層とを積層してなる積層構造を有している。

【0025】

50

画素回路 12 は、例えば、図 2 に示したように、トランジスタ T10, T20 と、保持容量 C10 とを有している。トランジスタ T10 は、信号線 DTL の電圧をサンプリングするとともにトランジスタ T20 のゲートに書き込むものである。トランジスタ T20 は、トランジスタ T10 によって書き込まれた電圧の大きさに応じて有機 EL 素子 13 に流れる電流を制御するものである。保持容量 C10 は、トランジスタ T20 のゲート - ソース間に所定の電圧を保持するものである。トランジスタ T10 は、例えば、n チャネル MOS 型の薄膜トランジスタ (TFT) により形成されている。トランジスタ T20 は、例えば、p チャネル MOS 型の TFT により形成されている。なお、トランジスタ T20 は、n チャネル MOS 型の TFT により形成されていてもよい。

【0026】

10

表示パネル 10 は、行方向に延在する複数の書込線 WSL と、列方向に延在する複数の信号線 DTL と、行方向に延在する複数の電源線 VCCL と、電源線 VCATL を有している。各信号線 DTL と各書込線 WSL の交差点近傍には、画素 11R、画素 11G または画素 11B が設けられている。各信号線 DTL は、後述の信号線駆動回路 23 の出力端 (図示せず) と、トランジスタ T10 のソースまたはドレインとに接続されている。各書込線 WSL は、後述の書込線駆動回路 24 の出力端 (図示せず) と、トランジスタ T10 のゲートに接続されている。各電源線 VCCL は、後述の電源 28 に含まれる固定の電圧 Vcc を出力する電源の出力端 (図示せず) と、トランジスタ T20 のソースまたはドレインに接続されている。電源線 VCATL は、後述の電源 28 において基準電位に相当する電圧 Vcat (例えばグラウンド電位) となっている配線 (図示せず) と、有機 EL 素子 13 のカソードに接続されている。

【0027】

20

トランジスタ T10 のゲートは、書込線 WSL に接続されている。トランジスタ T10 のソースまたはドレインが信号線 DTL に接続され、トランジスタ T10 のソースおよびドレインのうち信号線 DTL に未接続の端子がトランジスタ T20 のゲートに接続されている。トランジスタ T20 のソースまたはドレインが電源線 VCCL に接続され、トランジスタ T20 のソースおよびドレインのうち電源線 VCCL に未接続の端子が有機 EL 素子 13 のアノードに接続されている。保持容量 C10 の一端がトランジスタ T20 のゲートに接続され、保持容量 C10 の他端がトランジスタ T20 のソース (図 2 では電源線 VCCL 側の端子) に接続されている。つまり、保持容量 C10 は、トランジスタ T20 のゲート - ソース間に挿入されている。有機 EL 素子 13 のカソードは、電源線 VCATL に接続されている。

【0028】

30

トランジスタ T10 のドレインは信号線 DTL に接続されており、トランジスタ T10 のソースはトランジスタ T20 のゲートに接続されている。トランジスタ T20 のソースは電源線 VCCL に接続されており、トランジスタ T20 のドレインは有機 EL 素子 13 のアノードに接続されている。有機 EL 素子 13 のカソードは電源線 VCATL に接続されている。

【0029】

40

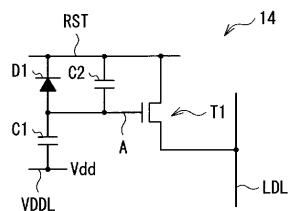

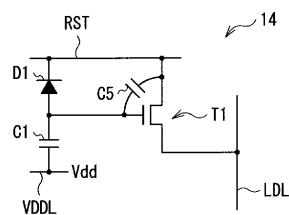

表示パネル 10 は、さらに、画素 11R、画素 11G または画素 11B から発せられた光を検出する複数の光検出回路 14 を有している。表示パネル 10 は、各光検出回路 14 をライン駆動することにより、画素 11R、画素 11G または画素 11B から発せられた光を検出するものである。光検出回路 14 は、画素 11R、画素 11G または画素 11B から発せられた光を検出可能な位置、具体的には、画素 11R、画素 11G または画素 11B に隣接して配置されている。光検出回路 14 は、例えば、画素 11R、画素 11G または画素 11B ごとに 1 つずつ設けられている。なお、光検出回路 14 は、複数の画素 11R、複数の画素 11G または複数の画素 11B ごとに 1 つずつ設けられていてもよい。

【0030】

光検出回路 14 は、例えば、図 3 に示したように、トランジスタ T1 と、フォトダイオード D1 と、容量素子 C1, C2 を有している。なお、容量素子 C1 は、本発明の「第

50

2容量素子」の一具体例に相当し、容量素子C2は、本発明の「第1容量素子」の一具体例に相当する。トランジスタT1は、光検出線LDLへ検出信号を出力するものである。フォトダイオードD1は、画素11R、画素11Gまたは画素11Bから発せられた光を検出するものである。容量素子C1、C2は、制御線RSTの電圧変化に応じてトランジスタT1のゲート電圧を変化させるものである。トランジスタT1は、例えば、nチャネルMOS型のTFTにより形成されている。なお、トランジスタT1は、pチャネルMOS型のTFTにより形成されていてもよい。

【0031】

表示パネル10は、行方向に延在する複数の制御線RSTと、列方向に延在する複数の光検出線LDLと、行方向に延在する複数の電源線VDDLとを有している。なお、電源線VDDLは、本発明の「固定電源線」の一具体例に相当する。各制御線RSTと各光検出線LDLとの交差点近傍に、光検出回路14が設けられている。各制御線RSTは、後述の制御線駆動回路25の出力端(図示せず)と、フォトダイオードD1のカソードおよび容量素子C2の一端とに接続されている。各光検出線LDLは、後述の受光信号処理回路26の出力端(図示せず)と、トランジスタT1ソースまたはドレインに接続されている。各電源線VDDLは、後述の電源28に含まれる固定の電圧Vddを出力する電源の出力端(図示せず)と、トランジスタT1のソースおよびドレインのうち光検出線LDLに未接続の端子および容量素子C1の一端とに接続されている。

【0032】

トランジスタT1のゲートがフォトダイオードD1のアノードと、容量素子C1と容量素子C2との接続点とに接続されている。トランジスタT1のソースまたはドレインが電源線VDDLに接続され、トランジスタT1のソースおよびドレインのうち電源線VDDLに未接続の方が光検出線LDLに接続されている。フォトダイオードD1のカソードが制御線RSTに接続されている。容量素子C1の一端がトランジスタT1のゲートに接続され、容量素子C1の他端が電源線VDDLに接続されている。容量素子C2の一端がトランジスタT1のゲートに接続され、容量素子C2の他端が制御線RSTに接続されている。

【0033】

(駆動回路20)

駆動回路20は、例えば、図1に示したように、タイミング制御回路21、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24および制御線駆動回路25を有している。さらに、駆動回路20は、例えば、図1に示したように、受光信号処理回路26、記憶回路27および電源28を有している。

【0034】

タイミング制御回路21は、映像信号処理回路22、信号線駆動回路23、書込線駆動回路24、制御線駆動回路25、受光信号処理回路26、記憶回路27および電源28が連動して動作するように制御するものである。タイミング制御回路21は、例えば、外部から入力された同期信号20Bに応じて(同期して)、上述した各回路に対して制御信号21Aを出力するようになっている。

【0035】

映像信号処理回路22は、外部から入力されたデジタルの映像信号20Aを補正すると共に、補正した後の映像信号をアナログに変換して信号線駆動回路23に出力するものである。本実施の形態では、映像信号処理回路22は、記憶回路27から入力される補正係数26Aを用いて映像信号20Aを補正するようになっている。映像信号処理回路22は、例えば、表示装置1の電源投入時に、記憶回路27から補正係数26Aを読み出しておき、読み出した補正係数26Aを映像信号20Aに掛け合わせることにより、映像信号20Aを補正するようになっている。このとき、映像信号処理回路22は、外部から入力された(補正前の)映像信号20Aの階調の大きさに応じて補正係数26Aに重み付けを行い、重み付けされた後の補正係数26Aを用いて映像信号20Aを補正するようになっていてもよい。なお、例えば、階調の大きさと、重み付けの度合いとの対応関係をまとめた

10

20

30

40

50

テーブルを記憶回路 27 などにあらかじめ記憶させておき、映像信号処理回路 22 が、例えば、表示装置 1 の電源投入時に、そのテーブルを記憶回路 27 から読み出すようにしてもよい。

【0036】

なお、記憶回路 27 から補正係数 26A を読み出すタイミングは、表示装置 1 の電源投入時だけに限られるものではない。例えば、映像を表示している期間中に記憶回路 27 に格納されている補正係数 26A が更新される場合には、映像信号処理回路 22 は、その都度、記憶回路 27 から補正係数 26A を読み出すようになっていてもよい。

【0037】

信号線駆動回路 23 は、映像信号処理回路 22 から入力されたアナログの映像信号を、制御信号 21A の入力に応じて（同期して）各信号線 DTL に出力するものである。書込線駆動回路 24 は、制御信号 21A の入力に応じて（同期して）、複数の書込線 WSL を所定の単位ごとに（例えば 1 本ずつ）順次選択するものである。

【0038】

制御線駆動回路 25 は、例えば、制御信号 21A の入力に応じて（同期して）、複数の制御線 RST を所定の単位ごとに（例えば 1 本ずつ）順次選択するものである。なお、制御線駆動回路 25 が、複数の制御線 RST を複数本ずつ順次選択する場合には、複数の光検出回路 14 からの検出信号が 1 本の光検出線 LDL に併せて出力されることになる。

【0039】

制御線駆動回路 25 は、3 種類の電圧を含む制御パルスを選択信号として制御線 RST に出力するものである。具体的には、制御線駆動回路 25 は、フォトダイオード D1 に順バイアスを印加するとともにトランジスタ T1 をオフ状態とする第 1 電圧（電圧 Vss）と、フォトダイオード D1 に逆バイアスを印加するとともにトランジスタ T1 をオフ状態とする第 2 電圧（電圧 Vin）と、フォトダイオード D1 に逆バイアスを印加するとともにトランジスタ T1 をオン状態とする第 3 電圧（電圧 Vdd2）とを含む制御パルスを選択信号として制御線 RST に出力するようになっている。ここで、第 1 電圧は、第 2 電圧および第 3 電圧よりも低い電圧であり、トランジスタ T1 のゲート電圧を初期化する電圧である。第 2 電圧は、第 1 電圧よりも大きく第 3 電圧よりも小さい電圧であり、光検出時においてフォトダイオード D1 に与えられる電圧である。第 3 電圧は、第 1 電圧および第 2 電圧よりも高い電圧であり、検出信号を光検出線 LDL に出力するための電圧である。

【0040】

受光信号処理回路 26 は、例えば、図 4 に示したように、電圧検出部 DT1 と、スイッチ SW1 とを有している。電圧検出部 DT1 は、光検出線 LDL の電圧を検出するものであり、光検出線 LDL に接続されている。スイッチ SW1 は光検出線 LDL の電圧を初期化するものである。スイッチ SW1 の一端が光検出線 LDL に接続され、スイッチ SW1 の他端が電源線 VINIL に接続されている。電源線 VINIL は、後述の電源 28 に含まれる固定の電圧 Vin を出力する電源の出力端（図示せず）に接続されている。

【0041】

受光信号処理回路 26 は、さらに、図示しないが、光検出回路 14 から入力された受光信号 14A（電気信号）に基づいて補正係数 26A を導出し、導出した補正係数 26A を、制御信号 21A の入力に応じて（同期して）記憶回路 27 に出力する信号処理回路を有している。

【0042】

記憶回路 27 は、受光信号処理回路 26 から入力された補正係数 26A を格納するものである。記憶回路 27 は、格納した補正係数 26A を、映像信号処理回路 22 によって読み出すことができるようになっている。

【0043】

電源 28 は、表示パネル 10 に対して固定の電圧を供給するものである。電源 28 は、例えば、固定の電圧 Vcc を出力する電源や、固定の電圧 Vdd を出力する電源、固定の

10

20

30

40

50

電圧  $V_{ini}$  を出力する電源、基準電位に相当する電圧  $V_{cat}$  となっている配線などを含んで構成されている。

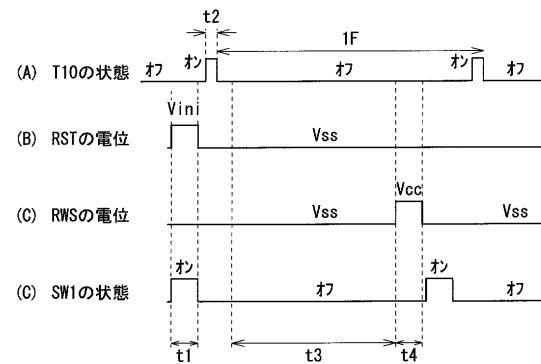

#### 【0044】

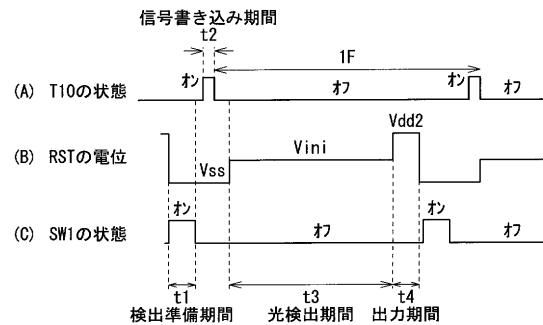

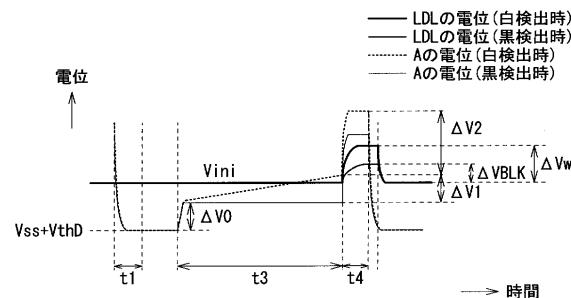

次に、図5～図12を参照しつつ、光検出回路14の動作について説明する。図5～図12は、光検出回路14の動作の一例を示したものである。図5、図6では、一例として光検出周期をほぼ1Fとしている。ここで、図5(A)は、図2の画素回路12内のトランジスタT10のオンオフの状態を表している。図5(B)は、図3の光検出回路14内の制御線RSTの電位を表している。図5(C)は、図4の受光信号処理回路26内のスイッチSW1の電位を表している。図6は、白検出時および黒検出時における光検出線LDLの電位とトランジスタT1のゲート(A点)の電位を表している。図7～図12は、光検出回路14の一連の動作を、画素11R, 11G, 11Bの動作と共に表したものである。

10

#### 【0045】

まず、図7に示したように、スイッチSW1をオンして、光検出線LDLの電位を  $V_{ini}$  にする。さらに、制御線RSTの電位を初期化電位である  $V_{ss}$  にする。これにより、検出準備期間  $t_1$  に入り、トランジスタT1のゲート電位が  $V_{ss} + V_{thD}$  ( $V_{thD}$  はフォトダイオードD1の閾値電圧)よりも大きければ図7のように電流が流れ、トランジスタT1のゲート電位は  $V_{ss} + V_{thD}$  という電位に初期化される。この時、トランジスタT1のゲート-ソース間電位は  $V_{ss} + V_{thD} - V_{ini}$  ( $< V_{th1}$ ) ( $V_{th1}$  はトランジスタT1の閾値電圧)となり、トランジスタT1はオフ状態となっている。一定時間経過後、制御線RSTを  $V_{ss}$  にしたままで、スイッチSW1をオフする。

20

#### 【0046】

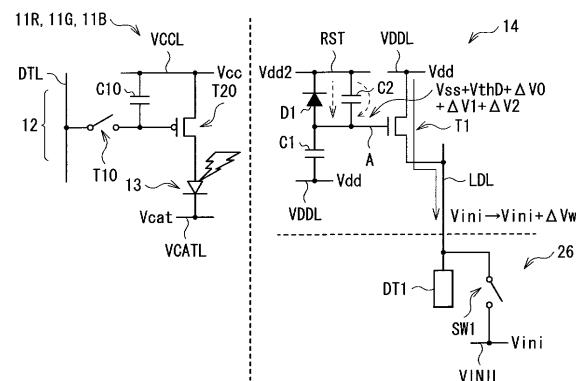

次に、図8に示したように、トランジスタT10をオンして画素回路12内のトランジスタT20のゲートに信号電圧  $V_{sig}$  を入力し、信号書き込み期間  $t_2$  に入る。この動作により、トランジスタT20のゲート-ソース間電圧はトランジスタT20の閾値電圧以上となり、トランジスタT20を介して有機EL素子13に電流が流れ、有機EL素子13は発光を開始する。このとき、フォトダイオードD1の端子間電圧は小さいので、更に次の動作である制御線RSTの電位を  $V_{ss}$  から  $V_{ini}$  へ変化させる動作までの時間を短くすれば、フォトダイオードD1にリーキ電流はほとんど流れない。

30

#### 【0047】

続いて、トランジスタT10をオフしたのち、一定時間経過後、図9に示したように、制御線RSTの電位を  $V_{ss}$  から光検出電位である  $V_{ini}$  に変化させ、光検出期間  $t_3$  に入る。これにより、制御線RSTの電位変化が容量素子C2を介してトランジスタT1のゲートに入力され、トランジスタT1のゲート電位は  $V_{ss} + V_{thD} + V_0$  という電位に増加する。その結果、フォトダイオードD1には  $V_{ss} + V_{thD} + V_0 - V_{ini}$  という電位差が発生するので、光を受光することで図9に示したように制御線RSTからトランジスタT1のゲートにリーキ電流が流れ。これにより、トランジスタT1のゲート電位は徐々に増加する。一定時間経過後、図10に示したように、トランジスタT1のゲート電位は  $V_{ss} + V_{thD} + V_0 + V_1$  という値となる。この時、トランジスタT1のゲート-ソース間電圧がトランジスタT1の閾値電圧よりも小さいので、トランジスタT1は依然オフ状態となり、光検出線LDLの電位は  $V_{ini}$  のままである。

40

#### 【0048】

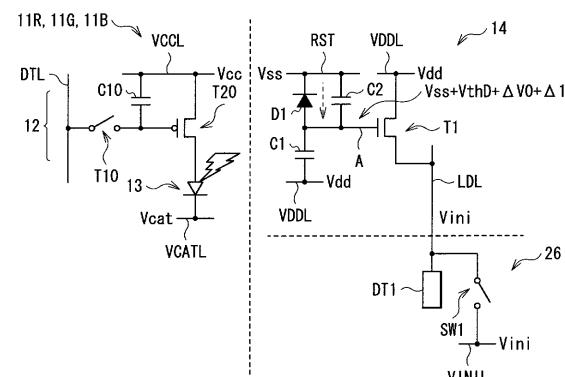

次に、図11に示したように、制御線RSTの電位を  $V_{ini}$  から  $V_{dd2}$  に増加させ、出力期間  $t_4$  に入る。これにより、制御線RSTの電位変化が容量素子C2を介してトランジスタT1のゲートに入力され、トランジスタT1のゲート電位は  $V_{ini} + V_{thD} + V_1 + V_2$  という電位に増加する。この時、トランジスタT1のゲート-ソース電圧 ( $V_2 + V_{ss} + V_{thD} + V_0 + V_1 - V_{ini}$ ) がトランジスタT1の閾値電圧以上であれば、図11に示したように電源線VDDLから電流が流れ、光検出線LDLの電位は上昇を開始する。そして、一定時間経過後、光検出線LDLは  $V_{ini} + V_w$  という電位となる。

50

## 【0049】

その後、図12に示したように、制御線RSTの電位をVdd2からVssに変化させ、出力期間t4を終了する。これにより、再び、制御線RSTの電位変化が容量素子C2を介してトランジスタT1のゲートに入力され、トランジスタT1のゲート電位はVss + VthDとなる。その結果、再び、トランジスタT1はオフ状態となる。最後に、図12に示したように、スイッチSW1をオンして、光検出線LDLの電位をVin1とする。

## 【0050】

## [効果]

次に、本実施の形態の光検出回路14の効果について、比較例と対比して説明する。

10

## 【0051】

有機EL素子は、通電する電流量に応じて素子が劣化し、発光効率が低下するという特徴を有している。そのため、有機EL素子を表示装置の画素として用いた場合には、画素ごとに劣化の状況が異なることがある。例えば、時刻や表示チャンネルなどの情報が長時間、同じ場所に高輝度で表示されていた場合には、その部分の画素だけ劣化が早まる。その結果、劣化の早まった画素を含む部分に高輝度の映像が表示された場合には、劣化の早まった画素の部分だけが暗く表示される焼き付きという現象が生じてしまう。この焼き付きは非可逆性であることから、一旦、焼き付きが生じると、焼き付きが消えることはない。

## 【0052】

20

有機EL素子に流す電流量を補正することにより、焼き付きを改善する手法は、今までに多数提案されている。例えば、画素回路に隣接して光検出回路を設けるとともに、光検出回路の出力に基づいて信号線の電圧を補正する信号処理回路を設けることが提案されている（特許文献1参照）。特許文献1に記載の方策では、電流変化を的確に検知するためには、電流変化の大きなオフ領域（印加電圧：負で0V付近）を用いることが必要となる。ところが、このときの電流値は大きくなっているとはいっても、オン電流と比較すると非常に小さい。そのため、輝度変化の検出精度が十分に得られないという問題があった。

## 【0053】

精度よく輝度変化を検出するためには、光検出線LDLの寄生容量を充電する時間を長くすることが必要となり、実際には、充電期間を1フレーム以上にしないと、精度良く電流変化を検出することは難しい。そこで、フォトダイオードD2のサイズを大きくして電流量を大きくすることが考えられる。しかし、フォトダイオードD2のサイズが大きくなると、その分だけ光検出回路200の占有面積も大きくなってしまう。

30

## 【0054】

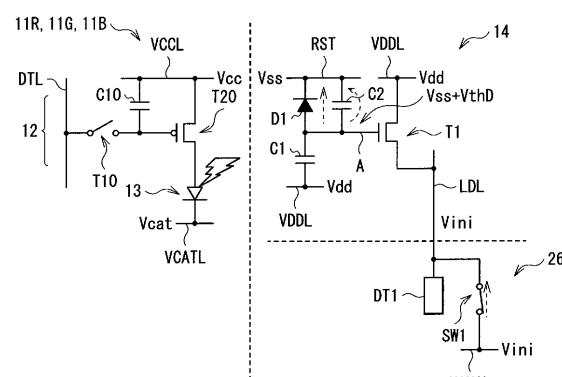

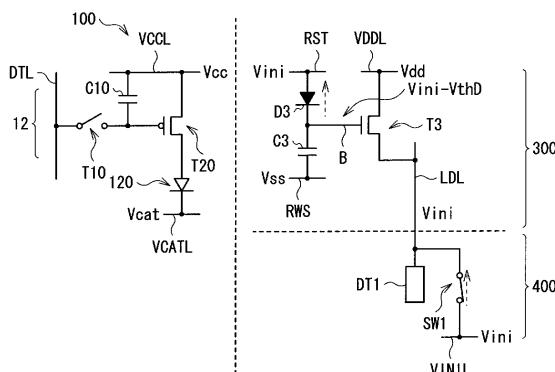

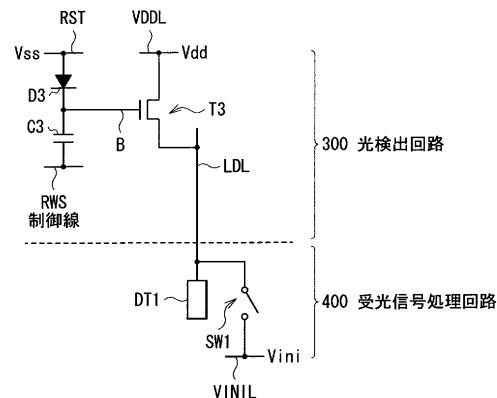

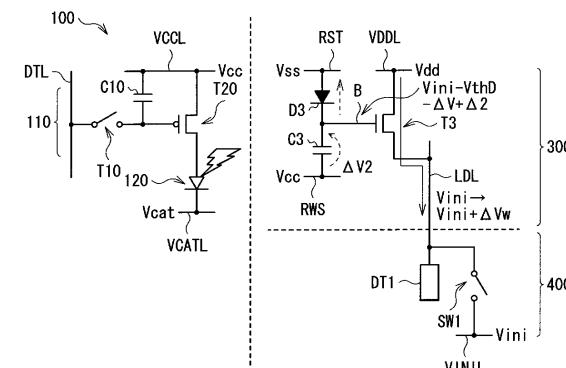

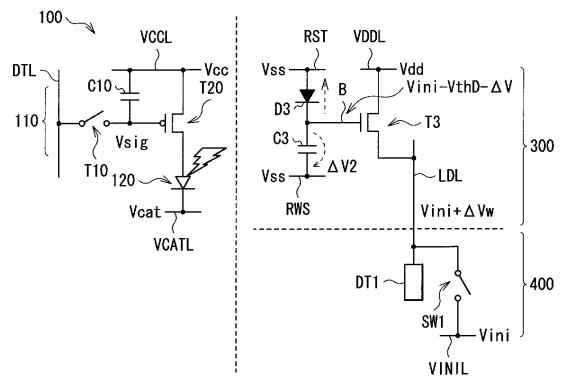

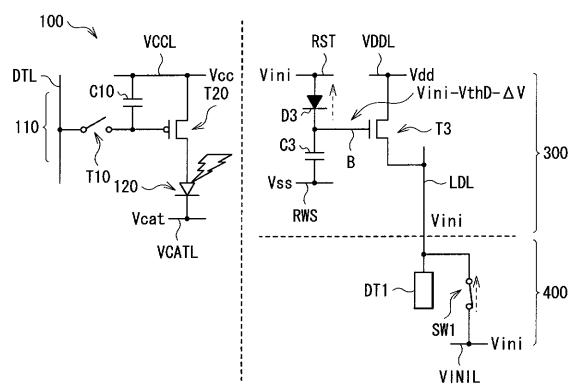

そのような問題に対して、例えば、図24に示した光検出回路300および受光信号処理回路400を用いることが考えられる。光検出回路300は、検出信号を出力するトランジスタT3と、光を検出するフォトダイオードD3と、容量素子C3とを有している。トランジスタT3は光検出線LDLと電源線VDDLとの間に設けられている。フォトダイオードD3は、トランジスタT3のゲートと制御線RSTとの間に、アノードをトランジスタT3のゲート側に向けた状態で設けられている。容量素子C3は、トランジスタT3のゲートと制御線RWSとの間に設けられている。受光信号処理回路400は、光検出線LDLに出力された電圧を検出する電圧検出部DT1と、光検出線LDLに接続されたスイッチSW1と、スイッチSW1を介して光検出線LDLに接続された電源線VINILとを有している。電圧検出部DT1は、図示しないが、検出電圧に対応する信号を信号処理回路に出力するようになっている。信号処理回路は、電圧検出部DT1から入力された信号に基づいて、信号線DTLに出力する電圧の大きさを補正するようになっている。

40

## 【0055】

次に、図25～図31を参照しつつ、光検出回路300の動作について説明する。図25～図31は、光検出回路300の動作の一例を示したものである。図25、図26では、一例として光検出周期をほぼ1Fとしている。ここで、図25（A）は、図20の画素

50

100内のトランジスタT10のオンオフの状態を表している。図25(B)は、図24の光検出回路300内の制御線RSTの電位を表している。図25(C)は、図24の光検出回路300内の制御線RWSの電位を表している。図25(D)は、図24の受光信号処理回路400内のスイッチSW1の電位を表している。図26は、白検出時および黒検出時における光検出線LDLの電位とトランジスタT3のゲート(B点)の電位を表している。図27～図31は、光検出回路300の一連の動作を、画素100の動作と共に表したものである。

#### 【0056】

まず、図27に示したように、制御線RWSをVssにするとともに、制御線RSTをViniにする。さらに、スイッチSW1をオンして、光検出線LDLの電位をViniにする。これにより、検出準備期間t1に入り、トランジスタT3のゲート電位がVini-VthD(VthDはフォトダイオードD3の閾値電圧)よりも小さければ図26のように電流が流れ、トランジスタT3のゲート電位はVini-VthDという電位に初期化される。この時、トランジスタT3のゲート-ソース間電位は-VthDとなり、トランジスタT3はオフ状態となっている。一定時間経過後、制御線RSTをVssにしたままで、スイッチSW1をオフする。

#### 【0057】

次に、図28に示したように、トランジスタT10をオンして画素100内のトランジスタT20のゲートに信号電圧Vsigを入力し、信号書き込み期間t2に入る。この動作により、トランジスタT20のゲート-ソース間電圧はトランジスタT20の閾値電圧以上となり、トランジスタT20を介して有機EL素子120に電流が流れ、有機EL素子120は発光を開始する。これにより、フォトダイオードD3は電位差が発生している状態で光を検出し、図28に示したように、トランジスタT3のゲートから制御線RSTにリーク電流が流れ、トランジスタT3のゲート電位は徐々に低下する。続いて、トランジスタT10をオフしたのち、光検出期間t3に入り、一定時間経過後、トランジスタT3のゲート電位はVini-VthD-Vという電位となる。この時、トランジスタT3のゲート-ソース間電位は-VthD-Vとなるため、トランジスタT3は依然オフ状態となり、光検出線LDLの電位はViniのままである。

#### 【0058】

次に、図29に示したように、制御線RWSの電位をVssからVccに増加させ、出力期間t4に入る。これにより、制御線RWSの電位変化量が容量素子C3を介してトランジスタT3のゲートに入力され、トランジスタT3のゲート電位はVini-VthD-V+V2という電位に増加する。この時、トランジスタT3のゲート-ソース電圧(V2-V-VthD)がトランジスタT3の閾値電圧以上であれば、図26に示したように電源線VDDLから電流が流れ、光検出線LDLの電位は上昇を開始する。そして、一定時間経過後、光検出線LDLはVini+Vwという電位となる。

#### 【0059】

その後、図30に示したように、制御線RWSの電位をVccからVssに変化させ、出力期間t4を終了する。これにより、再び、制御線RWSの電位変化が容量素子C3を介してトランジスタT3のゲートに入力され、トランジスタT3のゲート電位はVini-VthD-Vとなる。その結果、再び、トランジスタT3はオフ状態となる。最後に、図31に示したように、スイッチSW1をオンして、光検出線LDLの電位をViniとする。

#### 【0060】

次に、上記の一連の動作を白発光検出時と黒発光検出時で行った場合について考える。一般に、光検出素子の受光量が多いほど、光検出素子に流れる電流量は多くなる。そのため、白発光受光時におけるトランジスタT3のゲート電位の変化量の方が、黒発光受光時におけるトランジスタT3のゲート電位の変化量よりも大きくなる。これにより、出力時におけるトランジスタT3のゲート電位は黒発光受光時の方が大きくなり、最終的に光検出線LDLには、黒発光受光時の方が白発光受光時に比較して大きな電圧が出力される。

10

20

30

40

50

従って、精度良く電流変化を検出することができ、焼き付き等の画質不良を改善することができる。

【0061】

ところで、上記の光検出回路300では、電源線VDDL、制御線RST, RWSおよび光検出線LDLの計4本の配線が必要である。一般に、電源線や制御線などの配線は表示パネルの垂直方向もしくは水平方向に延伸している。そのため、それらの本数が多いと、配線間ショート等などの、歩留まりを低下させる問題が生じやすくなる。

【0062】

次に、本実施の形態の光検出回路14において、上記の一連の動作を白発光検出時と黒発光検出時で行った場合について考える。本実施の形態においても、上記の比較例と同様、白発光受光時におけるトランジスタT1のゲート電位の変化量の方が、黒発行受光時におけるトランジスタT1のゲート電位の変化量よりも大きくなる。これにより、出力時におけるトランジスタT1のゲート電位は黒発光受光時の方が大きくなり、最終的に光検出線LDLには、黒発光受光時の方が白発光受光時に比較して大きな電圧が出力される。従って、本実施の形態では、精度良く電流変化を検出することができ、焼き付き等の画質不良を改善することができる。

【0063】

また、本実施の形態では、カソードが制御線RST側を向くようにフォトダイオードD1が配置されている。これにより、1本の制御線RSTに上述の制御パルスを印加するだけで、光検出線LDLに接続されたトランジスタのT1ゲートに、画素11R, 11G, 11Bから発せられた光の光量の大きさに応じた電圧をオン電圧として印加することが可能となる。つまり、1本の制御線RST、1本の電源線VDDLおよび1本の光検出線LDLの計3本の配線だけで、画素11R, 11G, 11Bから発せられた光の光量の大きさに応じた電圧を得ることが可能となる。従って、図24に示した光検出回路300よりも1本少ない配線数で焼き付きを低減することができる。

【0064】

また、本実施の形態では、図24に示した光検出回路300よりも1本少ない配線で、光検出回路14を駆動することができることから、光検出回路300と比べて、配線間ショート等などの、歩留まりを低下させる問題が生じる可能性を低くすることができる。

【0065】

また、本実施の形態において、複数の制御線RSTが複数本ずつ順次選択される場合には、複数の光検出回路14からの検出信号が1本の光検出線LDLに併せて出力されることになる。なお、複数の制御線RSTが複数本ずつ順次選択される場合としては、例えば、複数の制御線RSTが同一タイミングで選択される場合や、複数の制御線RSTの出力期間がオーバーラップしている場合などがある。これにより、一度に使用されるフォトダイオードD1の数を増やすことができるので、光検出精度を向上させることができるとなる。

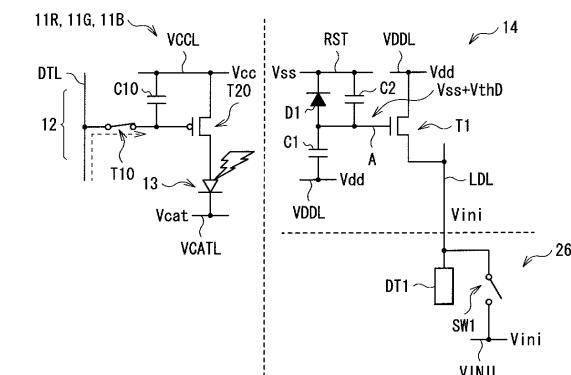

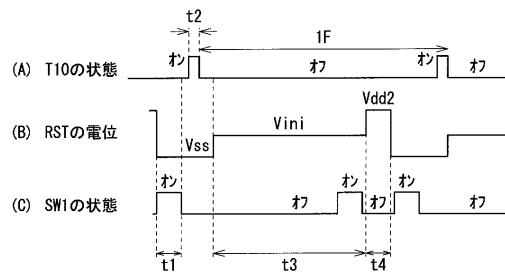

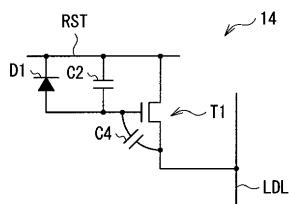

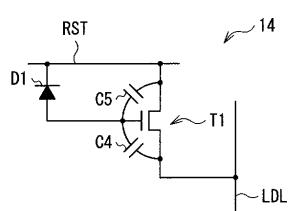

【0066】

<2. 変形例>

図13は、上記実施の形態に係る光検出回路14の一変形例を表したものである。本変形例に係る光検出回路14では、トランジスタT1に対して電源線VDDLの代わりに、制御線RSTが接続されている。本変形例に係る光検出回路14を含む表示装置1の基本的な動作は、上記実施の形態に係る光検出回路14を含む表示装置1の動作と同じである。つまり、制御線RSTをVssとしてトランジスタT1のゲート電位を初期化し、次にVinjとすることでトランジスタT1をオフした状態でフォトダイオードD1に電位差を発生させ光検出が行われる。最後に、制御線RSTの電位をVdd2とすることでトランジスタT1をオン状態とし、検出信号を光検出線LDLに出力させる。ただし、本変形例では、トランジスタT1のゲート電圧の変動が光検出線LDLに入力されてしまうので、例えば、図14に示したように、出力期間t4の直前に光検出線LDLの電位をVinjに初期化する必要がある。

10

20

30

40

50

## 【0067】

本変形例では、上記実施の形態と同様、1本の制御線RST、1本の電源線VDDLおよび1本の光検出線LDLの計3本の配線だけで、画素11R, 11G, 11Bから発せられた光の光量の大きさに応じた電圧を得ることが可能となる。従って、図22に示した光検出回路300よりも1本少ない配線数で焼き付きを低減することができる。また、本変形例では、上記実施の形態と同様、図24に示した光検出回路300よりも1本少ない配線で、光検出回路14を駆動することができることから、光検出回路300と比べて、配線間ショート等などの、歩留まりを低下させる問題が生じる可能性を低くすることができる。また、本変形例においても、複数の制御線RSTが複数本ずつ順次選択される場合には、光検出精度を向上させることが可能となる。

10

## 【0068】

なお、本変形例において、例えば、図15に示したように、容量素子C1をなくし、トランジスタT1のゲート-ソース間の寄生容量C4を容量素子C1と同様に機能させるようにしてもよい。また、本変形例において、例えば、図16に示したように、容量素子C2をなくし、トランジスタT1のゲート-ドレイン間の寄生容量C5を容量素子C2と同様に機能させるようにしてもよい。また、本変形例において、例えば、図17に示したように、容量素子C1, C2をなくし、トランジスタT1のゲート-ソース間の寄生容量C4を容量素子C1と同様に機能させるとともに、トランジスタT1のゲート-ドレイン間の寄生容量C5を容量素子C2と同様に機能させるようにしてもよい。

20

## 【0069】

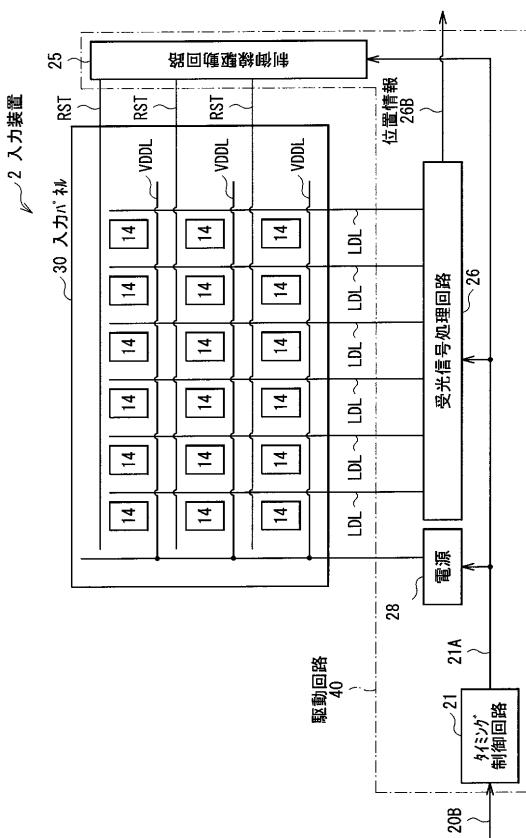

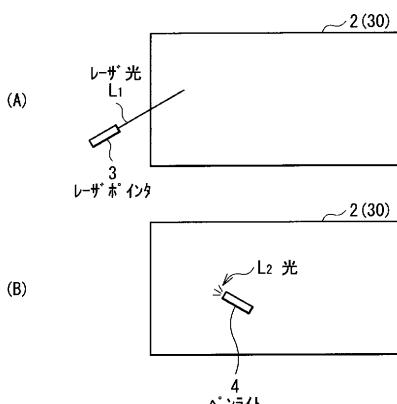

## &lt;3. 参考例&gt;

図18は、参考例に係る入力装置2の全体構成の一例を表したものである。この入力装置2は、入力パネル30と、入力パネル30の周辺に形成された駆動回路40とを備えている。

## 【0070】

## (入力パネル30)

入力パネル30は、複数の光検出回路14を入力パネル30の全面に渡って2次元配置したものである。入力パネル30は、各光検出回路14をライン駆動することにより、外部から入力された映像信号20Aに基づく画像を表示するものである。光検出回路14は、例えば、図3、図13、図15、図16または図17に示した構成となっている。

30

## 【0071】

入力パネル30は、行方向に延在する複数の制御線RSTと、列方向に延在する複数の光検出線LDLと、行方向に延在する複数の電源線VDDLとを有している。各制御線RSTと各光検出線LDLとの交差点近傍に、光検出回路14が設けられている。各制御線RSTは、光検出回路14が図3に示した構成となっている場合には、制御線駆動回路25の出力端(図示せず)と、フォトダイオードD1のカソードおよび容量素子C2の一端とに接続されている。光検出回路14が図13、図15、図16または図17に示した構成となっている場合には、各制御線RSTは、制御線駆動回路25の出力端(図示せず)と、フォトダイオードD1のカソードおよび容量素子C2の一端と、トランジスタT1のソースおよびドレインのうち光検出線LDLに未接続の端子に接続されている。

40

## 【0072】

各光検出線LDLは、受光信号処理回路26の出力端(図示せず)と、トランジスタT1ソースまたはドレインに接続されている。各電源線VDDLは、光検出回路14が図3に示した構成となっている場合には、電源28に含まれる固定の電圧Vddを出力する電源の出力端(図示せず)と、トランジスタT1のソースおよびドレインのうち光検出線LDLに未接続の端子および容量素子C1の一端とに接続されている。光検出回路14が図13、図15、図16または図17に示した構成となっている場合には、各電源線VDDLは、電源28に含まれる固定の電圧Vddを出力する電源の出力端(図示せず)と、容量素子C1の一端とに接続されている。

## 【0073】

50

## ( 駆動回路 40 )

駆動回路 40 は、例えば、図 18 に示したように、タイミング制御回路 21、制御線駆動回路 25、受光信号処理回路 26 および電源 28 を有している。

## 【 0074 】

タイミング制御回路 21 は、制御線駆動回路 25、受光信号処理回路 26 および電源 28 が連動して動作するように制御するものである。タイミング制御回路 21 は、例えば、外部から入力された同期信号 20B に応じて（同期して）、上述した各回路に対して制御信号 21A を出力するようになっている。

## 【 0075 】

10

制御線駆動回路 25 は、例えば、制御信号 21A の入力に応じて（同期して）、複数の制御線 RST を所定の単位ごとに（例えば 1 本ずつ）順次選択するものである。なお、制御線駆動回路 25 が、複数の制御線 RST を複数本ずつ順次選択する場合には、複数の光検出回路 14 からの検出信号が 1 本の光検出線 LDD に併せて出力されることになる。

## 【 0076 】

制御線駆動回路 25 は、上記実施の形態と同様、3 種類の電圧を含む制御パルスを選択信号として制御線 RST に出力するものである。具体的には、制御線駆動回路 25 は、フォトダイオード D1 に順バイアスを印加するとともにトランジスタ T1 をオフ状態とする第 1 電圧と、フォトダイオード D1 に逆バイアスを印加するとともにトランジスタ T1 をオフ状態とする第 2 電圧と、フォトダイオード D1 に逆バイアスを印加するとともにトランジスタ T1 をオン状態とする第 3 電圧とを含む制御パルスを選択信号として制御線 RST に出力するようになっている。

20

## 【 0077 】

受光信号処理回路 26 は、例えば、図 4 に示したように、電圧検出部 DT1 と、スイッチ SW1 とを有している。受光信号処理回路 26 は、さらに、図示しないが、光検出回路 14 から入力された受光信号 14A（電気信号）に基づいて、入射光によって形成された発光スポットの入力パネル 30 上の位置を導出し、導出した位置情報 26B を、制御信号 21A の入力に応じて（同期して）外部に出力する信号処理回路を有している。

## 【 0078 】

30

電源 28 は、入力パネル 30 に対して固定の電圧を供給するものである。電源 28 は、例えば、固定の電圧 Vdd を出力する電源などを含んで構成されている。

## 【 0079 】

次に、図 19 を参照しつつ、入力装置 2 の動作について説明する。図 19 (A) は、入力装置 2 の入力パネル 30 に対して、レーザポインタ 3 のレーザ光 L1 を照射することにより、入力装置 2 に所定の情報を入力している様子を模式的に表したものである。図 19 (B) は、入力装置 2 の入力パネル 30 に、先端だけが光るペンライト 4 の先端を接触させるとともに、入力パネル 30 に対してペンライト 4 の光 L2 を照射することにより、入力装置 2 に所定の情報を入力している様子を模式的に表したものである。入力装置 2 に入力する所定の情報としては、例えば、文字、記号、または画像などが挙げられる。

## 【 0080 】

40

本参考例では、レーザポインタ 3 やペンライト 4 などで入力装置 2 の入力パネル 30 を照射し、入力パネル 30 に形成された発光スポットを入力パネル 30 の表面で動かすことにより、発光スポットの位置情報 26B が output される。そして、この位置情報 26B を図示しない情報処理装置で蓄積することにより、例えば、文字、記号、または画像などの情報が得られる。

## 【 0081 】

本参考例において、入射光を検出するための解像度が、入力パネル 30 に含まれる光検出回路 14 の総数（解像度）よりも小さくても問題ない場合には、複数の制御線 RST を複数本ずつ順次選択することも可能である。なお、複数の制御線 RST を複数本ずつ順次選択する方法としては、例えば、複数の制御線 RST を同一タイミングで選択したり、複

50

数の制御線 R S T の出力期間をオーバーラップさせたりする方法がある。このようにした場合には、複数の光検出回路 1 4 からの検出信号が 1 本の光検出線 L D L に併せて出力されることになるので、一度に使用されるフォトダイオード D 1 の数を増やすことができ、光検出精度を向上させることが可能となる。

## 【符号の説明】

〔 0 0 8 2 〕

1 ... 表示装置、2 ... 入力装置、3 ... レーザポインタ、4 ... ペンライト、10 ... 表示パネル、11, 11R, 11G, 11B, 100 ... 画素、12, 110 ... 画素回路、13, 13R, 13G, 13B, 120 ... 有機EL素子、14, 200, 300 ... 光検出回路、20, 40 ... 駆動回路、20A ... 映像信号、20B ... 同期信号、21 ... タイミング制御回路、21A ... 制御信号、22 ... 映像信号処理回路、23 ... 信号線駆動回路、24 ... 書込線駆動回路、25 ... 制御線駆動回路、26, 400 ... 受光信号処理回路、26A ... 補正係数、26B ... 位置情報、27 ... 記憶回路、28 ... 電源、28 ... 電源、30 ... 入力パネル、C1, C2, C3 ... 容量素子、C4, C5 ... 寄生容量、C10 ... 保持容量、D1, D2, D10 ... フォトダイオード、DT1 ... 電圧検出部、DTL ... 信号線、Ids ... 電流、L1 ... レーザ光、L2 ... 光、LDL ... 光検出線、RST, RWS ... 制御線、SW1 ... スイッチ、t1 ... 検出準備期間、t2 ... 信号書き込み期間、t3 ... 光検出期間、t4 ... 出力期間、T1 ... トランジスタ、T10, T20 ... トランジスタ、Vcat, Vcc, Vdd, Vin ... 電圧、VCATL, VCCCL, VDDL, VINIT ... 電源線。

( 1 )

〔 図 2 〕

【図3】

【 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

【図15】

【 図 1 8 】

### 【図16】

【図17】

【図19】

【图 20】

【図 2 1】

【図 2 2】

【図 2 3】

【図 2 6】

【図 2 7】

【図 2 4】

【図 2 5】

【図 2 8】

【図 2 9】

【図30】

【図31】

---

フロントページの続き

(56)参考文献 特表2009-540628(JP,A)

特開2007-096387(JP,A)

特開2009-239442(JP,A)

特開平11-214738(JP,A)

国際公開第2010/140466(WO,A1)

(58)調査した分野(Int.Cl., DB名)

G01J1/00-1/60

H04N5/335

H01L27/146

G09G3/20

G09G3/30