## (12) 发明专利

(10) 授权公告号 CN 110398769 B

(45) 授权公告日 2024.03.22

(21) 申请号 201910645070.5

CN 1328701 A, 2001.12.26

(22) 申请日 2009.06.09

DE 102006033716 A1, 2008.02.14

(65) 同一申请的已公布的文献号

JP 2001318153 A, 2001.11.16

申请公布号 CN 110398769 A

JP 2006059901 A, 2006.03.02

(43) 申请公布日 2019.11.01

JP H05326572 A, 1993.12.10

(30) 优先权数据

US 2001038076 A1, 2001.11.08

08158304.9 2008.06.16 EP

US 2006056581 A1, 2006.03.16

(62) 分案原申请数据

US 2006113622 A1, 2006.06.01

200980122524.5 2009.06.09

US 2007003006 A1, 2007.01.04

(73) 专利权人 皇家飞利浦电子股份有限公司

US 2007235654 A1, 2007.10.11

地址 荷兰艾恩德霍芬

US 6069362 A, 2000.05.30

(72) 发明人 G·福格特米尔 C·赫尔曼

US 6236051 B1, 2001.05.22

K·J·恩格尔

CN 101002109 A, 2007.07.18

(74) 专利代理机构 永新专利商标代理有限公司

JP 2003004855 A, 2003.01.08

72002

CN 101010806 A, 2007.08.01

专利代理人 孟杰雄

GB 9912967 D0, 1999.08.04

(51) Int.Cl.

CN 102183777 A, 2011.09.14

G01T 1/29 (2006.01)

US 2006214109 A1, 2006.09.28

G01T 7/00 (2006.01)

US 2006289777 A1, 2006.12.28

(续)

(56) 对比文件

WO 2008004547 A1, 2008.01.10

CN 101030590 A, 2007.09.05

JP 2003086826 A, 2003.03.20

US 2003178570 A1, 2003.09.25

审查员 吴波

权利要求书1页 说明书5页 附图2页

(54) 发明名称

10

辐射探测器和制造辐射探测器的方法

(57) 摘要

3

本发明涉及一种辐射探测器(10)，包括像素(1)的阵列，其中，每个像素(1)包括用于将入射辐射转换成电信号的半导体材料(4)的转换层，并且其中，每个像素(10)被至少部分填充有阻隔材料的沟槽(3)围绕，所述阻隔材料吸收所述入射辐射生成的光子的至少一部分。本发明还涉及一种制造这种辐射探测器(10)的方法。

CN 110398769 B

[转续页]

[接上页]

(56) 对比文件

郑健;王立强;邢桂来.0.4mm像素X射线阵列探测器的设计.核电子学与探测技术.2007,(第04期),第680-682页.

顾嘉辉,王纳秀.CCD X射线探测器及其在同步辐射中的应用.物理.1997,(第11期),第683-

688页.

郑健;王立强;邢桂来.0.4mm像素X射线阵列探测器的设计.核电子学与探测技术.2007,(第04期),第680-682页.

顾嘉辉,王纳秀.CCD X射线探测器及其在同步辐射中的应用.物理.1997,(第11期),四683-688页.

1. 一种辐射探测器(10),包括:

像素(1)的阵列,其中,每个像素(1)包括:

用于将入射辐射转换成电信号的半导体材料的转换层,以及

子像素(2)的阵列,

其中,每个像素(1)以及每个子像素(2)或一群相邻的子像素(2)被至少部分地填充有

阻隔材料的沟槽(3)围绕,所述阻隔材料吸收由所述入射辐射生成的光子的至少一部分,

其中,根据所述像素(1)和所述子像素(2)的尺寸,限定相邻像素(1)和相邻子像素(2)

之间距离的沟槽(3)的尺寸,并且

其中,在所述沟槽(3)的部分中的所述阻隔材料的填充系数基于所述沟槽的所述部分

的位置而变化。

2. 根据权利要求1所述的辐射探测器(10),其中,所述阻隔材料包括在35 keV能量以上

不表现出K荧光的材料。

3. 根据权利要求1所述的辐射探测器(10),其中,所述阻隔材料包括钼、银或钨。

4. 根据权利要求1到3中的任一项所述的辐射探测器(10),其中,所述阻隔材料是具有

中等原子序数Z的材料。

5. 根据权利要求1所述的辐射探测器(10),其中,所述沟槽(3)在所述转换层中的深度

处于20μm和600μm之间的范围内。

6. 一种制造辐射探测器(10)的方法,包括以下步骤:

提供半导体材料的衬底(4);

在所述衬底(4)中提供沟槽(3);

利用隔离层(6)覆盖所述沟槽(3)的表面;

在所述衬底(4)上提供像素(1)的阵列,其中,每个像素(1)包括子像素(2)的阵列,其

中,每个像素(1)以及每个子像素(2)或一群相邻的子像素(2)被所述沟槽(3)围绕,并且其

中,根据所述像素(1)和所述子像素(2)的尺寸,限定相邻像素(1)和相邻子像素(2)之间距

离的沟槽(3)的尺寸;

利用阻隔材料至少部分地填充所述沟槽(3),所述阻隔材料吸收由入射辐射生成的光

子的至少一部分,

其中,在所述沟槽(3)的部分中的所述阻隔材料的填充系数基于所述沟槽的所述部分

的位置而变化。

7. 根据权利要求6所述的方法,其中,所述至少部分地填充所述沟槽(3)的步骤包括通

过配给装置在所述沟槽(3)内部选择性地设置所述阻隔材料的步骤。

8. 根据权利要求6所述的方法,其中,所述至少部分地填充所述沟槽(3)的步骤包括应

用掩蔽层的步骤,所述掩蔽层为所述沟槽(3)中将至少部分地被填充的那些部分限定开口。

9. 一种包括根据权利要求1所述的辐射探测器(10)的X射线探测器。

10. 一种成像系统,包括根据权利要求1所述的辐射探测器(10)。

11. 根据权利要求10所述的成像系统,其中,所述成像系统包括X射线、CT、PET、SPECT或

核成像装置。

## 辐射探测器和制造辐射探测器的方法

[0001] 本申请是2009年06月09日提交的申请号为200980122524.5、名称为“辐射探测器和制造辐射探测器的方法”的发明专利申请的分案申请。

### 技术领域

[0002] 本发明涉及一种辐射探测器和制造辐射探测器的方法。此外，本发明涉及一种X射线探测器和包括此类辐射探测器的成像系统。

### 背景技术

[0003] 具有像素阵列的辐射探测器被应用于例如CT成像系统中，以便在辐射已经离开被扫描对象后提供对探测器上入射辐射的充分精确的测量。与例如将Cd (Zn) Te作为传感器材相比，用于辐射探测器的易制造的半导体材料，诸如硅，在例如成本方面是有利的。尽管Cd (Zn) Te具有比硅高得多的阻止能力并表现出小得多的导致像素间串扰的康普顿(Compton)散射，但Cd (Zn) Te表现出很强的K荧光(K-fluorescence)，这使能量分辨率下降并且还可能导致像素间串扰。此外，Cd (Zn) Te是一种昂贵的材料，难以大尺寸制造，并且由于其易碎性，表现出层厚度方面的局限性。相反，基于诸如硅的半导体材料的辐射探测器的K-荧光可以忽略。尽管硅对于较高的X射线能量(100keV左右)几乎透明，但对低于35keV的光子能量却吸收良好。然而，对于中等光子能量而言极有可能存在康普顿散射，这会改变光子的方向及其能量，导致相邻以及较远像素之间的空间和频域串扰。同时，与Cd (Zn) Te相反，基于半导体的辐射探测器能够受益于工业中常规使用的成熟和周知的半导体技术。

[0004] 此类基于半导体的辐射探测器的一个主要缺点是像素间串扰的量，这主要是由于康普顿散射，其降低了图像质量。对于任何相关像素尺寸都是这种情况，因为康普顿散射光子在硅内部穿过长达数厘米范围的远距离，因此容易诱发不相邻像素之间的空间串扰。

[0005] JP59065487公开了一种用于降低由X射线CT单元中辐射探测器上的放射性射线散射导致的相邻辐射探测器之间串扰的辐射探测器。将半导体辐射探测器和信号提取装置固定到金属制成的准直器板上，该金属对放射性射线具有较高的阻止能力。准直器板在衰减相邻辐射探测器间的放射性射线散射效应的同时，充当负电极，其大大降低了由散射的放射性射线导致的相邻辐射探测器之间的串扰。这种辐射探测器的缺点是仅降低了相邻辐射探测器之间的串扰，而未降低每个辐射探测器的像素之间的串扰。此外，它需要复杂的加工工艺，其中，辐射探测器被安装到降低辐射探测器之间串扰的准直器板上。

[0006] WO 2008/004547 A1公开了一种光电二极管阵列，其在具有n型半导体层的n型衬底上形成有多个允许被探测的光进入的光探测通道。光电二极管阵列装备有形成于衬底上的n型半导体层上的p型半导体层以及光探测通道之间形成的n型隔离部分。P型半导体层在与衬底的界面处配置pn结，并与光探测通道对应，p型半导体层具有多个放大区域，用于对要探测的光的进入而生成的载流子进行雪崩放大。形成隔离区，使得对应于每个光探测通道形成p型半导体层的每个放大区域。

## 发明内容

[0007] 本发明的目的在于提供一种辐射探测器，其中，不仅降低了不同探测器之间的串扰，而且还降低了每个辐射探测器的不同像素之间的串扰，其制造容易整合到现有制造工艺中。本发明由独立权利要求限定。从属权利要求限定了有利的实施例。

[0008] 这一目的是通过在半导体材料中提供沟槽实现的，该沟槽围绕每个像素并至少部分地被阻隔材料填充，阻隔材料吸收由入射辐射生成的光子的至少一部分。于是，围绕每个像素的沟槽具有以下性质：其能够吸收一部分辐射生成的光子，从而降低像素之间入射辐射的串扰散射。通过这种方式，降低了从像素进入相邻像素的辐射串扰的量。此外，可以通过简单的方式将沟槽整合到标准半导体工艺中，用以制造根据本发明的辐射探测器。例如，用于制造根据本发明的辐射探测器的CMOS(互补金属氧化物半导体)工艺实现了根据本发明的辐射探测器的简单和廉价的制造，其中，通过简单的方式整合了沟槽的制造。有利地，半导体材料包括硅，对于硅而言可利用标准而低成本的制造工艺。根据本发明，沟槽中阻隔材料的填充系数在整个探测器上可设计地变化。通过这种方式，实现了沟槽的第一部分具有这样的阻隔材料的填充系数或填充体积，即该填充系数或填充体积不同于沟槽的第二部分的填充系数或填充体积。例如，沟槽的第一部分围绕像素，而沟槽的第二部分围绕子像素或一群子像素。这有利地实现了对用于填充的材料、沟槽的尺寸和填充工艺所得质量之间的优化。

[0009] 在根据本发明的辐射探测器的实施例中，每个像素包括子像素的阵列并且每个子像素被沟槽围绕。这进一步降低了辐射探测器中串扰的量。在另一实施例中，一群相邻的子像素被沟槽围绕。这允许优化子像素的有效面积的尺寸并降低串扰，因为沟槽占据一定面积，这减少了像素和子像素的有效面积，但另一方面也降低了串扰。例如，这允许以接受阵列子像素之间的一些空间串扰为代价来提高子像素阵列有效面积的覆盖度。

[0010] 在根据本发明的辐射探测器的实施例中，阻隔材料包括在35keV能量以上不表现出K荧光的材料。由此可以使不希望的串扰效应最小化。

[0011] 在根据本发明的辐射探测器的实施例中，阻隔材料是具有中等原子序数Z的材料。这实现了入射辐射生成的光子在沟槽中的有效吸收。用于阻隔材料的有利材料是钼、银或钨。

[0012] 在根据本发明的辐射探测器的实施例中，沟槽在转换层中的深度处于 $20\mu\text{m}$ 和 $600\mu\text{m}$ 之间的范围内。这实现了与光子穿入到半导体材料层中的最大深度对应的沟槽深度，从而使串扰最小化。

[0013] 该目的还通过制造根据本发明的辐射探测器的方法实现，其中，在半导体材料衬底中提供沟槽，之后利用隔离层覆盖沟槽的表面。此后，在衬底上制造像素的阵列，从而使每个像素都被沟槽围绕。最后，利用阻隔材料至少部分地填充沟槽，阻隔材料吸收由入射辐射生成的光子的至少一部分。提供沟槽以及至少部分地填充沟槽所需的步骤都是可以整合到标准半导体制造工艺中的工艺步骤，从而实现了根据本发明的辐射探测器的廉价而简单的制造。

[0014] 例如，可以通过深度反应离子蚀刻(DRIE)在衬底内产生沟槽，其中，沟槽的形式或几何结构是大体上是垂直的。备选地，可以使用湿法蚀刻技术来在衬底中产生沟槽。可以应用这些不同的蚀刻技术来调节沟槽的形式以实现利用阻隔材料对沟槽的最佳填充。

[0015] 根据本发明,至少部分地填充沟槽的步骤包括由配给装置在沟槽内部选择性地设置阻隔材料的步骤。通过这种方式,可以在沟槽中相继地应用阻隔材料。例如,墨喷印刷机在沟槽内部设置阻隔材料。这是在沟槽内部应用阻隔材料的简单方式的范例。此外,这实现了利用不同体积的阻隔材料选择性地设置沟槽的各部分。例如,可以利用与沟槽的第二部分不同的阻隔材料填充体积来填充沟槽的第一部分。

[0016] 作为范例,在根据本发明的方法中,可以应用嵌入环氧胶中金属粉末作为阻隔材料。有利地,环氧胶可以同时被用作胶合剂,从而在沟槽顶部安装另一装置,例如抗散射网格。

[0017] 在根据本发明的方法的另一实施例中,至少部分地填充沟槽的步骤包括应用掩蔽层的步骤,掩蔽层为沟槽中要至少部分地被填充的那些部分限定开口。这样能够在一个工艺步骤中在整个衬底上的沟槽内应用阻隔材料。

[0018] 该目的还通过包括根据本发明的辐射探测器的X射线探测器以及通过包括根据本发明的X射线辐射探测器的成像系统,尤其是X射线、CT、PET、SPECT或核成像装置实现。

[0019] 根据本发明的辐射探测器可以用于电磁辐射,尤其是X辐射或 $\gamma$ 辐射的定量和/或定性探测。

[0020] 辐射探测器通常将具有未明确提及的附加部件,例如光阀、抗散射网格、电子电路、外壳等,因为它们对于本领域的技术人员而言是显而易见的,其中,通常以这样一种方式布置这些部件,使得仅能够从相对于探测器的特定进入方向向该探测器上辐照光子。

## 附图说明

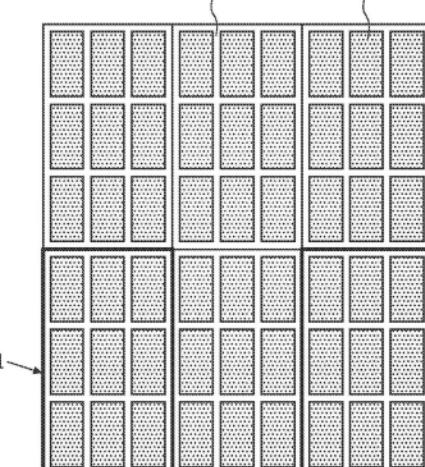

[0021] 图1示意性地示出了根据本发明的辐射探测器的一部分的顶视图;

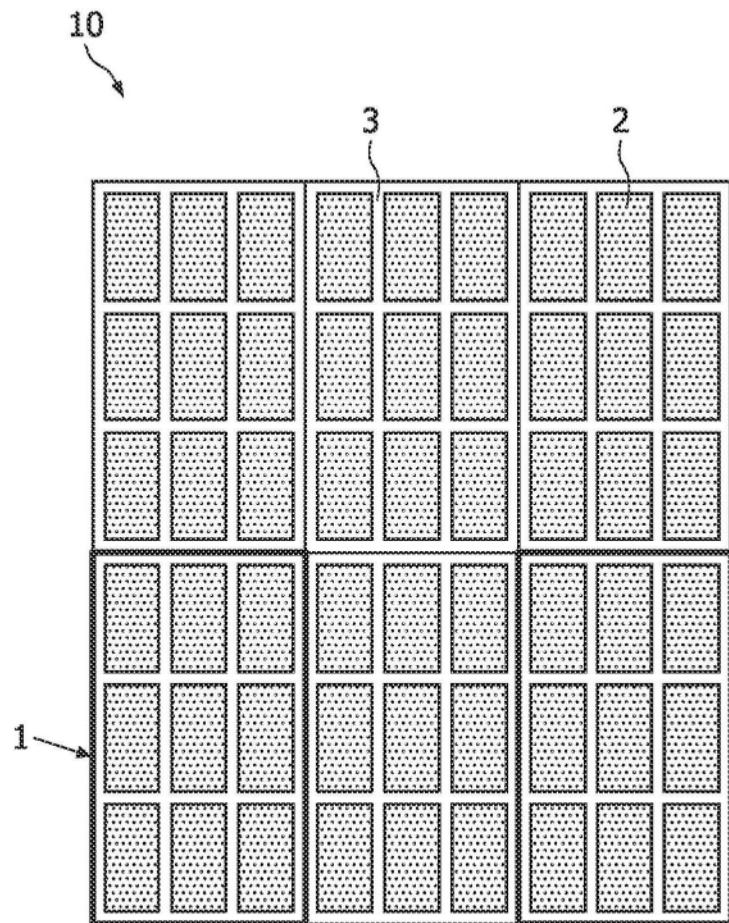

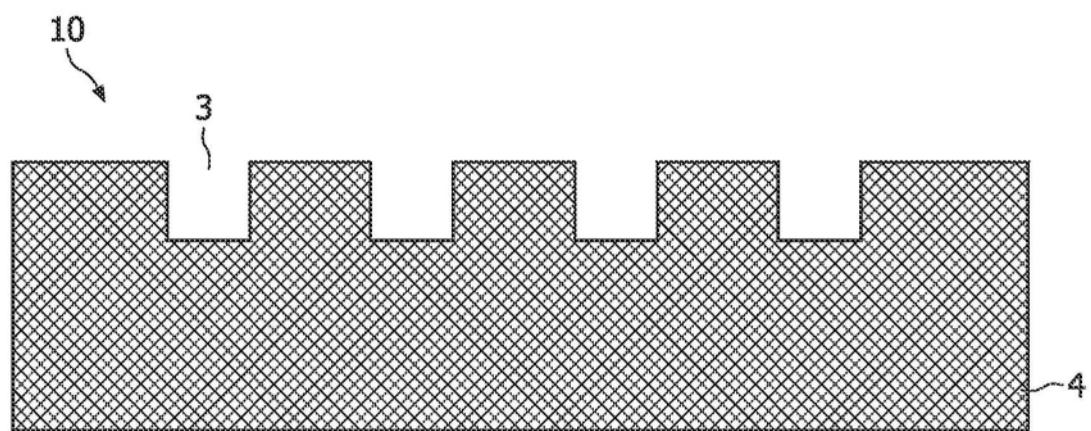

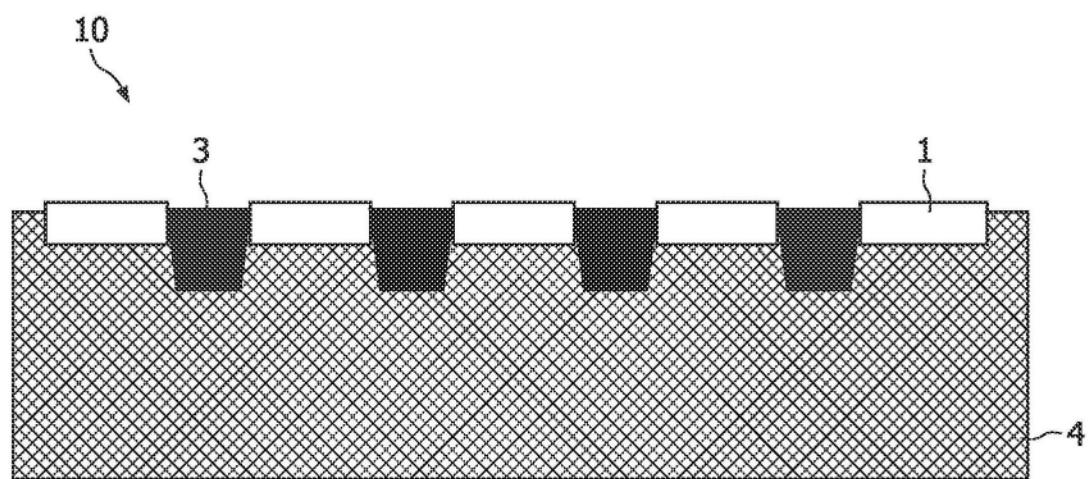

[0022] 图2a-2c示意地图示说明了制造根据本发明的辐射探测器的方法,示出了该辐射探测器的一部分的截面图;以及

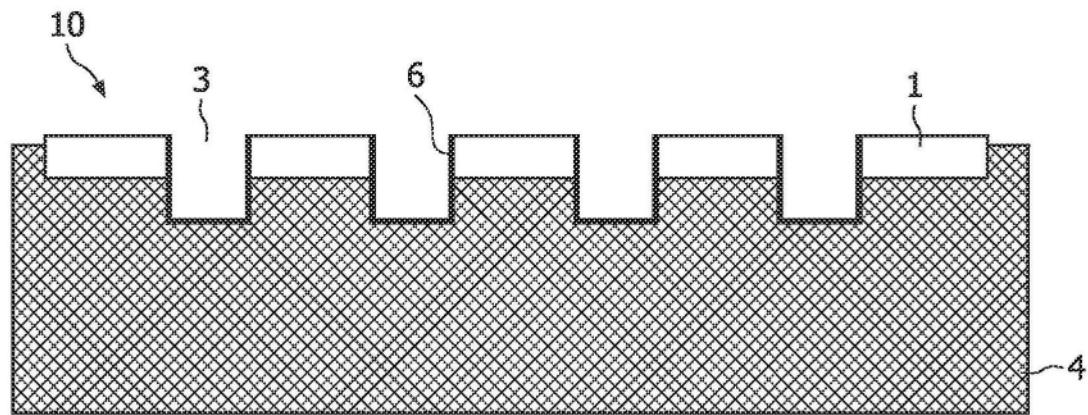

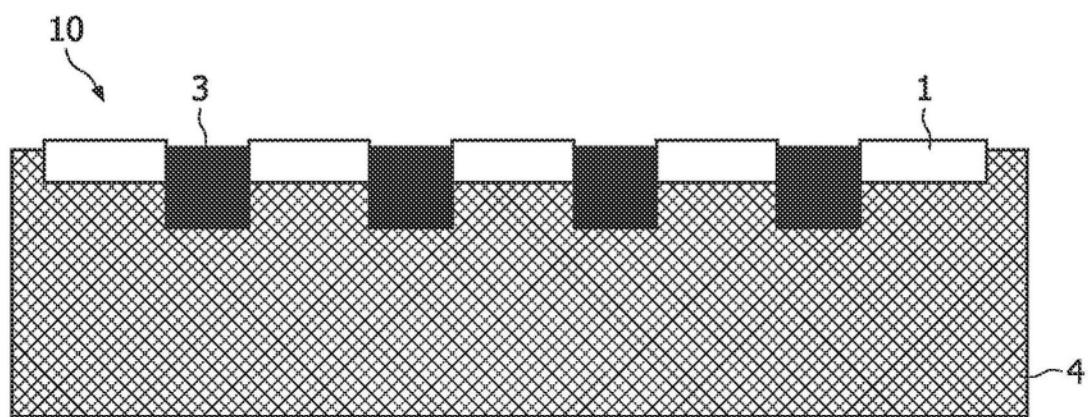

[0023] 图3示意地图示说明了根据本发明的辐射探测器的一部分,示出了辐射探测器的一部分的截面图。

[0024] 附图中类似的附图标记表示相同或类似的部件。

## 具体实施方式

[0025] “频谱CT”被认为具有通过以下方式使目前的CT系统发生革命的潜质,即,将X射线管生成的并穿过被扫描对象的多色(poly-chromatic)X射线束中包含的频谱信息用于提供新的对诊断非常关键的信息。用于频谱CT成像系统的使能技术是一种探测器,该探测器能够提供对击中被扫描对象后方探测器的光子能谱的充分精确的估计。由于出于图像重建的原因,探测器还暴露于直接射束,所以看到直接射束的探测器像素中的光子计数率非常大(大约每 $\text{mm}^2$ 每秒 $10^9$ 个光子,即每 $\text{mm}^2$  1000Mcps)。然而,预计读出电子线路能够处理至多10Mcps。为了限制计数率,可以将探测器的传感器部分(其中,X射线光子交互作用并生成电荷脉冲,电荷脉冲进一步由读出电子线路评估)子结构化为小的子像素(例如 $300\mu\text{m} \times 300\mu\text{m}$ )以及若干不同传感器层(三维子结构化),其中,传感器层中的每个子像素具有其自己的能量解析读出电子线路通道,该通道具有针对每个能量的子通道。

[0026] 作为用于频谱CT的传感器材料,由于CZT或CdTe相对高的X射线阻止能力(大约3mm

厚的CZT被认为足以完全代替当前使用的GOS闪烁体),人们对CZT或CdTe很感兴趣。然而,这种高阻止能力在某种程度上也是缺点:为了将传感器层内子像素的最大计数率限制为大约10Mcps,以便使服务的读出电子线路通道仅很少得看到脉冲积累,第一传感器层(像素为 $300\mu\text{m} \times 300\mu\text{m}$ )将需要远低于 $100\mu\text{m}$ 的厚度。但由于CZT的易碎性,能否制造这些CZT薄层存在疑问。此外,由于被限定为由“横向扩展”除以厚度的高宽比小得多,在那些厚度低于 $100\mu\text{m}$ 的非常薄的层中,失去了小像素效应的优点。

[0027] 为了解决以上问题,提出将像硅那样阻止能力低的材料用作频谱CT的传感器材料,可能结合还用于计数模式的CZT或CdTe,或甚至结合能量积分的GOS层。由于Si的低原子序数Z=14,与CZT或CdTe的情况相比,X射线的衰减更小。因此,为了实现不高于10Mcps的计数率,能量解析计数探测器中由Si制成的堆栈探测器的顶层的层厚在1.7mm范围内。顶层以下的转换层厚的度甚至可以逐层相继增大。因此,可以容易地制造出包括以若干层Si作为直接转换材料的频谱CT探测器。Si的进一步优点在于,它比CZT更为便宜,更加容易制造(甚至可能在标准CMOS制造工艺中制造),且几乎没有K荧光串扰,因为K边缘能量低于2keV且荧光产出(即,发生与K荧光交互作用的频率度量)仅为4.1%。

[0028] 图1示出了辐射探测器10的一部分的顶视图,辐射探测器10具有像素1的 $2 \times 3$ 阵列以及针对每个像素1的子像素2的 $3 \times 3$ 阵列。由连接到像素1和子像素2的读出电子线路(未示出)探测像素1和子像素2中生成的光子。在这种情况下,沟槽3围绕每个像素1和每个子像素2。在衬底4(未示出)内提供了沟槽3,还在衬底上提供了像素1和子像素2。沟槽3填充有阻隔材料,阻隔材料通过吸收辐射探测器10上的入射辐射生成的一部分由光子来降低像素1之间和子像素2之间的串扰的量。最有效的阻隔材料具有中等的z序数。例如钼、银或钨是合适的阻隔材料。如果具有高z序数的材料的K边缘位于35-70keV能量范围以上或以内,它们较不合适,因为串扰主要发生在35-70keV的能量范围内;在这种情况下,阻隔材料会遭受K边缘以下K荧光和较低吸收效率的影响。

[0029] 图2a-2c图示说明了制造根据本发明的辐射探测器10的方法,示出了辐射探测器10的一部分的截面图。在衬底4中,在包括硅的这一范例中,在这种情况下,通过应用DRIE(“深度反应离子蚀刻”)蚀刻形成沟槽3,这会获得相对直的并且垂直的沟槽3的壁,如图2a所示。例如,可以应用氧化掩蔽层以限定形成沟槽3的区域。根据衬底4的厚度以及导致串扰的X射线光子到达衬底4内部的最大深度,沟槽3的深度优选在 $20\mu\text{m}$ 到 $600\mu\text{m}$ 的范围内。根据像素1和子像素2的尺寸,将相邻像素1和子像素2之间距离的沟槽3宽度或尺寸限定在例如 $50\mu\text{m}$ 到 $300\mu\text{m}$ 的范围内。

[0030] 接下来,例如,如图2b所示,通过标准的CMOS工艺在沟槽3之间提供像素1。此外,为沟槽的壁和底部提供隔离层6。可以通过任何公知的隔离层形成步骤,诸如热氧化或钝化来执行这一工艺步骤。可以在制造像素1之前、期间或之后进行形成隔离层6的这一步骤。然后利用适当阻隔材料填充沟槽3,如图2c所示。隔离层6至少为沟槽3中的阻隔材料以及衬底4、像素1和子像素2之间提供电隔离。可以完全地或部分地执行沟槽3的填充。通过应用合适的技术,甚至可能制造具有阻隔材料的沟槽3的填充系数在整个辐射探测器上变化的辐射探测器10。例如,将围绕像素1的沟槽3填充到与子像素周围的沟槽3不同的程度。合适的技术例如是喷墨印刷,其中,以某种连续方式填充沟槽3。通过这种方式,可以选择性地在沟槽3中设置阻隔材料并根据衬底4上沟槽3的部分的位置设计或调节沟槽3的填充系数。另一种

合适的技术例如是丝网印刷,其中,应用掩蔽层,用以在要至少部分填充沟槽3的部分的位置上限定开口。之后可以应用另一填充步骤,或者任选地,可以应用第二掩蔽层以填充沟槽3的剩余部分并提高已经通过先前的掩蔽层步骤至少部分地填充的沟槽3的填充系数。

[0031] 例如,可以应用嵌入环氧胶中金属粉末作为阻隔材料。可以根据沟槽3的深度优化金属粉末和环氧树脂的颗粒大小以实现沟槽3的最佳填充。此外,环氧树脂还用作胶粘剂,用于在探测器10的顶部安装例如ASG(“抗散射网格”),获得辐射探测器10和ASG之间最佳温度系数匹配。

[0032] 在最终的固化步骤硬化阻隔材料之前,可以有利地应用预退火工艺步骤和前侧晶片清洗步骤。

[0033] 可以应用其他蚀刻技术,获得与应用DRIE蚀刻时的沟槽3的不同几何结构。例如,可以使用KOH作为蚀刻剂来施加湿法蚀刻技术,这是比干法蚀刻更快的蚀刻工艺,获得了沟槽3的不太竖直但更倾斜的壁,如图3所示。

[0034] 在至少部分填充的沟槽3顶部,可以提供一层反射材料以防止辐射进入阻隔材料。

[0035] 根据本发明的辐射探测器不限于在具有能量解析X射线光子计数CT中的串扰抑制,而是还有益于包括像素的Si探测器中的串扰抑制。

[0036] 最后应当指出,在本申请中,“包括”一词不排除其他元件或步骤的存在,“一”或“一个”并不排除多个,且单个处理器或其他单元可以实现若干模块的功能。本发明体现在每个新颖的特征要素和特征要素的每种组合中。此外,权利要求中的附图标记不应被解释为限制它们的范围。

图1

图2a

图2b

图2c

图3