US 20140231005A1

# (19) United States(12) Patent Application Publication

### Peterson et al.

#### (54) PRODUCING AN ELECTROMAGNETIC ISOLATION CAVITY BY STACKING TAPE LAYERS HAVING CONDUCTOR-COATED EDGE SURFACES FACING THE CAVITY

- (71) Applicants: Sandia Corporation, Albuquerque, NM (US); Honeywell Federal Manufacturing & Technologies, LL C, Kansas City, MO (US)

- (72) Inventors: Kenneth A. Peterson, Albuquerque, NM (US); Richard T. Knudson, Los Lunas, NM (US); Frank R. Smith, Los Lunas, NM (US); Gregory Barner, Overland Park, KS (US)

- (73) Assignee: Sandia Corporation, Albuquerque, NM (US)

- (21) Appl. No.: 14/266,514

- (22) Filed: Apr. 30, 2014

## (10) Pub. No.: US 2014/0231005 A1 (43) Pub. Date: Aug. 21, 2014

#### **Related U.S. Application Data**

- (63) Continuation of application No. 12/833,262, filed on Jul. 9, 2010, now Pat. No. 8,747,591.

- (60) Provisional application No. 61/244,650, filed on Sep. 22, 2009.

#### **Publication Classification**

#### (57) **ABSTRACT**

An electromagnetic isolation cavity surrounded by a generally annular solid conductive wall is produced by coating edge surfaces of respective dielectric tape layers with a material containing a conductor. The tape layers are then stacked, with the coated edge surfaces aligned and facing the electromagnetic isolation cavity.

#### PRODUCING AN ELECTROMAGNETIC ISOLATION CAVITY BY STACKING TAPE LAYERS HAVING CONDUCTOR-COATED EDGE SURFACES FACING THE CAVITY

**[0001]** This application is a continuation under 35 U.S.C. §120 of U.S. application Ser. No. 12/833,262, which was filed on Jul. 9, 2010, and which claims the priority under 35 U.S.C. §119(e)(1) of U.S. Provisional Application Ser. No. 61/244, 650 filed Sep. 22, 2009. Both of the aforementioned prior applications are incorporated herein by reference.

**[0002]** This invention was developed under Contract DE-AC04-94AL85000 between Sandia Corporation and the U.S. Department of Energy, and under Contract DE-NA0000622 between Honeywell Federal Manufacturing & Technologies, LLC and the U.S. Department of Energy. The U.S. Government has certain rights in this invention.

#### FIELD OF THE INVENTION

**[0003]** The invention relates generally to low temperature co-fired ceramics (LTCCs) and, more particularly, to providing EMI (electromagnetic isolation) structures in LTCCs.

#### BACKGROUND OF THE INVENTION

**[0004]** Applications for LTCC technology have been expanding as flat board technology has been augmented with three-dimensional features including cavities, channels, solid tubes, formed shapes, sacrificial volume materials (SVM) and various embedded components such as resistors, capacitors, inductors and heat sinks. See generally U.S. Pat. Nos. 7,494,557 and 7,155,812, both of which are incorporated herein by reference in their entirety.

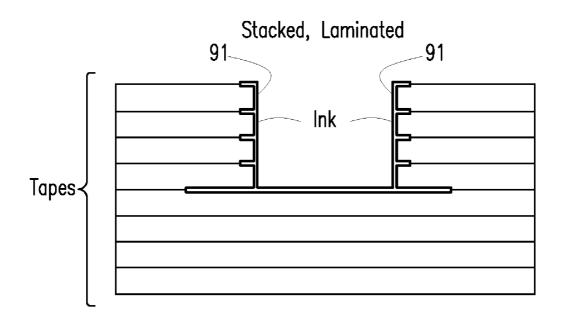

[0005] Recently, techniques have been developed for fabricating continuous EMI full tape thickness features (FTTF). These are based on via fill technology and use the full thickness of the tape to improve performance. In the case of conductors, this is accomplished by substituting full thickness lines for surface-printed traces that are typically much thinner. FIG. 1 shows the increased cross-sectional thickness provided by FTTF as compared to a surface printed trace (designated as a thick film line feature in FIG. 1). FIG. 2 provides a perspective view of a tape having features similar to the middle tape in the stack of FIG. 1. As indicated in FIG. 1, the increased cross-sectional area results in correspondingly reduced resistivity. The result is paths with very low resistance. FTTF technology has also been used to produce fences for EMI structures that are superior to traditional via fences because of their ability to block more line-of-sight radiation.

**[0006]** It is desirable to provide for improvements in the use of FTTF technology in EMI structures.

#### BRIEF DESCRIPTION OF THE DRAWINGS

**[0007]** FIG. **1** is a cross-sectional view of a tape stack showing the contrast between a surface printed trace and FTTF.

**[0008]** FIG. **2** is a perspective view of a tape having features similar to the middle tape in the stack of FIG. **1**.

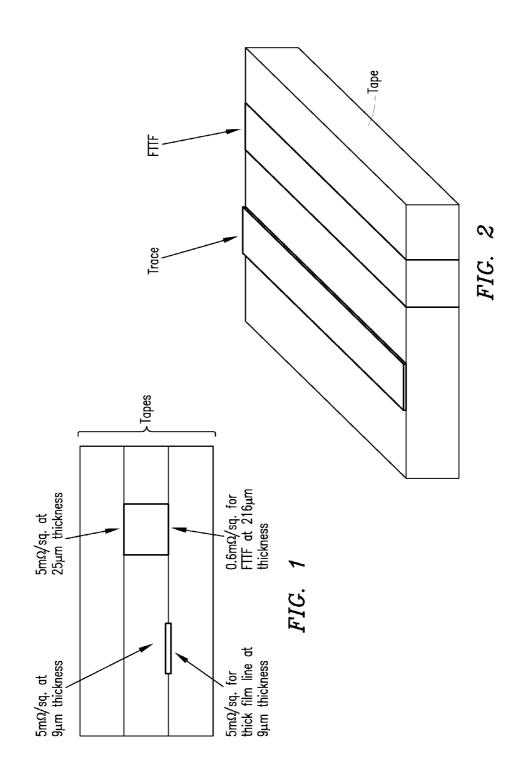

**[0009]** FIG. **3** diagrammatically illustrates a method of producing a solid wall conductive enclosure for EMI structures according to exemplary embodiments of the invention.

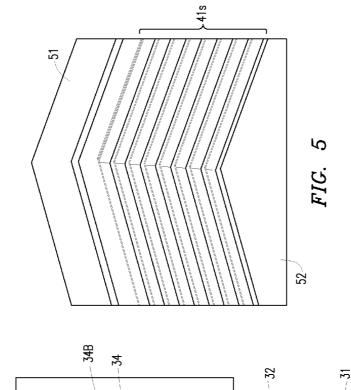

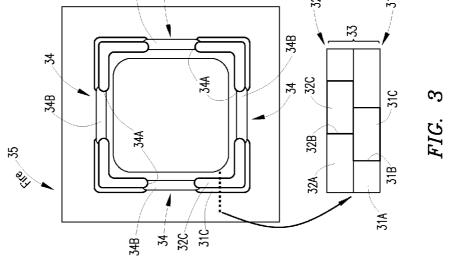

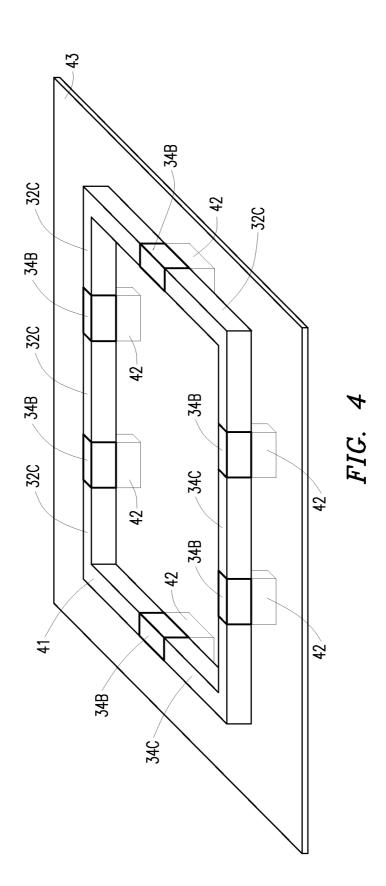

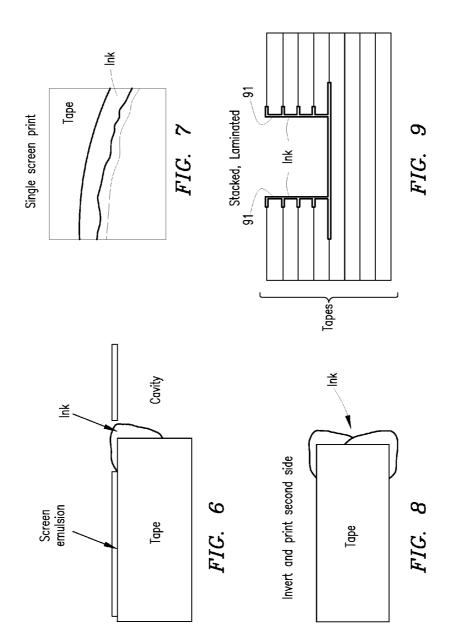

[0010] FIG. 4 diagrammatically illustrates other methods of producing a solid wall conductive enclosure for EMI structures according to exemplary embodiments of the invention. [0011] FIG. 5 diagrammatically illustrates a portion of the interior of a solid wall conductive enclosure for EMI structures according to exemplary embodiments of the invention. [0012] FIGS. 6-9 diagrammatically illustrate a further method of producing a solid wall conductive enclosure for EMI structures according to exemplary embodiments of the invention.

#### DETAILED DESCRIPTION

**[0013]** EMI is increasingly important for critical transceiver circuits. Exemplary embodiments of the invention provide improved EMI structures using FTTF. Techniques are provided to produce EMI structures having generally annular, solid conductive walls comprising multiple stacked FTTF conductors, together with a conductive lid or intermediate conductive structure adjoining one end of the walls, and a ground plane adjoining the other end of the walls. The ground plane may be mesh or solid, although solid provides better isolation. The intermediate conductive structure may be, for example, a metal seal frame, a soldered layer, or a conductiveepoxy-attach layer. The solid walls provide improved isolation relative to other known approaches such as via fences and slot-style FTTF fences.

[0014] Slot-style FTTF fences use staggered layers of FTTF conductors (basically, laterally elongated versions of vias). Each layer has intervening tape dielectric between the conductors in that layer. The conductors in alternate layers are arranged in a staggered fashion, such that the intervening tape dielectric material of one layer does not contact the intervening dielectric material of the adjacent layers, but rather contacts conductors in the adjacent layers. Thus, the intervening dielectric material of each layer is surrounded by conductors in the slot-style FTTF fence. These conductor-surrounded dielectric portions constitute isolation "gaps" in the fence. The solid wall construction described herein provides continuous FTTF conductors in each layer of the wall, and thus eliminates the isolation gaps of the slot-style FTTF fence. The solid wall construction requires less material than the staggered slot-style FTTF fences and is on a par with staggered via fences, is more compact, and greatly reduces the amount of tape punching required.

[0015] FIG. 3 diagrammatically illustrates a method of producing a solid wall Faraday enclosure for EMI according to exemplary embodiments of the invention. The wall is constructed of multiple layers of FTTF conductors stitched together in solid (continuous) annular configurations. The layers are produced in pairs as follows. In a step shown generally at 31, a lower tape layer 31A is punched at 31B, and the resulting trench portions are filled with thick film conductor material (e.g., conventional paste or ink) at 31C, by any suitable conventional method, such as screen printing, injection or stenciling. All fill operations shown and described herein are assumed to include drying the fill material. In FIG. 3, the punched and filled portions 31B/31C are separated by tethers that will be punched and filled later at 34. The tethers are retained so that the LTCC tape remains intact and does not detach completely from the tape layer.

[0016] In a step shown generally at 32, the upper tape layer 32A is punched at 32B to form further trench portions that have generally the same configuration as the corresponding trench portions 31B in the lower tape layer 31A, and are in

laterally (inwardly in the example of FIG. 3) offset but overlapping relationship relative to the respectively corresponding filled portions **31**C. Some embodiments provide the overlapping relationship but omit the lateral offset. Next, the trench portions **32**B are filled with thick film material at **32**C. In a step shown generally at **33**, the layers **31** and **32** are then laminated.

[0017] In a step shown generally at 34, with the dried thick film material 31C and 32C and unpunched tethers available to support the inboard tape material, the tethers (between the already-filled trench portions) in layers 31A and 32A are removed by punching in a two-layer punch operation at 34A. The resulting trench portions are then filled with thick film material at 34B. In the example of FIG. 3, a larger punch is used at 34A than at 31B and 32B so that the aspect ratio will ease the subsequent filling, but various embodiments use smaller punch profiles than shown at 34A. This completes the annular solid wall portion for layers 31 and 32.

**[0018]** The steps **31-34** are repeated for as many tape layer pairs as desired. After all desired tape layer pairs are processed through steps **31-34**, the processed pairs are collated and laminated to form a substrate containing an annular solid conductive wall. (Note that upper tape layers of the stack, including a portion of layer **32**, are removed in the top view of FIG. **3** in order to illustrate completely the structure of a single, two-layer annular solid wall portion.) One or more layers will contain a conductive ground plane in a typical configuration. The laminated layers may then be modified by any post-processing called for by a particular design and fired as shown generally at **35** to produce an LTCC substrate.

[0019] Some embodiments process a single tape layer at a time, to produce a single layer solid conductive wall. The single layer is punched as, for example, in step 32 in FIG. 3 above, with tethers remaining between the punched trench portions. These trench portions are then filled as in step 32. With the dried thick film material deposited in the trench portions now available to support the inboard tape, the single layer tethers are punched and filled as above in step 34 (but for only the single layer here) to complete the single layer annular solid wall portion. (An example of such a single layer solid wall portion can be seen at 41 in FIG. 4, ignoring for the moment the extra, lower layer wall portions shown at 42 in FIG. 4.) The process is repeated for as many layers as desired, after which all of the single layer solid wall portions are collated and laminated to form a substrate containing an annular solid conductive wall. The laminated layers may then be fired to produce an LTCC substrate. In some embodiments, each of the aforementioned single tape layers is formed as a composite tape layer that includes at least two constituent tape layers. This composite tape layer structure provides more material strength for processing.

**[0020]** Some embodiments provide place the ground plane on a lower tape layer so that it is one tape layer below the surface of the circuit to be isolated. The presence of this lower tape layer permits more of the single layer wall portion to be punched into the adjacent upper tape layer in the initial punch operation, with smaller tethers than would otherwise be needed for the above-described single layer processing. The lower tape layer, which has the ground plane on its surface, is then laminated to the upper, punched tape layer. Note that the lower tape layer does not require cutouts aligned with the trench portions punched in the upper layer, and none are provided in some embodiments. A second, two-layer punch and fill operation (**34**B/**42**) is performed to complete the wall in the upper layer. The wall is two layers deep in those areas punched and filled second, as shown at **34**B/**42** in FIG. **4**, but this presents no functional problems. All other layers for the stack may then be processed using the above-described single layer processing.

[0021] FIG. 5 diagrammatically illustrates a portion of the interior of an annular solid wall conductive enclosure for EMI according to exemplary embodiments of the invention. The ceramic material inboard of the solid wall is hidden in order to show the wall. The material shown between the wall layers is either a printed conductive capture pad in the shape of a ring or a printed ground plane (also partially hidden to show the solid wall). However, these are purely optional features, because all wall segments are already electrically connected. The specific example of FIG. 5 shows a wall composed of stacked single layer annular wall portions 41 produced according to the above-described single layer processing. Also shown are the ground plane 52 and a printed thick film seal ring 51, the latter being partially cut away to show the wall portions 41 forming the interior sidewalls of the cavity. The two-layer processing of FIG. 3 also produces similar solid conductive sidewalls for the cavity.

[0022] FIGS. 6-9 illustrate a further process for producing a multi-layer annular solid conductive wall for EMI. As shown in FIG. 6, a screen emulsion or stencil edge is used to stencil material containing conductor (ink in the example of FIG. 6) onto the tape layer near the edge surface of the tape that will face the cavity. In some embodiments, the stenciled material itself may not be conductive, but the ultimate fired product is. The ink runs, or flows, onto the surface of the tape (in order to provide wrapping of the EMI shield, and down the edge surface of the tape to coat more than half of that surface. This is also shown in FIG. 7, wherein the cavity 71 has a generally circular shape. Then, the tape is inverted, and the process of FIG. 6 is repeated. The result, shown in FIG. 8, is that the entire edge surface and a portion of the top and bottom surface of the tape is coated with the ink. The process of FIGS. 7 and 8 is repeated for as many tape layers as desired, and all of the tape layers are collated and laminated, to produce a substrate containing the desired annular solid conductive wall of dried ink on the interior sidewalls 91 of the cavity, as shown in the cross-sectional view of FIG. 9. The laminated layers may then be post-processed if called for in a particular design, and fired to produce an LTCC substrate.

**[0023]** Although exemplary embodiments have been described above in detail, this does not limit the scope of the invention, which can be practiced in a variety of embodiments.

What is claimed is:

**1**. A method for producing an electromagnetic isolation cavity surrounded by a generally annular solid conductive wall, comprising:

coating an edge surface of each of a plurality of dielectric tape layers with a material comprising a conductor;

drying the material coated on the edge surfaces; and

after said coating, stacking the tape layers on a ground plane formed from a material comprising a conductor, to form a tape stack with the coated edge surfaces aligned and facing the electromagnetic isolation cavity and with the ground plane defining a closed end of the electromagnetic isolation cavity.

2. The method of claim 1, wherein said coating includes using a screen emulsion to stencil said material onto each said

dielectric tape layer, and thereafter flowing said material along the dielectric tape layer onto said edge surface thereof.

3. The method of claim 2, wherein said coating includes using a screen emulsion to stencil said material onto opposite side surfaces of each said dielectric tape layer that are connected by said edge surface of the dielectric tape layer, and said flowing includes flowing said material from said opposite side surfaces onto said edge surface.

4. The method of claim 3, wherein said using a screen emulsion to stencil material onto opposite side surfaces includes stenciling material onto one side surface, and thereafter inverting the dielectric tape layer and stenciling material onto the other side surface.

**5**. The method of claim **3**, wherein the coated edge surfaces form a generally annular solid conductive wall surrounding the electromagnetic isolation cavity.

\* \* \* \* \*