(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2014-53901

(P2014-53901A)

(43) 公開日 平成26年3月20日(2014.3.20)

| (51) Int.Cl.                  | F 1         | テーマコード (参考) |

|-------------------------------|-------------|-------------|

| <b>H03K 19/0175 (2006.01)</b> | H03K 19/00  | 101F 2H192  |

| <b>H01L 29/786 (2006.01)</b>  | H01L 29/78  | 613Z 3K107  |

| <b>G02F 1/1368 (2006.01)</b>  | H01L 29/78  | 618B 5F110  |

| <b>H01L 51/50 (2006.01)</b>   | GO2F 1/1368 | 5J056       |

| <b>H05B 33/14 (2006.01)</b>   | H05B 33/14  | A           |

審査請求 有 請求項の数 5 O L (全 88 頁) 最終頁に続く

|              |                                   |          |                                                |

|--------------|-----------------------------------|----------|------------------------------------------------|

| (21) 出願番号    | 特願2013-194868 (P2013-194868)      | (71) 出願人 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (22) 出願日     | 平成25年9月20日 (2013.9.20)            | (72) 発明者 | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (62) 分割の表示   | 特願2013-48929 (P2013-48929)<br>の分割 | (72) 発明者 | 小山 潤<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| 原出願日         | 平成22年10月12日 (2010.10.12)          | (72) 発明者 | 津吹 将志<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (31) 優先権主張番号 | 特願2009-238918 (P2009-238918)      | (72) 発明者 | 野田 耕生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (32) 優先日     | 平成21年10月16日 (2009.10.16)          |          |                                                |

| (33) 優先権主張国  | 日本国 (JP)                          |          |                                                |

最終頁に続く

(54) 【発明の名称】半導体装置及び表示装置

## (57) 【要約】

【課題】トランジスタのリーク電流を低減し、論理回路の誤動作を抑制する。

【解決手段】チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅  $1 \mu m$  あたりのオフ電流が  $1 \times 10^{-13} A$  以下であるトランジスタを有し、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を出力信号として出力する構成とする。

【選択図】図 1

## 【特許請求の範囲】

## 【請求項 1】

第1乃至第8のトランジスタを有し、

前記第1乃至前記第8のトランジスタのそれぞれは、チャネル形成層としての機能を有する酸化物半導体層を含み、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第8のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第5のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第6のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第8のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第7のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の出力端子と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、第1の入力端子と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、第2の入力端子と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、第2の出力端子と電気的に接続されることを特徴とする半導体装置。

## 【請求項 2】

第1乃至第8のトランジスタと、第1乃至第4の容量素子と、を有し、

前記第1乃至前記第8のトランジスタのそれぞれは、チャネル形成層としての機能を有する酸化物半導体層を含み、

前記第1のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと電気的に接続され、

前記第4のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第7のトランジスタのソース又はドレインの一方は、前記第5のトランジスタのゲートと電気的に接続され、

前記第8のトランジスタのソース又はドレインの一方は、前記第6のトランジスタのゲートと電気的に接続され、

前記第1のトランジスタのソース又はドレインの他方は、前記第5のトランジスタのソ

10

20

30

40

50

ース又はドレインの他方と電気的に接続され、

前記第2のトランジスタのソース又はドレインの他方は、前記第6のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、前記第8のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、前記第7のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第1のトランジスタのソース又はドレインの一方は、第1の出力端子と電気的に接続され、

前記第3のトランジスタのソース又はドレインの他方は、第1の入力端子と電気的に接続され、

前記第4のトランジスタのソース又はドレインの他方は、第2の入力端子と電気的に接続され、

前記第5のトランジスタのソース又はドレインの一方は、第2の出力端子と電気的に接続され、

前記第1の容量素子の第1の端子は、前記第1のトランジスタのゲートと電気的に接続され、

前記第1の容量素子の第2の端子は、前記第1のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第2の容量素子の第1の端子は、前記第2のトランジスタのゲートと電気的に接続され、

前記第2の容量素子の第2の端子は、前記第2のトランジスタのソース又はドレインの他方と電気的に接続され、

前記第3の容量素子の第1の端子は、前記第5のトランジスタのゲートと電気的に接続され、

前記第3の容量素子の第2の端子は、前記第5のトランジスタのソース又はドレインの一方と電気的に接続され、

前記第4の容量素子の第1の端子は、前記第6のトランジスタのゲートと電気的に接続され、

前記第4の容量素子の第2の端子は、前記第6のトランジスタのソース又はドレインの他方と電気的に接続されることを特徴とする半導体装置。

### 【請求項3】

請求項1または請求項2において、

前記第1乃至前記第8のトランジスタのそれぞれは、ソース-ゲート間電圧が-10V、ソース-ドレイン間電圧が1Vのときに、チャネル幅1μmあたりのオフ電流が $1 \times 10^{-13}$ A以下であることを特徴とする半導体装置。

### 【請求項4】

請求項1乃至請求項3のいずれか一において、

前記第1乃至前記第8のトランジスタのいずれか一は、第1の導電層と第2の導電層とを有し、

前記第1の導電層は、前記酸化物半導体層の下方に設けられた第1の絶縁層を介して前記酸化物半導体層と重なり、

前記第2の導電層は、前記酸化物半導体層の上方に設けられた第2の絶縁層を介して前記酸化物半導体層と重なり、

前記第1の導電層と前記第2の導電層とは、前記第1乃至前記第8のトランジスタのいずれか一のゲート電極層として機能することを特徴とする半導体装置。

### 【請求項5】

請求項1乃至請求項4のいずれか一に記載の半導体装置を有する駆動回路と、

前記駆動回路により駆動される表示部と、

を有する表示装置。

10

20

30

40

50

## 【発明の詳細な説明】

## 【技術分野】

【 0 0 0 1 】

本発明の一態様は、論理回路に関する。また、該論理回路を用いた駆動回路を含む半導体装置に関する。

【 0 0 0 2 】

なお、本明細書中において半導体装置とは、半導体特性を利用して機能しうる装置全般を指し、表示装置などの電気光学装置、半導体回路及び電子機器は全て半導体装置である。

## 【背景技术】

【 0 0 0 3 】

液晶表示装置に代表されるように、ガラス基板などの平板に形成される薄膜トランジスタ（以下、TFT：Thin Film Transistorともいう）は、主にアモルファスシリコン又は多結晶シリコンなどの半導体材料を用いて作製される。アモルファスシリコンを用いたTFTは、電界効果移動度が低いもののガラス基板の大面積化に対応することができる。一方、多結晶シリコンを用いたTFTは、電界効果移動度が高いもののレーザアニールなどの結晶化工程が必要であり、ガラス基板の大面積化には必ずしも適応しないといった特性を有している。

【 0 0 0 4 】

これに対し、半導体材料として酸化物半導体を用いるTFTが注目されている。例えば、半導体材料として酸化亜鉛又はIn-Ga-Zn-O系酸化物半導体を用いてTFTを作製し、画像表示装置のスイッチング素子として用いる技術が特許文献1及び特許文献2で開示されている。

【 0 0 0 5 】

酸化物半導体にチャネル形成領域（チャネル領域ともいう）を設けた TFT は、アモルファスシリコンを用いた TFT よりも高い電界効果移動度が得られている。また、酸化物半導体膜は、スパッタリング法などによって膜形成が可能であり、多結晶シリコンを用いた TFT よりも作製が容易である。

【 0 0 0 6 】

このような酸化物半導体を用いて作製された TFT は、液晶ディスプレイ、エレクトロルミネセンスディスプレイ（以下、ELディスプレイともいう）又は電子ペーパーなどの表示装置の画素部及び駆動回路を構成するスイッチング素子に適用することが期待されている。例えば、上記の酸化物半導体を用いて作製された TFT によって表示装置の画素部及び駆動回路を構成する技術が特許文献 3 で開示されている。

## 【先行技術文献】

## 【特許文献】

【 0 0 0 7 】

【特許文献 1】特開 2006-165527 号公報

【特許文献 2】特開 2006-165529 号公報

【特許文献3】特開2006-165528号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

【 0 0 0 8 】

駆動回路は、シフトレジスタ及びバッファなどによって構成され、さらにシフトレジスタ又はバッファは、論理回路を用いて構成される。また、論理回路は、トランジスタを用いて構成されるが、従来のトランジスタは、オフ状態であってもリーク電流が発生する場合がある。リーク電流が発生すると、例えば論理回路において出力信号の電圧の値を一定の範囲に維持したい場合であっても、出力信号の値が変化し、誤動作する可能性がある。

【 0 0 0 9 】

本発明の一態様では、トランジスタのリーク電流を低減することを課題とし、また、トランジ

10

20

30

40

ンジスタのリーク電流を低減することにより論理回路の誤動作を抑制することを課題とする。

【課題を解決するための手段】

【0010】

本発明の一態様は、オフ電流が低く、チャネル形成層としての機能を有する酸化物半導体層を有するトランジスタを、論理回路を構成するトランジスタとして用いたものである。これにより論理回路における誤動作の抑制を図る。

【0011】

トランジスタのチャネル形成層として用いられる酸化物半導体層は、酸化物半導体中で電子供与体（ドナー）となる不純物を除去することにより高純度化させた、真性又は実質的に真性な半導体であり、シリコン半導体よりもエネルギーギャップが大きい。該酸化物半導体層を用いたトランジスタは、オフ状態のリーク電流（オフ電流）が小さくなる。また、チャネル形成層として酸化物半導体層を用いたトランジスタは、閾値電圧のばらつきによる影響が小さい。

【0012】

本発明の一態様は、チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅  $1 \mu m$ あたりのオフ電流が  $1 \times 10^{-13} A$  以下（好ましくは  $1 \times 10^{-17} A$  以下）であるトランジスタを有し、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号及び第5の信号を出力信号として出力する論理回路である。

【0013】

本発明の一態様において、論理回路は、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号を出力する第1の単位論理回路と、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第5の信号を出力する第2の単位論理回路と、を有する構成にすることもできる。

【0014】

本発明の一態様は、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号を出力する第1の単位論理回路と、入力信号として、第1の信号、第2の信号、及びクロック信号である第3の信号が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第5の信号を出力する第2の単位論理回路と、を有し、第1の単位論理回路及び第2の単位論理回路のそれぞれは、ゲート、ソース、及びドレインを有し、ゲートに第3の信号が入力され、ソース及びドレインの一方に第1の信号及び第2の信号のいずれか一方が入力される第1のトランジスタと、ゲート、ソース、及びドレインを有し、ゲートが第1のトランジスタのソース及びドレインの他方に電気的に接続され、ソース及びドレインの一方に高電源電圧及び低電源電圧のいずれか一方が与えられ、ソース及びドレインの他方の電圧が第4の信号又は第5の信号の電圧となる第2のトランジスタと、第1の電極及び第2の電極を有し、第1の電極が第2のトランジスタのゲートに電気的に接続され、第2の電極が第2のトランジスタのソース及びドレインの他方に電気的に接続された第1の容量素子と、ゲート、ソース、及びドレインを有し、ゲートに第3の信号が入力され、ソース及びドレインの一方に第1の信号及び第2の信号の他方が入力される第3のトランジスタと、ゲート、ソース、及びドレインを有し、ゲートが第3のトランジスタのソース及びドレインの他方に電気的に接続され、ソース及びドレインの一方が第2のトランジスタのソース及びドレインのいずれか一方に電気的に接続され、ソース及びドレインの他方に高電源電圧及び低電源電圧の他方が入力された第4のトランジスタと、第1の電極及び第2の電極を有し、第1の電極が第3のトランジスタのソース及びドレインの他方に電気的に接続され、第2の電極に高電源電圧及び低電源電圧の他方が入力された第2の容量素子と、を有し、第1のトランジスタ乃至第4のトランジスタのそれぞれは、チャネル形成層としての機能を有する酸化物半導体層を含み、チャネル幅  $1 \mu m$ あたりのオフ電流が  $1 \times 10^{-13} A$  以下（好ましくは  $1 \times 10^{-17} A$  以下）であ

10

20

30

40

50

る論理回路である。

【0015】

本発明の一態様は、上記記載の論理回路を含むシフトレジスタを備えた駆動回路と、駆動回路により表示状態が制御される画素を含む画素部と、を有する半導体装置である。

【発明の効果】

【0016】

本発明の一態様により、トランジスタにおけるリーク電流を低減することができ、また、トランジスタのリーク電流を低減することにより出力信号の電圧を所望の範囲の値に維持することができるため、誤動作を抑制することができる。

【図面の簡単な説明】

【0017】

【図1】実施の形態1における論理回路の構成の一例を示す図。

【図2】実施の形態1におけるシフトレジスタの構成の一例を示す回路図。

【図3】図2に示すシフトレジスタの動作の一例を説明するためのタイミングチャート。

【図4】実施の形態1における半導体装置を説明するブロック図。

【図5】実施の形態1における信号線駆動回路の構成を説明する図および信号線駆動回路のタイミングチャート。

【図6】トランジスタの作製方法を説明する図。

【図7】トランジスタを説明する図。

【図8】トランジスタの作製方法を説明する図。

【図9】トランジスタを説明する図。

【図10】トランジスタの作製方法を説明する図。

【図11】トランジスタの作製方法を説明する図。

【図12】トランジスタの作製方法を説明する図。

【図13】トランジスタの作製方法を説明する図。

【図14】トランジスタを説明する図。

【図15】半導体装置を説明する図。

【図16】半導体装置の画素等価回路を説明する図。

【図17】半導体装置を説明する図。

【図18】半導体装置を説明する図。

【図19】半導体装置を説明する図。

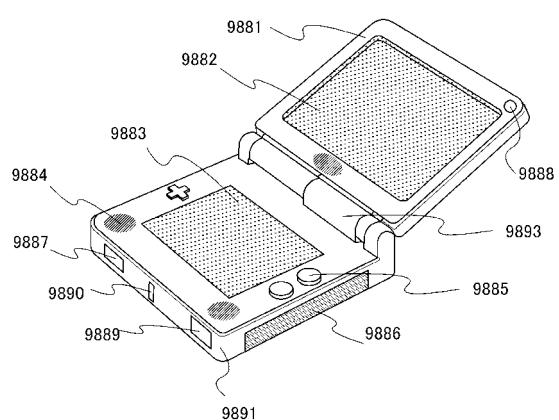

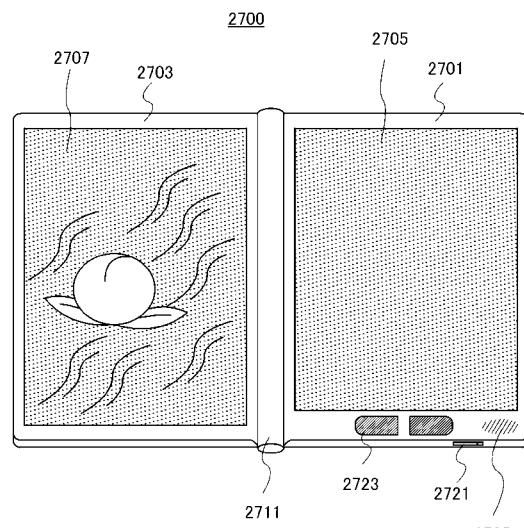

【図20】電子機器を示す図。

【図21】電子機器を示す図。

【図22】電子機器を示す図。

【図23】電子機器を示す図。

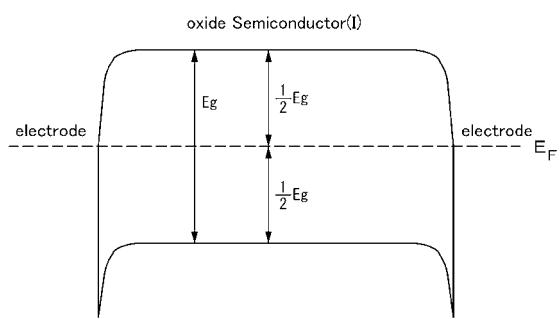

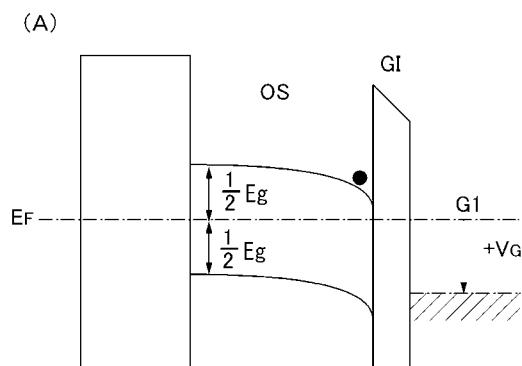

【図24】酸化物半導体を用いたMOSトランジスタのソース - ドレイン間のバンド構造を示す図。

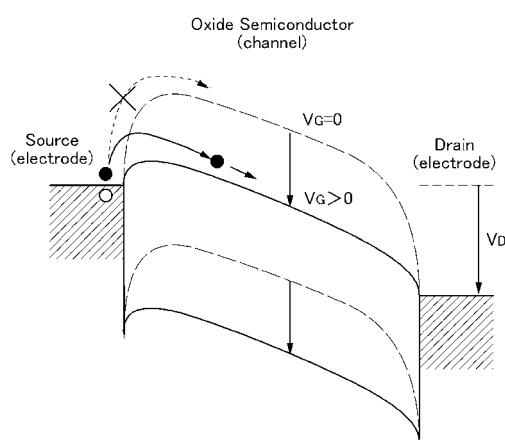

【図25】図24においてドレイン側に正の電圧が印加された状態を示す図。

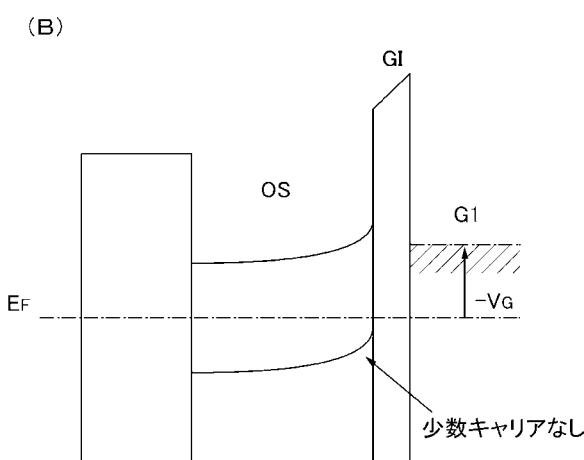

【図26】酸化物半導体を用いたMOSトランジスタのMOS構造のエネルギー・バンド図であり、(A)ゲート電圧を正とした場合、(B)ゲート電圧を負とした場合を示す図。

【図27】シリコンMOSトランジスタのソース - ドレイン間のバンド構造を示す図。

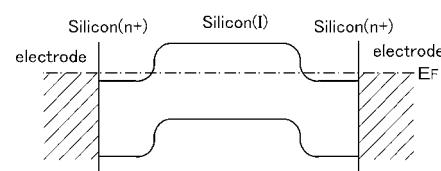

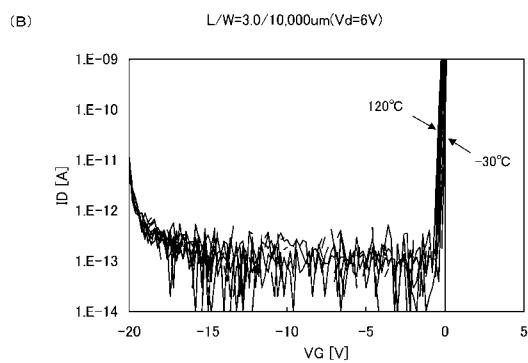

【図28】薄膜トランジスタの初期特性を示す図。

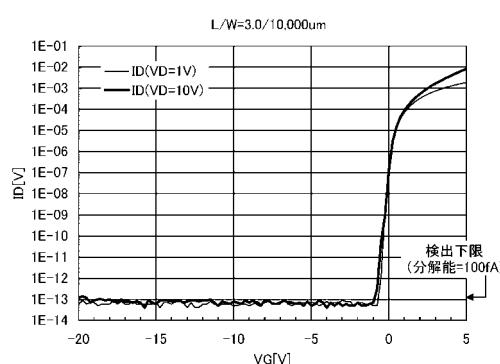

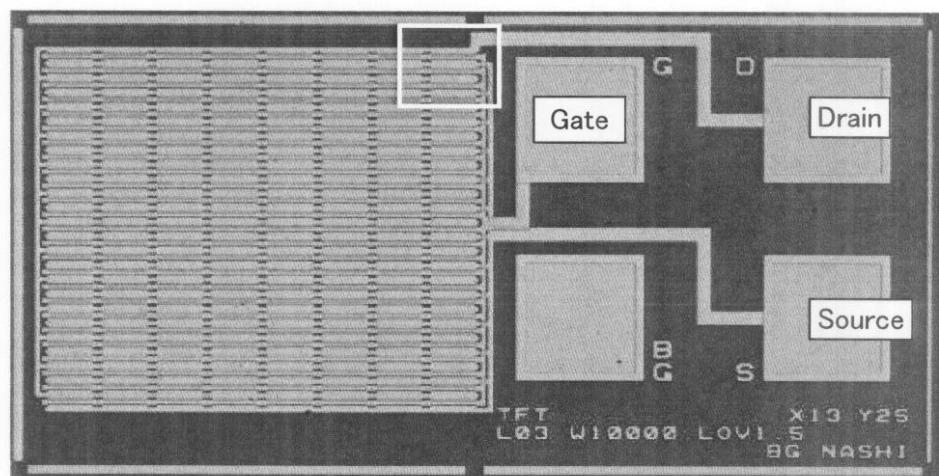

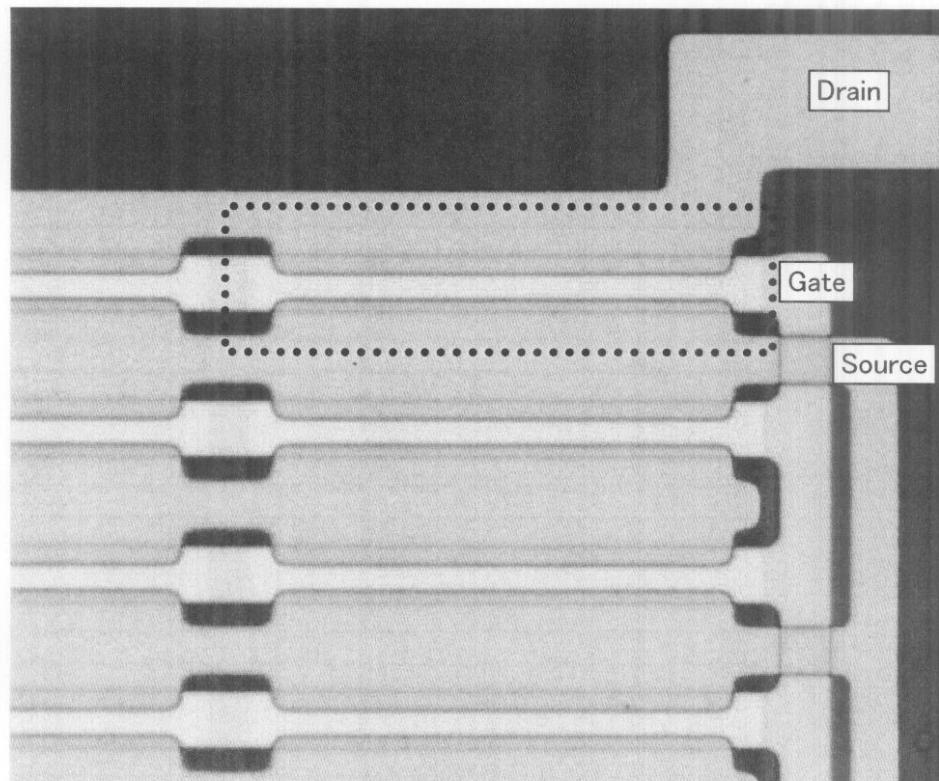

【図29】薄膜トランジスタの構造を示す上面図。

【図30】薄膜トランジスタのVg - Id特性を示す図。

【図31】半導体装置を説明する図。

【発明を実施するための形態】

【0018】

本発明の実施の形態の一例について、図面を用いて以下に説明する。但し、本発明は以下の説明に限定されず、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本発明は以下に示

10

20

30

40

50

す実施の形態の記載内容に限定して解釈されるものではないとする。

【0019】

(実施の形態1)

本実施の形態では、まず本発明の一態様である論理回路について説明する。なお、本明細書において、論理回路とは、特に指定する場合を除き、ある時点における出力信号の状態が、その時点における入力信号の状態のみで決まる論理回路である組み合わせ論理回路と、ある時点における出力信号の状態が、その時点における入力信号の状態だけでなく、それ以前に論理回路がどのような状態であったかによって決まる論理回路である順序論理回路と、を含むものとする。

【0020】

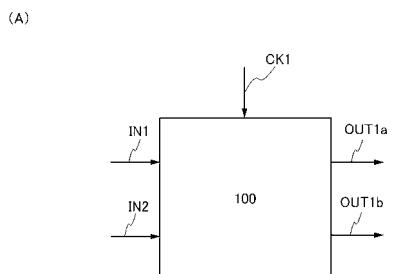

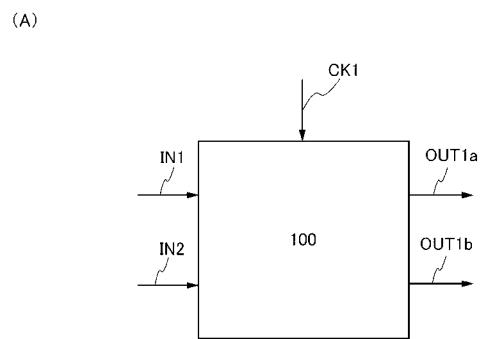

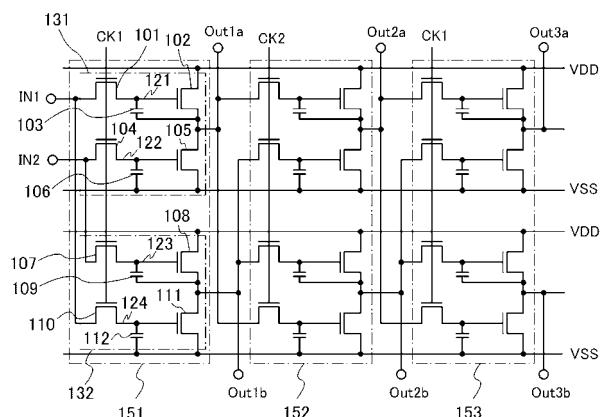

本実施の形態の論理回路の構成の一例について、図1を用いて説明する。図1は本実施の形態における論理回路の構成の一例を示す図である。

【0021】

図1(A)に示す論理回路100には、入力信号として信号IN1、信号IN2、及び信号CK1が入力される。また、図1(A)に示す論理回路100は、出力信号として信号OUT1a及び信号OUT1bを出力する。

【0022】

なお、一般的に電圧とは、ある二点間における電位の差（電位差ともいう）のことをいう。しかし、電圧及び電位の値は、回路図などにおいていずれもボルト（V）で表されることがあるため、区別が困難である。そこで、本明細書では、特に指定する場合を除き、ある一点の電位と基準となる電位（基準電位ともいう）との電位差を、該一点の電圧として用いる場合がある。

【0023】

なお、本明細書における信号としては、例えば電圧、電流、抵抗、又は周波数などを用いたアナログ信号又はデジタル信号を用いることができる。例えば、電圧を用いた信号（電圧信号ともいう）としては、少なくとも第1の電圧状態及び第2の電圧状態を有する信号を用いることが好ましく、例えば第1の電圧状態としてハイレベルの電圧状態及び第2の電圧状態としてローレベルの電圧状態を有する2値のデジタル信号などを用いることができる。なお、2値のデジタル信号において、ハイレベルの電圧を電圧 $V_H$ ともいい、ローレベルの電圧を電圧 $V_L$ ともいう。また、第1の電圧状態の電圧及び第2の電圧状態の電圧は、それぞれ一定値であることが好ましい。しかし、電子回路では、例えばノイズなどの影響があるため、第1の電圧状態の電圧及び第2の電圧状態の電圧は、一定値ではなく、それぞれ一定の範囲内の値であればよい。

【0024】

なお、本明細書において、高電源電圧とは、相対的に高電圧側の電圧（ $V_{DD}$ ともいう）であり、低電源電圧とは、相対的に低電圧側の電圧（ $V_{SS}$ ともいう）である。高電源電圧及び低電源電圧は、それぞれ定数であることが好ましいが、電子回路ではノイズなどにより電圧が所望の値とずれることがある。よって本明細書では、それぞれ一定の範囲内の値であれば、高電源電圧及び低電源電圧とみなすことができる。また、電源電圧の値は、それぞれ適宜設定することができる。なお高電源電圧と低電源電圧は、トランジスタの極性により与えられる場所が入れ替わるため、高電源電圧及び低電源電圧のいずれか一方を高電源電圧及び低電源電圧の一方とし、他方を高電源電圧及び低電源電圧の他方とする。

【0025】

また、本明細書において、第1、第2などの序数を用いた用語は、それぞれの要素の混同を避けるために付したものであり、数的に限定するものではない。

【0026】

信号IN2としては、例えば信号IN1の反転信号などを用いることができる。

【0027】

信号CK1は、論理回路100のクロック信号としての機能を有する。

【0028】

10

20

30

40

50

信号 OUT 1 a は、入力された信号 IN 1 及び信号 IN 2 により電圧状態が設定される信号である。

【 0 0 2 9 】

信号 OUT 1 b は、入力された信号 IN 1 及び信号 IN 2 により電圧状態が設定される信号である。

【 0 0 3 0 】

さらに、図 1 ( A ) に示す論理回路における回路構成の一例について図 1 ( B ) に示す。

図 1 ( B ) に示す論理回路は、単位論理回路 1 3 1 及び単位論理回路 1 3 2 を有する。

【 0 0 3 1 】

単位論理回路 1 3 1 には、信号 IN 1 、信号 IN 2 、及び信号 CK 1 が入力される。また、単位論理回路 1 3 1 は、入力された信号 IN 1 、信号 IN 2 、及び信号 CK 1 に応じて電圧状態が設定された信号 OUT 1 a を出力する機能を有する。

10

【 0 0 3 2 】

単位論理回路 1 3 2 は、信号 IN 1 、信号 IN 2 、及び信号 CK 1 が入力され、入力された信号 IN 1 、信号 IN 2 、及び信号 CK 1 に応じて電圧状態が設定された信号 OUT 1 b を出力する機能を有する。

【 0 0 3 3 】

さらに、単位論理回路 1 3 1 は、トランジスタ 1 0 1 と、トランジスタ 1 0 2 と、容量素子 1 0 3 と、トランジスタ 1 0 4 と、トランジスタ 1 0 5 と、容量素子 1 0 6 と、を有し、単位論理回路 1 3 2 は、トランジスタ 1 0 7 と、トランジスタ 1 0 8 と、容量素子 1 0 9 と、トランジスタ 1 1 0 と、トランジスタ 1 1 1 と、容量素子 1 1 2 と、を有する。

20

【 0 0 3 4 】

なお、本明細書において、トランジスタとしては、例えば電界効果トランジスタを用いることができる。

【 0 0 3 5 】

また、本明細書において、電界効果トランジスタは、ゲート、ソース、及びドレインを少なくとも有する。電界効果トランジスタとしては、例えば薄膜トランジスタ ( TFT ともいう ) を用いることができる。また、電界効果トランジスタとしては、例えばトップゲート型、又はボトムゲート型のトランジスタを用いることができる。また、電界効果トランジスタは、N 型又はP 型の導電型にすることができる。図 1 に示す論理回路では、トランジスタの一例として全て同一の導電型の電界効果トランジスタを用いた場合について説明する。全て同一の導電型とすることにより、異なる複数の導電型のトランジスタを用いる場合に比べて作製工程数を低減することができる。

30

【 0 0 3 6 】

なお、ゲートとは、ゲート電極及びゲート配線の一部又は全部のことをいう。ゲート配線とは、少なくとも一つのトランジスタのゲート電極と、別の電極や別の配線とを電気的に接続させるための配線のことをいい、例えば表示装置における走査線もゲート配線に含まれる。

【 0 0 3 7 】

ソースとは、ソース領域、ソース電極、及びソース配線の一部又は全部のことをいう。ソース領域とは、半導体層のうち、抵抗値がチャネル形成層より低い領域のことをいう。ソース電極とは、ソース領域に接続される部分の導電層のことをいう。ソース配線とは、少なくとも一つのトランジスタのソース電極と、別の電極や別の配線とを電気的に接続させるための配線のことをいい、例えば表示装置における信号線がソース電極に電気的に接続される場合にはソース配線に信号線も含まれる。

40

【 0 0 3 8 】

ドレインとは、ドレイン領域、ドレイン電極、及びドレイン配線の一部又は全部のことをいう。ドレイン領域とは、半導体層のうち、抵抗値がチャネル形成領域より低い領域のことをいう。ドレイン電極とは、ドレイン領域に接続される部分の導電層のことをいう。ドレイン配線とは、少なくとも一つのトランジスタのドレイン電極と、別の電極や別の配線

50

とを電気的に接続させるための配線のことをいい、例えば表示装置における信号線がドレイン電極に電気的に接続される場合にはドレイン配線に信号線も含まれる。

【0039】

また、本書類（明細書、特許請求の範囲又は図面など）において、トランジスタのソースとドレインは、トランジスタの構造や動作条件などによって互いに入れ替わるため、いずれがソース又はドレインであるかを限定することが困難である。そこで、本書類（明細書、特許請求の範囲又は図面など）においては、ソース及びドレインのいずれかから任意に選択した一方をソース及びドレインの一方と表記し、他方をソース及びドレインの他方と表記する。

【0040】

また、本書類（明細書、特許請求の範囲又は図面など）において、容量素子は、第1の電極と、第2の電極と、第1の電極及び第2の電極の間の電圧が印加される誘電体と、を有する構成である。

【0041】

トランジスタ101は、ゲートに信号CK1が入力され、ソース及びドレインの一方に信号IN1が入力される。

【0042】

トランジスタ102は、ゲートがトランジスタ101のソース及びドレインの他方に電気的に接続され、ソース及びドレインの一方に高電源電圧及び低電源電圧の一方が与えられる。図1では、一例としてトランジスタ102のソース及びドレインの一方に高電源電圧が与えられるとする。なお、トランジスタ102のゲートと、トランジスタ101のソース及びドレインの他方との接続箇所をノード121という。また、図1に示す論理回路は、トランジスタ102のソース及びドレインの他方の電圧を信号OUT1aとして出力する。

【0043】

容量素子103は、第1の電極がトランジスタ102のゲートに電気的に接続され、第2の電極がトランジスタ102のソース及びドレインの他方に電気的に接続される。なお、トランジスタ102のゲートとソース及びドレインの他方との間に寄生容量を有する場合、容量素子103として該寄生容量を用いることもできる。

【0044】

トランジスタ104は、ゲートに信号CK1が入力され、ソース及びドレインの一方に信号IN2が入力される。

【0045】

トランジスタ105は、ゲートがトランジスタ104のソース及びドレインの他方に電気的に接続され、ソース及びドレインの一方がトランジスタ102のソース及びドレインの他方に電気的に接続され、ソース及びドレインの他方に高電源電圧及び低電源電圧の他方が与えられる。図1に示す論理回路では、一例としてトランジスタ105のソース及びドレインの他方に低電源電圧が与えられるものとする。なお、トランジスタ105のゲートと、トランジスタ104のソース及びドレインの他方との接続箇所をノード122という。

【0046】

容量素子106は、第1の電極がトランジスタ104のソース及びドレインの他方に電気的に接続され、第2の電極に高電源電圧及び低電源電圧の他方が与えられる。図1に示す論理回路では、一例として容量素子106の第2の電極に低電源電圧が与えられるものとする。

【0047】

トランジスタ107は、ゲートに信号CK1が入力され、ソース及びドレインの一方に信号IN2が入力される。

【0048】

トランジスタ108は、ゲートがトランジスタ107のソース及びドレインの他方に電気

10

20

30

40

50

的に接続され、ソース及びドレインの一方に高電源電圧及び低電源電圧の一方が与えられる。なお、図1に示す論理回路は、トランジスタ108のソース及びドレインの他方の電圧を信号OUT1bとして出力する。なお、トランジスタ108のゲートと、トランジスタ107のソース及びドレインの他方との接続箇所をノード123という。

【0049】

容量素子109は、第1の電極がトランジスタ108のゲートに電気的に接続され、第2の電極がトランジスタ108のソース及びドレインの他方に電気的に接続される。なお、トランジスタ108のゲートと、ソース及びドレインの他方との間に寄生容量を有する場合には、該寄生容量を容量素子109として用いることができる。

【0050】

トランジスタ110は、ゲートに信号CK1が入力され、ソース及びドレインの一方に信号IN1が入力される。

【0051】

トランジスタ111は、ゲートがトランジスタ110のソース及びドレインの他方に電気的に接続され、ソース及びドレインの一方がトランジスタ108のソース及びドレインの他方に電気的に接続され、ソース及びドレインの他方に高電源電圧及び低電源電圧の他方が与えられる。図1に示す論理回路では、一例として、トランジスタ111のソース及びドレインの他方に低電源電圧が与えられるものとする。なお、トランジスタ111のゲートと、トランジスタ110のソース及びドレインの他方との接続箇所をノード124という。

【0052】

容量素子112は、第1の電極がトランジスタ110のソース及びドレインの他方に電気的に接続され、第2の電極に高電源電圧及び低電源電圧の他方が与えられる。なお、図1に示す論理回路では、容量素子112の第2の電極に低電源電圧が与えられるものとして説明する。

【0053】

なお、トランジスタ101、トランジスタ102、トランジスタ104、トランジスタ105、トランジスタ107、トランジスタ108、トランジスタ110、及びトランジスタ111としては、チャネル形成層としての機能を有する酸化物半導体層を有するトランジスタを適用することができる。なお、チャネル形成層の水素濃度は、 $5 \times 10^{19} / \text{cm}^3$ 以下、好ましくは $5 \times 10^{18} / \text{cm}^3$ 以下、さらに好ましくは $5 \times 10^{17} / \text{cm}^3$ 以下とする。該水素濃度は、例えば二次イオン質量分析法(SIMS: Secondary Ion Mass Spectrometry)による測定値である。またトランジスタのキャリア濃度は、 $1 \times 10^{14} / \text{cm}^3$ 以下、好ましくは $1 \times 10^{12} / \text{cm}^3$ 以下とする。

【0054】

図1に一例として示すように、本実施の形態の論理回路の一例は、入力信号として第1の信号(例えば信号IN1)、第2の信号(例えば信号IN2)、及び第3の信号(例えば信号CK1)が入力され、入力された第1の信号乃至第3の信号に応じて電圧状態が設定された第4の信号(例えば信号OUT1a)及び第5の信号(例えば信号OUT1b)を出力信号として出力する構成である。

【0055】

さらに、本実施の形態の論理回路の一例は、全て同一の導電型のトランジスタを用いて構成される。これにより、複数の導電型のトランジスタを用いる場合に比べて作製工程数を低減することができる。同一の導電型のトランジスタとしては、例えばN型トランジスタ又はP型トランジスタを用いることができる。

【0056】

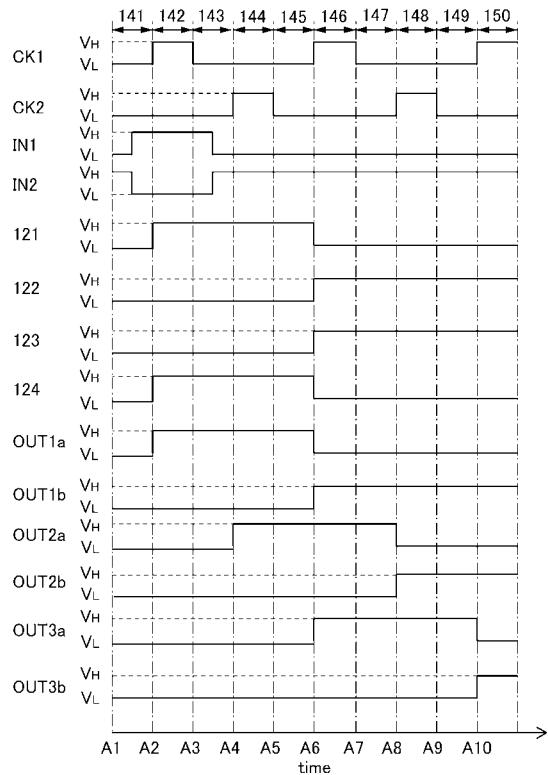

さらに、図1に示す論理回路を用いたシフトレジスタの構成の一例について図2に示す。図2は、シフトレジスタの構成の一例を示す回路図である。なお、論理回路の数は必ずしも限定されるものではなく、少なくとも2段以上の論理回路を有する構成とすればよい。な

10

20

30

40

50

お、図2では、一例としてシフトレジスタを構成するトランジスタが全てN型トランジスタである例について説明するが、これに限定されず、P型トランジスタを用いて構成することもできる。

【0057】

図2に示すシフトレジスタは、論理回路151、論理回路152、及び論理回路153を有する。なお、それぞれの各論理回路において、図1に示す論理回路と同じ部分については図1に示す論理回路の説明を適宜援用する。なお、論理回路151乃至論理回路153は、全て順序論理回路とする。

【0058】

論理回路151には、図1に示す論理回路と同様に、入力信号としてトランジスタ101のゲート、トランジスタ104のゲート、トランジスタ107のゲート、及びトランジスタ110のゲートに信号CK1が入力され、入力信号としてトランジスタ101のソース及びドレインの一方、並びにトランジスタ110のソース及びドレインの一方に信号IN1が入力され、入力信号としてトランジスタ104のソース及びドレインの一方、並びにトランジスタ107のソース及びドレインの一方に信号IN2が入力される。また、論理回路151は、入力された各信号の状態に応じて電圧状態が設定された信号OUT1a及び信号OUT1bを出力信号として出力する。

【0059】

論理回路152は、信号OUT1a、信号OUT1b、及び信号CK2が入力信号として入力され、入力された信号に応じて電圧状態が設定された信号OUT2a及び信号OUT2bを出力信号として出力する。また、論理回路152の回路構成については、論理回路151の回路構成と同じである。

【0060】

信号CK2は、論理回路151における信号CK1の代わりに論理回路152に入力される信号である。信号CK2としては、例えば信号CK1と異なるタイミングでハイレベルになるクロック信号を用いることができる。本実施の形態におけるシフトレジスタでは、信号CK1が入力される論理回路と信号CK2が入力される論理回路とが交互に電気的に接続された構成とすることができます。例えば、シフトレジスタにおける奇数段の論理回路には信号CK1及び信号CK2の一方が入力され、偶数段の論理回路には信号CK1及び信号CK2の他方が入力される構成とすることもできる。

【0061】

論理回路153は、信号OUT2a、信号OUT2b、及び信号CK1が入力され、入力された信号に応じて電圧状態が設定された信号OUT3a及び信号OUT3bを出力信号として出力する。また、論理回路153の回路構成については、論理回路151の回路構成と同じである。

【0062】

次に、図2に示すシフトレジスタの動作の一例について図3を用いて説明する。図3は、図2に示すシフトレジスタの動作の一例を説明するためのタイミングチャートであり、信号CK1、信号CK2、信号IN1、信号IN2、ノード121、ノード122、ノード123、ノード124、信号OUT1a、信号OUT1b、信号OUT2a、信号OUT2b、信号OUT3a、及び信号OUT3bの信号波形をそれぞれ示したものである。なお、図3を用いて説明する図2に示すシフトレジスタの動作の一例では、各信号を2値のデジタル信号とし、信号CK1及び信号CK2をクロック信号として説明する。また、高電源電圧の値をハイレベルの電圧VHと等しいとし、低電源電圧の値をローレベルの電圧VLと等しいものとする。また、本実施の形態における論理回路の動作では、図3に示す各信号の電圧状態を反転させることもできる。

【0063】

図2に示すシフトレジスタの動作は、複数の期間に分けて説明することができる。各期間における動作について以下に説明する。

【0064】

10

20

30

40

50

まず、論理回路 151 に着目して各期間の動作を説明する。期間 141 では、信号 CK1 はローレベルであり、信号 CK2 はローレベルであり、信号 IN1 はローレベルであり、信号 IN2 はハイレベルである。

【0065】

このとき、論理回路 151 における信号 OUT1a、信号 OUT1b、信号 OUT2a はローレベルである。

【0066】

次に、期間 142 では、信号 CK1 が時刻 A2 にてハイレベルになり、信号 CK2 はローレベルのままであり、信号 IN1 はハイレベルであり、信号 IN2 はローレベルである。なお、信号 IN1 は、期間 141 の間にハイレベルになってもよく、信号 IN2 は、期間 141 の間にローレベルになってもよい。 10

【0067】

このとき、論理回路 151 では、トランジスタ 101 及びトランジスタ 110 がオン状態になり、トランジスタ 104 及びトランジスタ 107 はオフ状態である。さらに、信号 IN1 に応じて、ノード 121 の電位及びノード 124 の電位が大きくなり、電圧  $V_H$  と同じになる。さらに、ノード 121 の電位に応じてトランジスタ 102 がオン状態になり、信号 OUT1a の電圧が上昇する。このとき、信号 OUT1a の電圧は、容量素子 103 によりノード 121 の電位に合わせて上昇し、電圧  $V_H$  と同じになる。いわゆるブーストアップである。また、ノード 124 の電位が信号 IN1 の電圧に応じて大きくなり、電圧  $V_H$  と同じである。さらに、ノード 124 の電位に応じてトランジスタ 111 がオン状態になり、信号 OUT1b の電圧が電圧  $V_L$  になる。このとき、容量素子 106 には、ノード 122 の電位と低電源電圧に応じた電圧が印加され、容量素子 106 によりノード 122 の電位は、一定期間保持される。また、容量素子 112 には、ノード 124 の電位と低電源電圧に応じた電圧が印加され、容量素子 112 によりノード 124 の電位は、一定期間保持される。トランジスタ 104 及びトランジスタ 110 のオフ電流が無い場合、容量素子 106 及び容量素子 112 に保持された電圧は、一定の範囲の値に保持されるため、本実施の形態の論理回路に適用可能なトランジスタのように、オフ電流の低いトランジスタを用いることにより、トランジスタがオフ状態のときのノード 122 の電位及びノード 124 の電位を一定の範囲内の値を維持しながら保持しておくことができる。 20

【0068】

次に、期間 143 では、信号 CK1 が時刻 A3 にてローレベルになり、信号 CK2 はローレベルのままであり、信号 IN1 はローレベルになり、信号 IN2 はハイレベルになる。 30

【0069】

このとき、論理回路 151 は、トランジスタ 101、トランジスタ 104、トランジスタ 107、及びトランジスタ 110 がオフ状態になり、ノード 121 の電位は電圧  $V_H$  と同じ値に保持され、ノード 122 の電位は電圧  $V_L$  に保持され、ノード 123 の電位は電圧  $V_L$  に保持され、ノード 124 の電位は電圧  $V_H$  に保持され、信号 OUT1a はハイレベルのままであり、信号 OUT1b はローレベルのままである。

【0070】

次に、期間 144 では、信号 CK1 はローレベルのままであり、信号 CK2 が時刻 A4 にてハイレベルになり、信号 IN1 はローレベルのままであり、信号 IN2 はハイレベルのままである。なお、信号 IN1 は、時刻 A3 にてローレベルになってもよく、信号 IN2 は、時刻 A3 にてハイレベルになってもよい。 40

【0071】

このとき、論理回路 151 は、期間 143 における状態を維持し、信号 OUT1a はハイレベルのままであり、信号 OUT1b はローレベルのままである。

【0072】

次に、期間 145 において、信号 CK1 はローレベルのままであり、信号 CK2 が時刻 A5 にてローレベルになり、信号 IN1 はローレベルのままであり、信号 IN2 はハイレベルのままである。 50

## 【0073】

このとき、論理回路151は、期間144における状態を維持し、信号OUT1aはハイレベルのままであり、信号OUT1bはローレベルのままである。

## 【0074】

次に、期間146において、信号CK1が時刻A6にてハイレベルになり、信号CK2はローレベルのままであり、信号IN1はローレベルのままであり、信号IN2はハイレベルのままである。

## 【0075】

このとき、論理回路151は、トランジスタ101、トランジスタ104、トランジスタ107、及びトランジスタ110がオン状態になり、ノード121の電位及びノード124の電位が電圧V<sub>L</sub>と同じになる。さらに、ノード121の電位及びノード124の電位に応じてトランジスタ102及びトランジスタ111がオフ状態になる。また、ノード122の電位及びノード123の電位が大きくなり、電圧V<sub>H</sub>と同じになる。さらに、ノード122の電位及びノード123の電位に応じてトランジスタ105及びトランジスタ111がオン状態になり、信号OUT1aの電圧が電圧V<sub>L</sub>になり、信号OUT1bの電圧が電圧V<sub>H</sub>になる。このとき、容量素子106には、ノード122の電位と低電源電圧に応じた電圧が印加され、容量素子106によりノード122の電位は一定期間保持される。また、容量素子112には、ノード124の電位と低電源電圧に応じた電圧が印加され、容量素子112によりノード124の電位は一定期間保持される。トランジスタが104及びトランジスタ110のオフ電流が無い場合、容量素子106及び容量素子112に保持された電圧は、一定の範囲の値に保持されるため、本実施の形態の論理回路に適用可能なトランジスタのように、オフ電流の低いトランジスタを用いることにより、トランジスタがオフ状態のときのノード122の電位及びノード124の電位を一定の範囲内の値を維持しながら保持しておくことができる。

10

20

30

40

50

## 【0076】

その後の期間において、論理回路151は、一定期間同じ状態を維持し、信号OUT1aの電圧は、一定期間ローレベルに維持され、信号OUT1bの電圧は、一定期間ハイレベルに維持される。

## 【0077】

さらに、論理回路151以降の段の論理回路（ここでは一例として論理回路152及び論理回路153）について説明する。なお、各論理回路内の動作は、入力信号及び出力信号の状態を除いては論理回路151と同じであるため、ここでの説明は省略する。

## 【0078】

まず、論理回路152は、期間144において、出力信号である信号OUT2aが時刻A4にてハイレベルになり、信号OUT2bはローレベルのままである。

## 【0079】

さらに、期間145乃至期間147において、論理回路152は、期間144と同じ状態を維持し、信号OUT2aはハイレベルのままであり、信号OUT2bはローレベルのままである。

## 【0080】

さらに、期間148において、論理回路152は、信号OUT2aが時刻A8にてローレベルになり、信号OUT2bが時刻A8にてハイレベルになる。

## 【0081】

さらに、論理回路153は、期間146において、出力信号である信号OUT2aが時刻A6にてハイレベルになり、信号OUT2bはローレベルのままである。

## 【0082】

さらに、期間147乃至期間149において、論理回路153は、期間146と同じ状態を維持し、信号OUT3aはハイレベルのままであり、信号OUT3bはローレベルのままである。

## 【0083】

さらに、期間 150において、論理回路 152は、信号 OUT3aが時刻 A10にてローレベルになり、信号 OUT3bはハイレベルになる。

【0084】

また、図示しないが、3段以上の論理回路を用いてシフトレジスタが構成される場合であっても同様に、段毎に論理回路における出力信号の電圧状態が順次変化する。

【0085】

以上のように、本実施の形態のシフトレジスタは、各段の論理回路において、2つの異なる電圧状態の出力信号を出力することができる。また、本実施の形態のシフトレジスタは、出力信号をハイレベル又はローレベルにするためのトランジスタのゲート電位を一定期間保持するための保持容量を有する構成であり、また、トランジスタとしてオフ電流が低く、チャネル形成層として酸化物半導体層を有するトランジスタを用いた構成である。該構成にすることにより、トランジスタを介してのリーク電流が低減するため、保持容量に保持された電圧を一定期間、一定の範囲の値に維持することができるため、誤動作を抑制することができる。また、トランジスタによるリーク電流が低減するため、消費電力を低減することもできる。また、チャネル形成層として酸化物半導体層を有するトランジスタは、酸化物半導体層の不純物濃度が低いため、閾値電圧のばらつきが小さい。一般的に複数のトランジスタを備えるシフトレジスタにおいて、トランジスタの閾値電圧のばらつきが大きいと全てのトランジスタをオンさせるときの電圧が高いため、チャネル形成層として酸化物半導体層を有するトランジスタを本実施の形態のシフトレジスタに用いることにより、消費電力を低減することができる。

10

20

30

40

50

【0086】

さらに、本実施の形態では、本発明の一態様であるシフトレジスタを駆動回路に用いた半導体装置について説明する。なお、本実施の形態では、一例として同一基板上に少なくとも駆動回路の一部と、該駆動回路により表示状態が制御される画素を含む画素部を有する表示装置について説明する。

【0087】

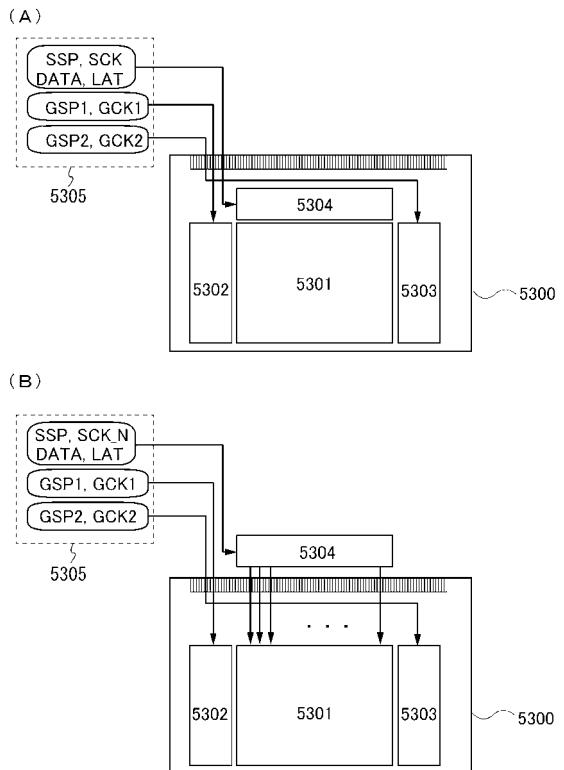

アクティブマトリクス型表示装置のブロック図の一例を図4(A)に示す。表示装置の基板 5300上には、画素部 5301、第1の走査線駆動回路 5302、第2の走査線駆動回路 5303、信号線駆動回路 5304を有する。画素部 5301には、複数の信号線が信号線駆動回路 5304から延伸して配置され、複数の走査線が第1の走査線駆動回路 5302、及び第2の走査線駆動回路 5303から延伸して配置されている。なお走査線と信号線との交差領域には、各々、表示素子を有する画素がマトリクス状に配置されている。また、表示装置の基板 5300は、FPC(Flexible Printed Circuit)等の接続部を介して、タイミング制御回路 5305(コントローラ、制御ICともいう)に接続されている。

【0088】

図4(A)では、第1の走査線駆動回路 5302、第2の走査線駆動回路 5303、信号線駆動回路 5304は、画素部 5301と同じ基板 5300上に形成される。そのため、外部に設ける駆動回路等の部品の数が減るので、コストの低減を図ることができる。また、基板 5300外部に駆動回路を設けた場合、配線を延伸させる必要が生じ、配線間の接続数が増える。同じ基板 5300上に駆動回路を設けた場合、その配線間の接続数を減らすことができ、信頼性の向上、又は歩留まりの向上を図ることができる。

【0089】

なお、タイミング制御回路 5305は、第1の走査線駆動回路 5302に対し、一例として、第1の走査線駆動回路用スタート信号(GSP1)、第1の走査線駆動回路用クロック信号(GCK1)を供給する。また、タイミング制御回路 5305は、第2の走査線駆動回路 5303に対し、一例として、第2の走査線駆動回路用スタート信号(GSP2)(スタートパルスともいう)、走査線駆動回路用クロック信号(GCK2)を供給する。また、タイミング制御回路 5305は、信号線駆動回路 5304に対し、一例として、信号線駆動回路用スタート信号(SSP)、信号線駆動回路用クロック信号(SCK)、ビ

デオ信号用データ（DATA）（単にビデオ信号ともいう）、ラッチ信号（LAT）を供給する。なお、各クロック信号は、周期のずれた複数のクロック信号でもよいし、クロック信号を反転させた信号（CKB）とともに供給されるものであってもよい。また、第1の走査線駆動回路用スタート信号、第2の走査線駆動回路用スタート信号、走査線駆動回路用クロック信号、信号線駆動回路用スタート信号、及び信号線駆動回路用クロック信号は、それぞれ複数あってもよい。本実施の形態の半導体装置では、第1の走査線駆動回路5302と第2の走査線駆動回路5303との一方を省略することが可能である。

【0090】

図4（B）では、駆動周波数が低い回路（例えば、第1の走査線駆動回路5302、第2の走査線駆動回路5303）を画素部5301と同じ基板5300に形成し、信号線駆動回路5304を画素部5301とは別の基板に形成する構成について示している。当該構成により、単結晶半導体を用いたトランジスタと比較すると電界効果移動度が小さい薄膜トランジスタによって、基板5300に形成する駆動回路を構成することができる。したがって、表示装置の大型化、工程数の削減、コストの低減、又は歩留まりの向上などを図ることができる。

10

【0091】

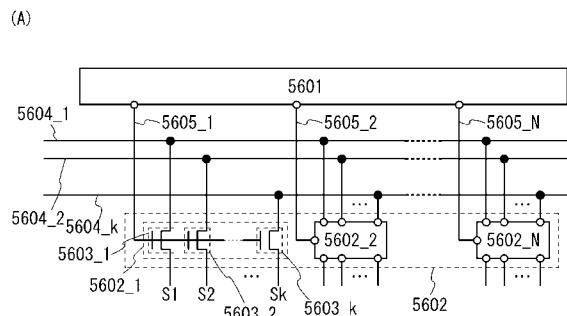

また、図5（A）、図5（B）ではNチャネル型TFTで構成する信号線駆動回路の構成、動作について一例を示し説明する。

【0092】

図5（A）に示す信号線駆動回路は、シフトレジスタ5601、及びスイッチング回路5602を有する。スイッチング回路5602は、複数のスイッチング回路を有する。スイッチング回路5602\_1～5602\_N（Nは2以上の自然数）は、各々、薄膜トランジスタ5603\_1～5603\_k（kは2以上の自然数）という複数のトランジスタを有する。ここでは、薄膜トランジスタ5603\_1～5603\_kが、Nチャネル型TFTである例を説明する。

20

【0093】

信号線駆動回路の接続関係について、スイッチング回路5602\_1を例にして説明する。薄膜トランジスタ5603\_1～5603\_kのソース及びドレインの一方は、各々、配線5604\_1～5604\_kと電気的に接続される。薄膜トランジスタ5603\_1～5603\_kのソース及びドレインの他方は、各々、信号線S1～Skと電気的に接続される。薄膜トランジスタ5603\_1～5603\_kのゲートは、配線5605\_1と電気的に接続される。

30

【0094】

シフトレジスタ5601は、配線5605\_1～5605\_Nに順番にハイレベルの信号を出力し、スイッチング回路5602\_1～5602\_Nを順番に選択する機能を有する。

【0095】

スイッチング回路5602\_1は、配線5604\_1～5604\_kと信号線S1～Skとの導通状態を制御する機能、即ち配線5604\_1～5604\_kの電位を信号線S1～Skに供給するか否かを制御する機能を有する。このように、スイッチング回路5602\_1は、セレクタとしての機能を有する。また、薄膜トランジスタ5603\_1～5603\_kは、各々、配線5604\_1～5604\_kと信号線S1～Skとの導通状態を制御する機能、即ち配線5604\_1～5604\_kの電位を信号線S1～Skに供給する機能を有する。このように、薄膜トランジスタ5603\_1～5603\_kは、各々、スイッチとしての機能を有する。

40

【0096】

なお、配線5604\_1～5604\_kには、各々、ビデオ信号用データ（DATA）が入力される。ビデオ信号用データ（DATA）は、画像情報又は画像信号に応じたアナログ信号である場合が多い。

【0097】

50

次に、図5(A)の信号線駆動回路の動作について、図5(B)のタイミングチャートを参照して説明する。図5(B)には、信号Sout\_1～Sout\_N、及び信号Vdata\_1～Vdata\_kの一例を示す。信号Sout\_1～Sout\_Nは、各々、シフトレジスタ5601の出力信号の一例であり、信号Vdata\_1～Vdata\_kは、各々、配線5604\_1～5604\_kに入力される信号の一例である。なお、信号線駆動回路の1動作期間は、表示装置における1ゲート選択期間に対応する。1ゲート選択期間は、一例として、期間T1～期間TNに分割される。期間T1～TNは、各々、選択された行に属する画素にビデオ信号用データ(DATA)を書き込むための期間である。

#### 【0098】

期間T1～期間TNにおいて、シフトレジスタ5601は、ハイレベルの信号を配線5605\_1～5605\_Nに順番に出力する。例えば、期間T1において、シフトレジスタ5601は、ハイレベルの信号を配線5605\_1に出力する。すると、薄膜トランジスタ5603\_1～5603\_kはオンになるので、配線5604\_1～5604\_kと、信号線S1～Skとが導通状態になる。このとき、配線5604\_1～5604\_kには、Data(S1)～Data(Sk)が入力される。Data(S1)～Data(Sk)は、各々、薄膜トランジスタ5603\_1～5603\_kを介して、選択された行に属する画素のうち、1列目～k列目の画素に書き込まれる。こうして、期間T1～TNにおいて、選択された行に属する画素に、k列ずつ順番にビデオ信号用データ(DATA)が書き込まれる。

#### 【0099】

以上のように、ビデオ信号用データ(DATA)が複数の列ずつ画素に書き込まれることによって、ビデオ信号用データ(DATA)の数、又は配線の数を減らすことができる。よって、外部回路との接続数を減らすことができる。また、ビデオ信号が複数の列ずつ画素に書き込まれることによって、書き込み時間を長くすることができ、ビデオ信号の書き込み不足を防止することができる。

#### 【0100】

なお、シフトレジスタ5601としては、本発明の一態様であるシフトレジスタを用いることができる。

#### 【0101】

次に、走査線駆動回路の構成について説明する。走査線駆動回路は、シフトレジスタを有している。また場合によってはレベルシフタやバッファ等を有していてもよい。走査線駆動回路では、シフトレジスタによって選択信号が生成される。生成された選択信号はバッファにおいて緩衝増幅され、対応する走査線に供給される。走査線には、1ライン分の画素のトランジスタのゲートが電気的に接続されている。そして、1ライン分の画素のトランジスタを一斉にONにしなくてはならないので、バッファは大きな電流を流すことが可能なものが用いられる。

#### 【0102】

以上のように、本発明の一態様であるシフトレジスタは、半導体装置の駆動回路に適用することが可能である。本発明の一態様であるシフトレジスタを用いることにより、単位画像の表示期間を延ばすことができるため、例えば静止画などを表示する場合など消費電力を低減することができる。

#### 【0103】

##### (実施の形態2)

本実施の形態は、本明細書で開示する論理回路及び半導体装置を構成するトランジスタに適用できる薄膜トランジスタの例を示す。

#### 【0104】

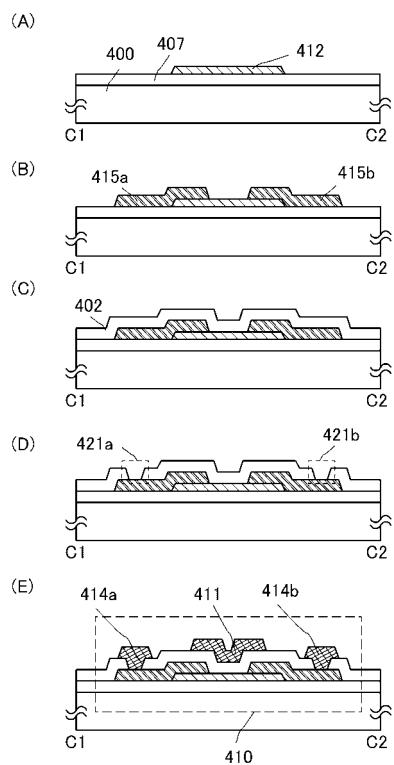

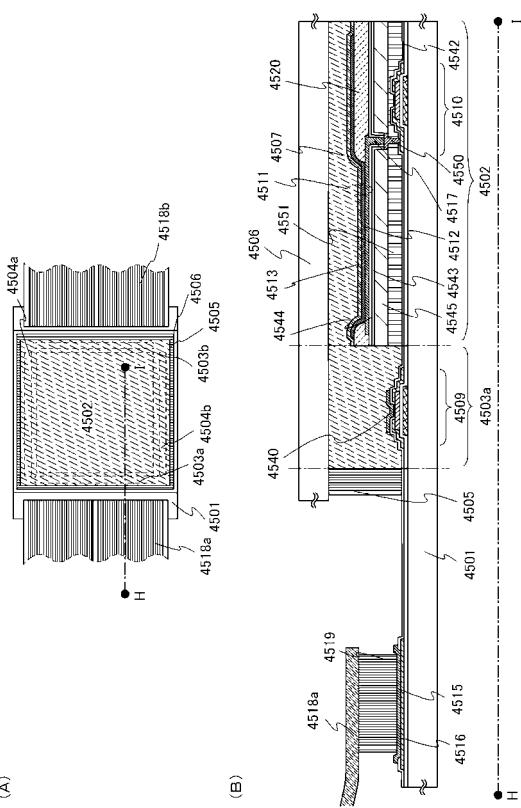

本実施の形態の半導体装置及び半導体装置の作製方法の一形態を、図31及び図6を用いて説明する。

#### 【0105】

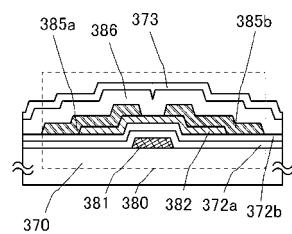

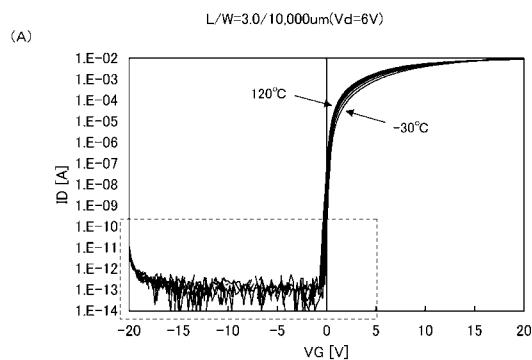

図31(A)(B)に半導体装置の平面及び断面構造の一例を示す。図31(A)(B)

10

20

30

40

50

に示す薄膜トランジスタ 410 は、トップゲート構造の薄膜トランジスタの一つである。

【0106】

図 31 (A) はトップゲート構造の薄膜トランジスタ 410 の平面図であり、図 31 (B) は図 31 (A) の線 C1 - C2 における断面図である。

【0107】

薄膜トランジスタ 410 は、基板 400 上に、絶縁層 407、酸化物半導体層 412、ソース電極層又はドレイン電極層 415a、及びソース電極層又はドレイン電極層 415b、ゲート絶縁層 402、ゲート電極層 411 を含み、ソース電極層又はドレイン電極層 415a、ソース電極層又はドレイン電極層 415b にそれぞれ配線層 414a、配線層 414b が接して設けられ電気的に接続している。

10

【0108】

また、薄膜トランジスタ 410 はシングルゲート構造の薄膜トランジスタを用いて説明したが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

【0109】

以下、図 6 (A) 乃至 (E) を用い、基板 400 上に薄膜トランジスタ 410 を作製する工程を説明する。

【0110】

絶縁表面を有する基板 400 に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

20

【0111】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、一般に酸化ホウ素 ( $B_2O_3$ ) と比較して酸化バリウム ( $BaO$ ) を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$  より  $BaO$  を多く含むガラス基板を用いることが好ましい。

【0112】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラス基板などを用いることができる。また、プラスチック基板等も適宜用いることができる。

30

【0113】

まず、絶縁表面を有する基板 400 上に下地膜となる絶縁層 407 を形成する。酸化物半導体層と接する絶縁層 407 は、酸化シリコン層、酸化窒化シリコン層、酸化アルミニウム層、又は酸化窒化アルミニウム層などの酸化物絶縁層を用いると好ましい。絶縁層 407 の形成方法としては、プラズマ CVD 法又はスパッタリング法等を用いることができるが、絶縁層 407 中に水素が多量に含まれないようにするために、スパッタリング法で絶縁層 407 を成膜することが好ましい。

40

【0114】

本実施の形態では、絶縁層 407 として、スパッタリング法により酸化シリコン層を形成する。基板 400 を処理室へ搬送し、水素及び水分が除去された高純度酸素を含むスパッタリングガスを導入しシリコンターゲットを用いて、基板 400 に絶縁層 407 として、酸化シリコン層を成膜する。また基板 400 は室温でもよいし、加熱されていてもよい。

【0115】

例えば、石英（好ましくは合成石英）をターゲットとして用い、基板温度 108°C、基板とターゲットの間との距離 (T-S 間距離) を 60 mm、圧力 0.4 Pa、高周波電源 1.5 kW、酸素及びアルゴン（酸素流量 25 sccm : アルゴン流量 25 sccm = 1 : 1）雰囲気下で RF スパッタリング法により酸化シリコン膜を成膜する。膜厚は 100 nm とする。なお、石英（好ましくは合成石英）に代えてシリコンターゲットを酸化シリコ

50

ン膜を成膜するためのターゲットとして用いることができる。なお、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

【0116】

この場合において、処理室内の残留水分を除去しつつ絶縁層407を成膜することが好ましい。絶縁層407に水素、水酸基又は水分が含まれないようにするためである。

【0117】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水( $H_2O$ )など水素原子を含む化合物等が排出されるため、当該成膜室で成膜し絶縁層407に含まれる不純物の濃度を低減できる。

10

【0118】

絶縁層407を成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

【0119】

スパッタリング法にはスパッタリング用電源に高周波電源を用いるRFスパッタリング法、直流電源を用いるDCスパッタリング法、さらにパルス的にバイアスを与えるパルスDCスパッタリング法がある。RFスパッタリング法は主に絶縁膜を成膜する場合に用いられ、DCスパッタリング法は主に金属膜を成膜する場合に用いられる。

20

【0120】

また、材料の異なるターゲットを複数設置できる多元スパッタリング装置もある。多元スパッタリング装置は、同一チャンバーで異なる材料膜を積層成膜することも、同一チャンバーで複数種類の材料を同時に放電させて成膜することもできる。

【0121】

また、チャンバー内部に磁石機構を備えたマグネットロンスパッタリング法を用いるスパッタリング装置や、グロー放電を使わずマイクロ波を用いて発生させたプラズマを用いるECRスパッタリング法を用いるスパッタリング装置がある。

30

【0122】

また、スパッタリング法を用いる成膜方法として、成膜中にターゲット物質とスパッタリングガス成分とを化学反応させてこれらの化合物薄膜を形成するリアクティブスパッタリング法や、成膜中に基板にも電圧をかけるバイアススパッタリング法もある。

【0123】

また、絶縁層407は積層構造でもよく、例えば、基板400側から窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、又は窒化酸化アルミニウム層などの窒化物絶縁層と、上記酸化物絶縁層との積層構造としてもよい。

【0124】

例えば、水素及び水分が除去され、窒素を含む高純度のスパッタリングガスを導入しシリコンターゲットを用いて、酸化シリコン層と基板との間に窒化シリコン層を成膜する。この場合においても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成膜することが好ましい。

40

【0125】

窒化シリコン層を形成する場合も、成膜時に基板を加熱してもよい。

【0126】

絶縁層407として窒化シリコン層と酸化シリコン層とを積層する場合、窒化シリコン層と酸化シリコン層と同じ処理室において、共通のシリコンターゲットを用いて成膜することができる。先に窒素を含むエッティングガスを導入して、処理室内に装着されたシリコンターゲットを用いて窒化シリコン層を形成し、次にエッティングガスを、酸素を含むエッティングガスに切り替えて同じシリコンターゲットを用いて酸化シリコン層を成膜する。窒化

50

シリコン層と酸化シリコン層とを大気に曝露せずに連続して形成することができるため、窒化シリコン層表面に水素や水分などの不純物が吸着することを防止することができる。

【0127】

次いで、絶縁層407上に、膜厚2nm以上200nm以下の酸化物半導体膜を形成する。

【0128】

また、酸化物半導体膜に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室で絶縁層407が形成された基板400を予備加熱し、基板400に吸着した水素、水分などの不純物を脱離し排出することが好ましい。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、後に形成するゲート絶縁層402の成膜前の基板400に行ってもよいし、後に形成するソース電極層又はドレイン電極層415a及びソース電極層又はドレイン電極層415bまで形成した基板400にも同様に行ってもよい。

10

【0129】

なお、酸化物半導体膜をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させて逆スパッタを行い、絶縁層407の表面に付着しているゴミを除去することが好ましい。逆スパッタとは、ターゲット側に電圧を印加せずに、アルゴン雰囲気下で基板側に高周波電源を用いて電圧を印加してプラズマを形成して基板表面を改質する方法である。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

20

【0130】

酸化物半導体膜はスパッタリング法により成膜する。酸化物半導体膜は、In-Ga-Zn-O系膜、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いる。本実施の形態では、酸化物半導体膜をIn-Ga-Zn-O系酸化物半導体成膜用ターゲットを用いてスパッタリング法により成膜する。また、酸化物半導体膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素混合雰囲気下においてスパッタリング法により形成することができる。また、スパッタリング法を用いる場合、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲットを用いて成膜を行ってもよい。

30

【0131】

酸化物半導体膜を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

【0132】

酸化物半導体膜をスパッタリング法で形成するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及びZnを含む酸化物半導体成膜用ターゲット(組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol%]、In : Ga : Zn = 1 : 1 : 0.5 [atom%])を用いることができる。また、In、Ga、及びZnを含む酸化物半導体成膜用ターゲットとして、In : Ga : Zn = 1 : 1 : 1 [atom%]、又はIn : Ga : Zn = 1 : 1 : 2 [atom%]の組成比を有するターゲットを用いることもできる。また、作製される酸化物半導体成膜用ターゲットの全体の体積に対して全体の体積から空隙などが占める空間を除いた部分の体積の割合(充填率ともいう)は、90%以上100%以下、好ましくは95%以上99.9%以下である。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

40

【0133】

50

減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスペッタリングガスを導入し、金属酸化物をターゲットとして基板400上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水( $H_2O$ )など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

## 【0134】

10

成膜条件の一例としては、基板温度を室温、基板とターゲットの間との距離を60mm、圧力0.4Pa、直流(DC)電源0.5kW、酸素及びアルゴン(酸素流量15sccm:アルゴン流量30sccm)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

## 【0135】

20

次いで、酸化物半導体膜を第1のフォトリソグラフィ工程により島状の酸化物半導体層412に加工する(図6(A)参照。)。また、島状の酸化物半導体層412を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0136】

なお、ここでの酸化物半導体膜のエッティングは、ドライエッティングでもウェットエッティングでもよく、両方を用いてもよい。

## 【0137】

30

ドライエッティングに用いるエッティングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素( $Cl_2$ )、塩化硼素( $BCl_3$ )、塩化珪素( $SiCl_4$ )、四塩化炭素( $CCl_4$ )など)が好ましい。

## 【0138】

40

また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素( $CF_4$ )、弗化硫黄( $SF_6$ )、弗化窒素( $NF_3$ )、トリフルオロメタン( $CHF_3$ )など)、臭化水素( $HBr$ )、酸素( $O_2$ )、これらのガスにヘリウム( $He$ )やアルゴン( $Ar$ )などの希ガスを添加したガス、などを用いることができる。

## 【0139】

ドライエッティング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッティング法を用いることができる。所望の加工形状にエッティングできるように、エッティング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

## 【0140】

ウェットエッティングに用いるエッティング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO 07N(関東化学社製)を用いてもよい。

## 【0141】

また、ウェットエッティング後のエッティング液はエッティングされた材料とともに洗浄によって除去される。その除去された材料を含むエッティング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッティング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

## 【0142】

50

所望の加工形状にエッティングできるように、材料に合わせてエッティング条件（エッティング液、エッティング時間、温度等）を適宜調節する。

【0143】

本実施の形態では、エッティング液として磷酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッティング法により、酸化物半導体膜を島状の酸化物半導体層412に加工する。

【0144】

本実施の形態では、酸化物半導体層412に、第1の加熱処理を行う。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。この第1の加熱処理によって酸化物半導体層412の脱水化又は脱水素化を行うことができる。

10

【0145】

なお、加熱処理装置としては、電気炉に限らず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を用いてもよい。例えば、G R T A ( G a s R a p i d T h e r m a l A n n e a l ) 装置、L R T A ( L a m p R a p i d T h e r m a l A n n e a l ) 装置等のR T A ( R a p i d T h e r m a l A n n e a l ) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光（電磁波）の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて加熱処理を行う装置である。ガスとしては、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物とほとんど反応しない不活性気体が用いられる。

20

【0146】

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すG R T Aを行ってもよい。G R T Aを用いると短時間での高温加熱処理が可能となる。

30

【0147】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N ( 99.9999% ) 以上、好ましくは7N ( 99.9999% ) 以上、（即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下）とすることが好ましい。

40

【0148】

また、第1の加熱処理の条件、又は酸化物半導体層の材料によっては、酸化物半導体層が結晶化し、微結晶膜又は多結晶膜となる場合もある。例えば、結晶化率が90%以上、又は80%以上の微結晶の酸化物半導体膜となる場合もある。また、第1の加熱処理の条件、又は酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体膜となる場合もある。また、非晶質の酸化物半導体の中に微結晶部（粒径1nm以上20nm以下（代表的には2nm以上4nm以下））が混在する酸化物半導体膜となる場合もある。

40

【0149】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うことでもできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

【0150】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にソース電極層及びドレイン電極層を積層させた後、ソース電極及びドレイン電極上にゲート絶縁層を形成した後、のいずれで行ってもよい。

50

## 【0151】

次いで、絶縁層407及び酸化物半導体層412上に、導電膜を形成する。例えばスパッタリング法や真空蒸着法で導電膜を形成すればよい。導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムのいずれか一又は複数から選択された材料を用いてもよい。また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。また、Alに、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、Sc(スカンジウム)から選ばれた元素を単数、又は複数組み合わせた膜、それらの合金膜、若しくは窒化膜を用いてもよい。

## 【0152】

第2のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bを形成した後、レジストマスクを除去する(図6(B)参照。)。なお、形成されたソース電極層、ドレイン電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。

## 【0153】

本実施の形態ではソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bとしてスパッタリング法により膜厚150nmのチタン膜を形成する。

## 【0154】

なお、導電膜のエッチングの際に、酸化物半導体層412は酸化物半導体層412が除去されて、その下の絶縁層407が露出しないようにそれぞれの材料及びエッチング条件を適宜調節する。

## 【0155】

なお、第2のフォトリソグラフィ工程では、酸化物半導体層412は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。また、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0156】

第2のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層412上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成される薄膜トランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm~数10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用いて第2のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さくすることができるため、低消費電力化も図ることができる。

## 【0157】

次いで、絶縁層407、酸化物半導体層412、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415b上にゲート絶縁層402を形成する(図6(C)参照。)。

## 【0158】

ゲート絶縁層402は、プラズマCVD法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム

10

20

30

40

50

ム層を単層で又は積層して形成することができる。なお、ゲート絶縁層402中に水素が多量に含まれないようにするためには、スパッタリング法でゲート絶縁層402を成膜することが好ましい。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

【0159】

ゲート絶縁層402は、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415b側から酸化シリコン層と窒化シリコン層を積層した構造とすることもできる。例えば、第1のゲート絶縁層として膜厚5nm以上300nm以下の酸化シリコン層(SiO<sub>x</sub>(x>0))を形成し、第1のゲート絶縁層上に第2のゲート絶縁層としてスパッタリング法により膜厚50nm以上200nm以下の窒化シリコン層(SiN<sub>y</sub>(y>0))を積層して、膜厚100nmのゲート絶縁層としてもよい。本実施の形態では、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により膜厚100nmの酸化シリコン層を形成する。

10

【0160】

次いで、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってゲート絶縁層402の一部を除去して、ソース電極層又はドレイン電極層415a、ソース電極層又はドレイン電極層415bに達する開口421a、開口421bを形成する(図6(D)参照。)。

20

【0161】

次に、ゲート絶縁層402、及び開口421a、421b上に導電膜を形成した後、第4のフォトリソグラフィ工程によりゲート電極層411、配線層414a、414bを形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0162】

また、ゲート電極層411、配線層414a、414bは、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

30

【0163】

例えば、ゲート電極層411、配線層414a、414bの2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、又は銅層上にモリブデン層を積層した2層構造、又は銅層上に窒化チタン層若しくは窒化タンタル層を積層した2層構造、窒化チタン層とモリブデン層とを積層した2層構造とすることが好ましい。3層の積層構造としては、タングステン層又は窒化タングステン層と、アルミニウムとシリコンの合金層又はアルミニウムとチタンの合金層と、窒化チタン層又はチタン層とを積層した層とすることが好ましい。なお、透光性を有する導電膜を用いてゲート電極層を形成することもできる。透光性を有する導電膜としては、透光性導電性酸化物等をその例に挙げることができる。

【0164】

本実施の形態ではゲート電極層411、配線層414a、414bとしてスパッタリング法により膜厚150nmのチタン膜を形成する。

40

【0165】

次いで、不活性ガス雰囲気下、又は酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。本実施の形態では、窒素雰囲気下で250、1時間の第2の加熱処理を行う。また、第2の加熱処理は、薄膜トランジスタ410上に保護絶縁層や平坦化絶縁層を形成してから行ってもよい。

【0166】

さらに、大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、1

50

00 以上 200 以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。

【0167】

以上の工程で、水素、水分、水素化物、水酸化物の濃度が低減された酸化物半導体層 412 を有する薄膜トランジスタ 410 を形成することができる（図 6（E）参照。）。

【0168】

また、薄膜トランジスタ 410 上に保護絶縁層や、平坦化のための平坦化絶縁層を設けてもよい。例えば、保護絶縁層として酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。

10

【0169】

また、平坦化絶縁層としては、ポリイミド、アクリル樹脂、ベンゾシクロブテン系樹脂、ポリアミド、エポキシ樹脂等の、耐熱性を有する有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k 材料）、シロキサン系樹脂、PSG（リンガラス）、BPSG（リンボロンガラス）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁層を形成してもよい。

【0170】

なお、シロキサン系樹脂とは、シロキサン系材料を出発材料として形成された Si-O-Si 結合を含む樹脂に相当する。シロキサン系樹脂は置換基としては有機基（例えばアルキル基やアリール基）やフルオロ基を用いてもよい。また、有機基はフルオロ基を有していてもよい。

20

【0171】

平坦化絶縁層の形成法は、特に限定されず、その材料に応じて、スパッタリング法、SOG 法、スピンドルコート、ディップ、スプレー塗布、液滴吐出法（インクジェット法、スクリーン印刷、オフセット印刷等）、ドクターナイフ、ロールコーラー、カーテンコーラー、ナイフコーラー等を用いることができる。

【0172】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

30

【0173】

上記のように酸化物半導体膜を成膜するに際し、反応雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

【0174】

以上のように、酸化物半導体層を用いる薄膜トランジスタを有する半導体装置において、安定な電気特性を有し信頼性の高い半導体装置を提供することができる。

40

【0175】

（実施の形態 3）

本実施の形態は、本明細書で開示する論理回路及び半導体装置を構成するトランジスタに適用できる薄膜トランジスタの他の例を示す。なお、実施の形態 2 と同一部分又は同様な機能を有する部分、及び工程は、実施の形態 2 と同様とすればよく、その繰り返しの説明は省略する。また同じ箇所の詳細な説明も省略する。

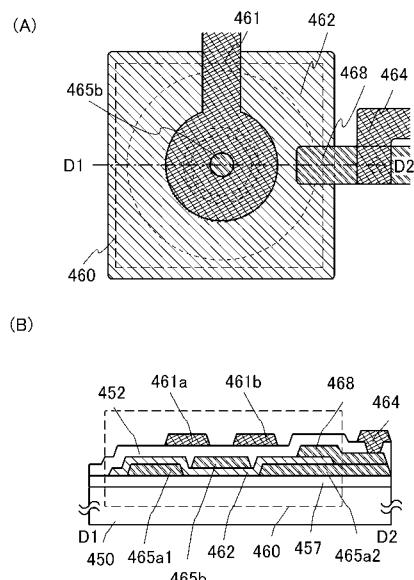

【0176】

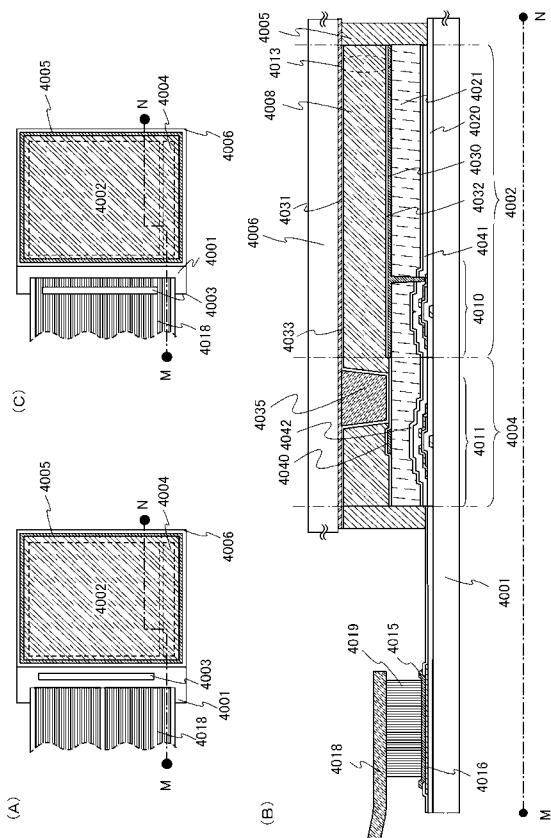

本実施の形態の半導体装置及び半導体装置の作製方法の一形態を、図 7 及び図 8 を用いて説明する。

【0177】

図 7（A）（B）に半導体装置の平面及び断面構造の一例を示す。図 7（A）（B）に示す薄膜トランジスタ 460 は、トップゲート構造の薄膜トランジスタの一つである。

【0178】

図 7（A）はトップゲート構造の薄膜トランジスタ 460 の平面図であり、図 7（B）は

50

図7(A)の線D1-D2における断面図である。

【0179】

薄膜トランジスタ460は、絶縁表面を有する基板450上に、絶縁層457、ソース電極層又はドレイン電極層465a(465a1、465a2)、酸化物半導体層462、ソース電極層又はドレイン電極層465b、配線層468、ゲート絶縁層452、ゲート電極層461(461a、461b)を含み、ソース電極層又はドレイン電極層465a(465a1、465a2)は配線層468を介して配線層464と電気的に接続している。また、図示していないが、ソース電極層又はドレイン電極層465bもゲート絶縁層452に設けられた開口において配線層と電気的に接続する。

【0180】

以下、図8(A)乃至(E)を用い、基板450上に薄膜トランジスタ460を作製する工程を説明する。

【0181】

まず、基板450上に下地膜となる絶縁層457を形成する。

【0182】

本実施の形態では、絶縁層457として、スパッタリング法により酸化シリコン層を形成する。基板450を処理室へ搬送し、水素及び水分が除去され、酸素を含む高純度のスパッタリングガスを導入しシリコンターゲット又は石英(好ましくは合成石英)を用いて、基板450に絶縁層457として、酸化シリコン層を成膜する。なお、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

【0183】

例えば、スパッタリングガスの純度が6Nであり、石英(好ましくは合成石英)を用い、基板温度108°C、基板とターゲットの間との距離(T-S間距離)を60mm、圧力0.4Pa、高周波電源1.5kW、酸素及びアルゴン(酸素流量25sccm:アルゴン流量25sccm=1:1)雰囲気下でRFスパッタリング法により酸化シリコン膜を成膜する。膜厚は100nmとする。なお、石英(好ましくは合成石英)に代えてシリコンターゲットを酸化シリコン膜を成膜するためのターゲットとして用いることができる。

【0184】

この場合において、処理室内の残留水分を除去しつつ絶縁層457を成膜することが好ましい。絶縁層457に水素、水酸基又は水分が含まれないようにするためである。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜し絶縁層457に含まれる不純物の濃度を低減できる。

【0185】

絶縁層457を成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

【0186】

また、絶縁層457は積層構造でもよく、例えば、基板450側から窒化シリコン層、窒化酸化シリコン層、窒化アルミニウム層、窒化酸化アルミニウム層などの窒化物絶縁層と、上記酸化物絶縁層との積層構造としてもよい。

【0187】

例えば、水素及び水分が除去され、窒素を含む高純度のスパッタリングガスを導入しシリコンターゲットを用いて、酸化シリコン層と基板との間に窒化シリコン層を成膜する。この場合においても、酸化シリコン層と同様に、処理室内の残留水分を除去しつつ窒化シリコン層を成膜することが好ましい。

【0188】

次いで、絶縁層457上に、導電膜を形成し、第1のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層又はドレイン電極層465a1、465a2を形成した後、レジストマスクを除去する(図8(A)参

10

20

30

40

50

照。)。ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 は断面図では分断されて示されているが、連続した膜である。なお、形成されたソース電極層、ドレイン電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。

【 0 1 8 9 】

ソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 の材料としては、A l、C r、C u、T a、T i、M o、W から選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムから選択されたいずれか一又は複数の材料を用いてもよい。また、導電膜は、単層構造でも、2 層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、T i 膜と、その T i 膜上に重ねてアルミニウム膜を積層し、さらにその上に T i 膜を成膜する3層構造などが挙げられる。また、A l に、チタン(T i)、タンタル(T a)、タングステン(W)、モリブデン(M o)、クロム(C r)、N d(ネオジム)、S c(スカンジウム)から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、若しくは窒化膜を用いてもよい。

【 0 1 9 0 】

本実施の形態ではソース電極層又はドレイン電極層 4 6 5 a 1、4 6 5 a 2 としてスパッタリング法により膜厚 1 5 0 n m のチタン膜を形成する。

【 0 1 9 1 】

次いで、ゲート絶縁層 4 5 2 上に、膜厚 2 n m 以上 2 0 0 n m 以下の酸化物半導体膜を形成する。

【 0 1 9 2 】

次に酸化物半導体膜を形成し、第2のフォトリソグラフィ工程により島状の酸化物半導体層 4 6 2 に加工する(図8(B)参照。)。本実施の形態では、酸化物半導体膜を I n - G a - Z n - O 系酸化物半導体成膜用ターゲットを用いてスパッタリング法により成膜する。

【 0 1 9 3 】

酸化物半導体膜は、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板 4 5 0 上に酸化物半導体膜を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。また、酸化物半導体膜成膜時に基板を加熱してもよい。

【 0 1 9 4 】

酸化物半導体膜を成膜する際に用いるスパッタリングガスは、水素、水、水酸基又は水素化物などの不純物が、濃度 p p m 程度、濃度 p p b 程度まで除去された高純度ガスを用いることが好ましい。

【 0 1 9 5 】

成膜条件の一例としては、基板温度を室温、基板とターゲットの間との距離を 6 0 m m、圧力 0 . 4 P a、直流(D C)電源 0 . 5 k W、酸素及びアルゴン(酸素流量 1 5 s c c m : アルゴン流量 3 0 s c c m)雰囲気下の条件が適用される。なお、パルス直流(D C)電源を用いると、成膜時に発生する粉状物質(パーティクル、ゴミともいう)が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは 5 n m 以上 3 0 n m 以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

10

20

30

40

50

## 【0196】

本実施の形態では、エッティング液として磷酸と酢酸と硝酸を混ぜた溶液を用いたウェットエッティング法により、酸化物半導体膜を島状の酸化物半導体層462に加工する。

## 【0197】

本実施の形態では、酸化物半導体層462に、第1の加熱処理を行う。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層を得る。この第1の加熱処理によって酸化物半導体層462の脱水化又は脱水素化を行うことができる。

10

## 【0198】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、GRTA (Gas Rapid Thermal Anneal) 装置、LRTA (Lamp Rapid Thermal Anneal) 装置等のRTA (Rapid Thermal Anneal) 装置を用いることができる。例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すGRTAを行ってもよい。GRTAを用いると短時間での高温加熱処理が可能となる。

20

## 【0199】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N (99.9999%) 以上、好ましくは7N (99.9999%) 以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下) とすることが好ましい。

## 【0200】

また、第1の加熱処理の条件、又は酸化物半導体層の材料によっては、酸化物半導体層が結晶化し、微結晶膜又は多結晶膜となる場合もある。

30

## 【0201】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜に行うこともできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

## 【0202】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にさらにソース電極層及びドレイン電極層を積層させた後、ソース電極及びドレイン電極上にゲート絶縁層を形成した後、のいずれで行ってもよい。

40

## 【0203】

次いで、絶縁層457及び酸化物半導体層462上に、導電膜を形成し、第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッティングを行ってソース電極層又はドレイン電極層465b、配線層468を形成した後、レジストマスクを除去する(図8(C)参照。)。ソース電極層又はドレイン電極層465b、配線層468はソース電極層又はドレイン電極層465a1、465a2と同様な材料及び工程で形成すればよい。

40

## 【0204】

本実施の形態ではソース電極層又はドレイン電極層465b、配線層468としてスパッタリング法により膜厚150nmのチタン膜を形成する。本実施の形態では、ソース電極層又はドレイン電極層465a1、465a2とソース電極層又はドレイン電極層465bに同じチタン膜を用いる例のため、ソース電極層又はドレイン電極層465a1、465a2とソース電極層又はドレイン電極層465bとはエッティングにおいて選択比がとれない。よって、ソース電極層又はドレイン電極層465a1、465a2が、ソース電極

50

層又はドレイン電極層 4 6 5 b のエッティング時にエッティングされないように、酸化物半導体層 4 6 2 に覆われないソース電極層又はドレイン電極層 4 6 5 a 2 上に配線層 4 6 8 を設けている。ソース電極層又はドレイン電極層 4 6 5 a 1 、 4 6 5 a 2 とソース電極層又はドレイン電極層 4 6 5 b とにエッティング工程において高い選択比を有する異なる材料を用いる場合には、エッティング時にソース電極層又はドレイン電極層 4 6 5 a 2 を保護する配線層 4 6 8 は必ずしも設けなくてもよい。

【 0 2 0 5 】

なお、導電膜のエッティングの際に、酸化物半導体層 4 6 2 が除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。

【 0 2 0 6 】

なお、第 3 のフォトリソグラフィ工程では、酸化物半導体層 4 6 2 は一部のみがエッティングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、ソース電極層又はドレイン電極層 4 6 5 b 、配線層 4 6 8 を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【 0 2 0 7 】

次いで、絶縁層 4 5 7 、酸化物半導体層 4 6 2 、ソース電極層又はドレイン電極層 4 6 5 a 1 、 4 6 5 a 2 、ソース電極層又はドレイン電極層 4 6 5 b 、及び配線層 4 6 8 上にゲート絶縁層 4 5 2 を形成する。

【 0 2 0 8 】

ゲート絶縁層 4 5 2 は、プラズマ C V D 法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層 4 5 2 中に水素が多量に含まれないようにするためには、スパッタリング法でゲート絶縁層 4 5 2 を成膜することが好ましい。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

【 0 2 0 9 】

ゲート絶縁層 4 5 2 は、ソース電極層又はドレイン電極層 4 6 5 a 1 、 4 6 5 a 2 、ソース電極層又はドレイン電極層 4 6 5 b 側から酸化シリコン層と窒化シリコン層を積層した構造とすることもできる。本実施の形態では、圧力 0 . 4 P a 、高周波電源 1 . 5 k W 、酸素及びアルゴン（酸素流量 2 5 s c c m : アルゴン流量 2 5 s c c m = 1 : 1 ）雰囲気下で R F スパッタリング法により膜厚 1 0 0 n m の酸化シリコン層を形成する。

【 0 2 1 0 】

次いで、第 4 のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッティングを行ってゲート絶縁層 4 5 2 の一部を除去して、配線層 4 3 8 に達する開口 4 2 3 を形成する（図 8 ( D ) 参照。）。図示しないが開口 4 2 3 の形成時にソース電極層又はドレイン電極層 4 6 5 b に達する開口を形成してもよい。本実施の形態では、ソース電極層又はドレイン電極層 4 6 5 b への開口はさらに層間絶縁層を積層した後に形成し、電気的に接続する配線層を開口に形成する例とする。

【 0 2 1 1 】

次に、ゲート絶縁層 4 5 2 、及び開口 4 2 3 上に導電膜を形成した後、第 5 のフォトリソグラフィ工程によりゲート電極層 4 6 1 ( 4 6 1 a 、 4 6 1 b ) 、配線層 4 6 4 を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【 0 2 1 2 】

また、ゲート電極層 4 6 1 ( 4 6 1 a 、 4 6 1 b ) 、配線層 4 6 4 の材料は、モリブデン、チタン、クロム、タンタル、タンクステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

10

20

30

40

50

## 【0213】

本実施の形態ではゲート電極層461(461a、461b)、配線層464としてスパッタリング法により膜厚150nmのチタン膜を形成する。

## 【0214】

次いで、不活性ガス雰囲気下、又は酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。本実施の形態では、窒素雰囲気下で250、1時間の第2の加熱処理を行う。また、第2の加熱処理は、薄膜トランジスタ410上に保護絶縁層や平坦化絶縁層を形成してから行ってもよい。

## 【0215】

さらに大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。

## 【0216】

以上の工程で、水素、水分、水素化物、水酸化物の濃度が低減された酸化物半導体層462を有する薄膜トランジスタ460を形成することができる(図8(E)参照。)。

## 【0217】

また、薄膜トランジスタ460上に保護絶縁層や、平坦化のための平坦化絶縁層を設けてもよい。なお、図示しないが、ゲート絶縁層452、保護絶縁層や平坦化絶縁層にソース電極層又はドレイン電極層465bに達する開口を形成し、その開口に、ソース電極層又はドレイン電極層465bと電気的に接続する配線層を形成する。

## 【0218】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

## 【0219】

上記のように酸化物半導体膜を成膜するに際し、反応雰囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

## 【0220】

以上のように、酸化物半導体層を用いる薄膜トランジスタを有する半導体装置において、安定な電気特性を有し信頼性の高い半導体装置を提供することができる。

## 【0221】

## (実施の形態4)

本実施の形態は、本明細書で開示する論理回路及び半導体装置を構成するトランジスタに適用できる薄膜トランジスタの他の例を示す。なお、実施の形態2と同一部分又は同様な機能を有する部分、及び工程は、実施の形態2と同様とすればよく、その繰り返しの説明は省略する。また同じ箇所の詳細な説明も省略する。本実施の形態で示す薄膜トランジスタ425、426は、実施の形態1の論理回路及び半導体装置を構成する薄膜トランジスタとして用いることができる。

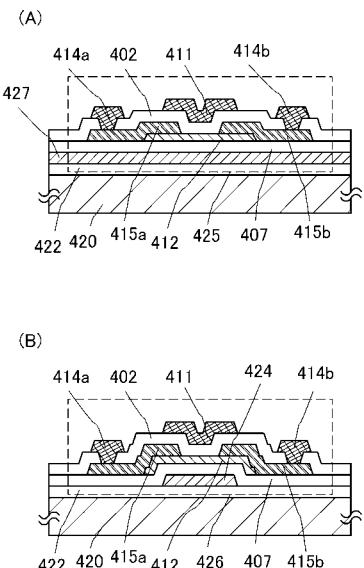

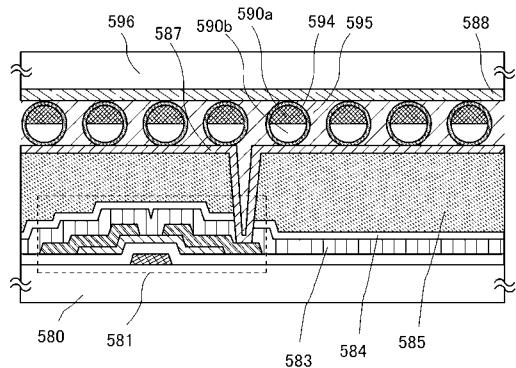

## 【0222】

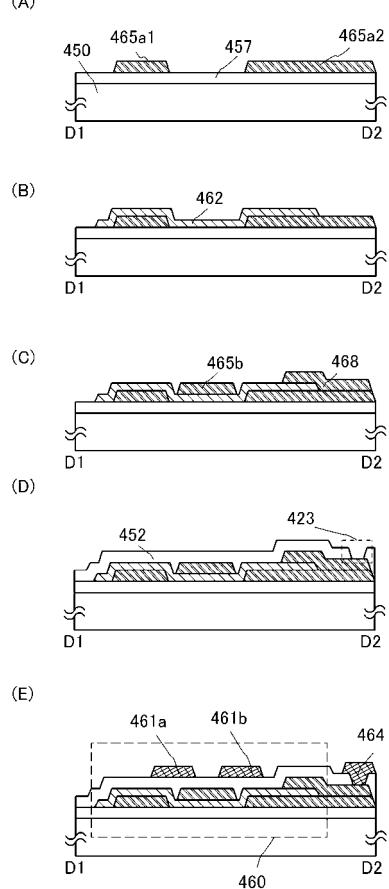

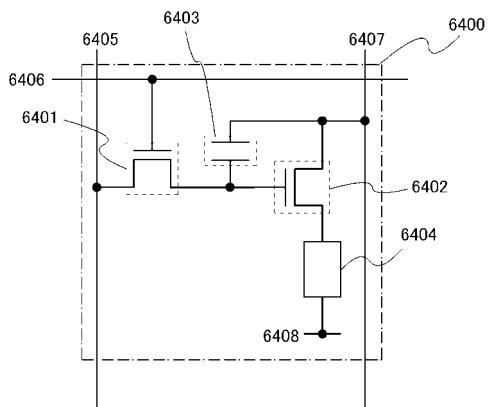

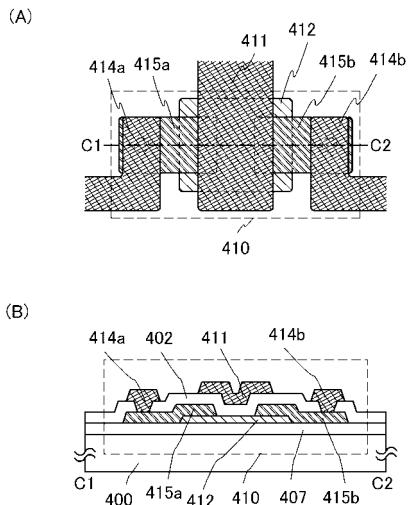

本実施の形態の薄膜トランジスタを、図9を用いて説明する。

## 【0223】

図9(A)(B)に薄膜トランジスタの断面構造の一例を示す。図9(A)(B)に示す薄膜トランジスタ425、426は、酸化物半導体層を導電層とゲート電極層とで挟んだ構造の薄膜トランジスタの一つである。

## 【0224】

また、図9(A)(B)において、基板はシリコン基板を用いており、シリコン基板420上に設けられた絶縁層422上に薄膜トランジスタ425、426がそれぞれ設けられている。

## 【0225】

10

20

30

40

50

図9(A)において、シリコン基板420に設けられた絶縁層422と絶縁層407との間に少なくとも酸化物半導体層412全体と重なるように導電層427が設けられている。

【0226】

なお、図9(B)は、絶縁層422と絶縁層407との間の導電層が、導電層424のようにエッチングにより加工され、酸化物半導体層412の少なくともチャネル領域を含む一部と重なる例である。

【0227】

導電層427、424は後工程で行われる加熱処理温度に耐えられる金属材料であればよく、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、スカンジウム(Sc)から選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜、又は上述した元素を成分とする窒化物などを用いることができる。また、単層構造でも積層構造でもよく、例えばタングステン層単層、又は窒化タングステン層とタングステン層との積層構造などを用いることができる。

【0228】

また、導電層427、424は、電位が薄膜トランジスタ425、426のゲート電極層411と同じでもよいし、異なっていても良く、第2のゲート電極層として機能させることもできる。また、導電層427、424の電位がGND、0Vという固定電位であってもよい。

【0229】

導電層427、424によって、薄膜トランジスタ425、426の電気特性を制御することができる。

【0230】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0231】

(実施の形態5)

本実施の形態は、本明細書で開示する論理回路及び半導体装置を構成するトランジスタに適用できる薄膜トランジスタの例を示す。

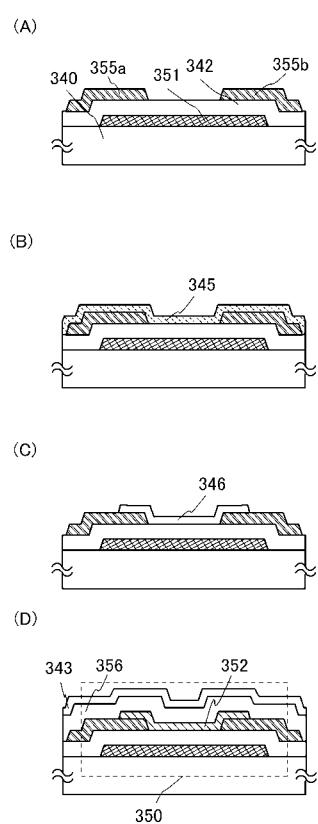

【0232】

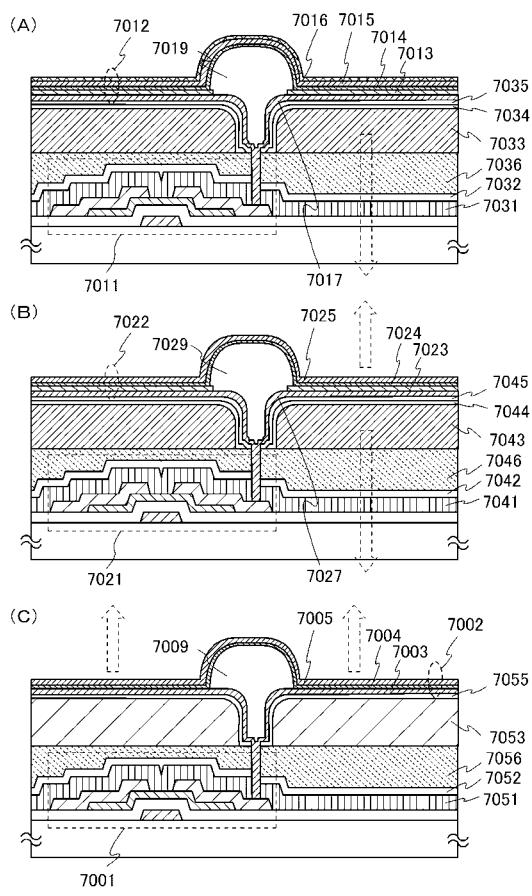

本実施の形態の薄膜トランジスタ及び薄膜トランジスタの作製方法の一形態を、図10を用いて説明する。

【0233】

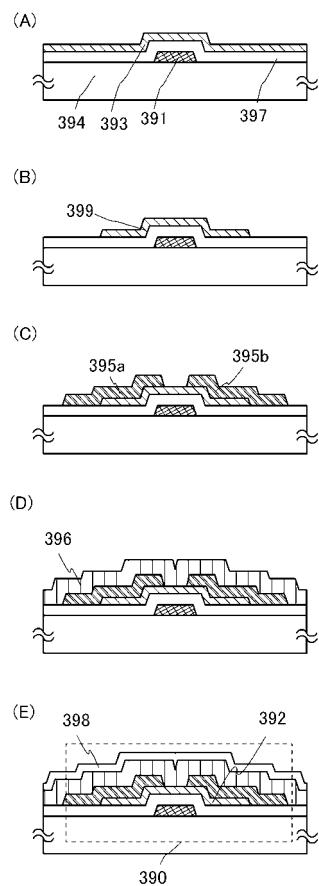

図10(A)乃至(E)に薄膜トランジスタの断面構造の一例を示す。図10(A)乃至(E)に示す薄膜トランジスタ390は、ボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

【0234】

また、薄膜トランジスタ390はシングルゲート構造の薄膜トランジスタを用いて説明するが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

【0235】

以下、図10(A)乃至(E)を用い、基板394上に薄膜トランジスタ390を作製する工程を説明する。

【0236】

まず、絶縁表面を有する基板394上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層391を形成する。形成されたゲート電極層の端部はテーパ形状であると、上に積層するゲート絶縁層の被覆性が向上するため好ましい。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【0237】

10

20

30

40

50

絶縁表面を有する基板 394 に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

【0238】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が 730 ℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、一般的に酸化ホウ素と比較して酸化バリウム (BaO) を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$  より BaO を多く含むガラス基板を用いることが好ましい

10

【0239】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラス基板などを用いることができる。また、プラスチック基板等も適宜用いることができる。

【0240】

下地膜となる絶縁膜を基板 394 とゲート電極層 391 との間に設けてもよい。下地膜は、基板 394 からの不純物元素の拡散を防止する機能があり、窒化シリコン膜、酸化シリコン膜、窒化酸化シリコン膜、又は酸化窒化シリコン膜から選ばれた一又は複数の膜による積層構造により形成することができる。

20

【0241】

また、ゲート電極層 391 の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

【0242】

例えば、ゲート電極層 391 の 2 層の積層構造としては、アルミニウム層上にモリブデン層が積層された 2 層の積層構造、銅層上にモリブデン層を積層した 2 層構造、銅層上に窒化チタン層若しくは窒化タンタル層を積層した 2 層構造、窒化チタン層とモリブデン層とを積層した 2 層構造、又は窒化タングステン層とタングステン層とを積層した 2 層構造とすることが好ましい。3 層の積層構造としては、タングステン層又は窒化タングステン層と、アルミニウムとシリコンの合金層又はアルミニウムとチタンの合金層と、窒化チタン層又はチタン層との積層とすることが好ましい。なお、透光性を有する導電膜を用いてゲート電極層を形成することもできる。透光性を有する導電膜としては、透光性導電性酸化物等をその例に挙げることができる。

30

【0243】

次いで、ゲート電極層 391 上にゲート絶縁層 397 を形成する。

【0244】

ゲート絶縁層 397 は、プラズマ CVD 法又はスパッタリング法等を用いて、酸化シリコン層、窒化シリコン層、酸化窒化シリコン層、窒化酸化シリコン層、又は酸化アルミニウム層を単層で又は積層して形成することができる。なお、ゲート絶縁層 397 中に水素が多量に含まれないようにするためには、スパッタリング法でゲート絶縁層 397 を成膜することが好ましい。スパッタリング法により酸化シリコン膜を成膜する場合には、ターゲットとしてシリコンターゲット又は石英ターゲットを用い、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いる。

40

【0245】

ゲート絶縁層 397 は、ゲート電極層 391 側から窒化シリコン層と酸化シリコン層を積層した構造とすることもできる。例えば、第 1 のゲート絶縁層としてスパッタリング法により膜厚 50 nm 以上 200 nm 以下の窒化シリコン層 ( $SiNy$  ( $y > 0$ )) を形成し、第 1 のゲート絶縁層上に第 2 のゲート絶縁層として膜厚 5 nm 以上 300 nm 以下の酸化シリコン層 ( $SiOx$  ( $x > 0$ )) を積層して、膜厚 100 nm のゲート絶縁層とする。

50

## 【0246】

また、ゲート絶縁層397、酸化物半導体膜393に水素、水酸基及び水分がなるべく含まれないようにするために、成膜の前処理として、スパッタリング装置の予備加熱室でゲート電極層391が形成された基板394、又はゲート絶縁層397までが形成された基板394を予備加熱し、基板394に吸着した水素、水分などの不純物を脱離し排気することが好ましい。なお、予備加熱の温度としては、100以上400以下好ましくは150以上300以下である。なお、予備加熱室に設ける排気手段はクライオポンプが好ましい。なお、この予備加熱の処理は省略することもできる。またこの予備加熱は、酸化物絶縁層396の成膜前に、ソース電極層395a及びドレイン電極層395bまで形成した基板394にも同様に行ってもよい。

10

## 【0247】

次いで、ゲート絶縁層397上に、膜厚2nm以上200nm以下の酸化物半導体膜393を形成する(図10(A)参照。)。

## 【0248】

なお、酸化物半導体膜393をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させて逆スパッタを行い、ゲート絶縁層397の表面に付着しているゴミを除去することが好ましい。

## 【0249】

酸化物半導体膜393はスパッタリング法により成膜する。酸化物半導体膜393は、In-Ga-Zn-O系膜、In-Sn-Zn-O系、In-Al-Zn-O系、Sn-Ga-Zn-O系、Al-Ga-Zn-O系、Sn-Al-Zn-O系、In-Zn-O系、Sn-Zn-O系、Al-Zn-O系、In-O系、Sn-O系、Zn-O系の酸化物半導体膜を用いる。本実施の形態では、酸化物半導体膜393をIn-Ga-Zn-O系酸化物半導体成膜用ターゲットを用いてスパッタリング法により成膜する。また、酸化物半導体膜393は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素混合雰囲気下においてスパッタリング法により形成することができる。また、スパッタリング法を用いる場合、SiO<sub>2</sub>を2重量%以上10重量%以下含むターゲットを用いて成膜を行ってもよい。

20

## 【0250】

酸化物半導体膜393をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及びZnを含む酸化物半導体成膜用ターゲット(組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol%]、In : Ga : Zn = 1 : 1 : 0.5 [atom%])を用いることができる。また、In、Ga、及びZnを含む酸化物半導体成膜用ターゲットとして、In : Ga : Zn = 1 : 1 : 1 [atom%]、又はIn : Ga : Zn = 1 : 1 : 2 [atom%]の組成比を有するターゲットを用いることもできる。酸化物半導体成膜用ターゲットの充填率は90%以上100%以下、好ましくは95%以上99.9%である。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

30

## 【0251】

減圧状態に保持された処理室内に基板を保持し、基板を室温又は400未満の温度に加熱する。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板394上に酸化物半導体膜393を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

40

50

## 【0252】

成膜条件の一例としては、基板とターゲットの間との距離を60mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

## 【0253】

次いで、酸化物半導体膜を第2のフォトリソグラフィ工程により島状の酸化物半導体層399に加工する(図10(B)参照。)。また、島状の酸化物半導体層399を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

10

## 【0254】

また、酸化物半導体層399の形成時に、ゲート絶縁層397にコンタクトホールを形成することができる。

## 【0255】

なお、ここでの酸化物半導体膜393のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。

## 【0256】

ドライエッチングに用いるエッチングガスとしては、塩素を含むガス(塩素系ガス、例えば塩素(Cl<sub>2</sub>)、塩化硼素(BCl<sub>3</sub>)、塩化珪素(SiCl<sub>4</sub>)、四塩化炭素(CCl<sub>4</sub>)など)が好ましい。

20

## 【0257】

また、フッ素を含むガス(フッ素系ガス、例えば四弗化炭素(CF<sub>4</sub>)、弗化硫黄(SF<sub>6</sub>)、弗化窒素(NF<sub>3</sub>)、トリフルオロメタン(CHF<sub>3</sub>)など)、臭化水素(HBr)、酸素(O<sub>2</sub>)、これらのガスにヘリウム(He)やアルゴン(Arg)などの希ガスを添加したガス、などを用いることができる。

## 【0258】

ドライエッチング法としては、平行平板型RIE(Reactive Ion Etching)法や、ICP(Inductively Coupled Plasma:誘導結合型プラズマ)エッチング法を用いることができる。所望の加工形状にエッチングできるように、エッチング条件(コイル型の電極に印加される電力量、基板側の電極に印加される電力量、基板側の電極温度等)を適宜調節する。

30

## 【0259】

ウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITOON(関東化学社製)を用いてもよい。

## 【0260】

また、ウェットエッチング後のエッチング液はエッチングされた材料とともに洗浄によって除去される。その除去された材料を含むエッチング液の廃液を精製し、含まれる材料を再利用してもよい。当該エッチング後の廃液から酸化物半導体層に含まれるインジウム等の材料を回収して再利用することにより、資源を有効活用し低コスト化することができる。

40

## 【0261】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件(エッチング液、エッチング時間、温度等)を適宜調節する。

## 【0262】

なお、次工程の導電膜を形成する前に逆スパッタを行い、酸化物半導体層399及びゲート絶縁層397の表面に付着しているレジスト残渣などを除去することが好ましい。

## 【0263】

次いで、ゲート絶縁層397、及び酸化物半導体層399上に、導電膜を形成する。スパ

50

ツタリング法や真空蒸着法で導電膜を形成すればよい。導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムのいずれか一又は複数から選択された材料を用いてもよい。また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。また、Alに、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、Sc(スカンジウム)から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、若しくは窒化膜を用いてもよい。

10

## 【0264】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層395a、ドレイン電極層395bを形成した後、レジストマスクを除去する(図10(C)参照。)。

## 【0265】

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層399上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成される薄膜トランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm~数10nmと極めて波長が短い超紫外線(Extreme Ultraviolet)を用いて第3のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄膜トランジスタのチャネル長Lを10nm以上1000nm以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。

20

## 【0266】

なお、導電膜のエッチングの際に、酸化物半導体層399は除去されないようにそれぞれの材料及びエッチング条件を適宜調節する。

30

## 【0267】

なお、第3のフォトリソグラフィ工程では、酸化物半導体層399は一部のみがエッチングされ、溝部(凹部)を有する酸化物半導体層となることもある。また、ソース電極層395a、ドレイン電極層395bを形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0268】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッチング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッチングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッチング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

40

## 【0269】

N<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去してもよい。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

## 【0270】

プラズマ処理を行った場合、大気に触れることなく、酸化物半導体層の一部に接する保護

50

絶縁膜となる酸化物絶縁層として酸化物絶縁層 396 を形成する(図 10 (D) 参照。)。本実施の形態では、酸化物半導体層 399 がソース電極層 395a、ドレイン電極層 395b と重ならない領域において、酸化物半導体層 399 と酸化物絶縁層 396 とが接するように形成する。

## 【0271】

本実施の形態では、酸化物絶縁層 396 として、島状の酸化物半導体層 399、ソース電極層 395a、ドレイン電極層 395b まで形成された基板 394 を室温又は 100 未満の温度に加熱し、水素及び水分が除去された高純度酸素を含むスパッタリングガスを導入しシリコン半導体のターゲットを用いて、欠陥を含む酸化シリコン層を成膜する。

## 【0272】

10 例えは、スパッタリングガスの純度が 6N であり、ボロンがドープされたシリコンターゲット(抵抗値 0.01 cm)を用い、基板とターゲットの間との距離(T-S 間距離)を 89mm、圧力 0.4Pa、直流(DC)電源 6kW、酸素(酸素流量比率 100%) 霧囲気下でパルス DC スパッタリング法により酸化シリコン層を成膜する。膜厚は 300 nm とする。なお、シリコンターゲットに代えて石英(好ましくは合成石英)を酸化シリコン膜を成膜するためのターゲットとして用いることができる。なお、スパッタリングガスとして酸素又は、酸素及びアルゴンの混合ガスを用いて行う。

## 【0273】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層 396 を成膜することが好ましい。酸化物半導体層 399 及び酸化物絶縁層 396 に水素、水酸基又は水分が含まれないようにするためである。

## 【0274】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えは、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えは、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層 396 に含まれる不純物の濃度を低減できる。

## 【0275】

なお、酸化物絶縁層 396 として、酸化シリコン層に代えて、酸化窒化シリコン層、酸化アルミニウム層、又は酸化窒化アルミニウム層などを用いることもできる。

## 【0276】

さらに、酸化物絶縁層 396 と酸化物半導体層 399 とを接した状態で 100 乃至 400 で加熱処理を行ってもよい。本実施の形態における酸化物絶縁層 396 は欠陥を多く含むため、この加熱処理によって酸化物半導体層 399 中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁層 396 に拡散させ、酸化物半導体層 399 中に含まれる該不純物をより低減させることができる。

## 【0277】

以上の工程で、水素、水分、水酸基又は水素化物の濃度が低減された酸化物半導体層 392 を有する薄膜トランジスタ 390 を形成することができる(図 10 (E) 参照。)。

## 【0278】

上記のように酸化物半導体膜を成膜するに際し、反応霧囲気中の残留水分を除去することで、該酸化物半導体膜中の水素及び水素化物の濃度を低減することができる。それにより酸化物半導体膜の安定化を図ることができる。

## 【0279】

酸化物絶縁層上に保護絶縁層を設けてもよい。本実施の形態では、保護絶縁層 398 を酸化物絶縁層 396 上に形成する。保護絶縁層 398 としては、窒化シリコン膜、窒化酸化シリコン膜、窒化アルミニウム膜、又は窒化酸化アルミニウム膜などを用いる。

## 【0280】

保護絶縁層 398 として、酸化物絶縁層 396 まで形成された基板 394 を 100 ~ 4

10

20

30

40

50

00 の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタリングガスを導入しシリコン半導体のターゲットを用いて窒化シリコン膜を成膜する。この場合においても、酸化物絶縁層396と同様に、処理室内の残留水分を除去しつつ保護絶縁層398を成膜することが好ましい。

【0281】

保護絶縁層398を形成する場合、保護絶縁層398の成膜時に100～400に基板394を加熱することで、酸化物半導体層中に含まれる水素若しくは水分を酸化物絶縁層に拡散させることができる。この場合上記酸化物絶縁層396の形成後に加熱処理を行わなくてもよい。

【0282】

酸化物絶縁層396として酸化シリコン層を形成し、保護絶縁層398として窒化シリコン層を積層する場合、酸化シリコン層と窒化シリコン層と同じ処理室において、共通のシリコンターゲットを用いて成膜することができる。先に酸素を含むエッチングガスを導入して、処理室内に装着されたシリコンターゲットを用いて酸化シリコン層を形成し、次にエッチングガスを窒素を含むエッチングガスに切り替えて同じシリコンターゲットを用いて窒化シリコン層を成膜する。酸化シリコン層と窒化シリコン層とを大気に曝露せずに連続して形成することができるため、酸化シリコン層表面に水素や水分などの不純物が吸着することを防止することができる。この場合、酸化物絶縁層396として酸化シリコン層を形成し、保護絶縁層398として窒化シリコン層を積層した後、酸化物半導体層中に含まれる水素若しくは水分を酸化物絶縁層に拡散させるための加熱処理（温度100乃至400）を行うとよい。

10

20

【0283】

保護絶縁層の形成後、さらに大気中、100以上200以下、1時間以上30時間以下での加熱処理を行ってもよい。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、ノーマリーオフとなる薄膜トランジスタを得ることができる。よって薄膜トランジスタの信頼性を向上できる。

30

【0284】

また、ゲート絶縁層上にチャネル形成領域とする酸化物半導体層を成膜するに際し、反応雰囲気中の残留水分を除去することで、該酸化物半導体層中の水素及び水素化物の濃度を低減することができる。

40

【0285】

上記の工程は、液晶表示パネル、エレクトロルミネセンス表示パネル、電子インクを用いた表示装置などのバックプレーン（薄膜トランジスタが形成された基板）の製造に用いることができる。上記の工程は、400以下の温度で行われるため、厚さが1mm以下で、一边が1mを超えるガラス基板を用いる製造工程にも適用することができる。また、400以下の処理温度で全ての工程を行うことができるので、表示パネルを製造するためには多大なエネルギーを消費しないで済む。

【0286】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0287】

以上のように、酸化物半導体層を用いる薄膜トランジスタにおいて、安定な電気特性を有し信頼性の高い薄膜トランジスタを提供することができる。

【0288】

（実施の形態6）

本実施の形態は、本明細書で開示する論理回路及び半導体装置を構成するトランジスタに適用できる薄膜トランジスタの他の例を示す。

【0289】

50

本実施の形態の薄膜トランジスタ及び薄膜トランジスタの作製方法の一形態を図11を用いて説明する。

【0290】

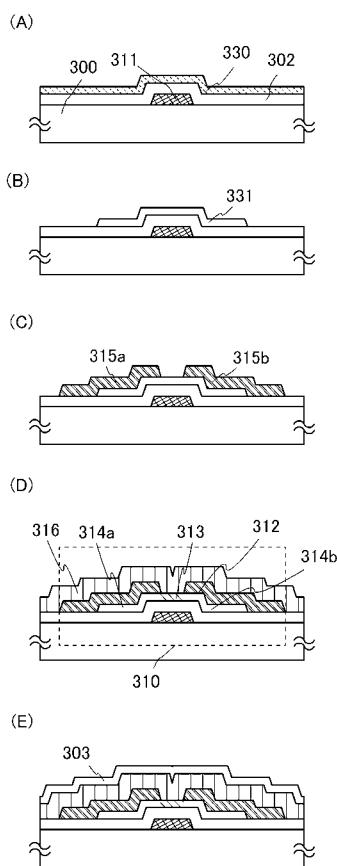

図11(A)乃至(E)に薄膜トランジスタの断面構造の一例を示す。図11(A)乃至(E)に示す薄膜トランジスタ310は、ボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

【0291】

また、薄膜トランジスタ310はシングルゲート構造の薄膜トランジスタを用いて説明したが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

10

【0292】

以下、図11(A)乃至(E)を用い、基板300上に薄膜トランジスタ410を作製する工程を説明する。

【0293】

まず、絶縁表面を有する基板300上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層311を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

20

【0294】

絶縁表面を有する基板300に使用することができる基板に大きな制限はないが、少なくとも、後の加熱処理に耐えうる程度の耐熱性を有していることが必要となる。バリウムホウケイ酸ガラスやアルミノホウケイ酸ガラスなどのガラス基板を用いることができる。

【0295】

また、ガラス基板としては、後の加熱処理の温度が高い場合には、歪み点が730℃以上のものを用いるとよい。また、ガラス基板には、例えば、アルミノシリケートガラス、アルミノホウケイ酸ガラス、バリウムホウケイ酸ガラスなどのガラス材料が用いられている。なお、酸化ホウ素( $B_2O_3$ )と比較して酸化バリウム( $BaO$ )を多く含ませることで、より実用的な耐熱ガラスが得られる。このため、 $B_2O_3$ より $BaO$ を多く含むガラス基板を用いることが好ましい

30

【0296】

なお、上記のガラス基板に代えて、セラミック基板、石英基板、サファイア基板などの絶縁体でなる基板を用いてもよい。他にも、結晶化ガラス基板などを用いることができる。

【0297】

下地膜となる絶縁膜を基板300とゲート電極層311との間に設けてもよい。下地膜は、基板300からの不純物元素の拡散を防止する機能があり、窒化珪素膜、酸化珪素膜、窒化酸化珪素膜、又は酸化窒化珪素膜から選ばれた一又は複数の膜による積層構造により形成することができる。

40

【0298】

また、ゲート電極層311の材料は、モリブデン、チタン、クロム、タンタル、タングステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

【0299】

例えば、ゲート電極層311の2層の積層構造としては、アルミニウム層上にモリブデン層が積層された2層の積層構造、銅層上にモリブデン層を積層した2層の積層構造、銅層上に窒化チタン層若しくは窒化タンタル層を積層した2層の積層構造、窒化チタン層とモリブデン層とを積層した2層の積層構造、又は窒化タングステン層とタングステン層との2層の積層構造とすることが好ましい。3層の積層構造としては、タングステン層又は窒化タングステン層と、アルミニウムと珪素の合金層又はアルミニウムとチタンの合金層と、窒化チタン層又はチタン層とを積層した積層とすることが好ましい。

50

【0300】

次いで、ゲート電極層 311 上にゲート絶縁層 302 を形成する。

【0301】

ゲート絶縁層 302 は、プラズマ CVD 法又はスパッタリング法等を用いて、酸化珪素層、窒化珪素層、酸化窒化珪素層、窒化酸化珪素層、又は酸化アルミニウム層を単層で又は積層して形成することができる。例えば、成膜ガスとして、SiH<sub>4</sub>、酸素及び窒素を用いてプラズマ CVD 法により酸化窒化珪素層を形成すればよい。ゲート絶縁層 302 の膜厚は、100 nm 以上 500 nm 以下とし、積層の場合は、例えば、膜厚 50 nm 以上 200 nm 以下の第 1 のゲート絶縁層と、第 1 のゲート絶縁層上に膜厚 5 nm 以上 300 nm 以下の第 2 のゲート絶縁層の積層とする。

【0302】

本実施の形態では、ゲート絶縁層 302 としてプラズマ CVD 法により膜厚 100 nm 以下の酸化窒化珪素層を形成する。

【0303】

次いで、ゲート絶縁層 302 上に、膜厚 2 nm 以上 200 nm 以下の酸化物半導体膜 330 を形成する。

【0304】

なお、酸化物半導体膜 330 をスパッタリング法により成膜する前に、アルゴンガスを導入してプラズマを発生させる逆スパッタを行い、ゲート絶縁層 302 の表面に付着しているゴミを除去することが好ましい。なお、アルゴン雰囲気に代えて窒素、ヘリウム、酸素などを用いてもよい。

【0305】

酸化物半導体膜 330 は、In-Ga-Zn-O 系、In-Sn-Zn-O 系、In-Al-Zn-O 系、Sn-Ga-Zn-O 系、Al-Ga-Zn-O 系、Sn-Al-Zn-O 系、In-Zn-O 系、Sn-Zn-O 系、Al-Zn-O 系、In-O 系、Sn-O 系、Zn-O 系の酸化物半導体膜を用いる。本実施の形態では、酸化物半導体膜 330 として In-Ga-Zn-O 系酸化物半導体ターゲットを用いてスパッタリング法により成膜する。この段階での断面図が図 11 (A) に相当する。また、酸化物半導体膜 330 は、希ガス (代表的にはアルゴン) 雰囲気下、酸素雰囲気下、又は希ガス (代表的にはアルゴン) 及び酸素雰囲気下においてスパッタリング法により形成することができる。また、スパッタリング法を用いる場合、SiO<sub>2</sub> を 2 重量 % 以上 10 重量 % 以下含むターゲットを用いて成膜を行ってもよい。

【0306】

酸化物半導体膜 330 をスパッタリング法で作製するためのターゲットとして、酸化亜鉛を主成分とする金属酸化物のターゲットを用いることができる。また、金属酸化物のターゲットの他の例としては、In、Ga、及び Zn を含む酸化物半導体成膜用ターゲット (組成比として、In<sub>2</sub>O<sub>3</sub> : Ga<sub>2</sub>O<sub>3</sub> : ZnO = 1 : 1 : 1 [mol %]、In : Ga : Zn = 1 : 1 : 0.5 [atom %] ) を用いることができる。また、In、Ga、及び Zn を含む酸化物半導体成膜用ターゲットとして、In : Ga : Zn = 1 : 1 : 1 [atom %]、又は In : Ga : Zn = 1 : 1 : 2 [atom %] の組成比を有するターゲットを用いることもできる。酸化物半導体成膜用ターゲットの充填率は 90 % 以上 100 % 以下、好ましくは 95 % 以上 99.9 % である。充填率の高い酸化物半導体成膜用ターゲットを用いることにより、成膜した酸化物半導体膜は緻密な膜となる。

【0307】

酸化物半導体膜 330 を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が、濃度 ppm 程度、濃度 ppb 程度まで除去された高純度ガスを用いることが好ましい。

【0308】

減圧状態に保持された処理室内に基板を保持し、基板温度を 100 以上 600 以下好ましくは 200 以上 400 以下とする。基板を加熱しながら成膜することにより、成膜した酸化物半導体膜に含まれる不純物濃度を低減することができる。また、スパッタリ

10

20

30

40

50

ングによる損傷が軽減される。そして、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタリングガスを導入し、金属酸化物をターゲットとして基板300上に酸化物半導体膜330を成膜する。処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子、水(H<sub>2</sub>O)など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

## 【0309】

成膜条件の一例としては、基板とターゲットの間との距離を100mm、圧力0.6Pa、直流(DC)電源0.5kW、酸素(酸素流量比率100%)雰囲気下の条件が適用される。なお、パルス直流(DC)電源を用いると、成膜時に発生する粉状物質が軽減でき、膜厚分布も均一となるために好ましい。酸化物半導体膜は好ましくは5nm以上30nm以下とする。なお、適用する酸化物半導体材料により適切な厚みは異なり、材料に応じて適宜厚みを選択すればよい。

## 【0310】

次いで、酸化物半導体膜330を第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。また、島状の酸化物半導体層を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0311】

次いで、酸化物半導体層に第1の加熱処理を行う。この第1の加熱処理によって酸化物半導体層の脱水化又は脱水素化を行うことができる。第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層331を得る(図11(B)参照。)。

## 【0312】

なお、加熱処理装置は電気炉に限られず、抵抗発熱体などの発熱体からの熱伝導又は熱輻射によって、被処理物を加熱する装置を備えていてもよい。例えば、G R T A (G a s R a p i d T h e r m a l A n n e a l) 装置、L R T A (L a m p R a p i d T h e r m a l A n n e a l) 装置等のR T A (R a p i d T h e r m a l A n n e a l) 装置を用いることができる。L R T A 装置は、ハロゲンランプ、メタルハライドランプ、キセノンアークランプ、カーボンアークランプ、高圧ナトリウムランプ、高圧水銀ランプなどのランプから発する光(電磁波)の輻射により、被処理物を加熱する装置である。G R T A 装置は、高温のガスを用いて加熱処理を行う装置である。気体には、アルゴンなどの希ガス、又は窒素のような、加熱処理によって被処理物と反応しない不活性気体が用いられる。

## 【0313】

例えば、第1の加熱処理として、650～700の高温に加熱した不活性ガス中に基板を移動させて入れ、数分間加熱した後、基板を移動させて高温に加熱した不活性ガス中から出すG R T Aを行ってもよい。G R T Aを用いると短時間での高温加熱処理が可能となる。

## 【0314】

なお、第1の加熱処理においては、窒素、又はヘリウム、ネオン、アルゴン等の希ガスに、水、水素などが含まれないことが好ましい。又は、加熱処理装置に導入する窒素、又はヘリウム、ネオン、アルゴン等の希ガスの純度を、6N(99.9999%)以上、好ましくは7N(99.9999%)以上、(即ち不純物濃度を1ppm以下、好ましくは0.1ppm以下)とすることが好ましい。

10

20

30

40

50

## 【0315】

また、第1の加熱処理の条件、又は酸化物半導体層の材料によっては、結晶化し、微結晶膜又は多結晶膜となる場合もある。例えば、結晶化率が90%以上、又は80%以上の微結晶の酸化物半導体膜となる場合もある。また、第1の加熱処理の条件、又は酸化物半導体層の材料によっては、結晶成分を含まない非晶質の酸化物半導体膜となる場合もある。また、非晶質の酸化物半導体の中に微結晶部（粒径1nm以上20nm以下（代表的には2nm以上4nm以下））が混在する酸化物半導体膜となる場合もある。

## 【0316】

また、酸化物半導体層の第1の加熱処理は、島状の酸化物半導体層に加工する前の酸化物半導体膜330に行うことでもできる。その場合には、第1の加熱処理後に、加熱装置から基板を取り出し、フォトリソグラフィ工程を行う。

10

## 【0317】

酸化物半導体層に対する脱水化、脱水素化の効果を奏する加熱処理は、酸化物半導体層成膜後、酸化物半導体層上にソース電極層及びドレイン電極層を積層させた後、ソース電極及びドレイン電極上に保護絶縁膜を形成した後、のいずれで行ってもよい。

## 【0318】

また、ゲート絶縁層302にコンタクトホールを形成する場合、その工程は酸化物半導体膜330に脱水化又は脱水素化処理を行う前でも行った後に行ってもよい。

## 【0319】

なお、ここでの酸化物半導体膜のエッチングは、ウェットエッチングに限定されずドライエッチングを用いてもよい。

20

## 【0320】

所望の加工形状にエッチングできるように、材料に合わせてエッチング条件（エッチング液、エッチング時間、温度等）を適宜調節する。

## 【0321】

次いで、ゲート絶縁層302、及び酸化物半導体層331上に、導電膜を形成する。導電膜をスパッタリング法や真空蒸着法で形成すればよい。導電膜の材料としては、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、マンガン、マグネシウム、ジルコニウム、ベリリウム、トリウムのいずれか一又は複数から選択された材料を用いてもよい。また、導電膜は、単層構造でも、2層以上の積層構造としてもよい。例えば、シリコンを含むアルミニウム膜の単層構造、アルミニウム膜上にチタン膜を積層する2層構造、Ti膜と、そのTi膜上に重ねてアルミニウム膜を積層し、さらにその上にTi膜を成膜する3層構造などが挙げられる。また、Alに、チタン(Ti)、タンタル(Ta)、タングステン(W)、モリブデン(Mo)、クロム(Cr)、Nd(ネオジム)、Sc(スカンジウム)から選ばれた元素を単数、又は複数組み合わせた膜、合金膜、若しくは窒化膜を用いてもよい。

30

## 【0322】

導電膜成膜後に加熱処理を行う場合には、この加熱処理に耐える耐熱性を導電膜に持たせることが好ましい。

40

## 【0323】

第3のフォトリソグラフィ工程により導電膜上にレジストマスクを形成し、選択的にエッチングを行ってソース電極層315a、ドレイン電極層315bを形成した後、レジストマスクを除去する（図11(C)参照。）。

## 【0324】

第3のフォトリソグラフィ工程でのレジストマスク形成時の露光には、紫外線やKrFレーザ光やArFレーザ光を用いる。酸化物半導体層331上で隣り合うソース電極層の下端部とドレイン電極層の下端部との間隔幅によって後に形成される薄膜トランジスタのチャネル長Lが決定される。なお、チャネル長L=25nm未満の露光を行う場合には、数nm～数10nmと極めて波長が短い超紫外線（Extreme Ultraviolet）

50

$t$  ) を用いて第 3 のフォトリソグラフィ工程でのレジストマスク形成時の露光を行う。超紫外線による露光は、解像度が高く焦点深度も大きい。従って、後に形成される薄膜トランジスタのチャネル長  $L$  を  $10\text{ nm}$  以上  $1000\text{ nm}$  以下とすることも可能であり、回路の動作速度を高速化でき、さらにオフ電流値が極めて小さいため、低消費電力化も図ることができる。

【 0 3 2 5 】

なお、導電膜のエッティングの際に、酸化物半導体層 3 3 1 は除去されないようにそれぞれの材料及びエッティング条件を適宜調節する。

【 0 3 2 6 】

なお、第 3 のフォトリソグラフィ工程では、酸化物半導体層 3 3 1 は一部のみがエッティングされ、溝部（凹部）を有する酸化物半導体層となることもある。また、ソース電極層 3 1 5 a、ドレイン電極層 3 1 5 b を形成するためのレジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

【 0 3 2 7 】

また、酸化物半導体層とソース電極層及びドレイン電極層の間に、酸化物導電層を形成してもよい。酸化物導電層とソース電極層及びドレイン電極層を形成するための金属層は、連続成膜が可能である。酸化物導電層はソース領域及びドレイン領域として機能しうる。

【 0 3 2 8 】

ソース領域及びドレイン領域として、酸化物導電層を酸化物半導体層とソース電極層及びドレイン電極層との間に設けることで、ソース領域及びドレイン領域の低抵抗化を図ることができ、トランジスタの高速動作をすることができる。

【 0 3 2 9 】

また、フォトリソグラフィ工程で用いるフォトマスク数及び工程数を削減するため、透過した光が複数の強度となる露光マスクである多階調マスクによって形成されたレジストマスクを用いてエッティング工程を行ってもよい。多階調マスクを用いて形成したレジストマスクは複数の膜厚を有する形状となり、エッティングを行うことでさらに形状を変形することができるため、異なるパターンに加工する複数のエッティング工程に用いることができる。よって、一枚の多階調マスクによって、少なくとも二種類以上の異なるパターンに対応するレジストマスクを形成することができる。よって露光マスク数を削減することができ、対応するフォトリソグラフィ工程も削減できるため、工程の簡略化が可能となる。

【 0 3 3 0 】

次いで、 $N_2O$ 、 $N_2$ 、又は  $Ar$  などのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

【 0 3 3 1 】

プラズマ処理を行った後、大気に触れることなく、酸化物半導体層の一部に接する保護絶縁膜となる酸化物絶縁層 3 1 6 を形成する。

【 0 3 3 2 】

酸化物絶縁層 3 1 6 は、少なくとも  $1\text{ nm}$  以上の膜厚とし、スパッタリング法など、酸化物絶縁層 3 1 6 に水、水素等の不純物を混入させない方法を適宜用いて形成することができる。酸化物絶縁層 3 1 6 に水素が含まれると、その水素の酸化物半導体層への侵入、又は水素による酸化物半導体層中の酸素の引き抜き、が生じ酸化物半導体層のバックチャネルが N 型化（低抵抗化）してしまい、寄生チャネルが形成されるおそれがある。よって、酸化物絶縁層 3 1 6 はできるだけ水素を含まない膜になるように、成膜方法に水素を用いないことが重要である。

【 0 3 3 3 】

本実施の形態では、酸化物絶縁層 3 1 6 として膜厚  $200\text{ nm}$  の酸化珪素膜をスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上  $300$  以下とすればよく、本実施の形態では  $100$  とする。酸化珪素膜のスパッタリング法による成膜は、希ガス（

10

20

30

40

50

代表的にはアルゴン) 雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素混合雰囲気下において行うことができる。また、ターゲットとして酸化珪素ターゲット又は珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び窒素雰囲気下でスパッタリング法により酸化珪素膜を形成することができる。酸素欠乏状態になり、N型化すなわち低抵抗化した酸化物半導体層に接して形成される酸化物絶縁層316は、水分、水素イオン、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、又は酸化窒化アルミニウム膜などを用いる。

#### 【0334】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層316を成膜することが好ましい。酸化物半導体層331及び酸化物絶縁層316に水素、水酸基又は水分が含まれないようにするためである。

10

#### 【0335】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層316に含まれる不純物の濃度を低減できる。

20

#### 【0336】

酸化物絶縁層316を成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

#### 【0337】

次いで、不活性ガス雰囲気下、又は酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行う。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)が酸化物絶縁層316と接した状態で加熱される。

30

#### 【0338】

以上の工程を経ることによって、成膜後の酸化物半導体層に対して脱水化又は脱水素化のための加熱処理を行うと同時に酸化物半導体層が酸素欠乏状態となり低抵抗化、すなわちN型化した後、酸化物半導体層に接するように酸化物絶縁層を形成することにより、酸化物半導体層の一部を選択的に酸素過剰な状態とする。その結果、ゲート電極層311と重なるチャネル形成領域313はI型となる。このとき、少なくともチャネル形成領域363に比べてキャリア濃度が高く、ソース電極層315aに重なる高抵抗ソース領域314aと、少なくともチャネル形成領域363に比べてキャリア濃度が高く、ドレイン電極層315bに重なる高抵抗ドレイン領域314bとが自己整合的に形成される。以上の工程で薄膜トランジスタ310が形成される(図11(D)参照。)。

30

#### 【0339】

さらに、大気中、100以上200以下、1時間以上30時間以下の加熱処理を行ってもよい。本実施の形態では150で10時間加熱処理を行う。この加熱処理は一定の加熱温度を保持して加熱してもよいし、室温から、100以上200以下の加熱温度への昇温と、加熱温度から室温までの降温を複数回くりかえして行ってもよい。また、この加熱処理を、酸化物絶縁層の形成前に、減圧下で行ってもよい。減圧下で加熱処理を行うと、加熱時間を短縮することができる。この加熱処理によって、酸化物半導体層から酸化物絶縁層中に水素がとりこまれ、ノーマリーオフとなる薄膜トランジスタを得ることができる。よって薄膜トランジスタの信頼性を向上できる。また、酸化物絶縁層に欠陥を多く含む酸化シリコン層を用いると、この加熱処理によって酸化物半導体層中に含まれる水素、水分、水酸基又は水素化物などの不純物を酸化物絶縁層に拡散させ、酸化物半導体層中に含まれる該不純物をより低減させる効果を奏する。

40

50

## 【0340】

なお、ドレイン電極層315b（及びソース電極層315a）と重畠した酸化物半導体層において高抵抗ドレイン領域314b（及び高抵抗ソース領域314a）を形成することにより、薄膜トランジスタの信頼性の向上を図ることができる。具体的には、高抵抗ドレイン領域314bを形成することで、ドレイン電極層315bから高抵抗ドレイン領域314b、チャネル形成領域313にかけて、導電性を段階的に変化させうるような構造とすることが可能である。そのため、ドレイン電極層315bを、高電源電位VDDを供給する配線に接続して動作させる場合、ゲート電極層311とドレイン電極層315bとの間に電圧が印加されても高抵抗ドレイン領域がバッファとなり局所的な電界集中が生じにくく、トランジスタの絶縁耐圧を向上させた構成とができる。

10

## 【0341】

また、酸化物半導体層における高抵抗ソース領域又は高抵抗ドレイン領域は、酸化物半導体層の膜厚が15nm以下と薄い場合は膜厚方向全体にわたって形成されるが、酸化物半導体層の膜厚が30nm以上50nm以下とより厚い場合は、酸化物半導体層の一部、ソース電極層又はドレイン電極層と接する領域及びその近傍が低抵抗化し高抵抗ソース領域又は高抵抗ドレイン領域が形成され、酸化物半導体層においてゲート絶縁膜に近い領域はI型とすることもできる。

## 【0342】

酸化物絶縁層316上にさらに保護絶縁層を形成してもよい。例えば、RFスパッタリング法を用いて窒化珪素膜を形成する。RFスパッタリング法は、量産性がよいため、保護絶縁層の成膜方法として好ましい。保護絶縁層は、水分、水素イオン、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、窒化シリコン膜、窒化アルミニウム膜、窒化酸化シリコン膜、窒化酸化アルミニウム膜などを用いる。本実施の形態では、保護絶縁層として保護絶縁層303を、窒化シリコン膜を用いて形成する（図11（E）参照。）。

20

## 【0343】

本実施の形態では、保護絶縁層として保護絶縁層303として、酸化物絶縁層316まで形成された基板300を100～400の温度に加熱し、水素及び水分が除去された高純度窒素を含むスパッタリングガスを導入しシリコンターゲットを用いて、保護絶縁層303として、窒化シリコン膜を成膜する。この場合においても、酸化物絶縁層316と同様に、処理室内の残留水分を除去しつつ保護絶縁層303を成膜することが好ましい。

30

## 【0344】

なお、保護絶縁層303上に平坦化のための平坦化絶縁層を設けてもよい。

## 【0345】

また、保護絶縁層303の上（平坦化絶縁層を設ける場合には平坦化絶縁層の上）に酸化物半導体層と重なる導電層を設けてもよい。導電層は、電位が薄膜トランジスタ310のゲート電極層311と同じでもよいし、異なっていても良く、第2のゲート電極層として機能させることもできる。また、導電層の電位がGND、0Vという固定電位であってもよい。

40

## 【0346】

導電層によって、薄膜トランジスタ310の電気特性を制御することができる。

## 【0347】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

## 【0348】

以上のように、酸化物半導体層を用いる薄膜トランジスタにおいて、安定な電気特性を有し信頼性の高い薄膜トランジスタを提供することができる。

## 【0349】

（実施の形態7）

本実施の形態は、本明細書で開示する論理回路及び半導体装置を構成するトランジスタに適用できる薄膜トランジスタの他の例を示す。

50

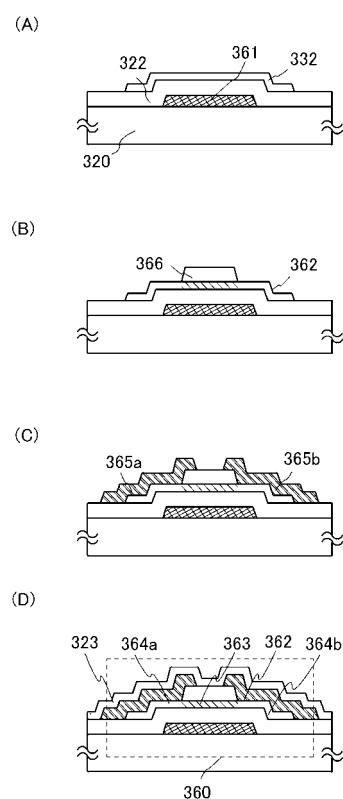

## 【0350】

本実施の形態の薄膜トランジスタ及び薄膜トランジスタの作製方法の一形態を、図12を用いて説明する。

## 【0351】

図12(A)乃至(D)に薄膜トランジスタの断面構造の一例を示す。図12(A)乃至(D)に示す薄膜トランジスタ360は、チャネル保護型(チャネルルストップ型ともいう)と呼ばれるボトムゲート構造の一つであり逆スタガ型薄膜トランジスタともいう。

## 【0352】

また、薄膜トランジスタ360はシングルゲート構造の薄膜トランジスタを用いて説明したが、必要に応じて、チャネル形成領域を複数有するマルチゲート構造の薄膜トランジスタも形成することができる。

## 【0353】

以下、図12(A)乃至(D)を用い、基板320上に薄膜トランジスタ360を作製する工程を説明する。

## 【0354】

まず、絶縁表面を有する基板320上に導電膜を形成した後、第1のフォトリソグラフィ工程によりゲート電極層361を形成する。なお、レジストマスクをインクジェット法で形成してもよい。レジストマスクをインクジェット法で形成するとフォトマスクを使用しないため、製造コストを低減できる。

## 【0355】

また、ゲート電極層361の材料は、モリブデン、チタン、クロム、タンタル、タンゲステン、アルミニウム、銅、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて、単層で又は積層して形成することができる。

## 【0356】

次いで、ゲート電極層361上にゲート絶縁層322を形成する。

## 【0357】

本実施の形態では、ゲート絶縁層322としてプラズマCVD法により膜厚100nm以下の酸化室化珪素層を形成する。

## 【0358】

次いで、ゲート絶縁層322上に、膜厚2nm以上200nm以下の酸化物半導体膜を形成し、第2のフォトリソグラフィ工程により島状の酸化物半導体層に加工する。本実施の形態では、In-Ga-Zn-O系酸化物半導体成膜用ターゲットを用いてスパッタリング法により酸化物半導体膜を成膜する。

## 【0359】

この場合において、処理室内の残留水分を除去しつつ酸化物半導体膜を成膜することが好ましい。酸化物半導体膜に水素、水酸基又は水分が含まれないようにするためである。

## 【0360】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物半導体膜に含まれる不純物の濃度を低減できる。

## 【0361】

酸化物半導体膜を、成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

## 【0362】

次いで、酸化物半導体層の脱水化又は脱水素化を行う。脱水化又は脱水素化を行う第1の加熱処理の温度は、400以上750以下、好ましくは400以上基板の歪み点未

10

20

30

40

50

満とする。ここでは、加熱処理装置の一つである電気炉に基板を導入し、酸化物半導体層に対して窒素雰囲気下450において1時間の加熱処理を行った後、大気に触れることなく、酸化物半導体層への水や水素の再混入を防ぎ、酸化物半導体層332を得る(図12(A)参照。)。

【0363】

次いで、N<sub>2</sub>O、N<sub>2</sub>、又はArなどのガスを用いたプラズマ処理を行う。このプラズマ処理によって露出している酸化物半導体層の表面に付着した吸着水などを除去する。また、酸素とアルゴンの混合ガスを用いてプラズマ処理を行ってもよい。

【0364】

次いで、ゲート絶縁層322、及び酸化物半導体層332上に、酸化物絶縁層を形成した後、第3のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行って酸化物絶縁層366を形成した後、レジストマスクを除去する。

【0365】

本実施の形態では、酸化物絶縁層366として膜厚200nmの酸化珪素膜をスパッタリング法を用いて成膜する。成膜時の基板温度は、室温以上300以下とすればよく、本実施の形態では100とする。酸化珪素膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガス(代表的にはアルゴン)及び酸素混合雰囲気下において行うことができる。また、ターゲットとして酸化珪素ターゲット又は珪素ターゲットを用いることができる。例えば、珪素ターゲットを用いて、酸素、及び窒素雰囲気下でスパッタリング法により酸化珪素膜を形成することができる。酸素欠乏状態となり低抵抗化した酸化物半導体層に接して形成する酸化物絶縁層366は、水分、水素イオン、OH<sup>-</sup>などの不純物を含まず、これらが外部から侵入することをブロックする無機絶縁膜を用い、代表的には酸化シリコン膜、酸化窒化シリコン膜、酸化アルミニウム膜、又は酸化窒化アルミニウム膜などを用いる。

【0366】

この場合において、処理室内の残留水分を除去しつつ酸化物絶縁層366を成膜することが好ましい。酸化物半導体層332及び酸化物絶縁層366に水素、水酸基又は水分が含まれないようにするためである。

【0367】

処理室内の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて排気した成膜室は、例えば、水素原子や、水(H<sub>2</sub>O)など水素原子を含む化合物等が排気されるため、当該成膜室で成膜した酸化物絶縁層366に含まれる不純物の濃度を低減できる。

【0368】

酸化物絶縁層366を成膜する際に用いるスパッタリングガスは水素、水、水酸基又は水素化物などの不純物が、濃度ppm程度、濃度ppb程度まで除去された高純度ガスを用いることが好ましい。

【0369】

次いで、不活性ガス雰囲気下、又は酸素ガス雰囲気下で第2の加熱処理(好ましくは200以上400以下、例えば250以上350以下)を行ってもよい。例えば、窒素雰囲気下で250、1時間の第2の加熱処理を行う。第2の加熱処理を行うと、酸化物半導体層の一部(チャネル形成領域)が酸化物絶縁層366と接した状態で加熱される。

【0370】

本実施の形態は、さらに酸化物絶縁層366が設けられ一部が露出している酸化物半導体層332を、窒素のような不活性ガス雰囲気下、又は減圧下で加熱処理を行う。酸化物絶縁層366によって覆われていない露出された酸化物半導体層332の領域は、窒素のような不活性ガス雰囲気下、又は減圧下で加熱処理を行うと、高抵抗化することができる。

10

20

30

40

50

例えば、窒素雰囲気下で 250 、 1 時間の加熱処理を行う。

【 0371 】

酸化物絶縁層 366 が設けられた酸化物半導体層 332 に対する窒素雰囲気下の加熱処理によって、酸化物半導体層 332 の露出領域は高抵抗化し、抵抗の異なる領域（図 12 (B) においては斜線領域及び白地領域で示す）を有する酸化物半導体層 362 となる。

【 0372 】

次いで、ゲート絶縁層 322 、酸化物半導体層 362 、及び酸化物絶縁層 366 上に、導電膜を形成した後、第 4 のフォトリソグラフィ工程によりレジストマスクを形成し、選択的にエッチングを行ってソース電極層 365a 、ドレイン電極層 365b を形成した後、レジストマスクを除去する（図 12 (C) 参照。）。

10

【 0373 】

ソース電極層 365a 、ドレイン電極層 365b の材料としては、Al 、 Cr 、 Cu 、 Ta 、 Ti 、 Mo 、 W から選ばれた元素、又は上述した元素を成分とする合金か、上述した元素を組み合わせた合金膜等が挙げられる。また、金属導電膜は、単層構造でも、2 層以上の積層構造としてもよい。

【 0374 】

以上の工程を経ることによって、成膜後の酸化物半導体層に対して脱水化又は脱水素化のための加熱処理を行うと同時に酸素欠乏状態となり、即ち N 型化した後、酸化物半導体層に接する酸化物絶縁層の形成を行うことにより酸化物半導体層の一部を選択的に酸素過剰な状態とする。その結果、ゲート電極層 361 と重なるチャネル形成領域 363 は、 I 型となる。このとき、少なくともチャネル形成領域 363 に比べてキャリア濃度が高く、ソース電極層 365a に重なる高抵抗ソース領域 364a と、チャネル形成領域 363 に比べてキャリア濃度が高く、ドレイン電極層 365b に重なる高抵抗ドレイン領域 364b とが自己整合的に形成される。以上の工程で薄膜トランジスタ 360 が形成される。

20

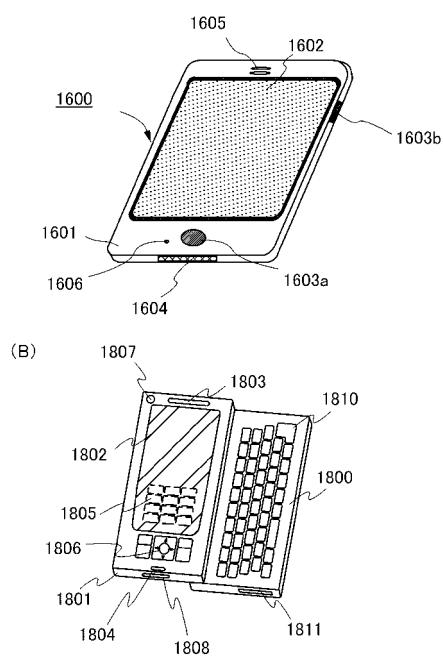

【 0375 】