(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-124549

(P2011-124549A)

(43) 公開日 平成23年6月23日(2011.6.23)

| (51) Int.Cl.        | F 1       | テーマコード (参考) |

|---------------------|-----------|-------------|

| H05K 1/02 (2006.01) | H05K 1/02 | N 5E338     |

| H05K 3/46 (2006.01) | H05K 3/46 | N 5E346     |

|                     | H05K 3/46 | Z           |

審査請求 未請求 請求項の数 7 O L (全 9 頁)

|              |                              |            |                                                                                       |

|--------------|------------------------------|------------|---------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2010-240054 (P2010-240054) | (71) 出願人   | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号                                            |

| (22) 出願日     | 平成22年10月26日 (2010.10.26)     | (74) 代理人   | 100126240<br>弁理士 阿部 琢磨                                                                |

| (31) 優先権主張番号 | 特願2009-258195 (P2009-258195) | (74) 代理人   | 100124442<br>弁理士 黒岩 創吾                                                                |

| (32) 優先日     | 平成21年11月11日 (2009.11.11)     | (72) 発明者   | 星 聰<br>東京都大田区下丸子3丁目30番2号キヤ<br>ノン株式会社内                                                 |

| (33) 優先権主張国  | 日本国 (JP)                     | F ターム (参考) | 5E338 AA03 BB75 CC04 CC06 CD23<br>CD32 EE11<br>5E346 AA35 AA43 BB07 FF01 FF45<br>HH02 |

(54) 【発明の名称】半導体装置

## (57) 【要約】

【課題】 半導体装置のインターポーラ基板内部に設けられた電源パターンに、GND用スルーホール、信号用スルーホール等により、インピーダンスが上昇するため、許容電流を上げることができない。

【解決手段】 半導体装置に設けられた、電源用端子、グラウンド用端子、信号用端子からなる接続用端子のうち、電源用端子はすべて1つの電源領域に配置されており、電源領域には、電源用端子のみが設ける。これによりインターポーラ基板内部に設けられた電源層に不要なスルーホールを空けることがなく、インピーダンスの上昇を抑制できる。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

内層に電源層を備えた多層基板であるインターポーザ基板と、前記インターポーザ基板の一方の表面に設けられている複数の接続用端子と、前記インターポーザ基板の他方の表面に実装されている半導体チップとを有する半導体装置において、

前記複数の接続用端子は、電源用端子、グラウンド用端子、信号用端子からなり、前記電源用端子は電源用スルーホールにより前記電源層の電源パターンおよび前記半導体チップと接続されており、前記グラウンド用端子はグラウンド用スルーホールにより前記半導体チップと接続されており、

前記信号用端子は信号用スルーホールにより前記半導体チップと接続されており、前記電源層の電源パターンに形成されているスルーホールはすべて、前記電源パターンと接続された電源用スルーホールであることを特徴とする半導体装置。 10

**【請求項 2】**

前記インターポーザ基板の内層にはさらにグラウンド層が備えられており、前記グラウンド用端子はグラウンド用スルーホールにより前記グラウンド層に設けられたグラウンドパターンおよび前記半導体チップと接続されており、前記グラウンドパターンに形成されるスルーホールは、すべて前記グラウンドパターンと接続された前記グラウンド用スルーホールであることを特徴とする請求項 1 に記載の半導体装置。

**【請求項 3】**

前記グラウンドパターンは、前記電源パターンと隣接して配置されていることを特徴とする請求項 2 に記載の半導体装置。 20

**【請求項 4】**

内層に電源層を備えた多層基板であるインターポーザ基板と、前記インターポーザ基板の一方の表面に設けられている複数の接続用端子と、前記インターポーザ基板の他方の表面に実装されている半導体チップとを有する半導体装置において、

前記複数の接続用端子は、少なくとも 2 種類の電源を供給する電源用端子、グラウンド用端子、信号用端子からなり、前記電源用端子は電源用スルーホールにより前記電源層の少なくとも 2 つ領域からなる電源パターン、および前記半導体チップと接続されており、前記グラウンド用端子はグラウンド用スルーホールにより前記半導体チップと接続されており、前記信号用端子は信号用スルーホールにより前記半導体チップと接続されており、

前記電源層のそれぞれの電源パターンに形成されているスルーホールはすべて、それぞれの電源パターンに接続された電源用スルーホールであることを特徴とする半導体装置。 30

**【請求項 5】**

前記インターポーザ基板の内層にはさらにグラウンド層が備えられており、前記グラウンド用端子はグラウンド用スルーホールにより前記グラウンド層に設けられたグラウンドパターンおよび前記半導体チップと接続されており、前記グラウンドパターンに形成されるスルーホールは、すべて前記グラウンドパターンと接続された前記グラウンド用スルーホールであることを特徴とする請求項 4 に記載の半導体装置。

**【請求項 6】**

前記グラウンドパターンは、前記電源パターンと隣接して配置されていることを特徴とする請求項 5 に記載の半導体装置。 40

**【請求項 7】**

前記少なくとも 2 種類の電源は、電圧がそれぞれ異なっていることを特徴とする請求項 4 ないし 6 のいずれか一つに記載の半導体装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、半導体集積回路を搭載する半導体装置の構造に関するものである。

**【背景技術】****【0002】**

10

20

30

40

50

ASIC(Application Specific Integrated Circuit)に代表される半導体集積回路(以下、半導体チップ)は、信号を処理するコア回路と、外部回路と信号の入出力を行う入出力回路、コア回路と入出力回路で使用する、電源・グラウンド入力回路(GND入力回路)を備えている。

#### 【0003】

半導体装置は、半導体チップがパッケージと呼ばれる部材に搭載されている。半導体チップを搭載したパッケージをプリント回路板へ実装することで、半導体チップの信号入出力回路、及び電源、GND入力回路がプリント回路板と接続される。

#### 【0004】

パッケージの形態は多種存在するが、数百の入出力端子を持つ半導体チップを用いる場合は、ボールグリッドアレイ型パッケージ(以下、BGA)などが多く使用される。BGAのようなパッケージにはインターポーラーと呼ばれる基板が存在し、半導体チップはインターポーラーに実装される。インターポーラーには、信号、電源、GNDのパターンが配線されており、それらの配線により、半導体チップと入出力端子を接続している。

#### 【0005】

近年の半導体チップには、信号入出力用やコア回路用の電源、GNDが複数存在するため、インターポーラー基板においても電源、GNDパターンが複数存在する。従来から、電源およびGNDを安定化させるために、様々な工夫がなされてきた。

#### 【0006】

インターポーラー基板の電源パターンとGNDパターンを対向して配置し、電源パターンとGNDパターンの間に容量成分を設けることが知られている。特許文献1では、インターポーラー基板の内層の電源プレーンおよびGNDプレーンを分割し、電源、GNDの端子を交互に並べることで容量を確保している。

#### 【先行技術文献】

#### 【特許文献】

#### 【0007】

#### 【特許文献1】特開2005-72311

#### 【発明の概要】

#### 【発明が解決しようとする課題】

#### 【0008】

現在、半導体プロセスの微細化に伴う半導体チップの消費電流増大のため、直流電圧降下やエレクトロマイグレーションが問題になっている。そのため、半導体装置やプリント回路板の、電源パターンおよびGNDパターンの抵抗を小さく、大電流量を流すことの可能な構造にしなければならない。

#### 【0009】

また、半導体チップの消費電流が増大しているため、半導体チップの電源を複数に分割し、動作中に一部の回路を停止させたり、低い動作周波数の回路には低い電圧を供給するなど、半導体チップの多電源化が進んでいる。そのため、半導体装置の電源パターンおよびGNDパターンも半導体チップの多電源化に対応し易い構造が求められている。

#### 【0010】

しかしながら、特許文献1に代表される、接近させた電源、GNDのビアを数多く配置する従来の考え方では、電源、GNDの各構造内に異電位の穴(例えば電源構造においては、GNDや異電源のビアのクリアランスホール)が数多く存在してしまう。従って、例えばプレーン形状を設けたつもりでも、実際には多数の穴によって実効的な抵抗値が上昇してしまう。

#### 【0011】

本発明は上述した課題に鑑みてなされたものであり、その目的は、電源、GNDパターンの抵抗を小さく、かつ許容電流の大きな半導体装置を提供することである。また、本発明の別の目的は、多電源化する半導体チップに対応した電源、GNDパターンを容易に構成可能な半導体装置を提供することである。

10

20

30

40

50

【課題を解決するための手段】

【0012】

前述した課題を解決するために本発明では、内層に電源層を備えた多層基板であるインターポーザ基板と、前記インターポーザ基板の一方の表面に設けられている複数の接続用端子と、前記インターポーザ基板の他方の表面に実装されている半導体チップとを有する半導体装置において、前記複数の接続用端子は、電源用端子、グラウンド用端子、信号用端子からなり、前記電源用端子は電源用スルーホールにより前記電源層の電源パターンおよび前記半導体チップと接続されており、前記グラウンド用端子はグラウンド用スルーホールにより前記半導体チップと接続されており、前記信号用端子は信号用スルーホールにより前記半導体チップと接続されており、前記電源層の電源パターンに形成されているスルーホールはすべて、前記電源パターンと接続された電源用スルーホールである半導体装置、を提供している。

10

【発明の効果】

【0013】

本発明によれば、インターポーザ基板の同一電圧の電源プレーンに、異なる電位の電源用スルーホール、GND用のスルーホール、信号用のスルーホールが開かないため、電源構造の面積を大きくすることが可能となる。従って、電源構造の抵抗を小さくし、かつ許容電流を大きくすることが可能となる。

20

【図面の簡単な説明】

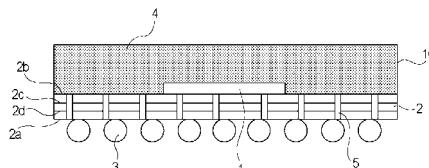

【0014】

【図1】第1の実施形態における半導体装置の断面図

【図2】第1の実施形態における半導体装置のインターポーザの各層の平面図

【図3】第2の実施形態における半導体装置のインターポーザの各層の平面図

【図4】従来の半導体装置の接続用端子面、電源層を示した平面図

【発明を実施するための形態】

【0015】

以下、本発明の実施の形態について図面を参照しながら説明する。

【0016】

(第1の実施の形態)

本発明の第1の実施形態を、図1、図2を用いて説明する。図1は本発明における半導体装置の断面図である。半導体装置10は、半導体チップ1、インターポーザ基板2、接続用端子3、封止樹脂4からなっている。インターポーザ基板2は多層基板であり、表面層は接続用端子面2aと、半導体チップ実装面2bが設けられており、内層には電源層2cおよびGND層2dが形成されている。半導体チップ1は、半導体チップ実装面2bに形成された、電源パターン、GNDパターン、信号パターン(不図示)と接続されている。電源パターン、GNDパターン、信号パターンは、スルーホール5を介して、接続用端子面2aに引き出され、接続用端子3と接続されている。図1における半導体装置10で使用する電源は1種類である。なお、電源層2cとGND層2dの配置は逆であっても構わない。

30

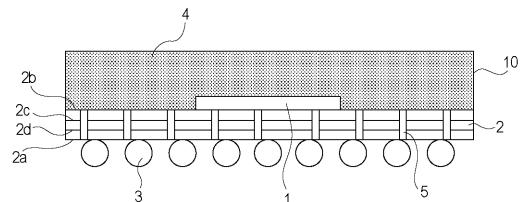

【0017】

図2(a)は半導体装置10の接続用端子面2aを示した平面図である。101は半導体チップ1に電源を供給する電源用端子であり、102は半導体チップ1にGNDを供給するグラウンド用端子(GND用端子)である。103は半導体チップ1に各種の信号を供給する信号用端子である。すべての電源用端子101は電源領域111に配置されており、電源領域111には電源用端子101のみが配置されている。また、すべてのGND用端子102はグラウンド領域(GND領域)112に配置されており、GND領域112にはGND用端子102のみが配置されている。

40

【0018】

図2(b)は、半導体装置10のGND層2dの平面図である。122はGNDパターンであり、スルーホール152を介してGND用端子102、および後述するGNDパタ

50

ーン 132 に接続されている。なお、説明を容易にするため、スルーホール 152 以外の電源用スルーホールおよび信号用スルーホールは、図 2 ( b ) には記載していない。

#### 【 0019 】

図 2 ( c ) は、半導体装置 10 の電源層 2c の平面図である。121 は電源パターンであり、スルーホール 151 を介して電源用端子 101 、および後述する電源パターン 131 に接続されている。なお、説明を容易にするため、スルーホール 151 以外の GND 用スルーホールおよび信号用スルーホールは、図 2 ( c ) には記載していない。

#### 【 0020 】

図 2 ( d ) は、半導体装置 10 の半導体チップ実装面 2b の平面図である。なお、説明を容易するために、半導体チップ 1 を点線で示し、スルーホールの記載は省略している。131 は半導体チップ実装面における電源パターンであり、前述のスルーホール 151 を介して電源用端子 101 、および電源パターン 121 に接続されている。11 は半導体チップ 1 の内部に設けられた接続用電源パターンであり、ワイヤボンディング ( 不図示 ) により電源パターン 131 と接続されている。132 は半導体チップ実装面における GND パターンであり、前述のスルーホール 152 を介して GND 用端子 102 、および GND パターン 122 に接続されている。12 は半導体チップ 1 の内部に設けられた GND 用電源パターンであり、ワイヤボンディング ( 不図示 ) により GND パターン 132 と接続されている。

10

#### 【 0021 】

このような第 1 の実施の形態とすることで、電源パターン 121 には GND 用のスルーホールや、信号用のスルーホールが形成されない。従って、電源パターン 121 抵抗値を下げ、インピーダンスを低く保つことができるため、電流量の多い場合であっても、安定して電源を供給することができる。また、GND パターン 122 には電源用のスルーホールや、信号用のスルーホールが形成されない。従って、GND パターン 122 の抵抗値を下げ、インピーダンスを低く保つことができるため、電流量の多い場合であっても、安定した GND とすることができる。

20

#### 【 0022 】

なお、本実施例の場合、バイパスコンデンサ ( 不図示 ) は、電源領域 111 と GND 領域 112 との境界部に配置することが好ましい。また、本実施例では、電源用端子 101 および GND 用端子 102 をともに、電源領域 111 および GND 領域 112 に集めているが、GND 用端子 102 に関しては必ずしも 1 つの GND 領域 112 に集める必要はなく、複数の領域に分散して配置してもかまわない。

30

#### 【 0023 】

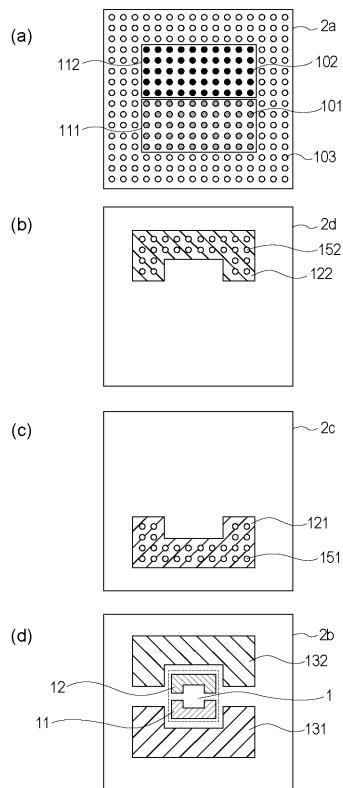

##### ( 第 2 の実施の形態 )

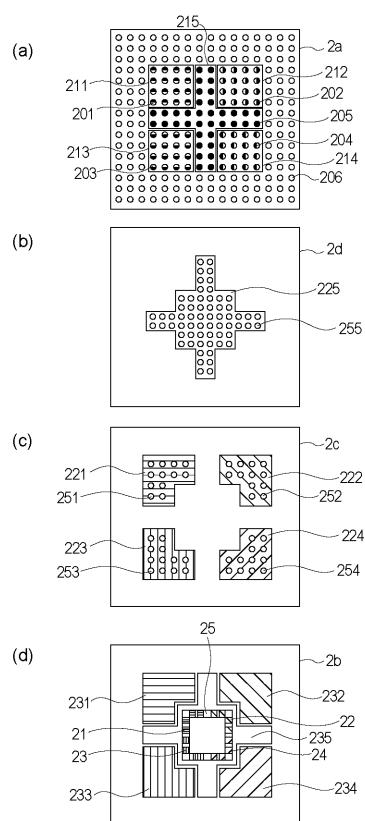

本発明の第 2 の実施形態を図 3 を用いて説明する。なお、本実施例で使用する半導体装置の断面図は、第 1 の実施形態で示した半導体装置 10 と同様であるため、図 1 と同じ符号を使って説明する。第 1 の実施形態と異なるのは、インターポーザ基板 2 の接続用端子面 2a および半導体チップ実装面 2b の形態である。本実施の形態における半導体装置では、4 種類の電源を使用している。

40

#### 【 0024 】

図 3 ( a ) は半導体装置 10 の接続用端子面 2a を示した平面図である。201 は半導体チップ 1 に電源を供給する第 1 の電源用端子である。202 は第 2 の電源用端子、203 は第 3 の電源用端子、204 は第 4 の電源用端子である。205 は半導体チップ 1 に GND を供給する GND 用端子である。206 は半導体チップ 1 に各種の信号を供給する信号用端子である。

#### 【 0025 】

すべての第 1 の電源用端子 201 は第 1 の電源領域 211 に配置されており、電源領域 211 には電源用端子 201 のみが配置されている。同様に、第 2 の電源用端子 202 は第 2 の電源領域 212 に配置されており、第 2 の電源領域 212 には電源用端子 202 のみが配置されている。第 3 の電源用端子 203 は第 3 の電源領域 213 に配置されており

50

、第3の電源領域213には電源用端子203のみが配置されている。第4の電源用端子204は第4の電源領域214に配置されており、第4の電源領域214には電源用端子204のみが配置されている。

#### 【0026】

また、すべてのGND用端子205はGND領域215に配置されており、GND領域215にはGND用端子205のみが配置されている。GND領域215は、第1の電源領域211、第2の電源領域212、第3の電源領域213、第4の電源領域214のすべてと隣接するように形成されており、図3(a)ではプラス状に形成されている。

#### 【0027】

図3(b)は、半導体装置10のGND層2dの平面図である。225はGNDパターンであり、スルーホール255を介してGND用端子205、およびGNDパターン215に接続されている。なお、説明を容易にするため、スルーホール255以外の電源用スルーホールおよび信号用スルーホールは、図3(b)には記載していない。

10

#### 【0028】

図3(c)は、半導体装置10の電源層2cの平面図である。221は第1の電源パターンであり、スルーホール251を介して第1の電源用端子201、および後述する電源パターン231に接続されている。同様に、222は第2の電源パターンであり、スルーホール252を介して第1の電源用端子202、および電源パターン232に接続されている。223は第3の電源パターンであり、スルーホール253を介して第3の電源用端子203、および電源パターン233に接続されている。224は第4の電源パターンであり、スルーホール254を介して第4の電源用端子204、および電源パターン234に接続されている。なお、説明を容易にするため、スルーホール251、252、253、254以外のGND用スルーホールおよび信号用スルーホールは、図3(c)には記載していない。

20

#### 【0029】

図3(d)は、半導体装置10の半導体チップ実装面2bの平面図である。なお、説明を容易するために、半導体チップ1を点線で示し、スルーホールの記載は省略している。231は半導体チップ実装面における第1の電源パターンであり、前述のスルーホール251を介して第1の電源用端子201、および第1の電源パターン221に接続されている。21は半導体チップ1の内部に設けられた第1の接続用電源パターンであり、ワイヤボンディング(不図示)により第1の電源パターン231と接続されている。

30

#### 【0030】

同様に、232は半導体チップ実装面における第2の電源パターンであり、前述のスルーホール252を介して第2の電源用端子202、および第2の電源パターン222に接続されている。22は半導体チップ1の内部に設けられた第2の接続用電源パターンであり、ワイヤボンディング(不図示)により第2の電源パターン232と接続されている。233は半導体チップ実装面における第3の電源パターンであり、前述のスルーホール253を介して第3の電源用端子203、および第3の電源パターン223に接続されている。23は半導体チップ1の内部に設けられた第3の接続用電源パターンであり、ワイヤボンディング(不図示)により第3の電源パターン233と接続されている。234は半導体チップ実装面における第4の電源パターンであり、前述のスルーホール254を介して第4の電源用端子204、および第4の電源パターン224に接続されている。24は半導体チップ1の内部に設けられた第4の接続用電源パターンであり、ワイヤボンディング(不図示)により第4の電源パターン234と接続されている。

40

#### 【0031】

235は半導体チップ実装面におけるGNDパターンであり、前述のスルーホール255を介してGND用端子205、およびGNDパターン225に接続されている。25は半導体チップ1の内部に設けられたGND用電源パターンであり、ワイヤボンディング(不図示)によりGNDパターン235と接続されている。

#### 【0032】

50

このような第2の実施の形態とすることで、第1の電源パターン221、第2の電源パターン222、第3の電源パターン223、第4の電源パターン224には、他の電源用のスルーホール、GND用のスルーホール、信号用のスルーホールが形成されない。従って、第1ないし第4の電源パターン221、222、223、224の抵抗値を下げ、インピーダンスを低く保つことができるため、電流量の多い場合であっても、安定して電源を供給することができる。

#### 【0033】

また、GNDパターン225には電源用のスルーホールや、信号用のスルーホールが形成されない。従って、GNDパターン225の抵抗値を下げ、インピーダンスを低く保つことができるため、電流量の多い場合であっても、安定したGNDとすることができる。

10

#### 【0034】

なお、本実施例の場合、バイパスコンデンサ（不図示）は、第1ないし第4の電源領域211、212、213、214とGND領域215との境界部に配置することが好ましい。また、GND用端子205に関しては必ずしも1つのGND領域215に集める必要はなく、複数の領域に分散して配置してもかまわない。

#### 【0035】

なお本実施の形態では、すべての電源用端子に対応してスルーホールが形成されているが、必ずしも1対1に対応する必要はなく、スルーホールの数は設計に応じて変更することも可能である。スルーホールの数が少なければ、電源パターンの領域をより広げることができ、より安定した電源とすることが可能である。

20

#### 【0036】

また、必ずしもスルーホールが必須ではなく、設計に応じて貫通していない非貫通ビアを使用することも可能である。非貫通ビアを使用することにより、電源パターンの領域をより広げることができ、より安定した電源とすることが可能である。

#### 【0037】

また、ワイヤボンディング型の半導体チップに代えて、フリップチップ型の半導体チップを使用することも可能である。ワイヤボンディング型の半導体チップを使用することにより、電源パターンの領域をより広げることができ、より安定した電源とすることが可能である。

30

#### 【0038】

また、第2の実施の形態では電源の種類が4つの場合について説明したが、本発明はこれに限られず、少なくとも2種類以上の電源であれば同様の手法により対応可能である。電源の種類としては、電圧が異なるもの、同じ電圧であるがノイズ干渉の点などから分離しているもの（例えばアナログ電源とデジタル電源）等が考えられる。

#### 【0039】

##### （比較例）

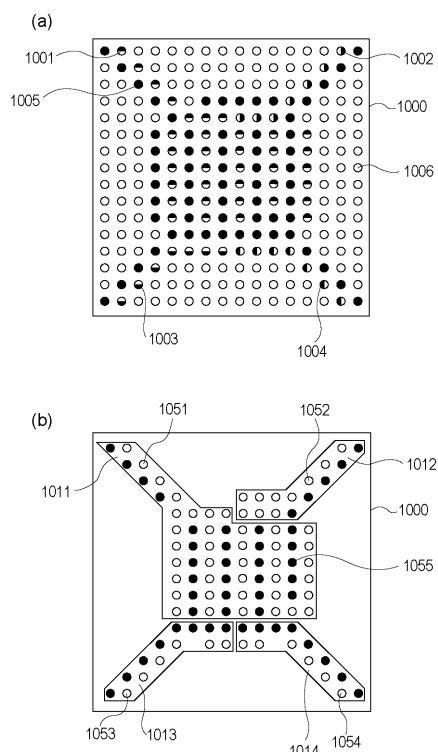

本発明の比較例を図4を用いて説明する。なお、本実施例で使用する半導体装置の断面図は、第1の実施形態で示した半導体装置10と同様であるため、図1と同じ符号を使って説明する。本比較実施例における半導体装置では、4種類の電源を使用している。

40

#### 【0040】

図4(a)は半導体装置1000の接続用端子面2aを示した平面図である。1001は半導体チップ1に電源を供給する第1の電源用端子である。1002は第2の電源用端子、1003は第3の電源用端子、1004は第4の電源用端子である。1005は半導体チップ1にGNDを供給するGND用端子である。1006は半導体チップ1に各種の信号を供給する信号用端子である。従来、電源用端子とGND用端子を近づけることが定石であったため、各電源用端子とGNDが交互に並ぶ配置となっている。

#### 【0041】

図4(b)は、半導体装置10の電源層2cの平面図である。1011は第1の電源パターンであり、スルーホール1051を介して第1の電源用端子1001、および半導体装置10に接続されている。同様に、1012は第2の電源パターンであり、スルーホー

50

ル 1 0 5 2 を介して第 2 の電源用端子 1 0 0 2 、および半導体装置 1 0 に接続されている。1 0 1 3 は第 3 の電源パターンであり、スルーホール 1 0 5 3 を介して第 3 の電源用端子 1 0 0 3 、および半導体装置 1 0 に接続されている。1 0 1 4 は第 4 の電源パターンであり、スルーホール 1 0 5 4 を介して第 4 の電源用端子 1 0 0 4 、および半導体装置 1 0 に接続されている。1 0 5 5 は G N D 用のスルーホールである。なお、説明を容易にするために、第 1 ないし第 4 の電源パターン 1 0 1 1 、1 0 1 2 、1 0 1 3 、1 0 1 4 以外の領域に形成された、G N D 用スルーホールおよび信号用スルーホールは、図 4 ( b ) には記載していない。

#### 【 0 0 4 2 】

図 4 に示すように、従来の半導体装置では、電源用端子と G N D 用端子の近接配置するため、他の電源用のスルホール、G N D 用のスルホール 1 0 5 5 、信号用のスルホールによって数多くの穴が空いてしまう。インピーダンスを低く保つために多くの面積を電源構造に割り当てたにも関わらず、実効的な電源構造の抵抗が増大し、かつ許容電流量が小さくなってしまう。

10

#### 【 符号の説明 】

#### 【 0 0 4 3 】

- 1 半導体チップ

- 2 インターポーザ基板

- 2 a 接続用端子面

- 2 b 半導体チップ実装面

- 2 c 電源層

- 2 d G N D 層

- 3 接続用端子

- 4 封止樹脂

- 5 、1 5 1 、2 5 1 ~ 2 5 4 、1 0 5 1 ~ 1 0 5 5 スルーホール

- 1 0 半導体装置

- 1 1 、2 1 ~ 2 4 電源接続用領域

- 1 0 1 、2 0 1 ~ 2 0 4 、1 0 0 1 ~ 1 0 0 4 電源用端子

- 1 0 2 、2 0 5 、1 0 0 5 G N D ( グラウンド ) 用端子

- 1 0 3 、2 0 6 、1 0 0 6 信号端子

- 1 1 1 、2 1 1 ~ 2 1 4 電源領域

- 1 1 2 、2 1 5 G N D ( グラウンド ) 領域

- 1 2 1 、1 3 1 、2 2 1 ~ 2 2 4 、2 3 1 ~ 2 3 4 電源パターン

20

30

【図1】

【図2】

【図3】

【図4】