(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2006-507684

(P2006-507684A)

(43) 公表日 平成18年3月2日(2006.3.2)

| (51) Int.C1.                  | F 1        | テーマコード (参考) |

|-------------------------------|------------|-------------|

| <b>HO1L 27/08 (2006.01)</b>   | HO1L 27/08 | 331E 5FO48  |

| <b>HO1L 29/786 (2006.01)</b>  | HO1L 29/78 | 613Z 5F11O  |

| <b>HO1L 21/8234 (2006.01)</b> | HO1L 29/78 | 618C        |

| <b>HO1L 27/088 (2006.01)</b>  | HO1L 29/78 | 617N        |

|                               | HO1L 27/08 | 102C        |

審査請求 未請求 予備審査請求 有 (全 17 頁)

(21) 出願番号 特願2004-555330 (P2004-555330)

(86) (22) 出願日 平成15年10月14日 (2003.10.14)

(85) 翻訳文提出日 平成17年7月7日 (2005.7.7)

(86) 國際出願番号 PCT/US2003/032782

(87) 國際公開番号 WO2004/049445

(87) 國際公開日 平成16年6月10日 (2004.6.10)

(31) 優先権主張番号 10/301,617

(32) 優先日 平成14年11月22日 (2002.11.22)

(33) 優先権主張国 米国(US)

(71) 出願人 591016172

アドバンスト・マイクロ・ディバイシズ・

インコーポレイテッド

ADVANCED MICRO DEVI

CES INCORPORATED

アメリカ合衆国、94088-3453

カリフォルニア州、サンディベイル、ビィ・

オウ・ボックス・3453、ワン・エイ・

エム・ディ・プレイス、メイル・ストップ

・68 (番地なし)

(74) 代理人 100099324

弁理士 鈴木 正剛

(74) 代理人 100111615

弁理士 佐野 良太

最終頁に続く

(54) 【発明の名称】 2トランジスタNORデバイス

## (57) 【要約】

NORゲートは、従来の4つのトランジスタを有するNORゲートの代わりに、2つの非対称のFinFET型トランジスタで形成される。トランジスタの数が4つから2つに減少することにより、集積半導体回路において著しく改良することができる。

## 【特許請求の範囲】

## 【請求項 1】

独立して制御可能な第1および第2ゲート領域(822)、(823)、ソース領域(821)、およびドレイン領域(820)を含む、第1FinFET(801)と、

独立して制御可能な第1および第2ゲート領域(832)、(833)、ソース領域(831)、およびドレイン領域(830)を含む、第2FinFET(802)と、

前記第1FinFET(801)の前記第1ゲート領域(822)と、前記第2FinFET(802)の前記第1ゲート領域(832)に接続されるNORゲートの第1入力線と、

前記第1FinFET(801)の前記第2ゲート領域(823)と、前記第2FinFET(802)の前記第2ゲート領域(833)に接続されるNORゲートの第2入力線と、

前記第1FinFET(801)の前記ソース(820)と、前記第2FinFET(802)の前記ドレイン(830)に接続されるNORゲートの出力線とを含む、NORゲート。

## 【請求項 2】

前記第1FinFETおよび第2FinFETの前記第1ゲート領域は、n型不純物でドープされる、請求項1記載のNORゲート。

## 【請求項 3】

前記第1FinFETおよび第2FinFETの前記第2ゲート領域は、p型不純物でドープされる、請求項2記載のNORゲート。

## 【請求項 4】

前記NORゲートに含まれるトランジスタは、前記第1FinFETおよび第2FinFETのみである、請求項1記載のNORゲート。

## 【請求項 5】

複数のFinFET(801)、(802)を含む集積半導体デバイスであって、複数のFinFETのうちの少なくともいくつかは、論理NORゲートを定義する対となるFinFETを複数含むようにして配列される、

集積半導体デバイス。

## 【請求項 6】

前記対となるFinFETは、

独立して制御可能な第1および第2ゲート領域(822)、(823)、ソース領域(821)、およびドレイン領域(820)を含む、第1FinFET(801)と、

独立して制御可能な第1および第2ゲート領域(832)、(833)、ソース領域(831)、およびドレイン領域(830)を含む、第2FinFET(802)と、

前記第1FinFET(801)の前記第1ゲート領域(822)と、前記第2FinFET(802)の前記第1ゲート領域(832)に接続される第1入力線と、

前記第1FinFET(801)の前記第2ゲート領域(823)と、前記第2FinFET(802)の前記第2ゲート領域(833)に接続される第2入力線と、

前記第1FinFET(801)の前記ソース(820)と、前記第2FinFET(802)の前記ドレイン(830)に接続される出力線とを含む、請求項5記載の集積半導体デバイス。

## 【請求項 7】

第1ダブルゲートトランジスタ(801)と、

第2ダブルゲートトランジスタ(802)とを含み、

前記第1トランジスタおよび第2トランジスタと接続される出力信号は、この第1トランジスタおよび第2トランジスタに与えられる2つの入力信号の論理NOR演算を反映する、

論理NOR回路。

## 【請求項 8】

10

20

30

40

50

前記第1ダブルゲートトランジスタおよび前記第2ダブルゲートトランジスタは、FinFETである、請求項7記載の論理NOR回路。

#### 【請求項9】

前記第1ダブルゲートトランジスタおよび前記第2ダブルゲートトランジスタはそれぞれ、

第1ゲート領域(822)、(832)と、

この第1ゲート領域と無関係に制御可能に構成される第2ゲート領域(823)、(833)と、

ソース領域(821)、(831)と、

ドレイン領域(820)、(830)とを含む、請求項7記載の論理NOR回路。

10

#### 【請求項10】

前記第1ゲート領域は、n型不純物でドープされる、請求項9記載の論理NOR回路。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、半導体製造、および半導体デバイスに関する。本発明は特に、ダブルゲートMOSFETに適用することができる。

##### 【背景技術】

##### 【0002】

MOSFETのようなトランジスタは、半導体デバイスの大部分のコア・ビルディング・ブロック(core building block)である。

高性能プロセッサのような半導体デバイスは、何百万ものトランジスタを含むことができる。

これらのデバイスについては、トランジスタの大きさを縮小すること、すなわちトランジスタ密度を増加させることができることが、半導体製造分野において従来からの最優先事項であった。

##### 【0003】

従来のMOSFETでは、製造処理において50nm未満にスケーリングすることが困難である。50nm以下のMOSFETを開発すべく、ダブルゲートMOSFETが提案されている。いくつかの点において、ダブルゲートMOSFETは従来のバルクシリコンMOSFETよりも優れた特性を呈する。

これらの優れた特性を呈するのは、ダブルゲートMOSFETは、従来のMOSFETのようにチャネルの片側上だけではなくチャネルの両側上にゲート電極を有するためである。

2つのゲートがある場合、ドレインによって生成される電界は、チャネルのソース端からより遮断される。また、2つのゲートはシングルゲートのおよそ2倍の電流を制御することができ、このことはより強いスイッチング信号に帰着する。

##### 【0004】

半導体デバイス上のトランジスタは、しばしば、より高いレベルの論理ゲートを実装するグループ中に接続される。よく使用される論理ゲートの1つは、NORゲートである。一般的に、NORゲートの生成には4つのダブルゲートMOSFETのような4つのトランジスタが使用される。

##### 【0005】

NORゲートのような論理ゲートをより効率的に実装することが望ましい。これにより半導体デバイスの総合効率を増加させ得る。

#### 【発明の開示】

##### 【0006】

本発明の趣旨に沿った実装は、2つのトランジスタのみで実装されるNORゲートを含む。

##### 【0007】

40

50

本発明の1つの態様は、集積半導体デバイスに関する。このデバイスは、多くの非対称のFinFETを含んでいる。このFinFETの少なくともいくつかは、論理NORゲートを定義する複数の対となるFinFETとして配列されている。

【0008】

本発明の他の態様は、第1ダブルゲートトランジスタと第2ダブルゲートトランジスタからなる論理NORゲートに関する。

第1および第2トランジスタと接続される出力信号は、第1トランジスタおよび第2トランジスタに接続される2つの入力信号の論理NOR演算を反映する。

【発明を実施するための最良の形態】

【0009】

同じ参照符号を有する要素は類似の要素を示している、添付した図面を参照する。

以下、添付の図面に言及して本発明の趣旨に沿った実装を詳細に記載する。異なる図面における同一の参照符号は、同一又は類似の要素を示す。また、以下の詳細な記載は本発明を制限するものではない。代わりに、本発明の範囲は添付の請求項および均等物によって定義される。

【0010】

NORゲートを実装すべく、2つのトランジスタが共に接続される。このトランジスタはそれぞれ、2つの別個にアドレス可能なゲートを有する非対称のFinFETであり得る。

【0011】

FinFETは、ここで使用されるように、セルフアラインされたダブルゲートによって制御される垂直方向のSi「フィン」中に導電性のチャネルが形成される、ダブルゲートMOSFETの種類を示す。FinFETは、当業者に知られている。

従来のFinFETは、典型的に「ダブルゲート」MOSFETと記載されるが、2つのゲートは電気的に接続され、それゆえ単一の論理的にアドレス可能なゲートを形成する。

【0012】

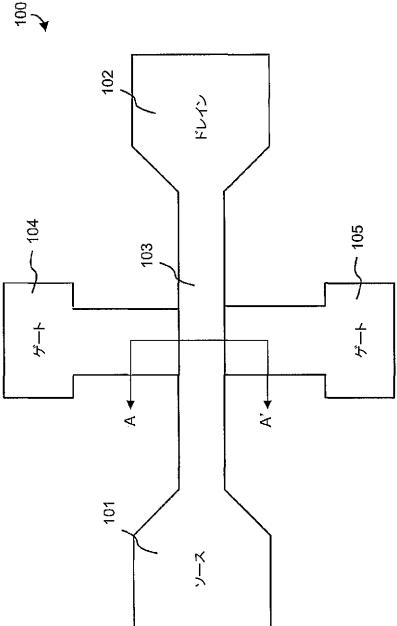

図1は、本発明の趣旨に沿ったFinFET100の上面図である。FinFET100は、ソース領域101、ドレイン領域102およびチャネル領域103を含んでいる。

図2について以下に記載するように、チャネル領域103は、トランジスタのフィンを含む。

ゲートの両側が共に電気的に接続されている従来のFinFETと異なり、FinFET100は、ゲート104および105と符号付けされた2つのアドレス可能なゲートをさらに含むことができる。さらにこれらのゲートを、非対称にドープしてもよい。

以下により詳細に記載するように、例えばゲート104にn型ドーパント（例えば、As<sup>+</sup>またはP<sup>+</sup>）を注入してもよい。また、ゲート105にp型ドーパント（例えばBまたはBF<sub>2</sub>）を注入してもよい。

【0013】

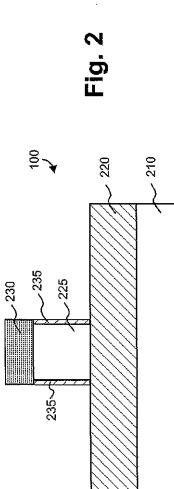

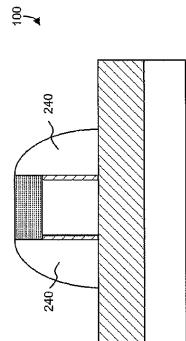

図2ないし図7は、図1中のA-A'線に沿った断面図である。図2ないし図8はそれぞれ、FinFET100の製造プロセスのステップを示す。

【0014】

図2に示すように、FinFET100は、シリコン基板210、およびこのシリコン基板に配置される埋込酸化物（BOX）層220を含むSOI（silicon on insulator）デバイスであり得る。

代替的に、基板210および層230は、ゲルマニウム、金属、またはシリコンゲルマニウムのようにこのような材料の組合せを含んでいてもよい。埋込酸化膜220は、従来の方法によりシリコン基板210上に形成することができる。埋込酸化膜220は、約200nmから400nmの範囲の厚みを有するようにしてよい。

【0015】

シリコン層は、BOX層220上に配置され、ソース、ドレイン、およびフィン225

10

20

30

40

50

(ソース及びドレインは、図2には示されない。)を生成すべくエッティングされてもよい。

代替的に、シリコンをたい積すると共に、フィン225を形成した後にこのシリコンをエッティングすることによって、ソース／ドレイン領域101、102を形成してもよい。

実装の一形態においては、フィン225は、例えば約5nmから約25nmの範囲の幅を有するようにしてもよい。

フィン225をエッティングする前に、フィン225上に $\text{Si}_3\text{N}_4$ 層230を化学蒸着法(CVD)によってたい積することができる。代替的に、層230は $\text{SiO}_2$ 層であってもよい。層230は、製造プロセス中にフィン225を保護する。この沿う230は、例えば、約20nmから約50nmの範囲の厚みにたい積してもよい。

10

#### 【0016】

フィン225のシリコン表面を酸化させることによって、ゲート絶縁層235をフィン225の側面上に成長させてもよい。ゲート絶縁層235は、0.8nmから2nmの幅のように薄くしてもよい。

#### 【0017】

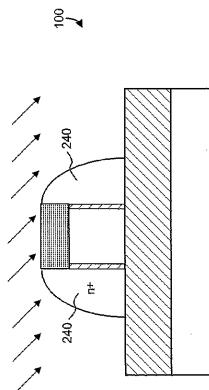

図3に示すように、次に、従来のたい積技術およびエッティング技術を使用して、ポリシリコン・スペーサ240をフィン225の周囲(およびゲート絶縁層235と層230の周囲)に形成することができる。

#### 【0018】

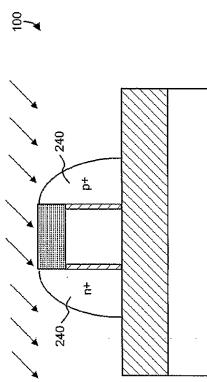

その後、傾斜(tilted)インプラントプロセス(図4)を使用して、ポリシリコン・スペーサ240にn型ドーパントを注入してもよい。このドーパントは、例えば $\text{As}^+$ または $\text{P}^+$ とすることができます、15度から45度の傾斜角で、(P<sup>+</sup>については)3から6keVまたは(As<sup>+</sup>については)12から15keVのイオンビームを使用して注入することができる。

20

ゲート絶縁層235および層230を含むフィン構造225があることにより、ほとんどのn型ドーパントのポリシリコン・スペーサ240の片面(例えば図4における右側)への侵入が妨げられることになる。

#### 【0019】

n型ドーパントを注入した後、ポリシリコン・スペーサに傾けたインプラントプロセスを使用して、p型ドーパントを注入してもよい。インプラントプロセスのイオンビームは、図4に示す角度に対する余角で傾けることができる。

30

このドーパントは、例えばBまたは $\text{BF}_2$ とすることができます、15度から45度の傾斜角で、(Bについては)1から2keVまたは(BF<sub>2</sub>については)4から8keVのイオンビームを使用して注入することができる。

ゲート絶縁層235および層230を含むフィン構造225があることにより、ほとんどのp型ドーパントのポリシリコン・スペーサ240の片面(例えば図4における左側)への侵入が妨げられることになる。

このように、この2つのポリシリコン・スペーサ240は、n型ドーパントとp型ドーパントで非対称的にドープされることになる。

当業者は、図4および図5に示すステップの順序を容易に変更し得ることを認識するであろう。

40

#### 【0020】

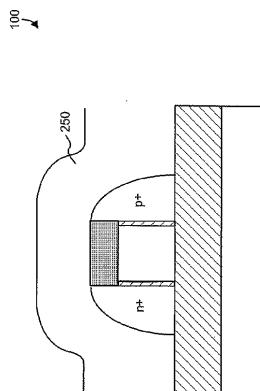

その後、図6に示すように、ドープされていないポリシリコン層250をFinFET100上にたい積することができる。

ポリシリコン層250は、FinFET100のゲートを形成することとなる。層250は、CVDによって、例えば約100nmの深さにたい積することができる。

#### 【0021】

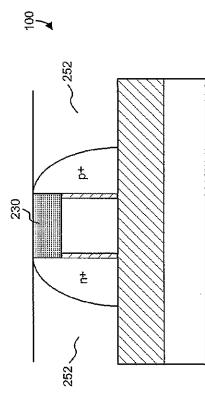

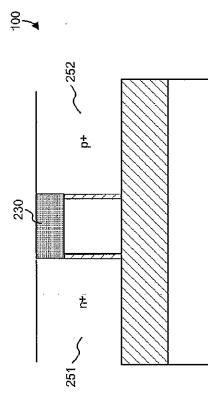

ポリシリコン層250をたい積した後、図7Aに示すように、層250が実質的に層230の上面と同じ高さになるように、FinFET100をプレーナ化することができる。

50

このことは、層 251、252 と符号付けされる 2 つの電気的に接続されていないポリシリコン層を生成する。その後、図 7B に示すように、完全にシリサイド化されたポリシリコン層 251、252 を生成すべく、FinFET100 をアニーリングしてもよい。層 251 および層 252 は、ゲートパッド 104、105 に接続され、独立して制御することができる。

#### 【0022】

代替的に、図 7B に示すような非対称の FinFET を生成する他のプロセスを使用してもよい。例えば、ポリシリコン・ゲート材料をたい積し、プレーナ化した後、図 4 および図 5 について記載される傾斜 (tilt) インプラントプロセスを実行してもよい。

この各場合においては、図 7B に示すように、生成される構造には別々に制御することができる 2 つのゲートを含む。

#### 【0023】

NOR ゲートは、集積回路でよく使用される論理ゲートである。NOR ゲートは、2 つ以上の入力信号に基づく値を出力する。通常、NOR ゲートは 4 つのトランジスタを使用して形成される。2 入力 NOR ゲートの論理を、以下の表 1 に示す。

#### 【0024】

##### 【表 1】

| 表1  |     |    |

|-----|-----|----|

| 入力A | 入力B | 出力 |

| 0   | 0   | 1  |

| 0   | 1   | 0  |

| 1   | 0   | 0  |

| 1   | 1   | 0  |

#### 【0025】

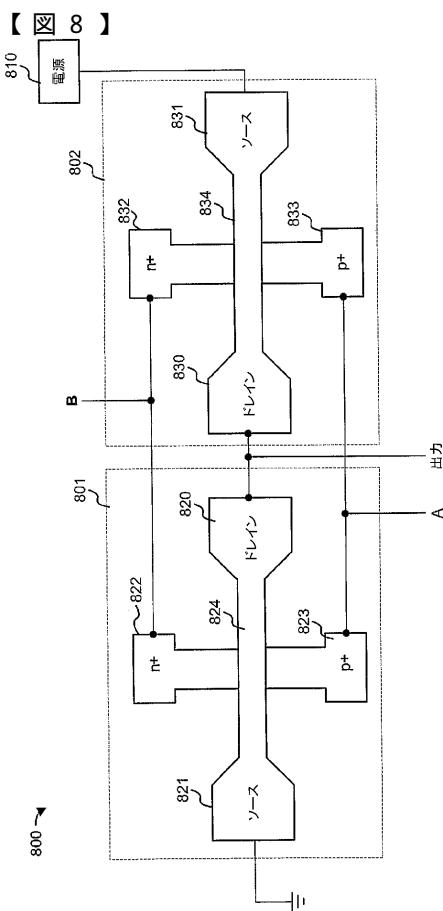

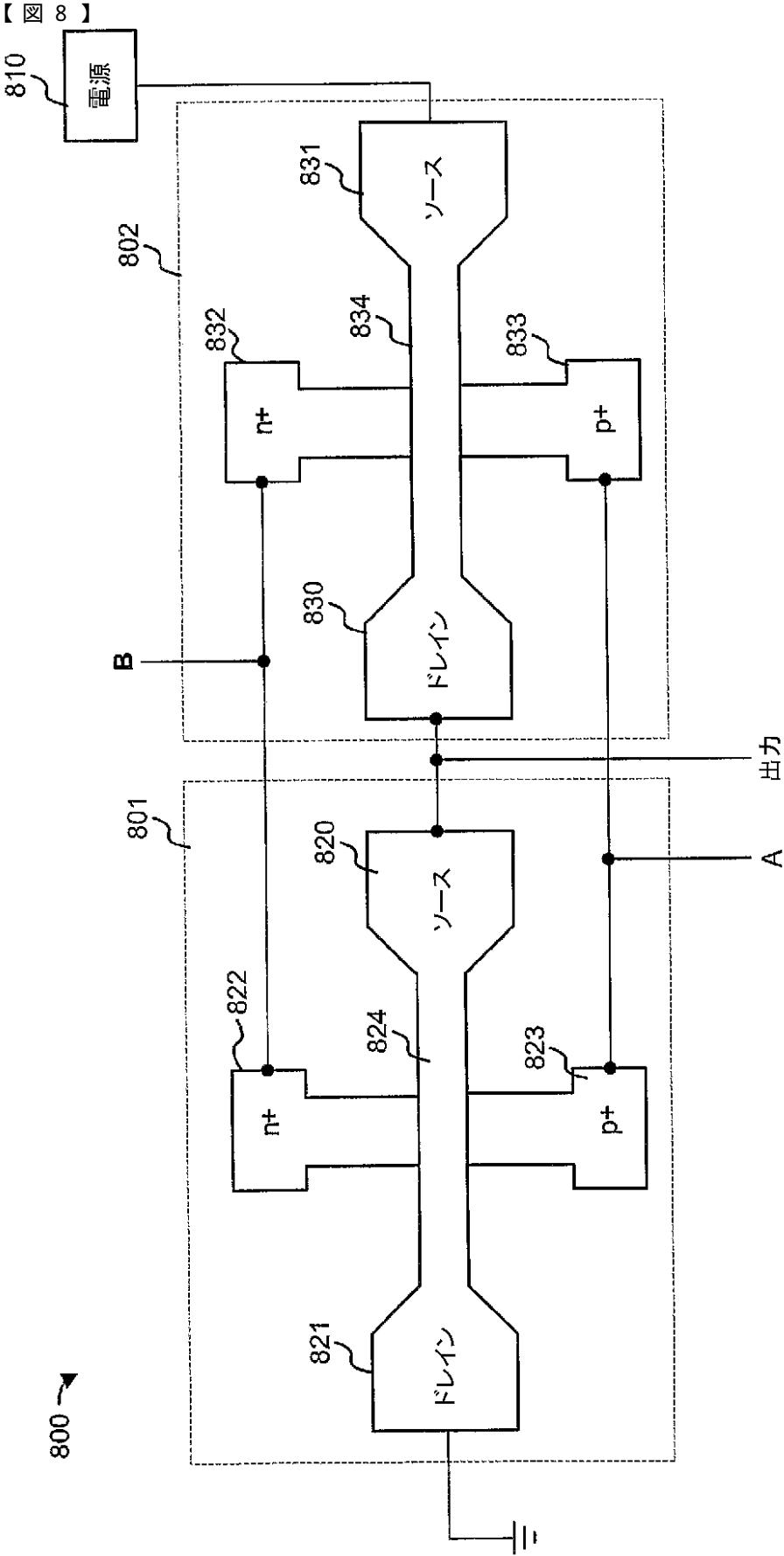

本発明の一態様によれば、NOR ゲートは、FinFET100 のような 2 つの非対称の FinFET を使用して構築される。

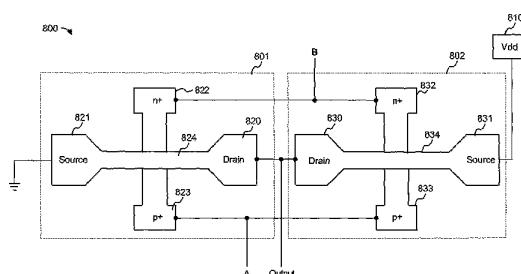

図 8 は、本発明による方法で構築した NOR ゲート 800 の上面図である。NOR ゲート 800 は集積半導体デバイス中に配置することができる。

#### 【0026】

NOR ゲート 800 は、FinFET801、802 と符号付けされる 2 つの FinFET を含む。各 FinFET801、802 は、FinFET100 と同様である。詳細には、FinFET801 はドレイン領域 820、ソース領域 821、第 1 ゲート 822、第 2 ゲート 823、およびチャネル (フィン) 領域 824 を含む。FinFET802 は同様に、ドレイン領域 830、ソース領域 831、第 1 ゲート 832、第 2 ゲート 833、およびチャネル領域 834 を含む。

第 1 ゲート 822 および 832 を n 型不純物でドープしてもよい。一方、第 2 ゲート 823、833 を p 型不純物でドープしてもよい。

#### 【0027】

図 8 に示すように、ゲート 822 およびゲート 832 を電気的に接続することができる。ゲート 823 およびゲート 833 を電気的に接続することができる。また、ソース 821 は、ドレイン 830 と電気的に接続することができる。ドレイン 820 をグランドに接続することができる。また、ソース 831 を電源 810 に接続することができる。

#### 【0028】

動作においては、NOR ゲート 800 への入力信号ライン (図 8 において、入力「A」、入力「B」とされる) は、電気的に接続された第 1 および第 2 の対となるゲートに加え

10

20

30

40

50

られる (apply)。

このように、入力信号線 A をゲート 823、833 に接続することができる。一方、入力信号線 B をゲート 822、832 に接続することができる。NOR ゲート 800 の出力信号は、ソース 821 とドレイン 830 の間で得られる。表 1 に示した論理にしたがって、出力値は入力 A、B による。

#### 【0029】

ある状況においては、単一接続された (single connected) ダブルゲートを有する、複数の従来の FinFET と、2 つの個別にアドレス可能なゲートを有する上述の非対称の FinFET の双方を含む集積回路を生成することが望ましい。

これらの状況では、図 2 ないし図 7 において上述したように、FinFET をすべて最初に生成してもよい。

その後、複数の FinFET のうち、従来の FinFET については付加的な選択的エピタキシャル成長ステップを適用してもよい。

#### 【0030】

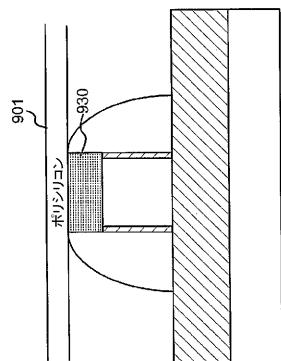

図 9 は、FinFET 900 の前記 2 つのゲート部分上のポリシリコンのたい積を示す図である。

ポリシリコン層 901 は、単一接続されたゲート構造を有するように設計される、集積回路中の複数の FinFET 上で選択的に形成することができる。

ポリシリコン層 901 は、例えば、選択エピタキシャル成長によって 100 nm の深さに形成されてもよい。

#### 【0031】

他の状況においては、FinFET についてのショットキー型ソース / ドレイン構造を形成することが望ましい。

これは、フィン上の窒化物層がエッチストップとして使用される、ダマシン・アプローチを使用して形成することができる。

図 9 に示すように、窒化物層 930 上にトレンチをエッチングすべく、ポリシリコン層 901 はエッチストップとして使用されてもよい。

このシリコンを除去した後、ソース / ドレイン領域上にトレンチが残る。

その後、金属をたい積するとともに、ストップ層として窒化物層 930 を使用して研磨することができる。この金属は、シリコン・チャネルを備えたショットキー・コンタクトを形成する。

#### 【0032】

NOR ゲートは、上述のように、従来の 4 つのトランジスタの代わりに 2 つの FinFET 型トランジスタで実装することができる。

したがって、ここに記述される NOR ゲートは、従来の半分の数のトランジスタを使用しており、これにより、ゲート密度および集積シリコンデバイスの全体的な機能性における著しく改良する。

#### 【0033】

前記記載においては、本発明について理解し易いように、特定の材料、構造、化学薬品、プロセス等のような多数の特定の詳細を記載している。

しかしながら、特にここに記載した詳細によることなく、本発明を実行することができる。その他、不必要に本発明の内容を不明瞭にしないように、周知のプロセス構造は詳細に記載していない。

#### 【0034】

本発明による、半導体デバイスを製造するのに使用される絶縁層および導電層は、従来のたい積技術によってたい積してもよい。例えば、低圧 CVD (LPCVD) およびエンハンスト CVD (ECD) を含んだ様々な種類の CVD プロセスのようなメタライゼーション技術を使用することができる。

#### 【0035】

本発明は、ダブルゲート半導体デバイスの製造、特に 100 nm 以下の構造的要素を有

10

20

30

40

50

する F i n F E T デバイスに適用可能である。

本発明は、様々な種類の半導体デバイスの形成に適用可能である。したがって、不必要に本発明の内容を不明瞭にしないようにその詳細は記載しない。本発明を実行する際に、従来のたい積技術、フォトリソグラフィ技術、およびエッチング技術を使用してもよい。なお、このような技術の詳細についてはここでは詳述していない。

【 0 0 3 6 】

本発明の好ましい実施形態およびその多様性のうちのいくつかの例のみが、本発明において開示されると共に記載される。本発明は、様々な他の組合せおよび環境において使用できると共に、ここに記載されるような本発明の概念の範囲内の変形または修正することができるものとして理解される。

10

【 図面の簡単な説明 】

【 0 0 3 7 】

【 図 1 】本発明の趣旨に沿った F i n F E T の上面を示す概略図。

【 図 2 】非対称の F i n F E T の形成方法を示す、図 1 中の A - A' 線に沿った概略図。

【 図 3 】非対称の F i n F E T の形成方法を示す、図 1 中の A - A' 線に沿った概略図。

【 図 4 】非対称の F i n F E T の形成方法を示す、図 1 中の A - A' 線に沿った概略図。

【 図 5 】非対称の F i n F E T の形成方法を示す、図 1 中の A - A' 線に沿った概略図。

【 図 6 】非対称の F i n F E T の形成方法を示す、図 1 中の A - A' 線に沿った概略図。

【 図 7 】非対称の F i n F E T の形成方法を示す、図 1 中の A - A' 線に沿った概略図。

【 図 8 】本発明の方法で形成された N O R ゲートの上面を示す概略図。

20

【 図 9 】 F i n F E T の 2 つのゲート部分上のポリシリコンのたい積を示す概略図。

【 図 1 】

【 図 2 】

Fig.2

20

【図3】

Fig. 3

【図4】

Fig. 4

【図5】

Fig. 5

【図6】

Fig. 6

Fig. 7A

Fig. 7B

【図 9】

**【手続補正書】**

【提出日】平成17年1月10日(2005.1.10)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】****【特許請求の範囲】****【請求項1】**

独立して制御可能な第1および第2ゲート領域(822)、(823)、ソース領域(821)、およびドレイン領域(820)を含む、第1FinFET(801)と、

独立して制御可能な第1および第2ゲート領域(832)、(833)、ソース領域(831)、およびドレイン領域(830)を含む、第2FinFET(802)と、

前記第1FinFET(801)の前記第1ゲート領域(822)と、前記第2FinFET(802)の前記第1ゲート領域(832)に接続されるNORゲートの第1入力線と、

前記第1FinFET(801)の前記第2ゲート領域(823)と、前記第2FinFET(802)の前記第2ゲート領域(833)に接続されるNORゲートの第2入力線と、

前記第1FinFET(801)の前記ソース(820)と、前記第2FinFET(802)の前記ドレイン(830)に接続されるNORゲートの出力線とを含む、NORゲート。

**【請求項2】**

前記第1FinFET(801)および前記第2FinFET(802)は、非対称のFinFETである、請求項1記載のNORゲート。

**【請求項3】**

前記第1FinFET(801)および第2FinFET(802)の前記第1ゲート領域は、n型不純物でドープされる、請求項1または2記載のNORゲート。

**【請求項4】**

前記第1FinFET(801)および第2FinFET(802)の前記第2ゲート領域は、p型不純物でドープされる、請求項3記載のNORゲート。

**【請求項5】**

前記NORゲートに含まれるトランジスタは、前記第1FinFET(801)および第2FinFET(802)のみである、請求項1記載のNORゲート。

**【請求項6】**

複数の非対称のFinFET(801)、(802)を含む集積半導体デバイスであって、

複数の非対称のFinFETのうちの少なくともいくつかは、論理NORゲートを定義する対となるFinFETを複数含むようにして配列される、

集積半導体デバイス。

**【請求項7】**

前記対となるFinFETは、

独立して制御可能な第1および第2ゲート領域(822)、(823)、ソース領域(821)、およびドレイン領域(820)を含む、第1非対称FinFET(801)と、

独立して制御可能な第1および第2ゲート領域(832)、(833)、ソース領域(831)、およびドレイン領域(830)を含む、第2非対称FinFET(802)と、

前記第1非対称FinFET(801)の前記第1ゲート領域(822)と、前記第2非対称FinFET(802)の前記第1ゲート領域(832)に接続される第1入力線

と、

前記第1非対称FinFET(801)の前記第2ゲート領域(823)と、前記第2非対称FinFET(802)の前記第2ゲート領域(833)に接続される第2入力線と、

前記第1非対称FinFET(801)の前記ソース(820)と、前記第2非対称FinFET(802)の前記ドレイン(830)に接続される出力線とを含む、請求項6記載の集積半導体デバイス。

【請求項8】

第1非対称ダブルゲートトランジスタ(801)と、

第2非対称ダブルゲートトランジスタ(802)とを含み、

前記第1トランジスタ(801)および第2トランジスタ(802)と接続される出力信号は、この第1トランジスタ(801)および第2トランジスタ(802)に与えられる2つの入力信号の論理NOR演算を反映する、

論理NOR回路。

【請求項9】

前記第1非対称ダブルゲートトランジスタ(801)および前記第2非対称ダブルゲートトランジスタ(802)はFinFETである、請求項8記載の論理NOR回路。

【請求項10】

前記第1非対称ダブルゲートトランジスタ(801)および前記第2非対称ダブルゲートトランジスタ(802)はそれぞれ、

第1ゲート領域(822)、(832)と、

この第1ゲート領域と無関係に制御可能に構成される第2ゲート領域(823)、(833)と、

ソース領域(821)、(831)と、

ドレイン領域(820)、(830)とを含む、請求項8または9記載の論理NOR回路。

【請求項11】

前記第1ダブルゲートトランジスタ(801)および前記第2ダブルゲートトランジスタ(802)は、FinFETである、請求項9記載の論理NOR回路。

【手続補正2】

【補正対象書類名】図面

【補正対象項目名】図8

【補正方法】変更

【補正の内容】

808

【 四 8 】

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 03/32782

A. CLASSIFICATION OF SUBJECT MATTER

IPC 7 H01L27/088 H01L27/092

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

IPC 7 H01L

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used);

EPO-Internal, WPI Data, PAJ, INSPEC

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                    | Relevant to claim No. |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X          | PATENT ABSTRACTS OF JAPAN<br>vol. 2000, no. 15,<br>6 April 2001 (2001-04-06)<br>-& JP 2000 340795 A (SONY CORP),<br>8 December 2000 (2000-12-08)<br>abstract; figures 1,2,11<br>paragraph '0055!                      | 1,4-9                 |

| X          | PATENT ABSTRACTS OF JAPAN<br>vol. 018, no. 684 (E-1650),<br>22 December 1994 (1994-12-22)<br>-& JP 06 275826 A (FUJITSU LTD),<br>30 September 1994 (1994-09-30)<br>abstract; figures 1,7<br>paragraphs '0007!, '0017! | 1,4-9                 |

| Y          | ---                                                                                                                                                                                                                   | 2,3,10<br>-/-         |

Further documents are listed in the continuation of box C.

Patent family members are listed in annex.

## \* Special categories of cited documents :

- \*A\* document defining the general state of the art which is not considered to be of particular relevance

- \*E\* earlier document but published on or after the international filing date

- \*L\* document which may throw doubts on priority, claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

- \*O\* document referring to an oral disclosure, use, exhibition or other means

- \*P\* document published prior to the International filing date but later than the priority date claimed

\*T\* later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

\*X\* document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

\*Y\* document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

\*&\* document member of the same patent family

|                                                                                                                                                                                        |                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Date of the actual completion of the international search                                                                                                                              | Date of mailing of the international search report |

| 29 January 2004                                                                                                                                                                        | 05/02/2004                                         |

| Name and mailing address of the ISA<br>European Patent Office, P.O. 5818 Patentlaan 2<br>NL - 2280 HV Rijswijk<br>Tel. (+31-70) 340-2040, Tx. 31 651 epo nl,<br>Fax. (+31-70) 340-3016 | Authorized officer<br>Wirner, C                    |

## INTERNATIONAL SEARCH REPORT

International Application No

PCT/US 03/32782

| C(Continuation) DOCUMENTS CONSIDERED TO BE RELEVANT |                                                                                                                                                                                                                                                                                        |                       |

|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Category *                                          | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                     | Relevant to claim No. |

| Y                                                   | TETSU TANAKA ET AL: "ULTRAFAST OPERATION OF VTH-ADJUSTED P+-N+ DOUBLE-GATE SOI MOSFET'S"<br>IEEE ELECTRON DEVICE LETTERS, IEEE INC.<br>NEW YORK, US,<br>vol. 15, no. 10,<br>1 October 1994 (1994-10-01), pages<br>386-388, XP000483212<br>ISSN: 0741-3106<br>abstract; figure 1<br>--- | 2,3,10                |

| A                                                   | US 2002/113270 A1 (NOWAK EDWARD JOSPEH ET AL) 22 August 2002 (2002-08-22)<br>abstract; figures 1,4<br>paragraph '0002!                                                                                                                                                                 | 1-10                  |

| A                                                   | US 6 396 108 B1 (BUYNOSKI MATTHEW ET AL)<br>28 May 2002 (2002-05-28)<br>abstract; claims; figures<br>column 5, line 10 - line 16<br>---                                                                                                                                                | 1-10                  |

| A                                                   | US 5 612 563 A (FITCH JON T ET AL)<br>18 March 1997 (1997-03-18)<br>abstract; claims; figures 14,26,27<br>column 9, line 4 - line 57<br>---                                                                                                                                            | 1-10                  |

| A                                                   | PATENT ABSTRACTS OF JAPAN<br>vol. 018, no. 461 (E-1597),<br>26 August 1994 (1994-08-26)<br>-& JP 06 151738 A (NIPPON STEEL CORP),<br>31 May 1994 (1994-05-31)<br>abstract; figures<br>---                                                                                              | 1-10                  |

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International Application No

PCT/US 03/32782

| Patent document cited in search report |    | Publication date | Patent family member(s) |             | Publication date |

|----------------------------------------|----|------------------|-------------------------|-------------|------------------|

| JP 2000340795                          | A  | 08-12-2000       | NONE                    |             |                  |

| JP 06275826                            | 5  | A                | NONE                    |             |                  |

| US 2002113270                          | A1 | 22-08-2002       | EP                      | 1362422 A2  | 19-11-2003       |

|                                        |    |                  | WO                      | 02067425 A2 | 29-08-2002       |

|                                        |    |                  | TW                      | 522640 B    | 01-03-2003       |

| US 6396108                             | B1 | 28-05-2002       | NONE                    |             |                  |

| US 5612563                             | A  | 18-03-1997       | US                      | 5308778 A   | 03-05-1994       |

|                                        |    |                  | US                      | 5286674 A   | 15-02-1994       |

|                                        |    |                  | JP                      | 6045452 A   | 18-02-1994       |

|                                        |    |                  | US                      | 5398200 A   | 14-03-1995       |

| JP 06151738                            | 5  | A                | NONE                    |             |                  |

## フロントページの続き

(81)指定国 AP(GH,GM,KE,LS,MW,MZ,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT, BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IT,LU,MC,NL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA, GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ, EC,EE,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,LU,LV,MA,MD,MG,MK,MN,M W,MX,MZ,NO,NZ,OM,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,TJ,TM,TN,TR,TT,TZ,UA,UG,UZ,VC,VN,YU,ZA,ZM,ZW

(74)代理人 100108604

弁理士 村松 義人

(72)発明者 ゾラン クリボカピク

アメリカ合衆国、カリフォルニア州 95050、サンタ クララ、デ ベローナ プレイス 2

321

(72)発明者 ジュディー ザイリン アン

アメリカ合衆国、カリフォルニア州 95129、サン ノゼ、レインツリー コート 905

(72)発明者 ミン - レン リン

アメリカ合衆国、カリフォルニア州 95014、キュパーティノ、サンタ テレサ ドライブ

10970

(72)発明者 ハイホン ワン

アメリカ合衆国、カリフォルニア州 94555、フレモント、ドナフエ テラス 34170

F ターム(参考) 5F048 AA01 AB03 AC01 BA16 BB01 BB02 BB06 BB07 BC01 BD01

BD06 BD07

5F110 AA04 BB03 BB20 DD01 DD05 DD11 EE09 EE14 EE22 EE30

EE42 EE45 EE48 FF02 FF22 GG02 GG22 GG42 HK50 QQ19