(19)日本国特許庁(JP)

## (12)公開特許公報(A)

(11)公開番号

特開2024-133071

(P2024-133071A)

(43)公開日 令和6年10月1日(2024.10.1)

## (51)国際特許分類

|         |                   |     |         |         |         |

|---------|-------------------|-----|---------|---------|---------|

| G 0 9 G | 3/20 (2006.01)    | F I | G 0 9 G | 3/20    | 6 2 2 E |

| H 0 3 K | 19/096 (2006.01)  |     | H 0 3 K | 19/096  | 2 3 0   |

| H 0 3 K | 19/0185 (2006.01) |     | H 0 3 K | 19/0185 |         |

| H 0 3 K | 19/0175 (2006.01) |     | H 0 3 K | 19/0175 | 2 2 0   |

| G 0 9 G | 3/3266 (2016.01)  |     | G 0 9 G | 3/20    | 6 2 1 M |

審査請求 有 請求項の数 4 O L (全34頁) 最終頁に続く

(21)出願番号 特願2024-101908(P2024-101908)

(22)出願日 令和6年6月25日(2024.6.25)

(62)分割の表示 特願2024-75235(P2024-75235)の分割

原出願日 平成25年7月16日(2013.7.16)

(31)優先権主張番号 特願2012-161253(P2012-161253)

(32)優先日 平成24年7月20日(2012.7.20)

(33)優先権主張国・地域又は機関

日本国(JP)

(71)出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72)発明者 三宅 博之

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

## (54)【発明の名称】 半導体装置及び表示装置

## (57)【要約】

【課題】動作不良の発生を抑制しつつ、トランジスタに対するストレスを抑制する。

【解決手段】パルス信号を出力する機能を有し、該パルス信号をハイレベルに設定するか否かを制御するトランジスタを有するパルス出力回路において、該パルス出力回路が高出するパルス信号がローレベルである期間に、該トランジスタのゲートの電位を、一定の値に保持するのではなく、間欠的に電位VSSよりも高くする。これにより、上記トランジスタに対するストレスの抑制を図る。

【選択図】図1

**【特許請求の範囲】****【請求項 1】**

ゲートドライバを有し、

前記ゲートドライバは、第1乃至第8のトランジスタを有し、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と常に導通し、

前記第1のトランジスタのソース又はドレインの他方は、出力信号線と常に導通し、

前記第2のトランジスタのソース又はドレインの一方は、電源線と常に導通し、

前記第2のトランジスタのソース又はドレインの他方は、前記出力信号線と常に導通し

、前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、10

前記第4のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの他方と常に導通し、

前記第4のトランジスタのゲートは、第1の信号線と常に導通し、

前記第5のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと常に導通し、10

前記第6のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第7のトランジスタのソース又はドレインの一方は、第2の配線と常に導通し、

前記第7のトランジスタのゲートは、前記第6のトランジスタのゲートと常に導通し、20

前記第8のトランジスタのソース又はドレインの一方は、前記電源線と常に導通し、

前記第8のトランジスタのソース又はドレインの他方は、前記第7のトランジスタのソース又はドレインの他方と常に導通し、

前記第4のトランジスタのソース又はドレインの他方が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第4のトランジスタのソース又はドレインの他方の電位が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、30

前記第5のトランジスタのソース又はドレインの他方には、前記第2の配線に応じた電位が入力され、

前記第6のトランジスタのソース又はドレインの他方が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第6のトランジスタのソース又はドレインの他方の電位が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、40

前記第6のトランジスタのゲートには、第2の信号線に応じた電位が入力され、

前記第7のトランジスタのゲートには、前記第2の信号線に応じた電位が入力され、

前記第8のトランジスタのゲートには、前記第1の信号線に応じた電位が入力される半導体装置。

**【請求項 2】**

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1乃至第8のトランジスタを有し、

前記画素は、第9及び第10のトランジスタと、発光素子と、を有し、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と常に導通し、

前記第1のトランジスタのソース又はドレインの他方は、出力信号線と常に導通し、

前記第2のトランジスタのソース又はドレインの一方は、電源線と常に導通し、

前記第2のトランジスタのソース又はドレインの他方は、前記出力信号線と常に導通し

、前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、50

前記第4のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの他方と常に導通し、

前記第4のトランジスタのゲートは、第1の信号線と常に導通し、

前記第5のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと常に導通し、

前記第6のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第7のトランジスタのソース又はドレインの一方は、第2の配線と常に導通し、

前記第7のトランジスタのゲートは、前記第6のトランジスタのゲートと常に導通し、

前記第8のトランジスタのソース又はドレインの一方は、前記電源線と常に導通し、

前記第8のトランジスタのソース又はドレインの他方は、前記第7のトランジスタのソース又はドレインの他方と常に導通し、

前記第4のトランジスタのソース又はドレインの他方が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第4のトランジスタのソース又はドレインの他方の電位が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第5のトランジスタのソース又はドレインの他方には、前記第2の配線に応じた電位が入力され、

前記第6のトランジスタのソース又はドレインの他方が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第6のトランジスタのソース又はドレインの他方の電位が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第6のトランジスタのゲートには、第2の信号線に応じた電位が入力され、

前記第7のトランジスタのゲートには、前記第2の信号線に応じた電位が入力され、

前記第8のトランジスタのゲートには、前記第1の信号線に応じた電位が入力され、

前記第9のトランジスタは、前記画素に入力されたデータ信号に従って、前記発光素子への電流の供給を制御する機能を有し、

前記第10のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのゲートと常に導通し、

前記第10のトランジスタのゲートは、前記出力信号線と常に導通している表示装置。

### 【請求項3】

ゲートドライバを有し、

前記ゲートドライバは、第1乃至第8のトランジスタと、容量素子と、を有し、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と常に導通し、

前記第1のトランジスタのソース又はドレインの他方は、出力信号線と常に導通し、

前記第2のトランジスタのソース又はドレインの一方は、電源線と常に導通し、

前記第2のトランジスタのソース又はドレインの他方は、前記出力信号線と常に導通し、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第4のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの他方と常に導通し、

前記第4のトランジスタのゲートは、第1の信号線と常に導通し、

前記第5のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと常に導通し、

前記第6のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第7のトランジスタのソース又はドレインの一方は、第2の配線と常に導通し、

10

20

30

40

50

前記第7のトランジスタのゲートは、前記第6のトランジスタのゲートと常に導通し、前記第8のトランジスタのソース又はドレインの一方は、前記電源線と常に導通し、前記第8のトランジスタのソース又はドレインの他方は、前記第7のトランジスタのソース又はドレインの他方と常に導通し、

前記容量素子の一方の電極は、前記第2のトランジスタのゲートと常に導通し、

前記容量素子の他方の電極は、前記電源線と常に導通し、

前記第4のトランジスタのソース又はドレインの他方が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第4のトランジスタのソース又はドレインの他方の電位が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第5のトランジスタのソース又はドレインの他方には、前記第2の配線に応じた電位が入力され、

前記第6のトランジスタのソース又はドレインの他方が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第6のトランジスタのソース又はドレインの他方の電位が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第6のトランジスタのゲートには、第2の信号線に応じた電位が入力され、

前記第7のトランジスタのゲートには、前記第2の信号線に応じた電位が入力され、

前記第8のトランジスタのゲートには、前記第1の信号線に応じた電位が入力される半導体装置。

#### 【請求項4】

ゲートドライバと、画素と、を有し、

前記ゲートドライバは、第1乃至第8のトランジスタと、容量素子と、を有し、

前記画素は、第9及び第10のトランジスタと、発光素子と、を有し、

前記第1のトランジスタのソース又はドレインの一方は、第1の配線と常に導通し、

前記第1のトランジスタのソース又はドレインの他方は、出力信号線と常に導通し、

前記第2のトランジスタのソース又はドレインの一方は、電源線と常に導通し、

前記第2のトランジスタのソース又はドレインの他方は、前記出力信号線と常に導通し

、

前記第3のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第4のトランジスタのソース又はドレインの一方は、前記第3のトランジスタのソース又はドレインの他方と常に導通し、

前記第4のトランジスタのゲートは、第1の信号線と常に導通し、

前記第5のトランジスタのソース又はドレインの一方は、前記第2のトランジスタのゲートと常に導通し、

前記第6のトランジスタのソース又はドレインの一方は、前記第1のトランジスタのゲートと常に導通し、

前記第7のトランジスタのソース又はドレインの一方は、第2の配線と常に導通し、

前記第7のトランジスタのゲートは、前記第6のトランジスタのゲートと常に導通し、

前記第8のトランジスタのソース又はドレインの一方は、前記電源線と常に導通し、

前記第8のトランジスタのソース又はドレインの他方は、前記第7のトランジスタのソース又はドレインの他方と常に導通し、

前記容量素子の一方の電極は、前記第2のトランジスタのゲートと常に導通し、

前記容量素子の他方の電極は、前記電源線と常に導通し、

前記第4のトランジスタのソース又はドレインの他方が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第4のトランジスタのソース又は

10

20

30

40

50

ドレインの他方の電位が少なくとも前記第4のトランジスタのチャネル形成領域及び前記第3のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第5のトランジスタのソース又はドレインの他方には、前記第2の配線に応じた電位が入力され、

前記第6のトランジスタのソース又はドレインの他方が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートと導通状態であるとき、前記第6のトランジスタのソース又はドレインの他方の電位が少なくとも前記第6のトランジスタのチャネル形成領域を介して前記第1のトランジスタのゲートに入力され、

前記第6のトランジスタのゲートには、第2の信号線に応じた電位が入力され、

10

前記第7のトランジスタのゲートには、前記第2の信号線に応じた電位が入力され、

前記第8のトランジスタのゲートには、前記第1の信号線に応じた電位が入力され、

前記第9のトランジスタは、前記画素に入力されたデータ信号に従って、前記発光素子への電流の供給を制御する機能を有し、

前記第10のトランジスタのソース又はドレインの一方は、前記第9のトランジスタのゲートと常に導通し、

前記第10のトランジスタのゲートは、前記出力信号線と常に導通している表示装置。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

20

本発明は、パルス出力回路に関する。さらに、本発明は、表示装置に関する。さらに、本発明は、電子機器に関する。

##### 【背景技術】

##### 【0002】

近年、作製プロセスの簡略化などを目的として、全てのトランジスタが同一の導電型である回路（単極性回路ともいう）の開発が進められている。

##### 【0003】

上記単極性回路の例としては、シフトレジスタを構成するパルス出力回路が挙げられる。

##### 【0004】

例えば、特許文献1では、クロック信号のパルスを、パルス信号のパルスの生成に用いたパルス出力回路を複数段有するシフトレジスタが開示されている。さらに、特許文献1では、ブートストラップを利用することにより、クロック信号の振幅に対し、出力するパルス信号の振幅の低下を抑制するシフトレジスタが開示されている。

30

##### 【先行技術文献】

##### 【特許文献】

##### 【0005】

##### 【特許文献1】特開2002-335153号公報

##### 【発明の概要】

##### 【発明が解決しようとする課題】

##### 【0006】

40

しかしながら、従来のパルス出力回路の構成では、クロック信号の振幅が大きいとトランジスタが劣化し、該トランジスタの電気特性が変動してしまうといった問題があった。

##### 【0007】

例えば、特許文献1のシフトレジスタでは、パルス出力回路から出力するパルス信号がローレベルのときに、出力するパルス信号をハイレベルに設定するか否かを制御するトランジスタ（例えば特許文献1の図1（B）のトランジスタ105）のゲートの電位が電位VSSに一定期間保持される。このとき、クロック信号に従って上記トランジスタのソース又はドレインの電位が繰り返し変化するため、該トランジスタにストレスが与えられる。これにより、上記トランジスタは劣化する。特に、特許文献1のシフトレジスタでは、上記ストレスが与えられる時間が非常に長いため、該上記トランジスタが劣化しやすく、電

50

気特性の変動が進行してしまう。

【0008】

トランジスタに与えられる上記ストレスの影響を抑制するためには、例えばトランジスタのチャネル長を長くするなどの対策が挙げられる。しかしながら、出力するパルス信号をハイレベルに設定するか否かを制御するトランジスタのチャネル長を長くすると、例えば寄生容量などにより、出力するパルス信号が遅延し、動作不良が起こる可能性が高くなるなどの別の問題が生じてしまう。

【0009】

上記問題に鑑み、本発明の一態様では、動作不良の発生を抑制しつつ、出力するパルス信号をハイレベルに設定するか否かを制御するトランジスタに対するストレスを抑制することを課題の一つとする。10

【課題を解決するための手段】

【0010】

本発明の一態様では、パルス出力回路が出力するパルス信号がローレベルである期間に、該パルス信号をハイレベルに設定するか否かを制御するトランジスタのゲートの電位を、一定の値にするのではなく、間欠的に電位VSSの電位よりも高くする。これにより、上記トランジスタに対するストレスの抑制を図る。

【0011】

本発明の一態様は、セット信号、リセット信号、第1のクロック信号、第2のクロック信号、及び第2のクロック信号の反転信号に従いパルス信号を生成する機能を有し、ソース及びドレインの一方の電位が第1のクロック信号に従って変化し、ソース及びドレインの他方の電位がパルス信号の電位となる第1のトランジスタと、ソース及びドレインの一方に第1の電位が与えられ、ソース及びドレインの他方が第1のトランジスタのソース及びドレインの他方に電気的に接続される第2のトランジスタと、ソース及びドレインの一方に第2の電位が与えられ、ソース及びドレインの他方が第1のトランジスタのゲートに電気的に接続され、ゲートの電位が第2のクロック信号に従って変化する第3のトランジスタと、ソース及びドレインの一方の電位がセット信号及びリセット信号に従って変化し、ソース及びドレインの他方が第1のトランジスタのゲートに電気的に接続され、ゲートの電位が第2のクロック信号の反転信号に従って変化する第4のトランジスタと、を有し、第1の電位と第2の電位の電位差は、第1のトランジスタのしきい値電圧よりも大きく、第2のクロック信号がハイレベルのとき、第1のクロック信号はローレベルであるパルス出力回路である。20

【発明の効果】

【0012】

本発明の一態様により、出力するパルス信号をハイレベルに設定するか否かを制御するトランジスタのチャネル長を長くせずとも、該トランジスタに対するストレスを低減できる。よって、上記トランジスタの劣化を抑制でき、電気特性の変動を抑制できる。

【図面の簡単な説明】

【0013】

【図1】パルス出力回路の例を説明するための図。

【図2】パルス出力回路の例を説明するための図。

【図3】パルス出力回路の例を説明するための図。

【図4】パルス出力回路の例を説明するための図。

【図5】パルス出力回路の例を説明するための図。

【図6】パルス出力回路の例を説明するための図。

【図7】表示装置の例を説明するための図。

【図8】表示装置の例を説明するための図。

【図9】表示装置の例を説明するための図。

【図10】表示装置の例を説明するための図。

【図11】電子機器の例を説明するための図。

10

20

30

40

50

**【発明を実施するための形態】**

**【0014】**

本発明に係る実施の形態の例について説明する。なお、本発明の趣旨及び範囲から逸脱することなく実施の形態の内容を変更することは、当業者であれば容易である。よって、例えば本発明は、下記実施の形態の記載内容に限定されない。

**【0015】**

なお、各実施の形態の内容を互いに適宜組み合わせることができる。また、各実施の形態の内容を互いに適宜置き換えることができる。

**【0016】**

また、第1、第2などの序数は、構成要素の混同を避けるために付しており、各構成要素の数は、序数に限定されない。 10

**【0017】**

本明細書において、「平行」とは、二つの直線が -10°以上10°以下の角度で配置されている状態をいう。従って、-5°以上5°以下の場合も含まれる。また、「垂直」とは、二つの直線が80°以上100°以下の角度で配置されている状態をいう。従って、85°以上95°以下の場合も含まれる。

**【0018】**

また、本明細書において、結晶が三方晶または菱面体晶である場合、六方晶系として表す。 20

**【0019】**

(実施の形態1)

本実施の形態では、パルス出力回路の例について説明する。

**【0020】**

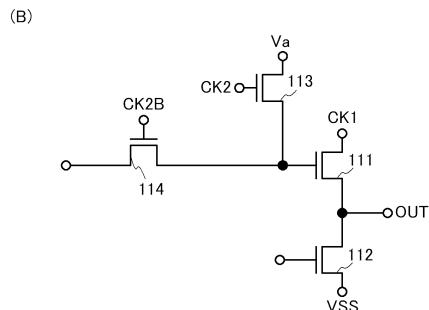

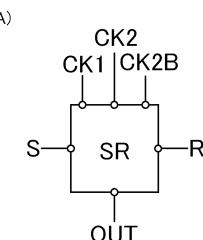

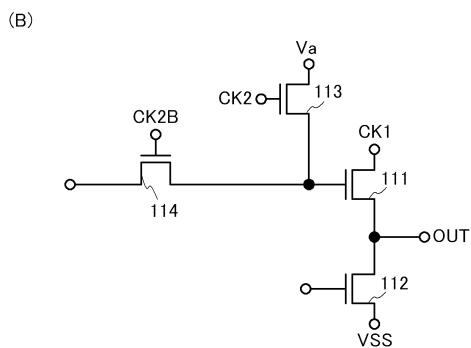

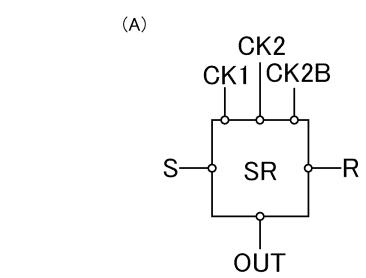

図1は、本実施の形態に係るパルス出力回路の例を説明するための図である。パルス出力回路SRは、図1(A)に示すように、入力されるセット信号S、リセット信号R、クロック信号CK1、クロック信号CK2、及びクロック信号CK2Bに従い、出力信号OUTとしてパルス信号を生成する機能を有する。クロック信号CK2Bとしては、クロック信号CK2の反転信号を用いることができるが、別のクロック信号をクロック信号CK2Bとして用いてもよい。

**【0021】**

さらに、図1(A)に示すパルス出力回路SRは、図1(B)に示すように、トランジスタT111乃至トランジスタT114を有する。トランジスタT111乃至トランジスタT114は、同一の導電型である。トランジスタT111乃至トランジスタT114のそれぞれは、セット信号S、リセット信号R、及びクロック信号CK1、クロック信号CK2、及びクロック信号CK2Bの一つ又は複数に従い導通が制御される。なお、図1(A)に示すパルス出力回路SRにトランジスタT111乃至トランジスタT114以外の素子を設けてもよい。 30

**【0022】**

トランジスタT111のソース及びドレインの一方の電位は、クロック信号CK1に従い変化し、他方の電位がパルス信号(出力信号OUT)の電位となる。トランジスタT111は、パルス信号(出力信号OUT)をハイレベルに設定するか否かを制御する機能を有する。 40

**【0023】**

なお、「信号に従い電位が変化する」とは、「信号が直接入力されることで電位が該信号の電位に変化する場合」のみに限定されない。例えば、「信号に従いスイッチがオン状態になることにより、電位が変化する場合」や、「容量結合により、信号の変化に合わせて電位が変化する場合」なども「信号に従い電位が変化する」に含まれる。

**【0024】**

また、「信号に応じた電位」とは、「信号の電位と同じ値の電位」のみに限定されない。例えば、電圧降下により信号の電位が変化した値も「信号に応じた電位」に含まれる。 50

## 【0025】

トランジスタ112のソース及びドレインの一方には、電位VSSが与えられ、他方は、トランジスタ111のソース及びドレインの他方に電気的に接続される。さらに、トランジスタ112のゲートの電位は、セット信号S及びリセット信号Rに従い変化する。なお、クロック信号CK1及びクロック信号CK2とは異なるクロック信号を用いてトランジスタ112のゲートの電位を制御してもよい。トランジスタ112は、ゲートの電位に応じてオン状態又はオフ状態になることにより、パルス信号(出力信号OUT)をローレベルに設定するか否かを制御する機能を有する。

## 【0026】

トランジスタ113のソース及びドレインの一方には、電位Vaが与えられ、他方は、トランジスタ111のゲートに電気的に接続される。さらに、トランジスタ113のゲートの電位は、クロック信号CK2に従い変化する。トランジスタ113は、トランジスタ111のゲートの電位V<sub>a</sub>に応じた値に設定するか否かを制御する機能を有する。10

## 【0027】

なお、「電位に応じた値」とは、「該電位と同じ値」のみに限定されない。例えば、電圧降下により上記電位の値から変化した場合も「電位に応じた値」に含まれる。

## 【0028】

トランジスタ114のソース及びドレインの一方の電位は、セット信号S及びリセット信号Rに従い変化し、他方は、トランジスタ111のゲートに電気的に接続される。さらに、トランジスタ114のゲートの電位は、クロック信号CK2Bに従い変化する。トランジスタ114は、トランジスタ111のゲートを浮遊状態にするか否かを制御する機能を有する。20

## 【0029】

トランジスタ111乃至トランジスタ114としては、チャネル形成領域に例えればシリコンよりもバンドギャップが広い半導体を含むトランジスタを適用できる。バンドギャップの広い半導体としては、例えば酸化物半導体を適用できる。ただし、これに限定されず、例えば14族(シリコンなどの)の元素を有する半導体を含むトランジスタをトランジスタ111乃至トランジスタ114に用いてもよい。このとき、14族の元素を有する半導体が単結晶、多結晶、又は非晶質でもよい。

## 【0030】

上記酸化物半導体としては、例えばIn系金属酸化物、Zn系金属酸化物、In-Zn系金属酸化物、又はIn-Ga-Zn系金属酸化物などを適用できる。また、上記In-Ga-Zn系金属酸化物に含まれるGaの一部若しくは全部の代わりに他の金属元素を含む金属酸化物を用いてもよい。30

## 【0031】

以下、酸化物半導体膜の構造について説明する。

## 【0032】

酸化物半導体膜は、単結晶酸化物半導体膜と非単結晶酸化物半導体膜とに大別される。非単結晶酸化物半導体膜とは、非晶質酸化物半導体膜、微結晶酸化物半導体膜、多結晶酸化物半導体膜、CAAC-OS(C Axis Aligned Crystalline Oxide Semiconductor)膜などをいう。40

## 【0033】

非晶質酸化物半導体膜は、膜中における原子配列が不規則であり、結晶成分を有さない酸化物半導体膜である。微小領域においても結晶部を有さず、膜全体が完全な非晶質構造の酸化物半導体膜が典型である。

## 【0034】

微結晶酸化物半導体膜は、例えば、1nm以上10nm未満の大きさの微結晶(ナノ結晶ともいう。)を含む。従って、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも原子配列の規則性が高い。そのため、微結晶酸化物半導体膜は、非晶質酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。50

**【 0 0 3 5 】**

C AAC - OS 膜は、複数の結晶部を有する酸化物半導体膜の一つであり、ほとんどの結晶部は、一辺が 100 nm 未満の立方体内に収まる大きさである。従って、C AAC - OS 膜に含まれる結晶部は、一辺が 10 nm 未満、5 nm 未満または 3 nm 未満の立方体内に収まる大きさの場合も含まれる。C AAC - OS 膜は、微結晶酸化物半導体膜よりも欠陥準位密度が低いという特徴がある。以下、C AAC - OS 膜について詳細な説明を行う。

**【 0 0 3 6 】**

C AAC - OS 膜を透過型電子顕微鏡 (TEM : Transmission Electron Microscope) によって観察すると、結晶部同士の明確な境界、即ち結晶粒界 (グレインバウンダリーともいう。) を確認することができない。そのため、C AAC - OS 膜は、結晶粒界に起因する電子移動度の低下が起こりにくいといえる。

**【 0 0 3 7 】**

C AAC - OS 膜を、試料面と概略平行な方向から TEM によって観察 (断面 TEM 観察) すると、結晶部において、金属原子が層状に配列していることを確認できる。金属原子の各層は、C AAC - OS 膜の膜を形成する面 (被形成面ともいう。) または上面の凹凸を反映した形状であり、C AAC - OS 膜の被形成面または上面と平行に配列する。

**【 0 0 3 8 】**

一方、C AAC - OS 膜を、試料面と概略垂直な方向から TEM によって観察 (平面 TEM 観察) すると、結晶部において、金属原子が三角形状または六角形状に配列していることを確認できる。しかしながら、異なる結晶部間で、金属原子の配列に規則性は見られない。

**【 0 0 3 9 】**

断面 TEM 観察および平面 TEM 観察より、C AAC - OS 膜の結晶部は配向性を有していることがわかる。

**【 0 0 4 0 】**

C AAC - OS 膜に対し、X 線回折 (XRD : X-Ray Diffraction) 装置を用いて構造解析を行うと、例えば InGaZnO<sub>4</sub> の結晶を有する C AAC - OS 膜の out-of-plane 法による解析では、回折角 (2θ) が 31° 近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (009) 面に帰属されることから、C AAC - OS 膜の結晶が c 軸配向性を有し、c 軸が被形成面または上面に概略垂直な方向を向いていることが確認できる。

**【 0 0 4 1 】**

一方、C AAC - OS 膜に対し、c 軸に概略垂直な方向から X 線を入射させる in-plane 法による解析では、2θ が 56° 近傍にピークが現れる場合がある。このピークは、InGaZnO<sub>4</sub> の結晶の (110) 面に帰属される。InGaZnO<sub>4</sub> の単結晶酸化物半導体膜であれば、2θ を 56° 近傍に固定し、試料面の法線ベクトルを軸 (c 軸) として試料を回転させながら分析 (スキャン) を行うと、(110) 面と等価な結晶面に帰属されるピークが 6 本観察される。これに対し、C AAC - OS 膜の場合は、2θ を 56° 近傍に固定して スキャンした場合でも、明瞭なピークが現れない。

**【 0 0 4 2 】**

以上のことから、C AAC - OS 膜では、異なる結晶部間では a 軸および b 軸の配向は不規則であるが、c 軸配向性を有し、かつ c 軸が被形成面または上面の法線ベクトルに平行な方向を向いていることがわかる。従って、前述の断面 TEM 観察で確認された層状に配列した金属原子の各層は、結晶の ab 面に平行な面である。

**【 0 0 4 3 】**

なお、結晶部は、C AAC - OS 膜を成膜した際、または加熱処理などの結晶化処理を行った際に形成される。上述したように、結晶の c 軸は、C AAC - OS 膜の被形成面または上面の法線ベクトルに平行な方向に配向する。従って、例えば、C AAC - OS 膜の形状をエッティングなどによって変化させた場合、結晶の c 軸が C AAC - OS 膜の被形成面

10

20

30

40

50

または上面の法線ベクトルと平行にならないこともある。

#### 【 0 0 4 4 】

また、C AAC - OS 膜中の結晶化度が均一でなくてもよい。例えば、C AAC - OS 膜の結晶部が、C AAC - OS 膜の上面近傍からの結晶成長によって形成される場合、上面近傍の領域は、被形成面近傍の領域よりも結晶化度が高くなることがある。また、C AAC - OS 膜に不純物を添加する場合、不純物が添加された領域の結晶化度が変化し、部分的に結晶化度の異なる領域が形成されることもある。

#### 【 0 0 4 5 】

なお、InGaZnO<sub>4</sub>の結晶を有するC AAC - OS 膜のout-of-plane 法による解析では、2θが31°近傍のピークの他に、2θが36°近傍にもピークが現れる場合がある。2θが36°近傍のピークは、C AAC - OS 膜中の一部に、c軸配向性を有さない結晶が含まれることを示している。C AAC - OS 膜は、2θが31°近傍にピークを示し、2θが36°近傍にピークを示さないことが好ましい。

10

#### 【 0 0 4 6 】

C AAC - OS 膜を用いたトランジスタは、可視光や紫外光の照射による電気特性の変動が小さい。よって、当該トランジスタは、信頼性が高い。

#### 【 0 0 4 7 】

なお、酸化物半導体膜は、例えば、非晶質酸化物半導体膜、微結晶酸化物半導体膜、CAC - OS 膜のうち、二種以上を有する積層膜であってもよい。

20

#### 【 0 0 4 8 】

以上が、酸化物半導体膜の構造に関する説明である。

#### 【 0 0 4 9 】

さらに、本実施の形態に係るパルス出力回路の構成例について図2を参照して説明する。

#### 【 0 0 5 0 】

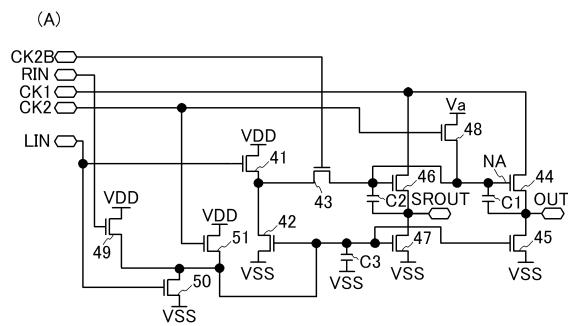

図2(A)に示すパルス出力回路は、セット信号Sに相当するセット信号LIN、リセット信号Rに相当するリセット信号RIN、クロック信号CK1、クロック信号CK2、及びクロック信号CK2Bに従い出力信号OUT及び出力信号SROUTを生成する機能を有する。

#### 【 0 0 5 1 】

図2(A)に示すパルス出力回路は、トランジスタ41乃至トランジスタ51を有する。

30

#### 【 0 0 5 2 】

トランジスタ41のソース及びドレインの一方には、電位VDDが与えられる。さらに、トランジスタ41のゲートには、セット信号LINが入力される。

#### 【 0 0 5 3 】

トランジスタ42のソース及びドレインの一方には、電位VSSが与えられ、他方は、トランジスタ41のソース及びドレインの他方に電気的に接続される。

#### 【 0 0 5 4 】

トランジスタ43のソース及びドレインの一方は、トランジスタ41のソース及びドレンの他方に電気的に接続される。さらに、トランジスタ43のゲートには、クロック信号CK2Bが入力される。トランジスタ43は、図1(B)に示すトランジスタ114に相当する。

40

#### 【 0 0 5 5 】

トランジスタ44のソース及びドレインの一方には、クロック信号CK1が入力され、他方の電位がパルス信号(出力信号OUT)の電位となる。さらに、トランジスタ44のゲートは、トランジスタ43のソース及びドレインの他方に電気的に接続される。トランジスタ44は、図1(B)に示すトランジスタ111に相当する。

#### 【 0 0 5 6 】

さらに、トランジスタ44のゲートとソース及びドレインの他方との間には、容量C1が形成される。例えば、トランジスタ44のゲートとソース及びドレインの他方との間の寄生容量を容量C1に用いてよい。

50

**【 0 0 5 7 】**

トランジスタ45のソース及びドレインの一方には、電位VSSが与えられ、他方は、トランジスタ44のソース及びドレインの他方に電気的に接続される。トランジスタ45は、図1(B)に示すトランジスタ112に相当する。

**【 0 0 5 8 】**

トランジスタ46のソース及びドレインの一方には、クロック信号CK1が入力され、他方の電位がパルス信号(出力信号SROUT)の電位となる。さらに、トランジスタ46のゲートは、トランジスタ43のソース及びドレインの他方に電気的に接続される。

**【 0 0 5 9 】**

さらに、トランジスタ46のゲートとソース及びドレインの他方との間には、容量C2が形成される。例えば、トランジスタ46のゲートとソース及びドレインの他方との間の寄生容量を容量C2に用いてもよい。なお、必ずしも容量C2を形成しなくてもよい。

**【 0 0 6 0 】**

トランジスタ47のソース及びドレインの一方には、電位VSSが与えられ、他方は、トランジスタ46のソース及びドレインの他方に電気的に接続される。さらに、トランジスタ47のゲートは、トランジスタ42のゲートに電気的に接続される。

**【 0 0 6 1 】**

なお、必ずしもトランジスタ46及び47を設けなくてもよい。

**【 0 0 6 2 】**

トランジスタ48のソース及びドレインの一方には、電位Vaが与えられ、他方は、トランジスタ44のゲート及びトランジスタ46のゲートに電気的に接続される。さらに、トランジスタ48のゲートには、クロック信号CK2が入力される。トランジスタ48は、図1(B)に示すトランジスタ113に相当する。

**【 0 0 6 3 】**

トランジスタ49のソース及びドレインの一方には、電位VDDが与えられ、他方は、トランジスタ45のゲート及びトランジスタ47のゲートに電気的に接続される。さらに、トランジスタ49のゲートには、リセット信号RINが入力される。

**【 0 0 6 4 】**

トランジスタ50のソース及びドレインの一方には、電位VSSが与えられ、他方は、トランジスタ45のゲート及びトランジスタ47のゲートに電気的に接続される。さらに、トランジスタ50のゲートには、セット信号LINが入力される。

**【 0 0 6 5 】**

トランジスタ51のソース及びドレインの一方には、電位VDDが与えられ、他方は、トランジスタ45のゲート及びトランジスタ47のゲートに電気的に接続される。さらに、トランジスタ51のゲートには、クロック信号CK2が入力される。なお、トランジスタ48及びトランジスタ51の一方又は両方のチャネル長をトランジスタ44又はトランジスタ46のチャネル長よりも長くしてもよい。トランジスタ51のチャネル長を長くすることにより、トランジスタ51に対するストレスの影響を低減できる。

**【 0 0 6 6 】**

容量C3の一対の電極の一方には、電位VSSが与えられ、他方は、トランジスタ45のゲート、トランジスタ47のゲートに電気的に接続される。容量C3は、保持容量としての機能を有する。なお、必ずしも容量C3を設けなくてもよい。

**【 0 0 6 7 】**

トランジスタ41乃至トランジスタ51としては、例えばチャネル形成領域に上記酸化物半導体を含むトランジスタを適用できる。

**【 0 0 6 8 】**

次に、本実施の形態に係るパルス出力回路の駆動方法例として、図2(A)に示すパルス出力回路の駆動方法例について、図2(B)のタイミングチャートを参照して説明する。ここでは、一例として、トランジスタ41乃至トランジスタ51のそれぞれがNチャネル型であり、電位VDDが正の電位であり、電位VSSが負の電位であり、電位Vaの値が

10

20

30

40

50

電位 V D D の値と同じであるとして説明する。また、セット信号 L I N、リセット信号 R I N、及びクロック信号 C K 1、クロック信号 C K 2、及びクロック信号 C K 2 B のハイレベルの電位は、電位 V D D 同じであり、ローレベルの電位は、電位 V S S 同じであるとする。また、電位 V a とクロック信号 C K 1 のローレベルの電位との電位差は、トランジスタ 4 4 及びトランジスタ 4 6 のしきい値電圧よりも大きいとする。また、トランジスタ 4 4 のゲートと他の素子との接続箇所をノード N A とする。

#### 【 0 0 6 9 】

なお本明細書において、電位 V S S とは、回路を動作させるために必要な、少なくとも 2 つの電源電位のうち、低い方の電位である。前記 2 つの電源電位のうち、高い方の電位は電位 V D D である。

10

#### 【 0 0 7 0 】

図 2 ( A ) に示すパルス出力回路では、図 2 ( B ) の期間 T 1 において、セット信号 L I N がハイレベルになり、トランジスタ 4 1 及びトランジスタ 5 0 がオン状態になる。また、リセット信号 R I N がローレベルであるため、トランジスタ 4 9 はオフ状態である。また、クロック信号 C K 1 はローレベルである。また、クロック信号 C K 2 がローレベルであるため、トランジスタ 4 8 及びトランジスタ 5 1 はオフ状態である。また、クロック信号 C K 2 B がハイレベルになり、トランジスタ 4 3 がオン状態になる。

#### 【 0 0 7 1 】

このとき、ノード N A の電位が電位 V D D と同等の値まで上昇し、トランジスタ 4 4、トランジスタ 4 6 がオン状態になり、トランジスタ 4 1 及びトランジスタ 4 3 がオフ状態になる。さらに、クロック信号 C K 1 がローレベルであるため、出力信号 O U T、出力信号 S R O U T は、ローレベルになる。以上により、図 2 ( A ) に示すパルス出力回路は、セット状態になる。

20

#### 【 0 0 7 2 】

次に、期間 T 2 において、セット信号 L I N がローレベルになり、トランジスタ 4 1 及びトランジスタ 5 0 がオフ状態になる。また、クロック信号 C K 1 がハイレベルになる。また、リセット信号 R I N がローレベルのままであるため、トランジスタ 4 9 はオフ状態のままである。また、クロック信号 C K 2 がローレベルのままであるため、トランジスタ 4 8 及びトランジスタ 5 1 はオフ状態のままである。また、クロック信号 C K 2 B はハイレベルのままである。

30

#### 【 0 0 7 3 】

このとき、トランジスタ 4 4 はオン状態のままであり、クロック信号 C K 1 がハイレベルであるため、トランジスタ 4 4 のゲートとソース及びドレインの他方との間に生じる容量 C 1 によって生じる容量結合により、ノード N A の電位が電位 V D D とトランジスタ 4 4 のしきい値電圧 ( V t h 4 4 ) の和よりもさらに高い値、すなわち、 $V D D + V t h 4 4 + V x$  ( $V x$  は任意の電位) まで上昇する。いわゆるブーストストラップである。これにより、出力信号 O U T の電位は、クロック信号 C K 1 のハイレベルの電位と同等の値になる。同様に、出力信号 S R O U T の電位もクロック信号 C K 1 のハイレベルの電位と同等の値になる。

40

#### 【 0 0 7 4 】

次に、期間 T 3 において、リセット信号 R I N がハイレベルになり、トランジスタ 4 9 がオン状態になる。また、クロック信号 C K 1 がローレベルになる。また、クロック信号 C K 2 B がローレベルになり、トランジスタ 4 3 がオフ状態になる。また、クロック信号 C K 2 がハイレベルになり、トランジスタ 4 8 及びトランジスタ 5 1 がオン状態になる。また、セット信号 L I N がローレベルのままであるため、トランジスタ 4 1 及びトランジスタ 5 0 はオフ状態のままである。

#### 【 0 0 7 5 】

このとき、トランジスタ 4 2、トランジスタ 4 5、トランジスタ 4 7 がオン状態になる。また、トランジスタ 4 8 がオン状態であるため、ノード N A の電位は、電位 V a と同等の値になり、トランジスタ 4 4、トランジスタ 4 6 はオン状態のままである。クロック信号

50

C K 1 はローレベルであるため、出力信号 O U T 、出力信号 S R O U T の電位は、クロック信号 C K 1 のローレベルの電位と同等の値になる。これにより、図 2 ( A ) に示すパルス出力回路は、リセット状態になる。

#### 【 0 0 7 6 】

次に、期間 T 4 において、リセット信号 R I N がローレベルになり、トランジスタ 4 9 がオフ状態になる。また、クロック信号 C K 2 がローレベルになり、トランジスタ 4 8 及びトランジスタ 5 1 がオフ状態になる。また、クロック信号 C K 2 B がハイレベルになり、トランジスタ 4 3 がオン状態になる。また、セット信号 L I N がローレベルのままであるため、トランジスタ 4 1 及びトランジスタ 5 0 はオフ状態のままである。また、クロック信号 C K 1 はローレベルのままである。

10

#### 【 0 0 7 7 】

このとき、トランジスタ 4 2 、トランジスタ 4 5 、及びトランジスタ 4 7 はオフ状態のままである。さらに、トランジスタ 4 3 がオン状態であり、ノード N A の電位が電位 V S S と同等の値のままであるため、トランジスタ 4 4 、トランジスタ 4 6 はオフ状態のままである。さらに、クロック信号 C K 1 がローレベルのままであるため、出力信号 O U T 、出力信号 S R O U T は、ローレベルのままである。

#### 【 0 0 7 8 】

次に、期間 T 5 において、セット信号 L I N がローレベルのままであるため、トランジスタ 4 1 及びトランジスタ 5 0 はオフ状態のままである。また、リセット信号 R I N がローレベルのままであるため、トランジスタ 4 9 はオフ状態のままである。また、クロック信号 C K 1 はローレベルのままである。また、クロック信号 C K 2 がローレベルのままであるため、トランジスタ 4 8 及びトランジスタ 5 1 はオフ状態のままである。また、クロック信号 C K 2 B がハイレベルのままであるため、トランジスタ 4 3 はオン状態のままである。

20

#### 【 0 0 7 9 】

このとき、トランジスタ 4 2 、トランジスタ 4 5 、及びトランジスタ 4 7 はオフ状態のままである。さらに、トランジスタ 4 3 がオン状態であり、ノード N A の電位が電位 V S S と同等の値のままであるため、トランジスタ 4 4 、トランジスタ 4 6 はオフ状態のままである。さらに、クロック信号 C K 1 がローレベルのままであるため、出力信号 O U T 、出力信号 S R O U T は、ローレベルのままである。

30

#### 【 0 0 8 0 】

次に、期間 T 6 において、クロック信号 C K 1 がハイレベルになる。また、セット信号 L I N がローレベルのままであるため、トランジスタ 4 1 及びトランジスタ 5 0 はオフ状態のままである。また、リセット信号 R I N がローレベルのままであるため、トランジスタ 4 9 はオフ状態のままである。また、クロック信号 C K 2 がローレベルのままであるため、トランジスタ 4 8 及びトランジスタ 5 1 はオフ状態のままである。また、クロック信号 C K 2 B がハイレベルのままであるため、トランジスタ 4 3 はオン状態のままである。

#### 【 0 0 8 1 】

このとき、トランジスタ 4 2 、トランジスタ 4 5 、及びトランジスタ 4 7 はオン状態のままである。さらに、トランジスタ 4 3 がオン状態であり、ノード N A の電位が電位 V S S と同等の値のままであるため、トランジスタ 4 4 、トランジスタ 4 6 はオフ状態のままである。このとき、クロック信号 C K 1 がハイレベルになるが、トランジスタ 4 4 、トランジスタ 4 6 がオフ状態であるため、出力信号 O U T 、出力信号 S R O U T はローレベルのままである。

40

#### 【 0 0 8 2 】

次に、期間 T 7 において、クロック信号 C K 2 がハイレベルになり、トランジスタ 4 8 及びトランジスタ 5 1 がオン状態になる。また、クロック信号 C K 2 B がローレベルになり、トランジスタ 4 3 がオフ状態になる。また、クロック信号 C K 1 がローレベルになる。また、セット信号 L I N がローレベルのままであるため、トランジスタ 4 1 及びトランジスタ 5 0 はオフ状態のままである。また、リセット信号 R I N がローレベルのままである

50

ため、トランジスタ 4 9 はオフ状態のままである。このように、クロック信号 C K 2 がハイレベルのとき、クロック信号 C K 1 はローレベルである。

#### 【 0 0 8 3 】

このとき、トランジスタ 4 2、トランジスタ 4 5、及びトランジスタ 4 7 はオン状態のままである。また、トランジスタ 4 8 がオン状態であるため、ノード N A の電位が電位 V a と同等の値になり、トランジスタ 4 4、トランジスタ 4 6 がオン状態になるが、クロック信号 C K 1 がローレベルであるため、出力信号 O U T、出力信号 S R O U T は、ローレベルのままである。

#### 【 0 0 8 4 】

上記のように、クロック信号 C K 2 に従い、間欠的にノード N A の電位を電位 V a と同等の値に変化させる。ノード N A の電位が電位 V a と同等の値であるとき、トランジスタ 4 4 のソース及びドレインの一方の電位、並びにトランジスタ 4 6 のソース及びドレインの一方の電位は、クロック信号 C K 1 のローレベルの電位と同等の値になる。また、ノード N A の電位が電位 V S S と同等の値であるとき、トランジスタ 4 4 のソース及びドレインの一方の電位、並びにトランジスタ 4 6 のソース及びドレインの一方の電位は、クロック信号 C K 1 のハイレベルの電位と同等の値になる。よって、トランジスタ 4 4 及びトランジスタ 4 6 のそれぞれにおいて、ゲートとソース及びドレインの一方との間の電圧が常に電位 V D D と電位 V S S の差よりも低くなるため、トランジスタ 4 4 に対するストレスを低減できる。

#### 【 0 0 8 5 】

以上が図 2 ( A ) に示すパルス出力回路の説明である。

10

#### 【 0 0 8 6 】

なお、本実施の形態に係るパルス出力回路の構成は、上記構成に限定されず、他の構成にすることもできる。

#### 【 0 0 8 7 】

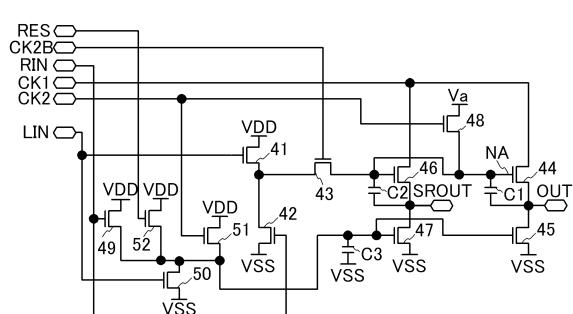

例えば、図 3 に示すパルス出力回路は、図 2 ( B ) に示すパルス出力回路のトランジスタ 4 2 のゲートをトランジスタ 4 5、トランジスタ 4 7 のゲートに電気的に接続する代わりに、トランジスタ 4 2 のゲートにリセット信号 R I N を入力する構成である。これにより、パルス出力回路をリセット状態にする際に、ノード N A の電位を電位 V S S と同等の値に設定する速度を速くできる。また、図 3 に示すように、トランジスタ 5 2 を設けてよい。このとき、トランジスタ 5 2 のソース及びドレインの一方には、電位 V D D が与えられ、他方は、トランジスタ 4 5、トランジスタ 4 7 に電気的に接続される。さらに、トランジスタ 5 2 のゲートには、初期化信号 R E S が入力される。図 3 に示すパルス出力回路では、初期化信号 R E S のパルスが入力されることにより、トランジスタ 4 5 及びトランジスタ 4 7 がオン状態になり、信号 O U T 及び信号 S R O U T がローレベルになり、初期化状態になる。

30

#### 【 0 0 8 8 】

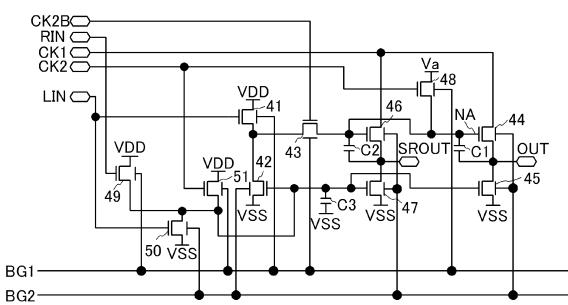

また、図 4 に示すように、トランジスタ 4 1 乃至トランジスタ 5 1 のそれぞれにバックゲートを設け、バックゲートの電位を制御することによりトランジスタ 4 1 乃至トランジスタ 5 1 のしきい値電圧を制御してもよい。例えば、N チャネル型トランジスタのバックゲートに負電位を与えると、N チャネル型トランジスタのしきい値電圧を正方向にシフトさせることができる。図 4 に示すパルス出力回路において、トランジスタ 4 1、トランジスタ 4 3、トランジスタ 4 8、トランジスタ 4 9、及びトランジスタ 5 1 のバックゲートのそれぞれには、電位 B G 1 が与えられ、トランジスタ 4 2、トランジスタ 4 4、トランジスタ 4 5、トランジスタ 4 6、トランジスタ 4 7、及びトランジスタ 5 0 のバックゲートのそれぞれには、電位 B G 2 が与えられる。なお、電位 B G 1 及び電位 B G 2 として負電位を用いる場合、電位 B G 2 の値は、電位 B G 1 よりも低いことが好ましい。電位 B G 1 が供給されるトランジスタのしきい値電圧が高すぎると、パルス出力回路の動作不良が起こりやすいためである。

40

#### 【 0 0 8 9 】

50

なお、図3に示す構成においても同様に、トランジスタにバックゲートを設けてもよい。

#### 【0090】

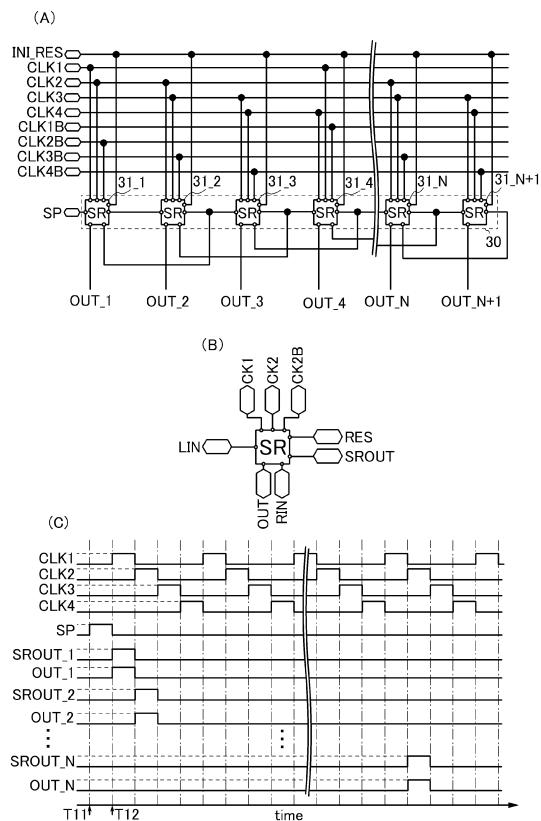

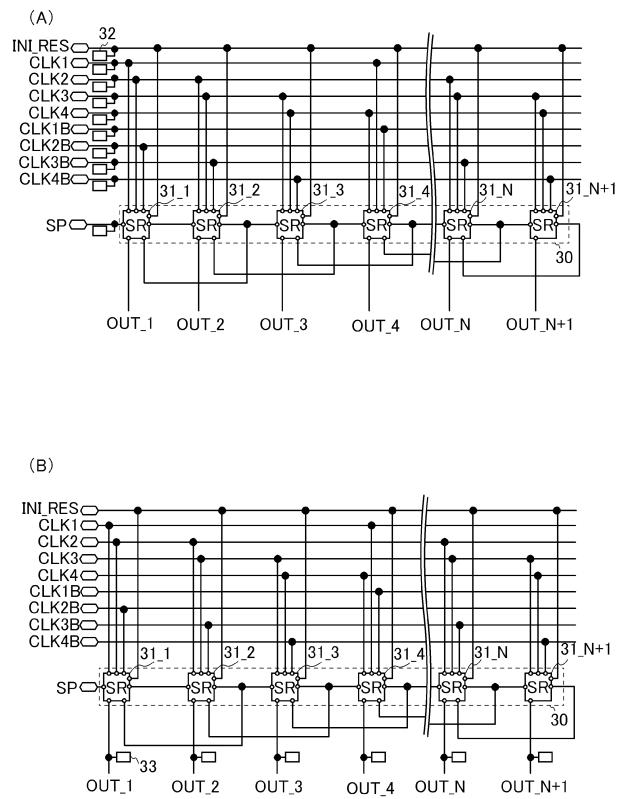

さらに、図2(A)に示すパルス出力回路を複数段備えるシフトレジスタの例について図5を参照して説明する。

#### 【0091】

図5(A)に示すシフトレジスタ30は、複数段のパルス出力回路(パルス出力回路31\_1乃至パルス出力回路31\_N(Nは2以上の自然数))を有する。図5(A)では、一例としてN=5以上の場合について示す。

#### 【0092】

パルス出力回路31\_1乃至パルス出力回路31\_Nのそれぞれは、図2(A)に示すパルス出力回路に相当する。パルス出力回路31\_1乃至パルス出力回路31\_Nは、図5(B)に示すように、セット信号LIN、リセット信号RIN、初期化信号RES、クロック信号CK1、クロック信号CK2、及びクロック信号CK2Bに従い、出力信号OUT、出力信号SROUTとして複数のパルス信号を生成して出力する機能を有する。

10

#### 【0093】

パルス出力回路31\_1には、セット信号LINとしてスタートパルス信号SPが入力される。さらに、パルス出力回路31\_K(Kは2以上N以下の自然数)には、セット信号LINとしてパルス出力回路31\_K-1から出力される出力信号SROUTであるパルス信号が入力される。

#### 【0094】

パルス出力回路31\_M(MはN-1以下の自然数)には、リセット信号RINとしてパルス出力回路31\_M+1から出力される出力信号SROUTであるパルス信号が入力される。

20

#### 【0095】

さらに、パルス出力回路31\_1には、クロック信号CK1としてクロック信号CLK1が入力され、クロック信号CK2としてクロック信号CLK2が入力され、クロック信号CK2Bとしてクロック信号CLK2の反転クロック信号CLK2Bが入力される。さらに、パルス出力回路31\_1を基準として、3つ置きのパルス出力回路毎にクロック信号CK1としてクロック信号CLK1が入力され、クロック信号CK2としてクロック信号CLK2が入力され、クロック信号CK2Bとして反転クロック信号CLK2Bが入力される。

30

#### 【0096】

さらに、パルス出力回路31\_2には、クロック信号CK1としてクロック信号CLK2が入力され、クロック信号CK2としてクロック信号CLK3が入力され、クロック信号CK2Bとしてクロック信号CLK3の反転クロック信号CLK3Bが入力される。さらに、パルス出力回路31\_2を基準として、3つ置きのパルス出力回路毎にクロック信号CK1としてクロック信号CLK2が入力され、クロック信号CK2としてクロック信号CLK3が入力され、クロック信号CK2Bとして反転クロック信号CLK3Bが入力される。

#### 【0097】

さらに、パルス出力回路31\_3には、クロック信号CK1としてクロック信号CLK3が入力され、クロック信号CK2としてクロック信号CLK4が入力され、クロック信号CK2Bとしてクロック信号CLK4の反転クロック信号CLK4Bが入力される。さらに、パルス出力回路31\_3を基準として、3つ置きのパルス出力回路毎にクロック信号CK1としてクロック信号CLK3が入力され、クロック信号CK2としてクロック信号CLK4が入力され、クロック信号CK2Bとして反転クロック信号CLK4Bが入力される。

40

#### 【0098】

さらに、パルス出力回路31\_4には、クロック信号CK1としてクロック信号CLK4が入力され、クロック信号CK2としてクロック信号CLK1が入力され、クロック信号

C K 2 B としてクロック信号 C L K 1 の反転クロック信号 C L K 1 B が入力される。さらに、パルス出力回路 3 1 \_ 4 を基準として、3つ置きのパルス出力回路毎にクロック信号 C K 1 としてクロック信号 C L K 4 が入力され、クロック信号 C K 2 としてクロック信号 C L K 1 が入力され、クロック信号 C K 2 B として反転クロック信号 C L K 1 B が入力される。

#### 【 0 0 9 9 】

パルス出力回路 3 1 \_ N + 1 は、ダミー段のパルス出力回路である。パルス出力回路 3 1 \_ N + 1 の構成は、図 2 ( A ) に示すパルス出力回路の構成のうち、トランジスタ 4 9 が無い構成である。パルス出力回路 3 1 \_ N + 1 から出力される出力信号 S R O U T \_ N + 1 であるパルス信号は、リセット信号 R I N としてパルス出力回路 3 1 \_ N に入力される。なお、パルス出力回路 3 1 \_ N + 1 を設けずに、別途生成したパルス信号をパルス出力回路 3 1 \_ N に入力してもよい。

10

#### 【 0 1 0 0 】

さらに、パルス出力回路 3 1 \_ 1 乃至パルス出力回路 3 1 \_ N + 1 のそれぞれには、初期化信号 R E S として、初期化信号 I N I \_ R E S が入力される。

#### 【 0 1 0 1 】

なお、反転クロック信号 C L K 1 B 乃至反転クロック信号 C L K 4 B は、例えばインバータなどを用いてクロック信号 C L K 1 乃至クロック信号 C L K 4 を反転させることにより生成される。

20

#### 【 0 1 0 2 】

次に、図 5 ( A ) に示すシフトレジスタ 3 0 の駆動方法例について、図 5 ( C ) のタイミングチャートを参照して説明する。ここでは、一例として、電位 V D D が正の電位であり、電位 V S S が負の電位であり、電位 V a が電位 V D D と同等の値であるとして説明する。また、一例として、セット信号 L I N 、リセット信号 R I N 、及びクロック信号 C L K 1 乃至クロック信号 C L K 4 、反転クロック信号 C L K 1 B 乃至反転クロック信号 C L K 4 B 、のハイレベルの電位は、電位 V D D と同じであり、ローレベルの電位は、電位 V S S と同じであるとする。また、一例として、クロック信号 C L K 1 乃至クロック信号 C L K 4 のデューティ比が 25 % であるとする。また、一例として、クロック信号 C L K 2 がクロック信号 C L K 1 よりも 1 / 4 周期分遅れているとし、クロック信号 C L K 3 がクロック信号 C L K 2 よりも 1 / 4 周期分遅れているとし、クロック信号 C L K 4 がクロック信号 C L K 3 よりも 1 / 4 周期分遅れているとする。また、一例として、スタートパルス信号 S P のパルスの幅がクロック信号 C L K 1 乃至クロック信号 C L K 4 のパルスの幅と同じであるとする。また、各パルス出力回路がセット状態になる前に、初期化信号 I N I \_ R E S のパルスを入力し、パルス出力回路の初期化を行うとする。

30

#### 【 0 1 0 3 】

図 5 ( C ) に示すように、図 5 ( A ) に示すシフトレジスタ 3 0 は、時刻 T 1 1 にスタートパルス信号 S P がハイレベルになることにより、時刻 T 1 2 にクロック信号 C L K 1 がハイレベルになる。さらに、シフトレジスタ 3 0 は、クロック信号 C L K 1 乃至クロック信号 C L K 4 、反転クロック信号 C L K 1 B 乃至反転クロック信号 C L K 4 B ( 図示せず ) に従い、出力信号 S R O U T \_ 1 乃至出力信号 S R O U T \_ N のパルスを順次出力し、出力信号 O U T \_ 1 乃至出力信号 O U T \_ N のパルスを順次出力する。

40

#### 【 0 1 0 4 】

以上が図 5 ( A ) に示すシフトレジスタ 3 0 の駆動方法例の説明である。

#### 【 0 1 0 5 】

なお、図 5 ( A ) に示すシフトレジスタ 3 0 に保護回路を設けてもよい。例えば、図 6 ( A ) に示すシフトレジスタ 3 0 は、図 5 ( A ) に示すシフトレジスタ 3 0 において、初期化信号 I N I \_ R E S 、クロック信号 C L K 1 乃至クロック信号 C L K 4 、反転クロック信号 C L K 1 B 乃至反転クロック信号 C L K 4 B 、スタートパルス信号 S P を入力するための配線に保護回路 3 2 が接続された構成である。

#### 【 0 1 0 6 】

50

また、図 6 (B) に示すシフトレジスタ 30 は、図 5 (A) に示すシフトレジスタ 30 から出力信号 OUT\_1 乃至出力信号 OUT\_N を出力するための配線に保護回路 33 が接続された構成である。

#### 【0107】

また、図 5 (A) に示すシフトレジスタ 30 に図 6 (A) に示す保護回路 32 と、図 6 (B) に示す保護回路 33 を設けてもよい。

#### 【0108】

保護回路 32 及び保護回路 33 は、自身が接続する配線に一定の範囲外の電位が与えられたときに、該配線と別の電源線とを導通状態にする回路である。保護回路 32 及び保護回路 33 は、例えばダイオードなどを用いて構成される。

10

#### 【0109】

図 6 に示すように、保護回路を設けることにより、シフトレジスタにおいて、静電気放電 (ESD ともいう) などにより発生する過電圧の耐性を高めることができる。

#### 【0110】

図 1 乃至図 6 を参照して説明したように、本実施の形態に係るパルス出力回路の一例では、出力するパルス信号がローレベルの期間において、トランジスタ 111 のゲートの電位を、一定の値にするのではなく、間欠的に電位 VSS の電位よりも高くする。これにより、トランジスタ 111 に対するストレスを抑制できるため、トランジスタの劣化を抑制できる。

20

#### 【0111】

##### (実施の形態 2)

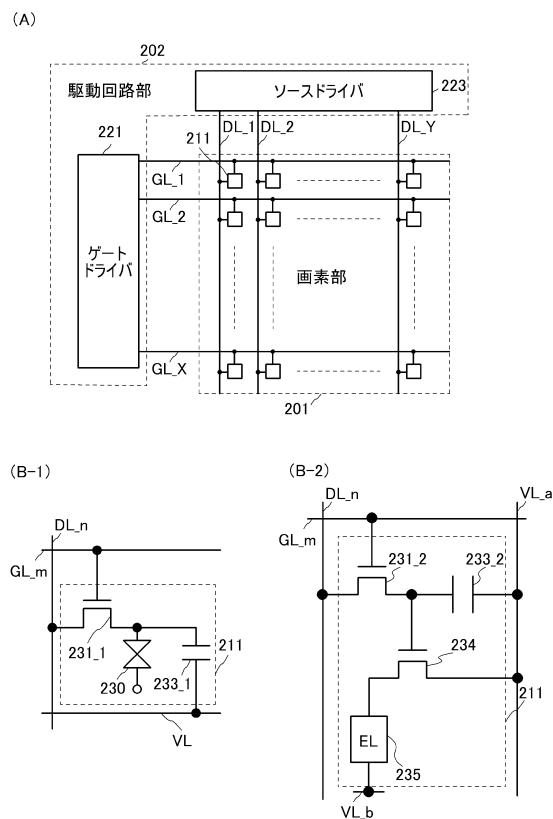

本実施の形態では、実施の形態 1 に係るパルス出力回路を用いた表示装置の例について図 7 乃至図 10 を参照して説明する。

#### 【0112】

図 7 (A) に示す表示装置は、画素部 201 と、駆動回路部 202 と、を含む。

#### 【0113】

画素部 201 は、X 行 (X は 2 以上の自然数) Y 列 (Y は 2 以上の自然数) に配置された複数の画素回路 211 を備え、駆動回路部 202 は、ゲートドライバ 221、ソースドライバ 223 などの駆動回路を備える。

30

#### 【0114】

ゲートドライバ 221 は、実施の形態 1 に示すパルス出力回路を複数段有するシフトレジスタ (例えば図 5 (A) に示すシフトレジスタ 30) を備える。例えば、ゲートドライバ 221 は、シフトレジスタから出力されるパルス信号により、走査線 GL\_1 乃至 GL\_X の電位を制御する機能を有する。なお、ゲートドライバ 221 を複数設け、複数のゲートドライバ 221 により、走査線 GL\_1 乃至 GL\_X を分割して制御してもよい。

#### 【0115】

ソースドライバ 223 には、画像信号が入力される。ソースドライバ 223 は、画像信号を元に画素回路 211 に書き込むデータ信号を生成する機能を有する。また、ソースドライバ 223 は、データ線 DL\_1 乃至 DL\_Y の電位を制御する機能を有する。

40

#### 【0116】

ソースドライバ 223 は、例えば複数のアナログスイッチなどを用いて構成される。ソースドライバ 223 は、複数のアナログスイッチを順次オン状態にすることにより、画像信号を時分割した信号をデータ信号として出力できる。また、シフトレジスタなどを用いてソースドライバ 223 を構成してもよい。このとき、シフトレジスタとしては、実施の形態 1 に示すパルス出力回路を複数段有するシフトレジスタ (例えば図 5 (A) に示すシフトレジスタ) を用いることができる。

#### 【0117】

複数の画素回路 211 のそれぞれは、複数の走査線 GL の一つを介してパルス信号が入力され、複数のデータ線 DL の一つを介してデータ信号が入力される。複数の画素回路 211 のそれぞれは、ゲートドライバ 221 によりデータ信号のデータの書き込み及び保持が

50

制御される。例えば、 $m$ 行 $n$ 列目の画素回路211は、走査線 $GL_m$ ( $m$ はX以下の自然数)を介してゲートドライバ221からパルス信号が入力され、走査線 $GL_m$ の電位に応じてデータ線 $DL_n$ ( $n$ はY以下の自然数)を介してソースドライバ223からデータ信号が入力される。

#### 【0118】

複数の画素回路211のそれぞれは、例えば、図7(B-1)に示すように、液晶素子230と、トランジスタ231\_1と、容量素子233\_1と、を備える。

#### 【0119】

液晶素子230の一対の電極の一方の電位は、画素回路211の仕様に応じて適宜設定される。液晶素子230は、書き込まれるデータにより配向状態が設定される。なお、複数の画素回路211のそれぞれが有する液晶素子230の一対の電極の一方に共通の電位(コモン電位)を与えてよい。また、液晶素子230の一対の電極の一方には、各行の画素回路211毎に異なる電位を与えてよい。

10

#### 【0120】

例えば、液晶素子を備える表示装置の表示方式としては、TN(Twisted Nematic)モード、IPS(In Plane Switching)モード、STN(Super Twisted Nematic)モード、VA(Vertical Alignment)モード、ASM(Axially Symmetric Aligned Micro-cell)モード、OCB(Optically Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、MVA(Multi-Domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、FFS(Fringe Field Switching)モード、又はTBA(Transverse Bend Alignment)モードなどを用いてよい。

20

#### 【0121】

また、ブルー相を示す液晶とカイラル剤とを含む液晶組成物により液晶素子を構成してもよい。ブルー相を示す液晶は、応答速度が1 msec以下と短く、光学的等方性であるため、配向処理が不要であり、視野角依存性が小さい。

30

#### 【0122】

$m$ 行 $n$ 列目の画素回路211において、トランジスタ231\_1のソース及びドレインの一方は、データ線 $DL_n$ に電気的に接続され、他方は液晶素子230の一対の電極の他方に電気的に接続される。また、トランジスタ231\_1のゲートは、走査線 $GL_m$ に電気的に接続される。トランジスタ231\_1は、オン状態又はオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

#### 【0123】

容量素子233\_1の一対の電極の一方は、電位供給線 $VL$ に電気的に接続され、他方は、液晶素子230の一対の電極の他方に電気的に接続される。なお、電位供給線 $VL$ の電位の値は、画素回路211の仕様に応じて適宜設定される。容量素子233\_1は、書き込まれたデータを保持する保持容量としての機能を有する。

40

#### 【0124】

図7(B-1)の画素回路211を備える表示装置では、ゲートドライバ221により各行の画素回路211を順次選択し、トランジスタ231\_1をオン状態にしてデータ信号のデータを書き込む。

#### 【0125】

データが書き込まれた画素回路211は、トランジスタ231\_1がオフ状態になることで保持状態になる。これを行毎に順次行うことにより、画像を表示できる。

#### 【0126】

また、図7(B-2)に示す画素回路211は、トランジスタ231\_2と、容量素子2

50

33\_2と、トランジスタ234と、発光素子（ELともいう）235と、を備える。

【0127】

トランジスタ231\_2のソース及びドレインの一方は、データ線DL\_nに電気的に接続される。さらに、トランジスタ231\_2のゲートは、走査線GL\_mに電気的に接続される。

【0128】

トランジスタ231\_2は、オン状態又はオフ状態になることにより、データ信号のデータの書き込みを制御する機能を有する。

【0129】

容量素子233\_2の一対の電極の一方は、電源線VL\_aに電気的に接続され、他方はトランジスタ231\_2のソース及びドレインの他方に電気的に接続される。 10

【0130】

容量素子233\_2は、書き込まれたデータを保持する保持容量としての機能を有する。

【0131】

トランジスタ234のソース及びドレインの一方は、電源線VL\_aに電気的に接続される。さらに、トランジスタ234のゲートは、トランジスタ231\_2のソース及びドレインの他方に電気的に接続される。

【0132】

発光素子235のアノード及びカソードの一方は、電源線VL\_bに電気的に接続され、他方は、トランジスタ234のソース及びドレインの他方に電気的に接続される。 20

【0133】

発光素子235としては、例えば有機エレクトロルミネセンス素子などを用いることができる。

【0134】

なお、電源線VL\_a及び電源線VL\_bの一方には、電位VDDが与えられ、他方には電位VSSが与えられる。

【0135】

図7(B-2)の画素回路211を備える表示装置では、ゲートドライバ221により各行の画素回路211を順次選択し、トランジスタ231\_2をオン状態にしてデータ信号のデータを書き込む。 30

【0136】

データが書き込まれた画素回路211は、トランジスタ231\_2がオフ状態になることで保持状態になる。さらに、書き込まれたデータ信号の電位に応じてトランジスタ234のソースとドレインの間に流れる電流量が制御され、発光素子235は、流れる電流量に応じた輝度で発光する。これを行毎に順次行うことにより、画像を表示できる。

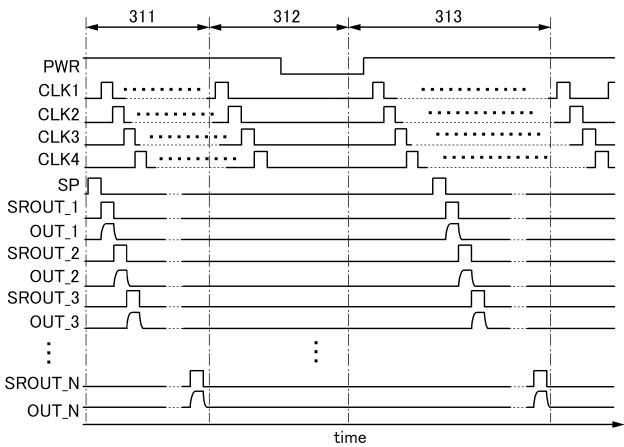

【0137】

さらに、図7(A)に示す表示装置が、低消費電力モードでの動作が可能な場合の駆動方法の例について、図8のタイミングチャートを参照して説明する。ここでは、一例として、ゲートドライバ221に実施の形態1に示すシフトレジスタを用いる場合について説明する。 40

【0138】

図7(A)に示す表示装置の動作は、通常モード及び低消費電力モードに分けられる。

【0139】

通常モードのときの動作について説明する。このとき、図8の期間311に示すように、スタートパルス信号SP、電源電圧PWR、及びクロック信号CLK1乃至クロック信号CLK4をシフトレジスタに入力すると、シフトレジスタは、スタートパルス信号SPのパルスに従い、出力信号SROUT\_1乃至出力信号SROUT\_Nのパルスを順次出力し、出力信号OUT\_1乃至出力信号OUT\_Nのパルスを順次出力する。なお、電源電圧PWRとしては、電位VDDと電位VSSからなる電源電圧、電位Vaと電位VSSからなる電源電圧が挙げられる。また、クロック信号CLK1乃至クロック信号CLK4の 50

入力を開始させると、対応する反転クロック信号 C L K 1 B 乃至クロック信号 C L K 4 B の入力も開始するとする。

#### 【 0 1 4 0 】

次に、通常モードから低消費電力モードになるときの動作について説明する。このとき、図 8 の期間 3 1 2 に示すように、シフトレジスタに対する電源電圧 P W R 、クロック信号 C L K 1 乃至クロック信号 C L K 4 、及びスタートパルス信号 S P の入力を停止させる。また、クロック信号 C L K 1 乃至クロック信号 C L K 4 の入力を停止させると、対応する反転クロック信号 C L K 1 B 乃至クロック信号 C L K 4 B の入力も停止するとする。

#### 【 0 1 4 1 】

このとき、シフトレジスタに対し、まずスタートパルス信号 S P の入力を停止させ、次にクロック信号 C L K 1 乃至クロック信号 C L K 4 の入力を順次停止させ、次に電源電圧 P W R の入力を停止させることが好ましい。これにより、シフトレジスタの誤動作を抑制できる。

#### 【 0 1 4 2 】

シフトレジスタに対する電源電圧 P W R 、クロック信号 C L K 1 乃至クロック信号 C L K 4 、及びスタートパルス信号 S P の入力を停止させると、出力信号 S R O U T \_ 1 乃至出力信号 S R O U T \_ N のパルスの出力が停止し、出力信号 O U T \_ 1 乃至出力信号 O U T \_ N のパルスの出力が停止する。よって、表示装置が低消費電力モードになる。

#### 【 0 1 4 3 】

その後シフトレジスタを通常モードに復帰させる場合には、図 8 の期間 3 1 3 に示すように、シフトレジスタに対するスタートパルス信号 S P 、クロック信号 C L K 1 乃至クロック信号 C L K 4 、及び電源電圧 P W R の入力を再開させる。

#### 【 0 1 4 4 】

このとき、シフトレジスタに対し、まず電源電圧 P W R の入力を再開させ、次にクロック信号 C L K 1 乃至クロック信号 C L K 4 の入力を再開させ、次にスタートパルス信号 S P の入力を再開させる。さらにこのとき、クロック信号 C L K 1 乃至クロック信号 C L K 4 が入力される配線の電位を電位 V D D に設定した後にクロック信号 C L K 1 乃至クロック信号 C L K 4 の入力を順次再開させることが好ましい。

#### 【 0 1 4 5 】

シフトレジスタに対するスタートパルス信号 S P 、クロック信号 C L K 1 乃至クロック信号 C L K 4 、及び電源電圧 P W R の入力を再開させると、シフトレジスタは、スタートパルス信号 S P のパルスに従い、出力信号 S R O U T \_ 1 乃至出力信号 S R O U T \_ N のパルスを順次出力し、出力信号 O U T \_ 1 乃至出力信号 O U T \_ N のパルスを順次出力する。よって、表示装置は通常モードに復帰する。

#### 【 0 1 4 6 】

以上が表示装置の例の説明である。

#### 【 0 1 4 7 】

図 8 を参照して説明したように、本実施の形態に係る表示装置の一例では、必要に応じてシフトレジスタを備える駆動回路の動作を停止できる。よって、例えば画素回路のトランジスタにオフ電流の低いトランジスタを用い、画像を表示する際に、一部又は全部の画素回路でデータ信号の書き換えが不要である場合、駆動回路の動作を停止させ、書き換え間隔を長くすることにより、消費電力を低減できる。

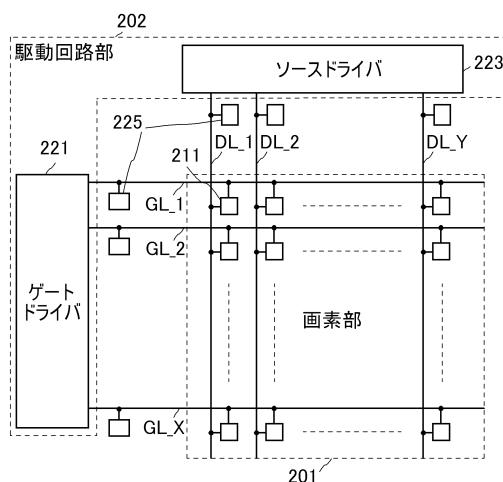

#### 【 0 1 4 8 】

なお、図 9 に示すように、ゲートドライバ 2 2 1 と画素回路 2 1 1 の間（走査線 G L ）に保護回路 2 2 5 を接続してもよい。また、ソースドライバ 2 2 3 と画素回路 2 1 1 の間（データ信号線 D L ）に保護回路 2 2 5 を接続してもよい。保護回路 2 2 5 は、自身が接続する配線に一定の範囲外の電位が与えられたときに、該配線と別の電源線とを導通状態にする回路である。保護回路 2 2 5 は、例えばダイオードなどを用いて構成される。

#### 【 0 1 4 9 】

図 9 に示すように、保護回路を設けることにより、E S D などにより発生する過電圧に対

10

20

30

40

50

する表示装置の耐性を高めることができる。

**【 0 1 5 0 】**

図1乃至図9を参照して説明したように、本実施の形態に係る表示装置の一例では、実施の形態1に示すパルス出力回路を用いてゲートドライバ、ソースドライバなどの駆動回路を構成する。上記駆動回路では、トランジスタに対するストレスが小さいため、表示装置の信頼性を高めることができる。

**【 0 1 5 1 】**

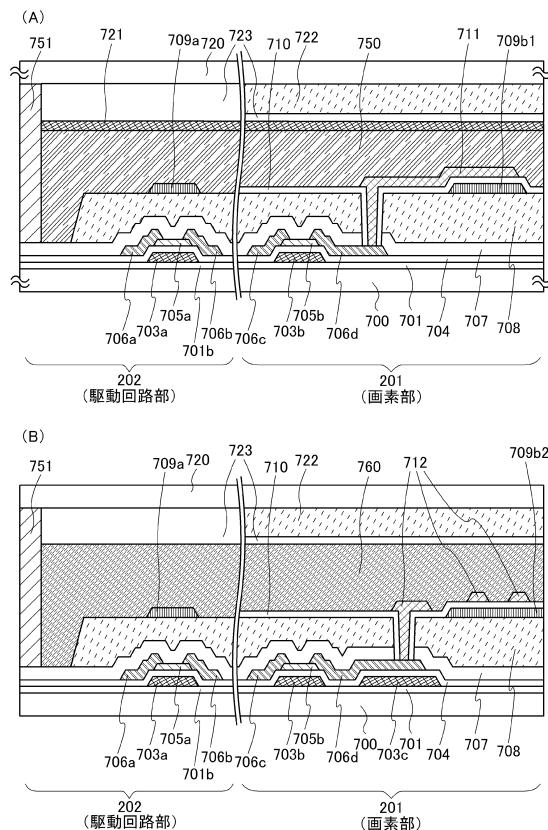

さらに、本実施の形態に係る表示装置の構造例について図10を参照して説明する。

**【 0 1 5 2 】**

図10(A)に示す表示装置は、縦電界方式の液晶表示装置である。

10

**【 0 1 5 3 】**

導電層703a及び703bは、絶縁層701を挟んで基板700の一平面に設けられる。

**【 0 1 5 4 】**

導電層703aは、駆動回路部202に設けられる。導電層703aは、駆動回路のトランジスタのゲートとしての機能を有する。

**【 0 1 5 5 】**

導電層703bは、画素部201に設けられる。導電層703bは、画素回路のトランジスタのゲートとしての機能を有する。

**【 0 1 5 6 】**

絶縁層704は、導電層703a及び703bの上に設けられる。絶縁層704は、駆動回路のトランジスタのゲート絶縁層、及び画素回路のトランジスタのゲート絶縁層としての機能を有する。

20

**【 0 1 5 7 】**

半導体層705aは、絶縁層704を挟んで導電層703aに重畳する。半導体層705aは、駆動回路のトランジスタのチャネルが形成される層(チャネル形成層ともいう)としての機能を有する。

**【 0 1 5 8 】**

半導体層705bは、絶縁層704を挟んで導電層703bに重畳する。半導体層705bは、画素回路のトランジスタのチャネル形成層としての機能を有する。

30

**【 0 1 5 9 】**

導電層706aは、半導体層705aに電気的に接続される。導電層706aは、駆動回路のトランジスタが有するソース及びドレインの一方としての機能を有する。

**【 0 1 6 0 】**

導電層706bは、半導体層705aに電気的に接続される。導電層706bは、駆動回路のトランジスタが有するソース及びドレインの他方としての機能を有する。

**【 0 1 6 1 】**

導電層706cは、半導体層705bに電気的に接続される。導電層706cは、画素回路のトランジスタが有するソース及びドレインの一方としての機能を有する。

**【 0 1 6 2 】**

導電層706dは、半導体層705bに電気的に接続される。導電層706dは、画素回路のトランジスタが有するソース及びドレインの他方としての機能を有する。

40

**【 0 1 6 3 】**

絶縁層707は、半導体層705a及び半導体層705bの上、及び導電層706a乃至導電層706dの上に設けられる。絶縁層707は、トランジスタを保護する絶縁層(保護絶縁層ともいう)としての機能を有する。

**【 0 1 6 4 】**

絶縁層708は、絶縁層707の上に設けられる。絶縁層708は、平坦化層としての機能を有する。絶縁層708を設けることにより、絶縁層708よりも下層の導電層と絶縁層708よりも上層の導電層とによる寄生容量の発生を抑制できる。

50

**【 0 1 6 5 】**

導電層 7 0 9 a 及び導電層 7 0 9 b 1 は、絶縁層 7 0 8 の上に設けられる。

**【 0 1 6 6 】**

導電層 7 0 9 a は、絶縁層 7 0 7 及び絶縁層 7 0 8 を挟んで半導体層 7 0 5 a に重畳する。導電層 7 0 9 a は、駆動回路のトランジスタのゲートとしての機能を有する。例えば、導電層 7 0 9 a を駆動回路のトランジスタのバックゲートとして機能させてもよい。例えば、N チャネル型トランジスタの場合、上記バックゲートに、負電位を与えることにより、トランジスタのしきい値電圧を正方向にシフトさせることができる。また、上記バックゲートを接地させてもよい。

**【 0 1 6 7 】**

導電層 7 0 9 b 1 は、画素回路の容量素子が有する一対の電極の一方としての機能を有する。

**【 0 1 6 8 】**

絶縁層 7 1 0 は、絶縁層 7 0 8 の表面及び導電層 7 0 9 b 1 の上に設けられる。なお、絶縁層 7 1 0 のうち、駆動回路のトランジスタの上に形成される部分を除去することにより、絶縁層 7 0 8 中の水素や水を外部に放出できるため、絶縁層 7 0 7 から絶縁層 7 0 8 が剥がれてしまうことを抑制できる。絶縁層 7 1 0 は、保護絶縁層としての機能を有する。また、絶縁層 7 1 0 は、画素回路の容量素子の誘電体層としての機能を有する。

**【 0 1 6 9 】**

導電層 7 1 1 は、絶縁層 7 1 0 の上に設けられ、絶縁層 7 0 7 、絶縁層 7 0 8 、及び絶縁層 7 1 0 を貫通して設けられた開口部により導電層 7 0 6 d に電気的に接続される。さらに、導電層 7 1 1 は、絶縁層 7 1 0 を挟んで導電層 7 0 9 b 1 に重畳する。導電層 7 1 1 は、画素回路の液晶素子が有する一対の電極の一方、及び容量素子が有する一対の電極の他方としての機能を有する。

**【 0 1 7 0 】**

着色層 7 2 2 は、基板 7 2 0 の一平面の一部に設けられる。着色層 7 2 2 は、カラーフィルタとしての機能を有する。

**【 0 1 7 1 】**

絶縁層 7 2 3 は、着色層 7 2 2 を挟んで基板 7 2 0 の一平面に設けられる。絶縁層 7 2 3 は、平坦化層としての機能を有する。

**【 0 1 7 2 】**

導電層 7 2 1 は、絶縁層 7 2 3 の一平面に設けられる。導電層 7 2 1 は、画素回路の液晶素子が有する一対の電極の他方としての機能を有する。なお、導電層 7 2 1 の上に別途絶縁層を設けてもよい。

**【 0 1 7 3 】**

液晶層 7 5 0 は、シール材 7 5 1 を用いて、導電層 7 1 1 と導電層 7 2 1 の間に設けられる。なお、絶縁層 7 0 7 及び絶縁層 7 1 0 のうち、シール材 7 5 1 下に位置する部分を除去してもよい。

**【 0 1 7 4 】**

さらに、図 1 0 ( B ) に示す表示装置は、横電界方式の表示装置であり、図 1 0 ( A ) に示す表示装置と比較した場合、導電層 7 0 3 c を別途有し、導電層 7 0 9 b 1 の代わりに導電層 7 0 9 b 2 を有し、導電層 7 1 1 の代わりに導電層 7 1 2 を有し、液晶層 7 5 0 の代わりに液晶層 7 6 0 を有する点が異なる。図 1 0 ( A ) に示す表示装置と同じ部分については、図 1 0 ( A ) に示す表示装置の説明を適宜援用する。

**【 0 1 7 5 】**

導電層 7 0 3 c は、絶縁層 7 0 1 の上に設けられる。このとき、導電層 7 0 6 d は、絶縁層 7 0 4 を挟んで導電層 7 0 3 c に重畳する。

**【 0 1 7 6 】**

導電層 7 0 9 b 2 は、絶縁層 7 0 8 の上に設けられる。導電層 7 0 9 b 2 は、画素回路の液晶素子が有する一対の電極の一方としての機能を有する。さらに、導電層 7 0 9 b 2 は

10

20

30

40

50

、画素回路の容量素子が有する一対の電極の一方としての機能を有する。

【0177】

導電層712は、絶縁層710の上に設けられ、絶縁層707、絶縁層708、及び絶縁層710を貫通して設けられた開口部により導電層706dに電気的に接続される。また、導電層712は、歯部を有し、歯部のそれぞれが絶縁層710を挟んで導電層709b2に重畠する。導電層712は、画素回路の液晶素子が有する一対の電極の他方としての機能を有する。さらに、導電層712は、画素回路の容量素子が有する一対の電極の他方としての機能を有する。

【0178】

液晶層760は、シール材751により、導電層711と導電層712の上に設けられる。

。

【0179】

なお、図10(A)及び図10(B)では、トランジスタをチャネルエッチ型のトランジスタとしているが、これに限定されず、例えばチャネル保護型のトランジスタとしてもよい。また、トップゲート型のトランジスタとしてもよい。

【0180】

さらに、図10(A)及び図10(B)に示す表示装置の各構成要素について説明する。

なお、各層を積層構造にしてもよい。

【0181】

基板700及び720としては、例えばガラス基板又はプラスチック基板などを適用できる。

20

【0182】

絶縁層701としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

【0183】

導電層703a乃至703cとしては、例えばモリブデン、チタン、クロム、タンタル、マグネシウム、銀、タングステン、アルミニウム、銅、ネオジム、又はスカンジウムなどの金属材料を含む層を適用できる。

【0184】

絶縁層704としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。例えば、絶縁層704としては、窒化シリコン層及び酸化窒化シリコン層の積層を適用できる。このとき、上記窒化シリコン層を、組成の異なる複数の窒化シリコン層の積層としてもよい。また、絶縁層704として、酸化物層を用いてもよい。上記酸化物層としては、例えばIn:Ga:Zn = 1:3:2の原子比である酸化物の層などを用いることができる。

30

【0185】

半導体層705a及び半導体層705bとしては、例えば酸化物半導体層を用いることができる。

【0186】

上記酸化物半導体としては、実施の形態1と同様に、例えばIn系金属酸化物、Zn系金属酸化物、In-Zn系金属酸化物、又はIn-Ga-Zn系金属酸化物などを適用できる。また、上記In-Ga-Zn系金属酸化物に含まれるGaの一部若しくは全部の代わりに他の金属元素を含む金属酸化物を用いてもよい。なお、上記酸化物半導体が結晶を有していてもよい。例えば、上記酸化物半導体が多結晶又は単結晶でもよい。また、上記酸化物半導体が非晶質でもよい。

【0187】

上記他の金属元素としては、例えばガリウムよりも多くの酸素原子と結合が可能な金属元素を用いればよく、例えばチタン、ジルコニウム、ハフニウム、ゲルマニウム、及び錫の

40

いずれか一つ又は複数の元素を用いればよい。また、上記他の金属元素としては、ランタン、セリウム、プラセオジム、ネオジム、サマリウム、ユウロピウム、ガドリニウム、テルビウム、ジスプロシウム、ホルミウム、エルビウム、ツリウム、イッテルビウム、及びルテチウムのいずれか一つ又は複数の元素を用いればよい。これらの金属元素は、スタビライザーとしての機能を有する。なお、これらの金属元素の添加量は、金属酸化物が半導体として機能することが可能な量である。酸素原子との結合がガリウムよりも多くできる金属元素を用い、さらには金属酸化物中に酸素を供給することにより、金属酸化物中の酸素欠陥を少なくできる。

#### 【0188】

さらに、例えば  $I_n : Ga : Zn = 1 : 1 : 1$  の原子比である第1の酸化物半導体層、 $I_n : Ga : Zn = 3 : 1 : 2$  の原子比である第2の酸化物半導体層、及び  $I_n : Ga : Zn = 1 : 1 : 1$  の原子比である第3の酸化物半導体層の積層により、半導体層705a及び半導体層705bを構成してもよい。上記積層により半導体層705a及び半導体層705bを構成することにより、例えばトランジスタの電界効果移動度を高めることができる。

#### 【0189】

上記酸化物半導体を含むトランジスタは、バンドギャップが広いため熱励起によるリーク電流が少ない。さらに、正孔の有効質量が10以上と重く、トンネル障壁の高さが2.8eV以上と高い。これにより、トンネル電流が少ない。さらに、半導体層中のキャリアが極めて少ない。よって、オフ電流を低くできる。例えば、オフ電流は、室温(25)でチャネル幅  $1 \mu m$ あたり  $1 \times 10^{-19} A$  ( $100 zA$ )以下である。より好ましくは  $1 \times 10^{-22} A$  ( $100 yA$ )以下である。トランジスタのオフ電流は、低ければ低いほどよいが、トランジスタのオフ電流の下限値は、約  $1 \times 10^{-30} A / \mu m$  であると見積もられる。なお、上記酸化物半導体層に限定されず、半導体層705a及び半導体層705bとして14族(シリコンなど)の元素を有する半導体層を用いてもよい。例えば、シリコンを含む半導体層としては、単結晶シリコン層、多結晶シリコン層、又は非晶質シリコン層などを用いることができる。

#### 【0190】

例えば、水素又は水などの不純物を可能な限り除去し、酸素を供給して酸素欠損を可能な限り減らすことにより、上記酸化物半導体を含むトランジスタを作製できる。このとき、チャネル形成領域において、ドナー不純物といわれる水素の量を、二次イオン質量分析法(SIMSともいう)の測定値で  $1 \times 10^{19} / cm^3$  以下、好ましくは  $1 \times 10^{18} / cm^3$  以下に低減することが好ましい。

#### 【0191】

高純度化させた酸化物半導体層を電界効果トランジスタに用いることにより、酸化物半導体層のキャリア密度を  $1 \times 10^{14} / cm^3$  未満、好ましくは  $1 \times 10^{12} / cm^3$  未満、さらに好ましくは  $1 \times 10^{11} / cm^3$  未満にできる。このように、キャリア密度を少なくすることにより、チャネル幅  $1 \mu m$ あたりの電界効果トランジスタのオフ電流を  $1 \times 10^{-19} A$  ( $100 zA$ )以下、より好ましくは  $1 \times 10^{-22} A$  ( $100 yA$ )以下にまで抑制できる。電界効果トランジスタのオフ電流は、低ければ低いほどよいが、電界効果トランジスタのオフ電流の下限値は、約  $1 \times 10^{-30} A / \mu m$  であると見積もられる。

#### 【0192】

なお、上記酸化物半導体を、C Axis Aligned Crystalline Oxide Semiconductor (CAAC-OSともいう)としてもよい。

#### 【0193】

例えば、スパッタリング法を用いてCAAC-OSである酸化物半導体層を形成できる。このとき、多結晶である酸化物半導体スパッタリング用ターゲットを用いてスパッタリングを行う。上記スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域がa-b面から劈開し、a-b面に平行な面を有する平板状

10

20

30

40

50

又はペレット状のスパッタリング粒子として剥離することができる。このとき、結晶状態を維持したまま、上記スパッタリング粒子が基板に到達することにより、スパッタリング用ターゲットの結晶状態が基板に転写される。これにより、C A A C - O S が形成される。

【0194】

また、C A A C - O S を形成するために、以下の条件を適用することが好ましい。

【0195】

例えば、不純物濃度を低減させてC A A C - O S を形成することにより、不純物による酸化物半導体の結晶状態の崩壊を抑制できる。例えば、成膜室内に存在する不純物（水素、水、二酸化炭素、及び窒素など）を低減することが好ましい。また、成膜ガス中の不純物を低減することが好ましい。例えば、成膜ガスとして露点が - 80 以下、好ましくは - 100 以下である成膜ガスを用いることが好ましい。10

【0196】

また、成膜時の基板温度を高くすることが好ましい。上記基板温度を高くすることにより、平板状のスパッタリング粒子が基板に到達したときに、スパッタリング粒子のマイグレーションが起こり、平らな面を向けてスパッタリング粒子を基板に付着させることができる。例えば、基板加熱温度を 100 以上 740 以下、好ましくは 200 以上 500 以下として酸化物半導体膜を成膜することにより酸化物半導体層を形成する。

【0197】

また、成膜ガス中の酸素割合を高くし、電力を最適化して成膜時のプラズマダメージを抑制させることが好ましい。例えば、成膜ガス中の酸素割合を、30 体積 % 以上、好ましくは 100 体積 % にすることが好ましい。20

【0198】

導電層 706 a 乃至導電層 706 d としては、例えばモリブデン、チタン、クロム、タンタル、マグネシウム、銀、タンクステン、アルミニウム、銅、ネオジム、スカンジウム、又はルテニウムなどの金属材料を含む層を適用できる。

【0199】

絶縁層 707 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

【0200】

絶縁層 708 としては、例えば有機絶縁材料又は無機絶縁材料の層などを適用できる。例えば、アクリル樹脂などを用いて絶縁層 708 を構成してもよい。30

【0201】

導電層 709 a、導電層 709 b 1、及び導電層 709 b 2 としては、例えば導体としての機能を有し、光を透過する金属酸化物の層などを適用できる。例えば、酸化インジウム酸化亜鉛又はインジウム錫酸化物などを適用できる。

【0202】

絶縁層 710 としては、例えば絶縁層 704 に適用可能な材料を用いることができる。

【0203】

導電層 711、導電層 712、及び導電層 721 としては、例えば光を透過する金属酸化物の層などを適用できる。例えば、酸化インジウム酸化亜鉛又はインジウム錫酸化物などを適用できる。40

【0204】

着色層 722 は、例えば赤 (R)、緑 (G)、及び青 (B) の一つを呈する光を透過する機能を有する。着色層 722 としては、染料又は顔料を含む層を用いることができる。

【0205】

絶縁層 723 としては、例えば酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、窒化アルミニウム、酸化窒化アルミニウム、窒化酸化アルミニウム、又は酸化ハフニウムなどの材料を含む層を適用できる。

【0206】

10

20

30

40

50

液晶層 750 としては、例えば TN 液晶、OCB 液晶、STN 液晶、VA 液晶、EBC 型液晶、GH 液晶、高分子分散型液晶、又はディスコチック液晶などを含む層を用いることができる。

【0207】

液晶層 760 としては、例えばブルー相を示す液晶を含む層を適用できる。

【0208】

ブルー相を示す液晶を含む層は、例えばブルー相を示す液晶、カイラル剤、液晶性モノマー、非液晶性モノマー、及び重合開始剤を含む液晶組成物により構成される。ブルー相を示す液晶は、応答時間が短く、光学的等方性であるため、配向処理が不要であり、視野角依存性が小さい。よって、ブルー相を示す液晶を用いることにより、液晶表示装置の動作を速くできる。

【0209】

以上が図 10 に示す表示装置の構造例の説明である。

【0210】

図 10 を参照して説明したように、本実施の形態に係る表示装置の一例では、画素回路と同一基板上に駆動回路を設ける。これにより、画素回路と駆動回路を接続するための配線の数を少なくできる。

【0211】

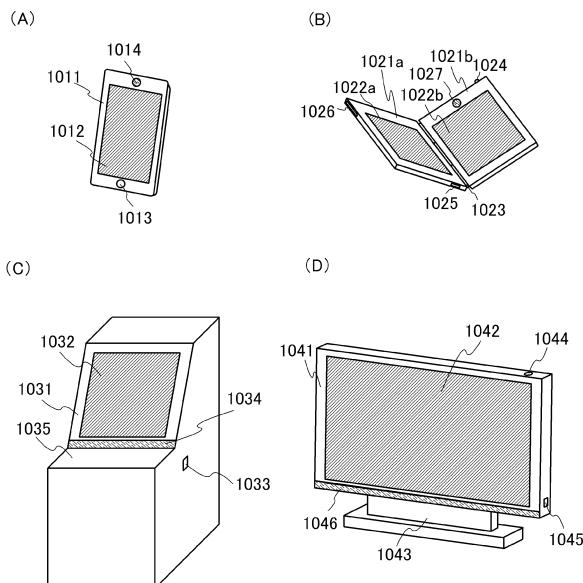

(実施の形態 3)

本実施の形態では、実施の形態 2 の表示装置を用いたパネルを備える電子機器の例について、図 11 を参照して説明する。

【0212】

図 11 (A) に示す電子機器は、携帯型情報端末の一例である。

【0213】

図 11 (A) に示す電子機器は、筐体 1011 と、筐体 1011 に設けられたパネル 1012 と、ボタン 1013 と、スピーカー 1014 と、を具備する。

【0214】

なお、筐体 1011 に、外部機器に接続するための接続端子及び操作ボタンが設けられてもよい。

【0215】

さらに、実施の形態 2 の表示装置を用いてパネル 1012 を構成してもよい。

【0216】

さらに、タッチパネルを用いてパネル 1012 を構成してもよい。これにより、パネル 1012 においてタッチ検出を行うことができる。タッチパネルとしては、例えば光学式タッチパネル、静電容量式タッチパネル、抵抗膜式タッチパネルなどを適用できる。

【0217】

ボタン 1013 は、筐体 1011 に設けられる。例えば、ボタン 1013 が電源ボタンであれば、ボタン 1013 を押すことにより、電子機器のオン状態を制御できる。

【0218】

スピーカー 1014 は、筐体 1011 に設けられる。スピーカー 1014 は音声を出力する。

【0219】

なお、筐体 1011 にマイクが設けられていてもよい。筐体 1011 にマイクを設けられることにより、例えば図 11 (A) に示す電子機器を電話機として機能させることができる。

【0220】

図 11 (A) に示す電子機器は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊戯機の一つ又は複数としての機能を有する。

【0221】

図 11 (B) に示す電子機器は、折り畳み式の情報端末の一例である。

10

20

30

40

50

## 【0222】

図11(B)に示す電子機器は、筐体1021aと、筐体1021bと、筐体1021aに設けられたパネル1022aと、筐体1021bに設けられたパネル1022bと、軸部1023と、ボタン1024と、接続端子1025と、記録媒体挿入部1026と、スピーカー1027と、を備える。

## 【0223】

筐体1021aと筐体1021bは、軸部1023により接続される。

## 【0224】

さらに、実施の形態2の表示装置を用いてパネル1022a及び1022bを構成してもよい。

10

## 【0225】

さらに、タッチパネルを用いてパネル1022a及び1022bを構成してもよい。これにより、パネル1022a及び1022bにおいてタッチ検出を行うことができる。タッチパネルとしては、例えば光学式タッチパネル、静電容量式タッチパネル、抵抗膜式タッチパネルなどを適用できる。

## 【0226】

図11(B)に示す電子機器は、軸部1023を有するため、パネル1022aとパネル1022bを対向させて折り畳むことができる。

## 【0227】

ボタン1024は、筐体1021bに設けられる。なお、筐体1021aにボタン1024を設けてもよい。例えば、ボタン1024が電源ボタンであれば、ボタン1024を押すことにより、電子機器のオン状態を制御できる。

20

## 【0228】

接続端子1025は、筐体1021aに設けられる。なお、筐体1021bに接続端子1025が設けられていてもよい。また、接続端子1025が筐体1021a及び筐体1021bの一方又は両方に複数設けられていてもよい。接続端子1025は、図11(B)に示す電子機器と他の機器を接続するための端子である。

## 【0229】

記録媒体挿入部1026は、筐体1021aに設けられる。筐体1021bに記録媒体挿入部1026が設けられていてもよい。また、記録媒体挿入部1026が筐体1021a及び筐体1021bの一方又は両方に複数設けられていてもよい。例えば、記録媒体挿入部にカード型記録媒体を挿入することにより、カード型記録媒体のデータを電子機器に読み出し、又は電子機器内のデータをカード型記録媒体に書き込むことができる。

30

## 【0230】

スピーカー1027は、筐体1021bに設けられる。スピーカー1027は、音声を出力する。なお、筐体1021aにスピーカー1027を設けてもよい。

## 【0231】

なお、筐体1021a又は筐体1021bにマイクを設けてもよい。筐体1021a又は筐体1021bにマイクが設けられることにより、例えば図11(B)に示す電子機器を電話機として機能させることができる。

40

## 【0232】

図11(B)に示す電子機器は、例えば電話機、電子書籍、パーソナルコンピュータ、及び遊戯機の一つ又は複数としての機能を有する。

## 【0233】

図11(C)に示す電子機器は、据え置き型情報端末の一例である。図11(C)に示す電子機器は、筐体1031と、筐体1031に設けられたパネル1032と、ボタン1033と、スピーカー1034と、を具備する。

## 【0234】

さらに、実施の形態2の表示装置を用いてパネル1032を構成してもよい。

## 【0235】

50

さらに、タッチパネルを用いてパネル 1032 を構成してもよい。これにより、パネル 1032 においてタッチ検出を行うことができる。タッチパネルとしては、例えば光学式タッチパネル、静電容量式タッチパネル、抵抗膜式タッチパネルなどを適用できる。

【0236】

なお、筐体 1031 の甲板部 1035 にパネル 1032 と同様のパネルを設けてもよい。

【0237】

さらに、筐体 1031 に券などを出力する券出力部、硬貨投入部、及び紙幣挿入部などを設けてもよい。

【0238】

ボタン 1033 は、筐体 1031 に設けられる。例えば、ボタン 1033 が電源ボタンであれば、ボタン 1033 を押すことにより、電子機器のオン状態を制御できる。 10

【0239】

スピーカー 1034 は、筐体 1031 に設けられる。スピーカー 1034 は、音声を出力する。

【0240】

図 11 (C) に示す電子機器は、例えば現金自動預け払い機、チケットなどの注文をするための情報通信端末（マルチメディアステーションともいう）、又は遊技機としての機能を有する。

【0241】

図 11 (D) は、据え置き型情報端末の一例である。図 11 (D) に示す電子機器は、筐体 1041 と、筐体 1041 に設けられたパネル 1042 と、筐体 1041 を支持する支持台 1043 と、ボタン 1044 と、接続端子 1045 と、スピーカー 1046 と、を備える。 20

【0242】

なお、筐体 1041 に外部機器に接続させるための接続端子を設けてもよい。

【0243】

さらに、実施の形態 2 の表示装置を用いてパネル 1042 を構成してもよい。

【0244】

さらに、タッチパネルを用いてパネル 1042 を構成してもよい。これにより、パネル 1042 においてタッチ検出を行うことができる。タッチパネルとしては、例えば光学式タッチパネル、静電容量式タッチパネル、抵抗膜式タッチパネルなどを適用できる。 30

【0245】

ボタン 1044 は、筐体 1041 に設けられる。例えば、ボタン 1044 が電源ボタンであれば、ボタン 1044 を押すことにより、電子機器のオン状態を制御できる。

【0246】

接続端子 1045 は、筐体 1041 に設けられる。接続端子 1045 は、図 11 (D) に示す電子機器と他の機器を接続するための端子である。例えば、接続端子 1045 により図 11 (D) に示す電子機器とパソコンコンピュータを接続すると、パソコンコンピュータから入力されるデータ信号に応じた画像をパネル 1042 に表示させることができる。例えば、図 11 (D) に示す電子機器のパネル 1042 が接続する他の電子機器のパネルより大きければ、当該他の電子機器の表示画像を拡大することができ、複数の人が同時に視認しやすくなる。 40

【0247】

スピーカー 1046 は、筐体 1041 に設けられる。スピーカー 1046 は、音声を出力する。

【0248】

図 11 (D) に示す電子機器は、例えば出力モニタ、パソコンコンピュータ、及びテレビジョン装置の一つ又は複数としての機能を有する。

【0249】

以上が図 11 に示す電子機器の例の説明である。

## 【0250】

図11を参照して説明したように、本実施の形態に係る電子機器では、パネルに実施の形態2の表示装置を用いたパネルを設けることにより、信頼性の高い電子機器を提供できる。

## 【符号の説明】

## 【0251】

|           |         |    |

|-----------|---------|----|

| 3 0       | シフトレジスタ | 10 |

| 3 1       | パルス出力回路 |    |

| 3 2       | 保護回路    |    |

| 3 3       | 保護回路    |    |

| 4 1       | トランジスタ  |    |

| 4 2       | トランジスタ  |    |

| 4 3       | トランジスタ  |    |

| 4 4       | トランジスタ  |    |

| 4 5       | トランジスタ  |    |

| 4 6       | トランジスタ  |    |

| 4 7       | トランジスタ  |    |

| 4 8       | トランジスタ  |    |

| 4 9       | トランジスタ  |    |

| 5 0       | トランジスタ  | 20 |

| 5 1       | トランジスタ  |    |

| 5 2       | トランジスタ  |    |

| 1 1 1     | トランジスタ  |    |

| 1 1 2     | トランジスタ  |    |

| 1 1 3     | トランジスタ  |    |

| 1 1 4     | トランジスタ  |    |

| 2 0 1     | 画素部     |    |

| 2 0 2     | 駆動回路部   |    |

| 2 1 1     | 画素回路    |    |

| 2 2 1     | ゲートドライバ | 30 |

| 2 2 3     | ソースドライバ |    |

| 2 2 5     | 保護回路    |    |

| 2 3 0     | 液晶素子    |    |

| 2 3 1 _ 1 | トランジスタ  |    |

| 2 3 1 _ 2 | トランジスタ  |    |

| 2 3 3 _ 1 | 容量素子    |    |

| 2 3 3 _ 2 | 容量素子    |    |

| 2 3 4     | トランジスタ  |    |

| 2 3 5     | 発光素子    |    |

| 3 1 1     | 期間      | 40 |

| 3 1 2     | 期間      |    |

| 3 1 3     | 期間      |    |

| 7 0 0     | 基板      |    |

| 7 0 1     | 絶縁層     |    |

| 7 0 3 a   | 導電層     |    |

| 7 0 3 b   | 導電層     |    |

| 7 0 3 c   | 導電層     |    |

| 7 0 4     | 絶縁層     |    |

| 7 0 5 a   | 半導体層    |    |

| 7 0 5 b   | 半導体層    | 50 |

|           |         |    |

|-----------|---------|----|

| 7 0 6 a   | 導電層     |    |

| 7 0 6 b   | 導電層     |    |

| 7 0 6 c   | 導電層     |    |

| 7 0 6 d   | 導電層     |    |

| 7 0 7     | 絶縁層     |    |

| 7 0 8     | 絶縁層     |    |

| 7 0 9 a   | 導電層     |    |

| 7 0 9 b 1 | 導電層     |    |

| 7 0 9 b 2 | 導電層     |    |

| 7 1 0     | 絶縁層     | 10 |

| 7 1 1     | 導電層     |    |

| 7 1 2     | 導電層     |    |

| 7 2 0     | 基板      |    |

| 7 2 1     | 導電層     |    |

| 7 2 2     | 着色層     |    |

| 7 2 3     | 絶縁層     |    |

| 7 5 0     | 液晶層     |    |

| 7 5 1     | シール材    |    |

| 7 6 0     | 液晶層     |    |

| 1 0 1 1   | 筐体      | 20 |

| 1 0 1 2   | パネル     |    |

| 1 0 1 3   | ボタン     |    |

| 1 0 1 4   | スピーカー   |    |

| 1 0 2 1 a | 筐体      |    |

| 1 0 2 1 b | 筐体      |    |

| 1 0 2 2 a | パネル     |    |

| 1 0 2 2 b | パネル     |    |

| 1 0 2 3   | 軸部      |    |

| 1 0 2 4   | ボタン     |    |

| 1 0 2 5   | 接続端子    | 30 |

| 1 0 2 6   | 記録媒体挿入部 |    |

| 1 0 2 7   | スピーカー   |    |

| 1 0 3 1   | 筐体      |    |

| 1 0 3 2   | パネル     |    |

| 1 0 3 3   | ボタン     |    |

| 1 0 3 4   | スピーカー   |    |

| 1 0 3 5   | 甲板部     |    |

| 1 0 4 1   | 筐体      |    |

| 1 0 4 2   | パネル     |    |

| 1 0 4 3   | 支持台     | 40 |

| 1 0 4 4   | ボタン     |    |

| 1 0 4 5   | 接続端子    |    |

| 1 0 4 6   | スピーカー   |    |

【図面】

【図1】

【図2】

【図2】

10

20

【図4】

30

40

50

【図5】

【図6】

【図7】

【図8】

10

20

30

40

50

【図9】

【図10】

【図11】

10

20

30

40

50

---

フロントページの続き

## (51)国際特許分類

|         | F               | I       |               |

|---------|-----------------|---------|---------------|

| G 0 9 G | 3/36 (2006.01)  | G 0 9 G | 3/20 6 8 0 G  |

| G 0 9 G | 3/3233(2016.01) | G 0 9 G | 3/3266        |

| H 1 0 K | 59/123(2023.01) | G 0 9 G | 3/36          |

| H 1 0 K | 59/121(2023.01) | G 0 9 G | 3/20 6 7 0 J  |

| H 1 0 K | 59/131(2023.01) | G 0 9 G | 3/20 6 7 0 E  |

| G 0 2 F | 1/1368(2006.01) | G 0 9 G | 3/3233        |

| G 0 2 F | 1/133(2006.01)  | G 0 9 G | 3/20 6 2 4 B  |

| H 0 1 L | 29/786(2006.01) | H 1 0 K | 59/123        |

| G 1 1 C | 19/28 (2006.01) | H 1 0 K | 59/121 2 1 6  |

|         |                 | H 1 0 K | 59/121 2 1 3  |

|         |                 | H 1 0 K | 59/131        |

|         |                 | G 0 2 F | 1/1368        |

|         |                 | G 0 2 F | 1/133 5 5 0   |

|         |                 | H 0 1 L | 29/78 6 1 4   |

|         |                 | H 0 1 L | 29/78 6 1 2 B |

|         |                 | G 1 1 C | 19/28 2 3 0   |