(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2012-150479

(P2012-150479A)

(43) 公開日 平成24年8月9日(2012.8.9)

| (51) Int.Cl.                | F 1                  | テーマコード (参考) |

|-----------------------------|----------------------|-------------|

| <b>G09G 3/30</b> (2006.01)  | G09G 3/30 J 3K107    |             |

| <b>G09G 3/20</b> (2006.01)  | G09G 3/20 624B 5C080 |             |

| <b>H01L 51/50</b> (2006.01) | G09G 3/20 642E 5C380 |             |

|                             | G09G 3/20 612F       |             |

|                             | G09G 3/20 641D       |             |

審査請求 有 請求項の数 1 O L (全 24 頁) 最終頁に続く

|              |                                     |            |                                                                                    |

|--------------|-------------------------------------|------------|------------------------------------------------------------------------------------|

| (21) 出願番号    | 特願2012-25697 (P2012-25697)          | (71) 出願人   | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地                                     |

| (22) 出願日     | 平成24年2月9日 (2012.2.9)                | (72) 発明者   | 三宅 博之<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                       |

| (62) 分割の表示   | 特願2005-264548 (P2005-264548)<br>の分割 | (72) 発明者   | 岩淵 友幸<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                       |

| 原出願日         | 平成17年9月13日 (2005.9.13)              | (72) 発明者   | 福本 良太<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内                                       |

| (31) 優先権主張番号 | 特願2004-270447 (P2004-270447)        | F ターム (参考) | 3K107 AA01 BB01 CC32 EE03 HH05<br>5C080 AA06 BB05 DD23 DD26 EE28<br>JJ03 JJ05 JJ06 |

| (32) 優先日     | 平成16年9月16日 (2004.9.16)              |            |                                                                                    |

| (33) 優先権主張国  | 日本国 (JP)                            |            |                                                                                    |

|              |                                     |            | 最終頁に続く                                                                             |

## (54) 【発明の名称】表示装置

## (57) 【要約】 (修正有)

【課題】発光素子と直列に接続された薄膜トランジスタのオフ電流により、発光素子が微発光する問題を解決し、表示のコントラストを上げて、明瞭な表示が可能な表示装置及びその駆動方法を提供する。

【解決手段】発光素子に直列に接続された薄膜トランジスタのオフを選択したときに、発光素子自体の容量に保持された電荷を放電する。発光素子と直列に接続された薄膜トランジスタにオフ電流が生じても、このオフ電流は発光素子自体の容量が再び所定の電圧を保持するまでこの容量を充電する。よって、薄膜トランジスタのオフ電流は発光に寄与しない。こうして、発光素子の微発光を低減することができる。

【選択図】図 1

## 【特許請求の範囲】

## 【請求項 1】

第1の薄膜トランジスタと第1の容量素子と発光素子とを有する画素と、第1の電源線と、第2の電源線とを有し、

前記第1の薄膜トランジスタのソース及びドレインの一方は、前記第1の電源線と接続され、他方は、前記発光素子の第1の電極及び前記第1の容量素子の一方の電極と接続され、

前記第1の容量素子の他方の電極は、前記第2の電源線に接続され、

前記発光素子の第2の電極は、前記第2の電源線に接続され、

前記第2の電源線の電位を変化させる手段を有することを特徴とする表示装置。 10

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、画素毎にスイッチング素子を設けたアクティブマトリクス駆動方式の表示装置及びその駆動方法に関する。特に、発光素子と直列に接続されたスイッチング素子を用いて、発光素子に流れる電流を制御し発光素子の輝度を制御する表示装置及びその駆動方法に関する。特に、発光素子としてダイオード特性を有する素子を用いた表示装置及びその駆動方法に関する。

## 【背景技術】

## 【0002】 20

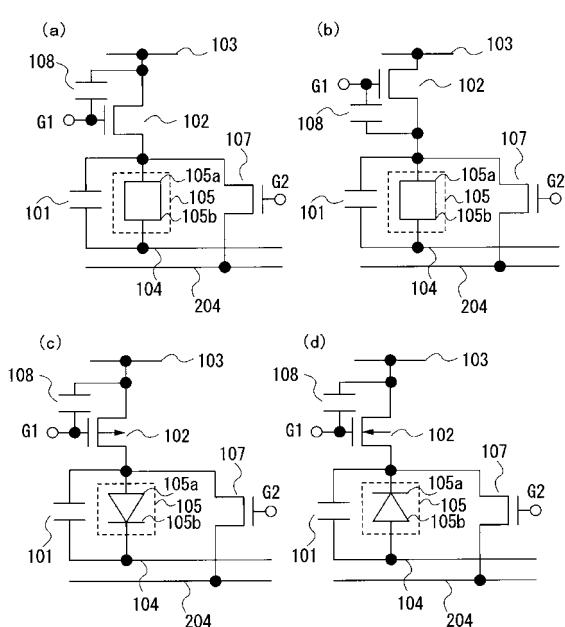

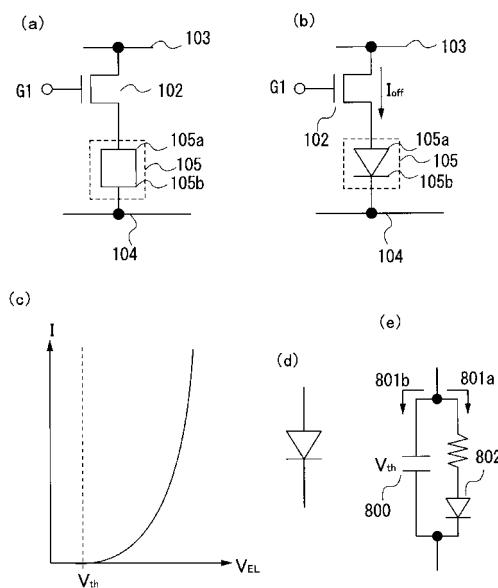

スイッチング素子として薄膜トランジスタを用いた表示装置及びその駆動方法が提案されている。図8(a)にその画素構成の一例を示す。

## 【0003】

図8(a)において、105は発光素子、102は薄膜トランジスタ、103は第1の電源線、104は第2の電源線である。発光素子105は、2つの電極を有し、2つの電極間に電流が流れると流れた電流値に応じた輝度で発光する素子である。発光素子105の2つの電極のうち一方を第1の電極105aで示し、他方を第2の電極105bで示す。図8(a)に示す画素では、薄膜トランジスタ102のゲートに与えられる電位G1に応じて、薄膜トランジスタ102のソースとドレインの間を流れる電流(以下、ドレン電流と表記する)の値が制御される。薄膜トランジスタ102のドレン電流は、薄膜トランジスタ102に直列に接続された発光素子105の第1の電極105aと第2の電極105bの間を流れる。発光素子は、流れる電流に応じた輝度で発光する。こうして、薄膜トランジスタ102のドレン電流を制御することによって、発光素子105の輝度を制御し表示を行う。 30

## 【0004】

発光素子105としてエレクトロルミネッセンス素子等を用いることができる。エレクトロルミネッセンス素子は、一方向のみに電流を流すダイオード特性を有する素子である。図8(a)の発光素子105をダイオードの表記としたものを図8(b)に示す。図8(b)では、第1の電極105aが陽極となり、第2の電極105bは陰極となっている。 40

## 【0005】

発光素子105に順バイアス電圧を印加し発光させるだけでなく、定期的に逆バイアス電圧を印加する表示装置及びその駆動方法が提案されている(特許文献1参照)。

## 【先行技術文献】

## 【特許文献】

## 【0006】

## 【特許文献1】特開2002-190390号公報

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】 50

図 8 ( b )において、発光素子 105 を発光させず「黒」を表示する場合を考える。電位 G1 を適当に定めることによって、薄膜トランジスタ 102 のソースとゲートの電位差を薄膜トランジスタ 102 のしきい値電圧以下にし、薄膜トランジスタ 102 をオフにする。こうして、薄膜トランジスタ 102 のドレイン電流をゼロにして、発光素子 105 を発光させず「黒」を表示する。しかし、ソースとゲートにしきい値電圧以下の電圧を印加したとき薄膜トランジスタ 102 が完全にオフすれば良いが、実際には完全にはオフにならざわざながらドレイン電流が流れる。この電流を図中  $I_{off}$  で示し以下オフ電流と表記する。オフ電流  $I_{off}$  によって、本来発光しないはずの発光素子が発光してしまう（以下、これを黒浮きと表記する）。そのため、表示のコントラストが悪くなるという問題がある。

10

#### 【0008】

特に、発光素子 105 を順バイアスで動作させ続けた場合、即ち、第 1 の電極 105a（陽極）の電位が第 2 の電極 105b（陰極）の電位よりも高くなるように動作させ続けた場合、黒浮きが顕著になるという問題を見出した。

#### 【0009】

発光素子 105 を順バイアスで動作させ続けた場合に黒浮きが顕著になるのは、第 1 の電極 105a と第 2 の電極 105b の間に常に発光素子 105 のしきい値電圧程度の電圧が保持されていることに原因があることを見出した。

#### 【0010】

発光素子のしきい値電圧とは、図 8 ( c )における  $V_{th}$  のことである。図 8 ( c )は、発光素子 105 において、陽極から陰極に流れる電流  $I$  と第 2 の電極 105b（陰極）の電位に対する第 1 の電極 105a（陽極）の電位の差  $V_{EL}$  との関係を示す。 $V_{EL}$  がしきい値電圧  $V_{th}$  より大きくなると電流  $I$  が流れる。即ち、発光素子 105 は、しきい値電圧  $V_{th}$  より大きな電圧が第 1 の電極 105a（陽極）と第 2 の電極 105b（陰極）の間に印加されると電流が流れ、発光する。

20

#### 【0011】

発光素子 105 の第 1 の電極 105a（陽極）と第 2 の電極 105b（陰極）の間にしきい値電圧  $V_{th}$  程度の電圧が保持されるのは、発光素子 105 自体が有する容量の効果である。図 8 ( d )に、ダイオードの表記とした発光素子を示し、図 8 ( e )に図 8 ( d )の等価回路図を示す。図中等価回路の容量 800 が発光素子 105 自体が有する容量に相当する。容量 800 によってしきい値電圧  $V_{th}$  が保持される。

30

#### 【0012】

発光素子 105 を順バイアスで動作させ続けた場合、薄膜トランジスタ 102 をオフしても第 1 の電極 105a（陽極）が第 2 の電極 105b（陰極）の電位より高い状態が続き、発光素子 105 自体の容量 800 には常にしきい値電圧  $V_{th}$  程度の電圧を保持される状態となる。そのため、薄膜トランジスタ 102 にオフ電流  $I_{off}$  が生じると、オフ電流  $I_{off}$  は、図 8 ( e )の等価回路の容量 800 の側の経路 801b ではなく、ダイオード 802 の側の経路 801a に流れて発光に寄与する。こうして、発光素子 105 を順バイアスで動作させ続けた場合、黒浮きの問題が顕著となることを本発明者らは見出した。

40

#### 【0013】

本発明は、上記の黒浮きを低減し表示のコントラストを上げて、明瞭な表示が可能な表示装置及びその駆動方法を提供することを課題とする。

#### 【課題を解決するための手段】

#### 【0014】

黒浮きを低減するため、本発明の表示装置及びその駆動方法は下記の第 1 の手段または第 2 の手段を用いる。

#### 【0015】

#### [第 1 の手段]

発光素子の第 1 の電極を陽極とし第 2 の電極を陰極とした場合には、発光素子と直列に接続された第 1 の薄膜トランジスタのオフを選択したとき、第 1 の電極の電位が第 2 の電

50

極の電位以上であり、且つ第1の電極と第2の電極間に印加される電圧が発光素子のしきい値電圧より小さくなるように、第2の電源線の電位を設定する。

#### 【0016】

発光素子の第1の電極を陰極とし第2の電極を陽極とした場合には、発光素子と直列に接続された第1の薄膜トランジスタのオフを選択したとき、第1の電極の電位が第2の電極の電位以下であり、且つ第1の電極と第2の電極間に印加される電圧が発光素子のしきい値電圧より小さくなるように、第2の電源線の電位を設定する。

#### 【0017】

##### [第2の手段]

発光素子の第1の電極を陽極とし第2の電極を陰極とした場合には、発光素子と直列に接続された第1の薄膜トランジスタとは別の第2の薄膜トランジスタを設ける。第2の薄膜トランジスタのソース及びドレインの一方は、発光素子の第1の電極に接続され、他方は、電源線に接続する。第1の薄膜トランジスタのオフを選択したとき、第2の薄膜トランジスタのオンを選択し、且つ当該電源線の電位を発光素子の第2の電極の電位以上とし、当該第2の電極の電位に発光素子のしきい値電圧をたした電位よりも低くする。

10

#### 【0018】

発光素子の第1の電極を陰極とし第2の電極を陽極とした場合には、発光素子と直列に接続された第1の薄膜トランジスタとは別の第2の薄膜トランジスタを設ける。第2の薄膜トランジスタのソース及びドレインの一方は、発光素子の第1の電極に接続され、他方は、電源線に接続する。第1の薄膜トランジスタのオフを選択したとき、第2の薄膜トランジスタのオンを選択し、且つ当該電源線の電位を発光素子の第2の電極の電位以下、当該第2の電極の電位から発光素子のしきい値電圧を引いた電位よりも高くする。

20

#### 【0019】

なお、第2の薄膜トランジスタが接続される電源線は、発光素子の第2の電極が接続される電源線と共に用することもできる。

#### 【0020】

また、第1の手段、第2の手段において、第1の薄膜トランジスタとして活性層が多結晶半導体でなる薄膜トランジスタを用いることができる。

30

#### 【0021】

上記第1の手段または第2の手段において、次の第3の手段を組み合わせることができる。

##### [第3の手段]

発光素子と並列に接続された容量素子を設ける。

即ち、一方の電極が発光素子の第1の電極と接続され、他方の電極が発光素子の第2の電極と接続されるように容量素子を設ける。

#### 【発明の効果】

#### 【0022】

本発明の表示装置及びその駆動方法は、発光素子に直列に接続された薄膜トランジスタのオフを選択し発光素子の非発光を選択するときに、発光素子自体の容量に保持されたしきい値電圧に相当する電荷を放電することができる。そのため、発光素子と直列に接続された薄膜トランジスタにオフ電流が生じても、このオフ電流は発光素子自体の容量が再びしきい値電圧を保持するまで発光素子自体の容量を充電するために流れ。そのため、発光素子に直列に接続された薄膜トランジスタのオフを選択した後、薄膜トランジスタのオフ電流はしばらく発光に寄与しない。こうして、黒浮きを低減することができる。そのため、本発明の表示装置及びその駆動方法は、表示のコントラストを上げて明瞭な表示が可能である。

40

#### 【0023】

第1の手段及び第2の手段では、発光素子に直列に接続された薄膜トランジスタのオフを選択し発光素子の非発光を選択するときに、発光素子の電極間に印加される電圧を順バイアスとし、且つその電圧を発光素子のしきい値電圧より小さくする。第1の手段及び第

50

2の手段両方において、発光素子に逆バイアス電圧は印加しない。そのため、定期的に発光素子に逆バイアス電圧を印加する手法と比較して、本発明の表示装置及びその駆動方法は消費電力を低減することができる。

#### 【0024】

また、第2の手段において、第2の薄膜トランジスタが接続される電源線は、発光素子の第2の電極が接続される電源線と共に用することによって、配線数を減らし、画素の開口率を向上させることができる。

#### 【0025】

活性層が単結晶半導体や非晶質半導体でなる薄膜トランジスタと比較して、活性層が多結晶半導体でなる薄膜トランジスタでは結晶粒界等の影響によりオフ電流は大きくなる。よって本発明は、第1の薄膜トランジスタとして活性層が多結晶半導体でなる薄膜トランジスタを用いる場合に特に有効である。

10

#### 【0026】

第1の手段または第2の手段において第3の手段を組み合わせることによって、発光素子に直列に接続された薄膜トランジスタのオフ電流は新たに設けられた容量素子を充電するまで当該容量素子に流れる。そのため、発光素子に直列に接続された薄膜トランジスタのオフを選択した後、当該薄膜トランジスタのオフ電流が発光に寄与するまでの時間を長くすることができる。こうして、黒浮きを更に低減することができる。

20

#### 【0027】

以上のとおり、本発明を用いることにより、表示のコントラストを上げて明瞭な表示が可能、且つ消費電力が少ない表示装置及びその駆動方法を提供することができる。

20

#### 【発明を実施するための形態】

#### 【0028】

##### (第1の実施の形態)

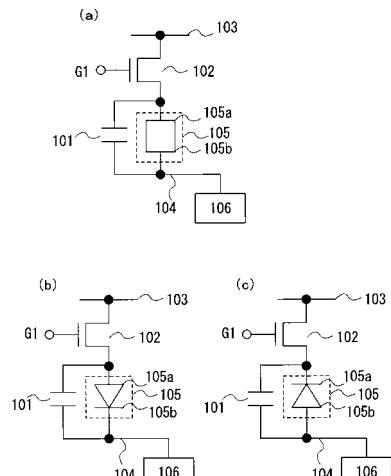

第1の手段と第3の手段を組み合わせた例について、図1を用いて説明する。図1において、105は発光素子、102は薄膜トランジスタ、103は第1の電源線、104は第2の電源線、101は容量素子、106は電位を設定する手段である。電位を設定する手段106が第1の手段に対応する。容量素子101が第3の手段に対応する。発光素子105は、2つの電極を有し、2つの電極間に電流が流れると流れた電流値に応じた輝度で発光する素子である。発光素子105の2つの電極のうち一方を第1の電極105aで示し、他方を第2の電極105bで示す。

30

#### 【0029】

図1(a)を用いて、第1の手段と第3の手段を組み合わせる例について詳述する。

#### 【0030】

発光素子105に直列に接続された薄膜トランジスタ102のオフを選択したときに、電位を設定する手段106は、発光素子105の電極間に印加される電圧を順バイアスとし、且つその電圧を発光素子105のしきい値電圧より小さくするように、第2の電源線104の電位を変化させる。こうして、発光素子105自体の容量に保持された電荷を放電し、発光素子105の微発光を低減することができる。

40

#### 【0031】

発光素子105に直列に接続された薄膜トランジスタ102のオンを選択したときに、電位を設定する手段106は、発光素子105の電極間に印加される電圧を順バイアスとし、且つその電圧を発光素子105のしきい値電圧以上とするように、第2の電源線104の電位を変化させる。ゲートに与えられる電位G1に応じて流れる薄膜トランジスタ102のドレイン電流は、発光素子105に流れる。発光素子105は当該ドレイン電流に応じた輝度で発光する。こうして、発光素子105の輝度を制御し表示を行う。

#### 【0032】

電位を設定する手段106は、例えば、異なる電位が与えられる2つの端子(第1の端子、第2の端子という)とスイッチとを有する構成の回路とすることができる。当該スイッチは、当該第1の端子と第2の電源線104との接続、または当該第2の端子と第2の

50

電源線 104との接続を選択する。薄膜トランジスタ102のオフを選択したときに当該スイッチは当該第1の端子と第2の電源線104との接続を選択し、薄膜トランジスタ102のオンを選択したときに当該スイッチは当該第2の端子と第2の電源線104との接続を選択する。第1の端子には、第1の電源線103に与えられる電位との関係において、発光素子105の電極間に印加される電圧を順バイアスとし、且つその電圧を発光素子105のしきい値電圧より小さくするような電位が与えられている。また、第2の端子には、第1の電源線103に与えられる電位との関係において、発光素子105の電極間に印加される電圧を順バイアスとし、且つその電圧を発光素子105のしきい値電圧以上とするような電位が与えられている。

## 【0033】

10

1フレーム期間内に発光素子105が発光した時間を制御することで階調を表現することもできる。

## 【0034】

容量素子101は、一方の電極が第1の電極105aと接続され、他方の電極が第2の電極105bと接続されている。即ち、発光素子105と並列に容量素子101が接続されている。発光素子105に直列に接続された薄膜トランジスタ102のオフ電流は新たに設けられた容量素子101を充電するまで容量素子101に流れる。そのため、発光素子105に直列に接続された薄膜トランジスタ102がオフした後、薄膜トランジスタ102のオフ電流が発光に寄与するまでの時間を長くすることができる。こうして、黒浮きを更に低減することができる。

20

## 【0035】

発光素子105としてエレクトロルミネッセンス素子等を用いることができる。エレクトロルミネッセンス素子は、一方向のみに電流を流すダイオード特性を有する素子である。図1(a)の発光素子105をダイオードの表記としたものを図1(b)及び図1(c)に示す。図1(b)では、第1の電極105aが陽極となり、第2の電極105bは陰極となっている。図1(c)では、第1の電極105aが陰極となり、第2の電極105bは陽極となっている。

## 【0036】

30

図1(b)における電位を設定する手段106について説明する。

## 【0037】

薄膜トランジスタ102のオンを選択したときには、第1の電極105aの電位が第2の電極105bの電位より高く、且つ第1の電極105aと第2の電極105b間に印加される電圧が発光素子105のしきい値電圧より大きくなるように、第2の電源線104の電位を設定して発光素子105を発光させる。

## 【0038】

薄膜トランジスタ102のオフを選択したときには、第1の電極105aの電位が第2の電極105bの電位以上であり、且つ第1の電極105aと第2の電極105b間に印加される電圧が発光素子105のしきい値電圧より小さくなるように、第2の電源線104の電位を設定して発光素子105を発光させない。

## 【0039】

40

図1(c)における電位を設定する手段106について説明する。

## 【0040】

薄膜トランジスタ102のオンを選択したときには、第1の電極105aの電位が第2の電極105bの電位より低く、且つ第1の電極105aと第2の電極105b間に印加される電圧が発光素子105のしきい値電圧より大きくなるように、第2の電源線104の電位を設定して発光素子105を発光させる。

## 【0041】

薄膜トランジスタ102のオフを選択したときには、第1の電極105aの電位が第2の電極105bの電位以下であり、且つ第1の電極105aと第2の電極105b間に印加される電圧が発光素子105のしきい値電圧より小さくなるように、第2の電源線104

50

4の電位を設定して発光素子105を発光させない。

【0042】

(第2の実施の形態)

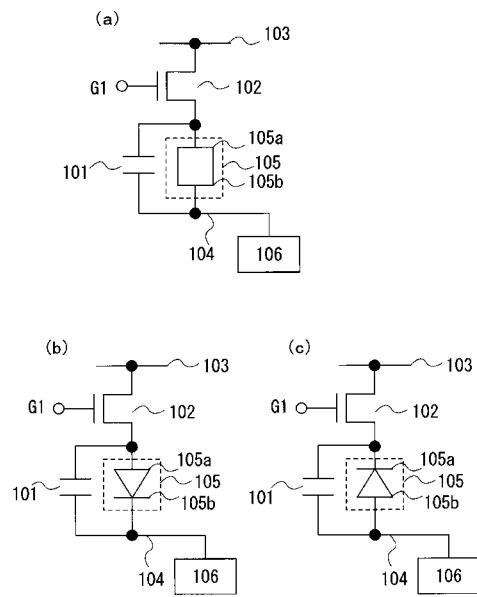

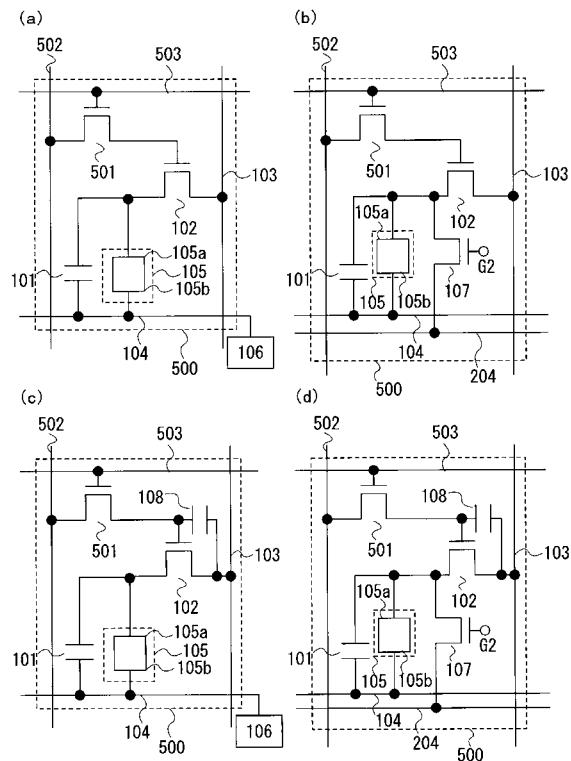

第2の手段と第3の手段を組み合わせた例について、図2を用いて説明する。図2において、図1と同じ部分は同じ符号を用いて示し、説明は省略する。107は薄膜トランジスタである。薄膜トランジスタ107及び第3の電源線204が第2の手段に対応する。容量素子101が第3の手段に対応する。

【0043】

図2(a)を用いて、第2の手段と第3の手段を組み合わせる例について詳述する。

【0044】

発光素子105に直列に接続された薄膜トランジスタ102のオフを選択したときに、ゲートに与えられる電位G2を制御することによって薄膜トランジスタ107のオンを選択する。こうして、第1の電極105aに第3の電源線204の電位が与えられる。薄膜トランジスタ107のオンを選択したとき、第2の電源線104と第3の電源線204との電位差は、ゼロ以上、発光素子105のしきい値電圧よりも低くなるよう設定されている。こうして、発光素子105自体の容量に保持された電荷を放電し、発光素子105の微発光を低減することができる。

【0045】

第2の電源線104と第3の電源線204を共用することもできる。こうして、配線数を減らして画素の開口率を向上させることができる。

【0046】

発光素子105に直列に接続された薄膜トランジスタ102のオンが選択されたときに、ゲートに与えられる電位G2を制御することによって薄膜トランジスタ107のオフを選択する。ゲートに与えられる電位G1に応じて流れる薄膜トランジスタ102のドレイン電流は、発光素子105に流れる。発光素子105は当該ドレイン電流に応じた輝度で発光する。こうして、発光素子105の輝度を制御し表示を行う。

【0047】

1フレーム期間内に発光素子105が発光した時間を制御することで階調を表現することができる。

【0048】

容量素子101を設けることによって、発光素子105に直列に接続された薄膜トランジスタ102のオフを選択した後、薄膜トランジスタ102のオフ電流が発光に寄与するまでの時間を長くすることができる。こうして、黒浮きを更に低減することができる。

【0049】

発光素子105としてエレクトロルミネッセンス素子等を用いることができる。エレクトロルミネッセンス素子は、一方向のみに電流を流すダイオード特性を有する素子である。図2(a)の発光素子105をダイオードの表記としたものを図2(b)及び図2(c)に示す。図2(b)では、第1の電極105aが陽極となり、第2の電極105bは陰極となっている。図2(c)では、第1の電極105aが陰極となり、第2の電極105bは陽極となっている。

【0050】

(第3の実施の形態)

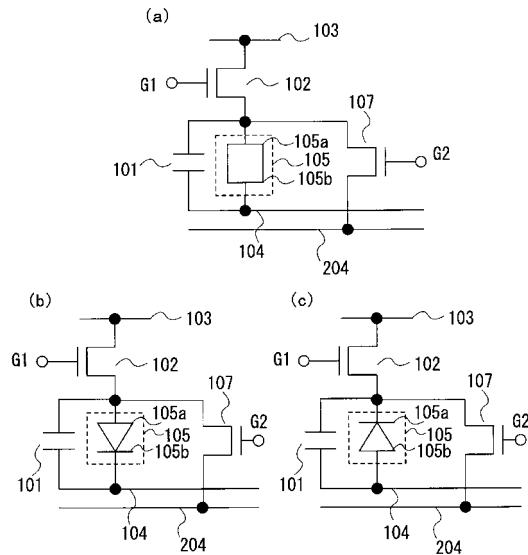

第1の手段と第3の手段を組み合わせた例について、図3を用いて説明する。図3において、図1と同じ部分は同じ符号を用いて示し説明は省略する。

【0051】

図3(a)及び図3(b)は、図1(a)において容量素子108を設けたものである。容量素子108は、薄膜トランジスタ102のゲートとソース間の電圧を保持するように設けられる。図3(a)は、第1の電源線103と接続された側が薄膜トランジスタ102のソースとなっている例である。図3(b)は、発光素子105の第1の電極105aと接続された側が薄膜トランジスタ102のソースとなっている例である。

10

20

30

40

50

## 【0052】

薄膜トランジスタ102のドレイン電流は、薄膜トランジスタ102のソースの電位に対するゲートの電位G1の電位差によって変化する。薄膜トランジスタのゲートの電位G1を制御してもソースの電位が変動すると、ソースの電位に対するゲートの電位の電位差が変化しドレイン電流が変化してしまう。そのため、薄膜トランジスタ102のソースを一定の電位に保つのが好ましい。よって、図3(a)のように、第1の電源線103と接続された側が薄膜トランジスタ102のソースとなっているのが好ましい。

## 【0053】

図3(c)及び図3(d)は、図3(a)において発光素子105をダイオードの表記としたものである。図3(c)では、第1の電極105aが陽極となり、第2の電極105bは陰極となっている。図3(d)では、第1の電極105aが陰極となり、第2の電極105bは陽極となっている。

10

## 【0054】

図3(c)では、第1の電源線103から第2の電源線104の方向に電流が流れ、発光素子105は発光する。薄膜トランジスタ102の第1の電源線103に接続された側の電位は、発光素子105の第1の電極105aに接続された側の電位より大きくなる。薄膜トランジスタ102のソースを第1の電源線103に接続された側とするために、薄膜トランジスタ102をPチャネル型とする。

20

## 【0055】

図3(d)では、第2の電源線104から第1の電源線103の方向に電流が流れ、発光素子105は発光する。薄膜トランジスタ102において、発光素子105の第1の電極105aに接続された側の電位は、第1の電源線103に接続された側の電位より大きくなる。薄膜トランジスタ102のソースを第1の電源線103に接続された側とするために、薄膜トランジスタ102をNチャネル型とする。

30

## 【0056】

## (第4の実施の形態)

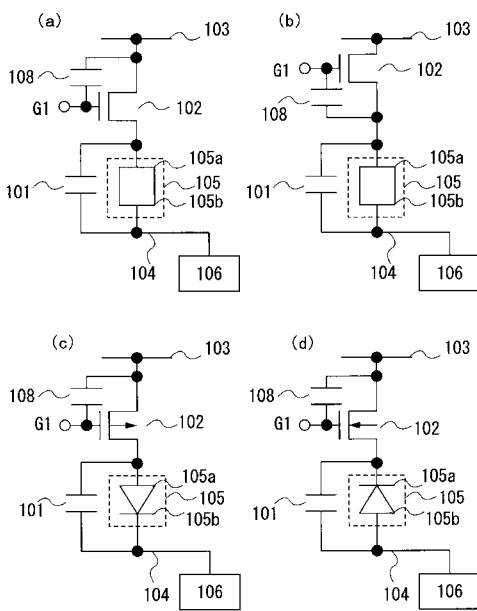

第2の手段と第3の手段を組み合わせた例について、図4を用いて説明する。図4において、図2や図3と同じ部分は同じ符号を用いて示し説明は省略する。

## 【0057】

図4(a)及び図4(b)は、図2(a)において容量素子108を設けたものである。容量素子108は、薄膜トランジスタ102のゲートとソース間の電圧を保持するように設けられる。図4(a)は、第1の電源線103と接続された側が薄膜トランジスタ102のソースとなっている例である。図4(b)は、発光素子105の第1の電極105aと接続された側が薄膜トランジスタ102のソースとなっている例である。

30

## 【0058】

図4(a)では、図3(a)と同様に第1の電源線103と接続された側が薄膜トランジスタ102のソースとなっているので好ましい。

## 【0059】

図4(c)及び図4(d)は、図4(a)において発光素子105をダイオードの表記としたものである。図4(c)では、第1の電極105aが陽極となり、第2の電極105bは陰極となっている。図4(d)では、第1の電極105aが陰極となり、第2の電極105bは陽極となっている。

40

## 【0060】

図4(c)では、薄膜トランジスタ102のソースを第1の電源線103に接続された側とするため、薄膜トランジスタ102をPチャネル型とする。図4(d)では、薄膜トランジスタ102のソースを第1の電源線103に接続された側とするため、薄膜トランジスタ102をNチャネル型となる。

## 【実施例1】

## 【0061】

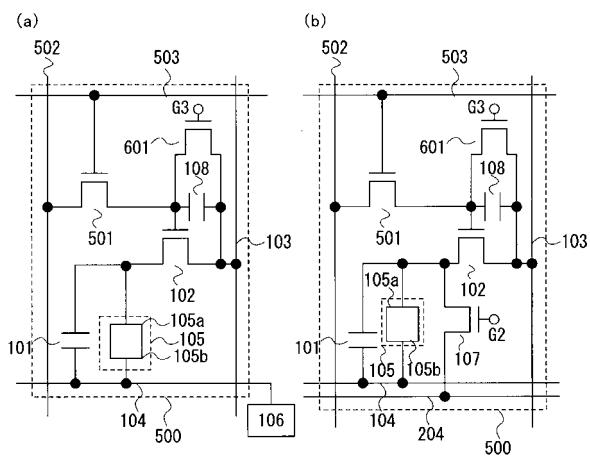

発明を実施するための最良の形態に示した構成を用いた画素の具体例について、図5を

50

用いて説明する。図5において、図1乃至図4と同じ部分は同じ符号を用いて示し説明は省略する。

#### 【0062】

図5(a)は、図1(a)の構成において、薄膜トランジスタ102のゲートに電位G1を入力する手段の具体例を示した図である。図5(b)は、図2(a)の構成において、薄膜トランジスタ102のゲートに電位G1を入力する手段の具体例を示した図である。図5(c)は、図3(a)の構成において、薄膜トランジスタ102のゲートに電位G1を入力する手段の具体例を示した図である。図5(d)は、図4(a)の構成において、薄膜トランジスタ102のゲートに電位G1を入力する手段の具体例を示した図である。

10

#### 【0063】

図5(a)乃至図5(d)において、500は画素、501は薄膜トランジスタ、502は信号線、503は走査線である。薄膜トランジスタ501のソース及びドレインの一方は信号線502に接続され、他方は薄膜トランジスタ102のゲートに接続されている。薄膜トランジスタ501のゲートは走査線503に接続されている。

#### 【0064】

図5(a)乃至図5(d)に示す画素500の構成では、走査線503に入力された信号により薄膜トランジスタ501のオンが選択されると、信号線502に入力された信号が薄膜トランジスタ102のゲートに入力される。こうして、薄膜トランジスタ102のオンとオフや、オンとなったときのドレイン電流の値を制御する。

20

#### 【0065】

図5(a)において、薄膜トランジスタ102のオンを選択した場合とオフを選択した場合それぞれにおける、電位を設定する手段106の動作については、第1の実施の形態と同様である。図5(b)において、薄膜トランジスタ102のオンを選択した場合とオフを選択した場合それぞれにおける、薄膜トランジスタ107の動作については、第2の実施の形態と同様である。図5(c)において、薄膜トランジスタ102のオンを選択した場合とオフを選択した場合それぞれにおける、電位を設定する手段106の動作については、第3の実施の形態と同様である。図5(d)において、薄膜トランジスタ102のオンを選択した場合とオフを選択した場合それぞれにおける、薄膜トランジスタ107の動作については、第4の実施の形態と同様である。

30

#### 【0066】

実施例1は、発明を実施するための最良の形態と自由に組み合わせることができる。

#### 【実施例2】

#### 【0067】

実施例1に示した画素の例とは別の例について、図6を用いて説明する。図6において、図1乃至図5と同じ部分は同じ符号を用いて示し説明は省略する。

#### 【0068】

図6(a)は、図5(c)の構成において、信号線502の信号に因らず薄膜トランジスタ102のオフを選択する手段を設けたものである。図6(b)は、図5(d)の構成において、信号線502の信号に因らず薄膜トランジスタ102のオフを選択する手段を設けたものである。

40

#### 【0069】

図6(a)及び図6(b)において、601は薄膜トランジスタである。薄膜トランジスタ601のソース及びドレインの一方は容量素子108の一方の電極に接続され、他方は容量素子108の他方の電極に接続されている。

#### 【0070】

図6(a)及び図6(b)に示す構成では、ゲートに入力される電位G3によって薄膜トランジスタ601のオンを選択し、容量素子108の2つの電極を概略等電位をする。容量素子108に保持された電荷は放電し、薄膜トランジスタ102のソースとゲート間の電位差を概略ゼロとなる。こうして、薄膜トランジスタ102のオフを選択する。

50

## 【0071】

本発明の第2の手段では、発光素子105と直列に接続された薄膜トランジスタ102のオフを選択したときに、薄膜トランジスタ107のオンを選択する。よって、図6(b)における薄膜トランジスタ601のオンを選択するタイミングと、薄膜トランジスタ107のオンを選択するタイミングとを同じとすることができる。そのため、薄膜トランジスタ107と薄膜トランジスタ601の極性を同じとし、薄膜トランジスタ107のゲートと薄膜トランジスタ601のゲートを同じ配線に接続し、同時に信号を入力して駆動することができる。薄膜トランジスタ107のゲートに信号を入力する配線と、薄膜トランジスタ601のゲートに信号を入力する配線とを共有することができるので、画素の開口率を向上させることができる。

10

## 【0072】

本実施例は、発明を実施するための最良の形態と自由に組み合わせて実施することができる。

## 【実施例3】

## 【0073】

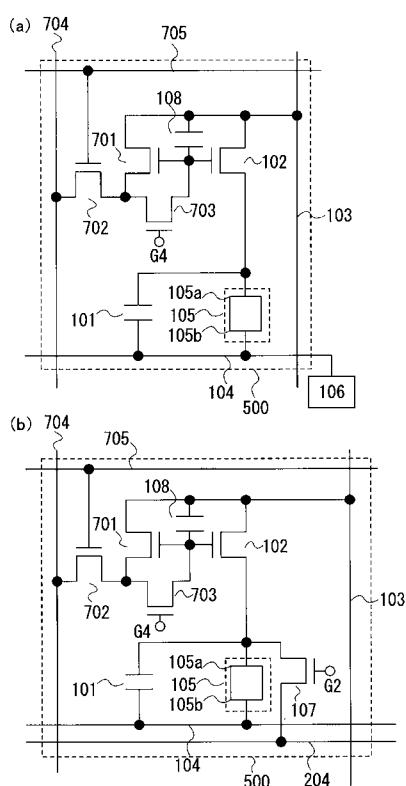

実施例1や実施例2に示した画素の例とは別の例について、図7を用いて説明する。図7において、図1乃至図6と同じ部分は同じ符号を用いて示し説明は省略する。

20

## 【0074】

図7(a)は、図3(a)の構成において、薄膜トランジスタ102のゲートに電位G1を入力する手段の具体例を示した図である。図7(b)は、図4(a)の構成において、薄膜トランジスタ102のゲートに電位G1を入力する手段の具体例を示した図である。

20

## 【0075】

図7(a)及び図7(b)において、701、702及び703は薄膜トランジスタ、704は信号線、705は走査線である。薄膜トランジスタ702のソース及びドレインの一方は信号線704に接続され、他方は薄膜トランジスタ701のソース及びドレインの一方及び薄膜トランジスタ703のソース及びドレインの一方に接続されている。薄膜トランジスタ702のゲートは走査線705に接続されている。薄膜トランジスタ701のソース及びドレインの他方は、第1の電源線103に接続されている。薄膜トランジスタ703のソース及びドレインの他方は、薄膜トランジスタ102のゲートに接続されている。薄膜トランジスタ701のゲートは、薄膜トランジスタ102のゲートと接続されている。

30

## 【0076】

なお図7では、薄膜トランジスタ703は、薄膜トランジスタ102のゲートと薄膜トランジスタ701のソース及びドレインの一方とをむすぶ経路上に設けられているが、別の位置に設けることができる。例えば、薄膜トランジスタ701のゲートと第2の容量素子108を結ぶ経路上に設けることができる。

30

## 【0077】

図7(a)及び図7(b)に示す構成では、走査線705に入力された信号により薄膜トランジスタ702のオンを選択し、更にゲートに入力される電位G4によって薄膜トランジスタ703のオンを選択すると、信号線704に入力された信号に対応する電圧が容量素子108に保持される。こうして、薄膜トランジスタ102のオンとオフや、オンとなつたときのドレイン電流の値を制御する。

40

## 【0078】

図7(a)及び図7(b)に示す構成の画素の動作を更に説明する。信号線704には所定の電流値の電流(以下、信号電流と表記する。)が入力される。薄膜トランジスタ702及び薄膜トランジスタ703のオンを選択すると、信号電流は薄膜トランジスタ702及び薄膜トランジスタ703を介して流れ、容量素子108を充電する。こうして、薄膜トランジスタ701が当該信号電流と等しいドレイン電流を流すように、容量素子108に電圧(以下、信号電流に対応する電圧と表記する。)が保持される。薄膜トランジス

50

タ701のゲートとソース間の電位差と薄膜トランジスタ102のゲートとソース間の電位差とは等しい。薄膜トランジスタ701と薄膜トランジスタ102は、同極性で、チャネル幅とチャネル長との比がほぼ等しく、且つ特性がほぼ等しいとすると、薄膜トランジスタ102には信号電流とほぼ等しいドレイン電流が流れる。こうして、発光素子105に流れる電流を制御し表示を行う。

#### 【0079】

薄膜トランジスタ702のオフが選択され、信号線から画素に信号電流が入力されなくなった後も、容量素子108には信号電流に対応する電圧が保持されている。よって、信号線から画素に信号電流が入力されなくなった後も、薄膜トランジスタ102には信号電流とほぼ等しいドレイン電流が流れる。なお、薄膜トランジスタ702のオフを選択する前または同時に薄膜トランジスタ703のオフを選択するのが好ましい。それは、薄膜トランジスタ703がオンしたまま薄膜トランジスタ702をオフすると、容量素子108に保持された電荷が放電され信号電流に対応する電圧を保持できなくなるためである。

10

#### 【0080】

薄膜トランジスタ702と薄膜トランジスタ703は同時にオン、オフを選択することができる。よって、薄膜トランジスタ702と薄膜トランジスタ703と同じ極性とし、薄膜トランジスタ703のゲートを走査線705に接続することができる。薄膜トランジスタ702のゲートに信号を入力する配線と、薄膜トランジスタ703のゲートに信号を入力する配線とを共有することができるので、画素の開口率を向上させることができる。

20

#### 【0081】

図7(a)において、薄膜トランジスタ102のオンを選択した場合とオフを選択した場合それぞれにおける、電位を設定する手段106の動作については、第3の実施の形態と同様である。図7(b)において、薄膜トランジスタ102がオンを選択した場合とオフを選択した場合それぞれにおける、薄膜トランジスタ107の動作については、第4の実施の形態と同様である。

#### 【0082】

実施例3は、発明を実施するための最良の形態と自由に組み合わせて実施することができる。

#### 【実施例4】

#### 【0083】

30

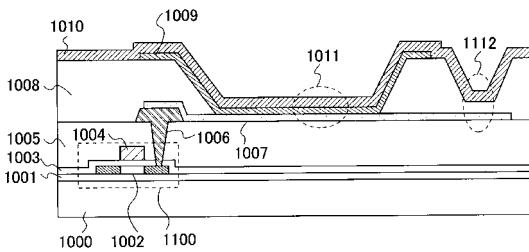

画素の構成の具体例を示す。図10は、本発明の画素の構成を示す断面図である。1000は基板、1001は下地膜、1002は半導体層、1003は第1の絶縁膜、1004はゲート電極、1005は第2の絶縁膜、1006は電極、1007は第1の電極、1008は第3の絶縁膜、1009は発光層、1010は第2の電極である。1100は薄膜トランジスタ、1011は発光素子、1012は容量素子である。

#### 【0084】

基板1000としては、例えばバリウムホウケイ酸ガラスや、アルミノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレスを含む金属基板または半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板を用いても良い。基板1000の表面を、CMP法などの研磨により平坦化しておいても良い。

40

#### 【0085】

下地膜1001としては、酸化珪素や、窒化珪素または窒化酸化珪素などの絶縁膜を用いることができる。下地膜1001によって、基板1000に含まれるNaなどのアルカリ金属やアルカリ土類金属が半導体層1002に拡散し薄膜トランジスタ1100の特性に悪影響をおよぼすのを防ぐことができる。図10では、下地膜1001を単層の構造としているが、2層あるいはそれ以上の複数層で形成してもよい。なお、石英基板など不純物の拡散がさして問題とならない場合は、下地膜1001を必ずしも設ける必要はない。

#### 【0086】

半導体層1002としては、結晶性半導体膜や非晶質半導体膜を用いることができる。

50

結晶性半導体膜は非晶質半導体膜を結晶化して得ることができる。結晶化方法としては、レーザ結晶化法、R T A又はファーネスアーニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法等を用いることができる。半導体層1002は、チャネル形成領域と、導電型を付与する不純物元素が添加された一対の不純物領域とを有する。なお、チャネル形成領域と一対の不純物領域との間に、前記不純物元素が低濃度で添加された不純物領域を有していてもよい。

#### 【0087】

第1の絶縁膜1003としては、酸化珪素、窒化珪素または窒化酸化珪素等を用い、単層または複数の膜を積層させて形成することができる。

#### 【0088】

ゲート電極1004としては、Ta、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた一種の元素または該元素を複数含む合金若しくは化合物からなる単層または積層構造を用いることができる。例えば、ゲート電極1004として、窒化タンタルとWの積層を用いることができる。導電型を付与する不純物元素を添加した多結晶珪素膜に代表される半導体膜を用いてもよい。

#### 【0089】

薄膜トランジスタ1100は、半導体層1002と、ゲート電極1004と、半導体層1002とゲート電極1004との間の第1の絶縁膜1003とによって構成される。図10では、画素を構成する薄膜トランジスタとして、発光素子1011の第1の電極1007に接続された薄膜トランジスタ1100のみを示したが、複数の薄膜トランジスタを有する構成としてもよい。また、本実施例では、薄膜トランジスタ1100をトップゲート型のトランジスタとして示したが、半導体層の下方にゲート電極を有するボトムゲート型のトランジスタであっても良いし、半導体層の上下にゲート電極を有するデュアルゲート型のトランジスタであっても良い。

#### 【0090】

第2の絶縁膜1005としては、無機絶縁膜や有機絶縁膜の単層または積層を用いることができる。無機絶縁膜としては、CVD法により形成された酸化シリコン膜や、SOG(Spin On Glass)法により塗布された酸化シリコン膜などを用いることができ、有機絶縁膜としてはポリイミド、ポリアミド、BCB(ベンゾシクロブテン)、アクリルまたはポジ型感光性有機樹脂、ネガ型感光性有機樹脂等の膜を用いることができる。

#### 【0091】

また、第2の絶縁膜1005として、珪素(Si)と酸素(O)との結合で骨格構造が構成される材料を用いることもできる。この材料の置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

#### 【0092】

電極1006としては、Al、Ni、C、W、Mo、Ti、Pt、Cu、Ta、Au、Mnから選ばれた一種の元素または該元素を複数含む合金からなる単層または積層構造を用いることができる。例えば、電極1006としてAlとTiが積層されたTi/Al/Tiからなる金属膜を用いることができる。また、第2の絶縁膜1005上に形成された電極1006の端部をテーパー状にしてもよい。電極1006の端部をテーパー状にすると、その上に形成される膜の段切れを防止しできる。

#### 【0093】

第1の電極1007及び第2の電極1010の一方もしくは両方を透明電極とすることができます。透明電極としては、酸化インジウムスズ(ITO)、酸化亜鉛(ZnO)、酸化インジウム亜鉛(IZO)、ガリウムを添加した酸化亜鉛(GZO)などその他の透光性酸化物導電材料を用いることができる。ITO及び酸化珪素を含む酸化インジウムスズ(以下、ITSOと記す)や、ITO及び酸化チタン含む酸化インジウムスズ(以下、I

10

20

30

40

50

TTOと記す)や、ITO及び酸化モリブデン含む酸化インジウムスズ(以下、ITMOと記す)や、ITOにチタン、モリブデン又はガリウムを添加したものや、酸化珪素を含んだ酸化インジウムにさらに2~20 atomic%の酸化亜鉛(ZnO)を添加したものを用いても良い。

#### 【0094】

第1の電極1007及び第2の電極1010の他方は、透光性を有さない材料で形成されてもよい。例えば、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、これらを含む合金(Mg:Ag、Al:Li、Mg:Inなど)、およびこれらの化合物(CaF<sub>2</sub>、窒化カルシウム)の他、YbやEr等の希土類金属を用いることができる。

10

#### 【0095】

第3の絶縁膜1008としては、第2の絶縁膜1005と同様の材料を用いて形成することができる。第3の絶縁膜1008は、第1の電極1007の端部を覆うように第1の電極1007の周辺に形成され、隣り合う画素において発光層1009を分離する隔壁として機能する。

#### 【0096】

発光層1009は、単数または複数の層で構成されている。複数の層で構成されている場合、これらの層は、キャリア輸送特性の観点から正孔注入層、正孔輸送層、発光層、電子輸送層、電子注入層などに分類することができる。なお各層の境目は必ずしも明確である必要はなく、互いの層を構成している材料が一部混合し、界面が不明瞭になっている場合もある。各層には、有機系の材料、無機系の材料を用いることが可能である。有機系の材料として、高分子系、中分子系、低分子系のいずれの材料も用いることが可能である。なお中分子系の材料とは、構造単位の繰返しの数(重合度)が2から20程度の低重合体に相当する。

20

#### 【0097】

発光素子1011は、発光層1009と、発光層1009を介して重なる第1の電極1007及び第2の電極1010とによって構成される。第1の電極1007及び第2の電極1010の一方が陽極に相当し、他方が陰極に相当する。発光素子1011は、陽極と陰極の間にしきい値電圧より大きい電圧が順バイアスで印加されると、陽極から陰極に電流が流れて発光する。

30

#### 【0098】

容量素子1012は、第3の絶縁膜1008と、第3の絶縁膜1008を介して重なる第1の電極1007及び第2の電極1010によって構成される。容量素子1012が、本発明の第3の手段の容量素子、即ち、発明を実施する最良の形態や実施例1乃至実施例3における容量素子101に相当する。

#### 【0099】

本実施例は、発明を実施する最良の形態や、実施例1乃至実施例3と自由に組み合わせて実施することができる。

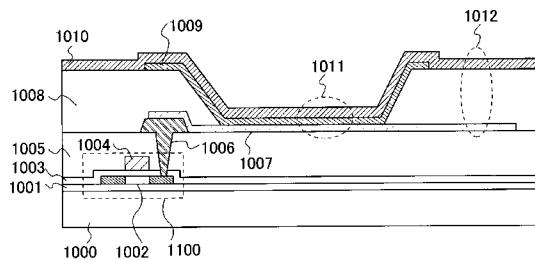

#### 【実施例5】

#### 【0100】

実施例4とは別の構成の画素の具体例を示す。図11は、本発明の画素の構成を示す断面図である。なお、図10と同じ部分は同じ符号を用いて示し、説明は省略する。

40

#### 【0101】

図11の構成では、第1の電極1007と重なる部分の第3の絶縁膜1008の一部の膜厚を薄くしている。容量素子1112は、第3の絶縁膜1008と、第3の絶縁膜1008を介して重なる第1の電極1007及び第2の電極1010によって構成される。容量素子1112が、本発明の第3の手段の容量素子、即ち、発明を実施する最良の形態や実施例1乃至実施例3における容量素子101に相当する。容量素子1112は、実施例4の容量素子1012と比較して、同じ容量を得るために必要な電極面積を小さくすることができる。こうして、画素の開口率を向上させることができる。

50

**【0102】**

本実施例は、発明を実施する最良の形態や、実施例1乃至実施例3と自由に組み合わせて実施することができる。

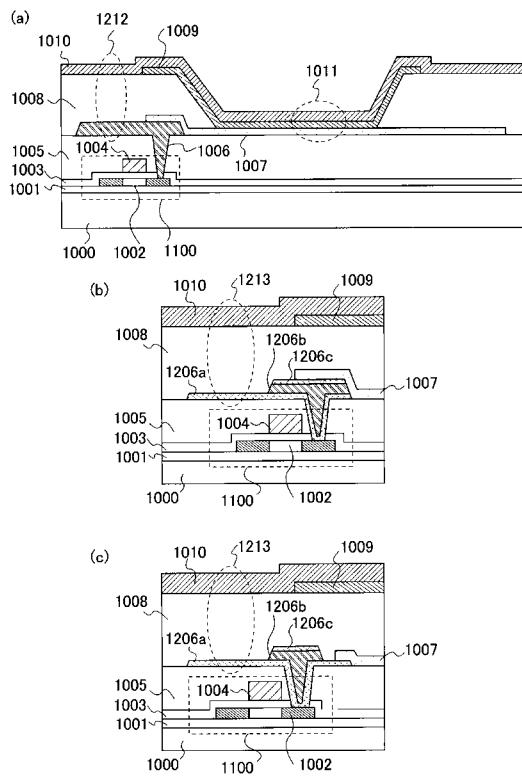

**【実施例6】****【0103】**

実施例4、実施例5とは別の構成の画素の具体例を示す。図12は、本発明の画素の構成を示す断面図である。なお、図10と同じ部分は同じ符号を用いて示し、説明は省略する。

**【0104】**

図12(a)の構成では、容量素子1212は、第3の絶縁膜1008と、第3の絶縁膜1008を介して重なる電極1006及び第2の電極1010によって構成される。容量素子1212が、本発明の第3の手段の容量素子、即ち、発明を実施する最良の形態や実施例1乃至実施例3における容量素子101に相当する。

10

**【0105】**

実施例4に記載したとおり、電極1006として積層を用いることができる。図12(b)及び図12(c)は、積層構造の電極1006の一例を示した図である。電極1006は、第1の層1206a、第2の層1206b、第3の層1206cよりなる。例えば、第1の層1206aとしてTiを用い、第2の層1206bとしてAlを用い、第3の層1206cとしてTiを用いることができる。

20

**【0106】**

図12(b)及び図12(c)では、第1の層1206aと重なる第2の層1206bの一部及び第3の層1206cの一部が除去され、第1の層1206aのみ残った部分(以下、第1の層1206aの延長部分と言う。)が存在する。容量素子1213は、第3の絶縁膜1008と、第3の絶縁膜1008を介して重なる第1の層1206aの延長部分及び第2の電極1010によって構成される。容量素子1213が、本発明の第3の手段の容量素子、即ち、発明を実施する最良の形態や実施例1乃至実施例3における容量素子101に相当する。

20

**【0107】**

図12(b)や図12(c)に示す構成では、第2の層1206bの無い第1の層1206aの延長部分において、容量素子1213を形成するので、第2の層1206bの平坦性が悪い場合であっても、電極間のショート等の不良を少なくすることができる。よって、第2の層1206bとして、電気抵抗は比較的低いが平坦性が悪い材料を用い、第1の層1206a及び第3の層1206cとして、電気抵抗は比較的高いが平坦性の良い材料を用いた場合、図12(b)や図12(c)に示す構成が特に有効である。例えば、第2の層1206bとしてAlを用い、第1の層1206a及び第3の層1206cとしてTiを用いた場合に有効である。

30

**【0108】**

図12(c)では、第1の層1206aの延長部分において、第1の層1206aと第1の電極1007の接続を取っている。電極1006において第1の電極1007と重なる部分の膜厚が薄いので、第1の電極1007の段切れを防止し、第1の電極1007と電極1006との接続を確実に取ることができる。

40

**【0109】**

本実施例は、発明を実施する最良の形態や、実施例1乃至実施例5と自由に組み合わせて実施することができる。

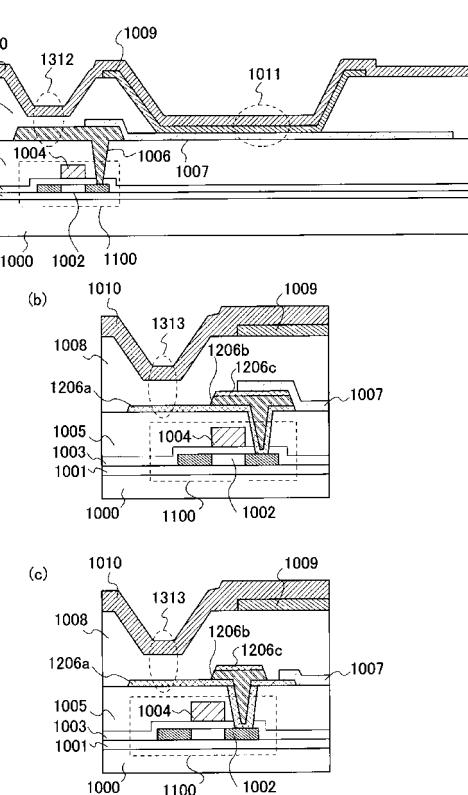

**【実施例7】****【0110】**

実施例4乃至実施例6とは別の構成の画素の具体例を示す。図13は、本発明の画素の構成を示す断面図である。なお、図10、図12と同じ部分は同じ符号を用いて示し、説明は省略する。

**【0111】**

50

図13(a)の構成では、電極1006(又は第1の層1206aの延長部分)と重なる部分の第3の絶縁膜1008の一部の膜厚を薄くしている。容量素子1312は、第3の絶縁膜1008と、第3の絶縁膜1008を介して重なる電極1006及び第2の電極1010によって構成される。容量素子1312が、本発明の第3の手段の容量素子、即ち、発明を実施する最良の形態や実施例1乃至実施例3における容量素子101に相当する。容量素子1312は、実施例6の容量素子1212と比較して、同じ容量を得るために必要な電極面積を小さくすることができる。こうして、画素の開口率を向上させることができる。

#### 【0112】

図13(b)及び図13(c)において、容量素子1313は、第3の絶縁膜1008と、第3の絶縁膜1008を介して重なる第1の層1206aの延長部分及び第2の電極1010によって構成される。容量素子1313が、本発明の第3の手段の容量素子、即ち、発明を実施する最良の形態や実施例1乃至実施例3における容量素子101に相当する。

#### 【0113】

図13(c)では、第1の層1206aの延長部分において、第1の層1206aと第1の電極1007の接続を取っている。

#### 【0114】

図13(b)及び図13(c)の効果は、実施例6の図12(b)及び図12(c)の効果と同様である。更に、図13(b)及び図13(c)の容量素子1313は、図12(b)及び図12(c)の容量素子1213と比較して、同じ容量を得るために必要な電極面積を小さくすることができる。こうして、画素の開口率を向上させることができる。

#### 【0115】

本実施例は、発明を実施する最良の形態や、実施例1乃至実施例5と自由に組み合わせて実施することができる。

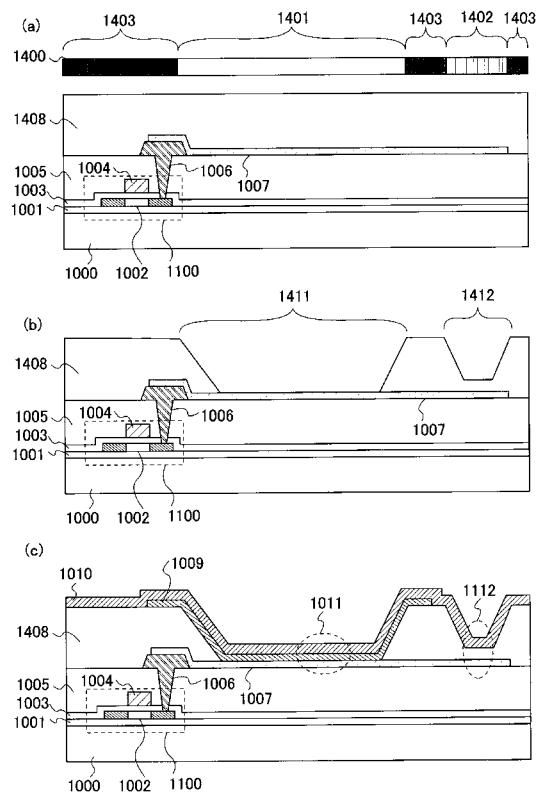

#### 【実施例8】

#### 【0116】

実施例5及び実施例7で示した、一部の膜厚が薄くなった第3の絶縁膜1008の作製方法について説明する。説明には、図14を用いる。図14において図11と同じ部分は同じ符号を用いて示し、説明は省略する。

#### 【0117】

図14(a)において、第1の電極1007を形成した後、絶縁膜1408を形成する。絶縁膜1408として感光性の材料を用いる。フォトマスク1400を用いて、絶縁膜1408を露光する。フォトマスク1400には、第1の光透過部1401、第2の光透過部1402、遮光部1403が設けられている。第1の光透過部1401は開口であっても良い。フォトマスク1400を介して透過する光の強度は、第1の光透過部1401よりも第2の光透過部1402のほうが小さい。遮光部1403はほとんど光を透過しない。フォトマスク1400として、このようなハーフトーンマスクを用いる。

#### 【0118】

図14(b)において、絶縁膜1408を現像する。遮光部1403と重なる部分の絶縁膜1408はほとんどエッチングされない。第1の光透過部1401を介して露光された部分の絶縁膜1408は大きくエッチングされる。こうして、第1の電極1007の表面が露出した開口部1411が形成される。第2の光透過部1402を介して露光された部分の絶縁膜1408は多少エッチングされる。こうして、絶縁膜1408において膜厚の薄い部分1412が形成される。こうして、一部の膜厚が薄くなった絶縁膜1408が得られる。図14(b)の絶縁膜1408が、実施例5及び実施例7で示した第3の絶縁膜1008に相当する。

#### 【0119】

図14(c)において、発光層1009、第2の電極1010を順に形成する。

#### 【0120】

10

20

30

40

50

本実施例は、発明を実施する最良の形態や、実施例1乃至実施例7と自由に組み合わせて実施することができる。

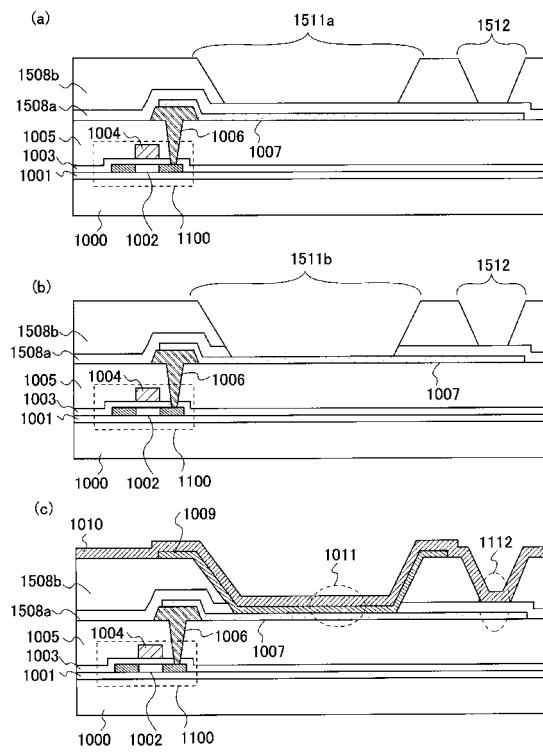

【実施例9】

【0121】

実施例5及び実施例7で示した、一部の膜厚が薄くなった第3の絶縁膜1008の作製方法について、実施例8で示した方法とは別の方法について説明する。説明には、図15を用いる。図15において図11と同じ部分は同じ符号を用いて示し、説明は省略する。

【0122】

図15(a)において、第1の電極1007を形成した後、絶縁膜1508aを形成する。絶縁膜1508a上に絶縁膜1508bを形成する。絶縁膜1508aや絶縁膜1508bとしては、無機絶縁膜や有機絶縁膜の単層または積層を用いることができる。また、珪素(Si)と酸素(O)との結合で骨格構造が構成される材料を用いることもできる。この材料の置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

10

【0123】

絶縁膜1508bをエッティングして、第1の開口部1511a及び第2の開口部1512を形成する。

【0124】

図15(b)において、第1の開口部1511a内において絶縁膜1508aをエッティングして、第3の開口部1511bを形成する。こうして、第1の電極1007の表面が露呈した第3の開口部1511bと、絶縁膜1508aの表面が露呈した第2の開口部1512が得られる。絶縁膜1508a及び絶縁膜1508bが、実施例5及び実施例7で示した第3の絶縁膜1008に相当する。こうして、一部の膜厚が薄くなった第3の絶縁膜1008が得られる。

20

【0125】

図15(c)において、発光層1009、第2の電極1010を順に形成する。

【0126】

容量素子1112は、絶縁膜1508aを誘電体として容量を形成するので、絶縁膜1508aとしては、高誘電率の材料が好ましい。例えば、窒化珪素膜などを用いることができる。

30

【0127】

本実施例は、発明を実施する最良の形態や、実施例1乃至実施例7と自由に組み合わせて実施することができる。

【実施例10】

【0128】

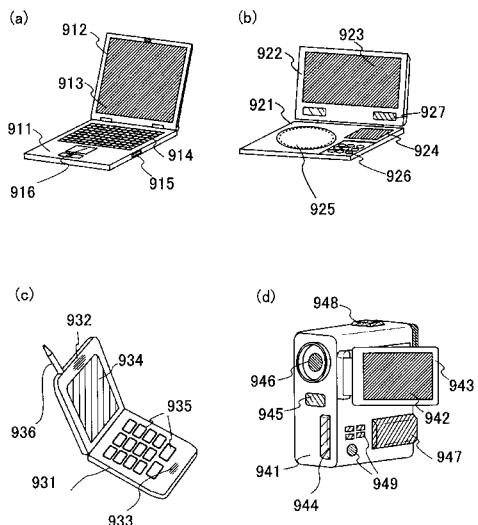

本発明の表示装置及びその駆動方法は、表示装置を表示部に組み込んだ様々な電子機器に適用することができる。

【0129】

電子機器としては、カメラ(ビデオカメラ、デジタルカメラ等)、プロジェクター、ヘッドマウントディスプレイ(ゴーグル型ディスプレイ)、ナビゲーションシステム、カーステレオ、パーソナルコンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。電子機器の例を図9に示す。

40

【0130】

図9(a)は、ノート型パーソナルコンピュータであり、本体911、筐体912、表示部913、キーボード914、外部接続ポート915、ポインティングパッド916等を含む。本発明の表示装置及びその駆動方法は、表示部913に適用される。本発明を用いることによって、表示部913の表示のコントラストを上げて明瞭な表示が可能、且つ

50

消費電力を少なくすることができる。ノート型パーソナルコンピュータは消費電力低減が重要となるので、本発明を用いることは非常に有効である。

#### 【0131】

図9(b)は記録媒体を備えた画像再生装置(具体的にはDVD再生装置)であり、本体921、筐体922、第1の表示部923、第2の表示部924、記録媒体(DVD等)読み込み部925、操作キー926、スピーカー部927等を含む。第1の表示部923は主として画像情報を表示し、第2の表示部924は主として文字情報を表示する。本発明の表示装置及びその駆動方法は、第1の表示部923、第2の表示部924に適用される。本発明を用いることによって、第1の表示部923、第2の表示部924の表示のコントラストを上げて明瞭な表示が可能、且つ消費電力を少なくすることができます。10

#### 【0132】

図9(c)は携帯電話機であり、本体931、音声出力部932、音声入力部933、表示部934、操作スイッチ935、アンテナ936等を含む。本発明の表示装置及びその駆動方法は、表示部934に適用される。本発明を用いることによって、表示部934の表示のコントラストを上げて明瞭な表示が可能、且つ消費電力を少なくすることができます。携帯電話は消費電力低減が重要となるので、本発明を用いることは非常に有効である。。20

#### 【0133】

図9(d)はカメラであり、本体941、表示部942、筐体943、外部接続ポート944、リモコン受信部945、受像部946、バッテリー947、音声入力部948、操作キー949等を含む。本発明の表示装置及びその駆動方法は、表示部942に適用される。本発明を用いることによって、表示部942の表示のコントラストを上げて明瞭な表示が可能、且つ消費電力を少なくすることができます。。20

#### 【0134】

本実施は、発明を実施するための最良の形態、実施例1乃至実施例9と自由に組み合わせて実施することができる。

#### 【図面の簡単な説明】

#### 【0135】

【図1】本発明の第1の実施の形態を示す図。

【図2】本発明の第2の実施の形態を示す図。

【図3】本発明の第3の実施の形態を示す図。

【図4】本発明の第4の実施の形態を示す図。

【図5】本発明の実施例1を示す図。

【図6】本発明の実施例2を示す図。

【図7】本発明の実施例3を示す図。

【図8】従来の構成を示す(a)及び(b)と、発光素子の構成を示す(c)乃至(e)。

【図9】本発明の実施例10を示す図。

【図10】実施例4を示す図。

【図11】実施例5を示す図。

【図12】実施例6を示す図。

【図13】実施例7を示す図。

【図14】実施例8を示す図。

【図15】実施例9を示す図。

#### 【符号の説明】

#### 【0136】

101 容量素子

102 薄膜トランジスタ

103 第1の電源線

104 第2の電源線

20

30

40

50

|         |                       |    |

|---------|-----------------------|----|

| 1 0 5   | 発光素子                  |    |

| 1 0 5 a | 第1の電極                 |    |

| 1 0 5 b | 第2の電極                 |    |

| 1 0 6   | 電位を設定する手段             |    |

| 1 0 7   | 薄膜トランジスタ              |    |

| 1 0 8   | 容量素子                  |    |

| 2 0 4   | 第3の電源線                |    |

| 5 0 0   | 画素                    |    |

| 5 0 1   | 薄膜トランジスタ              | 10 |

| 5 0 2   | 信号線                   |    |

| 5 0 3   | 走査線                   |    |

| 6 0 1   | 薄膜トランジスタ              |    |

| 7 0 1   | 薄膜トランジスタ              |    |

| 7 0 2   | 薄膜トランジスタ              |    |

| 7 0 3   | 薄膜トランジスタ              |    |

| 7 0 4   | 信号線                   |    |

| 7 0 5   | 走査線                   |    |

| 8 0 0   | 容量                    |    |

| 8 0 1 a | 経路                    | 20 |

| 8 0 1 b | 経路                    |    |

| 8 0 2   | ダイオード                 |    |

| 9 1 1   | 本体                    |    |

| 9 1 2   | 筐体                    |    |

| 9 1 3   | 表示部                   |    |

| 9 1 4   | キー ボード                |    |

| 9 1 5   | 外部接続ポート               |    |

| 9 1 6   | ポインティングパッド            |    |

| 9 2 1   | 本体                    |    |

| 9 2 2   | 筐体                    |    |

| 9 2 3   | 第1の表示部                | 30 |

| 9 2 4   | 第2の表示部                |    |

| 9 2 5   | 記録媒体( D V D 等 ) 読み込み部 |    |

| 9 2 6   | 操作キー                  |    |

| 9 2 7   | スピーカー部                |    |

| 9 3 1   | 本体                    |    |

| 9 3 2   | 音声出力部                 |    |

| 9 3 3   | 音声入力部                 |    |

| 9 3 4   | 表示部                   |    |

| 9 3 5   | 操作スイッチ                |    |

| 9 3 6   | アンテナ                  | 40 |

| 9 4 1   | 本体                    |    |

| 9 4 2   | 表示部                   |    |

| 9 4 3   | 筐体                    |    |

| 9 4 4   | 外部接続ポート               |    |

| 9 4 5   | リモコン受信部               |    |

| 9 4 6   | 受像部                   |    |

| 9 4 7   | バッテリー                 |    |

| 9 4 8   | 音声入力部                 |    |

| 9 4 9   | 操作キー                  |    |

| 1 0 0 0 | 基板                    | 50 |

|           |          |    |

|-----------|----------|----|

| 1 0 0 1   | 下地膜      |    |

| 1 0 0 2   | 半導体層     |    |

| 1 0 0 3   | 第1の絶縁膜   |    |

| 1 0 0 4   | ゲート電極    |    |

| 1 0 0 5   | 第2の絶縁膜   |    |

| 1 0 0 6   | 電極       |    |

| 1 0 0 7   | 第1の電極    |    |

| 1 0 0 8   | 第3の絶縁膜   |    |

| 1 0 0 9   | 発光層      |    |

| 1 0 1 0   | 第2の電極    | 10 |

| 1 0 1 1   | 発光素子     |    |

| 1 0 1 2   | 容量素子     |    |

| 1 1 0 0   | 薄膜トランジスタ |    |

| 1 1 1 2   | 容量素子     |    |

| 1 2 1 2   | 容量素子     |    |

| 1 2 1 3   | 容量素子     |    |

| 1 2 0 6 a | 第1の層     |    |

| 1 2 0 6 b | 第2の層     |    |

| 1 2 0 6 c | 第3の層     |    |

| 1 3 1 2   | 容量素子     | 20 |

| 1 3 1 3   | 容量素子     |    |

| 1 4 0 0   | フォトマスク   |    |

| 1 4 0 1   | 第1の光透過部  |    |

| 1 4 0 2   | 第2の光透過部  |    |

| 1 4 0 3   | 遮光部      |    |

| 1 4 0 8   | 絶縁膜      |    |

| 1 4 1 1   | 開口部      |    |

| 1 4 1 2   | 膜厚の薄い部分  |    |

| 1 5 0 8 a | 絶縁膜      |    |

| 1 5 0 8 b | 絶縁膜      | 30 |

| 1 5 1 1 a | 第1の開口部   |    |

| 1 5 1 1 b | 第3の開口部   |    |

| 1 5 1 2   | 第2の開口部   |    |

【図1】

【 図 2 】

【 図 3 】

【 図 4 】

【図5】

【図6】

【図7】

【図8】

【図9】

【図11】

【図10】

【図12】

【図13】

【図14】

【図15】

---

フロントページの続き

(51) Int.Cl.

F I

H 05B 33/14

テーマコード(参考)

A

F ターム(参考) 5C380 AA01 AB06 AB11 AB23 AB24 AB46 AC05 AC08 AC10 AC11

AC12 BA01 BA10 BA12 BB23 CA12 CC02 CC26 CC27 CC33

CC35 CC38 CC41 CC52 CC62 CC63 CC77 CD012 CD013 CD022

CD023 CD024 CD025 CF43 DA02 DA06 DA08