(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2004-96750

(P2004-96750A)

(43) 公開日 平成16年3月25日(2004.3.25)

(51) Int.C1.<sup>7</sup>

HO3K 19/0944

HO3F 3/34

HO3F 3/345

HO3K 17/04

HO3K 19/0185

F 1

HO3K 19/094

HO3F 3/34

HO3F 3/345

HO3K 17/04

HO3K 19/00

101B

審査請求 未請求 請求項の数 1 O L (全 11 頁)

(21) 出願番号 特願2003-299973 (P2003-299973)

(22) 出願日 平成15年8月25日 (2003.8.25)

(31) 優先権主張番号 10/233715

(32) 優先日 平成14年9月3日 (2002.9.3)

(33) 優先権主張国 米国(US)

(71) 出願人 399117121

アジレント・テクノロジーズ・インク

A G I L E N T T E C H N O L O G I E

S, I N C.

アメリカ合衆国カリフォルニア州パロアル

ト ページ・ミル・ロード 395

395 Page Mill Road

Palo Alto, California

U. S. A.

(74) 代理人 100075513

弁理士 後藤 政喜

(74) 代理人 100084537

弁理士 松田 嘉夫

最終頁に続く

(54) 【発明の名称】バイアス電流補償を有する電流モード論理回路系

## (57) 【要約】

【課題】 電流モード論理ゲートの動作安定化とスイッチング速度の高速化を図る。

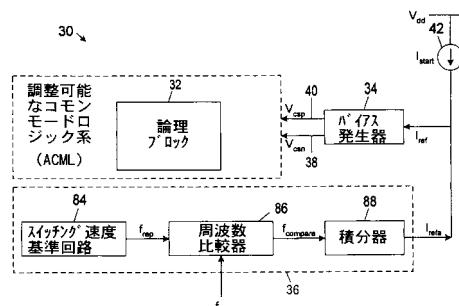

【解決手段】 回路システム30は、論理回路32とスイッチング速度基準回路84を備える。論理回路32は、それぞれが個別にテール電流を操作して出力電圧振幅を生成するよう動作可能な1以上の電流モード論理ゲートを含む。バイアス電流調整回路36は、スイッチング速度基準回路84で検出された論理回路32の固有スイッチング速度と基準クロック周波数 $f_{ref}$ との比較結果に基づき、基準電流 $I_{ref}$ を調整する。バイアス発生器34は、基準電流 $I_{ref}$ に基づいて論理回路32の負荷抵抗およびテール電流を制御する。

【選択図】 図4

## 【特許請求の範囲】

## 【請求項 1】

個々のテール電流を操作して出力電圧振幅を生成するようそれが動作可能な 1 以上の電流モード論理ゲートを備える論理回路と、

テール電流レベルにおける変化によらず、各電流源モード論理ゲートの電圧振幅を維持するよう動作可能なバイアス回路と、

を備えることを特徴とする回路システム。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本発明は、バイアス電流補償を有する電流モード論理回路系に関する。 10

## 【背景技術】

## 【0002】

C M O S 技術を用いて今日構築される大半の論理回路は、レール・ツー・レール論理回路で設計されており、電源とグラウンドとの間の全スイッチング路は N F E T ( n 型電界効果トランジスタ ) デバイスと P F E T ( p 型電界効果トランジスタ ) デバイスとが直列にコンプリメンタリ接続される。静的状態にあっては、レール・ツー・レール論理回路では一切の電流の吸い込みはなく、何故なら P F E T デバイスと N F E T デバイスのどちらも非導通とされるからである。電流は、過渡期間中にのみ必要となる。かくして、過渡周波数 ( 或いはクロック速度 ) に比例して電力が消費される。 20

## 【0003】

最大の絶縁だけでなく  $V_{dd}$  およびグラウンド・レールにおける最小の電源変動もまた要求される回路にとって、従来のレール・ツー・レール C M O S 論理回路系の過渡期間中の電流スパイクから生ずる電圧リップルは慎重に抑圧しなければならない。クロック速度が数ギガビットレベルを超すと、この問題は制御がますます難しいものとなる。これらの動作環境では、C M L ( 電流モード論理回路 ) として知られる論理回路系が代わりに用いられることが一般的である。C M L 論理回路系では、各スイッチごとに一定の電流が常時存在する。この電流の制御が、論理 1 或いは論理 0 に対応する差動電圧を生成する。C M L 論理回路系は電流スパイクを減らすが、クロック速度や論理回路の遷移に拘わらず電力消費を必要とする。 30

## 【0004】

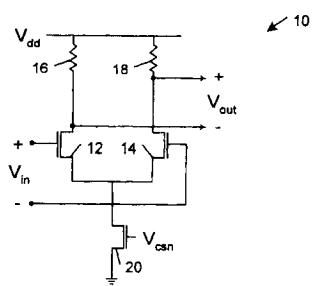

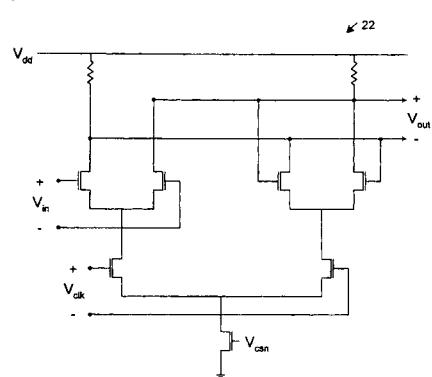

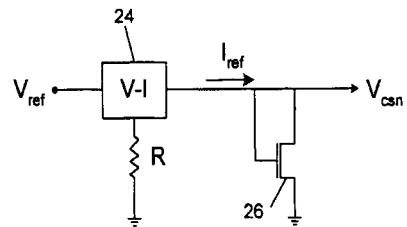

図 1 を参照すると、従来の C M L 論理バッファ 1 0 は作動対トランジスタ 1 2 , 1 4 と負荷抵抗 1 6 , 1 8 とトランジスタ差動対の電源を供給する電流源 2 0 からなる。差動対の追加スタックを論理ツリー内に挿入して論理回路を合体させることができる。例えば、図 2 に示すように、3 個の差動対を用いてラッチ 2 2 を形成することができる。図 3 を参照すると、C M L 電流源用のバイアス電流は通常、基準電流 (  $I_{ref}$  ) をダイオード構成されている N F E T カレントミラー 2 6 へ供給する主基準電流源 2 4 により供給される。主基準電流 (  $I_{ref}$  ) は、定電圧 (  $V_{ref}$  ) 源を備えた電圧 - 電流 (  $V - I$  ) 変換器から導出される。定電圧源は、バンドギャップ電圧基準と抵抗 ( R ) から導くことができる。この抵抗は、C M L ゲートの負荷抵抗に整合させるか、或いは一定電流が必要な場合は外部の、或いはレーザトリミングを施した精密抵抗とすることができる。 40

## 【0005】

C M L 論理セルの速度は、F E T 差動対スイッチのスイッチング速度だけでなく負荷抵抗における R C 時定数に依存する。製造過程では、負荷抵抗の値が先ず選択される。次いで、電流源の値がデバイスの大きさにより選択され、負荷抵抗にかかる電圧振幅の許容量が得られる。電圧振幅は通常、次の C M L 論理ゲートの切り替えに必要とされる電圧に対応する。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0006】

10

20

30

40

50

大量生産環境においてCML回路に対するタイミングの要求に応えるため、CMLゲートの速度は、一般に最も遅いFETデバイスに対応する最遅コーナーケースや、ICプロセスで保証される負荷抵抗の公差の最大値、最高温度、そして必要とされる最低 $V_{dd}$ に合わせて設計しなければならない。この要件が満たされた状態で、同一の設計を、一般に最速のFETデバイスとICプロセスで保証される負荷抵抗の公差の最小値に対応するワーストケース状況下における最大電力消費量や、最高温度、そして製品が必要とする最高 $V_{dd}$ に対して規定し、保証しなければならない。最小限の電力消費はICパッケージのコストを低減し、信頼性を高めることにつながるので、電力消費がより低いということは所与の回路設計の主要な競争に耐える長所となる。現在のところ、CML論理回路系が消費する最大電力は、最遅コーナーケースで必要とされる電流で決まる。

10

【課題を解決するための手段】

【0007】

一つの態様では、本発明は論理回路とバイアス回路を備える回路システムを特徴とするものである。論理回路は、それぞれが個々のテール電流を操作して出力電圧振幅を生成するよう動作可能な1以上の電流モード論理ゲートを含む。バイアス回路は、テール電流レベルの変化によらず各電流モード論理ゲートの電圧振幅を維持するよう動作可能である。

【0008】

別の態様では、本発明は論理回路とスイッチング速度基準回路を備える回路システムを特徴とするものである。論理回路は、それぞれが個別にテール電流を操作して出力電圧振幅を生成するよう動作可能な1以上の電流モード論理ゲートを含む。スイッチング速度基準回路は、1以上の電流モード論理ゲートの固有スイッチング速度を検出するよう動作可能である。

20

【0009】

別の態様では、本発明は論理回路とテール電流調整回路を備える回路システムを特徴とするものである。論理回路は、それぞれが個々のテール電流を操作して出力電圧振幅を生成せしめるよう動作可能な1以上の電流モード論理ゲートを含む。テール電流調整回路は、電流モード論理ゲートテール電流を動的に調整して基準クロック周波数に相關させて論理ゲートスイッチング速度を維持するよう動作可能である。

【0010】

本発明の他の特徴及び効果は、図面と特許請求の範囲を含む以下の説明から明らかとなろう。

30

【発明を実施するための最良の形態】

【0011】

以下の説明では、同様の参照符号は同様の要素を特定するのに用いるものとする。さらに、図面は例示実施形態の主要な特徴を図解することを意図して線図により描いたものである。図面は、実際の実施形態の全ての特徴、或いは図示した要素の相対的な寸法の描写も意図しておらず、実寸で描いたものではない。

【0012】

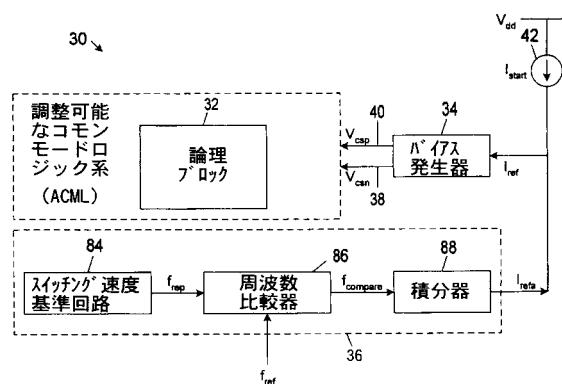

図4を参照すると、一実施形態では、回路システム30は様々な種類の異なる機能のうちの一つとして機能可能な一組の論理ブロック32と、バイアス発生器34と、バイアス電流調整回路36とを含む。例示実施形態では、一組の論理ブロック32は一般的な可調整コモンモード論理(ACML)設計に従ったものとなっている。このACML設計に従って、各ACML論理ブロックは電流源と、調整可能な負荷抵抗を有する負荷と、差動対電流制御回路網(current steering network)を含む。バイアス発生器34は、ACML論理ブロックの電流源に接続される電流源設定出力38と、ACML論理ブロックの負荷に接続される負荷抵抗設定出力40とを有する。バイアス発生器34は、基準電流( $I_{ref}$ )に基づいて所定の電源電流を供給するようACML電流源を設定可能である。この基準電流( $I_{ref}$ )は、バイアス電流調整回路36から供給される基準電流( $I_{refa}$ )と、始動電流源42から供給される始動電流( $I_{start}$ )との組み合わせに対応する。バイアス発生器34はまた、電源電流(の増減)に逆行してACM

40

50

L負荷を設定し、結果として所与の電流源設定（値）に対しロジック信号の振幅レベルをほぼ維持するような負荷抵抗レベルにACML負荷を設定するよう動作可能である。こうして、バイアス発生器34はACML論理に必要とされる電流を調整し、最遅コーナーケースにおけるタイミング要件と、最速コーナーケースにおける電力消費を切り離すことができるようになっている。特に、バイアス発生器34は、ACMLバイアス電流を遅いコーナーケースでは増大させ、速いコーナーケースでは減少させることを可能とするとともに、ACML負荷抵抗レベルを自動調整してロジック信号の必要振幅レベルを維持する。こうして、高速処理が行われるコーナーケースに通常関連する最大電力消費は排除される。これにより、トータルの電力消費の上限が低められ、ICパッケージに必要なコストの低減とより高い信頼性が得られる。

10

## 【0013】

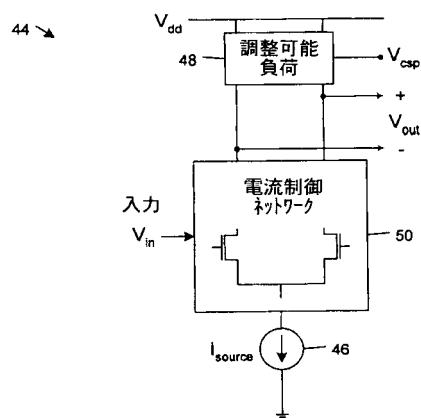

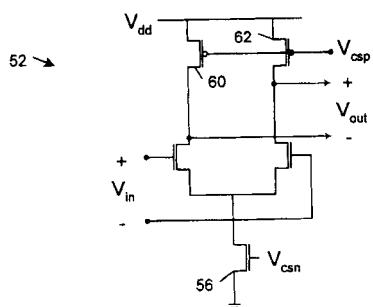

図5を参照する。一般に、ACML論理ブロック44は、電流源46と調整可能な負荷48と差動対電流制御回路網50を含む。電流源46は、第1の電圧のレール（例えばグラウンド）に結合され、電源電流（ $I_{source}$ ）を供給するよう動作可能である。可調整負荷48は第2の電圧のレール（例えば $V_{dd}$ ）に結合してあり、入力された負荷抵抗設定電圧 $V_{csp}$ のレベルに従って調整可能な負荷抵抗を有する。差動対電流制御回路網50は、コンプリメンタリの入力及び出力と、電流源と負荷の間に結合した1以上の差動対を含む。

## 【0014】

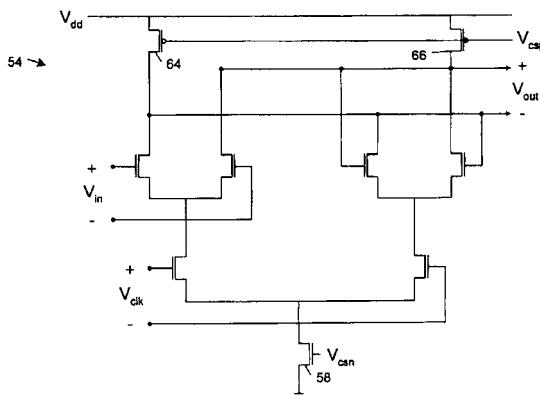

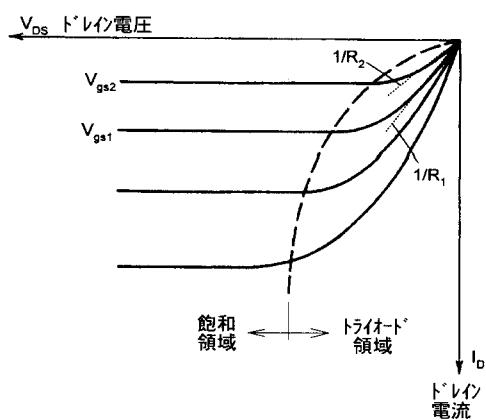

図5に示すACML論理ブロック44は、図6に示すようなバッファ52や、図7に示すようなラッチ54を含む様々な異なる論理回路のうちの任意の一つの形態として機能することができる。これらの機能形態では、ACML電流源はグラウンドに連結したn型電界効果トランジスタ（N F E T）56, 58である。バイアス発生器34（図4）のソース電流設定出力38がバイアス電圧（ $V_{c_{sn}}$ ）を印加し、N E E T電流源56, 58で供給されるテール電流を設定する。これらの機能形態では、調整可能な負荷はp型電界効果トランジスタ（P F E T）60, 62, 64, 66である。バイアス発生器34（図4）の負荷抵抗設定出力40が、P F E T負荷60～66のトライオードバイアス領域にあるバイアス電圧（ $V_{csp}$ ）を印加する。これらの機能形態では、P F E T負荷60～66はバイアス発生器34（図4）により調整可能な抵抗値をもった可変抵抗として機能し、バイアス発生器34により設定することのできる様々なテール電流レベルに対しロジック信号の所要の振幅レベルを維持する。

20

## 【0015】

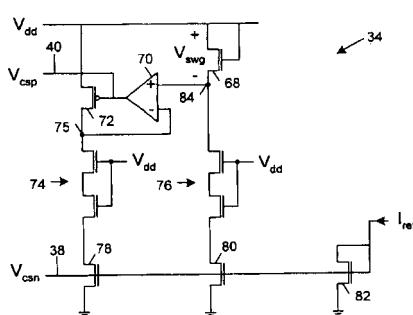

図8を参照すると、いくつかの実施形態では、バイアス発生器34はロジック信号の振幅設定トランジスタ68とオペアンプ70と出力トランジスタ72と一対のレベルシフタ74, 76と一対の電流源トランジスタ78, 80を含む。基準電流 $I_{ref}$ がN F E Tダイオードカレントミラー82内へ供給され、これによって電源電流設定出力バイアス $V_{c_n}$ が生成される。このバイアスがまた、電流源トランジスタ78, 80を駆動する。例示実施形態では、レベルシフタ74と出力トランジスタ72との組み合わせがACML論理回路54（図7）の論理スタッカと同様の機能を有し、これにより電流源トランジスタ78の早期効果を補償して電流源トランジスタ58（図7）と緊密に整合させる。特に、出力トランジスタ72がP F E T負荷60～66（図6、図7）と同様の機能を有し、レベルシフタが二つのレベルのACMLスイッチングと同様の機能を有する。レベルシフタ76もまた、二つのレベルのACMLスイッチングと同様の機能を有する。ロジック信号の振幅設定トランジスタ68は、 $V_{dd}$ レールとロジック信号振幅設定出力端84との間にダイオードとして接続してある。電流源トランジスタ80により供給される電流に応答してロジック信号振幅設定トランジスタ68の両端にはロジック信号振幅電圧（ $V_{swg}$ ）が生じる。ロジック信号振幅設定出力端84に生じた電圧（すなわち $V_{swg}$ ）がオペアンプ70の非反転入力端に供給される。オペアンプ70はロジック信号振幅設定出力端84とバイアス発生器34の負荷抵抗設定出力端40との間にフォロワとして結合しており、オペアンプ70の電圧出力は負荷抵抗設定出力バイアス $V_{csp}$ に対応する。

30

40

50

## 【0016】

動作時に、電圧  $V_{swg}$  がバイアス電流  $I_{ref}$  とは比較的無関係の所望レベルに設定してあるものと先ず仮定する。  $I_{ref}$  が増加あるいは減少すると、電流源 78 と P チャンネル FET 72 を通る電流は比例的に変化する。オペアンプ 70 は接続点 75 における電圧を監視し、 $V_{csp}$  を調整して FET 72 の抵抗を変化させ、接続点 75 が接続点 84 と同電圧となるようにする。負荷トランジスタとしての出力トランジスタ (FET) 72 は線形トライオード領域で動作し、図 9 に示すように、ゲート電圧 ( $V_{gs}$ ) を変化させることでその抵抗値は調整される。

## 【0017】

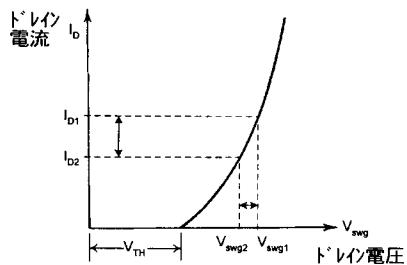

本実施形態では、ロジック信号振幅電圧 ( $V_{swg}$ ) は NFEトランジスタ 68 で生成され、何故なら ACM論理ブロックが必要とする電圧振幅は NFEトランジスタ 68 で切り替えるのに必要な電圧振幅に対応しているからである。こうして、 $V_{swg}$  は製造工程や温度に起因するスレショールド電位 ( $V_{th}$ ) の変動に追従する。 $V_{swg}$  の変化は、図 10 に示す如く、そのドレイン電流の変化に比して比較的小なものとなる。

## 【0018】

他の実施形態では、 $V_{dd}/2$  或いはバンドギャップ基準電位から得られたもの等、異なるロジック信号振幅レベルを用いることもできる。

## 【0019】

図 4 を再度参照すると、バイアス電流調整回路 36 は基準クロック周波数  $f_{ref}$  に相関させて基準電流  $I_{ref}$  を調整するよう動作可能である。特に、バイアス電流調整回路 36 は基準クロック周波数に追従して基準電流を増減するよう動作可能であり、従って ACM論理ブロックの電源電流を増減可能で、所望のスイッチング速度を得ることができる。こうして、バイアス電流調整回路 36 はレール・ツー・レール論理回路系の長所 (すなわちより低いクロック速度でのより低い電力消費) を達成し、その一方で電流モード論理回路系の長所 (すなわち低減された電流スパイク) を依然として達成する。例示実施形態では、バイアス電流調整回路 36 はスイッチング速度基準回路 84 と周波数比較器 86 と積分器 88 を含む。スイッチング速度基準回路 84 は ACM論理ブロックと実質的にマッチさせてあり、論理回路 (ACM論理ブロック) のスイッチング速度を表わす出力信号  $f_{rep}$  を生成するよう動作可能としてある。

## 【0020】

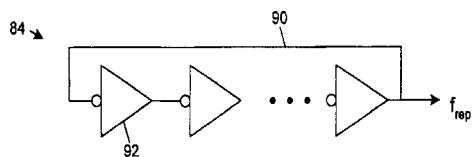

図 11 を参照すると、一実施形態では、スイッチング速度基準回路 84 は一連の ACMインバータ 92 で構築したリング発振器 90 とされる。この構成では、スイッチング速度基準回路 84 は、バイアス発生器 34 (図 4) と共に動作して電流制御発振器 (ICO) として機能し、ここで発振周波数は基準電流  $I_{ref}$  に比例する。リング発振器 90 は、その意図した動作範囲内で発振停止すべきではない。リング遅延インバータは同じ ACM論理ブロックであるため、ACM論理ブロック 32 の速度はリング発振器 90 の速度に追従する。

## 【0021】

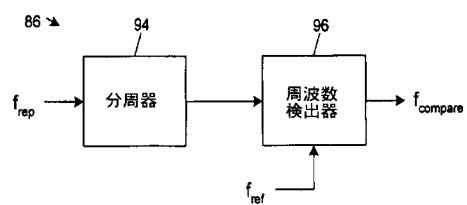

再度図 4 および図 12 を参照すると、スイッチング速度基準回路 84 の出力信号  $f_{rep}$  が周波数比較器 86 の入力端に供給され、この比較器が出力信号  $f_{rep}$  と基準クロック信号  $f_{ref}$  との間の比較に基づいて出力  $f_{compare}$  を生成するよう動作可能である。いくつかの実施形態では、スイッチング速度基準回路 84 と周波数比較器 86 は ACM論理ブロックで構成される。図 12 に示したように、一実施形態では、周波数比較器 86 は分周器 94 と周波数検出器 96 にて実施することができる。分周器 94 は、スイッチング速度基準回路 84 の出力信号  $f_{rep}$  を適当量にて分周する。周波数検出器 96 は得られた分周信号を基準クロック信号  $f_{ref}$  と比較し、リング発振器から出力された周波数が基準クロック周波数を超える (アップ) か満たない (ダウン) を示す出力信号  $f_{compare}$  を生成する。周波数検出器 96 は、回転検出器或いはリセット機能付きストップウォッチを含む様々な周知の周波数検出器のうちの任意の一つで実施することができる。周波数検出器 96 のアップ / ダウン指示値は、積分器 88 により積分される。

10

20

30

40

50

## 【0022】

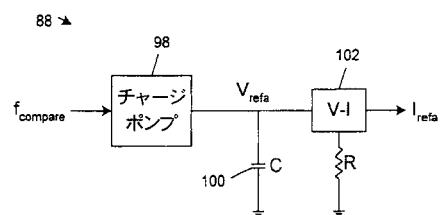

図13を参照すると、一実施形態では、積分器88はチャージポンプ98とコンデンサ100を含む。電圧-電流(V-I)変換器102はチャージポンプ出力端での電圧 $V_{refa}$ を出力電流 $I_{refa}$ へ変換する。リング発振器の分周周波数が基準クロック周波数に一度整合すると、V-I変換器102に供給された基準電圧は公称値周りで微動させられる。ループは閉じているため、 $V_{csn}$ バイアス電圧は発振周波数を外部基準クロック $f_{ref}$ にロックした状態に保つよう調整される。周波数変動はチャージポンプ電流と積分コンデンサ値と実効ICO(電流制御発振器)ゲインにより決定される。

## 【0023】

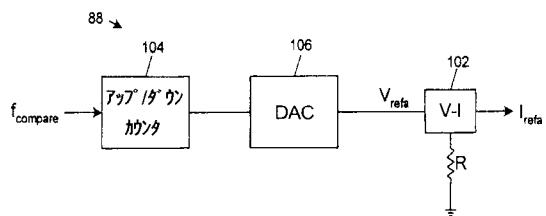

図14を参照すると、別の実施形態では、積分器88はデジタル/アナログ変換器(DA変換器)106を駆動するアップ/ダウンカウンタ104で実施される。DA変換器106は、 $V_{refa}$ バイアス信号を駆動する。 $V_{refa}$ 精度の分解能は、DA変換器106の分解能に基づく。この実施形態では、図13の積分器実施形態のアナログ機能がデジタル機能に置き換えてある。

## 【0024】

一部実施形態では、図13, 14の積分器実施形態のV-I変換器102は取り除かれ、 $V_{refa}$ 出力端は直接 $V_{csn}$ へ接続するものであってもよい。

## 【0025】

図4を参照すると、電力増強時には、スイッチング速度基準回路84や周波数比較器86などの図示の回路システム30内の少なくとも一部のACML論理セルは、バイアス電圧 $V_{csn}$ が適正に漸増するよう機能させねばならない。図示の実施形態では、電流源42はスタートアップトリックル(少しずつ流す)電流 $I_{start}$ を供給し、スイッチング速度基準回路84と周波数比較器86用のACML論理回路の機能を保証する。別の実施形態では、周波数比較器86は定電流源に接続した個別の独立したバイアス発生器によりバイアスされる。さらに別の実施形態では、周波数比較器86はバイアスを一切必要としない従来のレール・ツー・レールCMOS論理回路をもって実施される。この実施形態では、ACMLレベルをCMOS論理回路のレベルへ整合させるのに論理レベル変換器が必要となることがある。

## 【0026】

他の実施形態は特許請求の範囲内にある。

30

## 【0027】

例えば、上記の実施形態は電界効果トランジスタ回路に関連して説明したが、これらの実施形態はバイポーラトランジスタ技術などの他のトランジスタ技術をもって実施することもできる。

## 【0028】

なお、本発明は例として以下の態様を含む。

[1] 個々のテール電流を操作して出力電圧振幅を生成するようそれが動作可能な1以上の電流モード論理ゲートを備える論理回路(44)と、

テール電流レベルにおける変化によらず、各電流源モード論理ゲートの電圧振幅を維持するよう動作可能なバイアス回路(34)と、

を備えることを特徴とする回路システム(30)。

40

[2] 前記論理回路(44)が、

第1の電圧のレールに結合され、電源電流を供給するよう動作可能な電流源(46)と、

第2の電圧のレールに結合され、調整可能な負荷抵抗を有する負荷(48)と、

前記電流源(46)と前記負荷(48)の間に接続され、コンプリメンタリ入力及び出力を有する差動対電流制御回路網(50)とを備え、

前記バイアス回路(34)は、前記電流源(46)に接続された電源電流設定出力と前記負荷(48)に結合した負荷抵抗設定出力とを有しており、

前記バイアス回路(34)は、所与の電源電流を供給するよう前記電流源(46)を設

50

定し、また、電源電流源に逆行して前記負荷(48)を設定し、結果として所与の電源電流設定に対して前記論理回路(44)の前記コンプリメンタリ出力間のロジック信号振幅レベルをほぼ維持するように前記負荷(48)を設定するよう動作可能である、

ことを特徴とする[1]に記載の回路システム。

[3] 前記負荷(48)が、前記バイアス回路(34)の前記負荷抵抗設定出力に接続される制御入力をそれぞれ有する一対のトランジスタを備える、

ことを特徴とする[2]に記載の回路システム。

[4] 前記バイアス回路(34)が、ロジック信号振幅設定トランジスタ(68)を備える、

ことを特徴とする[2]に記載の回路システム。

10

[5] 前記バイアス回路(34)は、前記電流源(46)を設定して入力した基準電流に基づく所与の電源電流を供給するよう動作可能であり、さらに、前記バイアス回路(34)に接続され、基準クロック周波数に相関して前記基準電流を調整するよう動作可能なバイアス電流調整回路(36)を備える、

ことを特徴とする[2]に記載の回路システム。

[6] 前記バイアス電流調整回路(36)は、前記論理回路(44)とほぼマッチさせてあって論理回路スイッチング速度を表わす出力信号を生成するよう動作可能なスイッチング速度基準回路(84)を備える、

ことを特徴とする[5]に記載の回路システム。

20

[7] 前記スイッチング速度基準回路(36)がリング発振器(90)を備える、

ことを特徴とする[6]に記載の回路システム。

[8] 前記スイッチング速度基準回路(36)からの前記出力信号と基準周波数信号との比較に基づいて出力を生成するよう動作可能な周波数比較器(86)を備える、

ことを特徴とする[6]に記載の回路システム。

[9] 個々のテール電流を制御して出力電圧振幅を生成するようそれが動作可能な1以上の電流モード論理ゲートを有する論理回路(44)と、前記1以上の電流モード論理ゲートの固有スイッチング速度を検出するよう動作可能なスイッチング速度基準回路(84)とを備える、

ことを特徴とする回路システム(30)。

[10] 個々のテール電流を制御して出力電圧振幅を発生させるようそれが動作可能な1以上の電流モード論理ゲートを有する論理回路(44)と、

30

前記電流モード論理ゲートのテール電流を動的に調整し、基準クロック周波数に相関させて論理ゲートスイッチング速度を維持するよう動作可能なテール電流調整回路(36)とを備える、

ことを特徴とする回路システム(30)。

【図面の簡単な説明】

【0029】

【図1】従来技術の電流モード論理バッファ回路の回路図である。

【図2】従来技術の電流モード論理ラッチ回路の回路図である。

【図3】ダイオード構成電界効果トランジスタ電流ミラーをもたらす従来技術の主基準電流源の回路図である。

40

【図4】可調整電流モード論理系とバイアス発生器とバイアス電流調整回路と始動電流源を含む回路のブロック線図である。

【図5】可調整負荷と差動対電流操作回路網と電流源を含む可調整電流モード論理回路の線図である。

【図6】図5の可調整電流モード論理回路のバッファ実装回路図である。

【図7】図5の可調整電流モード論理回路のラッチ実装回路図である。

【図8】図4のバイアス発生器の実装回路図である。

【図9】pチャンネルエンハンスマントモードMOSFETのドレイン電流の線図である

。

50

【図10】ドレイン電圧の関数としてプロットしたダイオード接続エンハンスマントモードN M O Sトランジスタのドレイン電流の線図である。

【図11】スイッチング速度基準回路のブロック線図である。

【図12】周波数比較回路のブロック線図である。

【図13】積分器回路のブロック線図である。

【図14】別の積分器回路のブロック線図である。

【符号の説明】

【0030】

10 C M L 論理バッファ

12, 14 トランジスタ差動対

16, 18 負荷抵抗

20 電流源

22 ラッチ

24 主基準電流源

26 ダイオード構成N F E T電流ミラー

30 回路システム

32 論理ブロック

34 バイアス発生器(バイアス回路)

36 バイアス電流調整回路

38 電流源設定出力端

40 負荷抵抗設定出力端

42 始動電流源

44 A C M L 論理ブロック(論理回路)

46 電流源

48 可調整負荷

50 差動対電流操作回路網

52 バッファ

54 ラッチ

56, 58 N E E T電流源

60, 62, 64, 66 p型電界効果トランジスタ( P F E T )

68 ロジック信号振幅設定トランジスタ

70 オペアンプ

72 出力トランジスタ

74, 76 レベルシフタ

78, 80 一対の電流源トランジスタ

82 N F E T ダイオード電流ミラー

84 ロジック信号振幅設定出力端

84 スイッチング速度基準回路

86 周波数比較器

88 積分器

90 リング発振器

94 分周器

96 周波数検出器

98 チャージポンプ

100 コンデンサ

102 電圧 - 電流( V - I )変換器

104 アップ / ダウンカウンタ

106 ディジタル / アナログ変換器( D A 変換器 )

10

20

30

40

【図1】

【図2】

【図3】

【図4】

【図5】

【図7】

【図6】

【図 9】

【図 10】

【図 11】

【図 12】

【図 13】

【図 14】

## フロントページの続き

(72)発明者 ベニー ダブリュウ . レイ

アメリカ合衆国 カリフォルニア 94539 フリーモント ギャリンドウ・ドライヴ 473

05

F ターム(参考) 5J055 AX02 BX16 CX27 DX12 DX56 DX72 DX73 DX83 EX02 EY01

EY10 EY21 EZ00 EZ01 EZ03 EZ04 EZ07 EZ08 EZ09 EZ10

EZ20 EZ22 EZ24 EZ28 EZ36 EZ55 FX19 FX37 GX01 GX02

GX06

5J056 AA03 AA11 BB02 CC01 CC02 CC04 CC07 CC09 CC10 CC16

CC17 CC21 CC30 DD12 DD29 DD51 EE06 FF06 FF09 GG10

KK03

5J500 AA01 AA12 AC11 AC65 AF10 AH09 AH17 AH25 AH29 AK00

AK01 AK03 AK05 AK09 AK12 AK18 AK31 AK32 AK34 AK35

AM21 AT01 AT02 DN01 DN14 DN22 DN23 DP02