(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2018-159912

(P2018-159912A)

(43) 公開日 平成30年10月11日(2018.10.11)

(51) Int.CI.

**G09G 3/20 (2006.01)**

**G09G 3/36 (2006.01)**

**G09G 3/30 (2006.01)**

**G09G 3/3233 (2016.01)**

**G02F 1/1333 (2006.01)**

F 1

GO9G 3/20

GO9G 3/36

GO9G 3/20

GO9G 3/20

GO9G 3/20

テーマコード(参考)

2H189

2H193

3K107

5C006

5C080

審査請求 未請求 請求項の数 22 O L (全 72 頁) 最終頁に続く

(21) 出願番号 特願2018-21284 (P2018-21284)

(22) 出願日 平成30年2月8日 (2018.2.8)

(31) 優先権主張番号 特願2017-22685 (P2017-22685)

(32) 優先日 平成29年2月10日 (2017.2.10)

(33) 優先権主張国 日本国 (JP)

(31) 優先権主張番号 特願2017-74759 (P2017-74759)

(32) 優先日 平成29年4月4日 (2017.4.4)

(33) 優先権主張国 日本国 (JP)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 岡本 佑樹

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

F ターム(参考) 2H189 AA27 AA31 HA16 JA05 JA06

JA10 JA12 JA14 JA19 JA20 NA05

2H193 ZA04 ZF13 ZF14 ZF16 ZH04

ZH05 ZH07 ZH37 ZH52 ZQ06

ZQ07 ZQ11 ZQ14 ZQ16 ZQ22

ZQ26

最終頁に続く

(54) 【発明の名称】表示コントローラ、表示システム、および電子機器

## (57) 【要約】

【課題】高視認性の表示システムを提供する。

【解決手段】表示システムはホスト装置、表示コントローラおよび表示パネルを有する。表示パネルには、複数のサブ画素を有する画素アレイが設けられている。サブ画素は発光型表示素子、反射型表示素子を有する。ホスト装置は表示コントローラに画像データDT0を送信する。表示コントローラは次の機能をもつ。画像データDT0の色の分類。色の分類結果に基づく属性データの生成。画像データDT0から画像データDT1の生成。画像データDT1に対する属性データに応じた画像処理により、2種類の画像データDT2\_e、DT2\_rの生成。画像データDT2\_eから画像データDT3\_eの生成。画像データDT2\_rから画像データDT3\_rの生成。画像データDT3\_eは発光型表示素子で表示され、画像データDT3\_rは反射型表示素子で表示される。

【選択図】図1

FIG. 1

**【特許請求の範囲】****【請求項 1】**

ホスト装置、表示コントローラ、および表示パネルを有する表示システムであって、

前記ホスト装置は前記表示コントローラに第1画像データを送信し、

前記第1画像データは1画素分の画像データであり、

前記表示コントローラは、

前記第1画像データの色の分類を行い、分類結果に基づいて属性データを生成し、

前記第1画像データを処理し、第2画像データを生成し、

前記第2画像データに対して、前記属性データに応じた処理を行い、第3画像データを生成し、

前記第3画像データを処理して第4画像データを生成し、

前記第4画像データを前記表示パネルに送信する

ことを特徴とする表示システム。

**【請求項 2】**

請求項1において、

前記第2画像データへの処理には、前記第2画像データの画素値に、前記属性データに応じたゲイン値を乗算する処理が含まれることを特徴とする表示システム。

**【請求項 3】**

請求項1又は2において、

前記第3画像データへの処理には、ガンマ補正が含まれることを特徴とする表示システム。

**【請求項 4】**

ホスト装置、表示コントローラ、および表示パネルを有する表示システムであって、

前記表示パネルは画素アレイを有し、

前記画素アレイは複数のサブ画素を有し、

前記サブ画素は発光型表示素子および反射型表示素子を有し、

前記ホスト装置は前記表示コントローラに第1画像データを送信し、

前記第1画像データは1画素分の画像データであり、

表示コントローラは、

前記第1画像データの色の分類を行い、分類結果に基づいて属性データを生成し、

前記第1画像データを処理し、第2画像データを生成し、

前記第2画像データに対して前記属性データに応じた処理を行い、第3画像データおよび第4画像データを生成し、

前記第3画像データを処理して、第5画像データを生成し、

前記第4画像データを処理して、第6画像データを生成し、

前記第5画像データおよび前記第6画像データを前記表示パネルに送信し、

前記第5画像データは前記発光型表示素子で表示され、

前記第6画像データは前記反射型表示素子で表示されることを特徴とする表示システム

。

**【請求項 5】**

請求項4において、

前記第2画像データへの処理には、前記第2画像データの画素値に、前記属性データに応じたゲイン値を乗算する処理が含まれる表示システム。

**【請求項 6】**

請求項4又は5において、

前記第3画像データの処理には、ガンマ補正が含まれ、

前記第4画像データの処理には、ガンマ補正が含まれることを特徴とする表示システム

。

**【請求項 7】**

請求項4乃至6の何れか1項において、

10

20

30

40

50

前記反射型表示素子は反射型液晶素子であることを特徴とする表示システム。

【請求項 8】

請求項 4 乃至 7 の何れか 1 項において、

前記発光型表示素子はエレクトロルミネセンス素子であることを特徴とする表示システム。

【請求項 9】

表示コントローラ、および表示パネルを有する表示システムであって、

表示パネルは画素アレイ、および周辺回路を有し、

画素アレイは画素を有し、

10

前記画素は複数の第 1 サブ画素および複数の第 2 サブ画素を有し、

前記第 1 サブ画素は反射型表示素子を有し、

前記第 2 サブ画素は発光型表示素子を有し、

前記表示コントローラは、

外部から送信される第 1 データを処理して、第 2 データおよび第 3 データを生成し

、

前記第 2 データを処理して、第 4 データを生成し、

前記第 3 データを処理して、第 5 データを生成し、

前記第 4 データ、および前記第 5 データを表示パネルに送信し、

前記周辺回路は前記画素に前記第 4 データ、および前記第 5 データを書き込み、

前記第 4 データは前記複数の第 1 サブ画素によって表示され、

前記第 5 データは前記複数の第 2 サブ画素によって表示され、

前記表示コントローラは前記第 1 データがカラーデータであるか否かを判定し、前記第 1 データがカラーデータである場合は、前記第 2 データとして黒表示データを作成し、前記第 3 データとして前記第 1 データと同じデータを作成することを特徴とする表示システム。

20

【請求項 10】

請求項 9 において、

前記表示コントローラは前記第 1 データがカラーデータであるか否かを判定し、前記第 1 データがカラーデータではない場合は、前記第 2 データとして前記第 1 データをグレースケールデータに変換することでグレースケールデータを生成し、前記第 3 データとして黒表示データを作成することを特徴とする表示システム。

30

【請求項 11】

請求項 9 において、

前記表示コントローラは前記第 1 データがカラーデータであるか否かを判定し、第 1 データがカラーデータではない場合は、前記第 2 データとして前記第 1 データと同じデータを生成し、前記第 3 データとして黒表示データを作成することを特徴とする表示システム。

。

【請求項 12】

請求項 9 乃至 11 の何れか 1 項において、

40

前記表示システムは光センサを有し、

前記表示コントローラは、光センサで取得された情報に基づいて、前記第 3 データを処理することを特徴とする表示システム。

【請求項 13】

請求項 9 乃至 12 の何れか 1 項において、

前記反射型表示素子は反射型液晶素子であることを特徴とする表示システム。

【請求項 14】

請求項 9 乃至 13 の何れか 1 項において、

前記発光型表示素子はエレクトロルミネセンス素子であることを特徴とする表示システム。

50

**【請求項 1 5】**

請求項 1 乃至 1 4 の何れか 1 項において、

さらに、タッチセンサを有することを特徴とする表示システム。

**【請求項 1 6】**

請求項 1 乃至 1 5 の何れか 1 項において、

前記表示コントローラはメモリ装置を有し、

前記メモリ装置のメモリセルは、容量素子と前記容量素子への充放電を制御するためのトランジスタを有し、

前記トランジスタのチャネル形成領域は金属酸化物を有することを特徴とする表示システム。

10

**【請求項 1 7】**

筐体および表示部を有する電気機器であり、

前記表示部に、請求項 1 乃至 1 1 の何れか 1 項に記載の表示システムを備えることを特徴とする電子機器。

**【請求項 1 8】**

画素に複数の第 1 サブ画素および複数の第 2 サブ画素を有し、前記第 1 サブ画素が反射型表示素子を有し、前記第 2 サブ画素は発光型表示素子を有する表示パネルの表示コントローラであって、

前記表示コントローラは、外部から送信される画像データを処理して、前記複数の第 1 サブ画素の表示ための第 1 データと、前記複数の第 2 サブ画素の表示のための第 2 データとを生成し、

前記表示コントローラは前記画像データがカラーデータであるか否かを判定し、前記画像データがカラーデータである場合は、前記第 1 データとして黒表示データを作成し、前記第 2 データとして前記画像データと同じデータを作成することを特徴とする表示コントローラ。

20

**【請求項 1 9】**

請求項 1 8 において、

前記表示コントローラは前記画像データがカラーデータであるか否かを判定し、前記画像データがカラーデータではない場合は、前記画像データをグレースケールデータに変換することで前記第 1 データを生成し、前記第 2 データとして黒表示データを作成することを特徴とする表示コントローラ。

30

**【請求項 2 0】**

請求項 1 8 において、

前記表示コントローラは前記第 1 画像データがカラーデータであるか否かを判定し、前記画像データがカラーデータではない場合は、前記第 1 データとして前記画像データと同じデータを生成し、前記第 2 データとして黒表示データを作成することを特徴とする表示コントローラ。

40

**【請求項 2 1】**

請求項 1 8 乃至 2 0 の何れか 1 項において、

外部から入力される環境光の情報に基づいて、前記第 2 データを処理することを特徴とする表示コントローラ。

**【請求項 2 2】**

請求項 1 8 乃至 2 1 の何れか 1 項において、

さらにメモリ装置を有し、

前記メモリ装置はメモリセルを有し、

前記メモリセルは、容量素子と前記容量素子への充放電を制御するためのトランジスタを有し、

前記トランジスタのチャネル形成領域は金属酸化物を有することを特徴とする表示コントローラ。

**【発明の詳細な説明】**

50

**【技術分野】****【0001】**

本発明の一形態は、表示装置の技術の分野に属しており、例えば、表示装置の画素アレイ、駆動回路、および制御回路、表示装置の動作方法などに関する。なお、ここで記載する技術分野は例示であり、本発明の一形態の適用可能な技術分野は、これに限定されるものではない。

**【背景技術】****【0002】**

スマートフォン、スマートウォッチ、タブレット端末、電子書籍端末、ノートPC（パソコン用コンピュータ）等の携帯型電子機器が普及している。携帯型電子機器は様々な環境で利用されるため、携帯型電子機器に搭載される表示装置には、利用する環境に適した表示をすること、低消費電力であることが求められる。このような要求を実現する表示装置として、1のサブ画素に液晶素子と発光素子が設けられているハイブリッド（複合型）表示装置が提案されている（例えば、特許文献1～3）。

10

**【0003】**

チャネル形成領域に金属酸化物を有するトランジスタ（以下、「金属酸化物半導体トランジスタ」、または「OSトランジスタ」と呼ぶ場合がある。）が知られている。例えば、非特許文献1、2にはサブ画素がOSトランジスタで構成されているハイブリッド表示装置が記載されている。

20

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2003-157026号公報

【特許文献2】国際公開第2004/053819号

【特許文献3】国際公開第2007/041150号

**【非特許文献】****【0005】**

【非特許文献1】K. Kusunoki et al., “Transmissive OLED and Reflective LC Hybrid (TR Hybrid) Display,” SID Symposium Digest of Technical Papers, 2016, vol. 47, pp. 57–60.

30

【非特許文献2】T. Sakuishi et al., “Transmissive OLED and Reflective LC Hybrid (TR Hybrid) Display with High Visibility and Low Power Consumption,” SID Symposium Digest of Technical Papers, 2016, vol. 47, pp. 735–738.

**【発明の概要】****【発明が解決しようとする課題】****【0006】**

本発明の一形態の課題は、視認性向上すること、消費電力を低減すること、画像データ送信の負荷を低減すること、および動作不良を低減することである。

40

**【0007】**

複数の課題の記載は、互いの課題の存在を妨げるものではない。本発明の一形態は、例示した全ての課題を解決する必要はない。また、列記した以外の課題が、本出願の明細書、図面、および特許請求の範囲（以下、「本明細書等」と呼ぶ。）の記載から、自ずと明らかとなるものであり、このような課題も、本発明の一形態の課題となり得る。

**【課題を解決するための手段】****【0008】**

(1) 本発明の1形態は、ホスト装置、表示コントローラ、および表示パネルを有する表示システムであって、ホスト装置は表示コントローラに第1画像データを送信し、第1

50

画像データは1画素分の画像データであり、表示コントローラは、第1画像データの色の分類を行い、分類結果に基づいて属性データを生成し、第1画像データを処理して第2画像データを生成し、第2画像データに対して属性データに応じた処理を行うことで第3画像データを生成し、第3画像データを処理して第4画像データを生成し、第4画像データを表示パネルに送信する表示システムである。

【0009】

(2) 前記形態(1)において、第2画像データへの処理には、第2画像データの画素値に、属性データに応じたゲイン値を乗算する処理が含まれる。

【0010】

(3) 前記形態(1)又は(2)において、第3画像データへの処理には、ガンマ補正が含まれる。 10

【0011】

(4) 本発明の1形態は、ホスト装置、表示コントローラ、および表示パネルを有する表示システムであって、表示パネルは画素アレイを有し、画素アレイは複数のサブ画素を有し、サブ画素は発光型表示素子および反射型表示素子を有し、ホスト装置は表示コントローラに第1画像データを送信し、第1画像データは1画素分の画像データであり、表示コントローラは、第1画像データの色の分類を行い、分類結果に基づいて属性データを生成し、第1画像データを処理して第2画像データを生成し、第2画像データに対して属性データに応じた処理を行うことで第3画像データおよび第4画像データを生成し、第3画像データを処理して第5画像データを生成し、第4画像データを処理して第6画像データを生成し、第5画像データおよび第6画像データを表示パネルに送信し、第5画像データは発光型表示素子で表示され、第6画像データは反射型表示素子で表示されることを特徴とする表示システムである。 20

【0012】

(5) 前記形態(4)において、第2画像データへの処理には、第2画像データの画素値に、属性データに応じたゲイン値を乗算する処理が含まれる。

【0013】

(6) 前記形態(4)又は(5)において、第3画像データへの処理には、ガンマ補正が含まれ、第4画像データの処理には、ガンマ補正が含まれる。 30

【0014】

(7) 本発明の1形態は、表示コントローラおよび表示パネルを有する表示システムであって、表示パネルは画素アレイおよび周辺回路を有し、画素アレイは画素を有し、画素は複数の第1サブ画素、および複数の第2サブ画素を有し、第1サブ画素は反射型表示素子を有し、第2サブ画素は発光型表示素子を有し、表示コントローラは、外部から送信される第1データを処理して、第2データおよび第3データを生成し、第2データを処理して第4データを生成し、第3データを処理して第5データを生成し、第4データおよび第5データを表示パネルに送信し、周辺回路は画素に第4データおよび第5データを書き込み、第4データは複数の第1サブ画素によって表示され、第5データは複数の第2サブ画素によって表示され、表示コントローラは第1データがカラーデータであるか否かを判定し、第1データがカラーデータである場合は、第2データとして黒表示データを作成し、第3データとして第1データと同じデータを作成する表示システムである。 40

【0015】

(8) 前記形態(7)において、表示コントローラは第1データがカラーデータであるか否かを判定し、第1データがカラーデータではない場合は、第2データとして第1データをグレースケールデータに変換することでグレースケールデータを生成し、第3データとして黒表示データを作成する。

【0016】

(9) 前記形態(7)において、表示コントローラは第1データがカラーデータであるか否かを判定し、第1データがカラーデータではない場合は、第2データとして第1データと同じデータを生成し、第3データとして黒表示データを作成する。 50

**【 0 0 1 7 】**

( 1 0 ) 前記形態( 4 )乃至( 9 )の何れか 1 において、反射型表示素子は反射型液晶素子である。

**【 0 0 1 8 】**

( 1 1 ) 前記形態( 4 )乃至( 1 0 )の何れか 1 において、発光型表示素子はエレクトロルミネセンス素子である。

**【 0 0 1 9 】**

本明細書等において、半導体装置とは、半導体特性を利用した装置であり、半導体素子(トランジスタ、ダイオード、フォトダイオード等)を含む回路、同回路を有する装置等をいう。また、半導体特性を利用して機能しうる装置全般をいう。例えば、集積回路、集積回路を備えたチップや、パッケージにチップを収納した電子部品は半導体装置の一例である。また、記憶装置、表示装置、発光装置、照明装置及び電子機器等は、それ自体が半導体装置であり、半導体装置を有している場合がある。

10

**【 0 0 2 0 】**

本明細書等において、XとYとが接続されていると記載されている場合は、XとYとが電気的に接続されている場合と、XとYとが機能的に接続されている場合と、XとYとが直接接続されている場合とが、本明細書等に開示されているものとする。したがって、所定の接続関係、例えば、図または文章に示された接続関係に限定されず、図または文章に示された接続関係以外のものも、図または文章に記載されているものとする。X、Yは、対象物(例えば、装置、素子、回路、配線、電極、端子、導電膜、層など)であるとする。

20

**【 0 0 2 1 】**

トランジスタは、ゲート、ソース、およびドレインと呼ばれる 3 つの端子を有する。ゲートは、トランジスタの導通状態を制御する制御端子である。ソースまたはドレインとして機能する 2 つの端子は、トランジスタの入出力端子である。2 つの入出力端子は、トランジスタの導電型( n チャネル型、 p チャネル型)及びトランジスタの 3 つの端子に与えられる電位の高低によって、一方がソースとなり他方がドレインとなる。このため、本明細書等においては、ソースやドレインの用語は、入れ替えて用いることができるものとする。また、本明細書等では、ゲート以外の 2 つの端子を第 1 端子、第 2 端子と呼ぶ場合がある。

30

**【 0 0 2 2 】**

ノードは、回路構成やデバイス構造等に応じて、端子、配線、電極、導電層、導電体、不純物領域等と言い換えることが可能である。また、端子、配線等をノードと言い換えることが可能である。また、本明細書等において「電極」や「配線」の用語は、これらの構成要素を機能的に限定するものではない。例えば、「電極」は「配線」の一部として用いられることがあり、その逆もまた同様である。さらに、「電極」や「配線」の用語は、複数の「電極」や「配線」が一体となって設けられている場合なども含む。

40

**【 0 0 2 3 】**

電圧は、ある電位と、基準の電位(例えば接地電位( G N D )またはソース電位)との電位差のことを示す場合が多い。よって、電圧を電位と言い換えることが可能である。なお、電位とは相対的なものである。よって、 G N D と記載されていても、必ずしも 0 V を意味しない場合もある。

40

**【 0 0 2 4 】**

本明細書等において、「膜」という言葉と「層」という言葉とは、場合によっては、または、状況に応じて、互いに入れ替えることが可能である。例えば、「導電層」という用語を「導電膜」という用語に変更することが可能な場合がある。例えば、「絶縁膜」という用語を「絶縁層」という用語に変更することが可能な場合がある。

**【 0 0 2 5 】**

本明細書等において、「第 1 」、「第 2 」、「第 3 」などの序数詞は、順序を表すために使用される場合がある。または、構成要素の混同を避けるために使用する場合がある。これらの場合、序数詞の使用は構成要素の個数を限定するものではなく、順序を限定するも

50

のでもない。また、例えば、「第1」を「第2」または「第3」に置き換えて、本発明の一形態を説明することができる。

**【発明の効果】**

**【0026】**

本発明の一形態は、視認性向上すること、消費電力を低減すること、データ送信の負荷を低減すること、および動作不良を低減することが可能である。

**【0027】**

複数の効果の記載は、他の効果の存在を妨げるものではない。また、本発明の一形態は、必ずしも、例示した効果の全てを有する必要はない。また、本発明の一形態について、上記以外の課題、効果、および新規な特徴については、本明細書の記載および図面から自ずと明らかになるものである。10

**【図面の簡単な説明】**

**【0028】**

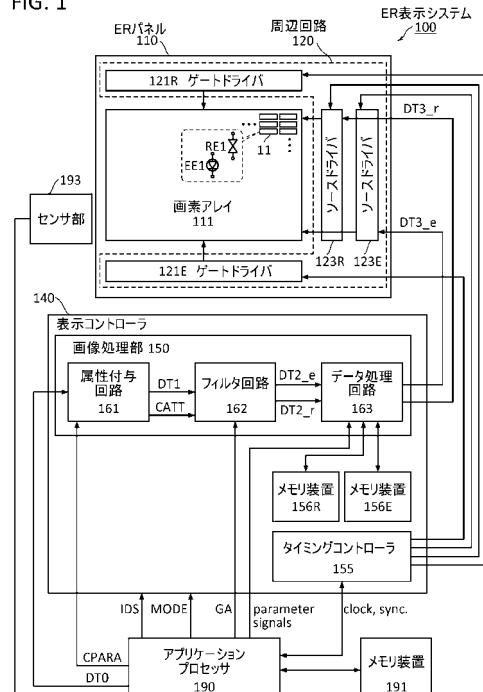

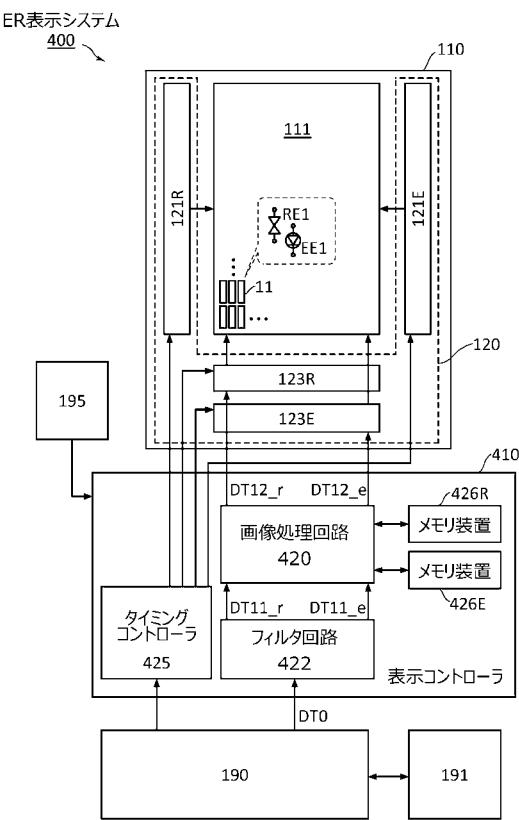

【図1】ER表示システムの構成例を示す機能ブロック図。

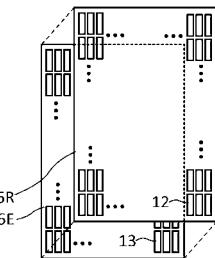

【図2】A：画素アレイ、サブ画素の構成例を示す回路図。B：画素の構成例を示す図。

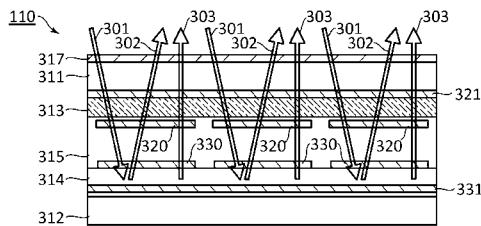

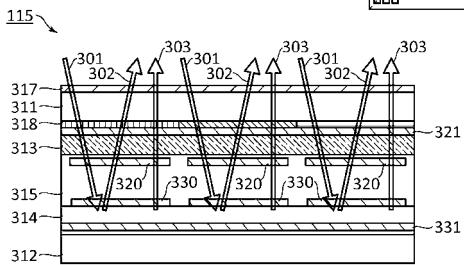

【図3】A、C：ERパネルの表示原理を示す断面図。B：画素アレイの構成例を示す模式図。

【図4】回路の動作例を示すフローチャート。

【図5】フィルタ回路の動作例を示すフローチャート。

【図6】表示コントローラの構成例を示す機能ブロック図。

【図7】T X Tモードでの画像処理部の動作例を示すタイミングチャート。

【図8】T X Tモードでの画像処理を説明する図。

【図9】属性付与回路の動作例を示すフローチャート。

【図10】フィルタ回路の動作例を示すフローチャート。

【図11】ER表示システムの構成例を示す機能ブロック図。

【図12】A：画素の構成例を示す図。B：画素アレイの構成例を示す模式図。C：ERパネルの表示原理を示す断面図。

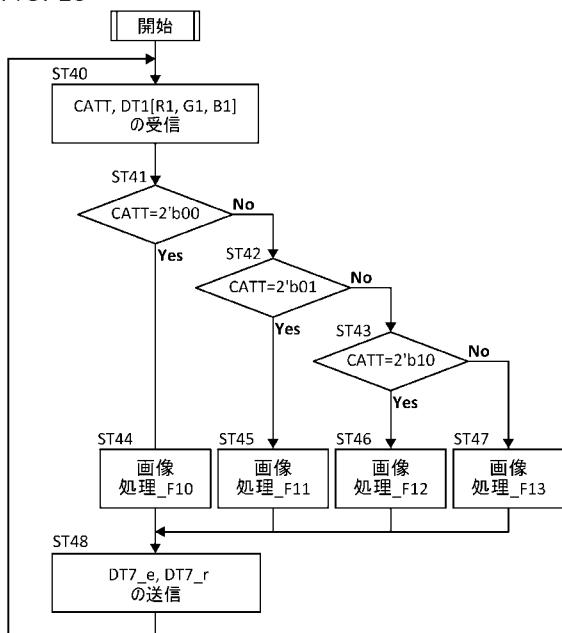

【図13】属性付与回路の動作例を示すフローチャート。

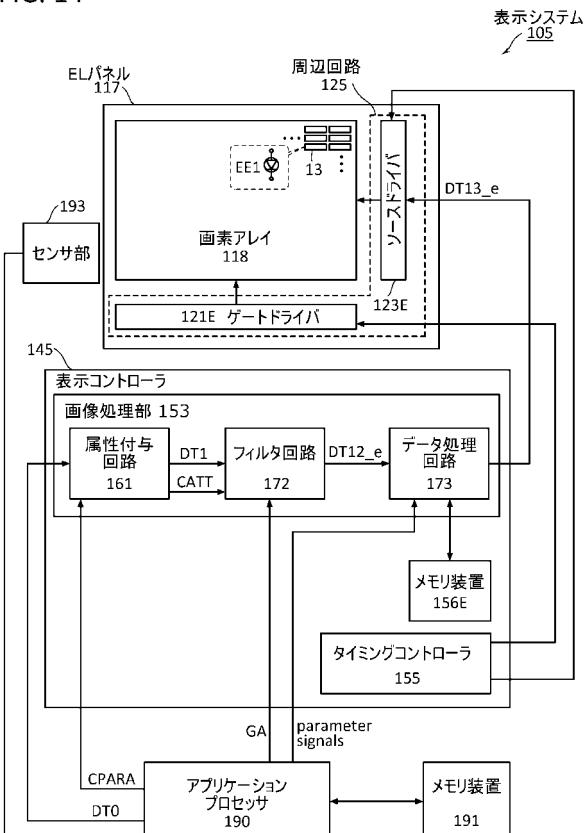

【図14】表示システムの構成例を示す機能ブロック図。

【図15】表示システムの構成例を示す機能ブロック図。

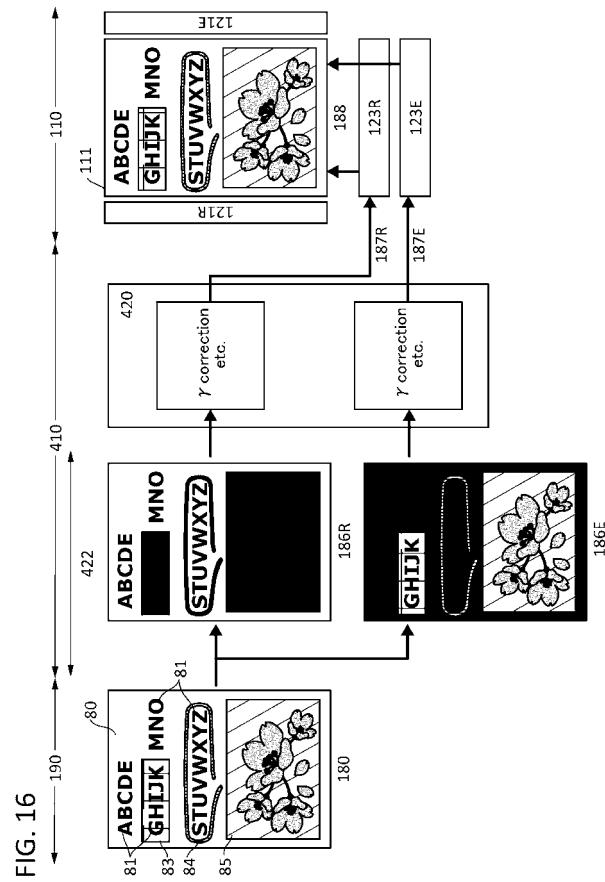

【図16】ER表示システムの表示モード（T X Tモード）を説明する図。

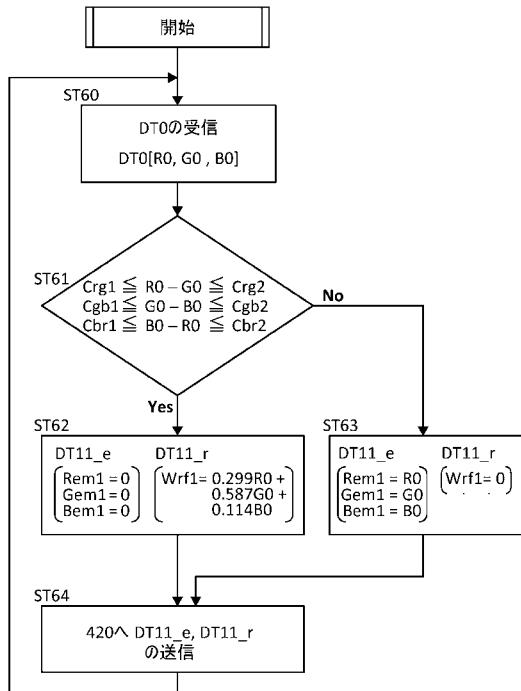

【図17】T X Tモードでのフィルタ回路の動作例を示すフローチャート。

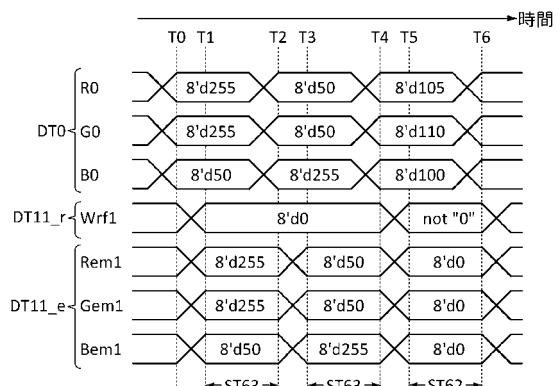

【図18】T X Tモードでのフィルタ回路の動作例を示すタイミングチャート。

【図19】T X Tモードでのフィルタ回路の動作例を示すフローチャート。

【図20】T X Tモードでのフィルタ回路の動作例を示すタイミングチャート。

【図21】ER表示システムの構成例を示す機能ブロック図。

【図22】T X Tモードでのフィルタ回路の動作例を示すフローチャート。

【図23】T X Tモードでのフィルタ回路の動作例を示すタイミングチャート。

【図24】T X Tモードでのフィルタ回路の動作例を示すフローチャート。

【図25】T X Tモードでのフィルタ回路の動作例を示すタイミングチャート。

【図26】ER表示システムの構成例を示す機能ブロック図。

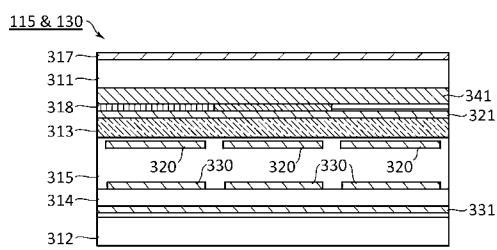

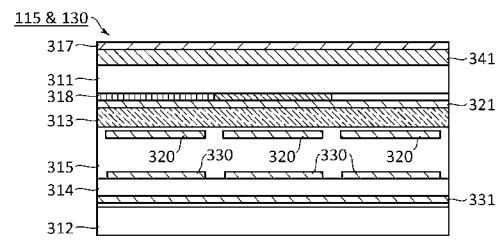

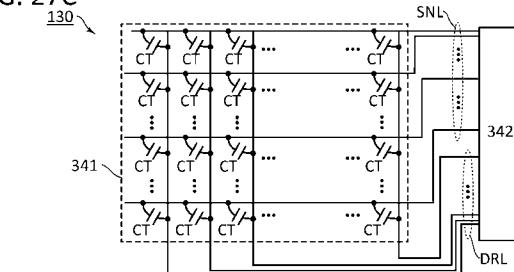

【図27】A、B：ERパネルの構成例を示す断面図。C：センサアレイの回路構成例を示す図。

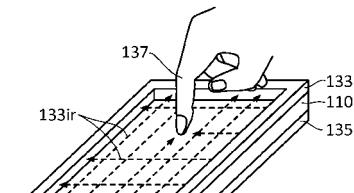

【図28】A C：ERパネルの構成例を示す斜視模式図。

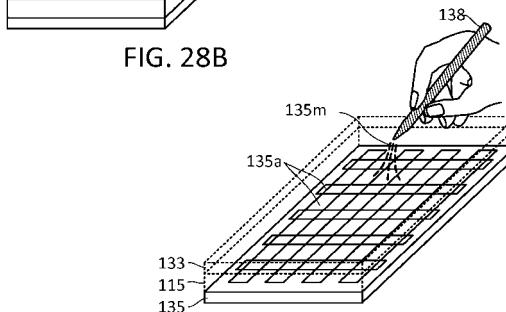

【図29】ER表示システムの構成例を示す機能ブロック図。

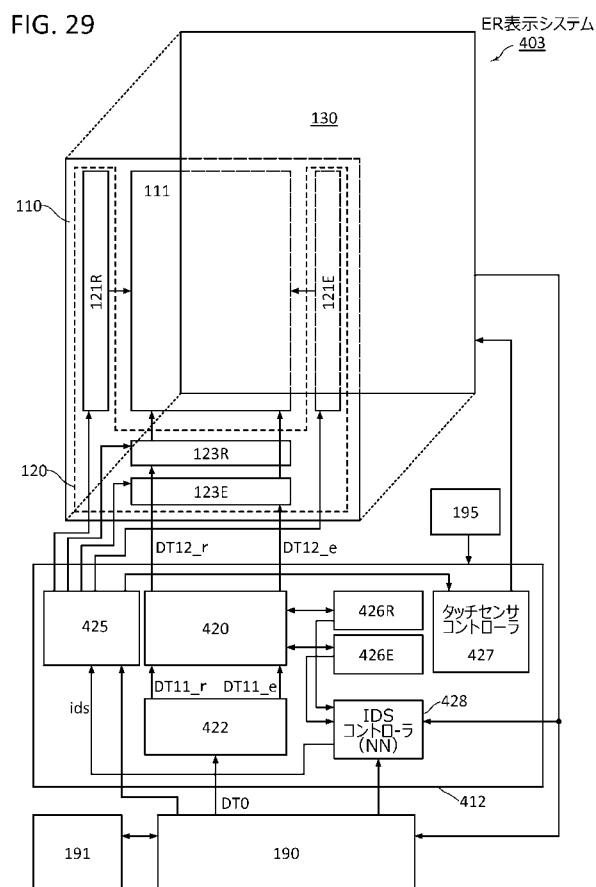

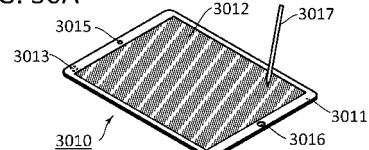

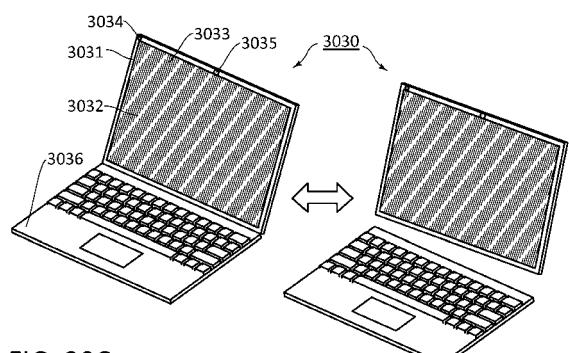

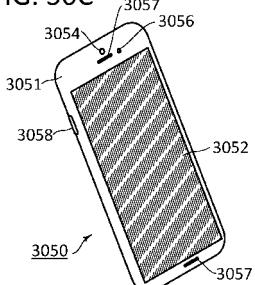

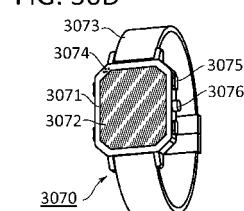

【図30】A D：電子機器の構成例を示す図。

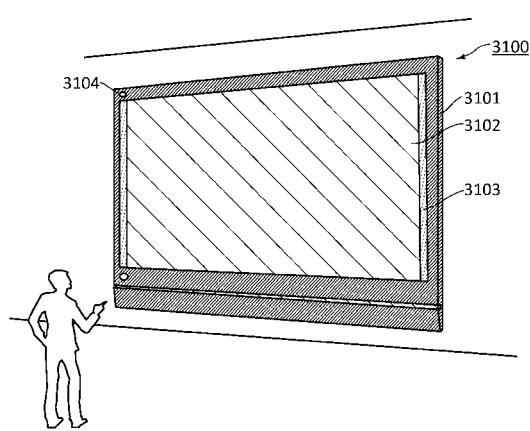

【図31】電子機器の構成例を示す図。

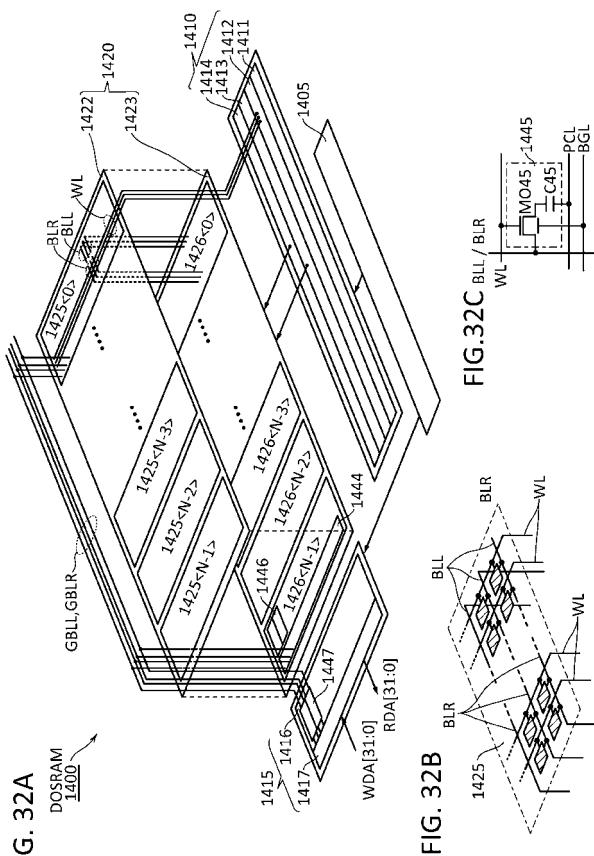

【図32】A：D O S R A Mの構成例を示す機能ブロック図。B：メモリセルアレイの構成例を示す図。C：メモリセルの回路構成例を示す図。

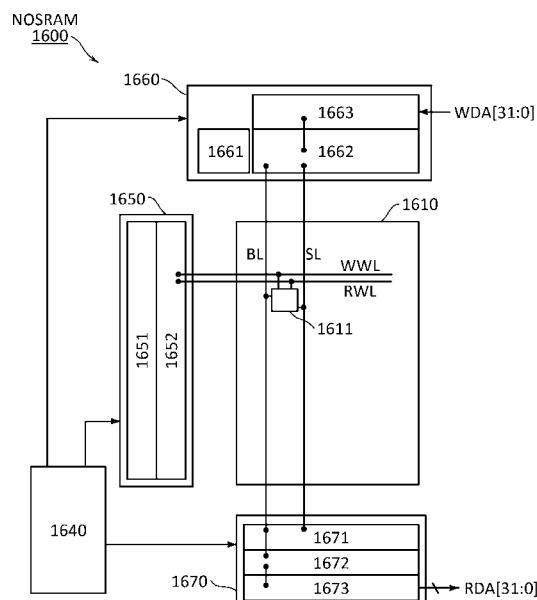

【図33】N O S R A Mの構成例を示す機能ブロック図。

10

20

30

40

50

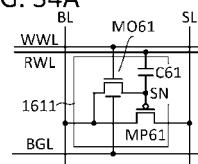

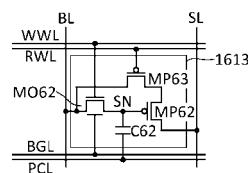

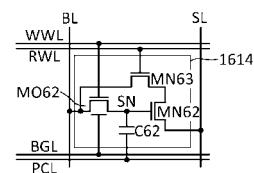

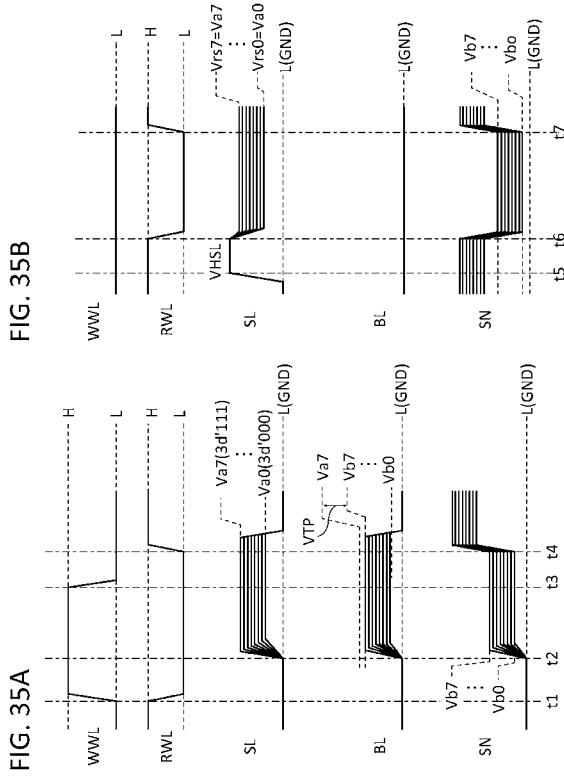

【図34】A D : メモリセルの回路構成例を示す図。

【図35】A、B : NOSRAMの動作例を示すタイミングチャート。

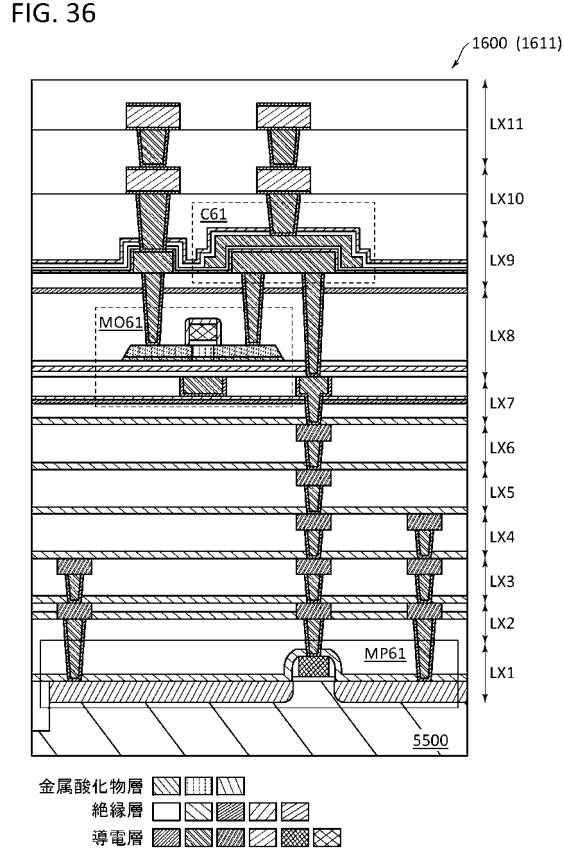

【図36】NOSRAMの断面構成例を示す図。

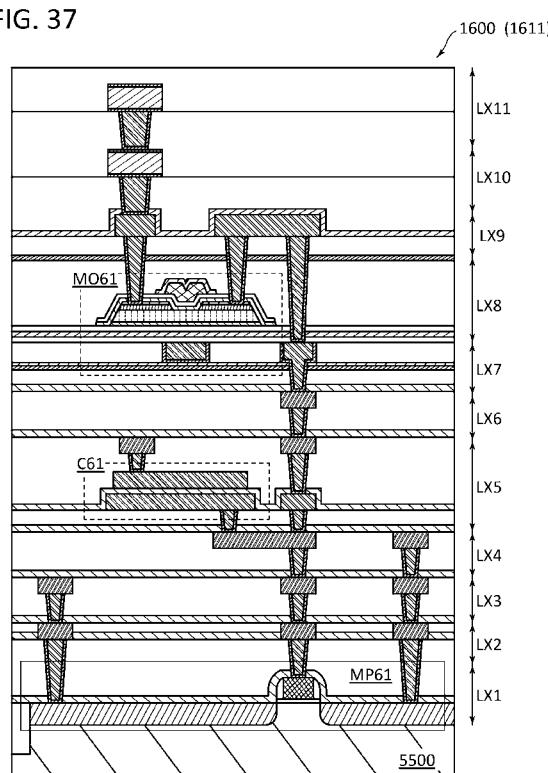

【図37】NOSRAMの断面構成例を示す図。

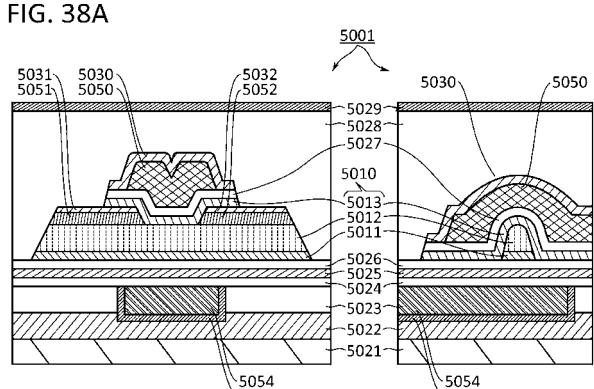

【図38】A、B : OSトランジスタの構成例を示す断面図。

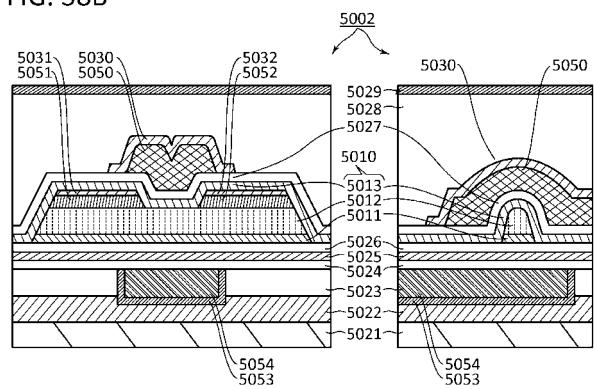

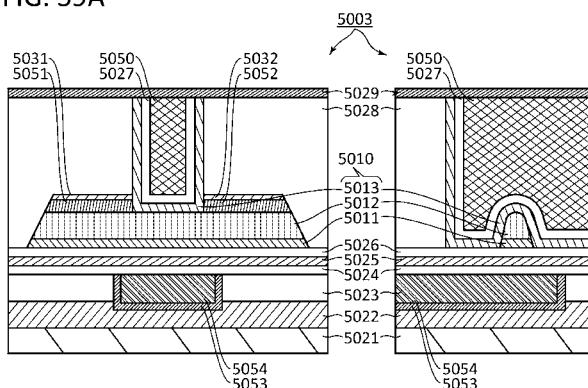

【図39】A、B : OSトランジスタの構成例を示す断面図。

【図40】ERパネルの構成例を示す図。

【図41】A : サブ画素のレイアウト例を示す平面図。B : サブ画素の透過領域と遮光領域とを示す図。

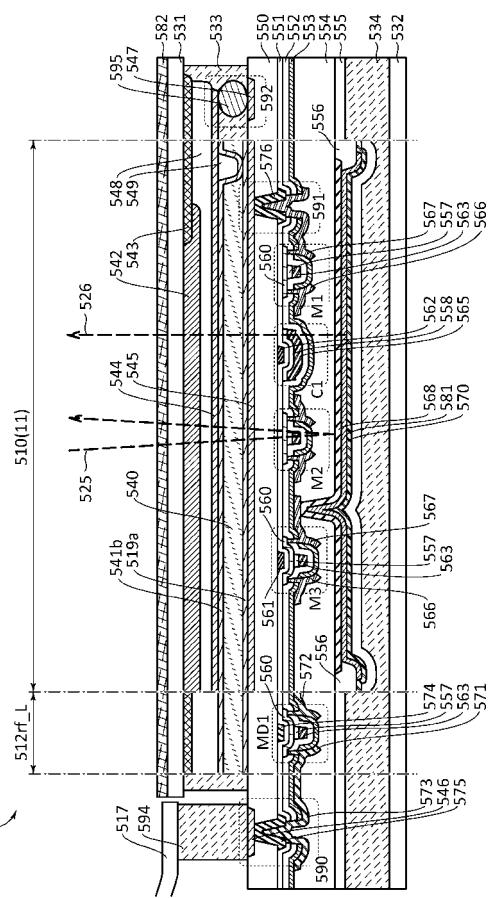

【図42】ERパネルの断面構成例を示す図。

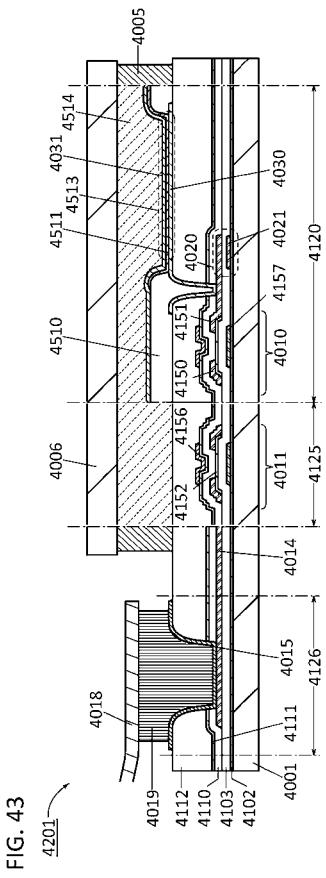

【図43】ELパネルの構成例を示す断面図。

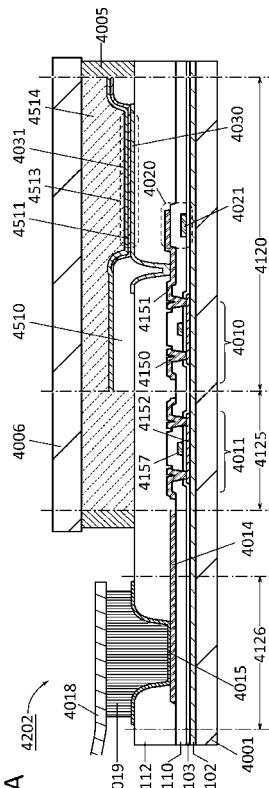

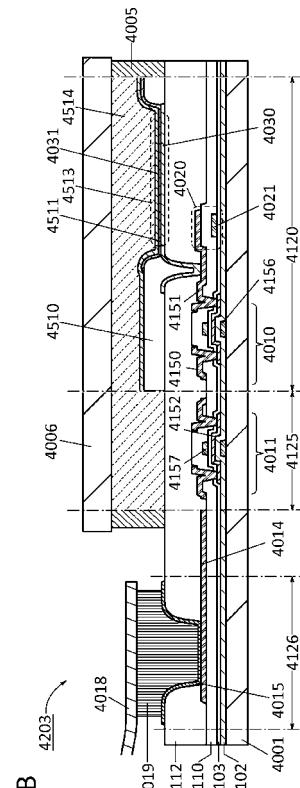

【図44】A、B : ELパネルの構成例を示す断面図。

【発明を実施するための形態】

【0029】

以下に、本発明の実施の形態を説明する。ただし、本発明の一形態は、以下の説明に限定されず、本発明の趣旨およびその範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者であれば容易に理解される。したがって、本発明の一形態は、以下に示す実施の形態の記載内容に限定して解釈されるものではない。

【0030】

以下に示される複数の実施の形態は適宜組み合わせることが可能である。また1の実施の形態の中に、複数の構成例（作製方法例、動作方法例、使用方法例等も含む。）が示される場合は、互いの構成例を適宜組み合わせること、および他の実施の形態に記載された1または複数の構成例と適宜組み合わせることも可能である。

【0031】

図面において、同一の要素または同様な機能を有する要素、同一の材質の要素、あるいは同時に形成される要素等には同一の符号を付す場合があり、その繰り返しの説明は省略する場合がある。

【0032】

また、複数の要素に同じ符号を用いる場合、特に、それらを区別する必要があるときには、符号に“\_1”、“\_2”、“[n]”、“[m, n]”等の識別用の符号を付記して記載する場合がある。

【0033】

本明細書において、例えば、電源電位VDDを、電位VDD、VDD等と省略して記載する場合がある。これは、他の構成要素（例えば、信号、電圧、回路、素子、電極、配線等）についても同様である。

【0034】

〔実施の形態1〕

本実施の形態では、表示システムについて説明する。なお、本明細書等では、発光型（light emitting）表示パネルと反射型（reflective）表示パネルとを複合化した表示パネルを「ERパネル」または「ER表示パネル」と呼ぶ。ERパネルを備える表示システムを「ER表示システム」と呼ぶこととする。

【0035】

<<ER表示システム100>>

図1は、ER表示システムの構成例を示す機能ブロック図である。図1に示すER表示システム100は、ERパネル110、表示コントローラ140、アプリケーションプロセッサ190、メモリ装置191、センサ部193を有する。

【0036】

ERパネル110は画素アレイ111、周辺回路120を有する。ERパネル110は、表示パネルに周辺回路120が実装されている構成であることから、ERパネル110をER表示モジュールと呼ぶこともできる。

10

20

30

40

50

## 【0037】

画素アレイ111は複数のサブ画素11を有する。サブ画素11は反射型表示素子と発光型表示素子とを有する。ここでは、反射型表示素子はLC(液晶)素子RE1であり、発光型表示素子はEL(エレクトロルミネセンス)素子EE1である。周辺回路120は、ゲートドライバ121E、121R、ソースドライバ123E、123Rを有する。

## 【0038】

ERパネルの発光型表示素子、反射型表示素子には特段の制約はない。例えば、発光型表示素子としては、EL素子の他、発光ダイオード、発光トランジスタ、量子ドットまたは量子ロッドを利用した発光素子などがある。例えば、反射型表示素子としては、反射型LC素子の他に、電気泳動方式の表示素子、粒子移動方式の表示素子、または粒子回転方式の表示素子などがある。

10

## 【0039】

LC素子としては、様々なモードが適用されたLC素子を用いることができる。例えば垂直配向(VA: Vertical Alignment)モード、TN(Twisted Nematic)モード、IPS(In Plane Switching)モード、VA IPSモード、FFS(Fringe Field Switching)モード、ASM(Axially Symmetric aligned Microcell)モード、OCB(Optically Compensated Birefringence)モード、FLC(Ferroelectric Liquid Crystal)モード、AFLC(AntiFerroelectric Liquid Crystal)モード、ゲスト-ホストモード等が適用されたLC素子を用いることができる。

20

## 【0040】

垂直配向モードには、MVA(Multi Domain Vertical Alignment)モード、PVA(Patterned Vertical Alignment)モード、ASV(Advanced Super View)モードなどがある。

## 【0041】

暗い環境でもLC素子RE1での表示を可能にするため、ER表示システム100は、画素アレイ111を照明する照明装置を有していてもよい。例えば、照明装置には、光源にLED光源を用いたエッジライト型フロントライトがある。

30

## 【0042】

表示コントローラ140は、ERパネル110を駆動するためのコントローラである。表示コントローラ140は画像処理部150、タイミングコントローラ155、メモリ装置156E、156Rを有する。画像処理部150は、属性付与回路161、フィルタ回路162、データ処理回路163を有する。画像処理部150はさらにレジスタ(図示せず)を有する。レジスタには、画像処理部150が画像データの処理に用いるパラメータ等が格納される。

## 【0043】

メモリ装置191は、画像データなど、アプリケーションプロセッサ190が処理を行うために必要なデータを記憶する。

40

## 【0044】

画像処理部150は、受信した画像データを処理し、反射型表示素子で表示させる画像データと、発光型表示素子で表示させる画像データとを生成する。ここでは、便宜的に、反射型表示素子用の画像データを「LC用画像データ」と呼び、発光型表示素子用の画像データを「EL用画像データ」と呼ぶ。

## 【0045】

画像処理部150は、LC用画像データをソースドライバ123Rに伝送し、EL用画像データをソースドライバ123Eに伝送する。メモリ装置156Eは、EL用画像データのためのフレームメモリとして用いられ、メモリ装置156Rは、LC用画像データのためのフレームメモリとして用いられる。

50

**【 0 0 4 6 】**

アプリケーションプロセッサ 190 は表示コントローラ 140 に各種の信号を送信する。送信する信号には、例えば、クロック信号、同期信号、コマンド信号（IDS、MODE 等）、パラメータ信号（CPARA、GA 等）がある。

**【 0 0 4 7 】**

信号 MODE は、ER パネル 110 の表示モードを設定するための信号である。ER パネルの表示モードは 3 種類に大別される。第 1 の表示モードは、反射型表示素子のみで表示を行うモードであり、第 2 の表示モードは、発光型表示素子のみで表示を行うモードである。第 3 の表示モードは、反射型表示素子と発光型表示素子双方によって表示を行うモードである。ここでは、便宜的に第 1 乃至第 3 の表示モードをそれぞれ、LCD モード、10

ELD モード、ハイブリッドモードと呼ぶこととする。

**【 0 0 4 8 】**

ハイブリッドモードには 2 種類ある。一方は、反射型素子と発光型素子とは共通の画像データを表示するモードである。他方は、反射型表示素子と発光型表示素子とで異なる画像データを表示するモードである。ここでは、便宜的に、前者のハイブリッドモードを HY モードと呼び、後者を TXT (テキスト) モードと呼ぶことにする。

**【 0 0 4 9 】**

信号 IDS は、ER パネル 110 でアイドリング・ストップ (IDS) 駆動を実行するためのコマンド信号である。IDS 駆動とは、通常駆動よりも低いリフレッシュレートで表示パネルを駆動することをいう。IDS 駆動については後述する。

10

20

30

40

**【 0 0 5 0 】**

例えば、アプリケーションプロセッサ 190 は、センサ部 193 で取得したデータ、使用者の操作等による割り込み信号、画像データの属性（動画 / 静止画、カラー画像 / グレースケール画像）等にもとづいて、コマンド信号、パラメータ信号を生成する。

**【 0 0 5 1 】**

例えば、センサ部 193 は、照度を検出する機能、および光の RGB 成分を検出する機能を有する。

**【 0 0 5 2 】**

タイミングコントローラ 155 は、アプリケーションプロセッサ 190 から送信された信号に基づいて、タイミング信号を生成する。タイミング信号は周辺回路 120 の動作タイミングを設定するための信号であり、例えば、クロック信号、スタートパルス信号、パルス幅制御信号などである。

30

**【 0 0 5 3 】**

画像処理部 150 が画像データの処理に用いるパラメータは、パラメータ信号によって設定される。設定されたパラメータは、画像処理部 150 のレジスタに記憶される。画像処理部 150 は、パラメータを用いて、画像データ DT0 を処理し、画像データ DT3\_e 、 DT3\_r を生成する。画像データ DT3\_e は EL 用画像データであり、ソースドライバ 123\_E に送信される。画像データ DT3\_r は LC 用画像データであり、ソースドライバ 123\_R に送信される。

**【 0 0 5 4 】**

なお、図 1 は機能プロック図であり、表示コントローラ 140 の構成は図 1 の構成に限定されない。例えば、画像処理部 150 の処理を 1 の処理回路（例えば、FPGA）で実行する構成であってもよい。或いは、フィルタ回路 162 およびデータ処理回路 163 が行う処理を 1 の処理回路（例えば、FPGA など）で実行する構成であってもよい。

40

**【 0 0 5 5 】**

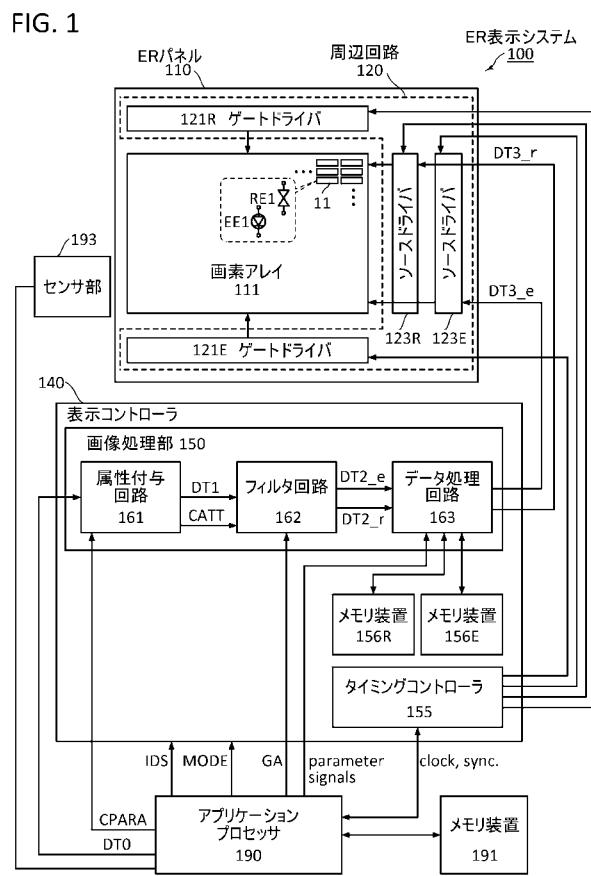

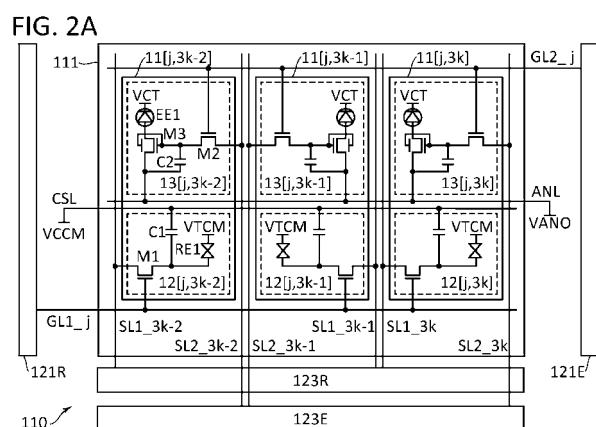

<< ER パネル 110 >>

図 2A、図 2B、図 3A - 図 3C を参照して、ER パネル 110 を説明する。

**【 0 0 5 6 】**

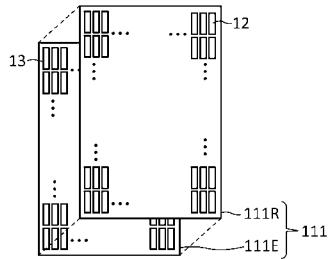

< 画素アレイ 111 、サブ画素 11 >

図 2A は画素アレイ 111 、サブ画素 11 の構成例を示す回路図である。画素アレイ 11

50

1には、ゲート線G L 1、G L 2、ソース線S L 1、S L 2、配線C S L、A N Lを有する。

【0057】

ゲートドライバ121Rはゲート線G L 1を駆動し、ゲートドライバ121Eはゲート線G L 2を駆動する。ソースドライバ123Rはソース線S L 1にL C用データ信号を入力し、ソースドライバ123Eはソース線S L 2にE L用データ信号を入力する。

【0058】

図2Aには、代表的に1行3列に配列された3のサブ画素11を示している。本明細書等において、ゲート線G L 1\_j(jは1以上の整数)は第j行のゲート線G L 1であり、ソース線S L 2\_3k(kは1以上の整数)は、第3k列のソース線S L 2であり、サブ画素11[j, 3k]とは、第j行第3k列のサブ画素11である。また、本明細書等において、複数のゲート線G L 1のうちの1を特定する必要があるときは、ゲート線G L 1\_1等と表記する。また、ゲート線G L 1と記載した場合は、任意のゲート線G L 1を指している。他の要素についても同様である。10

【0059】

サブ画素11はサブ画素12、13を有する。サブ画素12は、ゲート線G L 1、ソース線S L 1、配線C S Lに電気的に接続され、サブ画素13は、ゲート線G L 2、ソース線S L 2、配線A N Lに電気的に接続されている。

【0060】

サブ画素12はL C用画像データを表示するサブ画素であり、トランジスタM 1、容量素子C 1、L C素子R E 1を有する。配線C S Lには、電圧V C C Mが入力される。配線C S Lは、複数のサブ画素12で共有され、各サブ画素12の容量素子C 1が電気的に接続されている。20

【0061】

L C素子R E 1は、一対の電極(画素電極、コモン電極)、および一対の電極に挟まれたL C層を有する。L C素子R E 1の画素電極は、トランジスタM 1に電気的に接続され、L C素子R E 1のコモン電極には、電圧V T C Mが入力される。電圧V T C Mと電圧V C Mとは同じ電圧であってもよいし、異なっていてもよい。

【0062】

サブ画素13はE L用画像データを表示するサブ画素であり、トランジスタM 2、M 3、容量素子C 2、E L素子E E 1を有する。配線A N Lには電圧V A N Oが入力される。配線A N Lは、複数のサブ画素13で共有されており、各サブ画素13の容量素子C 2が電気的に接続されている。30

【0063】

トランジスタM 2は選択トランジスタと呼ばれ、トランジスタM 3は駆動トランジスタと呼ばれる。容量素子C 2はトランジスタM 3のゲート電圧を保持するために設けられている。トランジスタM 3はバックゲートを有する。トランジスタM 3のゲートにバックゲートを電気的に接続し、トランジスタM 3の電流駆動能力を向上させている。

【0064】

E L素子E E 1は、一対の電極(アノード電極、カソード電極)、および一対の電極に挟まれたE L層を有する。図2Aの例では、E L素子E E 1の画素電極がアノード電極であり、コモン電極がカソード電極である。E L素子E E 1の画素電極はトランジスタM 3に電気的に接続され、E L素子E E 1のコモン電極には電圧V C Tが入力される。図2Aの例では、電圧V A N Oは電圧V C Tよりも高い。40

【0065】

E L素子E E 1のE L層は少なくとも発光層を有する。E L層には、電子輸送物質を含む層(電子輸送層)、正孔輸送物質を含む層(正孔輸送層)など、他の機能層を適宜設けることができる。E L素子は、発光物質が有機物である場合は有機E L素子と呼ばれ、無機物である場合は無機E L素子と呼ばれる。

【0066】

10

20

30

40

50

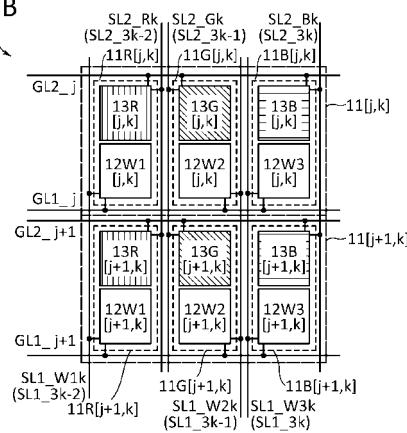

図2Bを参照して画素の構成例を説明する。図2Bの例では、赤色(R)、緑色(G)、青色(B)を表示する3のサブ画素11で、1画素が構成される。

#### 【0067】

サブ画素11Rは、サブ画素12W1、サブ画素13Rで構成され、サブ画素11Gは、サブ画素12W2、サブ画素13Gで構成され、サブ画素11Bは、サブ画素12W3、サブ画素13Bで構成される。サブ画素12W1、12W2、12W3は、白色(W)を表示するサブ画素であり、グレースケール表示用のサブ画素である。

#### 【0068】

本明細書等では、表示色を用いて、構成要素を区別する場合、R、\_R等の識別記号を付すこととする。例えば、サブ画素11Rは赤色のサブ画素11を表す。ソース線SL2\_Gkとは、緑色のデータ信号が入力される第k番のソース線SL2を表している。10

#### 【0069】

<<表示原理>>

図3Aを参照して、ERパネル110の表示原理を説明する。図3AはERパネル110の模式的な断面図である。

#### 【0070】

ERパネル110は基板311、312を有する。基板311と基板312の間に、LC層313、EL素子層314、トランジスタ層315が設けられている。ここでは、サブ画素13R、13G、13Bの各EL素子EE1を塗り分け方式で作製することで、表示色(RGB)で発光させている。20

#### 【0071】

トランジスタ層315には、画素アレイ111を構成する各種の素子、および外部接続用端子が設けられる。トランジスタ層315に設けられる素子としては、トランジスタ、容量素子、整流素子、抵抗素子等がある。トランジスタ層315には、周辺回路120の全てまたは一部の回路を構成する各種の素子が設けられる場合がある。

#### 【0072】

トランジスタ層315に設けられる各種素子(トランジスタ、容量素子等)のデバイス構造には、特段の制約はない。画素アレイ111および周辺回路120に適したデバイス構造を選択すればよい。例えば、トランジスタのデバイス構造には、トップゲート型、ボトムゲート型、およびゲート(フロントゲート)とボトムゲート双方を備えたデュアルゲート型、1つの半導体層に対して複数のゲート電極を有するマルチゲート型が挙げられる。トランジスタの活性層に用いられる半導体としては、単結晶半導体、非単結晶半導体に大別される。非単結晶としては、多結晶半導体、微結晶半導体、非晶質半導体などが挙げられる。半導体材料には、Si、Ge、C等の第14族元素を1種または複数含む半導体(例えば、シリコン、シリコンゲルマニウム、炭化シリコン等)、金属酸化物(酸化物半導体とも呼ばれる。)等が挙げられる。30

#### 【0073】

トランジスタの活性層に適用される金属酸化物は、Zn酸化物、Zn-Sn酸化物、Ga-Sn酸化物、In-Ga酸化物、In-Zn酸化物、In-M-Zn酸化物(Mは、Ti、Ga、Y、Zr、La、Ce、Nd、SnまたはHf)などがある。また、インジウムおよび亜鉛を含む酸化物に、アルミニウム、ガリウム、イットリウム、銅、バナジウム、ベリリウム、ホウ素、シリコン、チタン、鉄、ニッケル、ゲルマニウム、ジルコニウム、モリブデン、ランタン、セリウム、ネオジム、ハフニウム、タンタル、タングステン、またはマグネシウムなどから選ばれた一種、または複数種が含まれていてもよい。40

#### 【0074】

トランジスタ層315には、画素電極320、330が設けられている。画素電極320はLC素子RE1の画素電極であり、光301-303を透過する透過電極である。画素電極330はEL素子EE1の画素電極であり、光301-303を透過する透過電極である。

#### 【0075】

10

20

30

40

50

光301は環境光である。光302はLC素子RE1の反射光である。光303は、EL素子EE1が発する光である。

#### 【0076】

基板311の光301が入射する面には光学フィルム317が設けられている。光学フィルム317には、例えば、偏光フィルム（代表的には、円偏光フィルム）、位相差フィルム、プリズムシート、反射防止フィルム、防眩（アンチグレア）フィルムなどがある。光学フィルム317は複数の光学フィルムの積層であってもよい。光学フィルム317の種類は適宜選択される。例えば、LC素子RE1がゲストホストモードのLC素子である場合は、円偏光フィルムが不要である。

#### 【0077】

基板311のLC層313と対向する面には、コモン電極321が設けられている。コモン電極321はLC素子RE1のコモン電極であり、透過電極である。

#### 【0078】

EL素子EE1は、画素電極330、コモン電極331、EL層で構成される。EL層、コモン電極331はEL素子層314に設けられている。コモン電極331は反射電極である。LC素子RE1は、LC層313、画素電極320、コモン電極321、331で構成される。コモン電極321は透過電極であり、LC層313と対向する面に設けられている。光303の輝度はEL層を流れる電流で制御される。電流は画素電極330とコモン電極331間の電位差によって制御される。光303はコモン電極331で反射され、画素電極330、320、LC層313、コモン電極321、基板311、光学フィルム317を通過する。

#### 【0079】

画素電極320とコモン電極321はLC層313に電界を与える電極対を構成する。電界によって光302の輝度が制御される。電極対が透過電極で構成されているので、光302を取り出すための反射電極が設けられている。この反射電極としてEL素子EE1のコモン電極331が用いられている。このような構成によって、LC素子RE1は反射型表示素子として機能する。

#### 【0080】

光301は光学フィルム317、基板311、コモン電極321、LC層313、画素電極320、330を通過し、コモン電極331で反射される。コモン電極331で反射された光303は画素電極330、320、LC層313、コモン電極321、基板311、光学フィルム317を通過する。

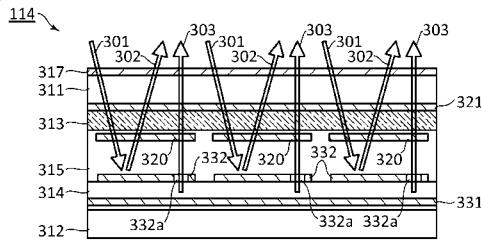

#### 【0081】

<<ERパネル114>>

なお、ERパネルの反射型表示素子の画素電極を反射電極にし、この画素電極で環境光を反射する構成とすることができます。このような構成例を図3Cに示す。ERパネル114はERパネル110の変形例であり、透過型の画素電極330に代えて反射型の画素電極332が設けられている。EL素子EE1の光303を取り出すため、画素電極332には少なくとも1の開口332aが設けられている。

#### 【0082】

<<表示モード>>

図3Aの表示原理に従うと、画素アレイ111は、サブ画素12W1、12W2、12W3で構成される画素アレイ111Rと、サブ画素13R、13G、13Bで構成される画素アレイ111Eとを複合化したものである（図3B参照）。画素アレイ111Eはカラー表示が可能であり、画素アレイ111Rはカラー表示が不可能であり、グレースケール表示を行う。

#### 【0083】

画素アレイ111Rは、反射型表示素子で表示を行うため、グレースケールの静止画を表示するのに適し、また低消費電力のデバイスである。他方、画素アレイ111Eは発光型表示素子で表示を行うため、高コントラスト比であり、色再現性が良い、そのため、カラ

10

20

30

40

50

ー表示に適したデバイスである。

**【0084】**

画素アレイ111Rは白黒表示のみであるため、ER表示システム100のRLCDモードでは、白黒表示のみが可能である。カラー表示は、ハイブリッドモードとELDモードにおいて可能である。

**【0085】**

ER表示システム100がユーザーに提示する画像は、画素アレイ111Eで表示された画像と、画素アレイ111Rで表示された画像とを合わせた画像である。本実施の形態では、画素アレイ111E、111Rの性能の違いを効果的に利用することで、ER表示システム100の性能を拡張している。

10

**【0086】**

<<画像処理部150>>

属性付与回路161は、アプリケーションプロセッサ190から送信される1フレームの画像データについて、1画素ごとに色属性を付与する。フィルタ回路162は、色属性、および使用環境（代表的には、外光の照度およびRGB成分）に応じた画像処理を行い、1フレームの画像データからEL用とLC用の2種類の画像データを生成する。データ処理回路163は、ERパネル110の特性に応じた画像処理をEL用およびLC用画像データに行う。

**【0087】**

ER表示システム100にはLC用とEL用の2種類の画像データが必要になるが、表示コントローラ140は1種類の画像データから2種類の画像データを生成できるため、アプリケーションプロセッサ190から表示コントローラ140へ送信する画像データ量が倍増することが回避できる。よって、アプリケーションプロセッサ190の画像データ送信の際の負荷が軽減されるため、ER表示システム100の動作の安定化につながる。

20

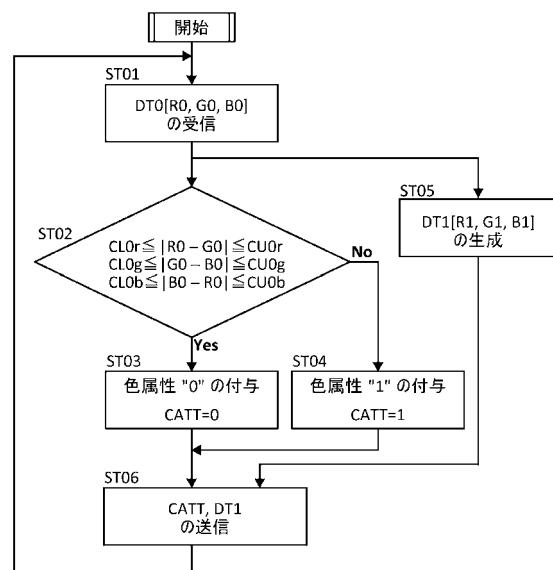

**【0088】**

<属性付与回路161>

図4を参照して、属性付与回路161の動作例を説明する。図4は属性付与回路161の動作例を示すフローチャートである。

**【0089】**

(画像データDT0の受信：ステップST01)

30

属性付与回路161はアプリケーションプロセッサ190が生成した画像データDT0[R0, G0, B0]を受信する。画像データDT0は1画素分の画像データである。R0、G0、B0はR、G、Bの画素値である。

**【0090】**

(色属性の付与：ステップST02-ST04)

属性付与回路161は、画像データDT0から画像データDT1を生成し、かつ画像データDT0の色の分類を行い、その結果に基づき、色属性を画像データDT1に付与する。信号CPARAによって、色の分類のためのパラメータが設定されている。図4の例では、色属性は2種類であり、画像データDT0の色が、特定の色またはこれと類似している色であるか、それ以外の色であるかを分類している。

40

**【0091】**

属性付与回路161はパラメータを用いて、画像データDT0のR、G、Bの画素値を分析し(ステップST02)、分析結果に応じた属性データCATTを生成する(ステップST03、ST04)。属性データCATTは色属性を表しており、ここでは1ビットとしている。

**【0092】**

ステップST02において、属性付与回路161は、下記式(a1)乃至(a3)の比較演算を行う。式中のCL0r、CL0g、CL0b等が信号CPARAによって設定されたパラメータである。CL0r、CL0g、CL0bは同じでも異なっていてもよい。CU0r、CU0g、CU0bは同じでも異なっていてもよい。

50

## 【0093】

|         |           |         |               |

|---------|-----------|---------|---------------|

| C L 0 r | R 0 - G 0 | C U 0 r | · · · ( a 1 ) |

| C L 0 g | G 0 - B 0 | C U 0 g | · · · ( a 2 ) |

| C L 0 b | B 0 - R 0 | C U 0 b | · · · ( a 3 ) |

## 【0094】

式 ( a 1 ) 乃至 ( a 3 ) の比較演算が全て真である場合は、ステップ S T 0 3 が実行され、それ以外の場合はステップ S T 0 4 が実行される。つまり、R、G、B 画素値の差分が設定範囲内である場合、色属性は “ 0 ” であり ( C A T T = 0 ) 、設定範囲外である場合、色属性は “ 1 ” である ( C A T T = 1 ) 。

## 【0095】

( 画像データ D T 1 の生成 : ステップ S T 0 5 )

属性付与回路 1 6 1 は、画像データ D T 0 [ R 0 , G 0 , B 0 ] を複製し、画像データ D T 1 [ R 1 , G 1 , B 1 ] を生成する。なお、画像データ D T 1 は画像データ D T 0 と異なっていてもよい。例えば、R 0 と定数との飽和加算を行い、R 1 を生成してもよい。G 1 、B 1 の生成も同様に行う。飽和加算で用いる定数は信号 C P A R A で設定すればよい。定数は負の数でも正の数でもよい。

## 【0096】

( データの送信 : ステップ S T 0 6 )

属性付与回路 1 6 1 は、属性データ C A T T 、画像データ D T 1 をフィルタ回路 1 6 2 に送信する。1 フレームの画像データを処理するために、ステップ S T 0 1 - S T 0 6 が所定の回数繰り返される。

## 【0097】

< フィルタ回路 1 6 2 >

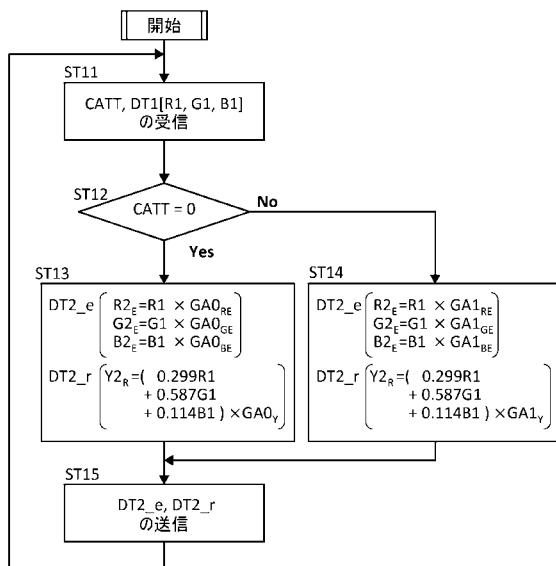

図 5 を参照して、フィルタ回路 1 6 2 の動作例を説明する。図 5 はフィルタ回路 1 6 2 の動作例を示すフローチャートである。

## 【0098】

( データの受信 : ステップ S T 1 1 )

フィルタ回路 1 6 2 は属性回路 1 6 1 が生成した属性データ C A T T 、画像データ D T 1 [ R 1 , G 1 , B 1 ] を受信する。

## 【0099】

( 画像データ D T 2 \_ e 、 D T 2 \_ r の生成 : ステップ S T 1 2 - S T 1 4 )

フィルタ回路 1 6 2 は、色属性を判別し ( ステップ S T 1 2 ) 、判別結果に応じた、調光および調色処理を画像データ D T 1 に行い、画像データ D T 2 \_ e 、 D T 2 \_ r を生成する ( ステップ S T 1 3 、 S T 1 4 ) 。

## 【0100】

画像データ D T 2 \_ e は、1 画素分の E L 用画像データであり、R、G、B の画素値 ( R 2 \_ E , G 2 \_ E , B 2 \_ E ) で構成される。画像データ D T 2 \_ r は 1 画素分の L C 用画像データである。画像データ D T 2 \_ r は、8 ビットの画素値 Y 2 \_ R のみで構成される。ここでは、画像データ D T 2 \_ r は、色相および彩度の属性をもたず、輝度の属性のみをもつ。

## 【0101】

図 5 の例では、画素値 R 1 、 G 1 、 B 1 それぞれにゲイン値を掛けることで、画像データ D T 2 \_ e [ R 2 \_ E , G 2 \_ E , B 2 \_ E ] を得ている。画像データ D T 2 \_ r の生成のための調色処理として、グレースケール変換が行われる。画像データ D T 1 のグレースケール変換によって得られた輝度値に対してゲイン値を掛けることで、画素値 Y 2 \_ R を得ている。

## 【0102】

C A T T = 0 であれば、フィルタ回路 1 6 2 は、下記式 ( a 1 1 ) 乃至 ( a 1 4 ) を実行し、画素値 R 2 \_ E 、 G 2 \_ E 、 B 2 \_ E 、 Y 2 \_ R を算出する。 G A 0 \_ R \_ E 、 G A 0 \_ B \_ E 、 G A 0 \_ G \_ E 、 G A 0 \_ Y はゲイン値である。

10

20

30

40

50

## 【 0 1 0 3 】

$$R_{2_E} = R_1 \times G_A 0_{R_E} \quad \dots (a \ 1 \ 1)$$

$$G_{2_E} = G_1 \times G_A 0_{G_E} \quad \dots (a \ 1 \ 2)$$

$$B_{2_E} = B_1 \times G_A 0_{B_E} \quad \dots (a \ 1 \ 3)$$

## 【 0 1 0 4 】

$$Y_{2_R} = (0.299R_1 + 0.587G_1 + 0.114B_1) G_A 0_Y \quad \dots (a \ 1 \ 4)$$

## 【 0 1 0 5 】

C A T T = 1 であれば、フィルタ回路 1 6 2 は、下記式 ( a 1 5 ) 乃至 ( a 1 8 ) を実行し、画素値  $R_{2_E}$ 、 $G_{2_E}$ 、 $B_{2_E}$ 、 $Y_{2_R}$  を算出する。 $G_A 1_{R_E}$ 、 $G_A 1_{B_E}$ 、 $G_A 1_{G_E}$ 、 $G_A 1_Y$  はゲイン値である。 10

## 【 0 1 0 6 】

$$R_{2_E} = R_1 \times G_A 1_{R_E} \quad \dots (a \ 1 \ 5)$$

$$G_{2_E} = G_1 \times G_A 1_{G_E} \quad \dots (a \ 1 \ 6)$$

$$B_{2_E} = B_1 \times G_A 1_{B_E} \quad \dots (a \ 1 \ 7)$$

## 【 0 1 0 7 】

$$Y_{2_R} = (0.299R_1 + 0.587G_1 + 0.114B_1) G_A 1_Y \quad \dots (a \ 1 \ 8)$$

## 【 0 1 0 8 】

式 ( a 1 4 )、( a 1 8 ) には、規格 I T U - R B T . 6 0 1 で定義されているグレースケールの変換式が用いられているが、グレースケール変換式はこれに限定されない。 20

## 【 0 1 0 9 】

フィルタ回路 1 6 2 が使用するゲイン値は、信号  $G_A$  によって設定される。アプリケーションプロセッサ 1 9 0 は、センサ部 1 9 3 が検出した使用環境の情報（例えば、環境光の照度、R G B 成分）に基づいて、信号  $G_A$  を生成する。さらに、アプリケーションプロセッサは、表示モードに応じてゲイン値を設定する。従って、フィルタ回路 1 6 2 は、使用環境および表示モードに応じた調光および調色処理が可能である。

## 【 0 1 1 0 】

（データの送信：ステップ S T 1 5 ）

フィルタ回路 1 6 2 は画像データ  $D_T 2_e$ 、 $D_T 2_r$  をデータ処理回路 1 6 3 に送信する。データ処理回路 1 6 3 が属性データ C A T T を使用する場合は、属性データ C A T T もデータ処理回路 1 6 3 に送信される。 30

## 【 0 1 1 1 】

フィルタ回路 1 6 2 では、ステップ S T 1 1 S T 1 5 が所定の回数繰り返され、1 フレームの画像データの画素ごとに、画像データ  $D_T 2_e$ 、 $D_T 2_r$  が生成される。

## 【 0 1 1 2 】

フィルタ回路 1 6 2 において、使用環境と色属性とに応じた調光および調色処理を、画素単位で行うことで、1 フレームの E L 用画像データが生成される。属性データ C A T T に応じて、1 画素ごとに、グレースケール変換または黒画像変換が行われ、1 フレームの L C 用画像データが生成される。 40

## 【 0 1 1 3 】

< データ処理回路 1 6 3 >

データ処理回路 1 6 3 は、画像データ  $D_T 2_e$  [  $R_{2_E}$  ,  $G_{2_E}$  ,  $B_{2_E}$  ] 、 $D_T 2_r$  [  $Y_{2_R}$  ] を処理し、画像データ  $D_T 3_e$  [  $R_{3_E}$  ,  $G_{3_E}$  ,  $B_{3_E}$  ] 、 $D_T 3_r$  [  $Y_{3_R}$  ] を生成する。データ処理回路 1 6 3 の代表的な処理はガンマ補正である。ガンマ補正是、表示パネルのガンマ特性に合わせて画像データの輝度を最適化する処理である。データ処理回路 1 6 3 は、異なるガンマ値を用いて画像データ  $D_T 2_e$  と画像データ  $D_T 2_r$  のガンマ補正をそれぞれ行う。

## 【 0 1 1 4 】

サブ画素 1 3 のトランジスタ M 3 の電気特性のばらつきを補正するための処理を、画像データ D T 2 \_ e に行ってもよい。

【 0 1 1 5 】

データ処理回路 1 6 3 は、画像データ D T 3 \_ e 、画像データ D T 3 \_ r をソースドライバ 1 2 3 E 、ソースドライバ 1 2 3 R に送信する。

【 0 1 1 6 】

ソースドライバ 1 2 3 E は画像データ D T 3 \_ e [ R 3 \_ E , G 3 \_ E , B 3 \_ E ] を処理し、ソース線 S L 2 \_ R 、 S L 2 \_ G 、 S L 2 \_ B に書き込む階調信号をそれぞれ生成する。ソースドライバ 1 2 3 R は画像データ D T 3 \_ r [ Y 3 \_ R ] を処理し、ソース線 S L 1 \_ W 1 、 S L 1 \_ W 2 、 S L 1 \_ W 3 に書き込む階調信号を生成する。ソース線 S L 1 \_ W 1 、 S L 1 \_ W 2 、 S L 1 \_ W 3 には、同じ階調値をもつ階調信号が入力されるが、画素アレイ 1 1 1 R の駆動方式（ゲートライン反転駆動、ソースライン反転駆動、フレーム反転駆動、ドット反転駆動）に応じて、ソース線 S L 1 \_ W 2 の階調信号の極性は、ソース線 S L 1 \_ W 1 、 S L 1 \_ W 3 の階調信号と異なる場合がある。

10

【 0 1 1 7 】

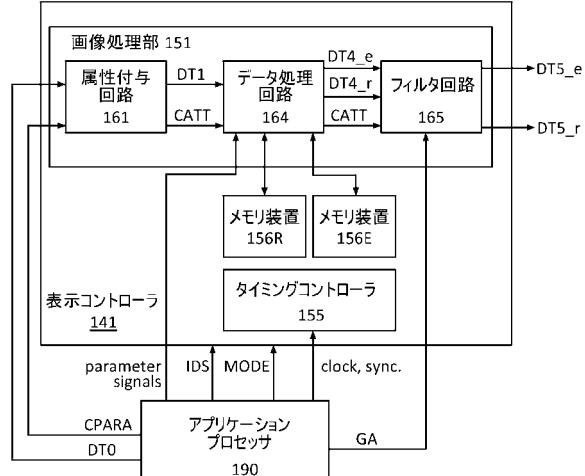

< < 表示コントローラ 1 4 1 > >

図 6 に表示コントローラの他の構成例を示す。図 6 に示す表示コントローラ 1 4 1 は、画像処理部 1 5 1 を有する。画像処理部 1 5 1 は、属性付与回路 1 6 1 、データ処理回路 1 6 4 、フィルタ回路 1 6 5 を有する。画像処理部 1 5 1 は、画像処理の順序が画像処理部 1 5 0 と異なる。

20

【 0 1 1 8 】

属性付与回路 1 6 1 は、画像データ D T 1 [ R 1 , G 1 , B 1 ] 、属性データ C A T T をデータ処理回路 1 6 4 に送信する。

【 0 1 1 9 】

データ処理回路 1 6 4 は、画像データ D T 1 を処理して、画像データ D T 4 \_ e [ R 4 \_ E , G 4 \_ E , B 4 \_ E ] 、 D T 4 \_ r [ R 4 \_ R , G 4 \_ R , B 4 \_ R ] を生成する。データ処理回路 1 6 4 が行う画像処理は、データ処理回路 1 6 3 と同様、ガンマ補正等の E R パネル 1 1 0 の特性に応じたものである。データ処理回路 1 6 4 はフィルタ回路 1 6 5 へ、画像データ D T 4 \_ e [ R 4 \_ E , G 4 \_ E , B 4 \_ E ] 、 D T 4 \_ r [ R 4 \_ R , G 4 \_ R , B 4 \_ R ] 、属性データ C A T T を送信する。

30

【 0 1 2 0 】

フィルタ回路 1 6 5 は、画像データ D T 4 \_ e [ R 4 \_ E , G 4 \_ E , B 4 \_ E ] に対して、属性データ C A T T に応じた調光調色処理を行い、画像データ D T 5 \_ e [ R 5 \_ E , G 5 \_ E , B 5 \_ E ] を生成する。具体的には、画素値 R 4 \_ E 、 G 4 \_ E 、 B 4 \_ E にそれぞれに対して、属性データ C A T T に応じたゲイン値を乗算し、画素値 R 5 \_ E 、 G 5 \_ E 、 B 5 \_ E を求める。

【 0 1 2 1 】

フィルタ回路 1 6 5 は、属性データ C A T T に応じて、画像データ D T 4 \_ r [ R 4 \_ R , G 4 \_ R , B 4 \_ R ] をグレースケール変換して、輝度値を算出し、輝度値と属性データ C A T T に応じたゲイン値との乗算を行うことで、画像データ D T 5 \_ r [ Y 5 \_ R ] を生成する。画像データ D T 5 \_ e 、 D T 5 \_ r はソースドライバ 1 2 3 E 、 1 2 3 R へ送信される。

40

【 0 1 2 2 】

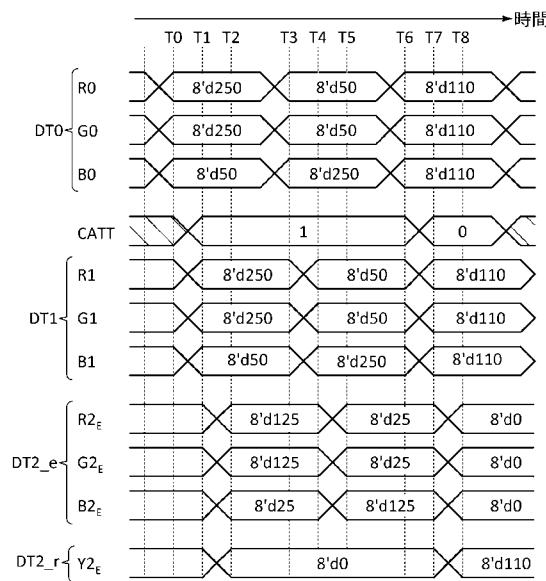

< < 表示モード > >

< T X T モード >

図 7 、図 8 を参照して、 T X T モードを説明する。ここでは、画像データの画素値は 8 ビットとする。

【 0 1 2 3 】

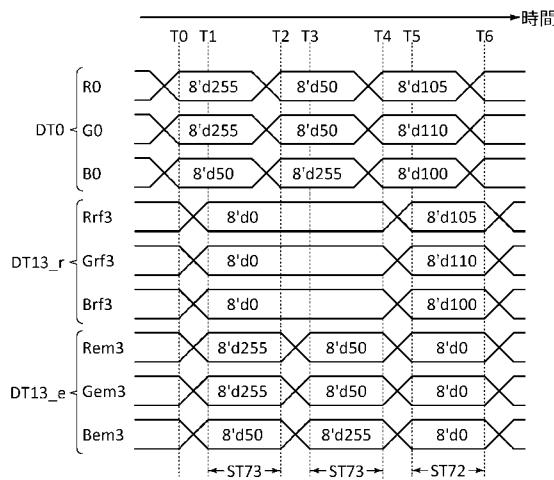

（画像処理部 1 5 0 の動作例）

図 7 は、 T X T モードでの画像処理部 1 5 0 の動作例を示すタイミングチャートである。

50

図7において、T0、T1等は時刻を表す。

【0124】

信号CPARAによって、属性付与回路161が使用するパラメータは以下のように設定されている。つまり、画像データDT0の画素値R0、G0、B0が全て等しい場合のみ、色属性CATTが0になる。

【0125】

$$\begin{aligned} CL0_r &= CL0_g = CL0_b = 0 \\ CU0_r &= CU0_g = CU0_b = 0 \end{aligned}$$

【0126】

信号GAによって、フィルタ回路162が使用するゲイン値は以下のように設定されている。つまり、色属性が“0”的画像データDT1は、LC素子RE1の反射光のみで表示され、他方、色属性が“1”的画像データDT1は、EE素子EE1の光のみで表示されることとなる。

【0127】

$$\begin{aligned} GA0_{RE} &= GA0_{BE} = GA0_{GE} = 0 \\ GA0_Y &= 1 \\ GA1_{RE} &= GA1_{BE} = GA1_{GE} = 0.5 \\ GA1_Y &= 0 \end{aligned}$$

【0128】

T0にて、属性付与回路161は画像データDT0[8'd250, 8'd250, 8'd50]を受信する。期間T0-T1で、属性付与回路161はステップST02-ST05を実行する。

【0129】

$$\begin{aligned} |R0 - G0| &= |250 - 250| = 0 \\ |G0 - B0| &= |250 - 50| = 200 \\ |B0 - R0| &= |50 - 250| = 200 \end{aligned}$$

ステップST02は偽であるので、属性データCATTは“1”である。

【0130】

図7の例では、属性付与回路161は、画像データDT0を複製することで、画像データDT1を生成する。T1で属性付与回路161はフィルタ回路162に画像データDT1[8'd250, 8'd250, 8'd50]、属性データCATT[1]を送信する。

【0131】

T2にて、フィルタ回路162は、画像データDT2\_e、DT2\_rを生成する。属性データCATTは“1”であるので、フィルタ回路162はステップST14を実行する。下記の演算が行われ、画像データDT2\_e[8'd125, 8'd125, 8'd25]、DT2\_r[8'd0]が生成される。

【0132】

$$\begin{aligned} R2_E &= R1 \times 0.5 = 125 \\ G2_E &= G1 \times 0.5 = 125 \\ B2_E &= B1 \times 0.5 = 25 \\ Y2_R &= 0 \end{aligned}$$

【0133】

T3にて、属性付与回路161は画像データDT0[8'd50, 8'd50, 8'd250]を受信する。期間T3-T4で、属性付与回路161はステップST02-ST05を実行する。

【0134】

$$\begin{aligned} |R0 - G0| &= |50 - 50| = 0 \\ |G0 - B0| &= |50 - 250| = 200 \\ |B0 - R0| &= |250 - 50| = 200 \end{aligned}$$

ステップST02の演算結果は偽であるので、属性データCATTは“1”である。

10

20

30

40

50

## 【0135】

T4で属性付与回路161はフィルタ回路162に画像データDT1[8'd50, 8'd50, 8'd250]、属性データCATT[1]を送信する。

## 【0136】

T5にて、フィルタ回路162はステップST14を実行する。下記の演算が行われ、画像データDT2\_e[8'd25, 8'd25, 8'd125]、DT2\_r[8'd0]が生成される。

## 【0137】

$$\begin{aligned} R_{2_E} &= R_1 \times 0.5 = 25 \\ G_{2_E} &= G_1 \times 0.5 = 25 \\ B_{2_E} &= B_1 \times 0.5 = 125 \\ Y_{2_R} &= 0 \end{aligned}$$

10

## 【0138】

T6にて、属性付与回路161は画像データDT0[8'd110, 8'd110, 8'd110]を受信する。期間T6-T7で、属性付与回路161はステップST02-ST05を実行する。

$$\begin{aligned} |R_0 - G_0| &= |110 - 110| = 0 \\ |G_0 - B_0| &= |110 - 110| = 0 \\ |B_0 - R_0| &= |110 - 110| = 0 \end{aligned}$$

20

## 【0139】

ステップST02の論理は真であるので、属性データCATTは“0”である。

## 【0140】

T7で属性付与回路161はフィルタ回路162に画像データDT1[8'd110, 8'd110, 8'd110]、属性データCATT[0]を送信する。

## 【0141】

属性データCATTは“0”であるので、T8にて、フィルタ回路162はステップST13を実行する。下記の演算が行われ、画像データDT2\_e[8'd0, 8'd0, 8'd0]、DT2\_r[8'd110]が生成される。

## 【0142】

$$\begin{aligned} R_{2_E} &= R_1 \times 0 = 0 \\ G_{2_E} &= G_1 \times 0 = 0 \\ B_{2_E} &= B_1 \times 0 = 0 \\ Y_{2_R} &= (0.299R_1 + 0.587G_1 + 0.114B_1) \times 1 = 110 \end{aligned}$$

30

## 【0143】

なお、TXTモードでは、色属性が“1”である場合、サブ画素12に黒画像を表示できればよいので、画像データDT2\_rの画素値Y2\_Rは0に限定されない。つまり、ゲイン値GA1\_Yを0よりも大きくし、画素値Y2\_Rが0よりも大きくなてもよい。

## 【0144】

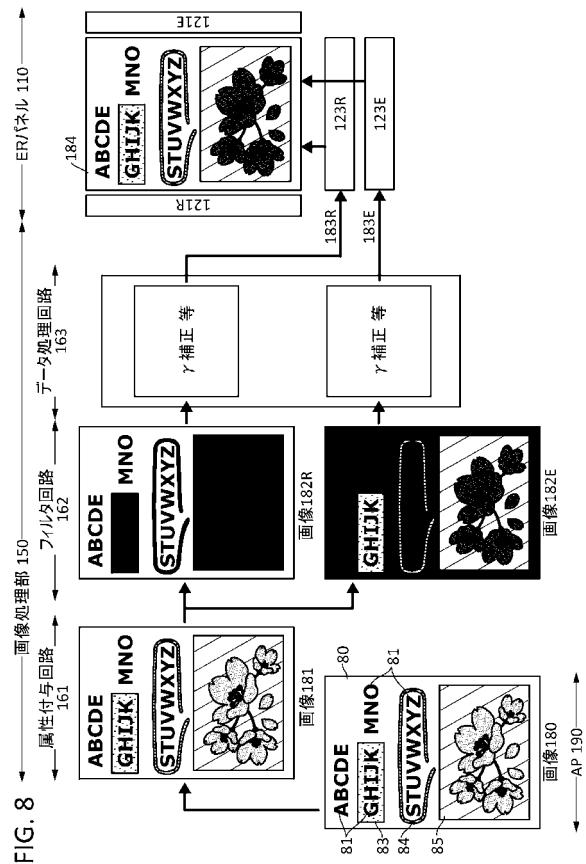

図8を参照して、EL用画像とLC用画像との違いを説明する。図8に示す画像180は、アプリケーションプロセッサ190で生成された1フレーム分の画像である。画像180は背景80、テキスト81、ハイライト83、84、およびカラー写真85で構成される。背景80は白( $R_0 = G_0 = B_0 = 8'd255$ )であり、テキスト81は黒( $R_0 = G_0 = B_0 = 8'd0$ )である。ハイライト83は黄であり、ハイライト84は赤である。なお、便宜的に、カラー写真85は、グレースケール画像( $R_0 = G_0 = B_0$ )を含まないこととする。

40

## 【0145】

画像181は属性付与回路161で生成される画像であり、画像180の複製である。属性付与回路161は画像180の色分類を行い、色属性を決定する。背景80とテキスト81の色属性は“0”に設定され、ハイライト83、84およびカラー写真85の色属性は“1”に設定される。

50

## 【0146】

フィルタ回路162では、画像181を色属性によってフィルタリング処理し、画像182E、182Rを生成する。画像182EはEL用画像である。画像182Eでは、色属性が“0”である画素の色は黒に変換されるため、背景80およびテキスト81は黒画像である。色属性が“1”であるハイライト83、84およびカラー写真85はカラー画像である。

## 【0147】

画像182RはLC用画像である。画像182Rにおいて、色属性が“0”である領域はグレースケール画像であるので、背景80は白であり、テキスト81は黒である。色属性が“1”である領域は黒画像であるので、ハイライト83、84およびカラー写真85は黒である。10

## 【0148】

データ処理回路163は、画像182E、182Rをそれぞれ処理して、画像183E、183Rを生成する。ERパネル110には画像183Eと画像183Rとを合成した画像184が表示される。

## 【0149】

EL素子EE1は、色再現性に優れた表示素子である。ハイライト83、84、カラー写真85の表示はEL素子EE1の発光のみで行われ、LC素子RE1の反射光は寄与しないため、ハイライト83、84、カラー写真85を画像180本来の色で、ERパネル110で表示させることができる。20

## 【0150】

ゲイン値GA1<sub>RE</sub>、GA1<sub>GE</sub>、GA1<sub>BE</sub>を使用環境の照度に応じて設定できるため、使用環境の照度の変化に対応して、EL素子EE1の輝度の調整が可能である。例えば、暗い環境下では、EL素子EE1の輝度を低くすることで、カラー画像の視認性の向上と、ERパネル110の消費電力の低減とが実現できる。

## 【0151】

背景80をLC素子RE1による反射光のみで表示すると、使用環境の照度が低い場合は、背景80が暗くなる場合がある。また、使用環境の色温度（または外光のRGB成分）によっては、背景80の色ずれが大きくなる。そのため、使用環境の照度、色温度に応じて、ゲイン値GA0<sub>RE</sub>、GA0<sub>GE</sub>、GA0<sub>BE</sub>を変更し、背景80をLC素子RE1の反射光とEL素子EE1の光とで表示するとよい。その結果として、背景80の輝度を上げることができる。さらに、背景80の色ずれを補正することができる。30

## 【0152】

<HY・RLCD・ELDモード>

画像処理部150は信号MODEに応じた画像処理を行う。画像処理の内容は、TXTモード以外の表示モードでも同様である。フィルタ回路が用いるゲイン値は、表示モードに関連付けて画像処理部150のレジスタに記憶すればよい。フィルタ回路162は信号MODEにもとづいて、使用するゲイン値を変更する。

## 【0153】

RLCDモードでは、サブ画素13が黒画像を表示するように、データDT2\_eの生成に用いるゲイン値を0に設定する。例えば、GA0<sub>RE</sub>=GA0<sub>BE</sub>=GA0<sub>GE</sub>=0、かつGA1<sub>RE</sub>=GA1<sub>GE</sub>=GA1<sub>BE</sub>=0とする。40

## 【0154】

ELDモードでは、サブ画素12が黒画像を表示するように、データDT2\_rの生成に用いるゲイン値を0に設定する。例えば、GA0Y=0、かつ、GA1Y=0である。

## 【0155】

<<色属性>>

上記の構成例では、色属性の数は2であるが、色属性の数は2以上であればよい。ここでは、色属性の数が4であり、属性データCATTが2ビットである例を示す。

## 【0156】

10

20

30

40

50

## &lt;属性付与回路161の動作例&gt;

図9は、属性付与回路161の動作例を示すフローチャートであり、図4のフローチャートとは属性データCATTの判定のプロセスが異なる。

## 【0157】

(画像データDT0の受信：ステップST20)

属性付与回路161はアプリケーションプロセッサ190が生成した画像データDT0[R0, G0, B0]を受信する。

## 【0158】

(画像データDT1の生成：ステップST21)

ステップST21は、ステップST05と同様である。属性付与回路161は、画像データDT0[R0, G0, B0]を処理し、画像データDT1[R1, G1, B1]を生成する。

10

## 【0159】

(色属性の付与：ステップST22 ST28)

信号CPARAによって、色分類のためのパラメータが設定されている。使用されるパラメータは下記式(b1)乃至(b3)の関係をもつ。

## 【0160】

|      |      |      |      |      |      |     |      |

|------|------|------|------|------|------|-----|------|

| CL2r | CL1r | CL0r | CU0r | CU1r | CU2r | ... | (b1) |

| CL2g | CL1g | CL0g | CU0g | CU1g | CU2g | ... | (b2) |

| CL2b | CL1b | CL0b | CU0b | CU1b | CU2b | ... | (b3) |

## 【0161】

ステップST22において、属性付与回路161は、下記式(b4)乃至(b6)の比較演算を行う。

|                       |     |      |

|-----------------------|-----|------|

| CL0r   R0 - G0   CU0r | ... | (b4) |

| CL0g   G0 - B0   CU0g | ... | (b5) |

| CL0b   B0 - R0   CU0b | ... | (b6) |

## 【0162】

ステップST23において、属性付与回路161は、下記式(b7)乃至(b9)の比較演算を行う。

|                       |     |      |

|-----------------------|-----|------|

| CL1r   R0 - G0   CU1r | ... | (b7) |

| CL1g   G0 - B0   CU1g | ... | (b8) |

| CL1b   B0 - R0   CU1b | ... | (b9) |

## 【0163】

ステップST24において、属性付与回路161は、下記式(b10)乃至(b12)の比較演算を行う。

|                       |     |       |

|-----------------------|-----|-------|

| CL2r   R0 - G0   CU2r | ... | (b10) |

| CL2g   G0 - B0   CU2g | ... | (b11) |

| CL2b   B0 - R0   CU2b | ... | (b12) |

## 【0164】

式(b4)乃至(b6)の比較演算が全て真である場合に、ステップST22は真となり、それ以外の場合は偽である。ステップST23、ST24の論理も同様である。

40

## 【0165】

ステップST22が真である場合、属性データCATTは2'b00に設定される。ステップST23が真である場合、属性データCATTは2'b01に設定される。ステップST24が真である場合、属性データCATTは2'b10に設定される。これら以外の場合、属性データCATTは2'b11に設定される。

## 【0166】

(データの送信：ステップST29)

属性付与回路161は、属性データCATT、画像データDT1をフィルタ回路162に送信する。1フレームの画像データを処理するため、ステップST20 ST29が所定

10

20

30

40

50

の回数繰り返される。

【0167】

<フィルタ回路162の動作例>

図10は、フィルタ回路162の動作例を示すフローチャートである。

【0168】

(データの受信：ステップST30)

フィルタ回路162は属性データCATT、画像データDT1[R1, G1, B1]を受信する。

【0169】

(色属性の判別：ステップST31 ST33)

フィルタ回路162は、属性データCATTを解析し、色属性を判別する。

【0170】

(画像データDT2\_e、DT2\_rの生成：ステップST34-ST37)

フィルタ回路162は、判別結果に応じた処理を画像データDT1に行い、画像データDT2\_e、DT2\_rを生成する。属性データCATTが2'b00の場合、画像処理\_F0が行われる。属性データCATTが2'b01の場合、画像処理\_F1が行われる。属性データCATTが2'b10の場合、画像処理\_F2が行われ、属性データCATTが2'b11の場合、画像処理\_F3が行われる。

【0171】

画像データDT2\_e、DT2\_rを生成するために使用されるゲイン値は、信号GAによって設定されている。

【0172】

(画像処理\_F0：ステップST34)

ステップST34において、フィルタ回路162は、下記式(b21)乃至(b24)を実行し、画素値R2\_E、G2\_E、B2\_E、Y2\_Rを算出する。

【0173】

$$\begin{aligned} R_{2E} &= R_1 \times G_{A0RE} && \cdots (b21) \\ G_{2E} &= G_1 \times G_{A0GE} && \cdots (b22) \\ B_{2E} &= B_1 \times G_{A0BE} && \cdots (b23) \end{aligned}$$

【0174】

$$Y_{2R} = (0.299R_1 + 0.587G_1 + 0.114B_1)GA1_Y \quad \cdots (b24)$$

【0175】

(画像処理\_F1：ステップST35)

ステップST35において、フィルタ回路162は、下記式(b25)乃至(b28)を実行し、画素値R2\_E、G2\_E、B2\_E、Y2\_Rを算出する。

【0176】

$$\begin{aligned} R_{2E} &= R_1 \times G_{A1RE} && \cdots (b25) \\ G_{2E} &= G_1 \times G_{A1GE} && \cdots (b26) \\ B_{2E} &= B_1 \times G_{A1BE} && \cdots (b27) \end{aligned}$$

【0177】

$$Y_{2R} = (0.299R_1 + 0.587G_1 + 0.114B_1)GA1_Y \quad \cdots (b28)$$

【0178】

(画像処理\_F2：ステップST36)

ステップST36において、フィルタ回路162は、下記式(b29)乃至(b32)を実行し、画素値R2\_E、G2\_E、B2\_E、Y2\_Rを算出する。

【0179】

$$\begin{aligned} R_{2E} &= R_1 \times G_{A2RE} && \cdots (b29) \\ G_{2E} &= G_1 \times G_{A2GE} && \cdots (b30) \end{aligned}$$

10

20

30

40

50

$B_{2E} = B_1 \times G_A 2_{BE}$  . . . ( b 31 )

**【 0 1 8 0 】**

$Y_{2R} = (0.299R_1 + 0.587G_1 + 0.114B_1) G_A 2_Y$  . . . ( b 32 )

**【 0 1 8 1 】**

(画像処理\_F3 : ステップST37)

ステップST37において、フィルタ回路162は、下記式( b 33 )乃至( b 36 )を実行し、画素値 $R_{2E}$ 、 $G_{2E}$ 、 $B_{2E}$ 、 $Y_{2R}$ を算出する。**【 0 1 8 2 】**

|                                  |                |    |

|----------------------------------|----------------|----|

| $R_{2E} = R_1 \times G_A 3_{RE}$ | . . . ( b 33 ) | 10 |

| $G_{2E} = G_1 \times G_A 3_{GE}$ | . . . ( b 34 ) |    |

| $B_{2E} = B_1 \times G_A 3_{BE}$ | . . . ( b 35 ) |    |

**【 0 1 8 3 】**

|                                                     |                |  |

|-----------------------------------------------------|----------------|--|

| $Y_{2R} = (0.299R_1 + 0.587G_1 + 0.114B_1) G_A 3_Y$ | . . . ( b 36 ) |  |

|-----------------------------------------------------|----------------|--|

**【 0 1 8 4 】**

(データの送信 : ステップST38)

フィルタ回路162は画像データDT2\_e、DT2\_rをデータ処理回路163に送信する。1フレームの画像データを処理するため、ステップST30 ST38が所定の回数繰り返される。データ処理回路163が属性データCATTを使用する場合は、属性データCATTもデータ処理回路163に送信される。

20**【 0 1 8 5 】**

表示モードがTXTモードである場合、例えば、以下のようにゲイン値を設定する。

**【 0 1 8 6 】**

|                                               |  |    |

|-----------------------------------------------|--|----|

| $G_A 0_{RE} = G_A 0_{BE} = G_A 0_{GE} = 0$    |  |    |

| $G_A 1_{RE} = G_A 1_{BE} = G_A 1_{GE} = 0.25$ |  |    |

| $G_A 2_{RE} = G_A 2_{BE} = G_A 2_{GE} = 0.5$  |  |    |

| $G_A 3_{RE} = G_A 3_{BE} = G_A 3_{GE} = 0.75$ |  |    |

| $G_A 0_Y = 1$                                 |  |    |

| $G_A 1_Y = G_A 2_Y = G_A 3_Y = 0$             |  | 30 |

**【 0 1 8 7 】**

この例では、属性データCATTが2'b00または2'b01であるとき、画像データDT2\_eは黒画像データであり、画像データDT2\_rはグレースケールデータである。色属性が2'b10または2'b11であるとき、画像データDT2\_eはカラー画像データであり、画像データDT2\_rは黒画像データである。

**【 0 1 8 8 】**

&lt;&lt;IDS駆動&gt;&gt;

静止画像データはフレームごとにデータの変化がない。よって、静止画像を表示する場合は、通常駆動と同じ頻度で、サブ画素11、特にサブ画素12のデータの書き換えを行う必要がない。そこで、静止画を表示する際は、通常駆動での1フレーム期間よりも長い時間、サブ画素11のデータの書き換えを一時的に停止するような駆動方法を実行させてもよい。ここでは、このような駆動方法を、「アイドリング・ストップ(IDS)駆動」と呼ぶこととする。IDS駆動では、通常駆動よりも画像データの書き換えが低頻度であるので、ER表示システム100の消費電力は通常動作よりも低い。

40**【 0 1 8 9 】**

例えば、アプリケーションプロセッサ190は、フレーム間で画像データに変更があるか否かを判定し、この判定結果に基づき信号IDSを生成し、表示コントローラ140に送信する。タイミングコントローラ155は信号IDSに基づき、周辺回路120のタイミング信号を生成する。信号IDSは、IDS駆動と通常駆動との切り替え、通常駆動およびIDS駆動のリフレッシュレートを設定するための信号である。例えば、リフレッシュ

レートは、通常駆動では 60 乃至 120 Hz とし、IDS 駆動では 60 Hz 未満、例えば 1 Hz とする。

#### 【0190】

別の例では、IDS 駆動において、画素アレイ 111E のリフレッシュレートは通常駆動と同じにし、画素アレイ 111R のリフレッシュレートは信号 ids により指定されるリフレッシュレートとしてもよい。

#### 【0191】

IDS 駆動でも通常駆動と同じ表示品位を保つために、容量素子 C1 からの電荷のリークをできるだけ少なくすることが望ましい。電荷がリークしてしまうと、LC 素子 RE1 に印加される電圧が変動して、サブ画素 12 の透過率が変化してしまうからである。そのため、トランジスタ M1 はオフ電流が小さいトランジスタであることが好ましい。サブ画素 13 についても同様である。そのため、サブ画素 11 のトランジスタ M1 - M3 は、オフ電流が極めて小さい OS トランジスタで構成されることが好ましい。OS トランジスタのオフ電流が Si トランジスタと比較して極めて小さいのは、金属酸化物のバンドギャップが Si よりも広い（例えば、2.5 eV 以上）からである。

10

#### 【0192】

フィルタ回路 162 において、環境光の照度および色温度（RGB 成分）に応じて、EL 用画像データに対して調光および調色処理が可能である。従って、様々な環境下において、月光下でも真夏の直射日光下でも、高い視認性があり、かつ低消費電力な表示システムを提供することができる。

20

#### 【0193】

<< ER 表示システム 101 >>

以下に、ER 表示システムの他の構成例を説明する。ここでは、ER パネルが、カラー反射型 LC 表示パネルと、カラー EL 表示パネルとを複合化したパネルである例を説明する。

#### 【0194】

図 11 に示す ER 表示システム 101 は、ER 表示システム 100 の変形例であり、ER パネル 110 に代えて、ER パネル 115 を有し、表示コントローラ 140 に代えて表示コントローラ 142 を有する。

30

#### 【0195】

ER パネル 115 は、画素アレイ 116、周辺回路 120 を有する。画素アレイ 116 も画素アレイ 111 と同様に、サブ画素 11 で構成される。画素アレイ 116 の回路構成は画素アレイ 111（図 2A 参照）と同様である。画素アレイ 116 の画素 15 は、サブ画素 12R、12G、12B、サブ画素 13R、13G、13B で構成される（図 12A）。画素アレイ 116 も画素アレイ 111 と同様に、LC 素子 RE1 で構成される画素アレイ 116R と、EL 素子 EE1 で構成される画素アレイ 116E とを複合化したものである（図 12B 参照）。

#### 【0196】

図 12C は ER パネル 115 の模式的な断面図である。ER パネル 115 では、画素アレイ 116R をカラー化するため、カラーフィルタ層 318 が基板 311 とコモン電極 321 との間に設けられている。カラーフィルタ層 318 を設けているので、サブ画素 13R、13G、13B の各 EL 素子 EE1 は白色発光素子でもよいし、表示色（RGB）で発光する発光素子でもよい。

40

#### 【0197】

ER パネル 114（図 3C）にカラーフィルタ層 318 を設けた ER パネルで、ER 表示システム 101 を構成することもできる。

#### 【0198】

<< 表示コントローラ 142 >>

表示コントローラ 142 は表示コントローラ 140 の変形例であり、画像処理部 150 に代えて画像処理部 152 を有する。画像処理部 152 は、属性付与回路 161、フィルタ

50

回路 167、データ処理回路 168 を有する。

【0199】

属性付与回路 161 は、画像データ DT1 [ R1, G1, B1 ]、属性データ CATT をフィルタ回路 167 に送信する。

【0200】

フィルタ回路 167 は、画像データ DT1 に対して、属性データ CATT に応じた調光および調色処理を行い、画像データ DT7\_e [ R7\_E, G7\_E, B7\_E ]、DT7\_r [ R7\_R, G7\_R, B7\_R ] を生成する。

【0201】

データ処理回路 168 は、画像データ DT7\_e、DT7\_r を処理して、画像データ DT8\_e [ R8\_E, G8\_E, B8\_E ]、DT8\_r [ R8\_R, G8\_R, B8\_R ] を生成する。画像データ DT8\_e、DT8\_r はソースドライバ 123E、123R に送信される。

【0202】

< フィルタ回路 167 の動作例 >

図 13 を参照して、フィルタ回路 167 の動作例を説明する。ここでは、属性データ CATT は 2 ビットである。

【0203】

( データの受信 : ステップ ST40 )

フィルタ回路 167 は属性データ CATT、画像データ DT1 [ R1, G1, B1 ] を受信する。

【0204】

( 色属性の判別 : ステップ ST41 ST43 )

フィルタ回路 167 は、属性データ CATT を解析し、色属性を判別する。

【0205】

( 画像データ DT7\_e、DT7\_r の生成 : ステップ ST44 ST47 )

フィルタ回路 167 は、判別結果に応じた処理を画像データ DT1 に行い、画像データ DT7\_e、DT7\_r を生成する。属性データ CATT が 2'b00 の場合、画像処理\_F10 が行われる。属性データ CATT が 2'b01 の場合、画像処理\_F11 が行われる。属性データ CATT が 2'b10 の場合、画像処理\_F12 が行われ、属性データ CATT が 2'b11 の場合、画像処理\_F13 が行われる。

【0206】

( 画像処理\_F10 : ステップ ST44 )

ステップ ST44において、フィルタ回路 167 は、下記式 (c1) 乃至 (c6) を実行し、画素値 R7\_E、G7\_E、B7\_E、R7\_R、G7\_R、B7\_R を算出する。

【0207】

$$\begin{aligned}

R7_E &= R1 \times GA0_{R_E} && \cdots (c1) \\

G7_E &= G1 \times GA0_{G_E} && \cdots (c2) \\

B7_E &= B1 \times GA0_{B_E} && \cdots (c3) \\

R7_R &= R1 \times GA0_{R_R} && \cdots (c4) \\

G7_R &= G1 \times GA0_{G_R} && \cdots (c5) \\

B7_R &= B1 \times GA0_{B_R} && \cdots (c6)

\end{aligned}$$

【0208】

( 画像処理\_F11 : ステップ ST45 )

ステップ ST45において、フィルタ回路 167 は、下記式 (c7) 乃至 (c12) を実行し、画素値 R7\_E、G7\_E、B7\_E、R7\_R、G7\_R、B7\_R を算出する。

【0209】

$$\begin{aligned}

R7_E &= R1 \times GA1_{R_E} && \cdots (c7) \\

G7_E &= G1 \times GA1_{G_E} && \cdots (c8) \\

B7_E &= B1 \times GA1_{B_E} && \cdots (c9)

\end{aligned}$$

10

20

30

40

50

$$\begin{array}{lll}

R_7_R = R_1 \times G_A 1_{RR} & \cdots & (c \quad 10) \\

G_7_R = G_1 \times G_A 1_{GR} & \cdots & (c \quad 11) \\

B_7_R = B_1 \times G_A 1_{BR} & \cdots & (c \quad 12)

\end{array}$$

## 【0210】

(画像処理\_F12:ステップST46)

ステップST46において、フィルタ回路167は、下記式(c 13)乃至(c 18)を実行し、画素値R7E、G7E、B7E、R7R、G7R、B7Rを算出する。

## 【0211】

$$\begin{array}{lll}

R_7_E = R_1 \times G_A 2_{RE} & \cdots & (c \quad 13) \\

G_7_E = G_1 \times G_A 2_{GE} & \cdots & (c \quad 14) \\

B_7_E = B_1 \times G_A 2_{BE} & \cdots & (c \quad 15) \\

R_7_R = R_1 \times G_A 2_{RR} & \cdots & (c \quad 16) \\

G_7_R = G_1 \times G_A 2_{GR} & \cdots & (c \quad 17) \\

B_7_R = B_1 \times G_A 2_{BR} & \cdots & (c \quad 18)

\end{array}$$

## 【0212】

(画像処理\_F13:ステップST47)

ステップST47において、フィルタ回路167は、下記式(c 19)乃至(c 24)を実行し、画素値R7E、G7E、B7E、R7R、G7R、B7Rを算出する。

## 【0213】

$$\begin{array}{lll}

R_7_E = R_1 \times G_A 3_{RE} & \cdots & (c \quad 19) \\

G_7_E = G_1 \times G_A 3_{GE} & \cdots & (c \quad 20) \\

B_7_E = B_1 \times G_A 3_{BE} & \cdots & (c \quad 21) \\

R_7_R = R_1 \times G_A 3_{RR} & \cdots & (c \quad 22) \\

G_7_R = G_1 \times G_A 3_{GR} & \cdots & (c \quad 23) \\

B_7_R = B_1 \times G_A 3_{BR} & \cdots & (c \quad 24)

\end{array}$$

## 【0214】

(データの送信:ステップST48)

フィルタ回路167は画像データDT7\_e、DT7\_rをデータ処理回路168に送信する。1フレームの画像データを処理するため、ステップST40 ST48が所定の回数繰り返される。データ処理回路168が属性データCATTを使用する場合は、属性データCATTもデータ処理回路168に送信される。

## 【0215】

画像データDT7\_e、DT7\_rの生成に使用されるゲイン値は、信号GAによって設定されている。例えば、GA0RE、GA0RR等の値は、表示モードに関連付けて画像処理部152のレジスタに記憶され、フィルタ回路167は信号MODEに基づいて、GA0RE等の値を変更する。

## 【0216】

例えば、表示モードがTXTモードである場合、属性データCATTが2'b00または2'b01であるときは、画像データDT7\_rがグレースケールデータになるようなゲイン値が用いられる。他方、属性データCATTが2'b10または2'b11であるときは、画像データDT7\_rが黒画像データになるようなゲイン値が用いられる。

## 【0217】

画素アレイ116Rはカラー表示が可能であるため、ER表示システム101はRLCDモードでもカラー表示が可能である。例えば、使用環境の明るさに応じて、RLCDモード、HYモード、ELDモード間で表示モードを切り替えることで、高表示品位と低消費電力とが実現できる。

## 【0218】

LC素子RE1の反射光が視認できない暗い環境では、ELDモードで表示を行う。

## 【0219】

環境光の照度が高くなるほど、LC素子RE1の反射光は視認性が向上するが、逆に、E

10

20

30

40

50

L 素子 E E 1 の光は視認性が低下する。そのため、E L 素子 E E 1 の光が視認できないような環境（例えば、晴天の昼間の屋外）では、E L 素子 E E 1 を発光させる必要がないため、R L C D モードで表示を行う。

#### 【0220】

また、L C 素子 R E 1 の反射光を視認できるが、反射光のみでは良好な表示品位が得られないような低照度の環境（照明の無い屋内）では、H Y モードで表示を行う。同様に、E L 素子 E E 1 の光が視認しにくい明るい環境（明るく照明された屋内、曇天の昼間の屋外など）では、H Y モードで表示を行う。H Y モードをサポートすることで、E R 表示システム 1 0 1 は様々な環境において、高品質の表示が可能である。

#### 【0221】

フィルタ回路 1 6 7 において、L C 用およびE L 用画像データに対して、環境光の照度およびR G B 成分に関連付けられた調光および調色処理が可能である。従って、E R 表示システム 1 0 1 は、低消費電力であり、かつ様々な環境下（月光下、真夏の直射日光下）において、高品位のカラー画像表示が可能である。

#### 【0222】

<<表示システム 1 0 5 >>

本実施の形態の表示コントローラが適用可能な表示システムは、E R 表示システムに限定されない。様々な表示システムに適用が可能である。L C パネル、E L パネル、量子ドット（または量子ロッド）パネル、マイクロ L E D パネルなどで表示パネルが構成されている表示システムに適用できる。以下では、E L パネルで構成される表示システムについて説明する。

#### 【0223】

図 1 4 に示す表示システム 1 0 5 は、E L パネル 1 1 7 、表示コントローラ 1 4 5 、アプリケーションプロセッサ 1 9 0 、メモリ装置 1 9 1 、センサ部 1 9 3 を有する。

#### 【0224】

E L パネル 1 1 7 は、画素アレイ 1 1 8 、周辺回路 1 2 5 を有する。周辺回路 1 2 5 はゲートドライバ 1 2 1 E 、ソースドライバ 1 2 3 E を有する。画素アレイ 1 1 8 は、サブ画素 1 3 で構成される。1 画素は、サブ画素 1 3 R 、1 3 G 、1 3 B で構成される。

#### 【0225】

表示コントローラ 1 4 5 は、画像処理部 1 5 3 、タイミングコントローラ 1 5 5 、メモリ装置 1 5 6 E を有する。画像処理部 1 5 3 は、属性付与回路 1 6 1 、フィルタ回路 1 7 2 、データ処理回路 1 7 3 を有する。

#### 【0226】

フィルタ回路 1 7 2 は、画像データ D T 1 に対して、属性データ C A T T に応じた調光および調色処理を行い、画像データ D T 1 2 \_ e [ R 1 2 \_ E , G 1 2 \_ E , B 1 2 \_ E ] を生成する。データ処理回路 1 7 3 は、画像データ D T 1 2 \_ e を処理して、画像データ D T 1 3 \_ e [ R 1 3 \_ E , G 1 3 \_ E , B 1 3 \_ E ] を生成する。画像データ D T 1 3 \_ e はソースドライバ 1 2 3 E に送信される。

#### 【0227】

なお、画像処理部 1 5 3 は、先にデータ処理回路 1 7 3 で画像データ D T 1 を処理し、データ処理回路 1 7 3 で処理した画像データをフィルタ回路 1 7 2 が処理する構成であってもよい。

#### 【0228】

<フィルタ回路 1 7 2 の動作例>

以下に、フィルタ回路 1 7 2 の動作例を説明する。ここでは、属性データ C A T T は 2 ビットである。フィルタ回路 1 7 2 の動作は、フィルタ回路 1 6 7 の動作（図 1 3 参照）と同様である。

#### 【0229】

（データの受信）

フィルタ回路 1 7 2 は、属性データ C A T T 、画像データ D T 1 [ R 1 , G 1 , B 1 ] を

10

20

30

40

50

受信する。

【0230】

(色属性の判別)

次に、フィルタ回路172は、属性データCATTを解析し、色属性を判別する。

【0231】

(画像データDT12\_eの生成)

フィルタ回路172は、色属性の判別結果に応じた処理を画像データDT1に行い、画像データDT12\_eを生成する。属性データCATTが2'b00の場合、画像処理\_F20が行われる。属性データCATTが2'b01の場合、画像処理\_F21が行われる。属性データCATTが2'b10の場合、画像処理\_F22が行われ、属性データCATTが2'b11の場合、画像処理\_F23が行われる。画像処理\_F20乃至F23で使用されるゲイン値は、信号GAによって設定されている。10

【0232】

(画像処理\_F20)

フィルタ回路172は、下記式(d-1)乃至(d-3)を実行し、画素値R12\_E、G12\_E、B12\_Eを算出する。

【0233】

$$\begin{array}{lll} R_{12\_E} = R_1 \times G_{A10\_{R\_E}} & \cdots & (d-1) \\ G_{12\_E} = G_1 \times G_{A10\_{G\_E}} & \cdots & (d-2) \\ B_{12\_E} = B_1 \times G_{A10\_{B\_E}} & \cdots & (d-3) \end{array}$$

20

【0234】

(画像処理\_F21)

フィルタ回路172は、下記式(d-4)乃至(d-6)を実行し、画素値R12\_E、G12\_E、B12\_Eを算出する。

【0235】

$$\begin{array}{lll} R_{12\_E} = R_1 \times G_{A11\_{R\_E}} & \cdots & (d-4) \\ G_{12\_E} = G_1 \times G_{A11\_{G\_E}} & \cdots & (d-5) \\ B_{12\_E} = B_1 \times G_{A11\_{B\_E}} & \cdots & (d-6) \end{array}$$

【0236】

(画像処理\_F22)

フィルタ回路172は、下記式(d-7)乃至(d-9)を実行し、画素値R12\_E、G12\_E、B12\_Eを算出する。30

【0237】

$$\begin{array}{lll} R_{12\_E} = R_1 \times G_{A12\_{R\_E}} & \cdots & (d-7) \\ G_{12\_E} = G_1 \times G_{A12\_{G\_E}} & \cdots & (d-8) \\ B_{12\_E} = B_1 \times G_{A12\_{B\_E}} & \cdots & (d-9) \end{array}$$

【0238】

(画像処理\_F23)

フィルタ回路172は、下記式(d-10)乃至(d-12)を実行し、画素値R12\_E、G12\_E、B12\_Eを算出する。40

【0239】

$$\begin{array}{lll} R_{12\_E} = R_1 \times G_{A13\_{R\_E}} & \cdots & (d-10) \\ G_{12\_E} = G_1 \times G_{A13\_{G\_E}} & \cdots & (d-11) \\ B_{12\_E} = B_1 \times G_{A13\_{B\_E}} & \cdots & (d-12) \end{array}$$

【0240】

(データの送信)

フィルタ回路172は画像データDT12\_eをデータ処理回路173に送信する。データ処理回路173が属性データCATTを使用する場合は、属性データCATTもデータ処理回路173に送信される。1フレームの画像データを処理するため、以上の処理が所定の回数繰り返される。50

**【0241】****[実施の形態2]**

本実施の形態では、ハイブリッド表示パネルを備えた表示システムについて説明する。

**【0242】****<<ER表示システム>>**

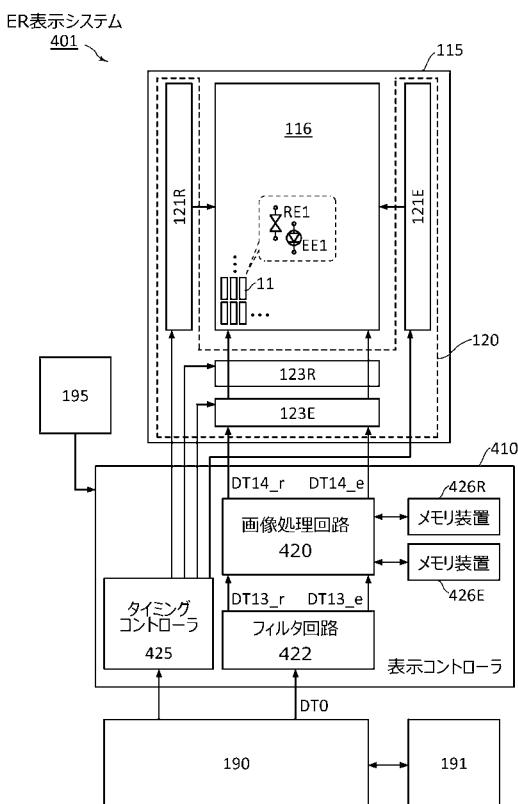

図15は、ER表示システムの構成例を示すブロック図である。図15に示すER表示システム400は、ERパネル110、表示コントローラ410、アプリケーションプロセッサ190、メモリ装置191、光センサ195を有する。

**【0243】**

表示コントローラ410は、ERパネル110のためのコントローラである。表示コントローラ410は、画像処理回路420、フィルタ回路422、タイミングコントローラ425、メモリ装置426E、426Rを有する。

10

**【0244】**

タイミングコントローラ425には、タイミング信号（例えば、クロック信号、同期信号）、およびコマンド信号等がアプリケーションプロセッサ190から送信される。タイミングコントローラ425は、アプリケーションプロセッサ190から送信された信号に基づいて、タイミング信号を生成する。タイミング信号は周辺回路120の動作タイミングを設定するための信号であり、例えば、クロック信号、スタートパルス信号、パルス幅制御信号などがある。

**【0245】**

20

なお、図15は機能ブロック図であり、例えば、画像処理回路420は1の回路で構成されている制約はない。或いは、画像処理回路420、フィルタ回路422が行う処理を1の処理回路（例えば、FPGAなど）で実行する構成であってもよい。

**【0246】**

アプリケーションプロセッサ190は、メモリ装置191から画像データを読み出し、読み出した画像データを処理して、表示コントローラ410に送信する。表示コントローラ410は、受信した画像データをフィルタ回路422でフィルタリング処理し、LC用画像データとEL用画像データとを生成する。表示コントローラ410は、画像処理したLC用画像データをソースドライバ123Rに伝送し、画像処理したEL用画像データをソースドライバ123Eに伝送する。

30

**【0247】**

表示コントローラ410には、LC用画像データを記憶するためのフレームメモリとして、メモリ装置426Rが設けられ、EL用画像データを記憶するためのフレームメモリとして、メモリ装置426Eが設けられている。

**【0248】****<<TXTモード>>**

ER表示システム400は、ER表示システム100と同じ表示モードを備える。図16を参照して、ER表示システム400のTXTモードでの動作例を説明する。ここでは、ER表示システム400が図8に示す画像180を表示する例を説明する。なお、画像180において、ハイライト83、84、カラー写真85はカラー領域であり、背景80、テキスト81は白黒領域である。

40

**【0249】**

TXTモードでは、カラー領域は、画素アレイ111EのEL素子EE1の発光で表示し、画素アレイ111Rは表示に寄与しない。カラー領域以外の領域（上記の白黒領域）は、画素アレイ111RのLC素子RE1の反射光で表示し、画素アレイ111Eは表示に寄与せず、EL素子EE1は非発光である。表示コントローラ410は、画像180に対して、このようなハイブリッド表示のための処理を行う。

**【0250】**

表示コントローラ410において、フィルタ回路422は画像180をフィルタリング処理して、2の画像186E、186Rを生成する。画像186RはLC用画像データであ

50

り、画像 186E は E L 用画像である。画像 180 のカラー領域の階調データは、画像 186R では黒表示の階調データに変換される。図 16 の例では、フィルタリング処理は、画像をカラー領域と白黒領域とに分離する処理に相当する。フィルタ回路 422 の詳しい動作例は後述する。

#### 【0251】

画像処理回路 420 は、画像 186E、186R をそれぞれ処理して、画像 187E、187R を生成する。画像処理回路 420 が行う処理は、ガンマ補正、調光、調色などがある。光センサ 195 で取得した環境光の情報（例えば、照度、色温度）に基づいて、ガンマ補正、調光処理等のための各種パラメータを設定することができる。

#### 【0252】

画像 187E、187R のデータはソースドライバ 123E、123R にそれぞれ送信される。ER パネル 110 には画像 187E と画像 187R とを合成した画像 188 が表示される。

#### 【0253】

TXT モードでは、テキスト 81 と背景 80 の表示には、EL 素子 EE1 の発光は寄与しない。他方、ハイライト 83、84 の表示は EL 素子 EE1 の発光のみで行われ、LC 素子 RE1 は黒表示を行うので、ハイライト 83、84 を際立たせて表示させることができる。同様に、カラー写真 85 は EL 素子 EE1 の発光のみで表示される。よって、視認性の優れた ER 表示システム 400 を提供することができる。

#### 【0254】

TXT モードでは、一部または全ての EL 素子 EE1 を非発光状態にできるので、ER 表示システム 400 の消費電力を低減できる。

#### 【0255】

図 16 に示すように、ER 表示システム 400 では、表示コントローラ 410 において、LC 用と EL 用の 2 種類の画像データの生成が行われる。よって、LC パネルと EL パネルとで別々の画像データを表示させる場合であっても、アプリケーションプロセッサ 190 から表示コントローラ 410 へ送信する画像データ量が 2 倍になることが回避できる。よって、アプリケーションプロセッサ 190 の画像データ送信の際の負荷が軽減されるため、ER 表示システム 400 の動作の安定化につながる。

#### 【0256】

< フィルタ回路 422 の動作例 1 >

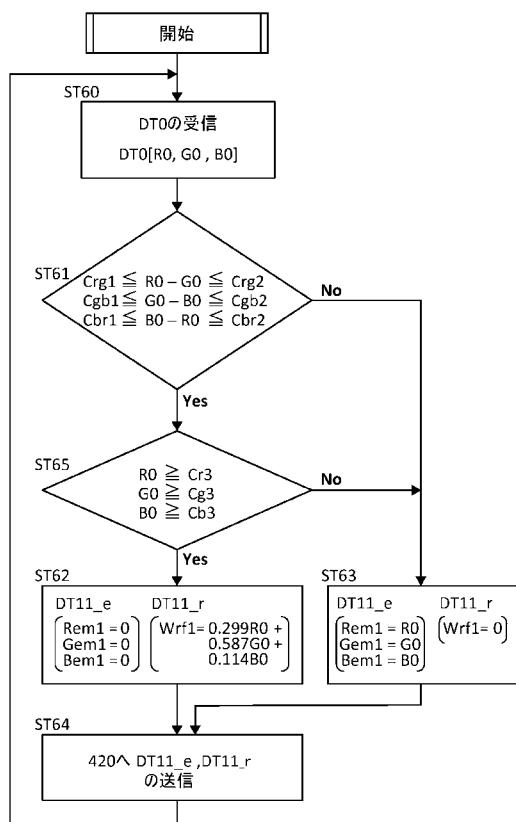

以下、図 17 を参照して、TXT モードでのフィルタ回路 422 の動作例を説明する。ここでは、階調データは 8 ビット (0 255) である。

#### 【0257】

(ステップ ST60)

フィルタ回路 422 はアプリケーションプロセッサ 190 が生成したデータ DT0 [ R0 , G0 , B0 ] を受信する。

#### 【0258】

(ステップ ST61)

フィルタ回路 422 は、画素ごとに、カラー領域に属しているか、白黒領域に属しているかの判定を行う。ステップ ST61 は、データ DT0 がカラーデータであるか否かの判定を行うステップである。具体的には、フィルタ回路 422 は、下記式 (f 1) 乃至 (f 3) の比較演算を行う。式中の Crg1、Crg2、Cgb1 等のパラメータは、表示コントローラ 410 のレジスタに設定されている。Crg1、Cgb1、Cbr1 は同じでも異なっていてもよい。Crg2、Cgb2、Cbr2 は同じでも異なっていてもよい。

#### 【0259】

|      |         |      |           |

|------|---------|------|-----------|

| Crg1 | R0 - G0 | Crg2 | ... (f 1) |

| Cgb1 | G0 - B0 | Cgb2 | ... (f 2) |

| Cbr1 | B0 - R0 | Cbr2 | ... (f 3) |

10

20

30

40

50

## 【0260】

式( $f_1$ )乃至( $f_3$ )の比較演算が全て真である場合は、ステップST62が実行され、それ以外の場合はステップST63が実行される。ステップST61は、RGBデータの差分が設定範囲に含まれていない場合は、データDT0はカラーデータであると判定し、設定範囲内にあれば、データDT0は白黒データであると判定するステップである。なお、ここでいう白黒データは無彩色データのことであり、白黒2値データだけでなく、グレースケールデータも含まれる。

## 【0261】

ステップST62、ST63では、フィルタ回路422はデータDT0からデータDT1<sub>1\_e</sub>、DT11\_rを生成する。データDT11\_eは画像186Eの1画素分の画像データであり、RGBデータ[R<sub>m1</sub>、G<sub>m1</sub>、B<sub>m1</sub>]で構成される。データDT11\_rは画像186Rの1画素分の画像データである。データDT11\_rは、色相および彩度の属性をもたず、輝度データ(W<sub>rf1</sub>)のみで構成される。輝度データも8ビットデータである。

10

## 【0262】

(ステップST62)

ステップST62では、データDT0を黒表示データに変換することで、EL用のデータDT11\_e[R<sub>m1</sub>, G<sub>m1</sub>, B<sub>m1</sub>]を生成する。具体的には、フィルタ回路422は、式( $f_4$ )乃至( $f_6$ )を演算することで、データDT11\_eを生成する。

20

## 【0263】

|                     |             |

|---------------------|-------------|

| R <sub>m1</sub> = 0 | ... (f - 4) |

| G <sub>m1</sub> = 0 | ... (f - 5) |

| B <sub>m1</sub> = 0 | ... (f - 6) |

## 【0264】

ここでは、データDT11\_eのRGBデータを全て“0”にしているが、これに限定されない。データDT11\_eはサブ画素13R、13G、13Bで黒表示を可能にするデータであればよい。

## 【0265】

データDT0をグレースケールデータに変換することで、LC用のデータDT11\_r[W<sub>rf1</sub>]を生成する。具体的には、フィルタ回路422は下記変換式( $f_7$ )を実行する。

30

## 【0266】

$$W_{rf1} = 0.299R_0 + 0.587G_0 + 0.114B_0 \quad \dots (f_7)$$

## 【0267】

ここでは、式( $f_7$ )に、規格ITU-R BT.601で定義されているRGBデータを輝度データに変換する式を適用しているが、RGBデータをグレースケールデータに変換する式は、式( $f_7$ )に限定されない。

40

## 【0268】

(ステップST63)

ステップST63では、フィルタ回路422は、下記変換式( $f_8$ )乃至( $f_{10}$ )を演算して、データDT0からデータDT11\_eを生成する。ここでは、データDT0はそのままデータDT11\_eとして用いられる。

## 【0269】

|                                  |            |

|----------------------------------|------------|

| R <sub>m1</sub> = R <sub>0</sub> | ... (f 8)  |

| G <sub>m1</sub> = G <sub>0</sub> | ... (f 9)  |

| B <sub>m1</sub> = B <sub>0</sub> | ... (f 10) |

## 【0270】

フィルタ回路422は、下記式( $f_{11}$ )を演算し、データDT11\_rを生成する。データDT11\_rは輝度0のデータ(黒表示用データ)である。

50

W r f 1 = 0

· · · ( f 1 1 )

## 【 0 2 7 1 】

(ステップ S T 6 4 )

フィルタ回路 4 2 2 は、データ D T 1 1 \_ e 、 D T 1 1 \_ r を画像処理回路 4 2 0 に送信する。フィルタ回路 4 2 2 は、ステップ S T 6 0 - S T 6 4 のサイクルを画素数と同じ回数繰り返すことで、1 フレーム分のデータ D T 1 1 \_ e とデータ D T 1 1 \_ r を生成する。

## 【 0 2 7 2 】

画像処理回路 4 2 0 は受信したデータ D T 1 1 \_ e 、 D T 1 1 \_ r を処理し、データ D T 1 2 \_ e [ R e m 2 , G e m 2 , B e m 2 ] 、 D T 1 2 \_ r [ W r f 2 ] を生成する。

表示コントローラ 4 1 0 は、データ D T 1 2 \_ e 、 D T 1 2 \_ r をソースドライバ 1 2 3 E 、 1 2 3 R にそれぞれ送信する。

10

## 【 0 2 7 3 】

ソースドライバ 1 2 3 E は、データ D T 1 2 \_ e [ R e m 1 , G e m 1 , B e m 1 ] を処理し、ソース線 S L 2 \_ R 、 S L 2 \_ G 、 S L 2 \_ B に書き込むデータ信号を生成する。ソースドライバ 1 2 3 R は、データ D T 1 2 \_ r [ W r f 2 ] を処理し、ソース線 S L 1 \_ W 1 、 S L 1 \_ W 2 、 S L 1 \_ W 3 に書き込むデータ信号を生成する。ソース線 S L 1 \_ W 1 、 S L 1 \_ W 2 、 S L 1 \_ W 3 のデータ信号は、同じ階調データを持つが、画素アレイ 1 1 1 R の駆動方式（ゲートライン反転駆動、ソースライン反転駆動、フレーム反転駆動、ドット反転駆動）に応じて、ソース線 S L 1 \_ W 2 のデータ信号の極性は、ソース線 S L 1 \_ W 1 、 S L 1 \_ W 3 のデータ信号と異なる場合がある。

20

## 【 0 2 7 4 】

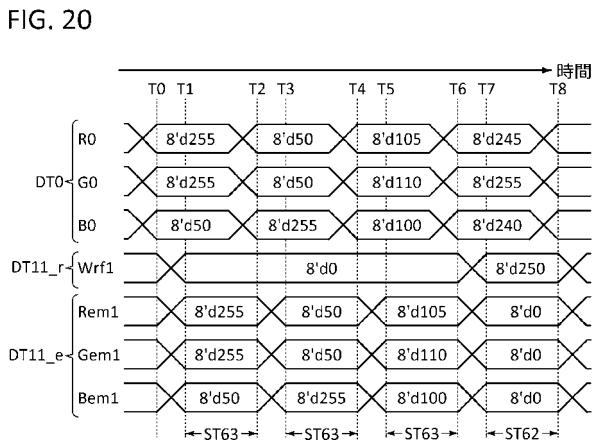

図 1 8 を参照して、フィルタ回路 4 2 2 の動作の具体例を説明する。各パラメータを以下のように設定する。

$$C r g 1 = C g b 1 = C b r 1 = -15$$

$$C r g 2 = C g b 2 = C b r 2 = 15$$

## 【 0 2 7 5 】

T 0 にて、フィルタ回路 4 2 2 はデータ D T 0 [ 8 ' d 2 5 5 , 8 ' d 2 5 5 , 8 ' d 5 0 ] を受信する。T 0 から T 1 の期間にフィルタ回路 4 2 2 はステップ S T 6 1 を実行する。

30

$$R 0 - G 0 = 2 5 5 - 2 5 5 = 0$$

$$G 0 - B 0 = 2 5 5 - 5 0 = 2 0 5$$

$$B 0 - R 0 = 5 0 - 2 5 5 = -2 0 5$$

であるので、式 ( f 1 ) は真であり、式 ( f 2 ) 、 ( f 3 ) は偽である。

## 【 0 2 7 6 】

よって、ステップ S T 6 1 は偽であるので、T 1 から T 2 の期間に、フィルタ回路 4 2 2 はステップ S T 6 3 を実行する。下記の演算を行い、データ D T 1 1 \_ r 、 D T 1 1 \_ e を生成する。

$$R e m 1 = R 0 = 8 ' d 2 5 5$$

40

$$G e m 1 = G 0 = 8 ' d 2 5 5$$

$$B e m 1 = B 0 = 8 ' d 5 0$$

$$W r f 1 = 8 ' d 0$$

## 【 0 2 7 7 】

T 1 から所定の時間経過すると、フィルタ回路 4 2 2 は、生成したデータ D T 1 1 \_ r [ 8 ' d 0 ] 、データ D T 1 1 \_ e [ 8 ' d 2 5 5 , 8 ' d 2 5 5 , 8 ' d 5 0 ] を画像処理回路 4 2 0 に送信を開始する（ステップ S T 6 4 ）。

## 【 0 2 7 8 】

T 2 にて、フィルタ回路 4 2 2 はデータ D T 0 [ 8 ' d 5 0 , 8 ' d 5 0 , 8 ' d 2 5 5 ] を受信する。T 2 から T 3 の期間に、フィルタ回路 4 2 2 はステップ S T 6 1 を実行する。

50

R 0 - G 0 = 5 0 - 5 0 = 0

G 0 - B 0 = 5 0 - 2 5 5 = - 2 0 5

B 0 - R 0 = 2 5 5 - 5 0 = 2 0 5

であるので、式 (f 1) は真であり、式 (f 2)、(f 3) は偽である。

#### 【0279】

よって、T 3 から T 4 の期間に、フィルタ回路 422 はステップ ST 63 を実行する。下記の演算を行い、データ DT11\_r、DT11\_e を生成する。

R em1 = R 0 = 8 ' d 5 0

G em1 = G 0 = 8 ' d 5 0

B em1 = B 0 = 8 ' d 2 5 5

W r f1 = 8 ' d 0

10

#### 【0280】

T 3 から所定の時間経過すると、フィルタ回路 422 は、生成したデータ DT11\_r [8 ' d 0]、データ DT11\_e [8 ' d 5 0, 8 ' d 5 0, 8 ' d 2 5 5] を画像処理回路 420 に送信を開始する（ステップ ST 64）。

#### 【0281】

T 4 にて、フィルタ回路 422 は、データ DT0 [8 ' d 1 0 5, 8 ' d 1 1 0, 8 ' d 1 0 0] を受信する。T 4 から T 5 の期間に、フィルタ回路 422 はステップ ST 61 を実行する。

R 0 - G 0 = 1 0 5 - 1 1 0 = - 5

G 0 - B 0 = 1 1 0 - 1 0 0 = 1 0

B 0 - R 0 = 1 0 0 - 1 0 5 = - 5

20

であるので、ステップ ST 61 は真である。

#### 【0282】

T 5 から T 6 の期間に、フィルタ回路 422 はステップ ST 62 を実行し、データ DT11\_r、DT11\_e を生成する。式 (f 7) から、W r f1 = 0 . 2 9 9 × 1 0 5 + 0 . 5 8 7 × 1 1 0 + 0 . 1 1 4 × 1 0 0 であり、DT11\_r は [8 ' d 1 0 8] である。式 (f 4) 乃至 (f 6) から、DT11\_e は [8 ' d 0, 8 ' d 0, 8 ' d 0] である。

30

#### 【0283】

T 5 から所定の時間経過すると、フィルタ回路 422 は、生成したデータ DT11\_r [8 ' d 1 0 8]、データ DT11\_e [8 ' d 0, 8 ' d 0, 8 ' d 0] を画像処理回路 420 に送信を開始する（ステップ ST 64）。

#### 【0284】

< フィルタ回路 422 の動作例 2 >

図 19 を参照して、TX T モードでのフィルタ回路 422 の他の動作例を説明する。図 19 に示す動作フローは、図 17 の動作フローの変形例であり、ステップ ST 65 が追加されている。ステップ ST 61 とステップ ST 65 とにより、データ DT0 がカラーデータであるか否かの判定が行われる。

#### 【0285】

40

(ステップ ST 65)

ステップ ST 61 が真である場合、ステップ ST 65 は実行される。フィルタ回路 422 は、下記式 (f 12) 乃至 (f 14) の比較演算を行う。式中の Cr3、Cg3、Cb3 はフィルタ回路 422 が使用するパラメータであり、表示コントローラ 410 のレジスタに設定されている。Cr3、Cg3、Cb3 はフィルタリング処理のしきい値である。Cr3、Cg3、Cb3 は同じでも異なっていてもよい。

#### 【0286】

|     |     |              |

|-----|-----|--------------|

| R 0 | Cr3 | · · · (f 12) |

| G 0 | Cg3 | · · · (f 13) |

| B 0 | Cb3 | · · · (f 14) |

50

**【0287】**

式( $f_{12}$ )乃至( $f_{14}$ )の比較演算が全て真である場合は、ステップST62が実行され、それ以外の場合はステップST63が実行される。つまり、式( $f_1$ )乃至( $f_3$ )および( $f_{12}$ )乃至( $f_{14}$ )が全て真である場合、ステップST62が実行され、それ以外の場合は、ステップST63が実行される。

**【0288】**

ステップST65で判定されるデータDT0は、ステップST61でグレースケールデータであると判定されたデータである。よって、ステップST65を実行することで、グレースケールデータの中から、RGBデータが全てしきい値以上であるデータを抽出することができる。LC素子RE1が表示するデータDT12\_rは、ステップST65で抽出されたグレースケールデータである。10

**【0289】**

図20を参照して、動作例2の具体例を説明する。以下のようにパラメータを設定する。

```

C_rg1 = C_gb1 = C_b1r = -15

C_rg2 = C_gb2 = C_b1r = 15

C_r3 = C_g3 = C_b3 = 200

```

**【0290】**

この場合、ステップST65によって、グレースケールデータの中から、白表示データとそれに近い高階調データが抽出される。データDT0がこのようなグレースケールデータである場合は、データDT0はLC素子RE1でグレースケール表示される。それ以外の場合は、データDT0はEL素子EE1でカラー表示される。20

**【0291】**

(期間T0-T2)

フィルタ回路422は、データDT0[8'd255, 8'd255, 8'd50]を受信する。ステップST61の比較演算の結果は偽であるので、フィルタ回路422はステップST63を実行し、データDT11\_r[8'd0]、データDT11\_e[8'd255, 8'd255, 8'd50]を生成し、生成したデータDT11\_r、DT11\_eを画像処理回路420に送信する。

**【0292】**

(期間T2-T4)

フィルタ回路422は、データDT0[8'd50, 8'd50, 8'd255]を受信する。ステップST61の比較演算の結果は偽であるので、フィルタ回路422はステップST63を実行し、データDT11\_r[8'd0]、データDT11\_e[8'd50, 8'd50, 8'd255]を生成し、生成したデータDT11\_r、DT11\_eを画像処理回路420に送信する。30

**【0293】**

(期間T4-T6)

フィルタ回路422は、データDT0[8'd105, 8'd110, 8'd100]を受信する。ステップST61は真であるが、ST65は偽であるので、フィルタ回路422はステップST63を実行し、データDT11\_r[8'd0]、データDT11\_e[8'd105, 8'd110, 8'd100]を生成し、生成したデータDT11\_r、DT11\_eを画像処理回路420に送信する。40

**【0294】**

データDT0[8'd105, 8'd110, 8'd100]に対する判定結果は、上掲の動作例1ではグレースケールデータであり、動作例2ではカラーデータである。当該データDT0の表示方法は、動作例1、2とで異なる。

**【0295】**

動作例2では、データDT0がステップST61の全ての条件を満たしていても、データDT0のRGBデータの何れか1つでもしきい値よりも小さい場合は、データDT0はEL素子EE1でカラー表示され、LC素子RE1は表示に寄与しない。フィルタ回路4250

2のパラメータを最適化することで、グレースケールデータであっても中間階調の画像データである場合は、EL素子EE1のみで表示させることができる。例えば、自然物など中間階調を多く含むカラー画像と、テキストおよび背景（2値画像）とで構成される画像の表示品位を向上できる。

## 【0296】

(期間T6-T8)

フィルタ回路422は、データDT0[8'd245, 8'd255, 8'd240]を受信する。ステップST61は真であり、かつステップST65は真であるので、フィルタ回路422はステップST62を実行し、データDT11\_r[8'd250]、データDT11\_e[8'd0, 8'd0, 8'd0]を生成し、生成したデータDT11\_r、DT11\_eを画像処理回路420に送信する。

10

## 【0297】

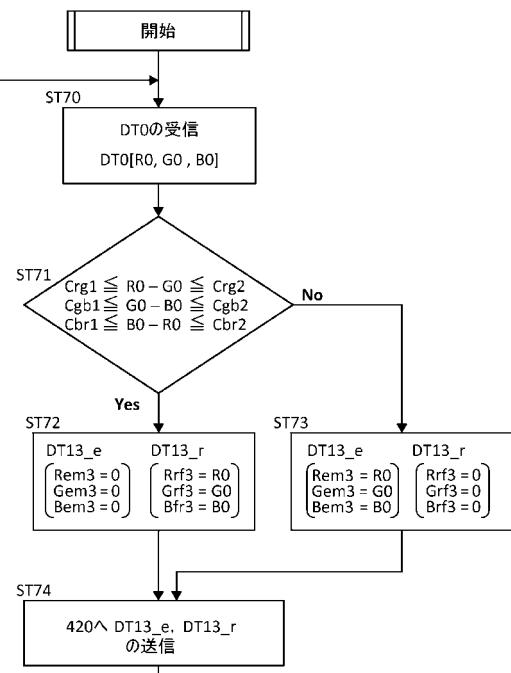

&lt;&lt;ER表示システム&gt;&gt;

図21に示すER表示システム401は、ER表示システム400の変形例であり、ERパネル110に代えて、ERパネル115を有する。フィルタ回路422は、アプリケーションプロセッサ190から送信されたデータDT0を処理し、データDT13\_r、DT13\_eを生成する。画像処理回路420は、データDT13\_r、DT13\_eをそれぞれ処理し、データDT14\_r、DT14\_eを生成する。

## 【0298】

&lt;フィルタ回路422の動作例3&gt;

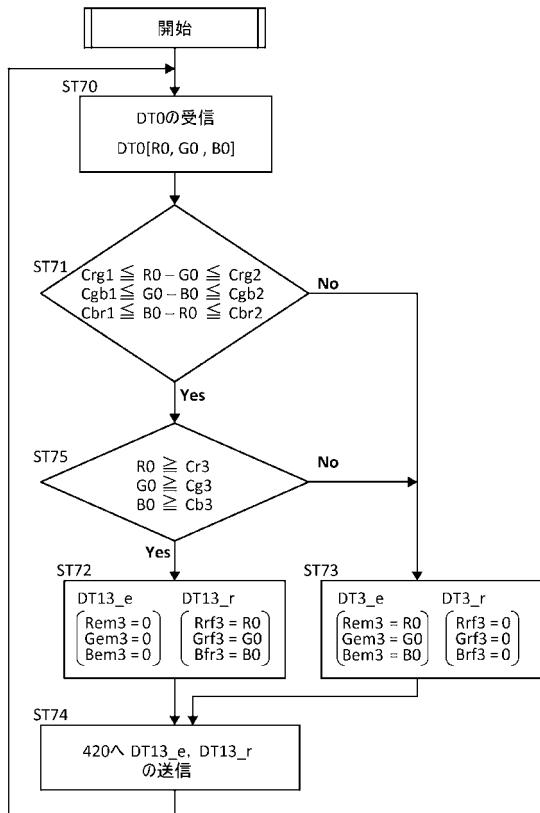

図22を参照して、TXTモードでのフィルタ回路422の動作例を説明する。図22に示す動作フローのステップST70-ST74は、動作例1のステップST60-ST64に対応する。

20

## 【0299】

(ステップST70)

ステップST70はステップST60と同じである。フィルタ回路422はアプリケーションプロセッサ190が生成したデータDT0[R0、G0、B0]を受信する。

## 【0300】

(ステップST71)

ステップST71はステップST61と同じである。フィルタ回路422は、下記式(f21)乃至(f23)の比較演算を行う。

30

## 【0301】

|         |           |         |                 |

|---------|-----------|---------|-----------------|

| C r g 1 | R 0 - G 0 | C r g 2 | · · · ( f 2 1 ) |

| C g b 1 | G 0 - B 0 | C g b 2 | · · · ( f 2 2 ) |

| C b r 1 | B 0 - R 0 | C b r 2 | · · · ( f 2 3 ) |

## 【0302】

式(f21)乃至(f23)の比較演算が全て真である場合は、ステップST72が実行され、それ以外の場合はステップST73が実行される。ステップST72、ST73では、フィルタ回路422はデータDT0からデータDT13\_e、DT13\_rを生成する。データDT13\_eは1画素分の画像データであり、RGBデータ[R e m 3, G e m 3, B e m 3]で構成される。データDT13\_rは1画素分の画像データであり、RGBデータ[R r f 3, G r f 3, B r f 3]で構成される。

40

## 【0303】

(ステップST72)

ステップST72では、データDT0を黒表示データに変換することで、EL用のデータDT13\_e[R e m 3, G e m 3, B e m 3]を生成する。具体的には、フィルタ回路422は、式(f24)乃至(f26)を演算することで、データDT13\_eを生成する。

## 【0304】

R e m 3 = 0                    · · · ( f 2 4 )

50

G e m 3 = 0                    . . . ( f    2 5 )

B e m 3 = 0                    . . . ( f    2 6 )

## 【 0 3 0 5 】

データ D T 1 3 \_ e の R G B データを全て “ 0 ” にしているが、これに限定されない。データ D T 1 3 \_ e はサブ画素 1 3 R 、 1 3 G 、 1 3 B の黒表示を可能にするデータであればよい。

## 【 0 3 0 6 】

フィルタ回路 4 2 2 は、下記変換式 ( f    2 7 ) 乃至 ( f    2 9 ) を演算して、データ D T 0 からデータ D T 1 3 \_ r を生成する。ここでは、データ D T 0 はそのままデータ D T 1 3 \_ r として用いられる。

10

## 【 0 3 0 7 】

R r f 3 = R 0                    . . . ( f    2 7 )

G r f 3 = G 0                    . . . ( f    2 8 )

B r f 3 = B 0                    . . . ( f    2 9 )

## 【 0 3 0 8 】

(ステップ S T 7 3 )

ステップ S T 7 3 では、フィルタ回路 4 2 2 は、下記変換式 ( f    3 0 ) 乃至 ( f    3 2 ) を演算して、データ D T 0 からデータ D T 1 3 \_ e を生成する。ここでは、データ D T 0 はそのままデータ D T 1 3 \_ e として用いられる。

20

## 【 0 3 0 9 】

R e m 3 = R 0                    . . . ( f    3 0 )

G e m 3 = G 0                    . . . ( f    3 1 )

B e m 3 = B 0                    . . . ( f    3 2 )

## 【 0 3 1 0 】

フィルタ回路 4 2 2 は、データ D T 0 を黒表示データに変換することで、データ D T 1 3 \_ r を生成する。そのため、フィルタ回路 4 2 2 は、下記式 ( f    3 3 ) 乃至 ( f    3 5 ) を演算する。

## 【 0 3 1 1 】

R r f 3 = 0                    . . . ( f    3 3 )

G r f 3 = 0                    . . . ( f    3 4 )

B r f 3 = 0                    . . . ( f    3 5 )

30

## 【 0 3 1 2 】

データ D T 1 3 \_ r の R G B データを全て “ 0 ” にしているが、これに限定されない。データ D T 1 3 \_ r はサブ画素 1 2 R 、 1 2 G 、 1 2 B の黒表示を可能にするデータであればよい。

## 【 0 3 1 3 】

(ステップ S T 7 4 )

フィルタ回路 4 2 2 は、データ D T 1 3 \_ e 、 D T 1 3 \_ r を画像処理回路 4 2 0 に送信する。フィルタ回路 4 2 2 は、ステップ S T 7 0 - S T 7 4 のサイクルを画素の数と同じ回数繰り返すことで、1フレーム分のデータ D T 1 3 \_ e 、 D T 1 3 \_ r を生成する。

40

## 【 0 3 1 4 】

画像処理回路 4 2 0 は受信したデータ D T 1 3 \_ e 、 D T 1 3 \_ r を処理し、データ D T 1 4 \_ e [ R e m 4 , G e m 4 , B e m 4 ] 、 D T 1 4 \_ r [ R r f 4 , G r f 4 , B r f 4 ] を生成する。表示コントローラ 4 1 0 は、データ D T 1 4 \_ e 、 D T 1 4 \_ r をソースドライバ 1 2 3 E 、 1 2 3 R にそれぞれ送信する。

## 【 0 3 1 5 】

ソースドライバ 1 2 3 E は、データ D T 1 4 \_ e [ R e m 4 , G e m 4 , B e m 4 ] を処理し、ソース線 S L 2 \_ R 、 S L 2 \_ G 、 S L 2 \_ B に書き込むデータ信号を生成する。ソースドライバ 1 2 3 R は、データ D T 1 4 \_ r [ R r f 4 , G r f 4 , B r f 4 ] を処理し、ソース線 S L 1 \_ R 、 S L 1 \_ G 、 S L 1 \_ B に書き込むデータ信号を生成する。

50

## 【0316】

図23を参照して、動作例3の具体例を説明する。以下のようにパラメータを設定する。

```

C r g 1 = C g b 1 = C b r 1 = - 1 5

C r g 2 = C g b 2 = C b r 2 = 1 5

```

## 【0317】

(期間T0-T2)

フィルタ回路422は、データDT0[8'd255, 8'd255, 8'd50]を受信する。ステップST71は偽であるので、フィルタ回路422はステップST73を実行し、データDT13\_r[8'd0, 8'd0, 8'd0]、データDT13\_e[8'd255, 8'd255, 8'd50]を生成する。生成されたデータDT13\_r、DT13\_eは画像処理回路420に送信される。

10

## 【0318】

(期間T2-T4)

フィルタ回路422は、データDT0[8'd50, 8'd50, 8'd255]を受信する。ステップST71は偽であるので、フィルタ回路422はステップST73を実行し、データDT13\_r[8'd0, 8'd0, 8'd0]、データDT13\_e[8'd50, 8'd50, 8'd255]を生成する。生成されたデータDT13\_r、DT13\_eは画像処理回路420に送信される。

20

## 【0319】

(期間T4-T6)

フィルタ回路422は、データDT0[8'd105, 8'd110, 8'd100]を受信する。ステップST71は真であるので、フィルタ回路422はステップST72を実行し、データDT13\_r[8'd105, 8'd110, 8'd100]、データDT13\_e[8'd0, 8'd0, 8'd0]を生成する。生成されたデータDT13\_r、DT13\_eは画像処理回路420に送信される。

30

## 【0320】

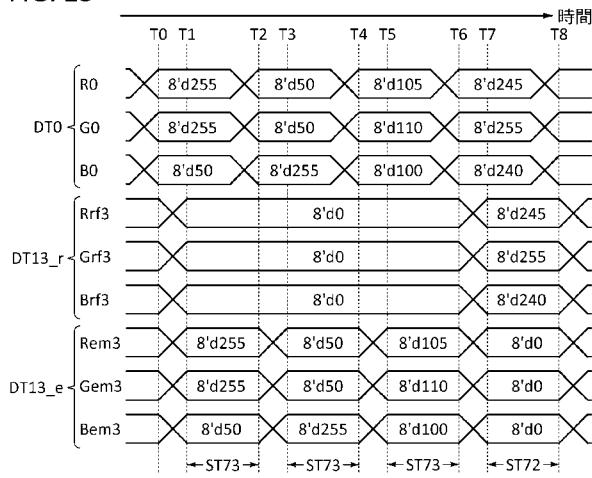

<フィルタ回路422の動作例4>

図24を参照して、TXTモードでのフィルタ回路422の他の動作例を説明する。図24に示す動作フローは、図22の動作フローの変形例であり、ステップST75が追加されている。ステップST71とステップST75とにより、データDT0がカラーデータであるか否かの判定が行われる。

30

## 【0321】

(ステップST75)

ステップST71が真である場合、ステップST75は実行される。ステップST75は動作例2のステップST65(図19参照)と同じステップである。フィルタ回路422は、下記式(f36)乃至(f38)の比較演算を行う。

## 【0322】

|     |       |                 |

|-----|-------|-----------------|

| R 0 | C r 3 | · · · ( f 3 6 ) |

| G 0 | C g 3 | · · · ( f 3 7 ) |

| B 0 | C b 3 | · · · ( f 3 8 ) |

40

## 【0323】

動作例4では、式(f21)乃至(f23)および(f36)乃至(f38)が全て真である場合、ステップST72が実行され、それ以外の場合は、ステップST73が実行される。

## 【0324】

図25を参照して、動作例4の具体例を説明する。以下のようにパラメータを設定する。

```

C r g 1 = C g b 1 = C b r 1 = - 1 5

C r g 2 = C g b 2 = C b r 2 = 1 5

C r 3 = C g 3 = C b 3 = 2 0 0

```

## 【0325】

50

(期間 T 0 - T 2 )

フィルタ回路 422 は、データ D T 0 [ 8 ' d 2 5 5 , 8 ' d 2 5 5 , 8 ' d 5 0 ] を受信する。ステップ S T 7 1 は偽であるので、フィルタ回路 422 はステップ S T 7 3 を実行し、データ D T 1 3 \_ r [ 8 ' d 0 , 8 ' d 0 , 8 ' d 0 ] 、データ D T 1 3 \_ e [ 8 ' d 2 5 5 , 8 ' d 2 5 5 , 8 ' d 5 0 ] を生成する。生成されたデータ D T 1 3 \_ r 、D T 1 3 \_ e は画像処理回路 420 に送信される。

【0326】

(期間 T 2 - T 4 )

フィルタ回路 422 は、データ D T 0 [ 8 ' d 5 0 , 8 ' d 5 0 , 8 ' d 2 5 5 ] を受信する。ステップ S T 7 1 は偽であるので、フィルタ回路 422 はステップ S T 7 3 を実行し、データ D T 1 3 \_ r [ 8 ' d 0 , 8 ' d 0 , 8 ' d 0 ] 、データ D T 1 3 \_ e [ 8 ' d 5 0 , 8 ' d 5 0 , 8 ' d 2 5 5 ] を生成する。生成されたデータ D T 1 3 \_ r 、D T 1 3 \_ e は画像処理回路 420 に送信される。

10

【0327】

(期間 T 4 - T 6 )

フィルタ回路 422 は、データ D T 0 [ 8 ' d 1 0 5 , 8 ' d 1 1 0 , 8 ' d 1 0 0 ] を受信する。ステップ S T 7 1 は真であり、ステップ S T 7 5 は偽であるので、フィルタ回路 422 はステップ S T 7 3 を実行し、データ D T 1 3 \_ r [ 8 ' d 0 , 8 ' d 0 , 8 ' d 0 ] 、データ D T 1 3 \_ e [ 8 ' d 1 0 5 , 8 ' d 1 1 0 , 8 ' d 1 0 0 ] を生成する。生成されたデータ D T 1 3 \_ r 、D T 1 3 \_ e は画像処理回路 420 に送信される。

20

【0328】

(期間 T 6 - T 8 )

フィルタ回路 422 は、データ D T 0 [ 8 ' d 2 4 5 , 8 ' d 2 5 5 , 8 ' d 2 4 0 ] を受信する。ステップ S T 7 1 は真であり、ステップ S T 7 5 は真であるので、フィルタ回路 422 はステップ S T 7 2 を実行し、データ D T 1 3 \_ r [ 8 ' d 2 4 5 , 8 ' d 2 5 5 , 8 ' d 2 4 0 ] 、データ D T 1 3 \_ e [ 8 ' d 0 , 8 ' d 0 , 8 ' d 0 ] を生成する。生成されたデータ D T 1 3 \_ r 、D T 1 3 \_ e は画像処理回路 420 に送信される。

30

【0329】

<< H Y モード >>

H Y モードでは、光センサ 195 で取得したデータ（例えば、環境光の照度、色温度）、および使用者の操作等に基づく割り込み要求に応じて、サブ画素 13R、13G、13B の輝度が変更される。光センサ 195 で取得されたデータ、割り込み要求に基づいて、調光処理のパラメータが設定され、画像処理回路 420 は、設定されたパラメータを用いてデータ D T 1 3 \_ e の調光処理を行う。

30

【0330】

(1) 明るい環境（例えば、晴天の昼間の屋外）では表示モードは、画素アレイ 116E の E L 素子 E E 1 を非発光にして、画素アレイ 116R のみで表示を行う。(2) 暗い環境（例えば、夜間の屋外、照明の無い屋内など）、つまり画素アレイ 116R が表示を行えない環境では、画素アレイ 116E のみで表示を行う。(3) 環境光の照度が低い環境（例えば、照明器具で照明された室内、曇天の屋外など）、L C 素子 R E 1 の反射光のみでは良好な表示品位が得られないような環境では、E L 素子 E E 1 を発光させ、画素アレイ 116R と画素アレイ 116E とで表示を行う。

40

【0331】

以上述べたように、H Y モードでは、使用環境の明るさに応じて、サブ画素 13R、13G、13B の輝度を調節することができるので、E R 表示システム 401 の表示品位の向上と、消費電力の低減とが図れる。また、E R 表示システム 401 では、T X T モード、H Y モードとともに I D S 駆動が可能であり、I D S 駆動によって、消費電力の低減を図れる。

【0332】

本実施の形態の E R 表示システムでは、ホスト装置では、E L 用と L C 用の 2 種類の画像

50

データを生成しなくてもよい。よって、ホスト装置が表示コントローラへ画像データを送信するときの負荷が軽減されるので、ER表示システムの動作不良を低減できる。

### 【0333】

#### 〔実施の形態3〕

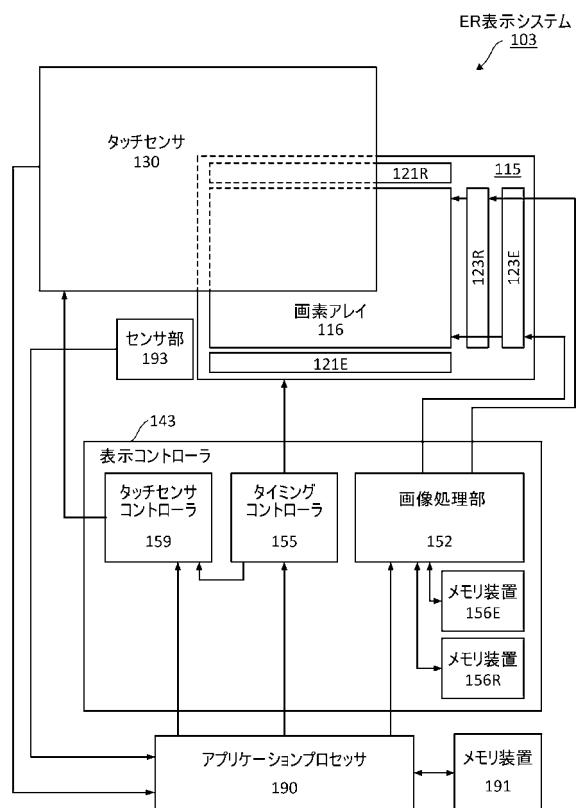

上掲の実施の形態の表示システムに、タッチセンサを組み込むことができる。本実施の形態では、タッチセンサが組み込まれた表示システムについて説明する。

### 【0334】

<<ER表示システム103>>

図26に、ER表示システム101をベースにしたタッチセンサ付きのER表示システム103の構成例を示す。ER表示システム103は、ERパネル115、タッチセンサ130、表示コントローラ143、アプリケーションプロセッサ190、メモリ装置191、センサ部193を有する。

10

### 【0335】

表示コントローラ143は、画像処理部152、タイミングコントローラ155、メモリ装置156E、156R、タッチセンサコントローラ159を有する。タッチセンサコントローラ159には、アプリケーションプロセッサから、クロック信号、同期信号などの信号が送信される。タッチセンサコントローラ159は、タッチセンサ130を駆動するためのタイミング信号を生成する。

### 【0336】

アプリケーションプロセッサ190は、タッチセンサ130で検出された位置情報等を反映した画像データを生成する。

20

### 【0337】

タッチセンサ130の構造は、アウトセル型（外付け型）、内蔵型に大別される。内蔵型タッチセンサの構造には、例えば、オンセル型とインセル型とがある。図27Aは、タッチセンサ130をインセル型タッチセンサで構成した例であり、基板311のLC層313側にセンサアレイ341が設けられている。図27Bは、タッチセンサ130がオンセル型タッチセンサである例であり、基板311の光取り出し側にセンサアレイ341が設けられている。センサアレイ341は、光301-303を遮光しない構造であることが好ましい。

### 【0338】

図27Cにタッチセンサ130の構成例を示す。図27Cに示すタッチセンサ130は相互容量型タッチセンサであり、センサアレイ341、タッチセンサドライバ342を有する。センサアレイ341は、複数のドライブ線DRL、複数のセンス線SNLを有する。1本のドライブ線DRLと1本のセンス線SNLと間に容量CTが形成される。タッチセンサドライバ342は、ドライブ線DRLを駆動している間、センス線SNLの信号を検出する。センス線SNLの信号は容量CTの容量値の変化量の情報をもつ。センス線SNLの信号を解析することで、タッチの有無、タッチ位置などの情報を得ることができる。

30

### 【0339】

図28Aに、アウトセル型タッチセンサとERパネル115との組み合わせ例を示す。図28Aの例では、ERパネル115の基板311側（光取り出し側）に光学式タッチセンサ133が設けられ、基板312側に電磁誘導方式タッチセンサ135が設けられている。

40

### 【0340】

光学式タッチセンサ133は、赤外線133irを発する赤外LEDと、赤外線133irを検知する受光素子（例えば、イメージセンサ）を備える。受光素子の信号を検知することで、指137で赤外線133irが遮られた位置を検出する（図28B）。

### 【0341】

電磁誘導方式タッチセンサ135は、画素アレイ116と重なる領域にセンサコイル135aを有する。位置の入力は電子ペン138で行う。電子ペン138とセンサコイル135a間で生じる磁束135mによって、センサコイル135aの誘導電流が変化する。こ

50

の変化量を検知することで、電子ペン 138 の位置、筆圧などを検出することができる（図 28C）。

#### 【0342】

ここでは、タッチセンサとして、相互容量型タッチセンサ、光学式タッチセンサ、および電磁誘導方式タッチセンサを挙げたが、これらに限定されない。抵抗膜方式タッチセンサ、表面弾性波方式タッチセンサなどのタッチセンサでもよい。1種類または複数種類のタッチセンサを、表示システムに組み込むことが可能である。

#### 【0343】

<< E R 表示システム 403 >>

図 29 に、タッチセンサを有する E R 表示システムの一例を示す。図 29 に示す E R 表示システム 403 は E R 表示システム 400 の変形例であり、表示コントローラ 410 に代えて表示コントローラ 412 を備え、タッチセンサ 130 が更に設けられている。

#### 【0344】

表示コントローラ 412 は、タッチセンサコントローラ 427、IDS コントローラ 428 を有する。タッチセンサコントローラ 427 は、タッチセンサ 130 を制御するためのタイミング信号を生成する。アプリケーションプロセッサ 190 は、タッチセンサ 130 で検出された位置情報等を反映した、画像データを生成する。

#### 【0345】

IDS コントローラ 428 は信号 ids を生成する。例えば、IDS コントローラ 428 をニューラルネットワーク（NN）で構築して、IDS コントローラ 428 で IDS 駆動の開始および終了タイミングを予測してもよい。学習機能を持つ IDS コントローラ 428 を備えることで、IDS 駆動と通常動作の切り替えを効率よく行えるため、E R 表示システム 403 全体の消費電力低減の効率化が図れる。

#### 【0346】

IDS コントローラ 428 の学習データとして、タッチセンサ 130 の出力データ、メモリ装置 426R、426E の消費電流、アプリケーションプロセッサ 190 の出力データ（実行しているアプリケーションの属性など）が用いられる。IDS コントローラ 428 は、これらのデータを用いて E R パネル 110 の最適なリフレッシュレートを学習する。

#### 【0347】

[実施の形態 4]

<< 電子機器 >>

本実施の形態では、実施の形態 1 乃至 3 に係る表示システムを備える電子機器を説明する。

#### 【0348】

図 30A にタブレット型情報端末の構成例を示す。図 30A に示す情報端末 3010 は、筐体 3011、表示部 3012、光センサ 3013、カメラ 3015、操作ボタン 3016 を有する。情報端末 3010 の機能には、音声通話、カメラ 3015 を利用したビデオ通話、電子メール、手帳、インターネット接続、音楽再生などがある。

#### 【0349】

表示部 3012 はタッチセンサが組み込まれた表示システムで構成される。情報端末 3010 の画面をスタイラスペン 3017（または電子ペン）、指などでタッチ操作することで、情報端末 3010 を操作することが可能である。光センサ 3013 で検知された環境光のデータに基づいて、表示部 3012 の明るさ、色合いなどが変更可能である。以下に例示される電子機器の表示部も、表示部 3012 と同様の機能を持つ。

#### 【0350】

情報端末 3010 に電子教科書のデータを記憶させることで、デジタル教科書リーダとして用いることが可能である。

#### 【0351】

図 30B に P C（パーソナルコンピュータ）の構成例を示す。図 30B に示す P C 3030 は、筐体 3031、表示部 3032、光センサ 3034、カメラ 3035、キーボード

10

20

30

40

50

3036を有する。キーボード3036は、筐体3031から着脱可能な構成である。筐体3031にキーボード3036を装着した状態では、PC3030はノート型PCとして使用できる。筐体3031からキーボード3036を脱着した状態では、PC3030はタブレット型PCとして使用できる。

#### 【0352】

PC3030に電子教科書のデータを記憶させることで、デジタル教科書リーダとして用いることが可能である。

#### 【0353】

図30Cにスマートフォンの構成例を示す。図30Cに示すスマートフォン3050は、筐体3051、表示部3052、光センサ3054、マイク3056、スピーカ3057、操作ボタン3058を有する。筐体3051の背面には、カメラなどが設けられている。スマートフォン3050は情報端末3010等と同様の機能をもつ。

10

#### 【0354】

図30Dにウエアラブル情報端末の構成例を示す。図30Dに示す情報端末3070は筐体3071、表示部3072、リストバンド3073、光センサ3074、操作ボタン3075、竜頭3076を有する。情報端末3070は情報端末3010等と同様の機能をもち、スマートウォッチとして用いることができる。

20

#### 【0355】

図30Dは、腕時計型のウエアラブル情報端末の構成例である。ウエアラブル情報端末には、眼鏡型、ゴーグル型、ブレスレット型、アームバンド型、ペンダント型など様々な態様がある。

20

#### 【0356】

図31にデジタルサイネージの構成例を示す。図31に示すデジタルサイネージ3100は、筐体3101、表示部3102、スピーカ3103、光センサ3104を有する。表示部3102に実施の形態1のER表示システムが設けられている。デジタルサイネージ3100によって、例えば、駅、空港、施設などの案内図表示システム、病院、銀行などの順番案内表示システムを提供できる。

30

#### 【0357】

上掲のER表示システムは、TXTモードをサポートしているため、電子教科書を収めた情報端末（デジタル教科書リーダ）に好適である。TXTモードでは、教科書のテキストは、環境光を利用した反射型表示パネルに表示されるため、ユーザーは、紙媒体の教科書を読むのと同様な感覚で、デジタル教科書リーダで教科書を読むことができ、長時間画面を見ても疲れにくい。

30

#### 【0358】

また、ユーザーは、カラーで各種の注釈（ハイライト表示、下線、取り消し線、フリーハンドの線図など）を白黒のテキストに記入することができるため、本デジタル教科書リーダによって紙媒体の教科書と同様の学習環境を得ることができる。注釈の表示は、反射型表示素子による黒表示と発光型表示素子によるカラー表示とのハイブリッド表示によって行われる。したがって注釈は色再現性の高い発光型素子だけで表示することができるため、白黒表示のテキストに対して、注釈を目立たせることができる。

40

#### 【0359】

##### 〔実施の形態5〕

本実施の形態では、メモリ装置について説明する。例えば、本実施の形態のメモリ装置は、ER表示システムのメモリ装置に適用される。

#### 【0360】

本明細書等では、データ保持部（例えば、メモリセル）にOSトランジスタが設けられているメモリ装置のことを、「OSメモリ」と呼ぶこととする。本実施の形態では、OSメモリの一例として、「DOSRAM（登録商標）」、および「NOSRAM（登録商標）」について、説明する。

#### 【0361】

50

「DOSRAM(ドスラム)」とは、「Dynamic Oxide Semiconductor RAM」の頭字語であり、1T(トランジスタ)1C(容量)型のメモリセルを有するRAMを指す。「NOSRAM(ノスラム)」とは「Nonvolatile Oxide Semiconductor RAM」の頭字語であり、ゲインセル型(2T型、3T型)のメモリセルを有するRAMを指す。

#### 【0362】

<< DOSRAM1400 >>

以下、図32A - 図32Cを参照して、DOSRAMについて説明する。

#### 【0363】

図32Aに示すDOSRAM1400は、コントローラ1405、行回路1410、列回路1415、MC-SAアレイ1420を有する。行回路1410はデコーダ1411、ワード線ドライバ1412、列セレクタ1413、センスアンプドライバ1414を有する。列回路1415はグローバルセンスアンプアレイ1416、入出力回路1417を有する。グローバルセンスアンプアレイ1416は複数のグローバルセンスアンプ1447を有する。MC-SAアレイ1420はメモリセルアレイ1422、センスアンプアレイ1423、グローバルビット線G BLL、G BLRを有する。

#### 【0364】

(MC-SAアレイ1420)

MC-SAアレイ1420は、メモリセルアレイ1422をセンスアンプアレイ1423上に積層した積層構造をもつ。グローバルビット線G BLL、G BLRはメモリセルアレイ1422上に積層されている。DOSRAM1400では、ビット線の構造に、ローカルビット線とグローバルビット線とで階層化された階層ビット線構造が採用されている。

#### 【0365】

メモリセルアレイ1422は、N個(Nは2以上の整数)のローカルメモリセルアレイ1425<0>-1425<N-1>を有する。図32Bに示すように、ローカルメモリセルアレイ1425は、複数のメモリセル1445、複数のワード線WL、複数のビット線B LL、B LRを有する。図32Bの例では、ローカルメモリセルアレイ1425の構造はオープンビット線型であるが、フォールデッドビット線型であってもよい。

#### 【0366】

図32Cに示すメモリセル1445は、OSトランジスタM045、容量素子C45を有する。OSトランジスタM045は容量素子C45の充放電を制御する機能をもつ。OSトランジスタM045のゲートはワード線WLに電気的に接続され、バックゲートは配線B GLに電気的に接続され、第1端子はビット線B LLまたはB LRに電気的に接続され、第2端子は容量素子C45の第1端子に電気的に接続されている。容量素子C45の第2端子は配線PCLに電気的に接続されている。配線PCL、B GLは電圧を供給するための電源線である。

#### 【0367】

配線B GLの電圧によって、OSトランジスタM045の閾値電圧を変更することができる。例えば、配線B GLの電圧は固定電圧(例えば、負の定電圧)であってもよいし、DOSRAM1400の動作に応じて、配線B GLの電圧を変化させてもよい。

#### 【0368】

OSトランジスタM045のバックゲートをOSトランジスタM045のゲート、ソース、またはドレインに電気的に接続してもよい。あるいは、OSトランジスタM045にバックゲートを設けなくてもよい。

#### 【0369】