(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5364912号

(P5364912)

(45) 発行日 平成25年12月11日(2013.12.11)

(24) 登録日 平成25年9月20日(2013.9.20)

(51) Int.Cl.

F 1

G09G 3/36 (2006.01)

G09G 3/36

G02F 1/133 (2006.01)

G02F 1/133 550

G09G 3/20 (2006.01)

G09G 3/20 624A

G09G 3/20 624D

G09G 3/20 624E

請求項の数 16 (全 25 頁) 最終頁に続く

(21) 出願番号

特願2007-16238 (P2007-16238)

(22) 出願日

平成19年1月26日 (2007.1.26)

(65) 公開番号

特開2007-199723 (P2007-199723A)

(43) 公開日

平成19年8月9日 (2007.8.9)

審査請求日

平成22年1月22日 (2010.1.22)

(31) 優先権主張番号

10-2006-0008148

(32) 優先日

平成18年1月26日 (2006.1.26)

(33) 優先権主張国

韓国 (KR)

(73) 特許権者 512187343

三星ディスプレイ株式會社

Samsung Display Co., Ltd.

大韓民国京畿道龍仁市器興区三星二路95

95, Samsung 2 Ro, Gih

eung-Gu, Yongin-City

, Gyeonggi-Do, Korea

(74) 代理人 110000051

特許業務法人共生国際特許事務所

全珍

大韓民国 京畿道 水原市 長安区 泉川

洞 三星レミアンアパート 107棟 2

04号

最終頁に続く

(54) 【発明の名称】表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート信号を伝達する複数のゲート線と、

データ電圧を伝達する複数のデータ線と、

維持信号を伝達する複数の維持電極線と、

三端子素子であって、その制御端子は前記ゲート線に接続され、入力端子はデータ線に接続されるスイッチング素子と、該スイッチング素子の出力端子と一定の大きさを有する直流電圧である共通電圧との間に接続される液晶キャパシタと、前記スイッチング素子の出力端子と前記維持電極線との間に接続されるストレージキャパシタとを各々含み、行列状に配列される複数の画素と、

10

前記ゲート信号に基づいて前記維持信号を生成する複数の信号生成回路とを有し、

前記各画素に印加される維持信号は、前記液晶キャパシタ及び前記ストレージキャパシタにデータ電圧の充電が終了した直後に電圧レベルが変化し、

前記各信号生成回路は、印加される第1制御信号の電圧レベルの変化と、(k+1)番目(kは自然数)ゲート線に印加される(k+1)番目ゲート信号の電圧上昇とに合わせて、動作状態が変化して、第1電圧レベルまたは第2電圧レベルを有する維持信号をk番目維持電極線に印加する維持信号印加部と、

印加される第2及び第3制御信号の電圧レベルの変化と、前記(k+1)番目ゲート信号の電圧上昇とに合わせて、動作状態が変化する制御部と、

前記制御部の動作によって前記維持信号印加部から出力される前記維持信号をその電圧

20

レベルが変化するまでの所定時間維持する信号維持部とを含み、

前記第1乃至第3制御信号は、同一の周期を有することを特徴とする表示装置。

**【請求項2】**

隣接した前記維持電極線に印加される維持信号の電圧レベルは、互いに異なることを特徴とする請求項1に記載の表示装置。

**【請求項3】**

同一の前記維持電極線に印加される維持信号の電圧レベルは、フレームごとに反転することを特徴とする請求項1に記載の表示装置。

**【請求項4】**

前記共通電圧は、一定の値を有することを特徴とする請求項1に記載の表示装置。

10

**【請求項5】**

前記第1制御信号は、前記第3制御信号と同一の位相を有することを特徴とする請求項1に記載の表示装置。

**【請求項6】**

前記第2制御信号は、前記第3制御信号と反対の位相を有することを特徴とする請求項5に記載の表示装置。

**【請求項7】**

前記第1乃至第3制御信号の周期は2H(2水平周期)であることを特徴とする請求項1に記載の表示装置。

**【請求項8】**

前記第1乃至第3制御信号のデューティ比は同一であることを特徴とする請求項1に記載の表示装置。

20

**【請求項9】**

前記第1乃至第3制御信号のデューティ比は50%であることを特徴とする請求項8に記載の表示装置。

**【請求項10】**

前記複数の信号生成回路のうちの一つにゲート信号を伝達する付加ゲート線をさらに含むことを特徴とする請求項1に記載の表示装置。

**【請求項11】**

前記付加ゲート線は、最後の信号生成回路に接続されることを特徴とする請求項10に記載の表示装置。

30

**【請求項12】**

前記ゲート信号はゲートオン電圧とゲートオフ電圧とを備え、隣接した二つのゲート信号のゲートオン電圧は、所定期間重畠することを特徴とする請求項1に記載の表示装置。

**【請求項13】**

隣接した二つのゲート信号のゲートオン電圧は、1Hの間に重畠することを特徴とする請求項12に記載の表示装置。

**【請求項14】**

前記維持信号印加部は、(k+1)番目ゲート線に印加される(k+1)番目ゲート信号に制御端子が接続され、前記第1制御信号に入力端子が接続され、前記k番目維持電極線に出力端子が接続される第1トランジスタを含むことを特徴とする請求項1に記載の表示装置。

40

**【請求項15】**

前記制御部は、前記(k+1)番目ゲート信号に制御端子が接続され、前記第2制御信号に入力端子が接続される第2トランジスタと、

前記(k+1)番目ゲート信号に制御端子が接続され、前記第3制御信号に入力端子が接続される第3トランジスタとを含むことを特徴とする請求項14に記載の表示装置。

**【請求項16】**

前記信号維持部は、前記第3トランジスタの出力端子に制御端子が接続され、第1駆動電圧に入力端子が接続され、前記k番目維持電極線に出力端子が接続される第4トランジ

50

スタと、

前記第2トランジスタの出力端子に制御端子が接続され、前記k番目維持電極線に入力端子が接続され、第2駆動電圧に出力端子が接続される第5トランジスタと、

前記第4トランジスタの入力端子と制御端子との間に接続される第1キャパシタと、

前記第5トランジスタの制御端子と出力端子との間に接続される第2キャパシタとを含むことを特徴とする請求項15に記載の表示装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は表示装置に関し、特に、表示装置の消費電力を減少させることのできる表示装置に関する。 10

【背景技術】

【0002】

一般的な液晶表示装置 (liquid crystal display、LCD) は、画素電極及び共通電極が具備された二つの表示板と、その間に入っている誘電率異方性 (dielectric anisotropy) を有する液晶層とを有する。画素電極は、行列状に配列されており、薄膜トランジスタ (TFT) などスイッチング素子に接続されて一つの行ずつ順次にデータ電圧の印加を受ける。共通電極は、表示板の全面にわたって形成されており、共通電圧の印加を受ける。画素電極と共通電極及びその間の液晶層は、回路的に見れば液晶キャパシタをなし、液晶キャパシタはこれに接続されたスイッチング素子と共に画素を構成する基本単位となる。 20

【0003】

このような液晶表示装置においては、二つの電極に電圧を印加して液晶層に電界を生成し、この電界の強さを調節して液晶層を通過する光の透過率を調節することによって所望の画像を得る。この時、液晶層に一方向の電界が長期印加されることによって発生する劣化現象を防止するために、フレーム毎に、行毎に、または画素毎に共通電圧に対するデータ電圧の極性を反転させる。

【0004】

しかし、液晶分子の応答速度が遅いため、液晶キャパシタに充電される電圧（以下、“画素電圧”と言う）が目標電圧、つまり、所望の輝度を得ることができる電圧まで到達するには所定の時間がかかり、この時間は液晶キャパシタに以前に充電されていた電圧との差によって変わる。したがって、例えば、目標電圧と以前電圧との差が大きい場合、最初から目標電圧だけを印加すれば、スイッチング素子が導通している時間の間に目標電圧に到達できないことがある。 30

【0005】

そのため、これを補償するためのDCC (Dynamic Capacitance Compensation) 方式が提案された。つまり、DCC方式は、液晶キャパシタ両端にかかった電圧が大きいほど充電速度が速くなるという点を利用したものであって、該当画素に印加するデータ電圧（実際には、データ電圧と共通電圧との差であるが、便宜上、共通電圧を0と仮定する）を目標電圧より高くすることで、画素電圧が目標電圧まで到達することにかかる時間を短縮する。 40

【0006】

しかし、このようなDCC方式を実施する場合、フレームメモリ (frame memory) とDCC演算のための駆動回路などが必要であるため、回路設計の難しさと製造費用が増加する。

また、液晶表示装置のうち、携帯電話などに使用される中小型表示装置の場合、消費電力などを節約するために、行毎に共通電圧に対するデータ電圧の極性を反転させる行反転 (row inversion) を実施しているが、中小型表示装置においても解像度が次第に増加して消費電力が問題となる。特に、DCC演算を実施する場合、追加された演算や回路などのための電力消費はさらに大きくなるという問題があった。 50

**【0007】**

さらに、行反転の場合、画素毎に共通電圧に対するデータ電圧の極性を反転させる点反転(*dot inversion*)の場合より、画像表示のためのデータ電圧の範囲が小さい。したがって、VA(Vertical Alignment)モード液晶表示装置などのように、液晶駆動のためのしきい電圧(*threshold voltage*)が高い場合、実際の画像表示のための階調を表現することに利用されるデータ電圧の範囲がしきい電圧ほど小さくなり、これによって輝度表示に難しさが発生するという問題があった。

**【発明の開示】****【発明が解決しようとする課題】**

10

**【0008】**

そこで、本発明は上記従来の表示装置における問題点に鑑みてなされたものであって、本発明の目的は、表示装置の消費電力を減少させることのできる表示装置を提供することにある。

**【0009】**

また、本発明の他の目的は、表示装置の液晶の応答速度を向上させることのできる表示装置を提供することにある。さらに、本発明の他の技術的課題は、表示装置の消費電力の増加を招くことなく、画質を向上させることのできる表示装置を提供することにある。

**【課題を解決するための手段】****【0010】**

20

上記目的を達成するためになされた本発明による表示装置は、ゲート信号を伝達する複数のゲート線と、データ電圧を伝達する複数のデータ線と、維持信号を伝達する複数の維持電極線と、三端子素子であって、その制御端子は前記ゲート線に接続され、入力端子はデータ線に接続されるスイッチング素子と、該スイッチング素子の出力端子と一定の大きさを有する直流電圧である共通電圧との間に接続される液晶キャパシタと、前記スイッチング素子の出力端子と前記維持電極線との間に接続されるストレージキャパシタとを各々含み、行列状に配列される複数の画素と、前記ゲート信号に基づいて前記維持信号を生成する複数の信号生成回路とを有し、前記各画素に印加される維持信号は、前記液晶キャパシタ及び前記ストレージキャパシタにデータ電圧の充電が終了した直後に電圧レベルが変化し、前記各信号生成回路は、印加される第1制御信号の電圧レベルの変化と、(k+1)番目(kは自然数)ゲート線に印加される(k+1)番目ゲート信号の電圧上昇とに合わせて、動作状態が変化して、第1電圧レベルまたは第2電圧レベルを有する維持信号をk番目維持電極線に印加する維持信号印加部と、印加される第2及び第3制御信号の電圧レベルの変化と、前記(k+1)番目ゲート信号の電圧上昇とに合わせて、動作状態が変化する制御部と、前記制御部の動作によって前記維持信号印加部から出力される前記維持信号をその電圧レベルが変化するまでの所定時間維持する信号維持部とを含み、前記第1乃至第3制御信号は、同一の周期を有することを特徴とする。

30

**【0011】**

隣接した前記維持電極線に印加される維持信号の電圧レベルは、互いに異なることが好ましい。

40

同一の前記維持電極線に印加される維持信号の電圧レベルは、フレームごとに反転することが好ましい。

前記共通電圧は一定の値を有することが好ましい。

前記第1制御信号は、前記第3制御信号と同一の位相を有することが好ましい。

前記第2制御信号は、前記第3制御信号と反対の位相を有することが好ましい。

前記第1乃至第3制御信号の周期は2H(2水平周期)であることが好ましい。

前記第1乃至第3制御信号のデューティ比は同一であることが好ましい。

前記第1乃至第3制御信号のデューティ比は50%であることが好ましい。

前記複数の信号生成回路のうちの一つにゲート信号を伝達する付加ゲート線をさらに含むことが好ましい。

50

前記付加ゲート線は、最後の信号生成回路に接続されることが好ましい。

前記ゲート信号はゲートオン電圧とゲートオフ電圧を備え、隣接した二つのゲート信号のゲートオン電圧は所定期間の間に重畠することが好ましい。

隣接した二つのゲート信号のゲートオン電圧は、1Hの間に重畠することが好ましい。

前記維持信号印加部は、(k+1)番目ゲート線に印加される(k+1)番目ゲート信号に制御端子が接続され、前記第1制御信号に入力端子が接続され、前記k番目維持電極線に出力端子が接続される第1トランジスタを含むことが好ましい。

前記制御部は、前記(k+1)番目ゲート信号に制御端子が接続され、前記第2制御信号に入力端子が接続される第2トランジスタと、前記(k+1)番目ゲート信号に制御端子が接続され、前記第3制御信号に入力端子が接続される第3トランジスタとを含むことが好ましい。10

前記信号維持部は、前記第3トランジスタの出力端子に制御端子が接続され、第1駆動電圧に入力端子が接続され、前記k番目維持電極線に出力端子が接続される第4トランジスタと、前記第2トランジスタの出力端子に制御端子が接続され、前記k番目維持電極線に入力端子が接続され、第2駆動電圧に出力端子が接続される第5トランジスタと、前記第4トランジスタの入力端子と制御端子との間に接続される第1キャパシタと、前記第5トランジスタの制御端子と出力端子との間に接続される第2キャパシタとを含むことが好ましい。

20

### 【発明の効果】

#### 【0014】

本発明に係る表示装置によれば、共通電圧を所定電圧に固定させた後、所定の周期でレベルが変化する維持電圧を維持電極線に印加する。この時、隣接した維持電極線に印加される維持電圧を互いに異なるように印加する。これによって、画素電極電圧の範囲が増加して画素電圧の範囲も広くなるので、階調を表現するための電圧の範囲が広くなり、これによって画質が向上するという効果がある。

#### 【0015】

同一の範囲のデータ電圧が印加される場合、一定の電圧の維持電圧が印加される時より広い範囲の画素電圧が生成されるので、消費電力が減少し、これに加えて共通電圧が一定の値に固定されるので、消費電力はさらに減少するという効果がある。30

また、液晶の充電動作が完了する前の画素電極電圧の範囲が、液晶の充電動作が完了した後の画素電極電圧の範囲より広いので、目標電圧より高いかまたは低い電圧が液晶駆動の初期に印加されることによって、液晶の応答速度が向上するという効果がある。

#### 【発明を実施するための最良の形態】

#### 【0016】

次に、本発明に係る表示装置を実施するための最良の形態の具体例を図面を参照しながら説明する。

#### 【0017】

図面において、いろいろな層及び領域を明確に表現するために厚さを拡大して示した。40

明細書全体にわたって類似の部分については同一の図面符号を付けた。層、膜、領域、板などの部分が他の部分の“上”にあるとする時、これは他の部分の“すぐ上”にある場合だけでなく、その中間に他の部分がある場合も含む。逆に、ある部分が他の部分の“すぐ上”にあるとする時には、中間に他の部分がないことを意味する。

#### 【0018】

以下、本発明の表示装置の一実施形態である液晶表示装置について、図面を参照して詳細に説明する。

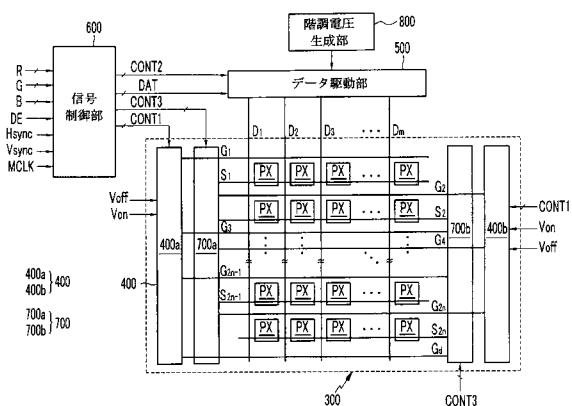

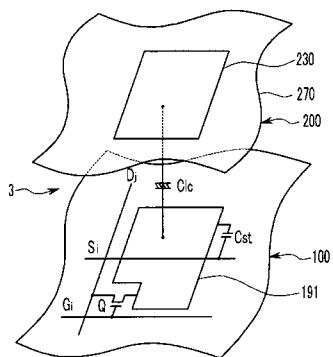

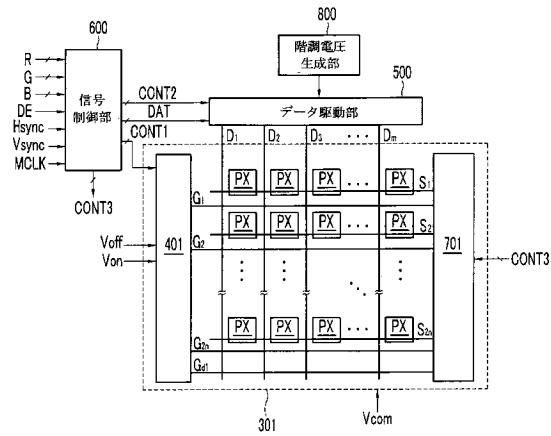

まず、図1及び図2を参照して、本発明の一実施形態による液晶表示装置について詳細に説明する。図1は本発明の一実施形態による液晶表示装置のブロック図であり、図2は本発明の一実施形態による液晶表示装置の一つの画素に対する等価回路図である。50

## 【0019】

図1を参照すれば、本発明の一実施形態による液晶表示装置は、液晶表示板組立体(liquid crystal panel assembly)300、ゲート駆動部(gate driver)400、データ駆動部(data driver)500、データ駆動部500に接続された階調電圧生成部(gray voltage generator)800、維持信号生成部(storage signal generator)700、及び信号制御部(signal controller)600を含む。液晶表示板組立体300は、等価回路から見れば、複数の信号線( $G_1 \sim G_{2n}$ 、 $G_d$ 、 $D_1 \sim D_m$ 、 $S_1 \sim S_{2n}$ )と、複数の画素PXとを含む。反面、図2に示す構造から見れば、液晶表示板組立体300は、互いに対向する下部及び上部表示板100、200と、その間に入っている液晶層3とを含む。

10

## 【0020】

信号線( $G_1 \sim G_{2n}$ 、 $G_d$ 、 $D_1 \sim D_m$ 、 $S_1 \sim S_{2n}$ )は、複数のゲート線 $G_1 \sim G_{2n}$ 、 $G_d$ 、複数のデータ線 $D_1 \sim D_m$ 、及び複数の維持電極線 $S_1 \sim S_{2n}$ を含む。ゲート線 $G_1 \sim G_{2n}$ 、 $G_d$ はゲート信号(“走査信号”とも言う)を伝達し、一般ゲート線 $G_1 \sim G_{2n}$ と付加ゲート線 $G_d$ とを含む。維持電極線 $S_1 \sim S_{2n}$ は、一般ゲート線 $G_1 \sim G_{2n}$ と交互に配置されており、維持信号(storage signal)を伝達する。データ線 $D_1 \sim D_m$ はデータ電圧を伝達する。

ゲート線 $G_1 \sim G_{2n}$ 、 $G_d$ と維持電極線 $S_1 \sim S_{2n}$ は、ほぼ行方向にのびて互いに平行であり、データ線 $D_1 \sim D_m$ は、ほぼ列方向にのびて互いにほとんど平行である。

20

## 【0021】

図1に示すように、画素PXは、一般ゲート線 $G_1 \sim G_{2n}$ 、データ線 $D_1 \sim D_m$ 、及び維持電極線 $S_1 \sim S_{2n}$ と接続されており、行列状に配列されている。各画素PX、例えば、i番目( $i = 1, 2, \dots, 2n$ )行、j番目( $j = 1, 2, \dots, m$ )列の画素PXは、図2に示すように、i番目一般ゲート線 $G_i$ とj番目データ線 $D_j$ に接続されたスイッチング素子Q、スイッチング素子Qに接続された液晶キャパシタ(liquid crystal capacitor)C1c、及びスイッチング素子Qとi番目の維持電極線 $S_i$ に接続されたストレージキャパシタ(storage capacitor)Cstを含む。

## 【0022】

スイッチング素子Qは、下部表示板100に備えられている薄膜トランジスタなどの三端子素子であって、その制御端子は一般ゲート線 $G_i$ と接続されており、入力端子はデータ線 $D_j$ と接続されており、出力端子は液晶キャパシタC1c及びストレージキャパシタCstと接続されている。

30

## 【0023】

液晶キャパシタC1cは、下部表示板100の画素電極191と上部表示板200の共通電極270とを二つの端子とし、二つの電極(191、270)の間の液晶層3は誘電体として機能する。画素電極191はスイッチング素子Qと接続され、共通電極270は上部表示板200の全面に形成されており、共通電圧Vcomの印加を受ける。共通電圧は一定の大きさを有する直流(DC)電圧である。図2とは異なって、共通電極270が下部表示板100に備えられる場合もあり、この場合には二つの電極(191、270)のうちの少なくとも一つが線状または棒状に作られることができる。

40

液晶キャパシタC1cの補助的な役割を果たすストレージキャパシタCstは、画素電極191と維持電極線 $S_i$ とが絶縁体を介在して重畠してなる。

## 【0024】

一方、色表示を実現するためには、各画素PXが基本色(primary color)のうちの一つを固有に表示したり(空間分割)、各画素PXが時間によって交互に基本色を表示するように(時間分割)して、これら基本色の空間的、時間的合計によって所望の色相が認識されるようにする。基本色の例としては、赤色、緑色、青色など三原色がある。図2は空間分割の一例として、各画素PXが画素電極191に対応する上部表示板2

50

00の領域に基本色のうちの一つを示すカラーフィルタ230を備えることを示している。図2とは異なって、カラーフィルタ230は下部表示板100の画素電極191の上または下に備えることもできる。液晶表示板組立体300には、少なくとも一つの偏光子(図示せず)が備えられている。

#### 【0025】

再び図1を参照すれば、階調電圧生成部800は、画素PXの透過率と関する全体階調電圧または限定された数の階調電圧(以下、“基準階調電圧”と言う)を生成する。(基準)階調電圧は、共通電圧Vcomに対して正の値を有するものと、負の値を有するものとを含むことができる。

ゲート駆動部400は、液晶表示板組立体300の両側面、例えば、左側端と右側端に配置されている第1及び第2ゲート駆動回路400a、400bを含む。

#### 【0026】

第1ゲート駆動回路400aは、奇数番目的一般ゲート線G<sub>1</sub>、G<sub>3</sub>、…、G<sub>2n-1</sub>及び付加ゲート線G<sub>d</sub>と一端で接続され、第2ゲート駆動回路400bは、偶数番目的一般ゲート線G<sub>2</sub>、G<sub>4</sub>、…、G<sub>2n</sub>と一端で接続される。しかし、これに限定されるわけではなく、反対に、奇数番目のゲート線G<sub>1</sub>、G<sub>3</sub>、…、G<sub>2n-1</sub>及び付加ゲート線G<sub>d</sub>が第2ゲート駆動回路400bに接続され、偶数番目のゲート線G<sub>2</sub>、G<sub>4</sub>、…、G<sub>2n</sub>は第1ゲート駆動回路400aに接続されることができる。

第1及び第2ゲート駆動回路400a、400bは、ゲートオン電圧Vonとゲートオフ電圧Voffとの組み合わせからなるゲート信号を、接続されたゲート線G<sub>1</sub>～G<sub>2n</sub>、G<sub>d</sub>に印加する。

#### 【0027】

ゲート駆動部400は、信号線G<sub>1</sub>～G<sub>2n</sub>、G<sub>d</sub>、D<sub>1</sub>～D<sub>m</sub>、S<sub>1</sub>～S<sub>2n</sub>及び薄膜トランジスタスイッチング素子Qなどと共に液晶表示板組立体300に集積される。しかし、ゲート駆動部400は、少なくとも一つの集積回路チップの形態で液晶表示板組立体300上に直接装着したり、可撓性印刷回路フィルム(flexible printed circuit film)(図示せず)上に装着されてTCP(tape carrier package)の形態で液晶表示板組立体300に付着させたり、別途の印刷回路基板(printed circuit board)(図示せず)上に装着することもできる。

#### 【0028】

維持信号生成部700は、液晶表示板組立体300の両側面、例えば、第1及び第2ゲート駆動回路400a、400bと各々隣接するように配置される第1及び第2維持信号生成回路700a、700bを備える。

第1維持信号生成回路700aは奇数番目の維持電極線S<sub>1</sub>、S<sub>3</sub>、…、S<sub>2n-1</sub>及び偶数番目的一般ゲート線G<sub>2</sub>、G<sub>4</sub>、…、G<sub>2n</sub>に接続されており、奇数番目の維持電極線S<sub>1</sub>、S<sub>3</sub>、…、S<sub>2n-1</sub>に高レベル電圧と低レベル電圧からなる維持信号を印加する。

#### 【0029】

第2維持電極線駆動部700bは、偶数番目の維持電極線S<sub>2</sub>、S<sub>4</sub>、…、S<sub>2n</sub>及び第1一般ゲート線G<sub>1</sub>を除いた奇数番目的一般ゲート線G<sub>3</sub>、G<sub>5</sub>、…、G<sub>2n-1</sub>と付加ゲート線G<sub>d</sub>に接続されており、偶数番目の維持電極線S<sub>2</sub>、S<sub>4</sub>、…、S<sub>2n</sub>に維持信号を印加する。

これとは異なって、維持信号生成部700は、ゲート駆動部400に接続された別途の付加ゲート線G<sub>d</sub>を通じて必要な信号の供給を受けず、別途の信号発生部や信号制御部600などのような別途の装置から必要な信号の供給を受けることができる。この場合、ゲート駆動部400に接続された付加ゲート線G<sub>d</sub>は液晶表示板組立体300に形成される必要がない。

#### 【0030】

維持信号生成部700は、信号線G<sub>1</sub>～G<sub>2n</sub>、G<sub>d</sub>、D<sub>1</sub>～D<sub>m</sub>、S<sub>1</sub>～S<sub>2n</sub>及び

10

20

30

40

50

薄膜トランジスタスイッチング素子Qなどと共に液晶表示板組立体300に集積される。しかし、維持信号生成部700は、少なくとも一つの集積回路チップの形態で液晶表示板組立体300上に直接装着したり、可撓性印刷回路フィルム(flexible printed circuit film)(図示せず)上に装着されてTCP(tape carrier package)の形態で液晶表示板組立体300に付着させたり、別途の印刷回路基板(printed circuit board)(図示せず)上に装着することもできる。

#### 【0031】

データ駆動部500は、液晶表示板組立体300のデータ線D<sub>1</sub>～D<sub>m</sub>と接続されており、階調電圧生成部800からの階調電圧を選択し、これをデータ電圧としてデータ線D<sub>1</sub>～D<sub>m</sub>に印加する。しかし、階調電圧生成部800が階調電圧を全て提供することではなく、限定された数の基準階調電圧のみを提供する場合に、データ駆動部500は基準階調電圧を分圧して所望のデータ電圧を生成する。10

信号制御部600は、ゲート駆動部400、データ駆動部500及び維持信号生成部700などを制御する。

#### 【0032】

このような駆動装置(500、600、800)各々は、少なくとも一つの集積回路チップの形態で液晶表示板組立体300上に直接装着したり、可撓性印刷回路フィルム(図示せず)上に装着されてTCPの形態で液晶表示板組立体300に付着させたり、別途の印刷回路基板(図示せず)上に装着することもできる。これとは異なって、これら駆動装置(500、600、800)が信号線G<sub>1</sub>～G<sub>2n</sub>、D<sub>1</sub>～D<sub>m</sub>、S<sub>1</sub>～S<sub>2n</sub>及び薄膜トランジスタスイッチング素子Qなどと共に液晶表示板組立体300に直接集積することもできる。また、駆動装置(500、600、800)は単一チップで集積でき、この場合、これらのうちの少なくとも一つまたはこれらをなす少なくとも一つの回路素子が单一チップの外側にあり得る。20

#### 【0033】

次に、このような液晶表示装置の動作について詳細に説明する。

信号制御部600は、外部のグラフィック制御器(図示せず)から入力画像信号R、G、B及びその表示を制御する入力制御信号を受信する。入力画像信号R、G、Bは各画素P Xの輝度(luminance)情報を含んでおり、輝度は決められた数、例えば、1024( $=2^{10}$ )、256( $=2^8$ )または64( $=2^6$ )個の階調(gray)を有している。入力制御信号の例としては、垂直同期信号V sync、水平同期信号H sync、メインクロック信号MCLK、及びデータインターブル信号DEなどがある。30

#### 【0034】

信号制御部600は、入力画像信号R、G、Bと入力制御信号に基づいて入力画像信号R、G、Bを液晶表示板組立体300の動作条件に合うように適切に処理し、ゲート制御信号CONT1、データ制御信号CONT2及び維持制御信号CONT3などを生成した後、ゲート制御信号CONT1をゲート駆動部400に送出し、データ制御信号CONT2と処理したデジタル画像信号DATをデータ駆動部500に送出し、維持制御信号CONT3を維持信号生成部700に送出する。40

#### 【0035】

ゲート制御信号CONT1は、走査開始を指示する走査開始信号STV1、STV2と、ゲートオン電圧V<sub>on</sub>の出力周期を制御する少なくとも一つのクロック信号とを含む。ゲート制御信号CONT1は、また、ゲートオン電圧V<sub>on</sub>の持続時間を限定する出力インターブル信号OEをさらに含むことができる。

#### 【0036】

データ制御信号CONT2は、一つの行の画素P Xに対するデジタル画像信号DATの伝送開始を知らせる水平同期開始信号STHと、データ線D<sub>1</sub>～D<sub>m</sub>にアナログデータ電圧の印加を指示するロード信号LOAD、及びデータクロック信号HCLKを含む。データ制御信号CONT2は、また、共通電圧V<sub>com</sub>に対するデータ電圧極性(以下、“共50

通電圧に対するデータ電圧の極性”を略して“データ電圧の極性”と言う)を反転させる反転信号RVSをさらに含むことができる。

#### 【0037】

信号制御部600からのデータ制御信号CONT2によって、データ駆動部500は一つの行、例えば、i番目行の画素PXに対するデジタル画像信号DATを受信し、各デジタル画像信号DATに対応する階調電圧を選択することによってデジタル画像信号DATをアナログデータ電圧に変換した後に、これを該当データ線D<sub>1</sub>～D<sub>m</sub>に印加する。

#### 【0038】

ゲート駆動部400は、信号制御部600からのゲート制御信号CONT1によってゲート線G<sub>1</sub>～G<sub>2n</sub>のうちの一つ、例えば、i番目ゲート線G<sub>i</sub>に印加されるゲート信号をゲートオン電圧V<sub>on</sub>に変えて、このゲート線G<sub>i</sub>に接続されたスイッチング素子Qを導通させる(但し、付加ゲート線G<sub>d</sub>にはスイッチング素子Qが接続されていないため除外)。そうすると、データ線D<sub>1</sub>～D<sub>m</sub>に印加されたデータ電圧が導通したスイッチング素子Qを通じてi番目行の画素PXに印加され、これにより画素PX内の液晶キャパシタC<sub>1c</sub>とストレージキャパシタC<sub>st</sub>が充電される。

#### 【0039】

液晶キャパシタC<sub>1c</sub>の充電電圧、つまり、画素電圧は画素PXに印加されたデータ電圧と共に共通電圧V<sub>com</sub>との差とほとんど同一である。液晶分子は画素電圧の大きさによってその配列を異ならせ、そのため液晶層3を通過する光の偏光が変化する。このような偏光の変化は偏光子によって光の透過率変化として現れ、これによって画素PXはデジタル画像信号DATの階調が示す輝度を表示する。

#### 【0040】

一つの水平周期(“1H”とも記し、水平同期信号Hsync及びデータイネーブル信号DEの一周期と同一である)が経過し、データ駆動部500が(i+1)番目行の画素PXに対するデータ電圧をデータ線D<sub>1</sub>～D<sub>m</sub>に印加すれば、ゲート駆動部400はi番目ゲート線G<sub>i</sub>に印加されるゲート信号をゲートオフ電圧V<sub>off</sub>に変え、その後、ゲート線(G<sub>i+1</sub>)に印加されるゲート信号をゲートオン電圧V<sub>on</sub>に変える。

そうすると、i番目画素行のスイッチング素子Qが遮断され、そのため画素電極191が孤立状態(floating)となる。

#### 【0041】

維持信号生成部700は、信号制御部600からの維持制御信号CONT3と、(i+1)番目ゲート線G<sub>i+1</sub>に印加されるゲート信号の電圧上昇によって、i番目維持電極線S<sub>i</sub>に印加される維持信号の電圧レベルを変える。以下、i番目画素行のストレージキャパシタC<sub>st</sub>の一側端子である画素電極191が、他側端子である維持電極線S<sub>i</sub>の電圧変化によってその電圧を変える。

このような過程を全ての画素行に対して繰り返すことによって、液晶表示装置は1フレーム(frame)の画像を表示する。

#### 【0042】

1フレームが終了すれば、次のフレームが開始し、各画素PXに印加されるデータ電圧の極性が直前フレームでの極性と反対になるように、データ駆動部500に印加される反転信号RVSの状態が制御される(“フレーム反転”)。また、一つの行の画素PXに印加されるデータ電圧の極性は全て同一であり、隣接した二つの行の画素PXに印加されるデータ電圧の極性は反対である(“行反転”)。

#### 【0043】

このように本実施形態による液晶表示装置がフレーム反転及び行反転を行うので、いずれか一つの行の画素PXに印加されるデータ電圧は全て正極性であるかまたは負極性であり、フレーム単位で極性が変わる。この時、維持電極線S<sub>1</sub>～S<sub>2n</sub>に印加される維持信号は、画素電極191に正極性のデータ電圧が充電された場合には低レベル電圧から高レベル電圧に変化し、反対に、画素電極191に負極性のデータ電圧が充電された場合には高レベル電圧から低レベル電圧に変化する。したがって、画素電極191の電圧は、正極

10

20

30

40

50

性データ電圧で充電された場合にはさらに上がり、負極性データ電圧で充電された場合にはさらに下がる。したがって、画素電極 191 の電圧範囲は、データ電圧の基礎である階調電圧の範囲より広く、これにより低い基本電圧にても広い範囲の輝度を実現することができる。

#### 【0044】

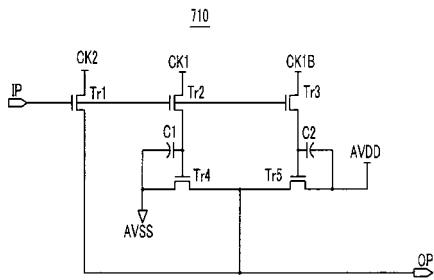

一方、第1及び第2維持信号生成回路 700a、700b は各々、維持電極線  $S_1 \sim S_{2n}$  に各々接続された複数の信号生成回路 (signal generating circuit) 710 を含むことができ、このような信号生成回路 710 の一例について、図3及び図4を参照して詳細に説明する。

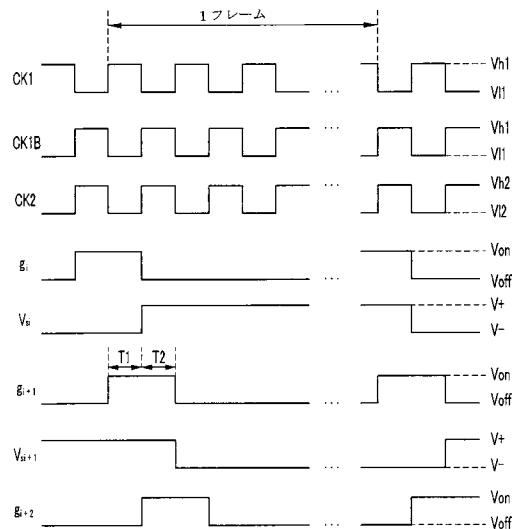

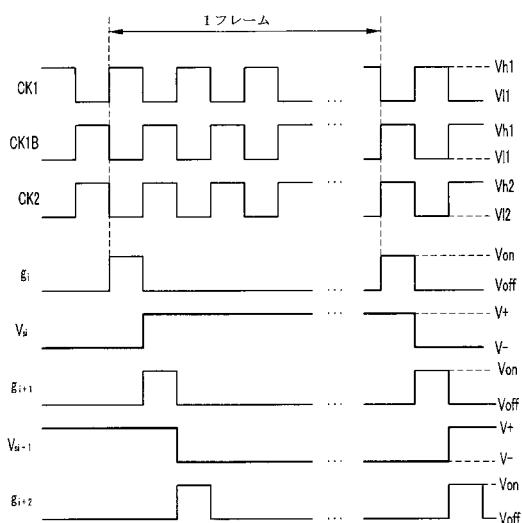

図3は本発明の一実施形態による信号生成回路の回路図であり、図4は図3に示した信号生成回路を含む液晶表示装置に用いられる信号のタイミング図である。

#### 【0045】

図3に示すように、信号生成回路 710 は、入力端IPと出力端OPを有する。 $i$  番目信号生成回路の場合、入力端IPは( $i+1$ )番目ゲート線  $G_{i+1}$  と接続されて、( $i+1$ )番目ゲート信号  $g_{i+1}$  (以下、“入力信号”と言う)を受け、出力端OPは*i* 番目維持電極線  $S_i$  と接続され、*i* 番目維持信号  $V_{S_i}$  を出力する。これと同様に、( $i+1$ )番目信号生成回路の場合、入力端IPは( $i+2$ )番目ゲート線  $G_{i+2}$  と接続され、( $i+2$ )番目ゲート信号  $g_{i+2}$  を入力信号として受け、出力端OPは( $i+1$ )番目維持電極線  $S_{i+1}$  と接続され、( $i+1$ )番目維持信号  $V_{S_{i+1}}$  を出力する。

#### 【0046】

信号生成回路 710 は、信号制御部 600 から維持制御信号 CONT3 の一種である第1、第2及び第3クロック信号 CK1、CK1B、CK2 を受け、信号制御部 600 または外部から高電圧 AVDD と低電圧 AVSS を受ける。

#### 【0047】

図4に示すように、第1乃至第3クロック信号 CK1、CK1B、CK2 は 2H の周期を有し、デューティ比は約 50% であり得る。第1クロック信号 CK1 と第2クロック信号 CK1B とは約 180° の位相差を有する互いに反転した信号であり、第2クロック信号 CK1B と第3クロック信号 CK2 の位相は互いに同一である。また、第1乃至第3クロック信号 CK1、CK1B、CK2 の波形はフレーム単位で反転する。

#### 【0048】

第1及び第2クロック信号 CK1、CK1B の高レベル電圧  $V_{h1}$  は約 1.5V であり、低レベル電圧  $V_{l1}$  は約 0V であり得、第3クロック信号 CK2 の高レベル電圧  $V_{h2}$  は約 5V であり、低レベル電圧  $V_{l2}$  は約 0V であり得る。高電圧 AVDD は第3クロック信号 CK2 の高レベル電圧  $V_{h2}$  と一緒に約 5V であり、低電圧 AVSS は第3クロック信号 CK2 の低レベル電圧  $V_{l2}$  と一緒に約 0V であり得る。

#### 【0049】

信号生成回路 710 は、制御端子、入力端子及び出力端子を各々有する五個のトランジスタ Tr1、Tr2、Tr3、Tr4、Tr5 と、二つのキャパシタ C1、C2 とを含む。

トランジスタ Tr1 の制御端子は入力端IPと接続されており、入力端子は第3クロック信号 CK2 と接続されており、出力端子は出力端OPと接続されている。

#### 【0050】

トランジスタ Tr2、トランジスタ Tr3 の各々の制御端子は入力端IPと接続されており、各々の入力端子は第1クロック信号 CK1、第2クロック信号 CK1B と接続されている。

トランジスタ Tr4、トランジスタ Tr5 の各々の制御端子はトランジスタ Tr2、トランジスタ Tr3 の出力端子と接続されており、各々の入力端子は低電圧 AVSS、高電圧 AVDD に接続されており、各々の出力端子は出力端OPと接続されている。

#### 【0051】

キャパシタ C1、キャパシタ C2 は、各々、トランジスタ Tr4 の制御端子と低電圧 A

10

20

30

40

50

VSSとの間、トランジスタTr5の制御端子と高電圧AVDDとの間に接続されている。トランジスタTr1～Tr5は、非晶質シリコン(amorphous silicon)または多結晶シリコン(poly crystalline silicon)薄膜トランジスタからなることができる。

#### 【0052】

このような信号生成回路の動作について詳細に説明する。

図4に示すように、隣接した二つのゲート線に印加されるゲートオン電圧Vonの印加時間が一部重畠しており、この時、ゲートオン電圧Vonの重畠時間は約1Hであり得る。これにより、全行の画素PXは直前行の画素PXに印加されるデータ電圧によって約1H間に充電されるが、残りの約1H間には自身のデータ電圧によって充電が行われ、正常に画像の表示動作が行われる。10

#### 【0053】

まず、i番目信号生成回路について説明する。

入力信号、つまり、(i+1)番目ゲート線G<sub>i+1</sub>に印加されるゲート信号g<sub>i+1</sub>がゲートオン電圧Vonになれば、第1乃至第3トランジスタTr1～Tr3が導通する。導通したトランジスタTr1は第3クロック信号CK2を出力端OPに伝達し、第3クロック信号CK2の低レベル電圧V12によって維持信号Vs<sub>i</sub>の電圧レベルは低レベル電圧(V-)になる。一方、導通したトランジスタTr2は第1クロック信号CK1をトランジスタTr4の制御端子に伝達し、導通したトランジスタTr3は第2クロック信号CK1BをトランジスタTr5の制御端子に伝達する。20

#### 【0054】

第1クロック信号CK1と第2クロック信号CK1Bとは互いに反転した信号であるので、トランジスタTr4とトランジスタTr5とは互いに反対に動作する。つまり、トランジスタTr4が導通すれば、トランジスタTr5が遮断され、反対に、トランジスタTr4が遮断されれば、トランジスタTr5が導通する。トランジスタTr4が導通し、トランジスタTr5が遮断されれば、低電圧AVSSが出力端OPに伝達され、トランジスタTr4が遮断され、トランジスタTr5が導通すれば、高電圧AVDDが出力端OPに伝達される。

#### 【0055】

ゲート信号g<sub>i+1</sub>のゲートオン電圧Vonの状態は、例えば、2H間維持され、前半1H間を前半区間T1、後半1H間を後半区間T2とする。30

前半区間T1の間に、第1クロック信号CK1は高レベル電圧Vh1であり、第2及び第3クロック信号CK1B、CK2は低レベル電圧V11、V12であるので、トランジスタTr1が伝達する第3クロック信号CK2の低レベル電圧V12がかかっている出力端OPには、トランジスタTr4が伝達する低電圧AVSSがかかる。したがって、維持信号Vs<sub>i</sub>は低レベル電圧V12及び低電圧AVSSと同一の大きさの低レベル電圧(V-)になる。一方、前半区間T1の間に、キャパシタC1には第1クロック信号CK1の高レベル電圧Vh1と低電圧AVSSとの差ほどの電圧が充電され、キャパシタC2には第2クロック信号CK1Bの低レベル電圧V11と高電圧AVDDとの差ほどの電圧が充電される。40

#### 【0056】

後半区間T2の間に、第1クロック信号CK1は低レベル電圧V11であり、第2及び第3クロック信号CK1B、CK2は高レベル電圧Vh1、Vh2であるので、前半区間T1とは反対にトランジスタTr5は導通し、トランジスタTr4は遮断される。

これにより、出力端OPには導通したトランジスタTr1を通じて伝えられる第3クロック信号CK2の高レベル電圧Vh2がかかるようになって、維持信号Vs<sub>i</sub>は低レベル電圧(V-)から高レベル電圧Vh2と同一レベルの高レベル電圧(V+)に変化するようになる。また、出力端OPには導通したトランジスタTr5を通じて高レベル電圧(V+)と同一レベルの高電圧AVDDが印加される。

#### 【0057】

10

20

30

40

50

一方、キャパシタC1の充電電圧は、第1クロック信号CK1の低レベル電圧V11と低電圧AVSSの差と同一であるので、これら二つの電圧が同一であればキャパシタC1は放電される。キャパシタC2の充電電圧は、第2クロック信号CK1Bの高レベル電圧V11と高電圧AVDDの差と同一であるので、これら二つの電圧が互いに異なればキャパシタC2の充電電圧は0でない。前述で例に挙げたように、第2クロック信号CK1Bの高レベル電圧Vh1が約15Vであり、高電圧AVDDが約5Vである場合には、約10Vの電圧がキャパシタC2に充電される。

#### 【0058】

後半区間T2が終了して、ゲート信号 $g_{i+1}$ がゲートオン電圧Vonからゲートオフ電圧Voffに変化すれば、トランジスタTr1～Tr3は遮断状態に変わる。したがって、トランジスタTr1の出力端子が孤立状態になってトランジスタTr1と出力端OPの電気的な接続が孤立状態となり、また、トランジスタTr2、Tr3の出力端子が孤立状態となる。これによりトランジスタTr4、Tr5の制御端子も孤立状態となる。

10

#### 【0059】

キャパシタC1には電圧が充電されていないので、トランジスタTr4は遮断状態を維持する。しかし、キャパシタC2には第2クロック信号CK1Bの高レベル電圧Vh1と高電圧AVDDの差によって電圧が充電されているので、その電圧がトランジスタTr5のしきい電圧以上である場合に、トランジスタTr5は導通状態を維持する。したがって、出力端OPには高電圧AVDDが伝えられて維持信号Vs1として出力される。これによつて維持信号Vs1は高レベル電圧(V+)を維持する。

20

#### 【0060】

次に、(i+1)番目信号生成回路の動作について説明する。

(i+1)番目信号生成回路(図示せず)に(i+2)番目ゲート信号 $g_{i+2}$ のゲートオン電圧Vonが印加されれば、(i+1)番目信号生成回路が動作する。

#### 【0061】

図4に示すように、(i+2)番目ゲート信号 $g_{i+2}$ がゲートオン電圧Vonになれば、この時の第1乃至第3クロック信号CK1、CK1B、CK2の状態は、(i+1)番目ゲート信号 $g_{i+1}$ がゲートオン電圧Vonになる時の状態と反対になる。

#### 【0062】

これによって、(i+2)番目ゲート信号 $g_{i+2}$ の前半ゲートオン電圧Vonの区間T1である時の動作は、(i+1)番目ゲート信号 $g_{i+1}$ の後半ゲートオン電圧Vonの区間T2である時の動作と同一であるので、トランジスタTr1、Tr3、Tr5のターンオン動作によって第3クロック信号CK2の高レベル電圧Vh2と高電圧AVDDが出力端OPにかかるようになって、維持信号Vs<sub>i+1</sub>は高レベル電圧(V+)になる。

30

#### 【0063】

しかし(i+2)番目ゲート信号 $g_{i+2}$ の後半ゲートオン電圧Vonの区間T2である時の動作は、(i+1)番目ゲート信号 $g_{i+1}$ の前半ゲートオン電圧Vonの区間T1である時の動作と同一であるので、トランジスタTr1、Tr2、Tr4のターンオン動作によって第3クロック信号CK2の低レベル電圧V12と低電圧AVSSが出力端OPにかかるようになって、維持信号Vs<sub>i+1</sub>は高レベル電圧(V+)から低レベル電圧(V-)に変化する。

40

#### 【0064】

上述したように、トランジスタTr1は、入力信号の電圧状態がゲートオン電圧Vonを維持する間に、第3クロック信号CK2を維持信号として印加するためのトランジスタであり、残りのトランジスタTr2～Tr5は、入力信号がゲートオフ電圧Voffであつて、出力端OPがトランジスタTr1の出力端子と孤立状態である時に、キャパシタC1、C2を利用して該当維持電極線に印加される維持信号の電圧状態を次のフレームまで維持するためのトランジスタである。つまり、トランジスタTr1は該当維持電極線に維持信号を初期に印加するためのものであり、残りのトランジスタTr2～Tr5は出力されている維持信号を一定に維持するためのものであるので、トランジスタTr2～Tr5

50

の大きさは第1トランジスタTr1の大きさよりはるかに小さいことが良い。

【0065】

このような維持信号Vsの電圧変化によって、画素電極電圧Vpが増減する。次に、このような維持信号Vsの電圧変化による画素電極電圧Vpの変化について説明する。以下、キャパシタとこれらキャパシタの静電容量は、同一の図面符号で表示する。

【0066】

まず、画素電極電圧Vpは以下の式1によって求められる。式1において、 $C_{1c}$ と $C_{st}$ は各々液晶キャパシタ及びストレージキャパシタこれらの静電容量を示し、(V+)は維持信号Vsの高レベル電圧であり、(V-)は維持信号Vsの低レベル電圧である。式1から分かるように、画素電極電圧Vpは、キャパシタの静電容量 $C_{1c}$ 、 $C_{st}$ 及び維持信号Vsの電圧変化によって決められる変化量△が、データ電圧 $V_D$ に加減された値である。10

【0067】

【数1】

$$Vp = V_D \pm \Delta = V_D \pm \frac{C_{st}}{C_{st} + C_{1c}} \{ (V+) - (V-) \}$$

データ電圧 $V_D$ の範囲は約0V～5Vであり、 $C_{st}$ と $C_{1c}$ の値が互いに同一になるように画素を設計して、(V+) - (V-) = 5Vである場合、式1は $Vp = V_D \pm 2.5$ となる。20

【0068】

結局、維持信号Vsの電圧が変わる時、画素電極電圧Vpは、データ電圧 $V_D$ の極性によって、該当データ線 $D_1$ ～ $D_m$ を通じて印加されるデータ電圧 $V_D$ より約±2.5Vほど増減される。つまり、(+)極性の時に約+2.5V増加し、(-)極性の時に約-2.5V減少する。このような画素電極電圧Vpの変化によって画素電圧の範囲も増加する。

【0069】

例えば、共通電圧 $V_{com}$ が約2.5Vに固定されている時、画素に印加される約0V～5Vのデータ電圧 $V_D$ による画素電圧の範囲は約-2.5V～+2.5Vであるが、維持信号Vsが高レベル電圧(V+)または低レベル電圧(V-)に変化する時、画素電圧の範囲は約-5V～+5Vに広くなる。30

このように、維持信号Vsの電圧変化{(V+) - (V-)}によって増加した画素電極電圧Vpの変化量△ほど画素電圧の範囲が広くなるので、階調表現のための電圧範囲が増加して輝度が向上する。

【0070】

また、共通電圧が一定の電圧に固定されているので、低い電圧と高い電圧を交互に印加する時より消費電力が減少する。つまり、データ線と共通電極との間に発生する寄生キャパシタにおいて、共通電極に印加される共通電圧が約0または5Vである場合、この寄生キャパシタに印加される電圧は最大約±5Vである。しかし、共通電圧が約2.5Vに固定される場合、データ線と共通電極との間に発生する寄生キャパシタに印加される電圧は最大約±2.5Vに減少する。したがって、データ線と共通電極との間で発生する寄生キャパシタで消費される電力が減少して、液晶表示装置の総消費電力が減少する。40

【0071】

しかし、液晶の応答速度が遅いため、画素電圧によって液晶分子が速かに反応しない。したがって、液晶キャパシタ $C_{1c}$ の静電容量は、液晶キャパシタ $C_{1c}$ の両端に印加される画素電圧に反応して、液晶分子の再整列が完了した安定化状態に到達したか否かによって変わる。この液晶分子が安定化状態に到達したか否かによって画素電極電圧Vpが変化する。50

## 【0072】

次に、画素電圧に反応して液晶分子が安定化状態に到達した場合と、そうでない場合との、画素電極電圧  $V_p$  の変化について説明する。

## 【0073】

最大値の画素電圧、つまり、最大階調（ノーマリープラックである場合、ホワイト階調）の画素電圧が液晶キャパシタ  $C_{1c}$  に印加された後に液晶分子が安定化状態に到達する時、液晶キャパシタ  $C_{1c}$  の静電容量が最小値の画素電圧、最少階調（ノーマリープラックである場合、ブラック階調）の画素電圧が液晶キャパシタ  $C_{1c}$  に印加された後に液晶分子が安定化状態に到達する時、液晶キャパシタ  $C_{1c}$  の静電容量の約 3 倍であると仮定する。また、 $(V+) - (V-) = 5 V$  であり、 $C_{1c} = C_{st}$  とする。

10

## 【0074】

したがって、最大階調の画素電圧が液晶キャパシタ  $C_{1c}$  に印加された後に液晶分子が安定化状態に到達する時、画素電極電圧  $V_p$  は上記数式 1 の通りであり、既に記述したように、 $(V+) - (V-) = 5 V$  であり、 $C_{1c} = C_{st}$  であるので、画素電極電圧  $V_p$  は  $V_p = V_D \pm 2.5$  となる。

しかし、最大階調の画素電圧が液晶キャパシタ  $C_{1c}$  に印加された後、液晶分子が安定化状態に到達できない場合には、画素電極電圧  $V_p$  は、以下の数式 2 の通りである。

## 【0075】

## 【数 2】

$$\begin{aligned} V_p &= V_D \pm \Delta = V_D \pm \frac{C_{st}}{C_{st} + C_k} \{ (V+) - (V-) \} \\ &= V_D \pm \frac{C_{st}}{C_{st} + \frac{1}{3} C_{st}} \{ (V+) - (V-) \} = V_D \pm \frac{3}{4} \{ (V+) - (V-) \} \end{aligned}$$

20

この時、 $(V+) - (V-) = 5 V$  であるので、 $V_p = V_D \pm 3.75$  である。

## 【0076】

このように、最大階調の画素電圧が液晶キャパシタ  $C_{1c}$  に印加された後、液晶分子が安定化状態に到達できない場合、画素電極電圧  $V_p$  は、最少階調の画素電圧が液晶キャパシタ  $C_{1c}$  に印加された後、液晶分子が安定化状態に到達した時の画素電極電圧を維持する。つまり、直前フレームの状態を維持する。したがって、維持信号の電圧変化  $\{ (V+) - (V-) \}$  による画素電極電圧  $V_p$  の変化量 は、 $\pm 2.5 V$  から  $\pm 3.75 V$  に増加する。

30

## 【0077】

したがって、最少階調の画素電極電圧から他の階調の画素電極電圧に変化する場合、液晶分子が安定化状態に到達する前までは、数式 2 によって維持信号の電圧変化  $\{ (V+) - (V-) \}$  による画素電極電圧  $V_p$  の変化量 はさらに増加し、 $(V+) - (V-) = 5 V$  である場合、最大  $\pm 3.75 V$  まで増加する。

## 【0078】

40

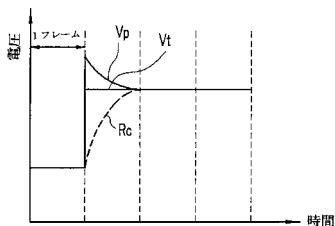

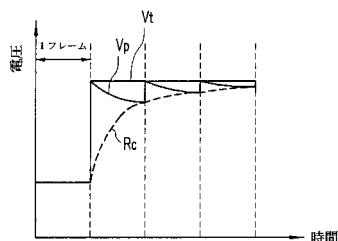

これによって、従来の技術においては、図 6 に示すように、毎フレームごとに目標画素電極電圧  $V_T$  に相当する画素電極電圧  $V_p$  を該当画素電極に印加しても、画素電極に充電された画素電極電圧は充電動作が完了した後、隣接したデータ電圧などの影響によって減少し、結局、1 フレーム内に目標画素電極電圧  $V_T$  に到達できず、いくつかのフレームを経て目標画素電極電圧  $V_T$  に到達するが、本実施形態においては、図 5 に示すように、該当画素電極に印加される画素電極電圧  $V_p$  が目標画素電極電圧  $V_T$  よりはるかに高い電圧が印加されるので、1 フレーム内に該当画素電極が目標画素電極電圧  $V_T$  に到達して、従来の技術より液晶の応答速度  $R_C$  が向上する。

## 【0079】

したがって、画素電極電圧  $V_p$  は、充電されているデータ電圧  $V_D$  に維持信号  $V_s$  の電

50

圧変化量が加減されて、画素 P X が正極性データ電圧によって充電されている場合には、画素電極電圧 V p は変化量ほど増加し、反対に、画素 P X が負極性データ電圧によって充電されている場合には、画素電極電圧 V p は変化量ほど減少する。これによって、画素電圧の変化は増減された画素電極電圧 V p によって階調電圧の範囲より広くなり、表現される輝度範囲も広くなる。

また、既に説明したように、共通電圧 V c o m が一定の電圧に固定されているので、低い電圧と高い電圧を交互に印加する時より消費電力が減少する。

#### 【 0 0 8 0 】

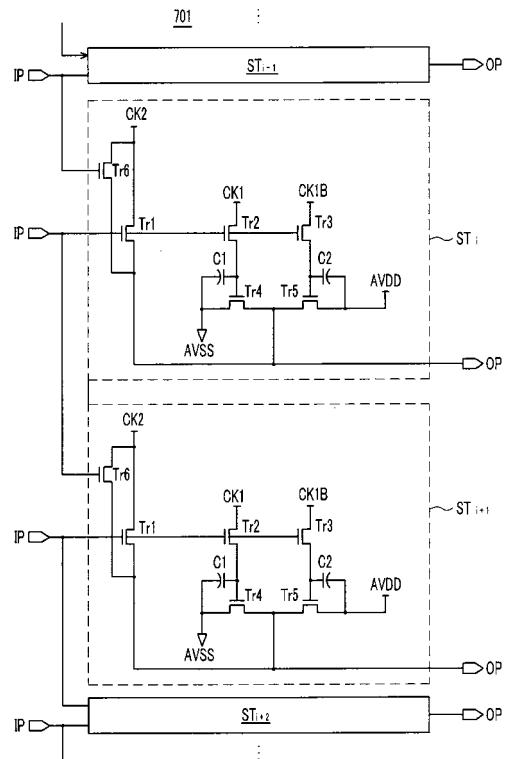

次に、図 7 ~ 図 9 を参照して、本発明の他の実施形態による液晶表示装置について説明する。

10

図 7 は本発明の他の実施形態による液晶表示装置のブロック図である。図 8 は本発明の他の実施形態による信号生成回路の回路図であり、図 9 は図 8 に示した信号生成回路を含む液晶表示装置に用いられる信号のタイミング図である。

#### 【 0 0 8 1 】

図 7 に示すように、本発明の他の実施形態による液晶表示装置は、全ての一般ゲート線 G<sub>1</sub> ~ G<sub>2n</sub> と付加ゲート線 G<sub>d1</sub> に接続された一つのゲート駆動部 401 と、全ての維持電極線 S<sub>1</sub> ~ S<sub>2n</sub> に接続された一つの維持信号生成部 701 とを除けば、図 1 に示した液晶表示装置の構造と同一であるため、同じ図面符号を付けており、これらに対する詳細な説明は省略する。

#### 【 0 0 8 2 】

ゲート駆動部 401 と維持信号生成部 701 は、画素 P X のスイッチング素子 Q と同一の工程により形成されて液晶表示板組立体 301 に集積されているが、これらは各々一つの集積回路チップの形態で液晶表示板組立体 301 上に直接装着したり、可撓性印刷回路フィルム（図示せず）上に装着されて T C P の形態で液晶表示板組立体 301 に付着させたり、別途の印刷回路基板（図示せず）上に装着することもできる。

20

ゲート駆動部 401 は、第 1 一般ゲート線 G<sub>1</sub> から付加ゲート線 G<sub>d1</sub> に順次にゲートオン電圧 V<sub>on</sub> を印加して、各一般ゲート線 G<sub>1</sub> ~ G<sub>2n</sub> に接続された該当画素行の充電動作と維持信号生成部 701 の動作を制御する。

#### 【 0 0 8 3 】

また、維持信号生成部 701 は、各維持電極線 S<sub>1</sub> ~ S<sub>2n</sub> に接続された複数の信号生成回路 S<sub>T1</sub> ~ S<sub>T2n</sub> を含んでおり、各信号生成回路は入力信号を除けば、全て同一の構造で形成されて同じ動作を行うので、図 8 を参照して、i 番目と (i + 1) 番目維持電極線 S<sub>i</sub>、S<sub>i+1</sub> に維持信号 V<sub>s\_i</sub>、V<sub>s\_{i+1}</sub> を各々印加する、i 番目と (i + 1) 番目信号生成回路 S<sub>Ti</sub>、S<sub>T{i+1}</sub> の構造と動作についてのみ説明する。

30

#### 【 0 0 8 4 】

図 8 に示すように、各信号生成回路 S<sub>T1</sub> ~ S<sub>T2n</sub> は、第 6 トランジスタ T<sub>r6</sub> をさらに含んでいることを除けば、図 3 に示した信号生成回路と同一であるため、これら T<sub>r1</sub> ~ T<sub>r5</sub> に対する構造の説明は省略する。

信号生成回路の第 6 トランジスタ T<sub>r6</sub> は、第 3 クロック信号 C K 2 に入力端子が接続されており、直前の信号生成回路の入力端 I P に制御端子が接続されており、出力端 O P に出力端子が接続されている。

40

#### 【 0 0 8 5 】

第 6 トランジスタは、第 1 ~ 第 5 トランジスタのように非晶質シリコンまたは多結晶シリコンの薄膜トランジスタからなることができる。

このように、任意の一つの画素行に形成された維持電極線に接続された信号生成回路は、該当画素行に印加されるゲート信号だけでなく、直前の画素行に印加されるゲート信号の印加を受けるので、最後の維持電極線 S<sub>2n</sub> に接続された信号生成回路は、補助ゲート線 G<sub>d1</sub> に接続されてゲート信号の印加を受ける。これとは異なって、最後の維持電極線 S<sub>2n</sub> に接続された信号生成回路は、信号制御部 600 などのようにゲート駆動部 401 でない他の装置や外部から制御信号の印加を受けることができる。

50

## 【0086】

このような信号生成回路の動作について、図9を参照して説明する。

既に説明したように、液晶表示装置は行反転とフレーム反転を行う。また、図9に示すように、第1乃至第3クロック信号CK1、CK1B、CK2は図4に示したクロック信号CK1、CK1B、CK2と同一である。

図9に示すように、各ゲート線 $G_1 \sim G_{2n}$ 、 $G_{d1}$ に順次に印加されるゲートオン電圧 $V_{on}$ は、隣接したゲートオン電圧 $V_{on}$ と所定時間重畠せず、第1一般ゲート線 $G_1$ から順次に補助ゲート線 $G_{d1}$ に印加される。

## 【0087】

まず、 $i$ 番目信号生成回路 $ST_i$ の動作について説明する。

10

$i$ 番目ゲート線 $G_i$ に印加されるゲート信号 $g_i$ がゲートオン電圧 $V_{on}$ になれば、 $i$ 番目信号生成回路 $ST_i$ の第6トランジスタ $Tr_6$ が導通して、第3クロック信号CK2の低レベル電圧 $V_{l2}$ が維持信号 $V_{s_i}$ として出力端OPを通じて $i$ 番目維持電極線 $S_i$ に印加され、低レベル電圧( $V_-$ )を維持する。

## 【0088】

次に、1H経過後、 $(i+1)$ 番目ゲート線 $G_{i+1}$ にゲートオン電圧 $V_{on}$ が印加されれば、第1乃至第3トランジスタ $Tr_1 \sim Tr_3$ が導通する。

したがって、図9に示すように、第1トランジスタ $Tr_1$ が導通する間に、第3クロック信号CK2の高レベル電圧 $V_{h2}$ が出力端OPを通じて維持信号 $V_{s_i}$ として維持電極線 $S_i$ に印加されるので、維持信号 $V_{s_i}$ は低レベル電圧( $V_-$ )から高レベル電圧( $V_+$ )に変化する。

20

## 【0089】

$(i+1)$ 番目ゲート信号 $g_{i+1}$ がゲートオン電圧 $V_{on}$ である時、第1クロック信号CK1は低レベル電圧 $V_{l1}$ を維持し、第2クロック信号CK1Bは高レベル電圧 $V_{h1}$ を維持する。したがって、導通したトランジスタ $Tr_2$ 、 $Tr_3$ を通じて各々第4及び第5トランジスタ $Tr_4$ 、 $Tr_5$ の制御端子に低レベル電圧と高レベル電圧が印加されて、第5トランジスタ $Tr_5$ は導通し、第4トランジスタ $Tr_4$ は遮断され、キャパシタC2の充電動作が行われる。これによって、 $(i+1)$ 番目ゲートオン電圧 $V_{on}$ が印加される間に、導通したトランジスタ $Tr_1$ 、 $Tr_5$ によって高レベル電圧( $V_+$ )の維持信号 $V_{s_i}$ が出力端OPに印加され、また、 $(i+1)$ 番目ゲート線 $G_{i+1}$ に印加されるゲート信号 $g_{i+1}$ がゲートオフ信号 $V_{off}$ を維持する間、キャパシタC2の充電電圧によりトランジスタ $Tr_5$ が導通して高電圧AVDDが出力端子OPに印加され、維持信号 $V_{s_i}$ は高レベル電圧( $V_+$ )を維持する。

30

## 【0090】

つまり、 $i$ 番目ゲート信号 $g_i$ がゲートオン電圧 $V_{on}$ になって $i$ 番目ゲート線 $G_i$ に接続された画素行の充電動作が完了した後、維持信号 $V_{s_i}$ が低レベル電圧( $V_-$ )から高レベル電圧( $V_+$ )に変換して、画素電極電圧 $V_p$ は数式1または数式2によって決められた変化量ほど増加する。

このような $i$ 番目信号生成回路 $ST_i$ の動作と類似して、図9に示すように、 $(i+1)$ 番目ゲート信号 $g_{i+1}$ がゲートオン電圧 $V_{on}$ を維持する間にトランジスタ $Tr_6$ が導通し、これによって導通したトランジスタ $Tr_6$ を通じて伝えられる第3クロック信号CK2の高レベル電圧 $V_{h2}$ によって、 $(i+1)$ 番目維持電極線 $S_{i+1}$ から出力される維持信号 $V_{s_{i+1}}$ は電圧状態である高レベル電圧( $V_+$ )を維持する。

40

## 【0091】

次に、 $(i+2)$ 番目ゲート信号 $g_{i+2}$ にゲートオン電圧 $V_{on}$ が印加されれば、トランジスタ $Tr_1$ 、 $Tr_2$ 、 $Tr_4$ が導通し、キャパシタC1が充電されて、維持信号 $V_{s_{i+1}}$ は導通したトランジスタ $Tr_1$ 、 $Tr_5$ を通じて伝えられる低レベル電圧 $V_{l2}$ と低電圧AVSSによって、高レベル電圧( $V_+$ )から低レベル電圧( $V_-$ )に変化する。

また、 $(i+2)$ 番目ゲート線 $G_{i+2}$ に印加されるゲート信号 $g_{i+2}$ がゲートオフ

50

信号  $V_{off}$  を維持する間に、キャパシタ  $C_1$  の充電電圧によってトランジスタ  $T_r4$  が導通し、低電圧  $AVSS$  が出力端  $OP$  に印加されて、維持信号  $V_{S_{i+1}}$  は低レベル電圧 ( $V-$ ) を維持する。

#### 【0092】

これによって、( $i+1$ )番目ゲート信号  $g_{i+1}$  がゲートオン電圧  $V_{on}$  になって、( $i+1$ )番目ゲート線  $G_{i+1}$  に接続された画素行の充電動作が完了した後、維持信号  $V_{S_{i+1}}$  が高レベル電圧 ( $V+$ ) から低レベル電圧 ( $V-$ ) に変換して、画素電極電圧  $V_p$  は数式1または数式2によって決められた変化量ほど減少する。本実施形態において、第6トランジスタ  $T_r6$  は該当維持電極線に印加される維持信号の電圧状態を維持するためのトランジスタであるので、トランジスタ  $T_r6$  の大きさは第1トランジスタ  $T_r1$  の大きさよりはるかに小さいことが良い。10

#### 【0093】

次に、このような本発明の一実施形態による液晶表示装置の薄膜トランジスタ表示板の詳細構造について、図面を参照して詳細に説明する。

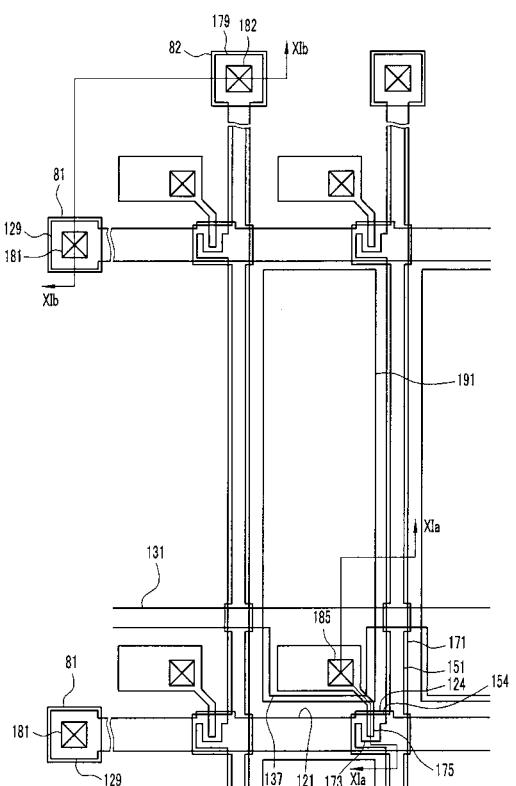

まず、図10及び図11(a)(b)を参照して、本発明の一実施形態による液晶表示装置の薄膜トランジスタ表示板の一例について説明する。

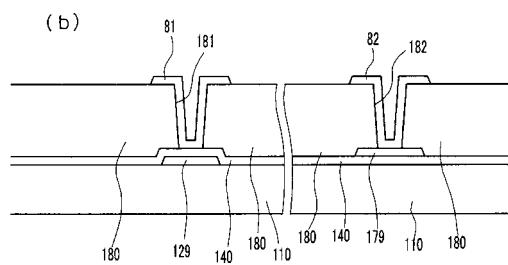

図10は本発明の一実施形態による液晶表示装置の薄膜トランジスタ表示板に対する配置図の一例であり、図11(a)及び(b)は各々図10の薄膜トランジスタ表示板のX $Ia$ - $XIa$ 線及び $XIb$ - $XIb$ 線に沿った断面図である。

#### 【0094】

透明なガラスまたはプラスチックなどで作られた絶縁基板110上に、複数のゲート線 (gate line) 121及び複数の維持電極線 (storage electrode line) 131が形成されている。20

ゲート線121はゲート信号を伝達し、主に横方向に延在している。各ゲート線121は、(図10で上に)突出した複数のゲート電極 (gate electrode) 124と、他の層または外部駆動回路との接続のために面積の広い端部129とを含む。

#### 【0095】

ゲート信号を生成するゲート駆動回路(図示せず)は、絶縁基板110上に付着される可撓性印刷回路フィルム(図示せず)上に装着したり、絶縁基板110上に直接装着されたり、絶縁基板110に直接集積できる。ゲート駆動回路が絶縁基板110上に集積されている場合、ゲート線121が延長されてこれと直接接続することができる。30

それぞれの維持電極線131は主に横方向に延在しており、(図10で幅が下に)拡張された複数の拡張部137を含む。維持電極線131は、また、他の層または外部駆動回路との接続のために面積の広い端部を含むことができる。しかし、維持電極線131の形状及び配置は多様に変更できる。

#### 【0096】

各維持電極線131には、約5Vの高レベル電圧 ( $V+$ ) と約0Vの低レベル電圧 ( $V-$ ) のような所定の電圧が、フレーム単位で交互に印加される。

維持電圧を生成する信号生成回路(図示せず)は、絶縁基板110上に付着される可撓性印刷回路フィルム(図示せず)上に装着したり、絶縁基板110上に直接装着したり、絶縁基板110に直接集積できる。信号生成回路が絶縁基板110上に集積される場合、維持電極線131が延長されて信号生成回路と直接接続することもできる。40

#### 【0097】

ゲート線121と維持電極線131は、アルミニウム(A1)やアルミニウム合金などアルミニウム系金属、銀(Ag)や銀合金など銀系金属、銅(Cu)や銅合金など銅系金属、モリブデン(Mo)やモリブデン合金などモリブデン系金属、クロム(Cr)、タンタル(Ta)及びチタニウム(Ti)などで作ることができる。しかし、これらは物理的性質が異なる二つの導電膜(図示せず)を含む多重膜構造を有することもできる。

#### 【0098】

このうちの一つの導電膜は、信号遅延や電圧降下を減らすことができるように比抵抗(

10

20

30

40

50

*resistivity*) が低い金属、例えば、アルミニウム系金属、銀系金属、銅系金属などで作られる。これとは異なって、他の方の導電膜は、他の物質、特にITO(indium tin oxide)及びIZO(indium zinc oxide)との物理的、化学的、電気的接合特性に優れた物質、例えば、モリブデン系金属、クロム、タンタル、チタニウムなどで作られる。このような組み合わせの良い例としては、クロム下部膜とアルミニウム(合金)上部膜、及びアルミニウム(合金)下部膜とモリブデン(合金)上部膜がある。しかし、ゲート線121及び維持電極線131はその他にも多様な金属または導電体で作ることができる。

#### 【0099】

ゲート線121及び維持電極線131の側面は絶縁基板110面に対して傾斜しており、その傾斜角は約30°～約80°であることが好ましい。10

ゲート線121及び維持電極線131上には、窒化ケイ素(SiNx)または酸化ケイ素(SiOx)などで作られたゲート絶縁膜(gate insulating layer)140が形成されている。

#### 【0100】

ゲート絶縁膜140上には、水素化非晶質シリコン(hydrogenated amorphous silicon)(非晶質シリコンは、略してa-Siと記す)または多結晶シリコン(polysilicon)などで作られた複数の線状半導体151が形成されている。線状半導体151は主に縦方向に延在しており、ゲート電極124に向かってのび出た複数の突出部(projection)154を含む。線状半導体151はゲート線121及び維持電極線131の付近で幅が広くなって、これらを幅広く覆っている。20

#### 【0101】

線状半導体151上には複数の線状及び島型オーミックコンタクト部材(ohmic contact)161、165が形成されている。オーミックコンタクト部材161、165は、リンなどのn型不純物が高濃度にドーピングされているn+水素化非晶質シリコンなどの物質、またはシリサイド(silicide)で作ることができる。線状オーミックコンタクト部材161は複数の突出部163を有しており、この突出部163と島型オーミックコンタクト部材165とは対をなして線状半導体151の突出部154上に配置されている。30

#### 【0102】

線状半導体151とオーミックコンタクト部材161、165の側面も絶縁基板110面に対して傾斜しており、その傾斜角は30°～80°程度である。

線状及び島型オーミックコンタクト部材161、165及びゲート絶縁膜140上には、複数のデータ線171と複数のドレイン電極175とが形成されている。

#### 【0103】

データ線171はデータ信号を伝達し、主に縦方向に延在してゲート線121及び維持電極線131と交差する。各データ線171は、ゲート電極124に向かって延在した複数のソース電極173と、他の層または外部駆動回路との接続のために面積の広い端部179とを含む。データ信号を生成するデータ駆動回路(図示せず)は、絶縁基板110上に付着される可撓性印刷回路フィルム(図示せず)上に装着したり、絶縁基板110上に直接装着したり、絶縁基板110に直接集積できる。データ駆動回路が絶縁基板110上に集積される場合、データ線171が延長されてこれと直接接続ができる。40

ドレイン電極175はデータ線171と分離されており、ゲート電極124を中心にしてソース電極173と対向する。各ドレイン電極175は、広い一側端部と、棒状の他側端部とを含む。広い端部は維持電極線131の拡張部137と重畠し、棒状の端部は曲がったソース電極173によって一部取り囲まれている。

#### 【0104】

一つのゲート電極124、一つのソース電極173、及び一つのドレイン電極175は、線状半導体151の突出部154と共に一つの薄膜トランジスタ(thin film)50

transistor、TFT)をなし、薄膜トランジスタのチャネルはソース電極173とドレイン電極175との間の突出部154に形成される。

#### 【0105】

データ線171及びドレイン電極175は、モリブデン、クロム、タンタル及びチタニウムなど耐火性金属(refractory metal)またはこれらの合金で作ることが好ましく、耐火性金属膜(図示せず)と低抵抗導電膜(図示せず)を含む多重膜構造を有することができる。多重膜構造の例としては、クロムまたはモリブデン(合金)下部膜とアルミニウム(合金)上部膜の二重膜、モリブデン(合金)下部膜とアルミニウム(合金)中間膜とモリブデン(合金)上部膜の三重膜がある。しかし、データ線171及びドレイン電極175はその他にも多様な金属または導電体で作ることができる。

データ線171及びドレイン電極175もその側面が、絶縁基板110面に対して30°～80°程度の傾斜角で傾斜していることが好ましい。

#### 【0106】

線状及び島型オーミックコンタクト部材161、165は、その下の線状半導体151と、その上のデータ線171及びドレイン電極175との間にだけ存在し、これらの間の接触抵抗を低くする。大部分の所では線状半導体151がデータ線171より狭いが、上述したように、ゲート線121と合う部分で幅が広くなって表面のプロファイルをスムーズにすることにより、データ線171が断線することを防止する。線状半導体151には、ソース電極173とドレイン電極175との間をはじめとして、データ線171及びドレイン電極175によって覆われずに露出した部分がある。

#### 【0107】

データ線171及びドレイン電極175と、露出した線状半導体151部分上には、保護膜(passivation layer)180が形成されている。保護膜180は、無機絶縁物または有機絶縁物などで作られ、表面が平坦であり得る。無機絶縁物の例としては、窒化ケイ素と酸化ケイ素がある。有機絶縁物としては、感光性(photo sensitivity)を有することができ、その誘電率(dielectric constant)は、約4.0以下であることが好ましい。しかし、保護膜180は、有機膜の優れた絶縁特性を生かしながらも露出した線状半導体151の部分に損傷を与えないよう、下部無機膜と上部有機膜の二重膜構造を有することもできる。

#### 【0108】

保護膜180には、データ線171の端部179とドレイン電極175を各々露する複数のコンタクトホール(contact hole)182、185が形成されており、保護膜180とゲート絶縁膜140には、ゲート線121の端部129を露する複数のコンタクトホール181が形成されている。

保護膜180上には、複数の画素電極(pixel electrode)191及び複数のコンタクト補助部材(contact assistant)81、82が形成されている。これらは、ITOまたはIZOなどの透明な導電物質や、アルミニウム、銀、クロムまたはその合金などの反射性金属で作ることができる。

#### 【0109】

画素電極191は、コンタクトホール185を通じてドレイン電極175と物理的・電気的に接続されており、ドレイン電極175からデータ電圧の印加を受ける。データ電圧が印加された画素電極191は、共通電圧(common voltage)の印加を受ける他の表示板(図示せず)の共通電極(common electrode)(図示せず)と共に電場を生成することによって、二つの電極の間の液晶層(図示せず)の液晶分子の方向を決定する。このように決定された液晶分子の方向によって液晶層を通過する光の偏光が変化する。画素電極191と共に電圧は、キャパシタ[以下、“液晶キャパシタ(liquid crystal capacitor)”と言う]をなし、薄膜トランジスタが遮断された後にも印加された電圧を維持する。

#### 【0110】

画素電極191及びこれと電気的に接続されたドレイン電極175が、維持電極線13

10

20

30

40

50

1と重畠してなすキャパシタをストレージキャパシタ(storage capacitors)と言い、ストレージキャパシタは液晶キャパシタの電圧維持能力を強化する。維持電極線131の拡張部137により、重畠面積が増加してストレージキャパシタの静電容量が増加する。

コンタクト補助部材81、82は、各々コンタクトホール181、182を通じてゲート線121の端部129及びデータ線171の端部179と接続される。コンタクト補助部材81、82は、ゲート線121の端部129及びデータ線171の端部179と外部装置との接着性を補完し、これらを保護する。

#### 【0111】

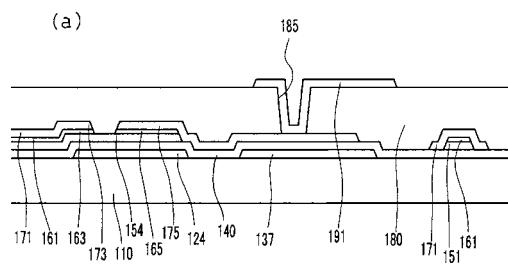

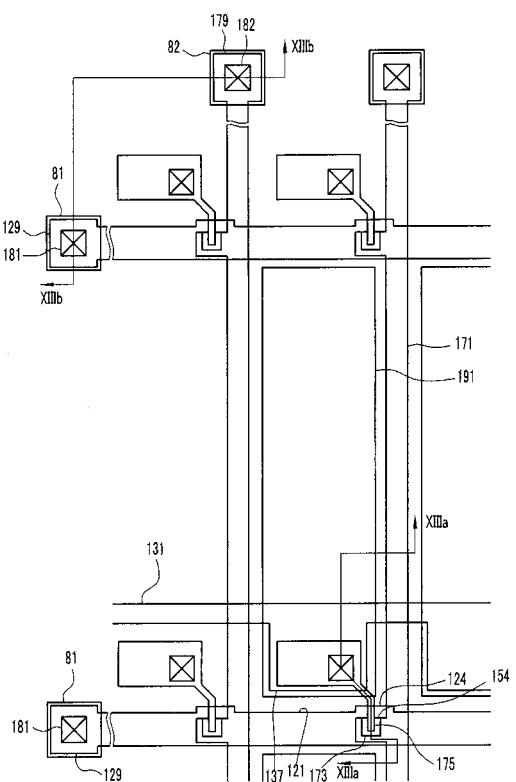

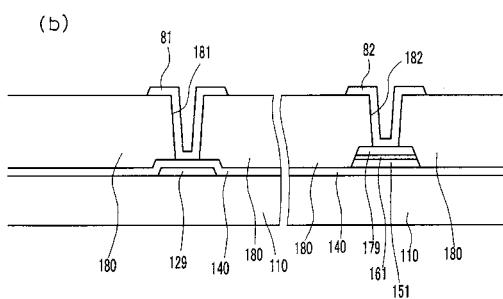

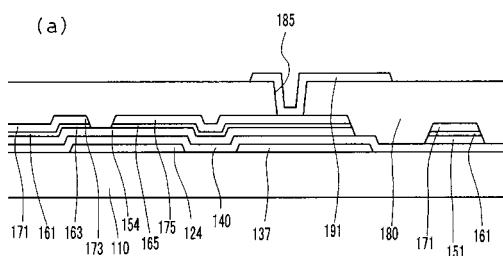

次に、図12～図13(a)(b)を参照して、本発明の一実施形態による薄膜トランジスタ表示板の他の例について詳細に説明する。

10

図12は本発明の一実施形態による液晶表示装置の薄膜トランジスタに対する他の例の配置図であり、図13(a)及び(b)は各々図12の薄膜トランジスタ表示板のXII-a-XIII-a線及びXII-Ib-XIII-Ib線に沿った断面図である。

本実施形態による薄膜トランジスタ表示板の他の例に対する構造は、図10～図11(a)、(b)に示したものと同一である。

#### 【0112】

絶縁基板110上に、ゲート電極124及び端部129を有する複数のゲート線121、及び複数の拡張部137を備えた複数の維持電極線131が形成されており、その上にゲート絶縁膜140、突出部154を有する複数の線状半導体151、突出部163を有する複数の線状オーミックコンタクト部材161、及び複数の島型オーミックコンタクト部材165が順次に形成されている。オーミックコンタクト部材(161、165)上には、ソース電極173及び端部179を含む複数のデータ線171、複数のドレイン電極175が形成されており、その上に保護膜180が形成されている。保護膜180及びゲート絶縁膜140には複数のコンタクトホール181、182、185が形成されており、その上には複数の画素電極191、複数のコンタクト補助部材81、82が形成されている。

20

#### 【0113】

しかし、本実施形態による薄膜トランジスタ表示板は、図10～図11(a)、(b)に示した薄膜トランジスタ表示板と異なって、線状半導体151が、薄膜トランジスタがの位置する突出部154を除けば、データ線171、ドレイン電極175及びその下部のオーミックコンタクト部材(161、165)と実質的に同一の平面形態を有している。つまり、線状半導体151は、データ線171及びドレイン電極175と、その下部のオーミックコンタクト部材(161、165)の下に露出していない部分と、ソース電極173とドレイン電極175の間にこれらによって覆われずに露出した部分を有している。

30

#### 【0114】

尚、本発明は、上述の実施形態に限られるものではない。本発明の技術的範囲から逸脱しない範囲内で多様に変更実施することが可能である。

#### 【図面の簡単な説明】

#### 【0115】

40

【図1】本発明の一実施形態による液晶表示装置のブロック図である。

【図2】本発明の実施形態による液晶表示装置の一つの画素に対する等価回路図である。

【図3】本発明の一実施形態による信号生成回路の回路図である。

【図4】図3に示した信号生成回路を含む液晶表示装置に用いられる信号のタイミング図である。

【図5】本発明の実施形態による信号生成回路の動作による画素電極電圧と液晶の応答速度の変化を示すグラフである。

【図6】従来の画素電極電圧と液晶の応答速度の変化を示すグラフである。

【図7】本発明の他の実施形態による液晶表示装置のブロック図である。

【図8】本発明の他の実施形態による信号生成回路の回路図である。

50

【図9】図8に示した信号生成回路を含む液晶表示装置に用いられる信号のタイミング図である。

【図10】本発明の実施形態による液晶表示装置の薄膜トランジスタ表示板に対する配置図の一例である。

【図11】(a)は図10の薄膜トランジスタ表示板のXⅠa-XⅠa線に沿った断面図であり、(b)は図10の薄膜トランジスタ表示板のXⅠb-XⅠb線に沿った断面図である。

【図12】本発明の実施形態による液晶表示装置の薄膜トランジスタ表示板に対する配置図の他の例である。

【図13】(a)は図12の薄膜トランジスタ表示板のXⅡIa-XⅡIa線に沿った断面図であり、(b)は図12の薄膜トランジスタ表示板のXⅡIb-XⅡIb線に沿った断面図である。 10

【符号の説明】

【0116】

3 液晶層

100、200 (下部及び上部)表示板

191 画素電極

230 カラーフィルタ

270 共通電極

300、301 液晶表示板組立体

20

400 ゲート駆動部

400a、400b 第1及び第2ゲート駆動回路

500 データ駆動部

600 信号制御部

700、701 維持信号生成部

700a、700b 第1及び第2維持信号生成回路

710 信号生成回路

800 階調電圧生成部

C1c 液晶キャパシタ

30

Cst ストレージキャパシタ

G<sub>1</sub> ~ G<sub>2n</sub>、G<sub>d</sub>、G<sub>d1</sub> ゲート線

D<sub>1</sub> ~ D<sub>m</sub> データ線

S<sub>1</sub> ~ S<sub>2n</sub> 維持電極線

ST<sub>1</sub> ~ ST<sub>2n</sub> 信号生成回路

PX 画素

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

---

フロントページの続き

(51)Int.Cl.

F I

|         |      |         |

|---------|------|---------|

| G 0 9 G | 3/20 | 6 1 1 A |

| G 0 9 G | 3/20 | 6 2 1 B |

| G 0 9 G | 3/20 | 6 2 1 F |

| G 0 9 G | 3/20 | 6 2 2 D |

審査官 森口 忠紀

(56)参考文献 特開2005-156764 (JP, A)

特開2005-257931 (JP, A)

特開2006-145923 (JP, A)

特開2007-163824 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 9 G 3 / 0 0 - 3 / 3 8

G 0 2 F 1 / 1 3 3