(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2007년10월09일

(11) 등록번호 10-0764919

(24) 등록일자 2007년10월01일

(51) Int. Cl.

H01L 29/73(2006.01)

(21) 출원번호 10-2002-7003997

(22) 출원일자 2002년03월27일

심사청구일자 2005년08월01일

번역문제출일자 2002년03월27일

(65) 공개번호 10-2002-0064291

공개일자 2002년08월07일

(86) 국제출원번호 PCT/US2000/020958

국제출원일자 2000년08월01일

(87) 국제공개번호 WO 2001/24273

국제공개일자 2001년04월05일

(30) 우선권주장

09/406,451 1999년09월27일 미국(US)

(56) 선행기술조사문헌

1991 IEEE 논문 A NOVEL HIGH-PERFORMANCE

LATERAL BIPOLAR ON SOI

(뒷면에 계속)

전체 청구항 수 : 총 16 항

심사관 : 박정식

(54) SOI 프로세스를 사용한 고속 래터럴 바이폴라 디바이스

### (57) 요 약

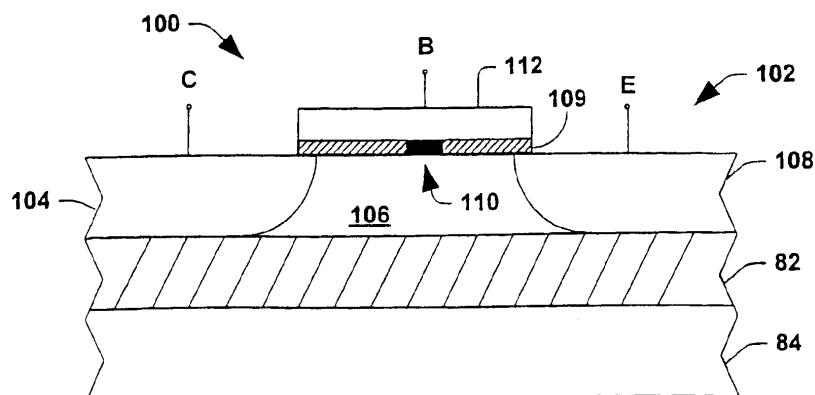

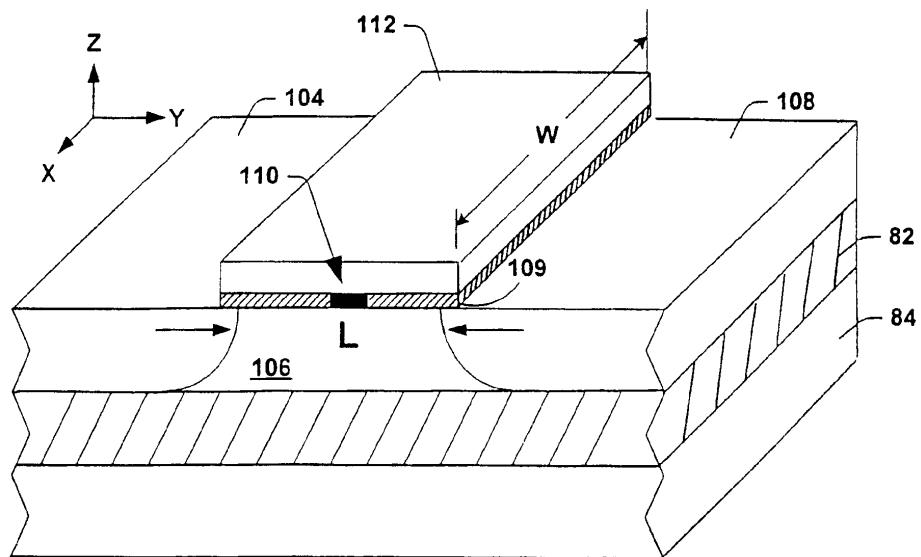

래터럴 바이폴라 트랜지스터(100)는 전기적인 절연 물질(82) 상에 반도체층 및 상기 반도체층의 중앙 부분 상에 절연층(109)을 구비한다. 상기 절연층(109)에 콘택트 정공이 있고, 상기 절연층(109) 상에 도전 물질이 있고, 상기 도전 물질은 상기 콘택트 정공을 통하여 상기 반도체층과 전기적 접촉을 하고, 그럼으로써 베이스 콘택트를 형성한다. 상기 반도체층은 상기 도전 물질의 실질적인 밀의 중앙 영역(106)에 제 1 도전형을 구비한다. 상기 중앙 영역 근처의 영역들(104), (108)에 제 2 도전형을 구비한다. 상기 제 1 영역은 베이스 영역(106)을 형성하고, 상기 인접한 영역들은 콜렉터 영역(104)과 이미터 영역(108)을 각각 형성한다. 그 방법은 절연 물질(109) 상에 반도체층을 형성하는 단계와 상기 반도체 물질 상에 절연층을 형성하는 단계와 상기 절연층(109) 내에 베이스 콘택트를 형성하는 단계와 상기 절연층의 일부분 상에 도전 베이스 콘택트 영역을 형성하는 단계와, 이때 상기 베이스 콘택트 영역은 상기 베이스 콘택트 정공 상에 있고, 상기 반도체층의 중간 부분과의 전기적 연결을 형성하고, 상기 중간 영역은 베이스 영역(106)에 대응하고 상기 베이스 영역의 반대면들 상에 콜렉터 영역(104)과 이미터 영역들(108)을 형성하는 단계를 구비하여 상기 콜렉터 영역(104)과 이미터 영역(108)이 상기 베이스 영역(106)에 각각 인접하도록 한다.

대표도 - 도7

(56) 선 행 기술조사 문현

EP0616370

JP2003510849

JP04116935

JP02003238

(81) 지정국

국내특허 : 중국, 일본, 대한민국, 싱가포르

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일,

덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드,

이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투

칼, 스웨덴, 핀란드, 사이프러스

---

## 특허청구의 범위

### 청구항 1

전기적 절연 물질(82) 상에 반도체층(102)과 상기 반도체층(102)의 중앙부(106)상에 절연 영역(109)을 구비하고, 상기 절연 영역(109)에 콘택트 정공(212)이 있으며, 상기 절연 영역(109) 상에 도전 물질(112)이 있고, 상기 도전 물질(112)은 상기 콘택트 정공(212)을 통하여 상기 반도체층(102)과 전기적으로 접촉함으로써 베이스 콘택트(112)를 형성하는 래터럴 바이폴라 트랜지스터(100)에 있어서,

상기 절연 영역(109)과 그 위의 베이스 콘택트(112)가 상기 반도체층(102)을 인접한 세 영역(104, 106, 108)으로 나누고, 상기 인접한 세 영역 중 중간 영역(106)은 제 1도전형을 구비함과 아울러 상기 트랜지스터(100)의 베이스 영역(106)을 형성하는 상기 중앙 영역(106)이고, 상기 인접한 세 영역 중 다른 한 영역(104)은 제 2 도전형을 구비하고 콜렉터 영역(104)을 형성하며, 상기 세 인접한 영역 중 나머지 한 영역(108)은 제 2 도전형을 구비하고 이미터 영역(108)을 형성하며,

상기 베이스 영역(106)은, 상기 베이스 콘택트(112)의 길이에 실질적으로 대응하는 상기 콜렉터 영역(104)과 이미터 영역(106) 사이의 거리에 의해 정해진 길이 또는 두께(L), 및 상기 베이스 영역 길이(L)에 실질적으로 수직인 방향으로 확장하는 폭(W)을 구비하고, 상기 베이스 콘택트(112)는 실질적으로 상기 베이스 영역(106)의 전체 폭을 따라 확장하는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 2

삭제

### 청구항 3

제 1 항에 있어서, 상기 제 1 도전형은 n-형 반도체 물질이고, 상기 제 2 도전형은 p-형 반도체 물질인 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 4

제 1 항에 있어서, 상기 제 1 도전형은 p-형 반도체 물질이고, 상기 제 2 반도전형은 n-형 반도체 물질인 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 5

제 1 항에 있어서, 상기 절연 영역(109)은 MOS-형 트랜지스터 디바이스에서 사용된 게이트 산화막층에 대응하는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 6

제 1 항에 있어서, 상기 전기적인 절연 물질(82)은 매몰된 실리콘 디옥사이드층으로 이루어지는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 7

제 1 항에 있어서, 상기 도전 물질(112)은 불순물 폴리실리콘 물질 또는 금속으로 이루어지는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 8

제 1 항에 따른 래터럴 바이폴라 트랜지스터(100)를 제조하는 방법에 있어서, 상기 방법은:

(a) 제 1 도전형을 구비한 반도체층(102)의 물질로, 상기 전기적인 절연 물질(82) 상에 상기 반도체층(102)을 형성하는 단계와;

(b) 상기 반도체층(102) 상에 상기 절연 영역(109)을 포함한 절연층(204)을 형성하는 단계와;

(c) 상기 절연 영역(109)에 상기 콘택트 정공(212)을 형성하는 단계와;

(d) 상기 베이스 콘택트(112)를 형성하는 단계 및;

(e) 상기 베이스 콘택트(112)에 대한 자기-정렬에 의해 상기 콜렉터 영역(104)과 이미터 영역(108)을 형성하는 단계를 포함함으로써 상기 콜렉터 및 이미터 영역들(104, 108) 사이에 및 근처에 상기 베이스 영역(106)을 형성하는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터를 제조하는 방법.

### 청구항 9

제 8 항에 있어서, 상기 베이스 콘택트 정공(212)을 형성하는 방법은 상기 절연층(204)의 일부분을 식각하는 단계를 포함하는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터 디바이스를 형성하는 방법.

### 청구항 10

제 9 항에 있어서, 상기 방법은 상기 베이스 콘택트 정공(212)의 측벽 형상을 변경시키는 단계를 추가적으로 포함함으로써, 상기 측벽 형상을 실질적인 수직 형상에서 경사진 형상으로 변경하여 상기 베이스 콘택트 정공(212) 내의 후속하는 단계 허용범위를 향상시키는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터 디바이스를 형성하는 방법.

### 청구항 11

제 8 항에 있어서, 상기 절연층(204) 상에 도전 베이스 영역(112)을 형성하는 단계는:

상기 절연층(204) 상에 도전층을 형성하는 단계 및;

상기 도전층을 패터닝하는 단계를 포함하여 베이스 콘택트(112)를 형성하는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터 디바이스를 형성하는 방법.

### 청구항 12

제 8 항에 있어서, 상기 콜렉터 영역(104)과 이미터 영역(108)을 형성하는 단계는 이온 주입을 수행하는 단계를 포함하고, 이때 주입물이 그 위에 베이스 콘택트(112)를 구비하지 않은 상기 절연층(204)의 부분들을 관통하여 상기 반도체층(102)에 도달하는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터 디바이스를 형성하는 방법.

### 청구항 13

래터럴 바이폴라 트랜지스터에 있어서, 상기 트랜지스터는:

전기적인 절연 물질 상에 반도체층 및;

상기 반도체층의 중앙 부분 상에 절연층을 구비하고, 상기 절연층에 콘택트 정공이 있고, 상기 절연층 상에 도전 물질이 있고, 상기 도전 물질은 상기 콘택트 정공을 통하여 상기 반도체층과 전기적 접촉을 함으로써 베이스 콘택트를 형성하고;

상기 반도체층은 상기 도전 물질의 실질적인 밑의 중앙 영역에 제 1 도전형을 구비하고, 상기 중앙 영역 근처의 영역들에 제 2 도전형을 구비하고, 상기 제 1 영역은 베이스 영역을 형성하고, 상기 인접한 영역들은 콜렉터 영역과 이미터 영역을 각각 형성하고, 상기 베이스 영역은 상기 콜렉터 영역과 이미터 영역 사이의 거리에 의해 정해진 길이 또는 두께와, 상기 베이스 영역 길이에 실질적으로 수직인 방향으로 확장하는 폭을 구비하고, 상기 베이스 콘택트는 상기 베이스 영역의 실질적으로 전체 폭을 따라 확장하고, 그럼으로써 상기 래터럴 바이폴라 트랜지스터의 베이스 저항을 최소화하는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 14

래터럴 바이폴라 트랜지스터에 있어서, 상기 트랜지스터는:

반도체 기판과;

상기 반도체 기판 상에 절연층과;

상기 절연층 상에 반도체층과;

상기 반도체층 상에 있고, 상기 반도체층을 제 1 영역과, 제 2 영역으로 상기 영역들의 중간 영역으로 분리하는 절연 영역 및, 이때 상기 중간 영역은 실질적으로 상기 절연 영역 밑에 있고, 상기 절연층의 상측 부분으로부터

하측 부분으로 콘택트 정공이 확장하고, 그럼으로써 그 밑의 반도체층의 일부분을 노출하고;

상기 콘택트 정공을 통하여 상기 반도체층의 중간 영역을 전기적으로 접촉하고, 상기 접연 영역 상에 있는 도전층을 구비하고,

상기 중간 영역은 제 1 도전형을 구비하고, 상기 래터럴 바이폴라 트랜지스터의 베이스 영역에 대응하고, 상기 제 1 영역은 제 2 도전형을 구비하고, 콜렉터 영역에 대응하고, 상기 제 2 영역은 제 2 도전형을 구비하고 이미터 영역에 대응하고, 상기 베이스 영역은 상기 콜렉터 영역과 이미터 영역 사이의 거리에 의해 정해진 길이 또는 두께와, 상기 베이스 영역 길이에 실질적으로 수직인 방향으로 확장하는 폭을 구비하고, 상기 도전층은 상기 베이스 영역의 실질적인 전체 폭을 따라 확장하고, 그럼으로써 상기 래터럴 바이폴라 트랜지스터의 베이스 저항을 최소화시키는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 15

제 14항에 있어서,

상기 콜렉터 영역과 상기 이미터 영역이 상기 베이스 콘택트에 대하여 자기-정렬(self-aligned)되는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 16

제 1항에 있어서,

상기 콜렉터 영역과 상기 이미터 영역이 상기 베이스 콘택트에 대하여 자기-정렬(self-aligned)되는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 17

제 13항에 있어서,

상기 콜렉터 영역과 상기 이미터 영역이 상기 베이스 콘택트에 대하여 자기-정렬(self-aligned)되는 것을 특징으로 하는 래터럴 바이폴라 트랜지스터.

### 청구항 18

삭제

### 청구항 19

삭제

## 명세서

### 기술 분야

<1> 본 발명은 일반적으로 반도체 디바이스들 및 반도체 공정에 관한 것으로서, 특히 베이스 저항을 저하시키지 않으면서 트랜지스터가 제어 가능한 높은 이득을 나타내는 고성능의 래터럴 바이폴라 트랜지스터를 형성하기 위하여 SOI MOS형 구조물을 이용하는 디바이스 구조 및 이의 제조 방법에 관한 것이다.

### 배경 기술

<2> 집적 회로들은 바람직한 기능을 수행하기 위하여, 예를 들어 트랜지스터들, 저항들, 캐패시터들 등과 같은 많은 회로 소자들을 이용한다. 트랜지스터들은 크게 두 개의 범주들: 바이폴라 트랜지스터들 및 MOSFET (전계 효과) 트랜지스터들로 분류될 수 있다. 바이폴라 트랜지스터들 및 MOSFET (MOS) 트랜지스터 디바이스들은 다른 물리적인 원리들에 의해 작동하지만, 이들은 모두 증폭 또는 스위칭 디바이스들로서 이용된다. 제 1 적용시, 트랜지스터의 기능은 작은 ac 신호들을 정확하게 증폭하는 것이며; 제 2 적용시, 트랜지스터는 ON 상태에서 OFF 상태로, 또는 그 반대로 전환시키는 스위치로서 작동한다. 이러한 트랜지스터 기능들은 하기에서 간단히 설명되는 "트랜지스터 작동" 때문에 존재하는 것이다.

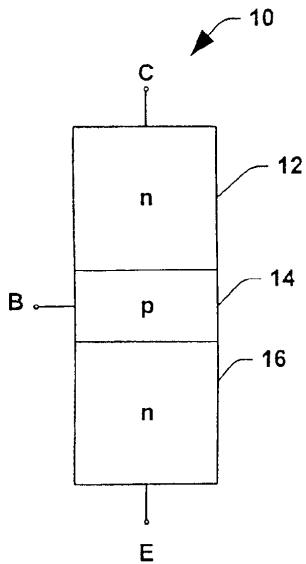

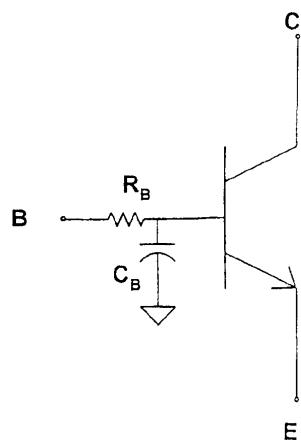

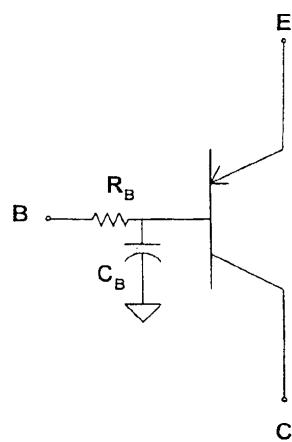

<3> 도 1a 및 1b는 도면 부호 10으로 도시한 종래 기술의 npn-형 바이폴라 트랜지스터의 단순화된 단면도 및 대응하

는 표현을 나타낸다. 도 1a의 종래 기술의 트랜지스터(10)는 npn-형 바이폴라 트랜지스터이고 도핑된 반도체 물질 영역들로 구성되며, 여기서 n-형 영역들은 그들의 다수 캐리어들로서 전자들을 가지며 p-형 영역들은 그들의 다수 캐리어들로서 정공들을 갖는다. 트랜지스터(10)는 콜렉터 영역(12), 베이스 영역(14) 및 이미터 영역(16)을 포함한다.

<4> 도 1a의 npn 바이폴라 트랜지스터는 일반적으로 다음과 같은 방식으로 작동한다. 베이스-이미터 접합에 순방향 바이어스 전압이 인가되면, 많은 양의 전자들이 이미터(16)로부터 베이스(15)로 주입된다. 이미터(16)와 콜렉터(12) 간의 거리가 충분히 작다면(즉, 베이스(14)가 얇다면), 전자들은 재결합되기 전에 콜렉터(12)에 이르게 될 것이다. 베이스(14)와 콜렉터(12) 간의 접합이 역방향으로 바이어스될지라도, 그 위치에서의 전기장은 접합을 가로질러 전자들을 쓸어버릴 것이며, 전자들은 콜렉터(12)에 의해 "콜렉트된다". 이러한 현상은 거의 베이스-이미터 접합에서의 순방향-바이어스 전류( $I_C$ ) 만큼 큰 콜렉터 전류( $I_C$ )를 발생시킨다. 이에 따라, 베이스(14)의 크기가 적절히 정해진다면, 가까운 순방향-바이어스 접합(즉, 베이스-이미터 접합)의 존재로 인하여, 큰 전류가 역방향-바이어스 접합(즉, 베이스-콜렉터 접합) 내에 흐르게 된다. 이러한 현상은 바이폴라 트랜지스터 작동으로 불려진다.

<5> 베이스(14)에 주입된 모든 전자들이 콜렉터(12)에 도달하는 것은 아니다. 일부 전자들은 베이스 영역(14)을 이동할 때 그 내에서 재결합된다. 베이스 영역(14)의 크기가 변하게 되면, 재결합의 양 또한 변하게 되며, 이에 따라 트랜지스터의 "콜렉션 효율"에 영향을 준다는 것은 명백하다. 이미터(16)로부터 베이스(14)로의 정공들의 주입과 함께 재결합 현상은 베이스 전류를 형성한다. 이에 따라, 베이스 영역(14)(그의 도핀트 농도 및 그의 크기)은 하기의 식으로 주어지는 이미터 접지 전류 이득( $\beta$ )에 의해 명백해지는 바와 같이, 바이폴라 트랜지스터(10)의 성능에 중요한 역할을 한다:

$$\beta = I_C / I_B$$

<7>  $I_B$ 가 감소함에 따라, 트랜지스터의 이득은 증가하는데, 이는 (증폭을 위한) 아날로그 형 회로 응용들 및 (스위칭 속도를 위한) 디지털 회로 응용들에 모두 유익하다는 것을 유념하자. 따라서, (트랜지스터의 이득을 개선하기 위해서는) 베이스 영역(14)을 가능한한 얇게 형성하는 것이 바람직하다.

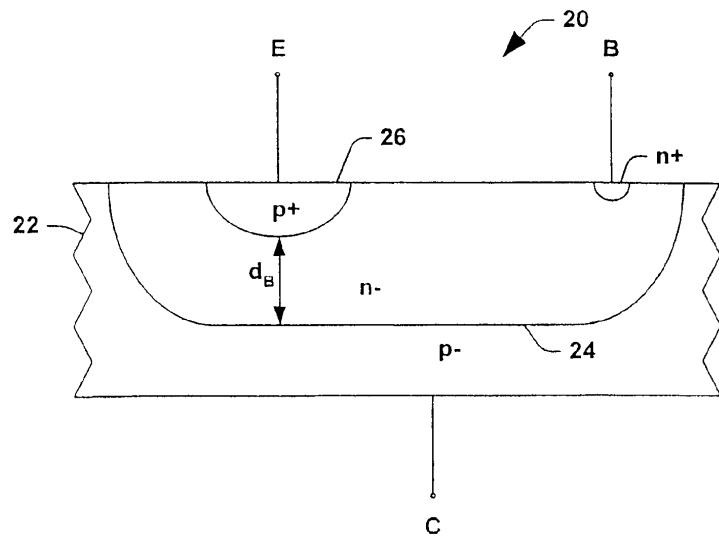

<8> 도 2는 종래 기술의 수직 pnp-형 바이폴라 트랜지스터(20)의 단면도이다. 트랜지스터(20)는, 가령 p-웰 또는 기판과 같은 p-형 콜렉터 영역(22)을 구비하며, 이 p-형 콜렉터 영역(22) 내에는 n-형 베이스 영역(24)이 형성된다. 이후, p-형 이미터 영역(26)이 전형적으로 중착 또는 이온 주입에 의해 베이스 영역(26) 내에 형성된다. (많은 바이폴라 트랜지스터 접적 회로들에 대한 일반적인 구성인) 이러한 수직 구조에서, 베이스의 두께( $d_B$ )는 불리하게는 베이스 영역(24) 및 이미터 영역(26)의 깊이들을 각각 제어하는 능력에 의해 제한된다. 결과적으로, 제어 가능한 높은 트랜지스터 이득을 얻기가 어렵게 된다.

<9> 바이폴라 트랜지스터들의 성능에 영향을 주는 다른 특징은 유효한 베이스 저항이다. 개략적으로, 베이스 저항은 종래 기술을 나타낸 도 3a 및 3b에 도시된다. 베이스 저항( $R_B$ )은 ( $RC$ 가 도시된 바와 같이  $R_B C_B$ 에 대응하는)  $RC$  시상수의 함수로서 트랜지스터의 스위칭 지연을 야기시킨다. 예를 들어, 종래 기술을 나타낸 도 2를 참조하면, 베이스 저항( $R_B$ )은 (그의 도핑 농도의 함수인) n-형 베이스 영역(24)의 저항률 및 콜렉터 영역(22)과 이미터 영역(26) 간의 최소 공간( $d_B$ )과 관련된 영역에 각각 관련된다.

<10> 상기 설명으로부터, 간격( $d_B$ )이 감소할수록(이는 트랜지스터의 이득에는 유리함), 베이스의 저항률은 증가한다 (이는 베이스 저항에 불리하다)는 것이 명백해진다. 결과적으로, 전형적인 바이폴라 트랜지스터 구조들은 종종 트랜지스터 이득과 베이스 저항 간의 설계 성능 조정을 요구한다.

상술된 수직 바이폴라 트랜지스터 구조물에 추가하여, 래터럴 바이폴라 트랜지스터 구조물이 알려졌다. 이러한 래터럴 바이폴라 트랜지스터 구조물은 절연층 위에 놓인 반도체 물질로 형성되고, 따라서 실리콘-온-인셜레이터 (Silicon-On- Insulator: SOI) 디바이스를 구성한다. 이러한 래터럴 바이폴라 트랜지스터들은 종래 MOS 트랜지스터 디바이스들과 여러 면에서 유사하다. 이러한 래터럴 바이폴라 트랜지스터를 개시하는 4개의 문서는 하기와 같다.

샤하디 지 지(SAHIDI G G) 등: 'SOI에서의 신규한 고성능 래터럴 바이폴라', 국제 전자 디바이스 회의의 회보, 미국 뉴욕, IEEE 제8권 1991년 12월(1991-12-08), 91-663-666, XP00034211 ISBN: 0-7803-0243-5는 트랜지스터 구조물을 개시하고, 이 구조물에서 상기 반도체 물질은 각각 n+-형 이미터 영역과, p-형 베이스 영역과, n--형

콜렉터 영역과 n+-형 콜렉터 영역을 형성하는 4개의 래터럴 인접 부분들로 분리된다. 산화층이 상기 n- 콜렉터 영역 위에 놓인다. P++ 폴리층이 상기 산화층 위에 놓이고, 상기 산화층의 일면 아래로 확장하여 상기 베이스 영역에 접촉한다. 상기 폴리층의 면들의 유전 스페이서들이 상기 이미터-베이스 접합 및 상기 n+ 콜렉터 영역의 부분을 덮는다.

일본 특허 초록, 제014권 제139호(E-0903), 1990년 3월 15일(1990-03-15), JP 02 003238 A(니산 모터 코.엘티디), 1990년 1월 8일(1990-01-08)은 트랜지스터 구조물을 개시하고, 상기 구조물에서 반도체 물질이 각각 P+-형 이미터 영역과, n-형 베이스 영역과, p--형 콜렉터 영역과 p+-형 콜렉터 영역을 형성하는 4개의 인접한 부분들로 분리된다. 단일 산화층이 상기 반도체 물질 상에 놓이고, 상기 베이스 영역으로 확장하는 베이스 콘택트 정공과, 상기 p+ 이미터와 콜렉터 영역들과 접촉하는 추가적인 정공들을 구비한다.

EP-A-0.616.370은 한 쌍의 npn 트랜지스터를 위한 구조물을 개시하고, 상기 구조물에서, 상기 반도체 물질은 제 1 트랜지스터의 각각 n+-형 이미터 영역과, 제 1 트랜지스터의 p-형 베이스 영역과, 제 1 트랜지스터의 n--형 콜렉터 영역과, 제 1 트랜지스터의 콜렉터 영역과, 제 2 트랜지스터의 이미터 영역을 모두 형성하는 공통 n+-형 영역과, 제 2 트랜지스터의 p-형 베이스 영역과, 제 2 트랜지스터의 n--형 콜렉터 영역과, 제 2 트랜지스터의 n+-형 콜렉터 영역을 형성하는 7개의 래터럴 인접 부분들로 분리된다. 단일 산화막이 상기 쌍의 트랜지스터의 반도체 물질 상에 놓인다. 각 트랜지스터에 있어서, 산화층 상의 p-형 폴리층은 상기 베이스 영역과 n--형 콜렉터 영역 상에 놓이고, 상기 산화층 내의 정공을 통하여 확장하여 상기 베이스 영역에 접촉한다. 2개의 추가적인 정공들이 제 1 트랜지스터의 이미터 영역과 제 2 트랜지스터의 n+-형 콜렉터 영역과의 각각의 접촉을 위해 산화층 내에 제공된다.

일본 특허 초록, 제016권, 제367(E-1245), 1992년 8월 7일(1992-08-07) 및 JP 04 116935 A(후지쯔 엘티디), 1992년 4월 17일(1992-04-17)은 트랜지스터 구조물을 개시하고, 상기 구조물에서 반도체 물질은 각각 n+-형 콜렉터 영역과, n-형 콜렉터 영역과, p+-형 베이스 영역과, n-형 이미터 영역과, n+-형 이미터 영역을 형성하는 5개의 래터럴 인접 부분들로 분리된다. 산화층은 2개의 n-형 영역들 위에 놓이고, 상기 베이스 영역으로 확장하는 정공을 구비한다. 폴리층은 상기 산화층 위에 놓이고 상기 정공을 통하여 확장하여 상기 베이스 영역에 접촉한다.

### 발명의 상세한 설명

- <11> 래터럴 바이폴라 트랜지스터를 개시하는 상술된 4개의 문서들 중의 마지막 문서(후지쯔 문서)는 본 발명에 가장 근접한 종래 기술로 고려되고, 상기 문서는 하기의 기술적 특징들의 조합을 개시한다:

- <12> 전기적인 절연 물질 상에 반도체층 및;

- <13> 상기 반도체층의 중앙 부분 상에 절연층을 구비하고, 그 내부에 콘택트 정공이 있고, 상기 절연층 상에 도전 물질이 있고, 상기 도전 물질은 상기 콘택트 정공을 통하여 상기 반도체층과 전기적 접촉을 하고, 그럼으로써 베이스 콘택트를 형성한다.

- <14> 본 발명에 따라, 래터럴 바이폴라 트랜지스터는 하기의 기술적 특징들을 구비한다:

- <15> 상기 절연 영역과 그 위의 베이스 콘택트가 상기 반도체를 3개의 인접한 부분들로 분리하고, 상기 3개의 인접한 부분들 중의 중간 부분은 상기 트랜지스터의 베이스 영역을 형성하고 제 1 도전형을 구비한 상기 중앙 부분이고, 상기 3개의 인접한 부분들 중의 다른 하나는 제 2 도전형이고 콜렉터 영역을 형성하고, 상기 3개의 인접한 부분들 중의 다른 하나는 제 2 도전형을 구비하고 이미터 영역을 형성한다.

- <16> 따라서, 본 발명의 트랜지스터에서, 상기 베이스 두께는 상기 절연 영역과 그 위의 베이스 콘택트의 래터럴 확장부에 대응하고, 상기 콘택트 정공의 래터럴 확장부에 대응하지 않는다. 장점으로, 상기 베이스 콘택트의 래터럴 확장부를 변화시킴으로써, 설계자는 조절된 반복가능한 방법으로 얇은 베이스 영역을 구비한 용이하게 변경할 수 있고 큰 트랜지스터 이득을 지닌 트랜지스터를 제조할 수 있다. 상기 래터럴 바이폴라 트랜지스터가 종래의 MOS-형 트랜지스터와 여러 면들에서 유사하기 때문에, 상기 베이스 두께는 MOS 트랜지스터에서의 채널 길이와 유사하다.

또한, 본 발명의 래터럴 바이폴라 트랜지스터는 상기 트랜지스터 베이스 저항을 부정적으로 증가시킴없이, 큰 트랜지스터 이득을 제공한다. 상기 베이스 콘택트가 상기 MOS-형 게이트 산화물과 유사한 절연 영역을 통하여 상기 베이스 영역에 접촉하기 때문에, 상기 트랜지스터는 충분한 길이의 상기 트랜지스터 "폭"으로 확장함으로써 상기 트랜지스터 베이스 저항을 허용가능한 레벨로 감소시킨다. 즉, 상기 래터럴 바이폴라 트랜지스터는 상

기 베이스 두께 크기에 수직인 제 2 차원으로 확장할 수 있기에, 상기 콜렉터와 이미터 영역들 사이의 베이스 영역의 면적을 증가시킨다.

본 발명에 따른 상기 래터럴 바이폴라 트랜지스터는 하기의 단계를 포함하는 방법에 의해 제조된다:

- (a) 제 1 도전형을 구비한 반도체층의 물질로, 상기 전기적인 절연 물질 상에 상기 반도체층을 형성하는 단계와;

- (b) 상기 반도체층 상에 상기 절연 영역을 포함한 절연층을 형성하는 단계와;

- (c) 상기 절연 영역 내에 상기 콘택트 정공을 형성하는 단계와;

- (d) 상기 베이스 콘택트를 형성하는 단계 및;

- (e) 상기 베이스 콘택트에 대한 자기-정렬에 의해 상기 콜렉터 영역과 이미터 영역을 형성하는 단계를 포함함으로써 상기 콜렉터 및 이미터 영역들 사이에 및 근처에 상기 베이스 영역을 형성한다.

따라서, 상기 콜렉터와 이미터 영역들을 자기-정렬하기 위해 상대적으로 염중하게 제어될 수 있는 상기 베이스 콘택트의 사용에 의해, 상기 베이스 두께는 염중하게 제어될 수 있다.

상술된 목적들과 이와 관련된 목적들을 성취하기 위해, 본 발명은 청구범위에 충분히 개시되고 지적된 특징들을 포함한다. 하기의 설명과 첨부된 도면은 본 발명의 특정의 설명적인 실시예들을 상세하게 개시한다. 이러한 실시예들은 본 발명의 원리들이 채용되는 다양한 방법들 중의 일부를 나타낼 뿐이다. 본 발명의 다른 목적들, 장점들 및 신규한 특징들은 하기의 도면들과 관련되어 고려될 때 본 발명의 하기의 상세한 설명으로부터 명확해질 것이다.

### 실시예

&lt;30&gt;

본 발명은 MOS-형 트랜지스터 구조물과 일부 유사점을 지닌 래터럴 바이폴라 트랜지스터 구조물과 그 제조 방법에 관한 것이다. 본 발명의 래터럴 바이폴라 트랜지스터는 이러한 유사점을 공유하고, 종래 MOS-형 트랜지스터의 간략한 설명이 종래 기술의 문제점을 충분히 이해하고, 본 발명이 이러한 문제점을 해결하는 방법을 충분히 이해하기 위해 제공된다.

&lt;31&gt;

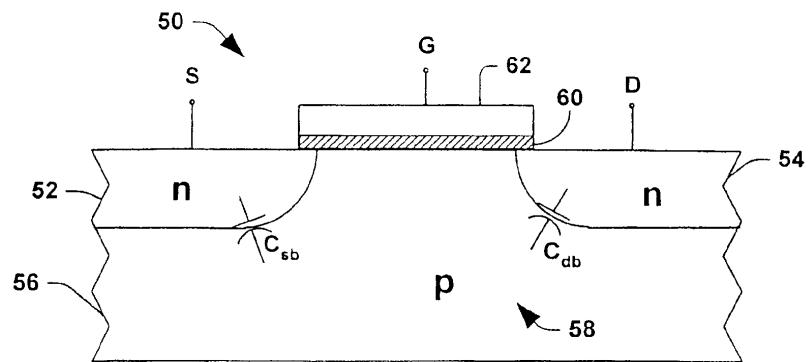

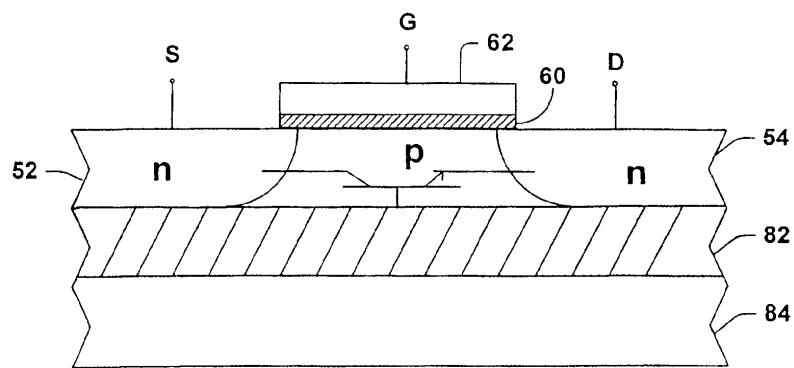

종래 개량형 MOS 트랜지스터가 도 4에 도시되고, 참조번호 50으로 지적된다. 상기 MOS 트랜지스터(50)는 n-채널 트랜지스터이고, n-형 소스와 드레인 영역들(52), (54)를 p-형 보디(body)(56) 내에 구비하고, 상기 보디는 벌크 기판일 수 있다. 상기 소스 및 드레인 영역들(52), (54) 사이의 영역(58)은 채널 영역이고, 이 영역 상에 게이트 산화막(60)과 제어 게이트 전극(62)이 형성되고, 때로는 불순물 폴리실리콘으로 형성된다. 0 볼트가 상기 게이트 전극(62)에 인가된 때, 상기 소스(52)로부터 상기 드레인(54)으로의 전기적 경로는 2개의 백-투-백(back-to-back) 다이오드의 직렬 연결로 이루어지고, 그 사이의 어떠한 전류 흐름도 방지한다. 상기 게이트 전극(62)에 포지티브 전압을 인가함으로써, 상기 보디(56) 내의 전자들은 상기 게이트 산화막(60) 밑의 상기 채널 영역(58)으로 유인됨으로써 상기 소스(52)와 드레인(54) 사이에 채널을 형성한다. 상기 게이트 전압이 임계 전압(V<sub>t</sub>)에 도달하면, 상기 채널은 충분히 형성되고, 상기 MOS 트랜지스터(50)는 도전성을 띤다.

&lt;32&gt;

상기 MOS 트랜지스터(50)는 상기 게이트 전극(62)에 다른 전압값들을 인가함으로써 스위치로서 일반적으로 사용된다. 상기 MOS 트랜지스터(50)의 스위칭 속도가 적어도 일면으로 상기 MOS 트랜지스터(50)를 채용하는 회로들이 어떤 속도로 동작하는가를 나타내기 때문에 매우 중요한 특성이다. 현재, 트랜지스터의 스위칭 속도는 상기 채널 전이 시간(channel transit time)(즉, 상기 채널을 통하여 전송되는 전하에 요구되는 시간)에 의해 제한되지 않는다; 대신에 상기 스위칭 속도는 상기 디바이스 전극들 사이에 또한 상호연결 도전선과 보디 사이에 존재하는 캐패시턴스들을 충전하고 방전하는데 요구되는 시간에 의해 제한된다.

&lt;33&gt;

상기 트랜지스터의 캐패시턴스를 인식하는 하나의 방법은 종래 기술 도 4에서 도시된 예시적인 단면도를 통해서이다. 종래 기술 도 4에 나타난 바와 같이, 캐패시턴스는 다양한 디바이스 전극들(도시되지 않음) 사이에, 또한 상기 전극들과 상기 보디 영역 사이에 존재한다. 상기 드레인-대-보디 캐패시턴스(C<sub>db</sub>)와 소스-대-보디 캐패시턴스(C<sub>sb</sub>)가 종래 기술 도 4에 나타나고, 종종 접합 캐패시턴스로 언급된다. 상기 접합 캐패시턴스의 값은 각각 상기 영역들의 도핑 농도뿐만 아니라, 상기 결합의 단면 영역의 함수이다.

&lt;34&gt;

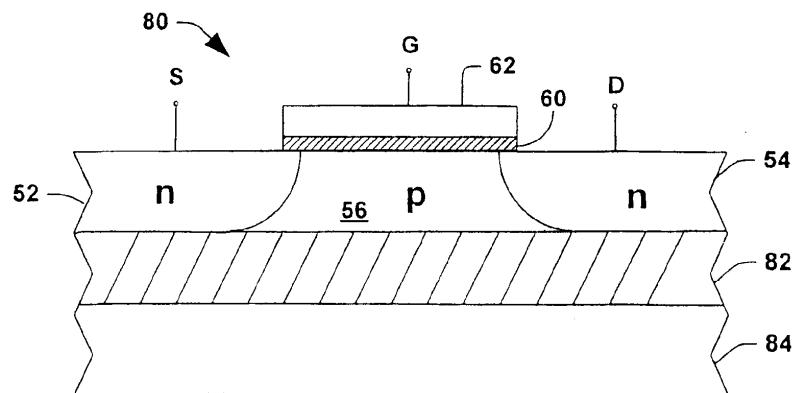

종래 기술 도 4의 상기 MOS 트랜지스터(50)의 성능을 향상시키는 방법은 상기 트랜지스터를 절연 영역 상에 형성함으로써 상기 결합 캐패시턴스를 감소시키는 것이다. 이러한 트랜지스터 디바이스 구조물은 실리콘-온-인슐레이터(silicon-on-insulator: SOI) 디바이스로 불리고, 종래 기술 도 5에 도시된다. 상기 SOI MOS 트랜지스터

(80)는 종래 기술 도 4의 상기 트랜지스터(50)와 유사한 구성소자들을 구비한다. 상기 SOI 트랜지스터(80)에서, 상기 보디(56)는 도 4에서와 같이, 벌크 반도체 물질로 형성되지 않고, 실리콘 디옥사이드(SiO<sub>2</sub>)와 같은 절연층(82) 위에 놓인다. 상기 절연층(82)은 벌크 반도체 물질 또는 기판(84) 위에 놓인다.

<35> 상기 SOI 트랜지스터(80)는 종래의 벌크 트랜지스터 디바이스 상에 여러 성능상의 잇점을 제공한다. 먼저, 각 디바이스가 다른 디바이스로부터 완벽하게 절연되기 (공통 보디를 공유하는 것에 반하여) 때문에, 보다 나은 개별 디바이스 절연이 성취되어, 회로 래치-업 조건들을 방지한다. 또한, 상기 소스 영역(52)과 드레인 영역(54)의 적어도 일부분이 상기 절연층(82)에 인접하기 때문에, 상기 소스/보디 및 드레인/보디 인터페이스들의 단면 영역이 감소되고, 그럼으로써 상기 접합 캐패시턴스가 현저하게 감소된다.

<36> 비록 SOI MOS 디바이스들(80)이 종래 MOS 벌크형 디바이스(50)에 대하여 여러 잇점을 제공할지라도, SOI 트랜지스터는 또한 여러 단점을 지닌다. SOI 트랜지스터들의 일 단점은 (상기 출원에 의존하여) 벌크 실리콘 또는 상기 트랜지스터로의 보디 콘택트의 부족일 것이다. 일부의 경우, 상기 SOI 보디 영역(56)을 고정된 전위에 연결하여, "부동 보디 효과(floating body effects)"를 회피하도록 하는 것이 바람직하다. 각 트랜지스터 디바이스에 대한 보디 콘택트의 사용은 바람직하지 않게, 상기 디바이스의 크기를 증가시키고, 그럼으로써 적절한 방법이 아니다.

<37> SOI 트랜지스터의 부동 보디 효과들은 접지에 상대적으로 부동적으로 되는 보디(56)와 관련된 다양한 히스테리시스 효과에 관련된다. 2개의 이러한 부동 보디 효과들은 "킹크(kink)" 효과와 기생 래터럴 바이폴라 효과를 포함한다. 상기 "킹크" 효과는 충격 이온화로부터 유래한다. 상기 SOI 트랜지스터(80)가 상대적으로 높은 드레인-대-소스 전압에서 동작할 때, 충분한 운동 에너지를 지닌 채널 전자들은 격자와의 이온화 충돌을 야기하여, 상기 채널(58)의 드레인 단부 근처에 캐리어를 증가시킨다. 생성된 정공들은 상기 디바이스(80)의 보디(56)에서 쌓여서, 상기 보디 전위를 증가시킨다. 상기 증가된 보디 전위는 상기 트랜지스터(80)의 임계 전압을 감소시키고, 따라서 상기 트랜지스터 전류를 증가시키며, 상기 트랜지스터 전류/전압(I/V) 곡선에서 "킹크"를 야기한다.

<38> 제 2의 부동 보디 효과는 상기 기생 래터럴 바이폴라 효과를 포함한다. 상술된 바와 같이, 만약 충격 이온화가 많은 수의 정공들을 생성하면, 상기 보디 바이어스는 충분한 전압으로 증가되어, 상기 소스/보디 p-n 결합인 순방향으로 바이어스된다. 상기 결합이 순방향 바이어스되는 때, 소수 캐리어들이 상기 보디(120)로 방출되어 기생 래터럴 npn 바이폴라 트랜지스터가 턴온되도록 한다. 이러한 기생 바이폴라 트랜지스터 동작은 상기 트랜지스터 전류의 게이트 제어의 손실을 야기하고, 따라서 MOS 트랜지스터 응용에서 매우 바람직하지 않다.

<39> 과거에는, 상기 SOI MOS 트랜지스터(80)의 성능에서, 상기 기생 바이폴라 효과의 충격을 감소시키거나 제거하려는 단계들이 수행되었다. 예를 들면, 미국 특허 제5,420,055호에 개시된 일 방법은 전자들과 정공들이 재결합할 수 있는 상대적으로 고농도의 재결합 센터들을 형성하기 위해, 상기 p-n결합 근처에 물질이 주입되는 주입 단계를 부가한다. 이러한 재결합 센터들은 전자 트랩들 또는 결정 구조 결합을 야기한다. 이러한 디바이스의 구성은 상기 보디 영역(56) 내에 흄들의 적층을 방지하기 위한 것이고, 따라서 상기 기생 바이폴라 트랜지스터가 "작동하거나 (triggering)" 턴온되지 않도록 한다. 미국 특허 제5,315,144호에 개시된 다른 종래 방법에서, 상기 기생 래터럴 바이폴라 트랜지스터의 이득이 상기 소스 및 드레인 영역들의 도핑 농도들을 각각 실질적으로 감소시킴으로써 감소된다. 상기 경우들 중의 하나에서, 상기 SOI MOS 디바이스(80)의 기생 래터럴 바이폴라 트랜지스터는 제한되어야하거나 제거되어야 할 문제로서 나타난다.

<40> 본 발명에 따라서, 상기 MOS SOI 트랜지스터 디바이스에서 상기 기생 래터럴 바이폴라 트랜지스터를 제거하는 대신에, 이러한 MOS-형 구조물에서의 상기 래터럴 바이폴라 트랜지스터 특성들이 개발되어 종래 바이폴라 트랜지스터 구조물에서 유래한 성능 설계 드레이드-오프의 일부들을 극복하는 고성능 바이폴라 디바이스를 만드는데 사용된다. 특히, 본 발명은 상기 트랜지스터 베이스 저항을 부정적으로 증가시킴없이, 재생산 가능한 방법으로 큰 트랜지스터 이득을 제공할 수 있는 바이폴라 트랜지스터 구조물에 관한 것이다.

<41> 본 발명은 상기 게이트 산화물이 베이스 콘택트 정공을 구비하고, 상기 게이트 전극이 상기 베이스 콘택트 정공을 통하여 그 밑에서 상기 베이스 영역을 전기적으로 접촉하는 베이스 콘택트로서 작동하는 점을 제외하고, 종래의 MOS-형 SOI 트랜지스터와 적어도 일특징에서 유사한 래터럴 바이폴라 SOI 트랜지스터에 관한 것이다. 상기 베이스 콘택트는 콜렉터와 이미터 영역들을 자기-정렬하는데 사용되고, 따라서, 상기 베이스의 두께는 상기 베이스 콘택트 형상 크기에 의해 잘 제어되고 조절된다. 또한, 상기 베이스 콘택트는 상기 트랜지스터의 충분한 "폭"을 따라 확장하고, 따라서 증가된 베이스 저항없이, 높은 트랜지스터 이득을 제공하고, 그럼으로써 종래 바이폴라 트랜지스터 구조물에서의 이제까지의 이득/베이스 저항 성능 트레이드-오프를 극복할 수 있다.

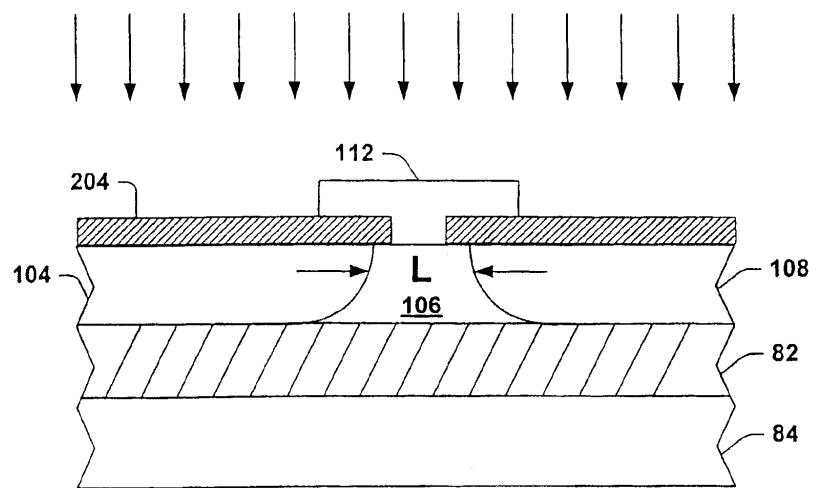

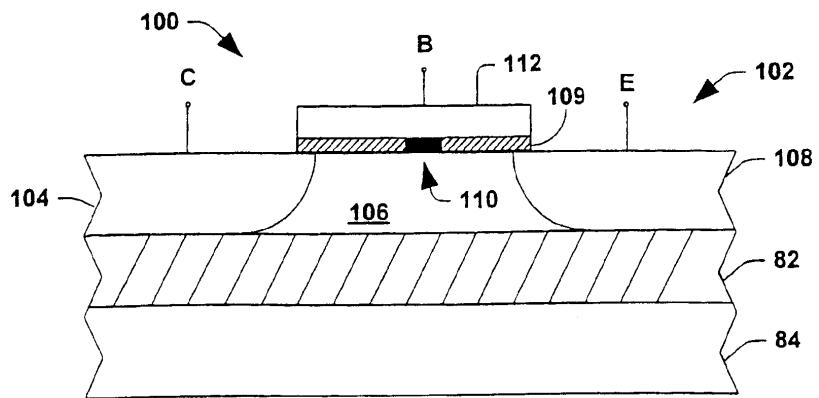

- <42> 도 7은 본 발명에 따른 래터럴 바이폴라 트랜지스터(100)의 부분 단면도이다. 상기 바이폴라 트랜지스터(100)는 벌크 기판(84) 상에 놓인 절연층(82)을 구비한 SOI 디바이스이다. 반도체층(102)이 상기 절연층(82) 상에 놓이고, 서로서로 인접한 3개의 개별 부분들을 구비한다. 이러한 부분들은 각각 콜렉터 영역(104)과, 베이스 영역(106) 및 이미터 영역(108)이다. 절연 영역(109)은 상기 반도체층(102) 상에 놓이고, 상기 베이스 영역(106)과 전기적 접촉을 하는 도전 부분(110)을 구비한다. 도전 베이스 콘택트(112)는 상기 절연 영역(108) 위에 놓이고, 상기 도전 부분(110)을 통하여 상기 베이스 영역(106)에 연결된다.

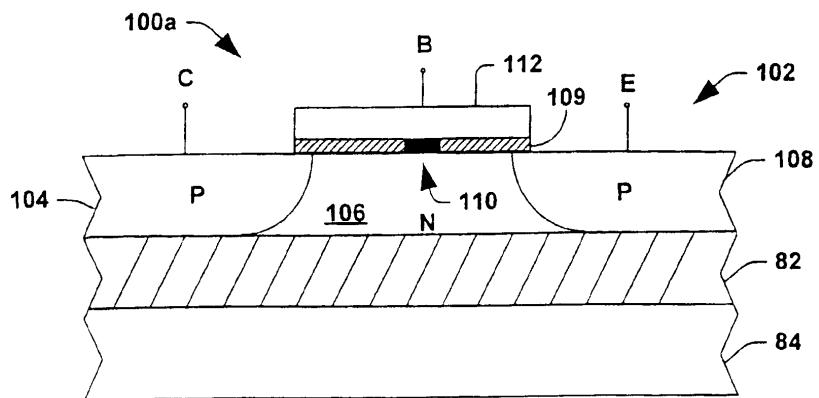

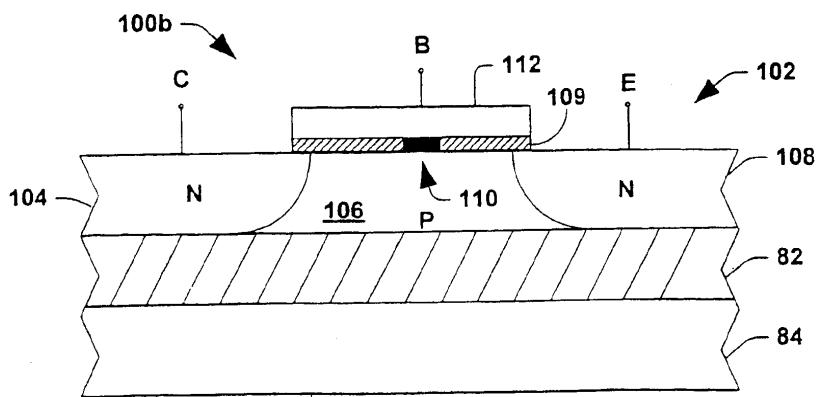

- <43> 본 발명에 따라, 상기 트랜지스터(100)는 도 8a 및 8b에 각각 도시된 바와 같이, pnp 래터럴 바이폴라 트랜지스터(100a)이거나 npn 래터럴 바이폴라 트랜지스터(100b)일 것이다. 각 경우에, 상기 콜렉터와 이미터 영역들(104), (108)은 제 1 도전형이고, 상기 베이스 영역(106)은 제 2의 다른 도전형이다.

- <44> 도 7에서, 상기 콜렉터 및 이미터 영역들(104), (108)은 상기 베이스 영역(106)에 인접하고, 그럼으로써 상기 트랜지스터(100)를 래터럴 트랜지스터 구조물로 형성한다. 바람직하게는, 상기 콜렉터와 이미터 영역들(104), (108)은 상기 베이스 콘택트(112)에 대하여 자기-정렬된다. 이러한 예에서, 상기 베이스 콘택트(112)는 예를 들면 상기 콜렉터와 이미터 영역들(104), (108)의 형성 이전에 중착과 식각을 통하여 한정된다. 상기 콜렉터와 이미터 영역들(104), (108)의 형성은 그 사이의 거리를 한정하는 상기 베이스 콘택트(112)를 사용하고, 또한 (종래의 MOS 트랜지스터 구조물의 채널 길이와 유사한) 상기 바이폴라 트랜지스터(100)의 베이스 두께 또는 "길이"를 한정한다. 상술된 바와 같이, 상기 베이스 두께는 상기 트랜지스터의 이득을 결정하는 중요한 인자이다. 따라서, 본 발명의 상기 바이폴라 트랜지스터의 구조물은 종래의 수직 바이폴라 디바이스에서와 같이 결합 깊이에 의존하지 않는 잘 제어된 베이스 두께를 가능하게 한다. 또한, 본 발명의 상기 베이스 두께는 상기 베이스 콘택트(112) 형상 크기와 같이 작게 형성될 수 있다. 리소그래피 기술이 향상됨에 따라, 상기 베이스 콘택트(112)가 지속적으로 감소됨에 따라, 상기 베이스 두께가 조절된 방법으로 지속적으로 감소된다.

- <45> 도 9는 본 발명의 다른 특징에 따른 래터럴 바이폴라 트랜지스터(100)의 사시도이다. 상술된 바와 같이, 종래의 바이폴라 트랜지스터 구조물의 일 단점은 트랜지스터 이득과 트랜지스터 베이스 저항 사이의 성능 트레이드-오프이었다. 특히, 상기 트랜지스터 이득을 증가시키기 위해 종래 구조물에서 상기 베이스 두께가 감소되었기 때문에, 상기 감소된 베이스 두께는 상기 트랜지스터 베이스 저항을 증가시킨다. 도 9의 사시도는 본 발명의 상기 바이폴라 트랜지스터 구조물(100)이 종래 구조물에 유래한 설계 트레이드-오프를 극복하는 방법을 제시한다.

- <46> 도 9에서 도시된 바와 같이, 상기 베이스 콘택트(112)는 원하는 정도로 "X"방향으로 확장되도록 형성된다. "X" 방향의 상기 베이스 콘택트(112)의 확장은 종래 MOS-형 트랜지스터의 "폭"과 유사하고, 따라서 그 특징은 상기 베이스 콘택트 폭(W)으로 지시된다. 상기 베이스 콘택트 폭(W)을 더 긴 크기로 확장함에 의해, 상기 활동 콜렉터 영역(104)과 이미터 영역(108) 사이의 전체 영역이 증가되고 반면에 상기 베이스 저항을 감소시킨다. 상기 트랜지스터(100)가 어떠한 크기의 폭(W)로 형성될 수 있기 때문에, 상기 베이스 저항은 원하다면 성능의 레벨들을 변화시키기 위해 맞추어질 수 있다.

- <47> 상기 베이스 저항은 상기 베이스 직렬 저항과 상기 베이스-확장(spreading) 저항으로 이루어진 다소 복잡한 파라미터이다. 종래의 수직 디바이스에서의 베이스 직렬 저항은 상기 베이스 콘택트와 상기 이미터 영역의 에지 사이의 저항 경로와 관련되고, 반면에 상기 베이스-확장 저항은 상기 이미터 영역의 에지와, 도전 동안에 전류가 실제적으로 흐르는 베이스 영역의 활성 부분 사이의 저항이다. 결과적으로, 상기 베이스-확장 저항의 2차원 (X-Y) 효과들이 중요하다. 실질적인 트랜지스터 폭(W)을 구비함으로써, 상기 전류는 어느 한 점에서의 전류 밀도를 감소시키는 "넓은(wide)" 이미터를 따라 분포된다. 명확하게, 본 발명의 래터럴 바이폴라 트랜지스터(100)는 상기 트랜지스터 베이스-확장 저항을 독립적으로 고칠 때(따라서 전체 베이스 저항에 대한 중요한 영향) 트랜지스터 이득의 유동성을 가능하게 한다.

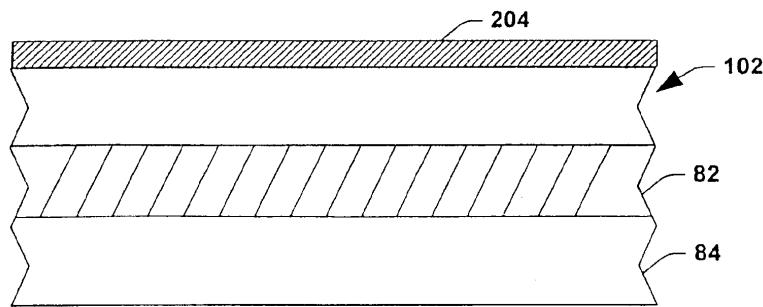

- <48> 도 7의 상기 래터럴 바이폴라 트랜지스터(100)의 방법(200)이 도 10과 11a 및 11d에 도시된다. 상기 방법(200)은 도 11a에 도시된 바와 같이, SOI 물질의 표면 상에 절연층(204)을 형성하는 단계(202)로 개시한다. 이러한 SOI 물질은 예를 들면, 중착 또는 깊은 주입을 통하여 그 위에 형성된 절연층(82)을 구비한 실리콘 기판(84)일 것이다. 중착의 경우, 다른 반도체층(102)이 예를 들면 중착을 통하여 그 위에 형성된다. 또는, 만약 상기 절연층(82)이 깊은 주입에 의해 형성되면, 그 위의 상기 층(102)은 상기 기판 벌크 물질의 상측 부분이다. 바람직하게는, 상기 반도체층(102) 상에 형성된 절연층(204)은 실리콘 디옥사이드이고, 화로에서의 산화물 성장을 통하여 형성되고, 실질적으로 두께가 변화한다. 또한, 실리콘 니트라이드와 같은 다른 절연 물질들과, 예를 들면 중착과 같은 다른 형성 방법이 사용될 수 있고 본 발명의 범위 내에서 고안된다.

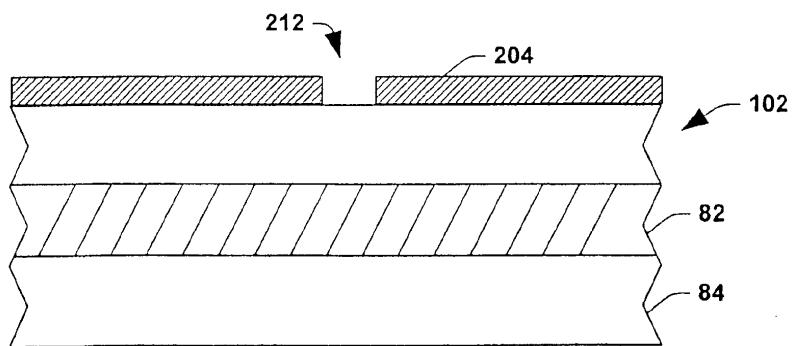

- <49> 상기 방법(200)은 도 11b에 도시된 바와 같이, 상기 절연층(204)에 베이스 콘택트 정공(212)을 형성하는 단계

(210)으로 진행한다. 상기 베이스 콘택트 정공(212)은 바람직하게는 식각에 의해 형성되나, 상기 정공(210)에 대응하는 절연층(204)의 부분을 선택적으로 제거하는 모든 방법이 사용되고 본 발명 내에서 고안된다. 바람직하게는, 일반적인 등방성 식각이 상기 트랜지스터 형성 프로세스에서 나중의 좋은 단계 허용범위(step coverage)를 가능하게 하기 위해 상기 정공(212)에 상기 절연층(204) 내의 비-수직 측벽들을 제공하는데 사용된다. 또는, 상기 베이스 콘택트 정공(212)의 크기와 상기 절연층의 깊이에 의존하여, 상기 정공(212)내의 나쁜 단계 허용범위가 이득이 아니고, 비등방성 식각이 사용된다.

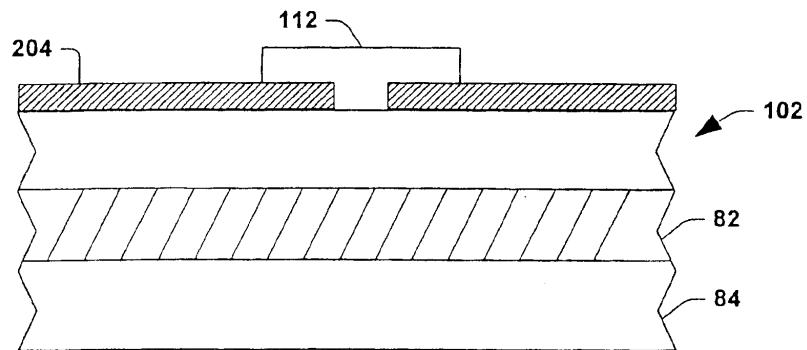

<50> 도전막은 예컨데 기상 증착 또는 스퍼터링에 의해 상기 절연층(204) 위에 증착된다. 상기 도전막은 불순물 폴리실리콘 또는 예를 들면 알루미늄과 같은 금속이다. 모든 도전 물질이 사용될 수 있고, 본 발명에서 고안된다. 단계 220에서, 상기 도전막은 예를 들면 식각에 의해 상기 베이스 콘택트(112)를 한정하기 위해 패터닝된다. 바람직하게는, 상기 베이스 콘택트(112)의 두께 또는 "길이"는 소정의 트랜지스터 이득에 의존할 것이다. 즉, 상대적으로 적은 트랜지스터 이득에 있어서, 상기 베이스 콘택트는 상대적으로 넓게 패턴되고, 반면에 상대적으로 큰 트랜지스터 이득에 있어서는 상기 베이스 콘택트(112)가 상술된 바와 같이, 얇게 패턴된다. 또한, 상기 베이스 콘택트(112)의 폭은 소정의 베이스 저항을 기준으로 하여 형성된다. 즉, 높은 베이스 저항에 있어서, 상기 폭(W)은 상대적으로 작고, 반면에 더 작은 베이스 저항에 있어서는 상기 폭(W)은 상대적으로 크다.

<51> 후속하여, 상기 방법(200)은 상기 콜렉터, 베이스 및 이미터 영역들이 각각 한정되는 단계(230)으로 진행한다. 바람직하게, 상기 반도체층(102)은 단계(202) 이전에 하나의 도전형으로 도핑된다; 이때 단계(230)는 예를 들면 이온 주입과 같은 단일 형성 단계를 사용하여 영역(104), (106), (108)을 형성하는 단계를 포함한다. 이러한 경우, 상기 주입 단계(230)는 상기 반도체층(102)의 도전형과는 다른 도전형이다. 이러한 방법으로, 상기 콜렉터 영역(104)와 이미터 영역(108)은 상기 베이스 콘택트(112)에 관해서 자기-정렬된다. 또한, 상기 형성 단계(230)는 도 11d에 도시된 바와 같이, 베이스 두께(L)을 한정한다.

<52> 상기 콜렉터, 베이스 및 이미터 영역들(104), (106), (108)의 형성 이후, 상기 노출된 절연층(204)의 부분들은 제거되어 도 7의 절연층(109)를 형성한다. 비록 도 11d가 상기 절연층(204)를 통하여 야기하는 단계(230)를 개시하지만, 상기 층(204)의 노출된 부분들이 제거되고, 이때 주입이 발생할 수 있다.

<53> 비록 본 발명이 특정의 바람직한 실시예 또는 실시예들과 관련하여 개시되고 설명되지만, 균등한 변형들과 변경들이 상기 명세서와 첨부된 도면을 판독하고 이해한 때 종래 기술에 익숙한 사람에 의해 이루어질 것이다. 상술된 구성요소들(조합체, 디바이스, 회로 등)에 의해 수행된 다양한 기능들에 관하여서는, 이러한 구성소자들을 설명하기 위해 사용된 그 용어("수단"으로 참조되는 것을 포함하여)는 비록 본 발명의 실시예에서 그 기능을 수행하는 개시된 구조물에 구조적으로 균등하지는 않을지라도, 개시된 구성소자의 특정 기능을 수행하는 모든 구성소자(즉, 기능적으로 균등한)에 대응하는 것이다. 또한, 본 발명의 특정한 특징이 여러 실시예들 중의 오직 하나에 관하여 개시되어도, 이러한 특징은 소정의 또는 특정 응용에 있어서 바람직하고 이로운 것과 같이, 다른 실시예들의 하나 또는 그 이상의 특징들과 결합될 것이다.

### 도면의 간단한 설명

- <17> 도 1a는 종래 기술의 바이폴라 트랜지스터 디바이스의 단순화된 1-차원 단면도이다.

- <18> 도 1b는 도 1a의 바이폴라 트랜지스터를 도시한 개략도이다.

- <19> 도 2는 일반적인 수직 바이폴라 트랜지스터 디바이스 단면도 및 바이폴라 트랜지스터의 이득에 관련된 베이스의 두께( $d_B$ ) 제어의 어려움을 도시한다.

- <20> 도 3a 및 3b는 종래의 npn 및 pnp 바이폴라 트랜지스터들, 및 베이스 저항이 바이폴라 트랜지스터 디바이스의 성능에 영향을 주는 방식을 설명하기 위하여 결합된 베이스 저항 및 베이스 캐패시턴스를 도시한다.

- <21> 도 4는 종래의 MOS 트랜지스터 구조 및 이에 결합된 실질적인 접합 캐패시턴스를 도시한 단면도이다.

- <22> 도 5는 종래의 MOS SOI 트랜지스터의 단면도이다.

- <23> 도 6은 보디(body) 영역이 플로팅될 수 있을 때 종래의 MOS SOI 트랜지스터 구조 내에서 턴온될 수 있는 기생적인 래터럴 바이폴라 트랜지스터를 도시한 단면도이다.

- <24> 도 7은 본 발명에 따른 래터럴 바이폴라 트랜지스터의 단면도이다.

- <25> 도 8a는 본 발명에 따른 pnp-형 래터럴 바이폴라 트랜지스터의 단면도이다.

- <26> 도 8b는 본 발명에 따른 npn-형 래터럴 바이폴라 트랜지스터의 단면도이다.

- <27> 도 9는 본 발명에 따른 래터럴 바이폴라 트랜지스터의 부분적인 투시도로서, 여기서 베이스 콘택트는 실질적으로 바이폴라 트랜지스터의 전체 폭을 따라 연장되며, 이로써 베이스 저항이 감소하게 된다.

- <28> 도 10은 본 발명에 따른 래터럴 바이폴라 트랜지스터 형성 방법을 도시한 흐름도이다.

- <29> 도 11a-11d는 본 발명의 예시적인 실시예에 따라 래터럴 바이폴라 트랜지스터를 형성하는 단계들을 도시한 단면도들이다.

## 도면

도면1a

도면1b

도면2

도면3a

도면3b

## 도면4

## 도면5

## 도면6

도면7

도면8a

도면8b

도면9

도면10

도면11a

도면11b

도면11c

도면11d