(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3804972号

(P3804972)

(45) 発行日 平成18年8月2日(2006.8.2)

(24) 登録日 平成18年5月19日(2006.5.19)

(51) Int.C1.

F 1

HO1L 27/108 (2006.01)

HO1L 27/10 651

HO1L 21/8242 (2006.01)

HO1L 27/10 444C

HO1L 27/105 (2006.01)

HO1L 21/8246 (2006.01)

請求項の数 10 (全 9 頁)

(21) 出願番号 特願平8-511563

(86) (22) 出願日 平成7年9月26日(1995.9.26)

(65) 公表番号 特表平9-507342

(43) 公表日 平成9年7月22日(1997.7.22)

(86) 国際出願番号 PCT/IB1995/000799

(87) 国際公開番号 WO1996/010845

(87) 国際公開日 平成8年4月11日(1996.4.11)

審査請求日 平成14年9月24日(2002.9.24)

(31) 優先権主張番号 94202867.1

(32) 優先日 平成6年10月4日(1994.10.4)

(33) 優先権主張国 オーストリア(AT)

(73) 特許権者

コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ

オランダ国 5621 ベーアー アインドーフェン フルーネヴアウツウェッハ

1

(74) 代理人

弁理士 杉村 興作

(72) 発明者 ヴォルテルス ロベルタス アドリアヌス

マリア

オランダ国 5621 ベーアー アイン

ドーフェン フルーネヴアウツウェッハ

1

最終頁に続く

(54) 【発明の名称】半導体デバイス及びその製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

導電領域を有する半導体素子を具える半導体本体を具え、前記導電領域上に、下部電極、酸化物強誘電体及び上部電極を有する、メモリ素子を構成するキャパシタが存在し、前記下部電極が前記導電領域と電気的に接触するとともにプラチナと導電性金属酸化物を形成しうる金属を含む層を具えている半導体デバイスにおいて、

前記下部電極は導電性金属酸化物の層を具え、且つ前記プラチナを含む層(111)が導電性金属酸化物を形成しうる金属を15原子%以上含み、且つ前記導電性金属酸化物の層が前記プラチナを含む層と前記強誘電体との間に存在することを特徴とする半導体デバイス。

## 【請求項 2】

導電性金属酸化物を形成しうる前記金属はルテニウムであることを特徴とする請求項1記載の半導体デバイス。

## 【請求項 3】

前記プラチナ含有層と前記導電領域との間に導電性酸化物を形成しうる金属の層が存在していることを特徴とする請求項1又は2記載の半導体デバイス。

## 【請求項 4】

前記導電領域はタンゲステンで構成されていることを特徴とする請求項1～3のいずれかに記載の半導体デバイス。

## 【請求項 5】

10

20

半導体デバイスの他の部分間又は他の部分への電気的接続が前記プラチナを含む層から形成されていることを特徴とする請求項 1 ~ 4 のいずれかに記載の半導体デバイス。

**【請求項 6】**

導電領域を有する半導体素子を具える半導体本体を見え、前記導電領域上に、下部電極、誘電体及び上部電極を有する、メモリ素子を構成するキャパシタが設けられた半導体デバイスの製造するにあたり、前記導電領域上にプラチナと導電性金属酸化物を形成しうる金属を含む層を具える下部電極を設ける工程と、酸化物強誘電体を設ける工程と、酸素含有雰囲気内において高温処理を実行する工程と、上部電極を設ける工程とを具える半導体デバイスの製造方法において

前記下部電極はプラチナと導電性酸化物を形成しうる金属の堆積により設け、導電性酸化物を形成しうる前記金属は 20 原子 % 以上含有させ、該堆積後に酸素含有雰囲気内における前記高温処理を実行し、その後前記強誘電体を設けることを特徴とする半導体デバイスの製造方法。 10

**【請求項 7】**

プラチナと導電性酸化物を形成しうる金属の前記堆積は、プラチナと導電性酸化物を形成しうる金属のスパッタリング、化学気相成長又は電気化学成長の何れで行なうことを特徴とする請求項 6 記載の半導体デバイスの製造方法。

**【請求項 8】**

導電性酸化物を形成しうる前記金属としてルテニウムを設けることを特徴とする請求項 6 又は 7 記載の方法。 20

**【請求項 9】**

プラチナと導電性金属酸化物を形成しうる前記金属の前記堆積後であるが、前記高温処理前に、プラチナ層を前記堆積により生成された金属層の上に設けることを特徴とする請求項 6 又は 7 記載の方法。

**【請求項 10】**

プラチナと導電性金属酸化物を形成しうる前記金属の前記堆積前に、導電性金属酸化物を形成しうる金属の層を前記導電領域上に設けることを特徴とする請求項 6 又は 7 記載の方法。

**【発明の詳細な説明】**

本発明は、導電領域を有する半導体素子を具える半導体本体を見え、前記導電領域上に、下部電極、酸化物の強誘電体及び上部電極を有する、メモリ素子を構成するキャパシタが存在し、前記下部電極が前記導電領域と電気的に接触するとともにプラチナと導電性金属酸化物を形成しうる金属を含む層を具えている半導体デバイスに関するものである。本発明はこのような半導体デバイスを製造する方法にも関するものである。 30

誘電体のような強誘電材料を有するキャパシタからなる上述のメモリ素子は不揮発性メモリ素子である。電圧をキャパシタの両端間に印加し、再び除去すると、即ち電圧パルスを印加すると、残留分極が強誘電材料内に存在する。反対極性の等しい大きさの電圧パルスをこのキャパシタの両端間に印加すると、残留分極が逆向きになる。従って、電圧パルスによって 2 つの安定な分極状態の間で繰り返し切り換えることができる。实际上、メモリ素子は電圧パルスを供給するスイッチングトランジスタに接続される場合が多い。経済上の理由から、半導体本体上に単位面積当たりできるだけ多数のメモリ素子を実現するのが望ましい。従って、実際には、メモリ素子は接点パッド、スイッチングトランジスタの電極及びスルーリード（バイア）のような導電領域上に設けられる場合が多い。これらの導通領域はドープシリコン、シリサイド又は金属のような材料を具える。 40

当初に記載された種類のデバイスは特開平 4 - 287968 号や特開平 6 - 21391 号から既知であり、これには集積メモリ素子として強誘電体キャパシタを具えた半導体デバイス及びその方法が開示されている。このデバイスでは酸化物強誘電体層との接続のために下部電極をプラチナと導電性金属酸化物を形成しうる金属を含有する層で形成している。この下部電極上に、酸化物強誘電体として鉛 - ジルコニアチタン酸塩からなる強誘電体層が設けられる。前記導電性金属酸化物を形成しうる金属を含む層は、製造中に酸素が 50

導電表面へ拡散するのを阻止する金属酸化物（酸素障壁）を構成する。この酸素は導電表面を酸化するため、下部電極が導電表面と良好に電気的に接觸しなくなる。

上述の既知のデバイスは、高い酸化温度での強誘電体処理中に金属酸化物の存在にもかかわらず下部電極と導電領域との電気的接觸が実際上しばしば不満足になり、導電領域と下部電極との間に増大した接觸抵抗がしばしば測定されるという欠点を有している。

本発明の目的は特に上述の欠点を克服することにある。

この目的を達成するために、本発明の半導体デバイスにおいては、前記下部電極が導電性金属酸化物層を具え、且つ前記プラチナ含有層が導電性金属酸化物を形成しうる金属を15原子%以上含み、且つ前記導電性金属酸化物層が前記プラチナ含有層と前記強誘電体との間に存在することを特徴とする。

この構成によれば、半導体デバイスの製造後に下部電極と導電領域との間に良好な電気的接觸を得ることができる。

本発明は、半導体デバイスの製造中に導電領域と下部電極との界面に導電領域の材料の酸化により非導電性酸化物が依然として形成されるという認識に基づくものである。既知のデバイスの製造中においては導電性金属酸化物を有する層の製造時及び強誘電体の製造時に酸素含有雰囲気中において高温処理が実施される。この処理中に酸素が比較的容易にプラチナ含有層を経て拡散する。従って、比較的少量の酸素が酸素障壁を経て導電領域まで拡散する。このとき、薄い非導電性酸化層が導電領域上に形成される。既知の半導体デバイスにおいてはこの非導電性酸化層が導電領域と下部電極との間の比較的高い接觸抵抗をもたらす。本発明に従ってプラチナ含有層を導電性金属酸化物を形成しうる金属を15原子%以上含むものとすると、デバイスの製造中に追加の酸素障壁が形成されるという驚くべき事実が確かめられた。この場合には酸素が製造中に導電領域と下部電極との界面まで拡散することは全く又は殆ど不可能になる。従って、本発明のデバイスは下部電極と導電領域との間の良好な電気的接觸をもたらす。導電性酸化物を形成しうる金属をプラチナ含有層に添加することによりこの層の電気的特性が低下することは全く又は殆どない。

導電性金属酸化物を形成しうる金属としては例えはレニウム又はルテニウムとすることができる。本発明デバイスの好適例においては、導電性金属酸化物を形成しうる金属をルテニウムとする。これにより、極めて良好な酸素障壁を製造中に形成することができる。

導電性酸化物を形成しうる金属の層をプラチナ含有層と導電領域との間に存在させると、追加の利点が得られる。この実施例ではプラチナ含有層の酸素透過度が極めて強く減少し、酸素含有雰囲気内における高温度( $> 500$ )の長時間(1時間)の処理の場合でも、導電領域と下部電極との間の電気的接觸抵抗に何の増大も測定されない。このようなデバイスは、導電性酸化物を形成しうる金属の層とプラチナの層を導電領域上に設け、これらの層を酸素含有雰囲気内で高温処理することにより比較的容易に製造することができる。次の過程が生ずるものと推測される。導電性金属酸化物を形成しうる金属の層は高温処理中に金属の拡散源を形成する。この層の金属の一部分がプラチナ含有層内に拡散し、従って導電性金属酸化物を形成しうる金属を15原子%以上含むプラチナの合金層を形成する。この合金層は導電領域への酸素の拡散を阻止する。導電性金属酸化物を形成しうる金属の他の部分がプラチナ含有層を経て拡散し、酸化し、導電性金属酸化物層を形成する。従って、導電表面に向かう酸素拡散が合金層と、導電性金属酸化物層とにより阻止される。既知の半導体デバイスでは、導電性酸化物層が導電性金属酸化物を形成しうる金属のプラチナ含有層内への拡散を阻止するためにこのような合金層が形成されない。

導電領域はタングステンで構成するのが好ましい。タングステンは電気的リードスルー(接点又はバイア)に極めて頻繁に使用されている。タングステンは極めて容易に酸化し、タングステン酸化物は約500以上的温度で蒸発し、タングステンの導電領域を有する既知の半導体デバイスの製造においてはタングステンが酸化する問題が生ずる。タングステン酸化物の蒸発は下部電極を導電領域から剥離させる。本発明の半導体デバイスでは、実際にタングステンに酸化物が形成されないため、下部電極はタングステン導電領域と良好な機械的及び電気的接觸を有する。

本発明半導体デバイスにおいては、半導体デバイスの他の部分間又は他の部分への電気的

10

20

30

40

50

接続はプラチナ含有層から形成するのが好ましい。プラチナ含有層を下部電極の製造中に導電表面上に設ける。下部電極のプラチナ含有層はこの層から製造する。次にこのプラチナ含有層をパターン化し、本発明では同時に下部電極と1個又は数個の他の電気接続をデバイス内に形成する。この際、このプラチナ含有層は半導体本体の表面上の追加の配線層としても使用する。

本発明は、導電領域を有する半導体素子を具える半導体本体を具え、前記導電領域上に下部電極、誘電体及び上部電極を有するメモリ素子を構成するキャパシタが設けられた半導体デバイスの製造するにあたり、前記導電領域上にプラチナと導電性金属酸化物を形成しうる金属を含む層を具える下部電極を設ける工程と、酸化物強誘電体を設ける工程と、酸素含有雰囲気内における高温処理を実行する工程と、上部電極を設ける工程とを具える半導体デバイスの製造方法にも関するものである。10

本発明の目的は導電領域と下部電極との間に良好な電気的接触を有する半導体デバイスを製造する方法を提供することにある。

本発明の方法においては、下部電極をプラチナと導電性酸化物を形成しうる金属の共堆積により設け、導電性酸化物を形成しうる前記金属は20原子%以上含有させ、その後に酸素含有雰囲気内における前記高温処理を実行し、前記強誘電体を設けることを特徴とする。20

この方法によれば、酸素雰囲気内における高温処理中に導電性金属酸化物層がプラチナ及びこの金属酸化物を形成する金属を含む金属層上に形成される。この金属酸化物層及び共堆積されたその下の金属層が酸素障壁として作用する。この2重障壁により、実際上酸素は導電領域と下部電極との界面まで拡散し得ない。従って、導電領域と下部電極との間に良好な電気的接触が生成される。共堆積は下部電極の比較的滑らかな表面ももたらす。高温処理後における導電性酸化物を形成する金属の原子パーセントはプラチナ含有層内において15%以上になる。20

導電性酸化物を形成しうる金属としてルテニウムを設けるのが好ましい。15%以上のルテニウムを有するプラチナ層とルテニウム酸化物層とが相まって極めて有効な対酸素障壁を形成する。

プラチナと導電性金属酸化物を形成しうる金属の共堆積により生成した金属層の上に、高温処理前に、プラチナ層を設けるのが好ましい。このようなプラチナ層を有する下部電極上に設けられた酸化物強誘電体は既知の疲労効果により生ずる誘電体の欠陥に対し高い抵抗を示すことが確かめられた。30

プラチナと導電性金属酸化物を形成しうる金属の共堆積前に導電性金属酸化物を形成しうる金属の層を設けると追加の利点が得られる。この場合には、酸素含有雰囲気内における長時間の高温処理に対しても接触抵抗が増大する問題が実際上生じないことが確かめられた。

以下に図面を参照して本発明を更に詳細に説明する。図面において、

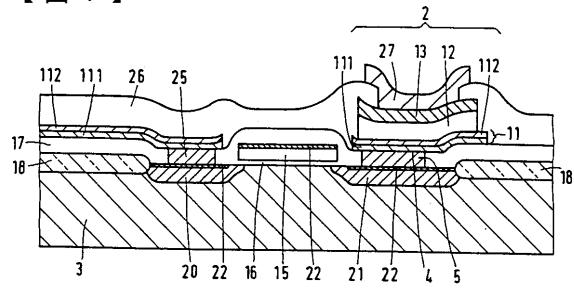

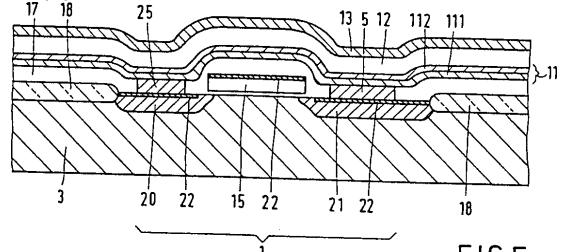

図1は本発明半導体デバイスの断面図であり、

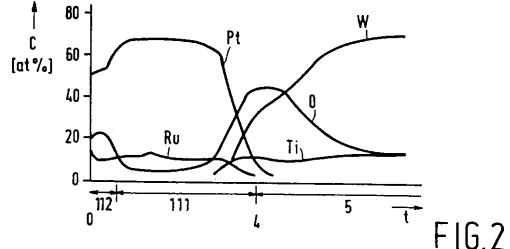

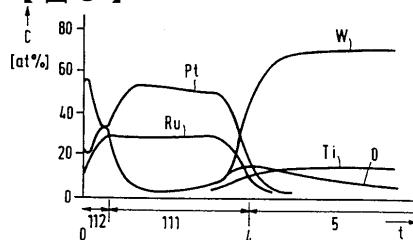

図2及び図3は種々の下部電極に対するオージェ電子分光法(AES)の測定結果を示すグラフ(横軸にスパッタリング時間、縦軸に原子濃度がプロットされている)、

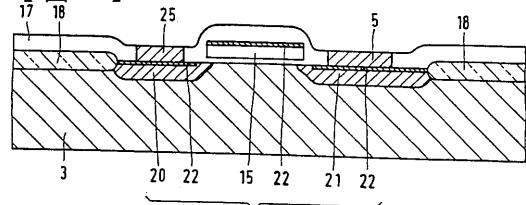

図4及び図5は本発明半導体デバイスの種々の製造工程を示し、40

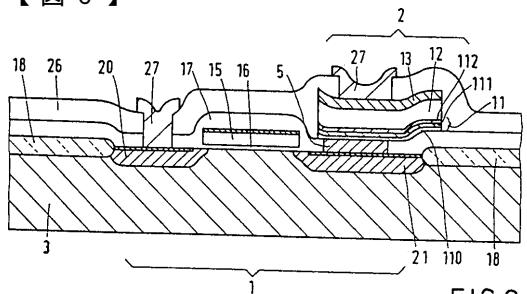

図6は本発明半導体デバイスの他の実施例の断面図である。

これらの図は純粋に略図であって、一定の寸法比で描いてない。

図1は本発明半導体デバイスの断面図である。この半導体デバイスは導電領域5を有する半導体素子1(本例ではトランジスタ)を有する半導体本体3を具え、その導電領域5上に、下部電極11、酸化物強誘電体12及び上部電極13を有する、メモリ素子を形成するキャパシタ2が存在し、この下部電極が導電領域5と電気的に接触し且つ導電性金属酸化物層112とプラチナ含有層111とを具得ている。トランジスタ1とキャパシタ2はスイッチングエロクトロニクスにより相互接続される。これらのスイッチングエレクトロニクスにより強誘電体12を2つの安定な分極状態の間でスイッチすることができる。図を簡単にするために、1つのトランジスタ1及び1つのキャパシタ2のみを示したが、実50

際には半導体本体 3 は極めて多数のこのようなトランジスタ及びキャパシタを具えている。図 1 に示す M O S トランジスタは通常の方法でシリコン半導体本体 3 内に設けられる。多結晶シリコンのゲート電極 1 5 は半導体本体 3 から約 3 0 n m の厚さのシリコン酸化膜 1 6 により絶縁される。ゲート電極 1 5 は更にシリコン酸化膜 1 7 により絶縁される。個々のトランジスタはフィールド酸化物領域 1 8 により互いに分離される。トランジスタのドレイン及びソース領域 2 0 及び 2 1 はフィールド酸化物領域 1 8 とゲート電極 1 5 との間に拡散により形成される。図 1 の M O S トランジスタは既知の方法で製造される。

経済上の理由から、半導体本体 3 上に単位面積当たりできるだけ多数のメモリ素子を実現するのが望ましい。このことは、実際には、メモリ素子は接点パッド、スイッチングトランジスタの電極及びスルー接続部（バイア、プラグ）のような半導体素子の導電領域上に設けられることが多いことを意味する。これらの導電領域はドープシリコン、シリサイド又は金属のような材料で構成される。図 1 の例では、導電領域 5 はタンクステンリードスルー領域（プラグ）である。このようなタンクステンプラグは実際に広く使われている。タンクステンは極めて酸化し易いため、既知の半導体デバイスでは導電領域と下部電極との間の接触抵抗がしばしば高くなりすぎる。

本発明の半導体デバイスにおいては、前記プラチナ含有層 1 1 1 が導電性金属酸化物を形成しうる金属を 1 5 原子%以上含み、導電性金属酸化物層 1 1 2 がプラチナ含有層 1 1 1 と強誘電体 1 2 との間に存在することを特徴とする。この構成によれば、半導体デバイスの製造後に下部電極 1 1 と導電領域 5 との間に良好な電気的接触を得ることができる。導電性金属酸化物を形成しうる金属としてはルテニウムを選択するのが好ましい。

図 2 及び図 3 はオージェ電子分光法（A E S）により記録されたデータのグラフを示す。スパッタリング時間がこれらの図の横軸にプロットされている。このスパッタリング時間は下部電極 1 1 の表面下の深さの尺度である。原子濃度（原子%）が図 2、3 の縦軸にプロットされている。図 2 は、プラチナ内に約 1 0 原子%のルテニウムを加え、N<sub>2</sub> / O<sub>2</sub> 雰囲気内で 5 5 0 で 1 時間加熱処理した後に、導電タンクステン層 5 とプラチナ含有層 1 1 との界面 4 にタンクステン酸化層がどのくらい形成されるかを示す。図 3 は、1 5 原子%以上（本例では約 3 0 原子%）のルテニウムの場合には、N<sub>2</sub> / O<sub>2</sub> 雰囲気内で 6 0 0 で 1 時間加熱した後に、界面 4 に極めて少量の酸素が存在するだけとなることを示す。この酸素は下部電極 1 1 を設ける前に既に存在していたものと予想される。この量の酸素は導電領域 5 のタンクステン上に密閉タンクステン酸化膜を形成するには不十分である。

本発明半導体デバイスの第 1 の実施例は次の通りである（図 4、5 及び 1 参照）。図 4 はゲート電極 1 5 、ドレイン領域 2 0 及びソース領域 2 1 を有するスイッチングトランジスタ 1 を半導体本体 3 内に既知の方法でどの様に形成するかを示す。ゲート電極 1 5 及びドレイン及びソース領域 2 0 及び 2 1 にシリサイド層 2 2 を既知の方法で設ける。トランジスタを既知の方法で燐珪酸ガラス層（P S G）1 7 により覆う。この層 1 7 に、ドレイン及びソース領域 2 0 、2 1 の区域において既知の方法でタンクステンプラグ 2 5 、5 を設けてソース領域 2 1 上に導電領域 5 を形成する。次に、2 0 0 n m のプラチナ／ルテニウム（7 0 / 3 0 原子%）の層を半導体本体 3 の表面上に設ける。この層は室温で 0 . 6 5 m P a アルゴンの圧力でスパッタする（R F スパッタリング、5 0 0 W パワー）。ここでは 2 つのスパッタリング源を使用し、約 1 . 5 n m の厚さのルテニウム層とプラチナ層を交互に堆積する。この場合にはプラチナ層を最終層にするのが好ましい。次に、堆積したこれらの層を N<sub>2</sub> / O<sub>2</sub> (8 0 / 2 0) 雰囲気内で 6 0 0 で 1 時間ベーキングする。これにより図 3 に示す本発明による構造を有する下部電極 1 1 が生成される。最後に設けた層をプラチナにしたので、ベーキング後に下部電極の良好な表面が得られる。このような表面を有する下部電極 1 1 上に設けられる酸化物強誘電体 1 2 は既知の疲労効果により生ずるような欠陥に対し高い抵抗力を示す。酸化物強誘電体 1 2 を下部電極 1 1 上に設ける。この強誘電体は既知の物質であり、本例では鉛 - ジルコニアウムチタン酸塩（P Z T）であり、これを既知のようにゾル - ゲル技術により設ける。これは、メトオキシエタノール内に 1 . 1 : 0 . 3 5 : 0 . 6 5 の組成比でリードアセテート、ジルコニアウムブトキサイド及びチタニウム n - ブトキサイドを含む溶液（約 0 . 4 5 モル濃度）で出発する。この溶

10

20

30

40

50

液を回転塗布処理（回転速度 2500 r p m、30 s）により下部電極上に設ける。層 12 を設けた後に、これを酸素雰囲気内で 550 で 30 分間ベーキングする。1 回の回転塗布処理及び 1 回のベーキングサイクルにおいて得られる強誘電体の層厚は約 0.1 μm である。約 0.2 μm の所望の層厚を得るために、この処理を 2 回実施する。次いで層を 600 で 1 時間ベーキングする。上述の処理により得られる鉛 - ジルコニウムチタン酸塩の組成は Pb<sub>1.0</sub>Zr<sub>0.35</sub>Ti<sub>0.65</sub>O<sub>3</sub> である。或いは又、スパッタリング又は有機金属化学気相成長（OMCVD）のような既知の技術を使用することができる。鉛チタン酸塩（PT）、鉛 - ランタニウム - ジルコニウムチタン酸塩、又は他の幾つかの酸化物強誘電体を使用することもできる。プラチナ上部電極 13 をスパッタリングにより誘電体 12 上に設ける（図 5 参照）。上部電極 13、誘電体 12 及び下部電極 11 をフォトリソグラフ及びエッチング技術によりパターン化する。このときプラチナ含有層 111 はタンゲステンプラグ 25 の区域においてエッチ除去されない（図 1 参照）。プラチナ含有層 111 はドレイン領域 20 と半導体デバイスの他の部分との間の電気接続も形成する。このようにこのプラチナ層は半導体本体 3 の表面上の追加の配線層として使用する。次に、半導体本体 3 の表面を絶縁性 PE（プラズマエンハンスト）CVD シリコン酸化層 26 で覆う。この層にコンタクトホールをエッチングし、その中にチタン / タンゲステン障壁層及びアルミニウム配線層 27 を既知の方法で設ける。このように製造された半導体デバイスは導電領域 5 と下部電極 11 との間の極めて低い抵抗値（即ち実際には約 10<sup>-8</sup> / cm<sup>2</sup>）を有する。

図 6 は本発明半導体デバイスの第 2 の実施例を示す。本例では導電性酸化物を形成しうる金属の層 110 をプラチナ含有層 111 と導電領域 5 との間に設ける。本例でもプラチナ含有層 111 の酸化し易さが著しく減少する。このようなデバイスは比較的製造が容易である。先の実施例（図 4）と同様にタンゲステンリードスルーフィールド 5 を有する燐珪酸ガラス層 17 で被覆された MOS トランジスタから出発して、導電領域 5 上に 100 nm のルテニウムの層と 100 nm のプラチナの層を順に設ける。これらの層は室温で 0.65 MPa アルゴンの圧力でスパッタする（RF スパッタリング、500 W パワー）。スパッタした層を N<sub>2</sub> / O<sub>2</sub> 雰囲気内で 600 で 1 時間ベーキングする。これにより約 25 原子 % のプラチナを含むルテニウム層 110 と、約 15 - 20 原子 % のルテニウムを含むプラチナ層 111 と、ルテニウム酸化層 112 をこの順に具える下部電極 11 が得られる。ルテニウム / プラチナ 75 / 25 層とプラチナ / ルテニウム 85 / 15 層の両層が酸素拡散を阻止する役割を演ずるものと推測される。AES 分析の結果は下部電極 11 の表面はプラチナの濃度が高いことを示した。この高濃度プラチナ表面は次にこの表面に設けられる酸化物強誘電体の良好な基板をもたらすものと推測される。次に、既知のスパッタリングプロセスにより PZT を強誘電体 12 として下部電極上に設け、次いでプラチナを上部電極 13 を設ける。次に上部電極 13、誘電体 12 及び下部電極 11 を既知のようにフォトリソグラフィ及びエッチングによりパターン化する。次に既知のように PE CVD シリコン酸化物層 26 を被覆し、上部電極 13 に接点手段 27 を設けて半導体デバイスを完成させる。この実施例も導電領域 5 と下部電極 11 との間に極めて良好な電気的接触（即ち 10<sup>-8</sup> / cm<sup>2</sup>）を有する。

本発明は上述の実施例に限定されない。例えば、実施例 1 及び 2 を組み合わせることもできる。この場合には、最初にルテニウム層を導電表面 5 上に設け、その後にプラチナ / ルテニウム層を共堆積処理により設ける。更に、キャパシタ 2 を各実施例において MOS トランジスタ 1 のソース領域上に位置させることができる。また、例えばバイポーラトランジスタのような他のスイッチング素子を使用することもできること明らかである。更に、導電領域 5 はタンゲステン以外の材料、例えばドープシリコン、シリサイド、シリコン - ゲルマニウム、又はタンゲステン以外の金属を使用することもできる。本発明半導体デバイスを製造する特定の技術について上述したが、これは本発明半導体デバイスの製造方法はこのような技術によって実施しうるのみであることを意味するものではない。例えば、電極 11、13 を設けるスパッタリングの代わりに、化学気相成長（CVD）又は電気化学成長のような他の技術を使用することもできる。強誘電体は溶液 - ゲル技術の代わりに

スパッタリングにより設けることもできる。既知の技術に関しもっと詳しいことを知りたければ、S.M. Sze: "VLSI Technology", McGraw-Hill Book Company, 及びS. Wolf: "Silicon Processing for the VLSI Era" vol.1,2, Lattice Pressを参照されたい。

【図面の簡単な説明】

図1は本発明半導体デバイスの断面図であり、

図2及び図3は種々の下部電極に対するオージェ電子分光法(AES)の測定結果を示すグラフ(横軸にスパッタリング時間、縦軸に原子濃度がプロットされている)、

図4及び図5は本発明半導体デバイスの種々の製造工程を示し、

図6は本発明半導体デバイスの他の実施例の断面図である。

【図1】

FIG.1

【図2】

FIG.2

【図3】

FIG.3

【図4】

FIG.4

【図5】

FIG.5

【図6】

FIG.6

---

フロントページの続き

(72)発明者 ケンペルマン ヨハンナ ヘンリカ ヘレナ マリア

オランダ国 5621 ベーアー アインドーフェン フルーネヴォウツウェッハ 1

審査官 國島 明弘

(56)参考文献 特開平06-021391(JP,A)

特開平04-287968(JP,A)

特開平04-367211(JP,A)

特開平07-093969(JP,A)

特開平06-013572(JP,A)

国際公開第91/13731(WO,A1)

米国特許第5003428(US,A)

特開平04-085878(JP,A)

特開平06-177347(JP,A)

特開平07-312365(JP,A)

特開平06-326250(JP,A)

特開平08-064767(JP,A)

特開平08-064786(JP,A)

特開平08-191137(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8242

H01L 21/8246

H01L 27/105

H01L 27/108