(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7123807号**

**(P7123807)**

(45)発行日 令和4年8月23日(2022.8.23)

(24)登録日 令和4年8月15日(2022.8.15)

(51)国際特許分類

|         |                 |         |       |   |

|---------|-----------------|---------|-------|---|

| H 0 2 J | 7/02 (2016.01)  | H 0 2 J | 7/02  | H |

| H 0 1 M | 10/48 (2006.01) | H 0 1 M | 10/48 | P |

| H 0 1 M | 10/44 (2006.01) | H 0 1 M | 10/44 | P |

F I

請求項の数 11 (全23頁)

(21)出願番号 特願2018-554384(P2018-554384)

(86)(22)出願日 平成29年4月12日(2017.4.12)

(65)公表番号 特表2019-514332(P2019-514332

A)

(43)公表日 令和1年5月30日(2019.5.30)

(86)国際出願番号 PCT/DK2017/000007

(87)国際公開番号 WO2017/178023

(87)国際公開日 平成29年10月19日(2017.10.19)

審査請求日 令和2年2月25日(2020.2.25)

(31)優先権主張番号 PA201600228

(32)優先日 平成28年4月16日(2016.4.16)

(33)優先権主張国・地域又は機関

デンマーク(DK)

前置審査

(73)特許権者 518359144

リチウム バランス エー / エス

デンマーク王国 ディーケイ - 2765

スメーロム、ハッセルルンデン 13

(74)代理人 110000855

特許業務法人浅村特許事務所

(72)発明者 ロペス、アルフレド キヤーノ

スペイン国、ヴァレンシア、パテルナ、

フアン デ ラ シエルヴァ アベニュー、

24

パディーヤ、ヴィンセンテ ギャヴァラ

スペイン国、ヴァレンシア、パテルナ、

フアン デ ラ シエルヴァ アベニュー、

24

ポンセ、ホセ マヌエル トレロ

最終頁に続く

(54)【発明の名称】 セルバランシング方法およびシステム

**(57)【特許請求の範囲】****【請求項1】**

複数のセルを備える少なくとも1つのモジュールを備える電池内の電池セルバランシングのためのシステムであって、

前記モジュール内の個々のセル(C1、C2、…、CN)にわたって電圧または関連する量を監視するように構成された、セル監視ブロック(16)と、

前記モジュールの正端子電圧(12)および負端子電圧(13)を監視するように、ならびに前記モジュールの出力電流Imodおよび前記個々のセル(C1、C2、…、CN)のセル電圧を監視するように構成された、マイクロコントローラ(18)であって、当該マイクロコントローラ(18)が、少なくとも前記監視された前記正端子電圧(12)、前記負端子電圧(13)、前記モジュールの前記出力電流Imod、および前記個々のセルのセル電圧に基づいて制御信号(20)を提供するように構成されている、マイクロコントローラ(18)と、

スイッチングアレイ(4)と、パッシブセルバランシング手段(5、6)と、アクティブセルバランシング手段(7)とを有するハイブリッドモジュールバランシングブロック(3)と、

前記電池内の特定のモジュールの正端子および負端子(12、13)の間に結合され、前記マイクロコントローラによって提供された前記制御信号により制御されるパッシブモジュールバランシング手段(8、9)とを備え、

前記スイッチングアレイ(4)と、前記パッシブセルバランシング手段(5、6)と、

前記アクティブセルバランシング手段(7)は前記マイクロコントローラによって提供された前記制御信号により制御され、

前記ハイブリッドモジュールバランシングブロック(3)は、前記マイクロコントローラによって提供された前記制御信号の制御下で、前記特定のモジュール内のセル(C<sub>1</sub>、C<sub>2</sub>、…、C<sub>N</sub>)のアクティブまたはパッシブのセルバランシングまたはアクティブおよびパッシブのセルバランシングの組み合わせのいずれかを提供し、

前記アクティブセルバランシング手段(7)が、前記特定のモジュール内において前記セル(C<sub>1</sub>、C<sub>2</sub>、…、C<sub>N</sub>)の全てから電力を抽出し、最も放電したセルと他のセルとのバランスを取るために制御された定電流を、他のセルとのバランスが取れるまで前記スイッチングアレイ(4)を介して1つのみ接続された当該最も放電したセルに注入し、

前記マイクロコントローラ(18)及び前記ハイブリッドモジュールバランシングブロック(3)は、前記特定のモジュール内の個々のセル(C<sub>1</sub>、C<sub>2</sub>、…、C<sub>N</sub>)間のアクティブセルバランシングを提供した後に、当該個々のセル(C<sub>1</sub>、C<sub>2</sub>、…、C<sub>N</sub>)のうちの1つ以上の充電状態(SOC)が所定の上限を超えたことに応答して、前記特定のモジュール内の個々のセル(C<sub>1</sub>、C<sub>2</sub>、…、C<sub>N</sub>)にパッシブセルバランシングを提供するように構成され、前記所定の上限は、前記セル(C<sub>1</sub>、C<sub>2</sub>、…、C<sub>N</sub>)の最大許容充電状態または前記モジュールの充電状態の平均値である、システム。

#### 【請求項2】

前記アクティブセルバランシング手段(7)がフライバックDC/DCコンバータである、請求項1に記載のシステム。

#### 【請求項3】

前記パッシブセルバランシング手段(5、6)が、たとえばMOSFETなど、スイッチ(6)と直列の抵抗器(5)である、請求項1に記載のシステム。

#### 【請求項4】

前記パッシブモジュールバランシング手段(8、9)が、たとえばMOSFETなど、スイッチ(9)と直列の抵抗器(8)である、請求項1に記載のシステム。

#### 【請求項5】

前記マイクロコントローラが、前記電池の全体的な性能を管理する電池管理システム(BMS)内のマイクロコントローラである、請求項1から請求項4のいずれか一項に記載のシステム。

#### 【請求項6】

アクティブのバランシングが前記電池を作り上げる前記モジュール内に適用され、その一方でパッシブまたはアクティブのバランシングが前記電池を作り上げる2つ以上のモジュール間に適用される、請求項1から請求項5のいずれか一項に記載のシステム。

#### 【請求項7】

前記システムが、前記電池内の前記モジュールの充電状態(SOC)または電圧を監視するモジュールSOC監視手段または電圧監視手段を備え、2つ以上のモジュール間で前記SOCまたは電圧の間のアンバランスが検出されたときに、前記電池内の前記2つ以上のモジュール間のパッシブまたはアクティブのバランシングが行われる、請求項6に記載のシステム。

#### 【請求項8】

前記電池内の2つ以上のモジュール間の前記パッシブまたはアクティブのバランシングが、前記ハイブリッドモジュールバランシングブロック(3)または前記マイクロコントローラによって制御される、請求項6または請求項7に記載のシステム。

#### 【請求項9】

複数のセルを備える少なくとも1つのモジュールを備える電池内の電池セルバランシングのための方法であって、前記方法が、

充電プロセスが進行中であるか否かを判断するステップと、

モジュール(M1)を選択するステップと、

10

20

30

40

50

前記モジュールの正端子電圧(12)、負端子電圧(13)、出力電流 $I_{mod}$ 、および個々のセルのセル電圧に基づいた制御信号の制御下で、前記モジュール(M1)のセル間にアクティブのセルバランシングを適用するステップと、

前記モジュールの1つ以上のセルが所定の上限を超えて充電されているか否かを判断するステップであって、前記所定の上限は、前記セルの最大許容充電状態または前記モジュールの充電状態の平均値であるステップと、

前記モジュールの1つ以上のセルが前記上限を超えて充電されている場合に、その充電を前記上限またはそれ未満の値に減少させるためにこのまたはこれらのセルに、前記制御信号の制御下でパッシブのセルバランシングを適用するステップと、

前記モジュール(M1)内の全てのセルが充電されたときに、前記電池内にさらなるモジュール(M2、M3、...)があるか否かを判断し、これが該当する場合には残りの前記モジュール(M2、M3、...)に対して上記ステップを繰り返す、ステップと、

前記電池の全てのモジュールが充電されていたら、前記電池内のそれぞれの前記モジュールの充電状態、または類似のパラメータの間にアンバランスがあるか否かを判断し、これが該当する場合には、モジュール間の前記アンバランスを要求されるレベルに低減するために、それぞれのモジュール間に、前記制御信号の制御下でパッシブのまたはアクティブのバランスングのいずれかを適用するステップと、を備え

前記アクティブのセルバランシングを適用するステップは、フライバックDC/DCコンバータにより、前記モジュールのセル(C1、C2、...、CN)の全てから電力を抽出し、その他のセルとのバランスが取れるまで最も放電したセルとのバランスを取りるために制御された定電流を、スイッチを介して1つのみ接続された当該最も放電したセルに注入する、方法。

#### 【請求項10】

アクティブのバランスングが前記電池を作り上げる前記モジュール内に適用される、その一方でパッシブまたはアクティブのバランスングが前記電池を作り上げるモジュール間に適用される、請求項9に記載の方法。

#### 【請求項11】

前記充電状態(SOC)または電圧が、前記電池内の2つ以上のモジュールの前記SOCまたは電圧を監視する監視手段によって監視され、2つ以上のモジュールの間で前記SOCまたは電圧間のアンバランスが検出されたときに、前記電池内の前記2つ以上のモジュール間のパッシブまたはアクティブのバランスングが行われる、請求項10に記載の方法。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は一般に、電池システムにおけるセルバランシングのためのシステムおよび方法に関し、より具体的には、異なる条件下でのセルバランシングを最適化するためにアクティブおよびパッシブセルバランシングの組み合わせを適用するようなシステムおよび方法に関する。

#### 【背景技術】

#### 【0002】

セルバランシングシステムおよび方法は、電池管理の技術分野において知られており、このようなシステムおよび方法は、たとえば電気自動車で動作するように設計された、中規模および大規模な電気化学貯蔵システムで必要とされるものなど、多数のセルからなる電池の性能の最適化において、不可欠である。

#### 【0003】

このようなシステムおよび方法の主な目的は、電池の全てのセル間で均質な条件を維持し、こうして効率、貯蔵エネルギー、および寿命の点で最適な動作を可能にすることである。電池パックの所望の動作電圧に達するために、電池は直列に接続される。完全にセルのバランスが取れている場合、合計電圧はセルごとに均等に分割される。しかしながら、

10

20

30

40

50

実際には、セルはアンバランスになる。セルバランスプロセスは、チェーン内の全てのセルの充電を均等化し、こうして電池容量を増加させる。最大充電は最高セル電圧によって制限され、最大放電は最低セル電圧によって制限されるので、このプロセスが必要である。その使用は、ほとんど全ての技術において望ましく（唯一の例外はレドックスフロー技術である）、イオンリチウム電池のように場合によっては不可欠である。

#### 【 0 0 0 4 】

充放電サイクルの間、直列ストリングの電池は均等に動作しない場合がある。電池は、とりわけその内部抵抗を特徴とし、これは任意のタイプの電池セルの特定の許容限界内で変化し得る。より効率的なセルを有する（すなわち、比較的低い内部抵抗を有するセルを有する）電池はより高い電圧を有する傾向があり、効率の低いセルを有する電池は電圧が低いままとなる。一旦アンバランスが生じると、これはさらなる使用によって増大する傾向がある。したがって、電池を充電するときには、他のものよりもずっと早くフル充電に達するものもある。同様に、より弱いセルは、パック内の他のものよりもずっと早く放電する傾向がある。これは、ほとんどのセルの不十分な利用につながる。要約すると、これらのアンバランスな電池がセル均等化などの制御がなされないまま使用されていると、エネルギー貯蔵容量が著しく減少する。

#### 【 0 0 0 5 】

直列接続されたバッテリストリングは、電気自動車、ハイブリッド電気自動車（H E V）、電動スクーター、および無停電電源など、多くの用途に使用されてきた。これらのうち、H E V電池は充放電環境に激しく曝される。この曝露が生じるのは、H E Vが回生制動中にホイールからエネルギーを回収し（過去に無駄になったエネルギー源）、車両を低速で推進するために、または高加速用に余分な電力を提供するために、これを再利用できるからである。この繰り返される充放電現象は、セルのミスマッチ問題を悪化させる。

#### 【 0 0 0 6 】

セル間のアンバランスは、電圧またはS O C（充電状態）の観点から定義されることが可能である。その性質上、前述されたように、修正措置が講じられないまま、たとえばセルの内部抵抗によるアンバランスは、時間が経過して電池上で充放電サイクルが実施されるにつれて増加し、これにより、他のものが有効なS O Cを有している間に1つ以上の素子が過充電または過放電の状態に到達する事態を招く可能性があるこれらの極端な状況は、他の内部要因とともにシステム全体の早期故障を引き起こす可能性のある、電池の著しい劣化を招く可能性がある。アンバランスおよび劣化の両方が生じる過酷さおよび速さは、以下のような要因に大きく依存する。

・プロセス技術：とりわけ鉛またはN i C dなどのいくつかの技術は、一定レベルの過充電および／または過放電に耐えられる。これらの技術の中には、電池のバランスを定期的に実現するために、わずかな過充電プロセスが使用されるものさえある。しかしながら、リチウムイオンなどの他の技術は、電池を損傷し、その寿命を短縮し、危険な状況を引き起こす可能性さえある、過充電または過放電状態にまったく耐えられない。

・電池使用サイクル：充放電電流および温度の全体的なS O C変動に応じて、アンバランスのプロセスは大幅に変化する可能性がある。たとえば、わずかな過充電が強制される技術では、100%の充電負荷を提供しない不完全な充電サイクルの使用は有害である。

#### 【 0 0 0 7 】

いずれにせよ、電池システムを構成する全てのセル間のバランスを回復する仕組みを確立する必要がある。過充電によるバランスを許容する技術の場合であっても、これらはシステムの効率および寿命の延長の両方に關して有益である。

#### 【 0 0 0 8 】

この意味では、特定のサイズ（直列接続された素子の数）の電池システムにおいて、バランス技術を使用することが望ましい（または必要でさえある）。均等化システムを使用することによって得られる利点は、（i）電池システムの寿命の延長；（ii）電池システムの効率の向上；（iii）電池システムの使用可能なエネルギーの増加；および（iv）電池システムの動作安全性の向上を含む。

**【発明の概要】****【発明が解決しようとする課題】****【0009】**

したがって、全ての現実的な動作条件下で最適なセルバランシングを提供するセルバランシングシステムおよび方法へのアクセスを有することが望ましい。

**【課題を解決するための手段】****【0010】**

上記およびさらなる目的および利点は、本発明にしたがって、セルバランシングシステムおよびセルバランシング方法によって得られるものであり、システムおよび方法は、アクティブおよびパッシブセルバランシングの組み合わせを適用する。

10

**【0011】**

アクティブセルバランシングは、セルエネルギーの熱としての散逸が回避されるべきときに適用する方法である。アクティブセルバランシングは、パッシブセルバランシングよりも効率的であり、熱の発生を生じないため、パッシブバランシングよりも高いバランシング電流を適用できるようにする。

**【0012】**

通常の使用中、任意のモジュール内で最も放電されたセルは、それらの特定のモジュールからエネルギーを得るようにバランスが取られる。

**【0013】**

特定のモジュールが低い充電状態(SOC)にあるとき、アクティブセルバランシングは、特定のモジュールの平均を下回るSOCを有するセルのSOCを平均値まで引き上げることによって、その特定のモジュールに貯蔵されたエネルギーを利用するのに役立ち、このようにして、最低SOCフロアに到達するたった1つのセルによって制限される代わりに、ほとんど全てのセルに対して許容される最低SOCまでモジュール全体を放電させる。

20

**【0014】**

充電プロセスの終盤の間、SOC平均値を下回る1つまたは少数のセルがある場合には、アクティブバランシングが使用されることも可能である。

**【0015】**

パッシブセルバランシングは、たとえば、(少なくとも)以下の状況において有利に適用され得る。

30

充電プロセスの終盤の間、モジュールのSOC平均値を超える1つまたは少数のセルのSOCを減少させ、その後最大可能なSOCで全てのセルの充電プロセスを終了するために、パッシブバランシングが使用可能である。充電プロセス中に、比較的少数のセルのみが不十分に充電された場合には、それらの充電状態を迅速に引き上げるために、アクティブバランシングが適用可能である。反対に、比較的少数のセルが最大許容充電状態を超えて充電された場合には、パッシブバランシングが有利に適用され得る。

**【0016】**

本発明の第1の態様によれば、上記およびさらなる目的および利点は、電池セルモジュール内の個々のセル( $C_1, C_2, \dots, C_N$ )にわたって電圧または関連する量を監視するように構成された、セル監視ブロックと、

40

電池セルモジュールの正端子電圧および負端子電圧を監視するように、ならびにモジュールの出力電流  $I_{mod}$  および個々のセル( $C_1, C_2, \dots, C_N$ )の監視されたセル電圧を監視するために構成された、マイクロコントローラであって、マイクロコントローラは、少なくとも正端子電圧、負端子電圧、モジュールの出力電流  $I_{mod}$ 、および前記個々のセルの監視されたセル電圧に基づいて制御信号を提供するように構成されている、マイクロコントローラと、

マイクロコントローラによって提供された制御信号の制御下で、特定のモジュール内のセル( $C_1, C_2, \dots, C_N$ )のアクティブまたはパッシブのセルバランシングまたはアクティブおよびパッシブのセルバランシングの組み合わせのいずれかを提供するように構成されている。

50

成された、ハイブリッドモジュールバランシングブロックと、

を備えるシステムによって提供される。

**【 0 0 1 7 】**

本発明の第 1 の態様の一実施形態において、ハイブリッドモジュールバランシングブロ

ックは、

制御信号の制御下で特定のモジュール内の個々のセル (C<sub>1</sub>、 C<sub>2</sub>、 ...、 C<sub>N</sub>) のうち

の 1 つ以上にアクティブまたはパッシブまたはアクティブおよびパッシブのバランシング

の組み合わせを提供するように構成された、スイッチングアレイと、

制御信号の制御下でパッシブのバランシングを提供するように構成された、パッシブセ

ルバランシング手段と、

制御信号 (20) の制御下でアクティブのバランシングを提供するように構成された、

アクティブセルバランシング手段と、

を備える。

**【 0 0 1 8 】**

本発明の第 1 の態様の一実施形態において、システムは、特定のモジュールの正端子と

負端子との間に結合されたパッシブモジュールバランシング手段を備える。

**【 0 0 1 9 】**

本発明の第 1 の態様の一実施形態において、アクティブセルバランシング手段はフライ

バック DC / DC コンバータである。

**【 0 0 2 0 】**

本発明の第 1 の態様の一実施形態において、パッシブセルバランシング手段は、たとえ

ば MOSFET など、スイッチと直列の抵抗器である。

**【 0 0 2 1 】**

本発明の第 1 の態様の一実施形態において、パッシブモジュールバランシング手段は、

たとえば MOSFET など、スイッチと直列の抵抗器である。

**【 0 0 2 2 】**

本発明の第 1 の態様の一実施形態において、フライバック DC / DC コンバータは、モ

ジュールのセル (C<sub>1</sub>、 C<sub>2</sub>、 ...、 C<sub>N</sub>) の全てから電力を抽出し、その他のセルとのバ

ランスが取れるまで最も放電したセルのバランスを取るために制御された電流を注入する。

**【 0 0 2 3 】**

本発明の第 1 の態様の一実施形態において、制御された電流は一定である。

**【 0 0 2 4 】**

本発明の第 1 の態様の一実施形態において、マイクロコントローラは、電池の全体的な

性能を管理する電池管理システム (BMS) 内のマイクロコントローラである。

**【 0 0 2 5 】**

本発明の第 1 の態様の一実施形態において、アクティブのバランシングが電池を作り上

げるモジュール内に適用され、その一方でパッシブのバランシングが電池を作り上げるモ

ジュール間に適用される。

**【 0 0 2 6 】**

本発明の第 1 の態様の一実施形態において、システムは、電池内のモジュールの充電状

態 (SOC) または電圧を監視するモジュール SOC 監視手段または電圧監視手段を備え

、2つ以上のモジュール間で SOC または電圧の間のアンバランスが検出されたときに、

電池内の2つ以上のモジュール間のパッシブのバランシングが行われる。

**【 0 0 2 7 】**

本発明の第 1 の態様の一実施形態において、電池内の2つ以上のモジュール間のパッシ

ブのバランシングは、ハイブリッドモジュールバランシングブロックまたは電池管理シス

テム (BMS) によって制御される。本発明の第 2 の態様によれば、複数のセルを備える

少なくとも1つのモジュールを備える電池内の電池セルバランシングのための方法が提供

され、方法は、充電プロセスが進行中であるか否かを判断するステップと、

モジュール (M1) を選択するステップと、

10

20

30

40

50

前記モジュール（M1）のセル間にアクティブのセルバランシングを適用するステップと、

1つ以上のセルが所定の上限を超えて充電されているか否かを判断するステップと、

1つ以上のセルが所定の上限を超えて充電されている場合に、その充電を前記上限またはそれ未満の値に減少させるためにこのまたはこれらのセルにパッシブのセルバランシングを適用するステップと、

前記モジュール（M1）内の全てのセルが充電されたときに、電池内にさらなるモジュール（M2、M3、…）があるか否かを判断し、これが該当する場合には残りのモジュール（M2、M3、…）のために上記ステップを繰り返す、ステップと、

電池の全てのモジュールが充電されていたら、電池内のそれぞれのモジュールの充電状態、または類似のパラメータの間にアンバランスがあるか否かを判断し、これが該当する場合には、モジュール間の前記アンバランスを要求されるレベルに低減するために、それぞれのモジュール間にパッシブのまたはアクティブにバランシングのいずれかを適用するステップと、

を備える。

#### 【0028】

本発明の第2の態様の一実施形態において、アクティブのバランシングが電池を作り上げるモジュール内に適用され、その一方でパッシブのバランシングが電池を作り上げるモジュール間に適用される。

#### 【0029】

本発明の第2の態様の一実施形態において、充電状態（SOC）または電圧は、電池内の2つ以上のモジュールのSOCまたは電圧を監視する監視手段によって監視され、2つ以上のモジュールの間でSOCまたは電圧間のアンバランスが検出されたときに、電池内の2つ以上のモジュール間のパッシブのバランシングが行われる。

#### 【0030】

本発明のさらなる特徴は、本発明の以下の詳細な説明および図面から明らかになるであろう。

#### 【0031】

本発明のさらなる恩典および利点は、以下の添付図面と併せて本発明の比限定期的な例示的実施形態の詳細な説明を読めば明らかになるであろう。

#### 【図面の簡単な説明】

#### 【0032】

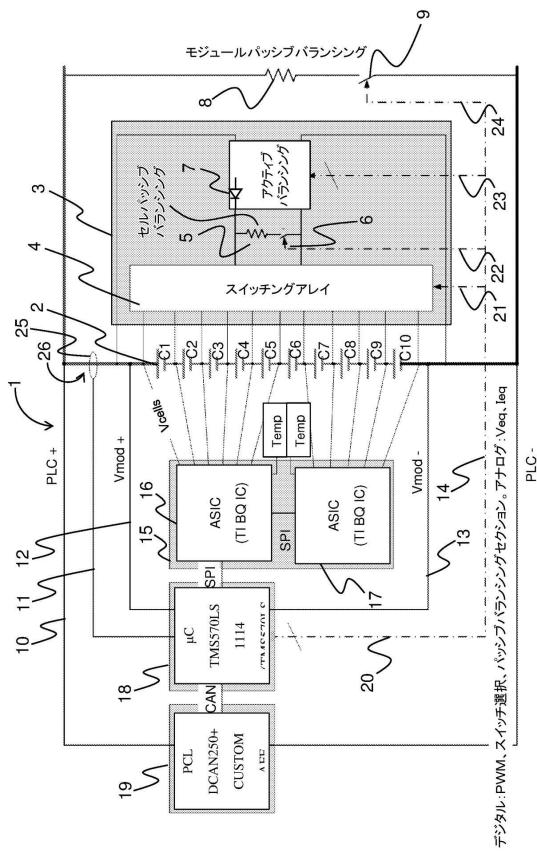

【図1】本発明によるセルバランシングシステムの一実施形態を示す図である。

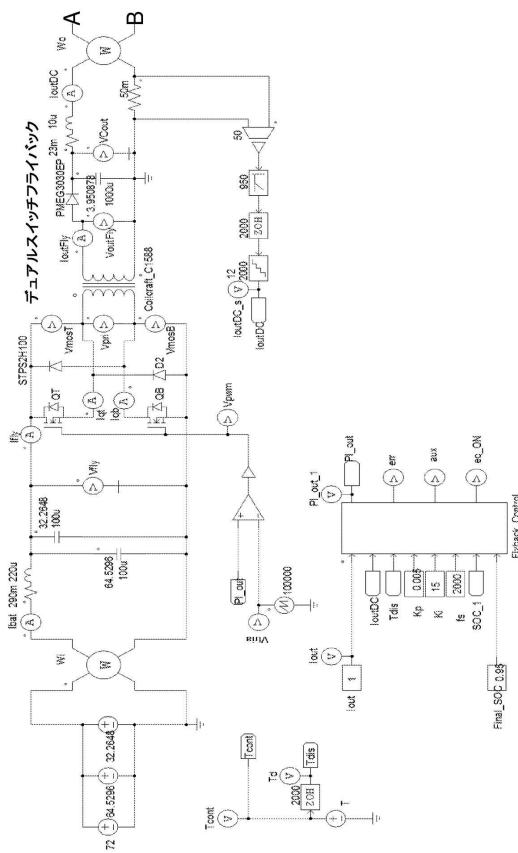

【図2】本発明による方法の一実施形態の基本ステップを示すフローチャートである。

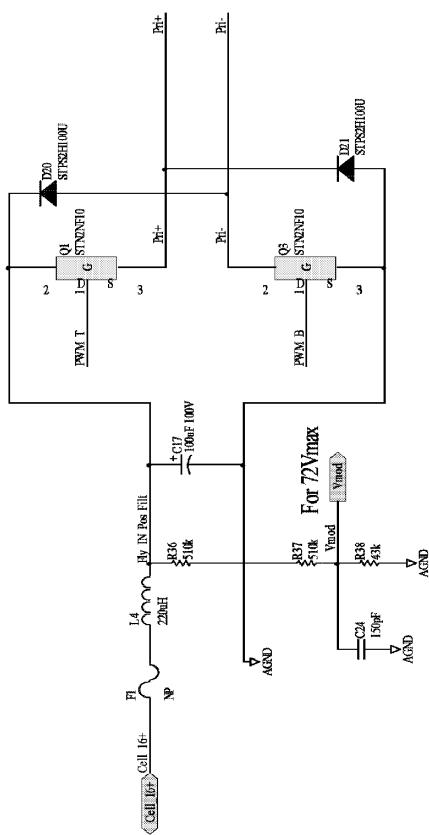

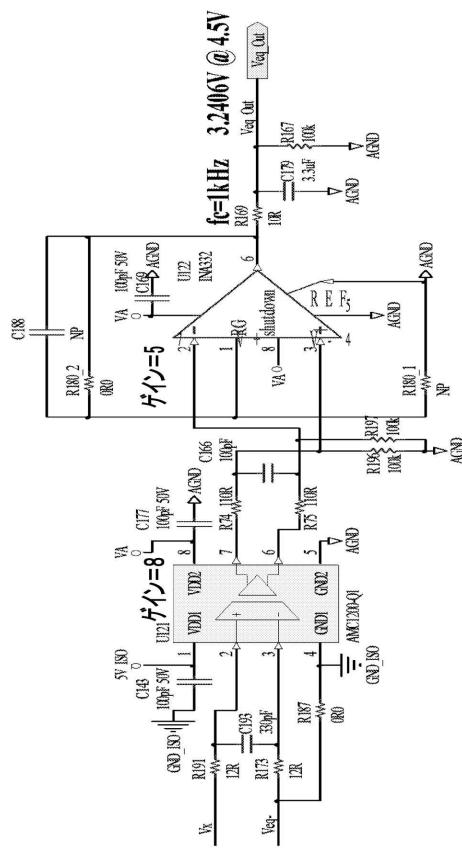

【図3a】本発明の実施形態で使用される絶縁フライバックコンバータの回路図である。

【図3b】本発明の実施形態で使用される絶縁フライバックコンバータの回路図である。

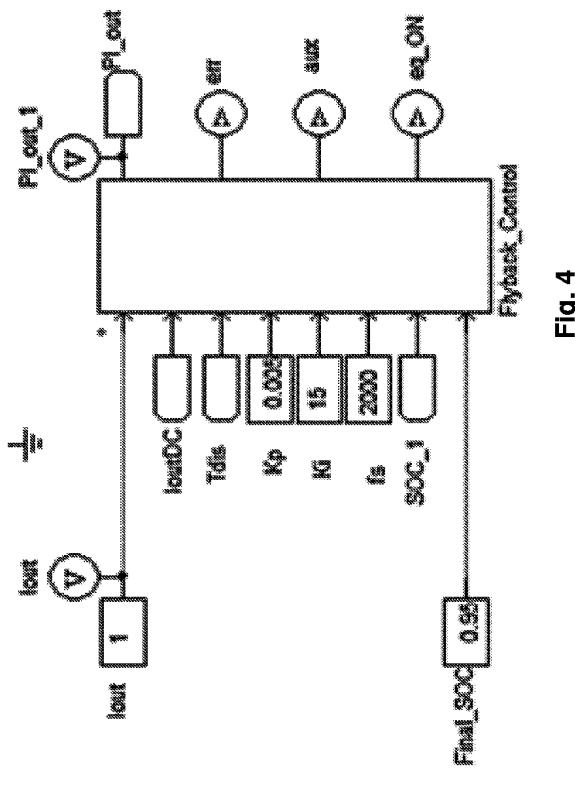

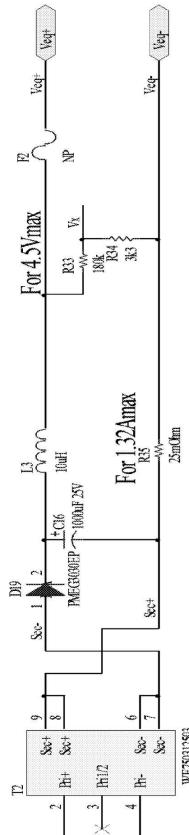

【図4】本発明の実施形態で使用されるフライバック制御ロックを示す図である。

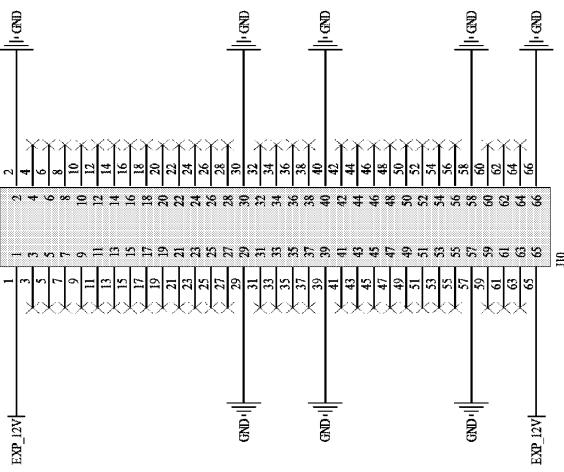

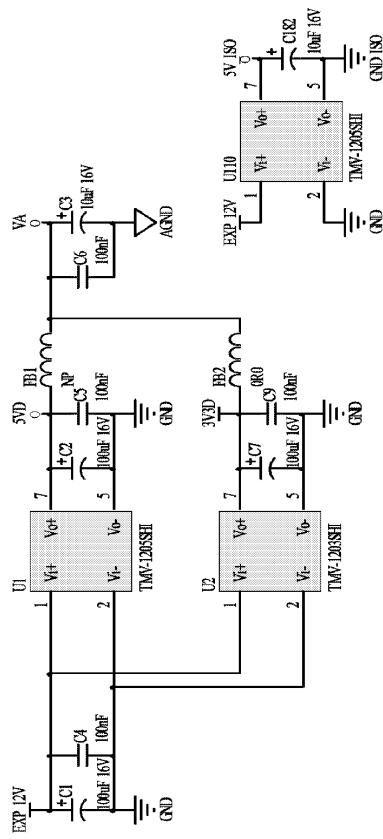

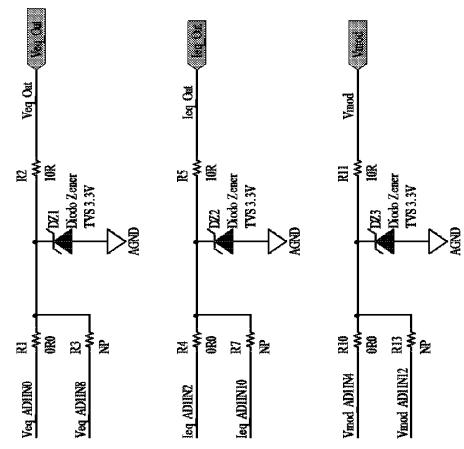

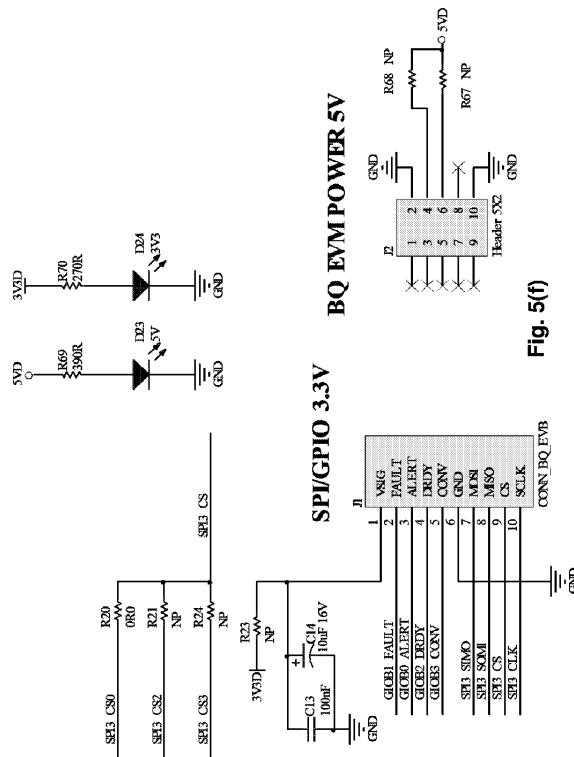

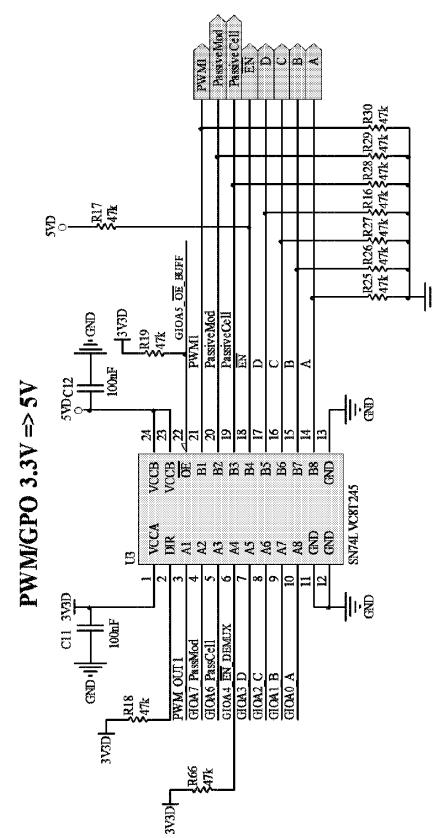

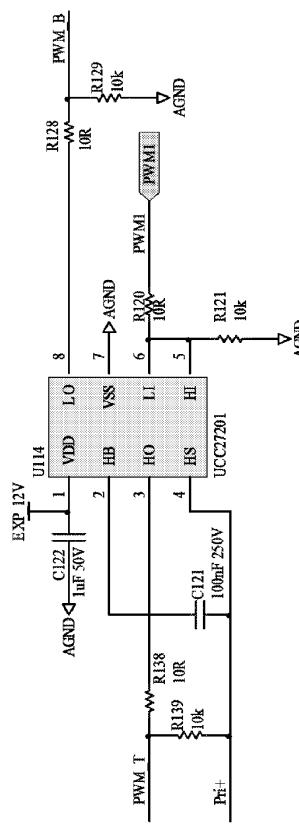

【図5a】本発明の実施形態で使用されるHerculesマイクロコントローラとのインターフェースの回路図である。

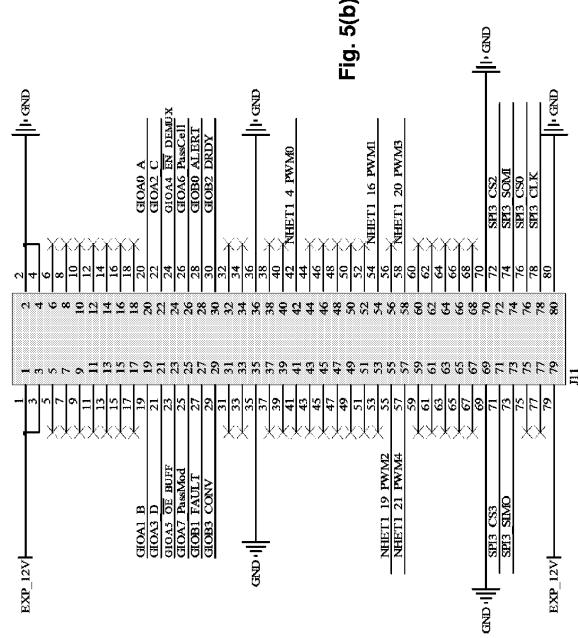

【図5b】本発明の実施形態で使用されるHerculesマイクロコントローラとのインターフェースの回路図である。

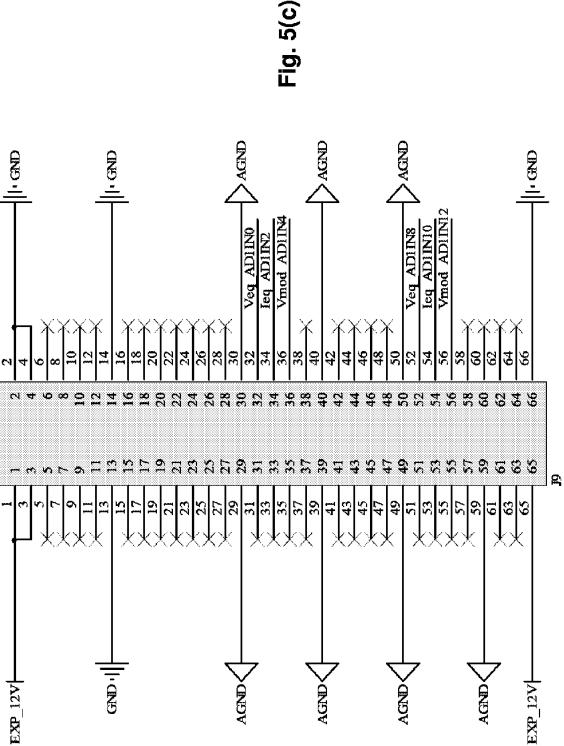

【図5c】本発明の実施形態で使用されるHerculesマイクロコントローラとのインターフェースの回路図である。

【図5d】本発明の実施形態で使用されるHerculesマイクロコントローラとのインターフェースの回路図である。

【図5e】本発明の実施形態で使用されるHerculesマイクロコントローラとのインターフェースの回路図である。

【図5f】本発明の実施形態で使用されるHerculesマイクロコントローラとのインターフェースの回路図である。

【図5g】本発明の実施形態で使用されるHerculesマイクロコントローラとのイ

10

20

30

40

50

ンターフェースの回路図である。

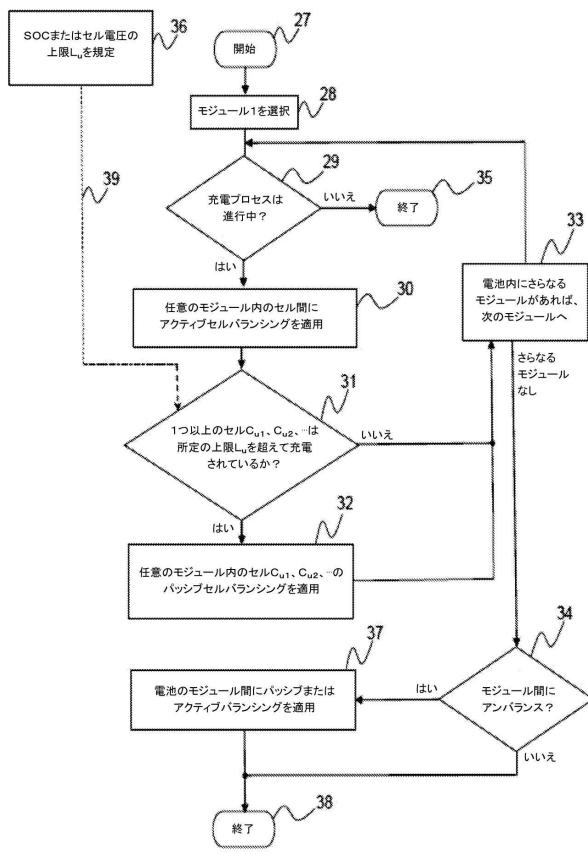

【図 6 a】本発明の一実施形態で使用されるデュアルスイッチ絶縁フライバックコンバータの回路図である。

【図 6 b】本発明の一実施形態で使用されるデュアルスイッチ絶縁フライバックコンバータの回路図である。

【図 6 c】本発明の一実施形態で使用されるデュアルスイッチ絶縁フライバックコンバータの回路図である。

【図 6 d】本発明の一実施形態で使用されるデュアルスイッチ絶縁フライバックコンバータの回路図である。

【図 6 e】本発明の一実施形態で使用されるデュアルスイッチ絶縁フライバックコンバータの回路図である。 10

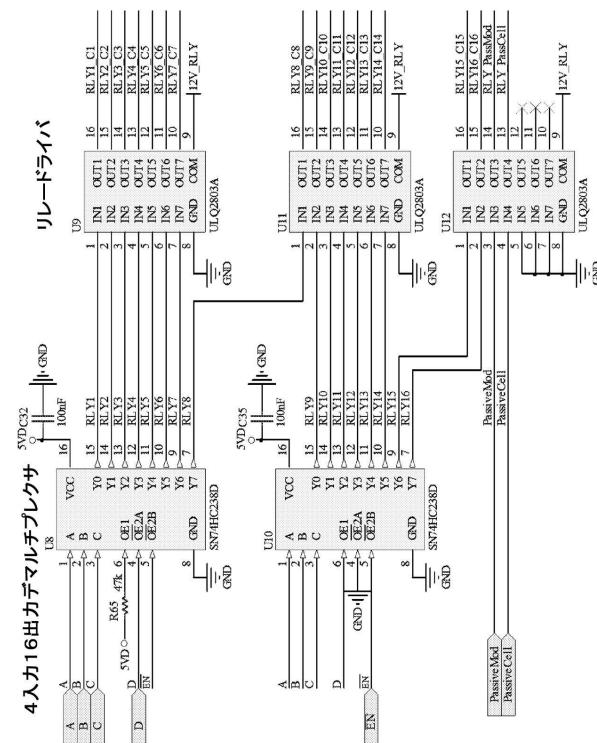

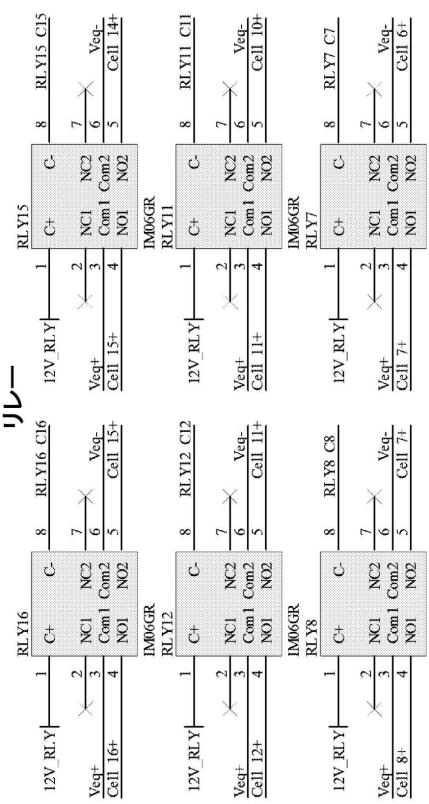

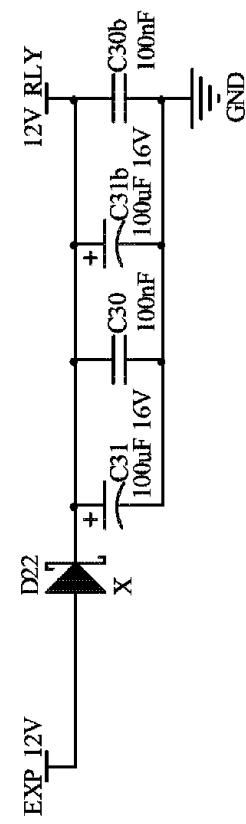

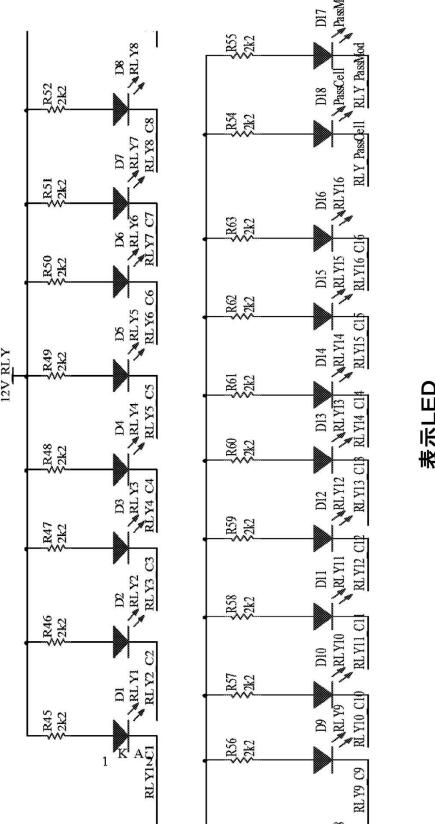

【図 7 a】本発明の一実施形態で使用されるデマルチブレクサを備えるリレー選択回路の回路図である。

【図 7 b】本発明の一実施形態で使用されるデマルチブレクサを備えるリレー選択回路の回路図である。

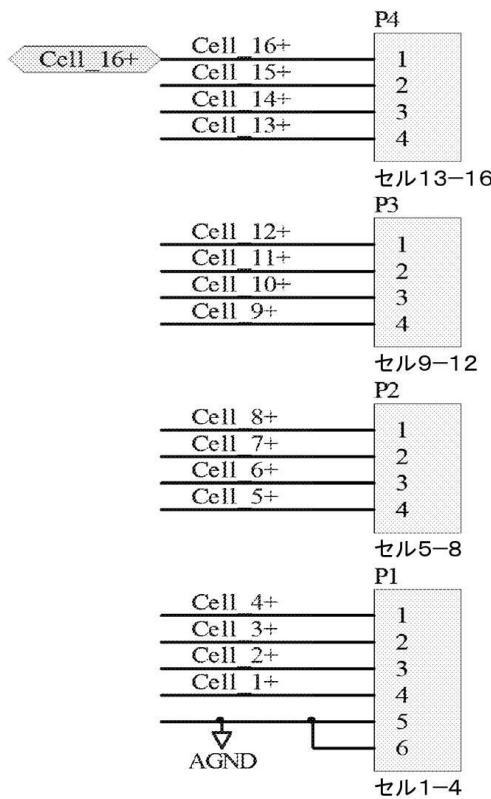

【図 7 c】本発明の一実施形態で使用されるデマルチブレクサを備えるリレー選択回路の回路図である。

【図 7 d】本発明の一実施形態で使用されるデマルチブレクサを備えるリレー選択回路の回路図である。 20

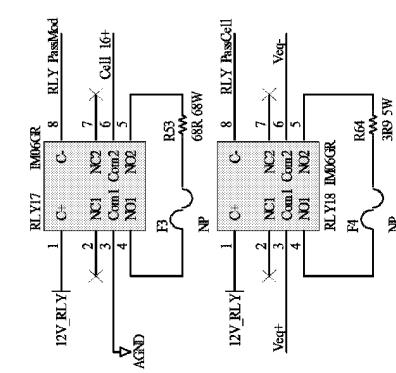

【図 7 e】本発明の一実施形態で使用されるデマルチブレクサを備えるリレー選択回路の回路図である。

【図 7 f】本発明の一実施形態で使用されるデマルチブレクサを備えるリレー選択回路の回路図である。

【図 7 g】本発明の一実施形態で使用されるデマルチブレクサを備えるリレー選択回路の回路図である。

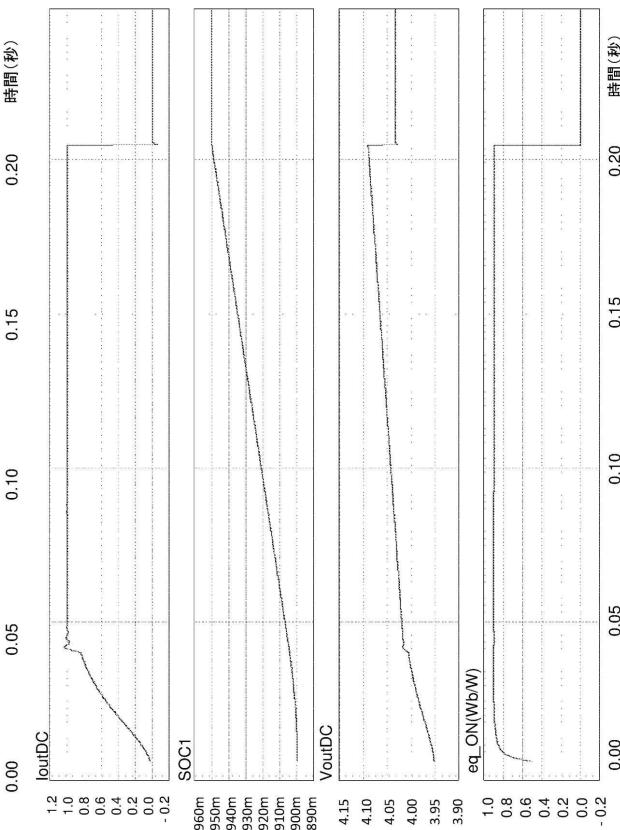

【図 8】16個のセルモジュールに対するシミュレーション結果のグラフである。

【図 9】8個のセルモジュールに対するシミュレーション結果のグラフである。

#### 【発明を実施するための形態】

##### 【0033】

本発明によるセルバランシングシステムの比限定的な実施形態が、以下に詳細に記載される。しかしながら、本発明は他の方法で実施されてもよく、本発明のこのような実施形態の全てが特許請求項によって定義される保護範囲に含まれることは、理解される。 30

##### 【0034】

様々なパラメータなどについて特定の数値が以下に挙げられるものの、このような特定の数値は単なる例示と見なされるべきであり、その結果としてこれらは特許保護の範囲を限定するものではないことは、明らかである。

##### 【0035】

図1を参照すると、アクティブおよびパッシブセルバランシングの組み合わせを適用するための手段を備える、参考番号1で全体的に示される、本発明によるセルバランシングシステムの一実施形態が示されている。

##### 【0036】

図1に示されるシステムは、図示される実施形態において10個のセルC1、C2、…、C10の直列接続を含む電池モジュールを備える。当然ながら、異なる数のセルがモジュール内にあってもよく、本発明の原理はそのようなモジュールにも等しく適用されるることは、理解される。

##### 【0037】

図1に示される実施形態の説明では用語「モジュール」が繰り返し使用されているが、本発明は、電池全体を構成する1つ以上の物理的モジュールに限定されるものではないことが、さらに理解される。したがって、電池は、特定のモジュールへのいかなる細分も伴わずに直列で結合された多数のセルを単純に備えることができ、またはモジュールは単純 50

に、電池内の任意の数のセルの架空の細分であってもよい。このように、用語「モジュール」への言及は、本発明の範囲に対する制限を示唆するものではない。

#### 【0038】

システムは、スイッチングアレイ4と、MOSFETなど、制御可能なスイッチ6を通じて作動可能な抵抗器5などのパッシブバランスング手段と、DC/DCコンバータ7などのアクティブバランスング装置と、を備えるハイブリッドモジュールバランスングブロック3を備える。

#### 【0039】

モジュール全体にわたって結合されて、MOSFETなどのスイッチ9を通じて作動可能な抵抗器8などの、モジュールパッシブバランスング手段がさらに結合されている。

10

#### 【0040】

スイッチングアレイ4、セルパッシブバランスング手段5および6、DC/DCコンバータ7、ならびにモジュールパッシブバランスング手段8および9は、制御線20から25で象徴的に示されるように、適切な制御信号によって制御される。

#### 【0041】

それぞれのセルC1からC10にかかる電圧は、図示される実施形態において、セル電圧測定線Vcel11sを通じてそれぞれのセルの端子に接続された2つのASIC16および17を備えるセル監視ブロック15によって、測定される。

#### 【0042】

本発明のこの実施形態によるシステムの性能を最適化し、バランスング電流を最大化してバランスング時間を短縮するために、フライバックコンバータは、電池管理システム(BMS)内の主マイクロコントローラから制御されることが可能である。このようなマイクロコントローラの一例は、テキサス・インスツルメンツ(Texas Instruments)社製のHERCULES MCU 32ビットARM Cortex R4である。本発明によるシステムおよび方法は、BMS主マイクロコントローラ内で実施されることが可能であるが、代わりに別個のマイクロコントローラ内で実施されることも可能である。制御マイクロコントローラは、図示される実施形態では参照番号18で指定され、シリアル周辺インターフェースSPIを通じてセル監視ブロック15内のASIC16および17と接続されている。

20

#### 【0043】

マイクロコントローラ18は、信号線12を介して正のモジュール電圧Vmod+を示す信号を、信号線13を介して負のモジュール電圧Vmod-を示す信号を、受信する。さらに、マイクロコントローラ18は、信号線11を介してモジュールからの出力電流Imod26を示す信号を受信する。出力電流26は、25で象徴的に示される適切な手段によって測定される。マイクロコントローラ18は、とりわけこれらの信号に基づいて、制御信号20をバランスングシステムの様々な機能ブロックに、すなわち制御信号21、22、23、および24に供給する。

30

#### 【0044】

本発明の図示される実施形態で使用されるこのスイッチドDC/DCコンバータは、「モジュール・トゥ・セル」トポロジーに基づいており、余分な費用をかけ過ぎずに、バランスを取りながら各セルに注入される電流を監視できるようにし、こうしてバランスングプロセスの間に注入される電流を考慮して、より良いSOCを得られるようとする。

40

#### 【0045】

DC/DCコンバータ7は、全てのモジュールセル(図1に示される実施形態ではC1からC10)から電力を抽出し、他のセルとのバランスが取れるまで最も放電したセルのバランスを取るために、制御された定電流(CC)を注入する、絶縁フライバックコンバータである。最も放電したセルとの絶縁フライバックコンバータの接続は、リレーのアレイ4によって行われ、危険な短絡を回避するために同時に1つしか切り替えられない。

#### 【0046】

本発明の実施形態で使用可能なDC/DCコンバータの設計は、以下にある程度詳細に

50

記載される。コンバータは上述のように、望ましければ、たとえばHERCULESマイクロコントローラに実装されることが可能である。

#### 【0047】

コンバータ制御は、バランスング電流を測定する（および制御用のフィードバックループを閉じる）ためのアナログ信号と、PWMデジタル出力と、バランスングを必要とするセルにDC/DCコンバータを接続するスイッチを作動させるためのセルごとのデジタル出力（外部デマルチプレクスシステムを用いて構築）とを必要とする。

#### 【0048】

本発明の一実施形態によるスイッチドDC/DCコンバータは、「モジュール・トゥ・セル」トポロジーに基づいており、限られた余分な費用をかけずに、バランスを取りながら各セルに注入される電流を監視できるようにし、こうしてバランスングプロセスの間に注入される電流を考慮して、より最適な充電状態（SOC）を得られるようにする。

10

#### 【0049】

図2を参照すると、たとえば図1に示されるような、各々が多数のセルを備える、たとえば1つ以上のモジュールを備える電池に適用可能な、本発明によるセルバランスング方法の一実施形態を示すフローチャートが示されている。

#### 【0050】

バランスング方法はステップ27で開始され、任意の電池モジュールがステップ28で選択される。ステップ29において、充電プロセスが行われているか否かが判断され、これが該当する場合には方法はステップ30に進み、これにより、任意のモジュール、すなわちステップ28で選択されたモジュール内のセル間にアクティブセルバランスングを適用する。

20

#### 【0051】

充電の終了に向けて、任意のモジュールの1つまたは少数のセルがSOCまたはセル電圧の所定の上限 $L_u$ を超えて充電されることがあるかも知れない。ステップ31でこれが検出された場合、図2に示される方法の実施形態にしたがって、このセルまたはこれらのセルは所定の上限 $L_u$ を超えて充電され、必要とされる値までその充電を減少させるために、ステップ32においてこれらのセルにパッシブセルバランスングが適用される。ステップ31において上限を超えたセルがないと判断された場合には、プロセスはステップ33に進み、そこで充電すべきさらなるモジュールが電池内に存在するか否かが判断され、その後、次のモジュールに対して上記のプロセスが繰り返される。

30

#### 【0052】

電池内にさらなるモジュールが存在しない場合、モジュール間の電圧のSOCの間にアンバランスがあるか否かがステップ34で判断される。これが該当する場合、プロセスは、たとえば（パッシブバランスングの場合）図1に示される抵抗器8によって、モジュール間にパッシブまたはアクティブバランスングのいずれかを適用する。このモジュール間バランスングは、モジュール間で必要とされるバランスが得られるまで進められ、その後、プロセスはステップ38で終了する。

#### 【0053】

機能ブロック36において、上限 $L_u$ が判断され、39で示されるように、機能ステップ31に供給されることが可能である。

40

#### 【0054】

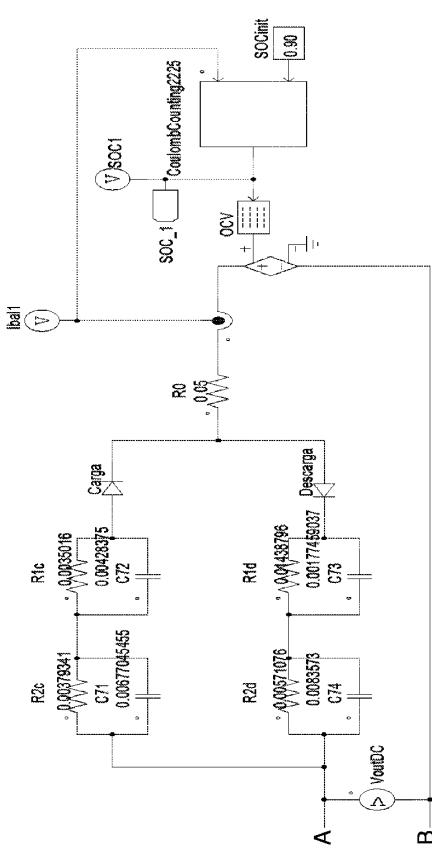

図3aおよび図3bを参照すると、絶縁フライバックコンバタ回路（MOSFET、フィルタ、絶縁変圧器など）の一実施形態の概略回路図が示されており、フライバック制御ブロックならびにセルC1、C2、およびC3がフライバックコンバタの出力に接続されている。なお、本発明によれば、実際に図示されている3つ以外の数のセルが使用されてもよいことに留意されたい。回路図には、回路全体に沿って電流および電圧を測定するために使用される、その他の部品もある。ある特定のセルの不均衡状態を補正するために必要とされるエネルギーは、モジュールの全てのセルから得られ、その後その特定のセルに注入される。

50

**【 0 0 5 5 】**

D C / D C コンバータトポロジーは、絶縁されたバックコンバータのように動作する、絶縁フライバックコンバータである。P W M 信号は、D C / D C コンバータの出力電流および電圧の制御を可能にする。

**【 0 0 5 6 】**

本発明のシステムおよび方法の目的は、モジュールを構成するセルの完全なアレイから抽出された、たとえば 1 A の制御された電流で、不均衡なセルを再充電することである。

**【 0 0 5 7 】**

後に H E R C U L E S マイクロコントローラに実装される制御アルゴリズムを設計するために、シミュレーション回路図は、出力電流フィードバック測定のフィルタリングおよび離散化を含む。これは、アナログ段およびアナログデジタルコンバータ（A D C）が実際の電子システム内で動作する方法と似ている。また、フライバック制御ブロックは、H E R C U L E S マイクロコントローラ内で動作するよう期待される通りに動作するが、これは、アナログ信号のサンプル取得ごとに制御コードが 1 回実行されることを意味する。

10

**【 0 0 5 8 】**

サンプリング周波数は、以下に示されるシミュレーションの結果において、2 k H z に設定されており、A D C の分解能は 12 ビットである。出力電流は、シャント抵抗器（この例では 50 m V）および以下に示される結果では 50 倍の固定ゲインを有する計装用増幅器（たとえば、I N A 2 8 2）を使用して感知される。P W M スイッチング周波数は 1 0 0 k H z に設定されているが、他のスイッチング周波数もまた使用可能である。

20

**【 0 0 5 9 】**

図 4 を参照すると、特定のセルをその初期の不均衡状態から所望のバランスの取れた状態まで再充電できるようにする制御アルゴリズムを実装する、フライバック制御ブロックが示されている。スタート・ストップおよび電流注入を制御するために必要なパラメータは：

- ・所望の出力電流：1 A に固定（I o u t）

- ・出力電流フィードバック：I o u t D C

- ・セルS O C：S O C \_ 1

- ・所望の最終S O C：F i n a l \_ S O C

**【 0 0 6 0 】**

30

出力電流を制御するためのP S I M ( f s ) およびP I レギュレータパラメータ ( K p 、K i ) のシミュレーションプロセスに関するフライバック制御ブロックには、その他の制御パラメータがある。フライバック制御ブロックは、H E R C U L E S マイクロコントローラに容易に移植できるようにするために一実施形態ではC コードでプログラムされているが、他のプログラム言語が代わりに使用されることは理解される。

**【 0 0 6 1 】**

「f l y b a c k \_ C o n t r o l」ブロックに実装された制御アルゴリズム（P I コントローラ）の最も重要な部分が、以下に示される。

40

50

## 【表 1】

```

...

if(SOC<=Final_SOC) // Final_SOCに達するまでアルゴリズムを実行

{

// 1msまで何もしない。uControllerの初期化状態をシミュレート

if (Tdis <= 0.001)

{

Iout = 0;

IoutDC_s = 0;

Tdis = 0;

Kp = 0;

Ki = 0;

err = 0;

err_k1 = 0;

Int = 0;

Out = 0;

PI_out = 0;

y1= 0;

y2 = 0;

y3 = 0;

y4 = 0;

}

else // フライバックPI制御アルゴリズム

{

Iout=x1; // 出力電流目標

IoutDC_s=x2; // 離散出力電流フィードバック

// PIコントローラ

err=Iout-IoutDC_s; // 誤差計算

Int=Int+(err/fs); // 積分計算

Out=Kp * err+Ki * Int; // PI結果

PI_out = Out;

// 過剰なPWMデューティサイクルまたは0未満を回避するための飽和

if (PI_out >= 0.44)

{

PI_out = 0.44;

sat = 1;

}

else if (PI_out <= 0)

{

PI_out = 0;

sat = 2;

}

else sat=0;

y1 = PI_out;

y2 = err;

y3 = sat;

y4 = 1;

} // end if

} // end if SOC

else

{

y1 = 0;

y4 = 0;

}

```

10

20

30

40

## 【0062】

Hercules μC は、モジュール全体について PWM 信号、スイッチ（リレー）選択信号、可能なパッシブバランシング起動信号 / 信号？を生成し、制御ループを閉じるためにバランシング出力電流信号のフィードバックを受信する。

## 【0063】

PWM 信号は、選択されたセルを再充電するための所望の量（大きさ）の電流を発生させるために、絶縁フライバック DC / DC コンバータを制御？する。

## 【0064】

図 5a から図 5g を参照すると、Hercules μC 評価ボードとのインターフェ

ース、ならびに出力電流およびセル電圧測定演算増幅器に必要な絶縁電圧（5Vなど）を含む、異なる電源レベルを生成するために必要な電源も、示されている。図2の回路図はまた、本発明のこの実施形態に存在する全ての信号の異なる電圧レベルを管理するために必要なインターフェースコンポーネントも示している。アナログおよびデジタル信号は、異なる組み合わせおよび構成との互換性を確保するために、μCにおいて異なるピンに送られることが可能である。

#### 【0065】

本発明のこの実施形態では、T1 BQ76PL536EVMとの接続はSPIバスおよびいくつかのデジタル信号で行われ、これはコネクタJ1およびJ2内に存在する。

#### 【0066】

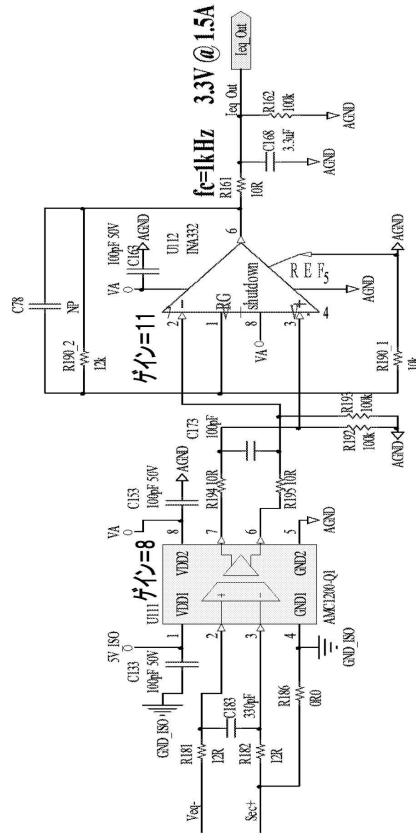

図6aから図6eを参照すると、デュアルスイッチ絶縁フライバックコンバータが示されている。両方のMOSFETのPWM信号を管理するために、IC U114（UCC27201）は、ハイおよびローゲートドライバとして機能し、μCからPWM信号を受信する。

10

#### 【0067】

マイクロコントローラに電流信号を送るために使用される電流センサは、この実施形態では、25mシャント抵抗器と2つのアナログ増幅器との組み合わせである。チェーン内の1つ目は、AMC1200-Q1である。これは8倍の固定ゲインを有する平衡絶縁増幅器であり、TMV-1205SHI絶縁DC/DCコンバータによって5Vで電力供給される。この絶縁増幅器のバランス出力は、INA332によって再び増幅される（電流測定では11倍、電圧測定では5倍）。両方の信号は、eq\_OutおよびVeq\_OutポートのHERCULES μC ADC入力に与えられる。モジュール電圧もまた、抵抗器分割器ネットワークによって測定され、VmodポートのuCに与えられる。

20

#### 【0068】

本発明のこの実施形態、および可能であればさらなる実施形態においても、36Vから72Vの間の入力電圧で動作するフライバックコンバータ用のウルト（Wurth）社WE750312503絶縁変圧器が使用される。選択されたトポロジーはデュアルスイッチフライバックであり、MOSFETの基準はSTN2NF10である。導電損失を低減するために、その低Vfのため出力ダイオードD19（PMEG3030EP）が選択されている。

30

#### 【0069】

図7aから図7gを参照すると、2つ以上のセル間の短絡を招く、セルの異なる部分に2つのリレーが同時に接続されることを回避するために、デマルチプレクサが設けられたリレー選択回路の一実施形態が示されている。単一のセルをフライバック出力に接続するリレーの選択は、SN74HC238Dデマルチプレクサに基づいて論理回路で行われる。このようにして、単一のリレーのみが同時に起動され、セル間の危険な短絡を回避することが保証される。最後に、リレーは、リレーコイルの起動を管理するULQ2003Aダーリントンアレイによって駆動される。

#### 【0070】

最後の2つのリレー（RLY17およびRLY18）は、この実施形態において、パッシブバランスングを可能にするために単一セルまたはモジュール全体と抵抗器を直列に接続するために使用され、こうしてハイブリッドバランスングプロトタイプを得る。このアプリケーション向けに選択されたリレーはIMR6である。

40

#### 【0071】

##### ソフトウェア設計

HERCULES μCは、以下の周辺機器を使用して、フライバックコンバータを制御するために構成およびプログラムされている。

- ・リレーを制御する論理回路を管理するための汎用入出力（GPIO）ピン。

- ・出力電流を測定するためのアナログデジタルコンバータ（ADC）モジュール。

- ・制御アルゴリズムの内部割込を生成するためのハイエンドタイマ（HET）モジュ

50

ル。

- ・ PWM 信号を生成するための拡張パルス幅変調器 ( e PWM ) モジュール。

#### 【 0 0 7 2 】

$\mu$ C 周辺機器は、以下のように構成されている。

G I O :     ・ポート A ( A 5 、 C 2 、 C 1 、 E 1 、 A 6 、 B 5 、 H 3 、 M 1 )

A D C :     ・A D R E F H I を選択するためのジャンパ J 8 、 3 . 3 V

・ピン A D C 1 I N 2 ( V 1 8 )

・トリガ H E T 1 8

・分解能 12 ビット

・サンプル時間 1  $\mu$ s

H E T :     ・ピン H E T 1 8 ( E 1 8 )

・P W M 1

・時間 5 0 0  $\mu$ s

E T P W M :     ・時間 1 0 0 k H z     ・ピン E T P W M 6 B ( P 2 )

#### 【 0 0 7 3 】

e PWM モジュールを用いて、 H E R C U L E S  $\mu$ C は、フライバックコンバータを制御できる PWM 信号を生成する。 H E T モジュールを用いて、 2 k H z などの適切な周波数で A D C の変換をトリガするための信号が生成され、これによって電流センサの測定値を捕捉する。  $\mu$ C は、制御ループを閉じるために電流センサからアナログ信号を受信し、 P I コントローラとして機能する。ポート A の G P I O を使用して、  $\mu$ C は、再充電すべきセルを選択する。望ましければ、  $\mu$ C は、 1 つのセルまたはモジュール全体のパッシブバランシングも可能にする。

#### 【 0 0 7 4 】

1 A の固定および制御された電流で 1 つのセルを充電するデュアルスイッチフライバックコンバータを使用して、試験が行われた。アクティブバランシング回路のコアは、絶縁フライバックコンバータである。フライバックコンバータは、 PWM 信号を有する H E R C U L E S  $\mu$ C によって制御され ( E T P W M 6 B ピン ) 、制御ループは、出力電流に対応するアナログ信号によって供給される ( A D 1 I N 2 ピン ) 。

#### 【 0 0 7 5 】

H E R C U L E S  $\mu$ C は、 G I O A ポートに取り付けられた論理回路により、再充電されなければならないセルを選択することができる。 G I O A 0 から G I O A 3 までの配線は、 1 から 1 6 までのセルを選択するために使用され、 G I O A 5 は 3 . 3 V から 5 V のバッファからの出力をイネーブルするために使用され、 G I O A 4 は、デマルチプレクサの出力をイネーブルするために使用される。イネーブル信号は両方ともアクティブロー信号である。

#### 【 0 0 7 6 】

セルが選択されると、  $\mu$ C は、選択されたセルを 1 A の速度で再充電するために、フライバックコンバータの PWM 信号を制御し始める。これらの試験で使用されるセルモデルは、 K o k a m 社の S L P B 9 0 2 5 5 2 5 5 H である。

#### 【 0 0 7 7 】

バランシング試験中に行われた測定は、設計された回路および制御コードが、選択されたセルに注入される電流の量を制御できることを示している。

#### 【 0 0 7 8 】

出力電流値の精度は、  $\pm$  1 . 5 % である。

#### 【 0 0 7 9 】

フライバックコンバータの電力変換効率は、ほとんどの入出力条件において 8 2 . 5 % を超え、入力電圧が約 5 5 V のときに約 8 7 . 5 % の効率ピークに達する。

#### 【 0 0 8 0 】

約 1 A の速度で 1 つのセルを放電するための 1 つの 4 抵抗器 ( 5 W ) 、および約 1 A の速度で 1 6 セルモジュール全体を放電するための 1 つの 6 8 抵抗器 ( 1 0 0 W ) を接

10

20

30

40

50

続することによって、パッシブバランシングも試験された。異なる抵抗値が使用され得ること、ならびに抵抗器以外の手段によってパッシブバランシングが実行され得ることは、理解される。

【0081】

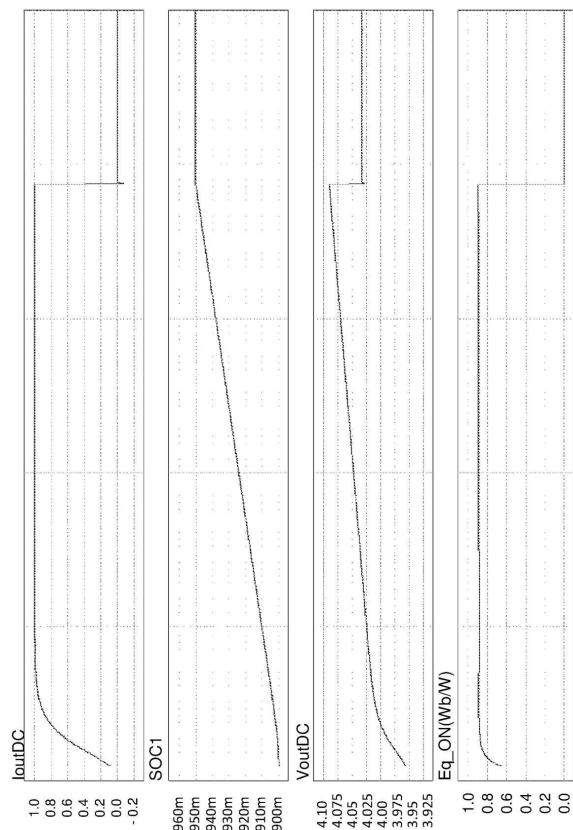

シミュレーション結果

16セルおよび8セルモジュールのPSIMシミュレーションの結果が、以下に示される。

【0082】

図8を参照すると、90%SOCから95%SOCに移行する必要がある1つのセルのバランシングプロセスのシミュレーションで得られた結果が示されている。フライバックの入力電圧は64.45Vであり、15個のセルがSOC95%で充電されて1つのセルが90%で充電されている16個のセルに相当する。この最後のセルが、バランシングされるセルである。

10

【0083】

電流「IoutDC」は、1Aに達するまで増加し、その後SOCが95%の充電に達するまで一定のままで、その後停止する。

【0084】

時間に対するSOC(SOC\_1)およびセル電圧(VoutDC)も示されている。

【0085】

最後に、図8の下のグラフは、フライバックコンバータがONになっている間の、導電損失を考慮したシミュレーションにおける電力変換効率を示す。このシミュレーションでの効率の値は89%である。

20

【0086】

図9を参照すると、90%SOCから95%SOCまで充電される必要がある1つのセルのバランシングプロセスのシミュレーションで得られた結果が示されている。フライバックの入力電圧は32.18Vであり、7つのセルが95%SOCで充電されて1つのセルが90%で充電されている8つのセルに相当する。この最後のセルが、バランシングされるセルである。残りの信号は、図8に示される結果と同じである。

【0087】

要約すると、図8および図9に示されるグラフから、本発明の一実施形態による制御されたフライバック電源は、そのSOCが所望の値に達するまで1Aの定電流で特定のセルを再充電できることがわかる。

30

40

50

【図面】

【 図 1 】

【図3(a)】

【图2】

【図3(b)】

**Fig. 3(b)**

【図4】

Fig. 4

Fig. 5(a)

10

【図5(b)】

Fig. 5(b)

【図5(c)】

20

30

40

50

【図 5 (d)】

Fig. 5(d)

【図 5 (e)】

Fig. 5(e)

【図 5 (f)】

Fig. 5(f)

【図 5 (g)】

Fig. 5(g)

【図6(a)】

【図6(b)】

**Fig. 6(a)**

【図6(c)】

**Fig. 6(c)**

【図6(d)】

【図6(e)】

### 【図7(a)】

【図7(b)】

セルコネクタ

【図7(c)】

Fig. 7(c)

【図 7 (d)】

【図 7 (e)】

【図 7 (f)】

Fig. 7(f)

【図 7 (g)】

表示LED

【図8】

【図9】

10

20

30

40

50

---

フロントページの続き

スペイン国、ヴァレンシア、パテルナ、ファン デ ラ シエルヴァ アベニュー、24

(72)発明者 イーオピス、カルロス ブラスコ

スペイン国、ヴァレンシア、パテルナ、ファン デ ラ シエルヴァ アベニュー、24

(72)発明者 トルモ、ハヴィエル モンレアル

スペイン国、ヴァレンシア、パテルナ、ファン デ ラ シエルヴァ アベニュー、24

(72)発明者 ヴェステイン、カール ラグナール

スウェーデン国、セドラ サンドビー、スカッテベルガ 1422

審査官 田中 慎太郎

(56)参考文献 特開平10-032936(JP,A)

特開2011-072153(JP,A)

特開2005-151720(JP,A)

(58)調査した分野 (Int.Cl., DB名)

H02J 7/00 - 7/12

7/34 - 7/36

H01M 10/42 - 10/48