## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-92169 (P2006-92169A)

最終頁に続く

(43) 公開日 平成18年4月6日 (2006. 4.6)

| (51) Int.C1. |       | FI              |               |        |     |         |      | テーマコード (参考) |        |  |

|--------------|-------|-----------------|---------------|--------|-----|---------|------|-------------|--------|--|

| G06F         | 12/00 | (2006.01)       | GO6F          | 12/00  | 0 5 | 60A     |      | 5B005       |        |  |

| G06F         | 3/06  | (2006.01)       | GO6F          | 12/00  | 0 5 | 60B     |      | 5B035       |        |  |

| G06F         | 3/08  | (2006.01)       | GO6F          | 12/00  | 0 5 | 97U     |      | 5B060       |        |  |

| G06F         | 12/08 | (2006.01)       | GO6F          | 3/06   | 6 3 | 3 O 1 N |      | 5B065       |        |  |

| G06K         | 19/07 | (2006.01)       | GO6F          | 3/08   | 3   | С       |      |             |        |  |

|              |       |                 | 審査請求 未        | 詩求     | 請求項 | 夏の数 5   | ΟL   | (全 17 頁)    | 最終頁に続く |  |

| (21) 出願番号    |       | 特願2004-275651 ( | P2004-275651) | (71) 出 | 人願と | 0000030 | 178  |             |        |  |

| (22) 出願日     |       | 平成16年9月22日(     |               | `      |     | 株式会社    | 土東芝  |             |        |  |

|              |       |                 |               |        |     | 東京都海    | 巷区芝河 | 甫一丁目1番1     | 1号     |  |

|              |       |                 |               | (74) 代 | 过理人 | 1000838 | 806  |             |        |  |

|              |       |                 |               |        |     | 弁理士     | 三好   | 秀和          |        |  |

|              |       |                 |               | (74) 代 | 建人  | 1001007 | 12   |             |        |  |

|              |       |                 |               |        |     | 弁理士     | 岩▲岬  | 奇▼ 幸邦       |        |  |

|              |       |                 |               | (74) 代 | 过理人 | 1001009 | 129  |             |        |  |

|              |       |                 |               |        |     | 弁理士     | 川又   | 澄雄          |        |  |

|              |       |                 |               | (74) 代 | 过理人 | 1001087 | 07   |             |        |  |

|              |       |                 |               |        |     | 弁理士     | 中村   | 友之          |        |  |

|              |       |                 |               | (74) 代 | (理人 | 1000955 | 00   |             |        |  |

|              |       |                 |               |        |     | 弁理士     | 伊藤   | 正和          |        |  |

|              |       |                 |               | (74) 代 | (理人 | 1001012 | 247  |             |        |  |

|              |       |                 |               |        |     | 弁理士     | 高橋   | 俊一          |        |  |

(54) 【発明の名称】メモリコントローラ、メモリ装置及びメモリコントローラの制御方法

## (57)【要約】

【課題】不揮発性半導体メモリに対して、上位装置のデータ書き込み単位が小さい場合においても書き込み性能を向上する。

【解決手段】ホスト機器20に接続され、第1のデータ書き込み単位を有する受信データを受信するホストインタフェース6と、第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する不揮発性半導体メモリ3に接続され、第1のデータ書き込み単位を有する書き込みデータを送信するメモリインタフェース5と、メモリインタフェース5を介して不揮発性半導体メモリ3の一時書き込みブロック12に受信データを書き込み、ホストインタフェース6が受信した複数の受信データが第2のデータ書き込み単位のエリアデータに達した際に、対応する書き込みデータを一時書き込みブロック12から読み出し、一時書き込みブロック12とは別のターゲットブロック11に書き込む中央演算処理装置8とを備えるメモリコントローラ4。

【選択図】図1

#### 【特許請求の範囲】

## 【請求項1】

ホスト機器に接続され、前記ホスト機器から第1のデータ書き込み単位を有する受信データを受信するホストインタフェースと、

前記第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する不揮発性半導体メモリに接続され、前記不揮発性半導体メモリに対して前記第1のデータ書き込み単位を有する書き込みデータを送信するメモリインタフェースと、

前記メモリインタフェースを介して前記不揮発性半導体メモリの一時書き込みブロックに前記受信データを前記書き込みデータとして書き込み、前記ホストインタフェースが受信した複数の受信データが前記第2のデータ書き込み単位のエリアデータに達した際に、前記エリアデータに対応する書き込みデータを前記一時書き込みブロックから読み出し、読み出された前記書き込みデータを含む前記エリアデータを前記一時書き込みブロックとは別のターゲットブロックに書き込む中央演算処理装置

とを備えることを特徴とするメモリコントローラ。

## 【請求項2】

ホスト機器に接続され、前記ホスト機器から第1のデータ書き込み単位を有する受信データを受信するホストインタフェースと、

前記第1のデータ書き込み単位を有する受信データを記憶し、かつランダムアクセス可能な不揮発性キャッシュメモリと、

前記第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する不揮発性半導体メモリに接続されるメモリインタフェースと、

前記ホストインタフェースを介して前記不揮発性キャッシュメモリに前記受信データを書き込みデータとして書き込み、前記ホストインタフェースが受信した複数の受信データが前記第2のデータ書き込み単位のエリアデータに達した際に、前記エリアデータに対応する書き込みデータを前記不揮発性キャッシュメモリから読み出し、読み出された前記書き込みデータを含む前記エリアデータを、前記メモリインタフェースを介して、ページ単位で前記不揮発性半導体メモリのターゲットブロックに書き込む中央演算処理装置

とを備えることを特徴とするメモリコントローラ。

## 【請求項3】

第1のデータ書き込み単位を有する送信データを送信するホスト機器に接続されるメモリ装置であって、

ー時書き込みブロックと、前記一時書き込みブロックとは別のターゲットブロックとを備え、前記第 1 のデータ書き込み単位よりも大きな第 2 のデータ書き込み単位を有する不揮発性半導体メモリと、

前記ホスト機器に接続され,前記第1のデータ書き込み単位を有する受信データを受信するホストインタフェースと、前記不揮発性半導体メモリに接続され,前記不揮発性半導体メモリに対して前記第1のデータ書き込み単位を有する書き込みデータを送信するメモリインタフェースと、前記メモリインタフェースを介して前記不揮発性半導体メモリの前記一時書き込みブロックに前記受信データを前記書き込みデータとして書き込み,前記ホストインタフェースが受信した複数の受信データが前記第2のデータ書き込み単位のエリアデータに達した際に,前記エリアデータに対応する書き込みデータを前記一時書き込みブロックから読み出し,読み出された前記書き込みデータを含む前記エリアデータを前記ターゲットブロックに書き込む中央演算処理装置とを備えるメモリコントローラ

とを備えることを特徴とするメモリ装置。

#### 【請求項4】

ホストインタフェースにおいて、ホスト機器から第1のデータ書き込み単位を有する受信データを受信するステップと、

メモリインタフェースにおいて、前記第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する不揮発性半導体メモリへ、前記第1のデータ書き込み単位を有する書き込みデータを送信するステップと、

10

20

30

40

30

40

50

前記メモリインタフェースを介して前記不揮発性半導体メモリの一時書き込みブロック に前記受信データを前記書き込みデータとして書き込むステップと、

前記ホストインタフェースが受信した複数の受信データが前記第2のデータ書き込み単位のエリアデータに達した際に、該エリアデータに対応する書き込みデータを前記一時書 き込みブロックから読み出すステップと、

読み出された前記書き込みデータを含む前記エリアデータを前記不揮発性半導体メモリ内の前記一時書き込みブロックとは別のターゲットブロックに書き込むステップ

とを備えることを特徴とするメモリコントローラの制御方法。

#### 【請求項5】

ホストインタフェースにおいて、ホスト機器から第1のデータ書き込み単位を有する受信データを受信するステップと、

メモリインタフェースにおいて、前記第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する不揮発性半導体メモリへ書き込みデータを送信するステップと

前記ホストインタフェースを介してメモリコントローラ内の不揮発性キャッシュメモリ に前記受信データを前記書き込みデータとして書き込むステップと、

前記ホストインタフェースが受信した複数の受信データが前記第2のデータ書き込み単位のエリアデータに達した際に、該エリアデータに対応する書き込みデータを前記不揮発性キャッシュメモリから読み出すステップと、

読み出された前記書き込みデータを含む前記エリアデータを、前記メモリインタフェースを介して、前記の不揮発性半導体メモリのターゲットブロックに書き込むステップ とを備えることを特徴とするメモリコントローラの制御方法。

## 【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、メモリコントローラ及びその制御方法に関し、特にNAND型フラッシュメモリ等の不揮発性半導体記憶装置を内蔵したメモリカード或いはメモリ装置に関する。

#### 【背景技術】

## [0002]

フラッシュメモリのようなメモリ部品には、それにデータを書き込む場合、一度に書き込めるデータ量が固定されているものがある。また、ファイルシステムを持つコンピュータのような上位装置では、書き込むデータ量の単位がメモリ部品とは別に決まっている。例えば、メモリ部品の書き込み単位が 2 0 4 8 バイト、上位装置の書き込み単位が 5 1 2 バイトのように、メモリ部品側の書き込み単位の方が上位装置 (メモリカードを利用する装置:ホスト)の書き込み単位より大きい場合がある。

#### [0003]

このように大きい書き込み単位のメモリ部品を内蔵したメモリカード等のメモリ装置は、上位装置からの書き込み指示に対応するため、小さい単位のデータ書き込みでも処理で きなければならない。

## [0004]

上位装置のデータ書き込み単位が小さく(例えば512バイト)、不揮発性メモリ部品のデータ書き込み可能単位が大きい(例えば2048バイト)状態において、上位装置から不揮発性メモリ部品に小さい単位のデータD1を書き込み、そのデータ書き込みが完了した後、データD1が書き込まれたページの次のエリア位置に小さい単位のデータD2を書く場合を考える。フラッシュメモリには、ページを分割してデータを書き込むことが許されていないものがある。この場合、そのフラッシュメモリは、データD1を含むブロックからデータD1以外のデータを新たなブロックにコピーし、その新たなブロックにデータD1,D2を書き込まなければならない。以下では、便宜上、このような処理を「巻き添え引越し」と呼ぶ。この「巻き添え引越し」は書き換えられないデータのコピー動作を伴うため、「巻き添え引越し」が多発すると、メモリ装置の書き込み性能を下げてしまう。し

20

30

40

50

たがって、不揮発性メモリ部品として一般的に使われているフラッシュメモリには、ライト処理に長い時間が掛かるという問題点があった。

[00005]

なお、特許文献1には、メモリコントローラの制御により、ホストからの書き込みデータを、一旦不揮発性メモリに取り込んで処理を行ない、停電等による処理中断後の装置立ち上げの際は、キャッシュメモリに書き戻す、高速書き込み方式が開示されている。

【特許文献1】特開平5-151094号公報

【発明の開示】

【発明が解決しようとする課題】

[0006]

本発明は、大きなデータ書き込み単位を有するNAND型フラッシュメモリ等の不揮発性半導体記憶装置を内蔵したメモリカード或いはメモリ装置において、上位装置のデータ書き込み単位が小さい場合においても書き込み性能を向上できるメモリコントローラ及びその制御方法及びメモリ装置を提供する。

【課題を解決するための手段】

[0007]

本発明の実施の形態の第1の特徴は、(イ)ホスト機器に接続され、ホスト機器から第1のデータ書き込み単位を有する受信データを受信するホストインタフェースと、(ロ)第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する不揮発性半導体メモリに対して第1のデータ書き込み単位を有する不揮発性半導をメモリに対して第1のデータ書き込み単位を有するスを介して不揮発性半導体メモリの一時書き込みブロックに受信データを書き込みデータとして書き込み、ホストインタフェースが受信した複数の受信データが第2のデータ書き込み単位のエリアデータに達した際に、エリアデータに対応する書き込みデータを一時書き込みブロックから読み出し、読み出された書き込みデータを含むエリアデータを一時書き込みブロックとは別のターゲットブロックに書き込む中央演算処理装置(CPU)とを備えるメモリコントローラであることを要旨とする。

[00008]

本発明の実施の形態の第2の特徴は、(イ)ホスト機器に接続され、ホスト機器から第1のデータ書き込み単位を有する受信データを受信するホストインタフェースと、(ロコンデータ書き込み単位を有する受信データを記憶し、かつランダムアクセス可能な揮発性キャッシュメモリと、(ハ)第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する不揮発性半導体メモリに接続されるメモリインタフェースと、(コンタフェースを介して不揮発性キャッシュメモリに受信データを書き込みデータを書き込みデータを書き込みデータを書き込みデータに達した際に、エリアデータに対応する書き込みデータを不揮発性キャッシュメモリから読み出し、読み出された書き込みデータを含むエリアデータをメモリインタフェースを介して、不揮発性半導体メモリのターゲットブロックに書き込む中央演算処理装置とを備えるメモリコントローラであることを要旨とする。

[0009]

本発明の実施の形態の第3の特徴は、(イ)第1のデータ書き込み単位を有する送信データを送信するホスト機器に接続されるメモリ装置であって、(ロ)一時書き込みブロックとは別のターゲットブロックとを備え、第1のデータ書き込み単位を有する不揮発性半導体メモリと、(ハ)ホスト機器に接続され,第1のデータ書き込み単位を有する受信データを受信するホストインタフェースと、不揮発性半導体メモリに接続され,不揮発性半導体メモリに対して第1のデータ書き込み単位を有する書き込みデータを送信するメモリインタフェースと、メモリインタフェースを介して不揮発性半導体メモリの一時書き込みブロックに受信データを書き込みデータとして書き込み,ホストインタフェースが受信した複数の受信データが第2のデータ書き込み単位のエリアデータに達した際に,エリアデータに対応する書き込

30

40

50

みデータを一時書き込みブロックから読み出し、読み出された書き込みデータを含むエリアデータをターゲットブロックに書き込む中央演算処理装置とを備えるメモリコントローラとを備えるメモリ装置であることを要旨とする。

#### [0010]

本発明の実施の形態の第4の特徴は、(イ)ホストインタフェースにおいて、ホスト機器から第1のデータ書き込み単位を有する受信データを受信するステップと、(ロ)メモリインタフェースにおいて、第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有する書き込みずータ書き込み単位を有する書き込みデータを送信するステップと、(ハ)メモリインタフェースを介して不揮発性半導体メモリの一時書き込みデータとして書き込みデータと、(コ)ホストインタフェースが受信した複数の受信データが第2のデータ書き込み単位のエリアデータに達した際に、エリアデータに対応する書き込みデータを含むエリアデータをアデータに強いる。まさいる。

#### [0011]

#### 【発明の効果】

## [0012]

本発明により、大きなデータ書き込み単位を有するNAND型フラッシュメモリ等の不揮発性半導体記憶装置を内蔵したメモリカード或いはメモリ装置において、上位装置のデータ書き込み単位が小さい場合においても書き込み性能を向上できるメモリコントローラ及びその制御方法を提供することができる。

# 【発明を実施するための最良の形態】

## [0013]

次に、図面を参照して、本発明の第1及び第3の実施の形態を説明する。以下の図面の記載において、同一又は類似の部分には同一又は類似の符号を付している。又、以下に示す第1及び第2の実施の形態は、この発明の技術的思想を具体化するための装置や方法を例示するものであって、この発明の技術的思想は、構成部品の材質、形状、構造、配置等を下記のものに特定するものでない。この発明の技術的思想は、特許請求の範囲において、種々の変更を加えることができる。

#### [0014]

本発明の第1乃至第3の実施の形態に係るメモリコントローラ及びその制御方法においては、メモリカード等のメモリ装置内において、上位装置からの小さい単位のデータの書き込み指示に対し、データを本来書くべき不揮発性メモリ部品のアドレスに直ぐには書き込まず、不揮発性メモリの他の領域、或いはメモリコントローラ内に配置した不揮発性キャッシュメモリに一時的に書き込んでおき、上位装置から連続的なアドレスへ書き込み指示が送られた場合に、不揮発性メモリ部品の書き込みデータ単位に達したら、不揮発性メモリの他の領域、或いはメモリコントローラ内に配置した不揮発性キャッシュメモリに一時的に書き込んであったデータを本来書き込むべき不揮発性メモリ部品の領域へ書き込む

30

40

50

。この処理により、「巻き添え引越し処理」を減らし、メモリ装置の書き込み性能を向上 する。

#### [0015]

[第1の実施の形態]

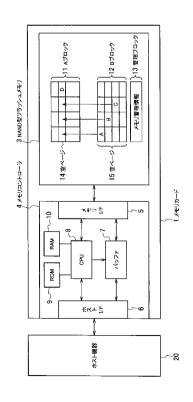

本発明の第1の実施の形態に係るメモリコントローラは、図1に示すように、ホスト機 器 2 0 に 接 続 さ れ 、 ホ ス ト 機 器 2 0 か ら 第 1 の デ ー タ 書 き 込 み 単 位 を 有 す る 受 信 デ ー タ を 受信するホストインタフェース(I/F)6と、第1のデータ書き込み単位よりも大きな 第 2 のデータ書き込み単位を有するNAND型フラッシュメモリ 3 に接続され、NAND 型フラッシュメモリ3に対して第1のデータ書き込み単位を有する書き込みデータを送信 するメモリインタフェース(I/F) 5 と、メモリインタフェース 5 を介してNAND型 フ ラ ッ シ ュ メ モ リ 3 の 一 時 書 き 込 み ブ ロ ッ ク に 受 信 デ ー タ を 書 き 込 み デ ー タ と し て 書 き 込 み、 ホストインタフェース 6 が受信した複数の受信データが第 2 のデータ書き込み単位の エリアデータに達した際に、そのエリアデータに対応する書き込みデータを一時書き込み ブロック(Bブロック)12から読み出し、読み出された書き込みデータを含むエリアデ ータを一時書き込みブロック( B ブロック) 1 2 とは別のターゲットブロック( A ブロッ ク ) 1 1 に書き込む中央演算処理装置(CPU)8とを備える。CPU8は、NAND型 フラッシュメモリ3の管理ブロック13に記憶するメモリ管理情報を読み出して、書き込 みデータのアドレスを決定する。或いは又、後述するように、一時書き込みブロック(B ブロック)12内のページアドレス情報と、ターゲットブロック(Aブロック)11内の 書 き 込 み 先 の ぺ ー ジ ア ド レ ス 情 報 を N A N D 型 フ ラ ッ シ ュ メ モ リ 3 内 の 所 定 の 記 憶 領 域 に 記憶しても良い。

#### [0016]

(メモリ装置)

本発明の第1の実施の形態に係るメモリコントローラ4のメモリカードへの適用例は、図1に示す様に表される。図1は、ホスト機器20とメモリカード1を含む構成を示すブロック図である。ホスト機器20は、接続されるメモリカード1に対してアクセスを行うためのハードウェア及びソフトウェア(システム)を備えている。

[0017]

メモリカード1は、ホスト機器20に接続されたときに電源供給を受けて動作し、ホスト機器20からのアクセスに応じた処理を行う。このメモリカード1は、本発明の第1の 実施の形態に係るメモリコントローラ4を備える。

[0018]

本発明の第1の実施の形態に係るメモリコントローラ4をメモリカード1等のメモリ装 置へ適用した構成例は、図1を参照して説明すると、第1のデータ書き込み単位を有する 送信データを送信するホスト機器20に接続されるメモリ装置であって、一時書き込みブ ロック(Bブロック)12と、一時書き込みブロック(Bブロック)12とは別のターゲ ットブロック ( A ブロック ) 1 1 とを備え、第 1 のデータ書き込み単位よりも大きな第 2 の デ ー タ 書 き 込 み 単 位 を 有 す る N A N D 型 フ ラ ッ シ ュ メ モ リ 3 等 の 不 揮 発 性 半 導 体 メ モ リ と、 ホスト機 器 2 0 に 接 続 さ れ , 第 1 の デ ー タ 書 き 込 み 単 位 を 有 す る 受 信 デ ー タ を 受 信 す るホストインタフェース 6 と、NAND型フラッシュメモリ 3 に接続され,NAND型フ ラッシュメモリ3に対して第1のデータ書き込み単位を有する書き込みデータを送信する メモリイン タフェース 5 と、メモリイン タフェース 5 を介 して N A N D 型 フラッシュメモ リ 3 の 一 時 書 き 込 み ブ ロ ッ ク ( B ブ ロ ッ ク ) 1 2 に 受 信 デ ー タ を 書 き 込 み デ ー タ と し て 書 き 込 み , ホ ス ト イ ン タ フ ェ ー ス 6 が 受 信 し た 複 数 の 受 信 デ ー タ が 第 2 の デ ー タ 書 き 込 み 単 位のエリアデータに達した際に,エリアデータに対応する書き込みデータを一時書き込み ブロック( B ブロック) 1 2 から読み出し,読み出された書き込みデータを含むエリアデ ータをターゲットブロック( A ブロック) 1 1 に書き込む中央演算処理装置 8 とを備える メモリコントローラ4とを備える。

[0019]

NAND型フラッシュメモリ3は、例えば、消去時の消去ブロックサイズ(消去単位の

20

30

40

50

プロックサイズ)が 2 5 6 k バイトに定められている不揮発性メモリである。この N A N D 型フラッシュメモリ 3 は、例えば 0 . 0 9 μ m プロセス技術を用いて製作される。即ち、 N A N D 型フラッシュメモリ 3 のデザインルールは、 0 . 1 μ m 未満となっている。また、メモリカード 1 を実用上有効な製品とするためには、 N A N D 型フラッシュメモリ 3 の記憶容量は 1 G バイト以上であることが望ましい。

- [0020]

- (メモリコントローラ)

本発明の第1の実施の形態に係るメモリコントローラ4は、CPU8及びROM9の他に、メモリインタフェース5、ホストインタフェース6、バッファメモリ7、及びRAM10を搭載している。このメモリコントローラ4は、NAND型フラッシュメモリ3内部の物理状態(何処の物理ブロックアドレスに、何番目の論理セクタアドレスデータが含まれているか、或いは、何処のブロックが消去状態であるか)を管理するものとして構築されている。

[0021]

メモリ I / F 5 は、メモリコントローラ 4 と N A N D 型 フラッシュメモリ 3 との間のインタフェース処理を行うものである。ホスト I / F 6 は、メモリコントローラ 4 とホスト機器 2 0 との間のインタフェース処理を行うものである。

[0022]

バッファメモリ7は、ホスト機器20から送られてくるデータをNAND型フラッシュメモリ3へ書き込む際に、一定量のデータ(例えば1ページ分)を一時的に記憶したり、NAND型フラッシュメモリ3から読み出されるデータをホスト機器20へ送り出す際に、一定量のデータを一時的に記憶したりするものである。

[0023]

CPU8は、メモリカード1全体の動作を制御する。CPU8は、例えば、メモリカード1が電源供給を受けた際に、ROM9の中に格納されている制御プログラム等のファームウェアに従って所定の処理を実行することにより、各種のテーブルをRAM10上で作成したり、ホスト機器20から書き込みコマンド,読み出しコマンド,消去コマンドを受けてNAND型フラッシュメモリ3のNANDメモリセル領域上の該当領域に対するアクセスを実行したり、バッファメモリ7を通じたデータ処理を制御したりする。

[0024]

ROM9は、CPU8により使用される制御プログラム等を格納するメモリである。

[ 0 0 2 5 ]

R A M 1 0 は、 C P U 8 の作業エリアとして使用され、各種のテーブルを記憶するメモ リである。

- [0026]

- (NAND型フラッシュメモリ)

本発明の第1の実施の形態に適用するNAND型フラッシュメモリ3の構造は、図1内に示すように、連続書き込みデータをメモリインタフェース5を介して一時的に記憶する一時書き込みブロック(Bブロック)12と、一時書き込みブロック(Bブロック)12からのエリアデータをページ単位で書き込むターゲットブロック(Aブロック)11と、メモリ管理情報を記憶する管理ブロック13とを備える。14,15は空ページを表示している。

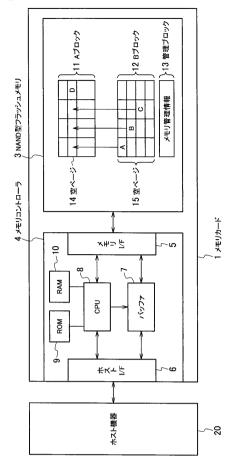

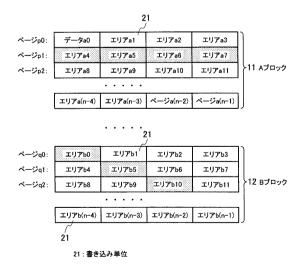

[0027]

図 2 は、フラッシュメモリ(即ち、メモリカード 1 内のNAND型フラッシュメモリ 3 のデータ配置を示している。フラッシュメモリ 3 の各ページは、 2 1 1 2 バイト (5 1 2 バイト分のデータ記憶部 × 4 + 1 0 バイト分の冗長部 × 4 + 2 4 バイト分の管理データ記憶部)を有しており、1 2 8 ページ分が一つの消去単位(即ち、2 5 6 k バイト+8 k バイト)となる。なお、以下の説明においては、便宜上、このフラッシュメモリの消去単位を 2 5 6 k バイトと呼ぶ。NAND型フラッシュメモリ 3 は、フラッシュメモリへのデータ入出力を行うためのデータレジスタ 1 6 を備えている。データ書き込みなどの際には

30

40

50

、データレジスタ16は、フラッシュメモリに対するデータ入出力処理を自身の記憶容量に相当する1ページ分の単位で実行する。データレジスタ16の記憶容量は、2112バイト(2048バイト+64バイト)である。このデータレジスタ16の記憶容量がフラッシュメモリのデータ書き込み単位(第2のデータ書き込み単位)に対応する。このNAND型フラッシュメモリ3のデータ書き込み単位に対し、ホスト機器20のデータ書き込み単位(第1のデータ書き込み単位)は、512バイトである。つまり、NAND型フラッシュメモリ3の1ページには、ホスト機器20のデータ書き込み単位4つ分のデータが格納される。

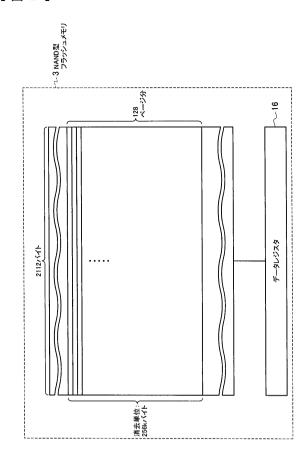

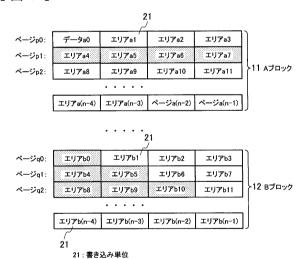

## [0028]

更に又、本発明の第1の実施の形態に適用するNAND型フラッシュメモリ3の構造は、図3及び図5に詳細に説明するように、ホスト機器の書き込み単位(第1のデータ書きこみ単位)21によってそれぞれ4分割された,ページp0,p1,p2,…を備えるターゲットブロック(Aブロック)11と、同様に書き込み単位21によってそれぞれ4分割された,ページq0,q1,q2,…を備える一時書き込みブロック(Bブロック)12とを備える。ターゲットブロック(Aブロック)11と一時書き込みブロック(Bブロック)12は同一のNAND型フラッシュメモリ3のデータ記憶領域を分割して形成することができる。同一のNAND型フラッシュメモリ3ではなく、別々に構成されたNAND型フラッシュメモリ3を用いても良いことは勿論である。例えば、図2において説明した1ページ分のデータ部2048バイトに対しては、4分割することによって512バイトが書き込みページ単位となる。

#### [0029]

ターゲットブロック(Aブロック)11の目的エリアと一時書き込みブロック(Bブロック)12の一時エリアとの対応関係は、例えば図4に示すように、メモリ管理テーブルによって関連付けられている。図4の管理テーブルは、図1に示すメモリ管理情報を記憶する管理ブロック13に格納される。但し、図4に示されるような管理テーブルは必須のものではなく、後述する動作例1において説明するように、ページ情報として、NAND型フラッシュメモリ3内の所定の記憶領域に記憶しても良い。

#### [0030]

ここで、不揮発性半導体メモリとして、NAND型フラッシュメモリ3の例を説明しているが、NOR型、AND型、2トランジスタ/セル型、3トランジスタ/セル型等の他の形式の不揮発性半導体メモリを適用しても良いことは勿論である。また、不揮発性半導体メモリとして、2値記憶に限らず、4値データ等の多値論理を記憶する方式であっても良いことも勿論である。

## [ 0 0 3 1 ]

(メモリコントローラの制御方法)

本発明の第1の実施の形態に係るメモリコントローラ4の制御方法は、図1を参照して説明すると、ホストインタフェース6において、ホスト機器20から第1のデータ書で入りにおいて、ホスト機器20から第1のデータ書で入りにおいて、ホスト機器20から第1のデータを受信するステップと、メモリインタフェース5において型であるNAND型フラッシュメモリ3の不揮発性半導体メモリへのデータ書を込みデータを選信するステップと、メモリインタフェース5を介してNAND型フラッタとデータを選信するステップと、メモリインタフェース5を介しても変数の受信データが第2のオータ書を込みずータを当されたででは、そのエリアデータに達した際に、そのエリアデータが第2のみが第2のよりに達した際に、そのエリアデータが第2のみにででする書き込みが一タを一時書き込みブロック(Bブロック)12から読み出すステップと、読み出でででき込みデータを含むエリアデータをNAND型フラッシュメモリ3内の一時書き込むステック(Bブロック)12とは別のターゲットブロック(Aブロック)11に書き込むステップとを備える。

## [0032]

(動作例1)

上位装置であるホスト機器 2 0 が、本発明の第 1 の実施の形態に係るメモリコントローラ 4 を内蔵するメモリカード 1 に以下の指示を出した時の動作の一例を図 3 を参照して、説明する。

[0033]

(a) ホスト機器 2 0 が、ターゲットブロック(A ブロック) 1 1 内の<エリア a 4 > にデータ D 1 を書くことをメモリコントローラ 4 に指示すると、メモリコントローラ 4 は、そのデータ D 1 を、一時書き込みブロック(B ブロック) 1 2 内の<エリア b 0 > の位置に書き込み、ホスト機器 2 0 の指示を完了する。

[0034]

(b)次に、ホスト機器 2 0 が < エリア a 5 > の位置にデータ D 2 を書くことをメモリコントローラ 4 に指示すると、メモリコントローラ 4 は、データ D 2 を一時的に、一時書き込みブロック (B ブロック) 1 2 内の < エリア b 5 > に書き込む。同時に、一時書き込みブロック (B ブロック) 1 2 内の < エリア b 0 > の位置に書き込まれたデータ D 1 を < エリア b 4 > にコピーして書き込む。

[0035]

(c) 同様に、ホスト機器 2 0 が < エリア a 6 > の位置にデータ D 3 を書くことをメモリコントローラ 4 に指示すると、メモリコントローラ 4 はデータ D 3 を一時的に、一時書き込みブロック(Bブロック) 1 2 内の < エリア b 1 0 > に書き込む。同時に、一時書き込みブロック(Bブロック) 1 2 内の < エリア b 4 > の位置に書き込まれたデータ D 1 を < エリア b 8 > にコピーして書き込み、 < エリア b 5 > の位置に書き込まれたデータ D 2 を < エリア b 9 > にコピーして書き込む。

[0036]

(d)次に、ホスト機器20が<エリアa7>の位置にデータD4を書くことをメモリコントローラ4に指示すると、メモリコントローラ4は、一時書き込みブロック(Bブロック)12内の<エリアb8>,<エリアb9>,<エリアb10>に保持されているデータD1~D3を読み込み、ターゲットブロック(Aブロック)11内の<エリアa4>~<エリアa6>に転送する。

[0037]

( e ) 続いて、データ D 4 をターゲットブロック( A ブロック) 1 1 内の<エリア a 7 > に転送し、<エリア a 4 > ~<エリア a 7 > への書き込みを一回で実施する。

[0038]

動作例1において、一時書き込みブロック(Bブロック)12内のどのページが最新のページであるかのページアドレス情報と、その最新のページに記憶されたデータをターゲットブロック(Aブロック)11内のどこに書き込むかを表す書き込み先のページアドレス情報については、NAND型フラッシュメモリ3内の所定の記憶領域に記憶しておくことができる。例えば、メモリカード1をホスト機器20から急に引き抜いたために電源がオフになり、再度オンする場合、NAND型フラッシュメモリ3内の所定の記憶領域に記憶しておいたページのデータを読み出すことによって、効率的且つ迅速に再起動することができるからである。

[0039]

(動作例2)

上位装置であるホスト機器20が、本発明の第1の実施の形態に係るメモリコントローラ4を内蔵するメモリカード1に以下の指示を出した時の動作の別の例を図5を参照して、説明する。

[0040]

( a ) ホスト機器 2 0 が、ターゲットブロック( A ブロック) 1 1 内の<エリア a 4 > にデータ D 1 を書くことをメモリコントローラ 4 に指示すると、メモリコントローラ 4 は、そのデータ D 1 を、一時書き込みブロック( B ブロック) 1 2 内の<エリア b 0 > の位置に書き込み、ホスト機器 2 0 の指示を完了する。

[0041]

50

40

20

20

30

40

50

( b ) 次に、ホスト機器 2 0 が < エリア a 5 > の位置にデータ D 2 を書くことをメモリコントローラ 4 はデータ D 2 を一時的に、一時書き込みブロック ( B ブロック ) 1 2 内の < エリア b 5 > に書き込む。

[0042]

( c ) 同様に、ホスト機器 2 0 が < エリア a 6 > の位置にデータ D 3 を書くことをメモリコントローラ 4 はデータ D 3 を一時的に、一時書き込みブロック ( B ブロック ) 1 2 内の < エリア b 1 0 > に書き込む。

[0043]

(d)次に、ホスト機器20が<エリアa7>の位置にデータD4を書くことをメモリコントローラ4に指示すると、メモリコントローラ4は、一時書き込みブロック(Bブロック)12内の<エリアb0>,<エリアb5>,<エリアb10>に保持されているデータD1~D3を読み込み、ターゲットブロック(Aブロック)11内の<エリアa4>~<エリアa6>に転送する。

[ 0 0 4 4 ]

( e ) 続いて、データ D 4 をターゲットブロック( A ブロック) 1 1 内の<エリア a 7 > に転送し、<エリア a 4 > ~<エリア a 7 > への書き込みを一回で実施する。

[0045]

動作例2において、ページの部分書き込みを禁止するのは、プログラムディスターブを 防止するためである。即ち、データD2を<エリアb1>に書かずに<エリアb5>に書 いた理由は、データ D 2 の処理の前に < ページ q 0 > の < エリア b 0 > に書き込みを行な っているので、同じ<ページa0>にある<エリアb1>に対して、2回目の書き込みを 行なうことを禁止して、プログラムディスターブを防止することができるからである。或 いは又、データD3についても同様である。即ち、データD3を < エリアb6 > に書かず に < エリア b 1 0 > に書いた理由は、データ D 3 の処理の前に < ページ q 1 > の < エリア b5>に書き込みを行なっているので、同じ<ページ q 1>にある<エリアb6>に対し て、2回目の書き込みを行なうことを禁止して、プログラムディスターブを防止すること ができるからである。一時的に書き込むデータをRAM等の揮発性のメモリに書き込まず に、 N A N D 型 フ ラ ッ シ ュ メ モ リ 3 等 の 不 揮 発 性 メ モ リ に 書 い て い る 理 由 は 、 例 え ば 、 ホ スト機器20がデータD1を書いた後にメモリカード1の電源をオフにし、その後オンに した時でも、データD1を解読することができるからである。また、この状態で、ホスト 機 器 2 0 が メ モ リ カ ー ド 1 に 対 し て 、 < エ リ ア a 5 > の デ ー タ D 2 の 読 み 込 み を 指 示 し た とき、実際には、図4に示すメモリ管理テーブルに従って、メモリコントローラ4が<エ リア b 5 > のデータ D 2 を ホスト機器 2 0 に返すという動作を実現することができるから である。

[0046]

以上のメモリコントローラの制御方法により、ホスト機器 2 0 からの小さいデータ書き込み単位、即ち第 1 のデータ書き込み単位の書き込み指示であって、そのアドレスが連続する場合、「巻き添え引越し」をすることなく、NAND型フラッシュメモリ 3 等の大きなデータ書き込み単位、即ち第 2 のデータ書き込み単位を有する不揮発性メモリ部品にデータを効率よく書き込むことができる。

[0047]

本発明の第1の実施の形態により、大きなデータ書き込み単位を有するNAND型フラッシュメモリ等の不揮発性半導体記憶装置を内蔵したメモリカード或いはメモリ装置において、上位装置のデータ書き込み単位が小さい場合においても書き込み性能を向上できるメモリコントローラ , メモリ装置及びメモリコントローラの制御方法を提供することができる。

[ 0 0 4 8 ]

[第2の実施の形態]

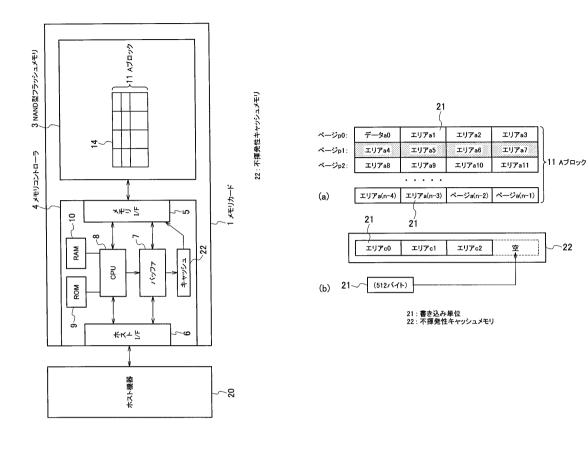

本発明の第2の実施の形態に係るメモリコントローラ4は、図6に示すように、ホスト機器20に接続され、ホスト機器20から第1のデータ書き込み単位を有する受信データ

20

30

40

50

を受信するホストインタフェース6と、第1のデータ書き込み単位を有する受信データを記憶し、かつランダムアクセス可能な不揮発性キャッシュメモリ22と、第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有するNAND型フラッシュメモリ3に接続されるメモリインタフェース5と、ホストインタフェース6を介して不揮発性キャッシュメモリ22に受信データを書き込みデータとして書き込み、ホストインタフェース6が受信した複数の受信データが第2のデータ書き込み単位のエリアデータに達した際に、エリアデータに対応する書き込みデータを不揮発性キャッシュメモリ22から読み出し、読み出された書き込みデータを含むエリアデータを、メモリインタフェース5を介して、NAND型フラッシュメモリ3のターゲットブロック(Aブロック)11に書き込む中央演算処理装置(CPU)8とを備える。

[0049]

図6は、本発明の第2の実施の形態に係るメモリコントローラの模式的ブロック構成図であって、NAND型フラッシュメモリ3と共に全体としてメモリカード1を構成するブロック構成図を示し、図7(a)は、図6におけるNAND型フラッシュメモリ3のデータ構造図、図7(b)は、図6におけるメモリコントローラ4内の不揮発性キャッシュメモリ22のデータ構造図をそれぞれ示す。

[0050]

メモリコントローラ4は、不揮発性キャッシュメモリ22を内蔵している。不揮発性キャッシュメモリ22は、バッファメモリ7とメモリI/F5に接続されている。不揮発性キャッシュメモリ22は、例えば、強誘電体メモリ(FeRAM: Ferroelectric Random Access Memory)や磁気ランダムアクセスメモリ(MRAM: Magnetic Random Access Memory)などのランダムアクセス可能な不揮発性メモリ等で構成している。

[0051]

図6に示すように、NAND型フラッシュメモリ3は、図1に示す例とは異なり、一時書き込みブロック(Bブロック)12は不要である。メモリコントローラ4内に配置された不揮発性キャッシュメモリ22によって、一時書き込みブロック(Bブロック)12と同様の動作を実現しているからである。

[ 0 0 5 2 ]

(メモリ装置)

本発明の第2の実施の形態に係るメモリコントローラ4のメモリカードへの適用例は、図6に示す様に表される。図6は、ホスト機器20とメモリカード1を含む構成を示すブロック図である。ホスト機器20は、接続されるメモリカード1に対してアクセスを行うためのハードウェア及びソフトウェア(システム)を備えている。

[0053]

メモリカード1は、ホスト機器20に接続されたときに電源供給を受けて動作し、ホスト機器20からのアクセスに応じた処理を行う。このメモリカード1は、本発明の第2の 実施の形態に係るメモリコントローラ4を備える。

[0054]

本発明の第2の実施の形態に係るメモリコントローラ4をメモリカード1等のメモリ芸 での での 実施の形態に係るメモリコントロータ書き込み単位を有する は信データを送信するホスト機器20に接続されるメモリ装置であって、ターゲットター でック(Aブロック)11を備え,第1のデータ書き込み単位よりも大きな第2ので がの でっと、第1のデータ書き込み単位を有する NAND型フラッシュメモリ3等の不揮発性半導体メモリと、データを といる が でいる でいる が でいる が でいる が でいる といる が でいる が でいる が でいる が でいる が でいる が でいる でいる が でいる が でいる でいる が でいる でいる が でいる が でいる が でいる が でいる が でいる が でいる か でいる か でいる か でいる か でいる でいる か でいる

に , エリアデータに対応する書き込みデータを不揮発性キャッシュメモリ 2 2 から読み出し , 読み出された書き込みデータを含むエリアデータを , メモリインタフェース 5 を介して , N A N D 型フラッシュメモリ 3 のターゲットブロック ( A ブロック ) 1 1 に書き込む中央演算処理装置 8 とを備えるメモリコントローラ 4 とを備える。

### [0055]

(メモリコントローラの制御方法)

本発明の第2の実施の形態に係るメモリコントローラ4の制御方法は、図6を参照して説明すると、ホストインタフェース6において、ホスト機器20から第1のデータ書き込み単位を有する受信ずるステップと、メモリインタフェース5において、第1のデータ書き込み単位よりも大きな第2のデータ書き込み単位を有するNAND型フラムストインタフェース6を介してメモリコントローラ4内の不揮発性キャッシュメモリ22に受信データを書き込みデータとして書き込むステップと、ホストインタフェース6が受信データに達した際に、エリアデータに対応する書き込みデータを含むエリアデータに達した際に、エップと、読み出された書き込みデータを含むエリアデータを、メモリインタフェース5を介して、NAND型フラッシュメモリ3のターゲットブロック(Aブロック)11に書き込むステップとを備える。

## [0056]

## (動作例)

上位装置であるホスト機器 2 0 が、本発明の第 2 の実施の形態に係るメモリコントローラ 4 を内蔵するメモリカード 1 に以下の指示を出した時の動作の例を図 7 を参照して、説明する。

## [0057]

(a) ホスト機器 2 0 が、図 7 (a) に示すように、ターゲットブロック(A ブロック) 1 1 内の〈エリア a 4 〉にデータ D 1 を書くことをメモリコントローラ 4 に指示すると、メモリコントローラ 4 は、そのデータ D 1 を、図 7 (b) に示すように、メモリコントローラ 4 内部の不揮発性キャッシュメモリ 2 2 のデータ構造内の〈エリア c 0 〉の位置に書き込み、ホスト機器 2 0 の指示を完了する。

#### [0058]

(b)次に、ホスト機器20がターゲットブロック(Aブロック)11内の<エリアa5>の位置にデータD2を書くことをメモリコントローラ4に指示すると、メモリコントローラ4はデータD2を一時的に不揮発性キャッシュメモリ22内の<エリアc1>に書き込む。

## [0059]

( c ) 同様に、ホスト機器 2 0 がターゲットブロック(A ブロック) 1 1 内の<エリア a 6 > の位置にデータ D 3 を書くことをメモリコントローラ 4 に指示すると、メモリコントローラ 4 はデータ D 3 を一時的に不揮発性キャッシュメモリ 2 2 内の<エリア c 2 > に書き込む。

## [0060]

(d)次に、ホスト機器20がターゲットブロック(Aブロック)11内の<エリアa7>の位置にデータD4を書くことをメモリコントローラ4に指示すると、メモリコントローラ4は、不揮発性キャッシュメモリ22内の<エリアc0>~<エリアc2>に保持されているデータD1~D3を読み込み、ターゲットブロック(Aブロック)11内の<エリアa4>~<エリアa6>に転送する。

## [0061]

( e ) 続いて、データ D 4 をターゲットブロック( A ブロック) 1 1 内の < エリア a 7 > に転送し、ターゲットブロック( A ブロック) 1 1 内の < エリア a 4 > ~ < エリア a 7 > への書き込みを一回で実施する。

## [0062]

50

10

20

30

30

40

50

以上の動作例において、不揮発性キャッシュメモリ22内のどのページが最新のページであるかのページアドレス情報と、その最新のページに記憶されたデータをターゲットブロック(Aブロック)11内のどこに書き込むかを表す書き込み先のページアドレス情報については、NAND型フラッシュメモリ3若しくは不揮発性キャッシュメモリ22内の所定の記憶領域に記憶しておくことができる。例えば、メモリカード1をホスト機器20から急に引き抜いたために電源がオフになり、再度オンする場合、NAND型フラッシュメモリ3若しくは不揮発性キャッシュメモリ22内の所定の記憶領域に記憶しておいたページのデータを読み出すことによって容易に再起動することができるからである。

[0063]

以上の処理により、ホスト機器 2 0 からの小さいデータ書き込み単位、即ち第 1 のデータ書き込み単位の書き込み指示に対し、「巻き添え引越し」をすることなく、NAND型フラッシュメモリ 3 等の大きなデータ書き込み単位、即ち第 2 のデータ書き込み単位を有する不揮発性メモリ部品にデータを効率よく書き込むことができる。したがって、本発明の第 2 の実施の形態によれば、書き込み性能を向上できるメモリコントローラ,メモリ装置及びメモリコントローラの制御方法を提供することができる。

[0.064]

更に又、本発明の第2の実施の形態によれば、第1の実施の形態に比較して、ランダムアクセス可能な不揮発性キャッシュメモリ22に一時的なデータを保存することにより、 不揮発性メモリ部品上には余計なアクセスが発生せず、更に書き込み性能が向上する。

[0065]

(第3の実施の形態)

(分割書き込み機能のオン/オフ機能)

本発明の第1の実施の形態に係るメモリコントローラ4を図1に示すようなメモリカード1へ適用したメモリ装置においては、メモリコントローラ4の分割書き込み機能をオン/オフする機能を付加することもできる。同様に本発明の第2の実施の形態に係るメモリコントローラ4を図6に示すようなメモリカード1へ適用したメモリ装置においても、メモリコントローラ4の分割書き込み機能をオン/オフする機能を付加することもできる。

[0066]

本発明の第3の実施の形態に係るメモリコントローラ4においては、内蔵されるメモリコントローラ4の分割書き込み機能をオン/オフする機能を付加する。

[0067]

本発明の第3の実施の形態に係るメモリコントローラ4は、2値を記憶するNAND型フラッシュメモリにも適用することができる。2値を記憶するNAND型フラッシュメモリは、図1或いは図6に示すようなメモリカード1に適用する場合、NAND型フラッシュメモリ3側で分割書き込み(512バイト単位の書き込み動作)が可能である。NAND型フラッシュメモリ3側で512バイト単位の書き込み動作が実現できれば、メモリコントローラ4側で分割書き込みを回避する動作を実行するよりもむしろ、メモリ装置の動作を高速化することができる。

[0068]

したがって、分割書き込み機能を必要としない 2 値を記憶する N A N D 型フラッシュメモリ 3 の場合には、分割書き込み機能をオフにした方がメモリカード 1 の性能を向上することができる。このため、本発明の第 3 の実施の形態に係るメモリコントローラ 4 においては、分割書き込み機能のオン / オフ機能を付加することによって、幅広い N A N D 型フラッシュメモリの性能に対応することができるようになる。

[0069]

メモリコントローラ 4 の分割書き込み機能のオン / オフ機能の設定は、NAND型フラッシュメモリに格納されたメモリ管理情報の値で決まる。メモリコントローラ 4 若しくはメモリ装置の初期化時に、CPU8がメモリ管理情報の値を読み込み、その読み込まれた設定値に従って、メモリコントローラ 4 を制御することによって、メモリコントローラ 4 の分割書き込み機能のオン / オフ機能の設定が実行される。

## [0070]

本発明の第3の実施の形態に係るメモリコントローラ4においては、内蔵されるメモリコントローラ4の分割書き込み機能をオン/オフする機能を付加することによって、幅広いNAND型フラッシュメモリの性能に対応することができると共に、NAND型フラッシュメモリ3側で512バイト単位の書き込み動作が実現できる場合には、内蔵されるメモリコントローラ4の分割書き込み機能をオフにすることによって、メモリ装置の動作を高速化することができる。

## [0071]

[その他の実施の形態]

上記のように、本発明は第1乃至第3の実施の形態によって記載したが、この開示の一部をなす論述及び図面はこの発明を限定するものであると理解すべきではない。この開示から当業者には様々な代替実施の形態、実施例及び運用技術が明らかとなろう。

[0072]

このように、本発明はここでは記載していない様々な実施の形態等を含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係る発明特定事項によってのみ定められるものである。

【図面の簡単な説明】

[0073]

【図1】本発明の第1の実施の形態に係るメモリコントローラの模式的ブロック構成図であって、NAND型フラッシュメモリと共に全体としてメモリカードを構成するブロック構成図。

【図2】NAND型フラッシュメモリの構成例。

【図3】不揮発性メモリ(NAND型フラッシュメモリ)のデータ構造図であって、本発明の第1の実施の形態に係るメモリコントローラの動作の一例を説明する図。

【図4】メモリ管理テーブルの構成例。

【図5】不揮発性メモリ(NAND型フラッシュメモリ)のデータ構造図であって、本発明の第1の実施の形態に係るメモリコントローラの動作の別の一例を説明する図。

【図 6 】本発明の第 2 の実施の形態に係るメモリコントローラの模式的ブロック構成図であって、NAND型フラッシュメモリと共に全体としてメモリカードを構成するブロック構成図。

【図7】本発明の第2の実施の形態に係るメモリコントローラの動作の一例を説明する図であって、(a) NAND型フラッシュメモリのデータ構造図及び(b) メモリコントローラ内の不揮発性キャッシュメモリのデータ構造図。

【符号の説明】

[0074]

1 ... メモリカード

3 ... N A N D 型 フラッシュメモリ

4 ... メモリコントローラ

5 ... メモリインタフェース

6 ... ホストインタフェース

8 ... 中央演算処理装置( C P U )

1 1 ... ターゲットブロック ( A ブロック )

1 2 ... - 時書き込みブロック(Bブロック)

2 0 ... ホスト機器

2 1 ... 書き込み単位

2 2 ... 不揮発性キャッシュメモリ

30

20

10

## 【図1】

## 【図2】

# 【図3】

【図5】

メモリ管理テーブル 目的エリア 一時エリア ьо b5 а5 ь10 a6

【図4】

【図6】

# 【図7】

# フロントページの続き

(51) Int.CI. F I テーマコード (参考)

G 0 6 F 12/08 5 1 5 Q G 0 6 F 12/08 5 5 3 B G 0 6 K 19/00 N

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 相沢 英夫

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝マイクロエレクトロニクスセンター内

F ターム(参考) 5B005 MM01 NN03 UU16

5B035 AA02 BB09 CA11 CA29

5B060 AA02 AA06 CB01

5B065 BA09 CH03