(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2013년04월16일

(11) 등록번호 10-1254735

(24) 등록일자 2013년04월09일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/36* (2006.01) *G09G 5/10* (2006.01)

*G02F 1/133* (2006.01) *G02F 1/13357* (2006.01)

- (21) 출원번호 10-2006-0088247

(22) 출원일자 2006년09월12일

심사청구일자 2011년08월31일

(65) 공개번호 10-2008-0024001

(43) 공개일자 2008년03월17일

- (56) 선행기술조사문현

JP2002141191 A

JP2000292767 A

- (73) 특허권자

삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성2로 95 (농서동)

- (72) 발명자

한송이

경기도 용인시 기흥구 금화로105번길 28, 301호

(상갈동)

시무라 타츠히사

도쿄도, 미나토-구, 롯본기, 롯본기 T-Cube

3-1-1, 일본삼성주식회사내

센고쿠 오사무

도쿄도, 미나토-구, 롯본기, 롯본기 T-Cube

3-1-1, 일본삼성주식회사내

- (74) 대리인

오세준, 권혁수, 송윤호

전체 청구항 수 : 총 20 항

심사관 : 이성현

- (54) 발명의 명칭 휘도 조정 장치 및 액정표시장치

### (57) 요 약

수직 신호를 임의의 배수에 체배해서 체배신호를 출력하는 체배회로와, 상기 체배신호를 미분하는 미분회로와, 상기 미분회로부터 출력되는 신호에 의해 콘텐서에 저축되어진 전하의 충방전을 실시하고, 상기 체배신호의 주파수가 변화해도 진폭이 일정한 거치상파를 발생시키는 거치상파 발생회로와 펄스 드티를 결정하는 기준 전압을 발생하는 휘도조정전압 발생 회로와, 상기 거치상파 전압과 상기 휘도 조정 전압을 비교해 휘도 조정 펄스 신호를 출력하는 비교 회로를 구비하고, 상기 휘도조정전압 발생회로는 그 출력전압을 가변으로 하는 회로를 포함하고, 상기 체배회로는 그 체배수를 가변으로 하는 회로를 포함한다.

### 대 표 도

## 특허청구의 범위

### 청구항 1

입력되는 조광동기 신호를 체배해서 체배신호를 출력하는 체배회로:

상기 체배회로에 접속되어 상기 체배신호를 미분하는 미분 회로:

상기 미분 회로에 접속되어, 상기 체배신호의 주파수가 변화해도 진폭이 일정한 거치상파를 발생시키는 거치상파 발생 회로:

제1 기준 전압을 발생하는 제1 기준 전압 발생 회로: 및

상기 거치상파 발생 회로에 접속되어 상기 거치상파의 전압과 상기 제1 기준 전압을 비교해 펄스 신호를 출력하는 비교 회로를 구비하고,

상기 제1 기준 전압 발생 회로는 그 출력전압을 가변으로 하는 회로를 포함하고,

상기 체배회로는 그 체배수를 가변으로 하는 회로를 포함하는 것을 특징으로 하는 휘도조정장치.

### 청구항 2

제 1항에 있어서, 상기 체배회로는,

위상 비교기, 루프 필터, 전압 제어 발진기 및 분주 카운터를 구비하여서 상기 조광동기 신호에 동기한 체배신호를 출력하는 것을 특징으로 하는 휘도 조정 장치.

### 청구항 3

제 1항에 있어서, 상기 미분 회로는,

일단에 입력 신호가 입력되고 타단에 콘덴서의 일단이 접속된 제1 저항기:

일단에 상기 제1 저항기가 접속되고 타단에 다이오드의 캐소드가 접속된 콘덴서:

애노드가 그라운드에 접속되고 캐소드가 상기 콘덴서의 타단에 접속된 다이오드: 및

일단에 상기 다이오드의 캐소드와 상기 콘덴서의 타단이 접속되고, 타단이 그라운드에 접속된 제2 저항기를 가지는 것을 특징으로 하는 휘도 조정 장치.

### 청구항 4

제 1항에 있어서, 상기 거치상파 발생 회로는,

제2 기준 전압을 발생하는 제2 기준 전압 발생 회로:

제3 기준 전압을 발생하는 제3 기준 전압 발생 회로:

출력 전류가 입력 전압으로 제어되는 전압 제어 전류원:

상기 전압 제어 전류원에서 출력되는 전류를 충전하는 콘덴서:

상기 미분 회로의 출력이 베이스에 접속되고, 상기 콘덴서가 콜렉터에 접속되고, 에미터가 그라운드에 접속된 트랜지스터:

상기 트랜지스터의 콜렉터 전압이 정입력 단자에 입력되고, 상기 제2 기준 전압이 부입력 단자에 입력되고, 상기 트랜지스터의 콜렉터 전압과 상기 제2 기준 전압을 비교한 결과를 출력하는 제1 연산증폭기:

상기 제1의 연산증폭기의 출력에 접속된 저항기와 콘덴서를 갖는 적분 회로:

정입력 단자에는 상기 적분 회로의 출력이 입력되고, 부입력 단자에는 상기 제3 기준 전압이 저항기를 개재해 입력되고, 출력 단자로부터 병렬로 접속된 저항기와 콘덴서를 개재해 부입력 단자에 부궤환이 걸리고, 출력 단자가 상기 전압 제어 전류원에 접속된 제2 연산증폭기를 포함하고,

상기 미분 회로의 출력 신호에 의해 상기 트랜지스터가 작동해 상기 콘덴서의 충방전을 행하고 상기 트랜지스터의 콜렉터에 거치상파를 발생시키는 것을 특징으로 하는 휘도 조정 장치.

### 청구항 5

제 1항에 있어서,

상기 거치상파의 전압과 상기 제1 기준 전압을 비교해 펄스 신호를 출력하는 비교 회로는 제3 연산증폭기를 포함하고, 상기 거치상파 전압이 상기 제3 연산증폭기의 정입력 단자에 입력되고, 상기 제1 기준 전압이 상기 제3 연산증폭기의 부입력 단자에 입력되어서 상기 펄스 신호를 출력하는 것을 특징으로 하는 휘도 조정 장치.

### 청구항 6

제 5항에 있어서, 상기 제1 기준 전압 발생 회로와, 상기 제3 연산증폭기의 정입력 단자 사이에 상기 제1 기준 전압을 조정하는 레벨 시프터를 구비하는 것을 특징으로 하는 휘도 조정 장치.

### 청구항 7

제 6항에 있어서,

상기 레벨 시프터는, 상기 제1 기준 전압 발생 회로에서 출력되는 상기 제1 기준 전압을 분압하는 2개의 저항기의 저항값과, 제4 연산증폭기의 부웨환에 사용하는 저항기의 저항값의 선택에 의해, 출력되는 전압 레벨을 조정하는 것을 특징으로 하는 휘도 조정 장치.

### 청구항 8

액정 표시부:

2종의 게이트 전압의 조합으로 이루어지는 게이트 신호를 액정 표시부의 게이트선에 인가하는 게이트 구동부: 및

계조 전압군 중에서, 필요한 휘도와 반전 제어에 따라 선택한 계조 전압을 데이터선에 인가하는 데이터 구동부를 가지는 액정 표시판:

상기 계조 전압군과 상기 2종의 게이트 전압을 생성하는 전압 생성부:

RGB 영상 신호 및 그 표시를 제어하는 입력 제어 신호를 받아, 조광동기 신호를 포함하는 복수의 제어 신호를 생성하고, 영상 신호를 상기 액정 표시부의 동작 조건에 대응하도록 처리하고, 상기 복수의 제어 신호를 출력하는 신호 제어부:

복수의 방전관으로 이루어진 램프부:

상기 복수의 방전관에 교류 고전압을 공급하는 1개 이상의 인버터:

상기 조광동기 신호를 입력받아 체배해서 체배신호를 출력하는 체배회로:

상기 체배회로에 접속되어 상기 체배신호를 미분 하는 미분 회로:

상기 미분 회로에 접속되어 상기 미분 회로에서 출력되는 신호에 의해 콘덴서에 축적된 전하의 충방전을 행하고, 상기 체배신호의 주파수가 변화해도 진폭이 일정한 거치상파를 발생시키는 거치상파 발생 회로:

제1 기준 전압을 발생하는 제1 기준 전압 발생 회로:

상기 거치상파 발생 회로에 접속되어 상기 거치상파 전압과 상기 제 1 기준 전압을 비교해 펄스 신호를 출력하는 비교 회로를 구비하고,

상기 제1 기준 전압 발생 회로는 그 출력전압을 가변으로 하는 회로를 포함하고,

상기 조광동기 신호를 체배하는 체배회로는 그 체배수를 가변으로 하는 회로를 포함하는 휘도 조정 장치를 구비하는 것을 특징으로 하는 액정표시장치.

### 청구항 9

제 8항에 있어서, 상기 채배회로는,

위상 비교기, 루프 필터, 전압 제어 발진기 및 분주 카운터를 구비하여서 상기 조광동기 신호에 동기한 채배신호를 출력하는 것을 특징으로 하는 액정표시장치.

### 청구항 10

제 8항에 있어서, 상기 미분 회로는,

일단에 입력 신호가 입력되고 타단에 콘덴서의 일단이 접속된 제1 저항기:

일단에 상기 저항기가 접속되고 타단에 다이오드의 캐소드가 접속된 콘덴서:

애노드가 그라운드에 접속되고 캐소드가 상기 콘덴서의 타단에 접속된 다이오드: 및

일단에 상기 다이오드의 캐소드와 상기 콘덴서의 타단이 접속되고 타단이 그라운드에 접속된 제2 저항기를 가지는 것을 특징 하는 액정표시장치.

### 청구항 11

제 8항에 있어서, 상기 거치상파 발생 회로는,

제2 기준 전압을 발생하는 제2 기준 전압 발생 회로:

제3 기준 전압을 발생하는 제3 기준 전압 발생 회로:

출력 전류가 입력 전압에 제어되는 전압 제어 전류원:

상기 전압 제어 전류원에서 출력되는 전류를 충전하는 콘덴서:

상기 미분 회로의 출력이 베이스에 접속되고, 상기 콘덴서가 콜렉터에 접속되고, 에미터가 그라운드에 접속된 트랜지스터:

상기 트랜지스터의 콜렉터 전압이 정입력 단자에 입력되고, 상기 제2 기준 전압이 부입력 단자에 입력되고, 상기 트랜지스터의 콜렉터 전압과 상기 제2 기준 전압을 비교한 결과를 출력하는 제1의 연산증폭기:

상기 제1의 연산증폭기의 출력에 접속된 저항기와 콘덴서로 구성되는 적분 회로: 및

정입력 단자에는 상기 적분 회로의 출력이 입력되고, 부입력 단자에는 상기 제3 기준 전압이 저항기를 개재해 입력되고, 출력 단자에서 병렬로 접속된 저항기와 콘덴서를 개재해 부입력 단자로 부궤환이 걸리고, 또한, 출력 단자가 상기 전압 제어 전류원에 접속된 제2 연산증폭기를 가지고,

상기 미분 회로의 출력 신호에 의해 상기 트랜지스터가 작동해 상기 콘덴서의 충방전을 행하고 상기 트랜지스터의 콜렉터에 거치상파를 발생시키는 것을 특징으로 하는 액정표시장치.

### 청구항 12

제 8항에 있어서,

상기 거치상파 전압과 상기 제1 기준 전압을 비교해 펄스 신호를 출력하는 비교 회로는 제3 연산증폭기로 구성되고, 상기 거치상파 전압이 상기 제3 연산증폭기의 정입력 단자에 입력되고, 상기 제1 기준 전압이 상기 제3 연산증폭기의 부입력 단자에 입력되어, 상기 펄스 신호를 출력하는 것을 특징으로 하는 액정표시장치.

### 청구항 13

제 12항에 있어서, 상기 제1 기준 전압 발생 회로와 상기 제3의 연산증폭기의 정입력 단자 사이에 상기 제1 기준 전압을 조정하는 레벨 시프터를 구비하는 것을 특징으로 하는 액정표시장치.

### 청구항 14

제 13항에 있어서, 상기 레벨 시프터는 상기 제 1 기준 전압 발생 회로에서 출력되는 상기 제1 기준 전압을 분압하는 2개의 저항기의 저항값과, 제4 연산증폭기의 부궤환에 사용하는 저항기의 저항값의 선택에 의해, 출력되는 전압 레벨을 조정하는 것을 특징으로 하는 액정표시장치.

**청구항 15**

제 8항에 있어서, 상기 펄스 신호는, 반전 신호와 비반전 신호로 분할되어, 상기 방전판의 점멸 시기가 인접하는 램프와의 사이에 상호로 반전하는 것을 특징으로 하는 액정표시장치.

**청구항 16**

제 8항에 있어서, 상기 조광동기 신호는, 60Hz인 것을 특징으로 하는 액정표시장치.

**청구항 17**

제 8항에 있어서, 상기 조광동기 신호는, 50Hz인 것을 특징으로 하는 액정표시장치.

**청구항 18**

제 8항에 있어서, 상기 조광동기 신호는, 수직 동기 개시 신호인 것을 특징으로 하는 액정표시장치.

**청구항 19**

제 8항 내지 제 18항 중 어느 한 항에 있어서, 그 용도가 액정 모니터인 것을 특징으로 하는 액정표시장치.

**청구항 20**

제 8항 내지 제 18항 중 어느 한 항에 있어서, 그 용도가, 액정 TV인 것을 특징으로 하는 액정표시장치.

**명세서****발명의 상세한 설명****발명의 목적****발명이 속하는 기술 및 그 분야의 종래기술**

[0048] 본 발명은 표시장치의 조광 동기 신호에 동기해서 광원의 밝기(휘도)를 조정하는 회로를 가지는 휘도 조정 장치 및 이것을 구비하는 액정표시장치에 관한 것이다.

[0049] 액정표시장치의 백 라이트 광원으로서 일반적으로 냉음극관이 사용된다. 백 라이트의 휘도 조정은, 냉음극관을 주기적으로 점멸시켜, 그 점등 시간과 소등 시간의 시간 비율(듀티비)을 변화시켜 냉음극관의 평균 밝기를 조정함으로써 이루어진다. 점등시간에 대해서 소등 시간이 짧을 때에는 휘도는 높고, 반대로 점등 시간에 대해서 소등 시간이 길 때에는 휘도는 낮다. 냉음극관의 점등 시간과 소등 시간의 듀티비는, 냉음극관을 구동하는 인버터 회로의 펄스 신호의 듀티비에 의해 조정된다.

[0050] 이 펄스 신호 (이하, 「휘도 조정 펄스」라고 함)의 조정 방법에는 몇 개의 방법이 있지만, 일례로서 차동증폭기 (연산증폭기)를 사용하는 종래의 방법을 설명한다.

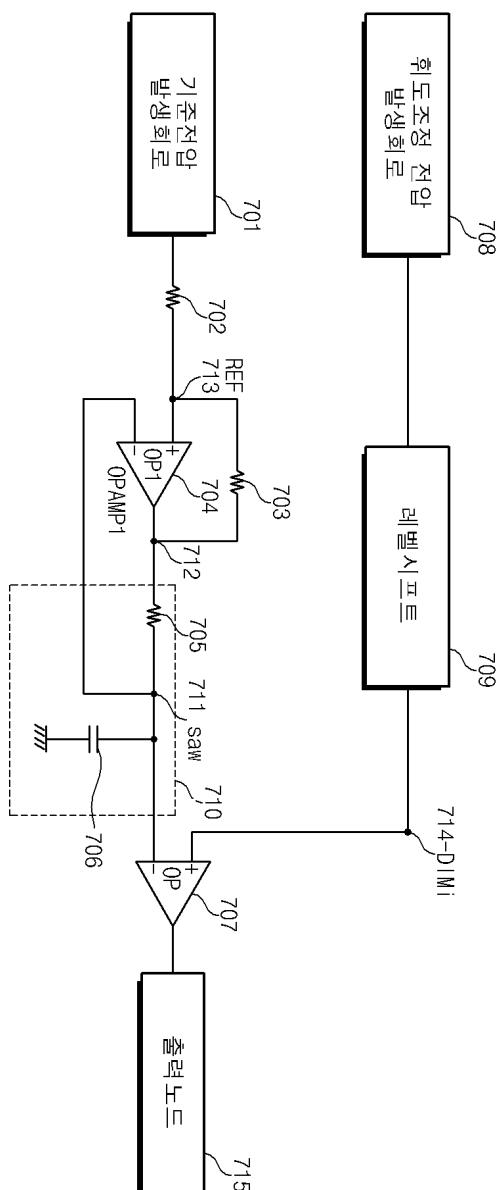

[0051] 도7은 종래의 휘도 조정 펄스 발생 회로도이다. 기준 전압 발생 회로(701)로부터 출력되는 기준 전압을, 저항기 (702)를 개재해서 연산증폭기(704)의 정입력단자에 입력한다. 연산증폭기(704)의 출력은, 저항기(705)와 콘덴서 (706)로 구성되는 적분 회로(710)에 접속되는 것과 함께, 저항기(703)를 개재시켜 연산증폭기(704)의 정입력단자로 정궤환된다. 또, 적분 회로(710)의 노드(saw 711)로부터 부입력 단자로 부궤환이 걸리는 것과 함께, 연산증폭기(707)의 부입력 단자에 입력된다. 한편, 휘도 조정 전압 발생 회로(708)로부터 출력되는 휘도 조정 전압이 레벨 쉬프트(709)를 통해서 연산증폭기(707)의 정입력단자에 입력된다.

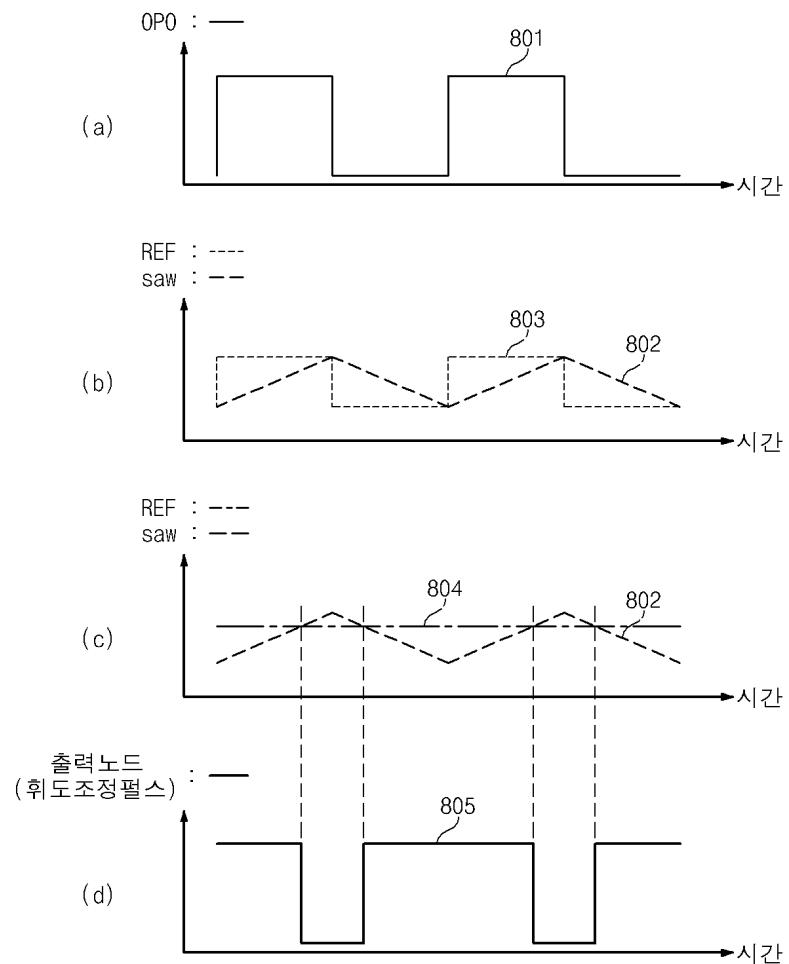

[0052] 도8(a)~(d)는, 도 7에 나타낸 종래의 휘도 조정 펄스 발생 회로의 각 노드의 타이밍 차트도이다. 도8(a)는, 연산증폭기(704)의 출력 노드(712)의 전압 파형을 나타낸 도이다. 도8(b)는, 연산증폭기의 정입력단자 노드 (REF713)의 전압 파형 및 적분 회로(710)의 노드(saw711)의 전압 파형을 나타낸 도이다. 도8(c)는, 상기 노드 (saw711)의 전압 파형 및 연산증폭기(707)의 정입력 단자 노드(A-DIMi714)의 전압 파형을 나타낸 도이다. 도8(d)는, 연산증폭기(707)의 출력 노드(715)의 전압 파형을 나타낸 도이다.

[0053] 도8(a)에 나타낸 연산증폭기(704)의 펄스 출력(801)을 저항기(705)와 콘덴서(706)로 구성되는 적분 회로(710)로 적분하고, 노드(saw711)에는, 도 8 (b)에 나타난 것과 같은, 거의 직선적으로 변화하는 삼각파의 전압 파형

(802)를 얻는다. 노드(saw711)는, 연산증폭기(704)의 부입력 단자로 케환하고, 연산증폭기(704)의 정입력 단자에 입력되는 기준 전압(803)과 비교된다. 연산증폭기(704)는, 저항기(703)과 저항기(702)로, 정케환되고, 노드(saw711)의 전압(802)가 노드(REF713)의 전압(803)에 이를 때마다 연산증폭기(704)의 출력전압(801)이 반전하고, 거기에 따라 노드(REF713)의 전압(803)도 변화한다. 연산증폭기(704)의 출력전압(801)이 하이(HI)레벨 일 때에는 적분 회로(710)은, 저항기(705)를 통해서 콘텐서(706)을 충전하고, 노드(saw711)의 전압(802)는, 단조롭게 증가한다. 연산증폭기(704)의 출력전압(801)이 하이이기 때문에, 정케환을 받는 노드(REF713)의 전압(803)도 하이레벨이 된다. 이 상태로 노드(saw711)의 전압(802)가 노드(REF713)의 전압(803)을 넘으면 연산증폭기(704)의 출력은 반전해서 로우(LOW)레벨이 되고, 적분 회로(710)의 콘텐서(706)에 충전된 전하를, 저항기(705)를 통해서 방전할 방향으로 전환한다. 이상의 동작을 반복해서 노드(saw711)에는 삼각파형이 얻어진다.

[0054] 다음에 휘도 조정 전압 발생 회로에서 발생된 휘도 조정 전압은, 유저가 제어하는 휘도 레벨로 DC전압으로서 연산증폭기(707)의 정입력 단자로 입력된다. 연산증폭기(707)의 정입력단자노드(A-DIMi714)의 전압(804)와 노드(saw711)의 전압(802)를 연산증폭기(707)로 비교해 출력으로 휘도 조정 펄스 전압(805)가 얻어진다.

[0055] 일반적으로 액정 패널로의 표시 영상 신호의 수직 구동 신호에 휘도 조정 펄스의 주파수를 동기 시킴으로써, 간섭 노이즈의 발생이나 휘도 얼룩짐을 방지하고 있다. 그렇지만, 상기의 종래 회로는, 콘텐서(706) 등의 불균형이나 온도 드리프트 등에 의해 안정적으로 설계하는 것은 어렵다. 또한, 수직 구동 신호에 동기 시키려고 한 경우, 종래의 구성에서는 입력되는 조광동기 신호의 주파수가 변화했을 때에, 상기 적분 회로의 저항, 콘텐서의 값으로 결정될 시정수가 고정되었기 때문에, 상기 적분 회로에서 출력되는 삼각파의 진폭이 변화하고, 일정 직류 전압인 상기 조광 제어 전압과 상기 삼각파를 비교해서, 출력되는 상기 조광 제어 펄스의 듀티비가 변화해, 백 라이트의 밝기가 변화한다.

[0056] 또, 액정 패널로의 표시 영상 신호의 수직 구동 신호와 휘도 조정 펄스의 주파수 사이에 엇갈림이 생겨 간섭 노이즈가 발생하는 문제점이 있었다. 특히, 액정 패널로의 표시 영상 신호의 수직 구동 신호와 휘도 조정 펄스의 주파수가 공배수나 공약수의 관계이고, 게다가 완전하게 고정되지 않고 엇갈림을 일으키게 했을 때에 간섭 노이즈가 현저해진다.

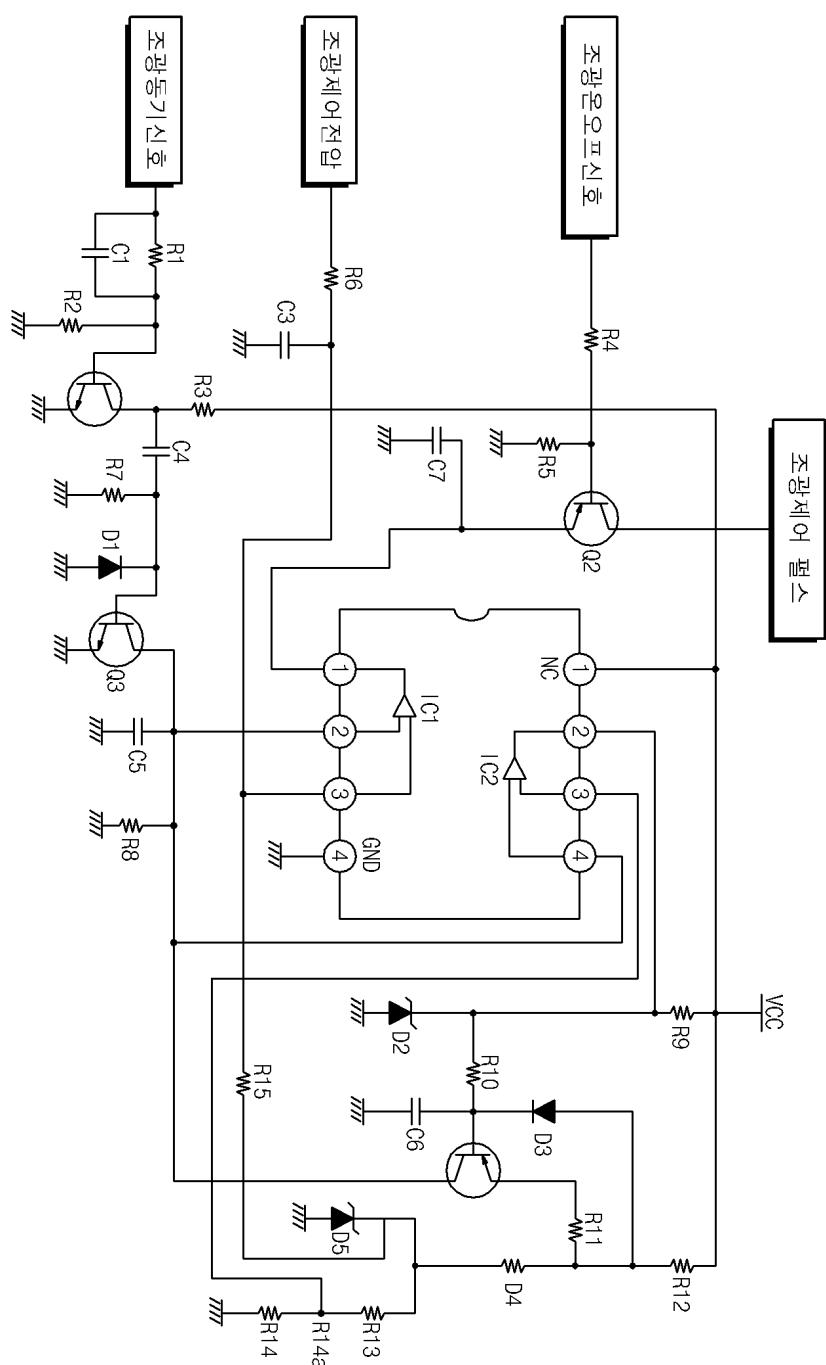

[0057] 이에, 예를들면, 특개평2003-173892호와 같은 조광제어장치가 제안되고 있다. 도9는, 그 조광제어장치의 회로도이다.

[0058] 도9에 나타나는 조광제어장치는, 콘텐서(C5)와 충전 전류를 공급하는 트랜지스터(Q4)에 의해 구성되는 적분 수단과, 조광동기 신호에 의해, 상기 콘텐서(C5)의 충전 전압을 방전하는 리셋 수단((C4, R7, D1)로 이루어진 미분 회로와 트랜지스터(Q3))과, 기준 전압 발생 수단과 연산증폭기(IC2)에 의해 상기 콘텐서(C5)의 충전 전압과 상기 기준 전압을 비교한 결과, 출력되는 펄스 신호를(R10)과(C6)로 적분하고, 상기 트랜지스터(Q4)의 제어 단자에 피드백시키는 수단을 구비하고, 연산증폭기(IC1)에 의해 상기 콘텐서(C5)의 충전 전압과 조광제어 전압을 비교해 얻어진 조광제어 펄스를 출력하는 수단을 가지며, 상기 콘텐서(C5)의 충전 전압 파형은 직선성이 양호하고 진폭이 일정하게 유지되어진 거치상파이며, 출력되는 상기 조광제어 펄스의 듀티비는, 조광제어 전압에 비례해 설정 가능해진다. 이에 의해, 조광동기 신호의 주파수가 변화해도, 상기 액정 디스플레이의 표시 구동 주기와 백 라이트의 점멸 주기의 불일치에 의한 휘도 얼룩짐이 발생하지 않고, 또, 상기조광제어 전압에 비례한 듀티비로 설정되기 때문에, 백 라이트의 밝기를 안정화 시킬 수 있다.

[0059] 그렇지만, 상기 특개평2003-173892호에 의해 제안되는 조광제어장치는, 출력되는 조광제어 펄스의 주파수가 조광동기 신호와 동일한 주파수 밖에 얻을 수 없는 문제가 있다.

[특허 문헌 1]특개평7-191298호 공보

[특허 문헌 2]특개평2003-173892호 공보

### 발명이 이루고자 하는 기술적 과제

[0062] 본 발명은, 조광동기 신호의 주파수와 휘도 조정 펄스의 주파수가 동기 해 항상 고정의 배율이 되어 간섭에 의한 노이즈를 회피하고, 게다가, 조광동기 신호의 주파수가 변동해도 휘도 조정 펄스의 듀티비는 변화하지 않는 것과 함께, 체배회로에 의한 체배수의 제어에 의해 출력되는 휘도 조정 펄스의 주파수를 바꿀 수 있는 휘도 조정 장치를 갖춘 액정표시장치를 제공한다.

### 발명의 구성 및 작용

- [0063] 일 실시 형태에 관한 본 발명의 휘도 조정 장치는, 입력되는 조광동기 신호를 체배하여 체배신호를 출력하는 체 배회로, 상기 체배회로에 접속되어 상기 체배신호를 미분 하는 미분 회로, 상기 미분 회로에 접속되어, 상기 체 배신호의 주파수가 변화해도 진폭이 일정한 거치상파를 발생시키는 거치상파 발생 회로, 제1 기준 전압을 발생 하는 제1 기준 전압 발생 회로, 상기 거치상파 발생 회로에 접속되어 상기 거치상파 전압과 상기 제 1 기준 전 압을 비교해 펄스 신호를 출력하는 비교 회로를 구비한다. 상기 제 1 기준 전압 발생 회로는 그 출력전압을 가변으로 하는 회로를 포함하고, 상기 체배회로는 그 체배수를 가변으로 하는 회로를 포함한다.

- [0064] 또, 일실시 형태와 관한 본 발명의 액정표시장치에서, 액정 표시부는 액정 표시부, 2종의 게이트 전압의 조압으로 이루어지는 게이트 신호를 액정 표시부의 게이트선에 인가하는 게이트 구동부 및 계조 전압군중에서, 필요 한 휘도와 반전 제어에 응답해 선택한 계조 전압을 데이터 선에 인가하는 데이터 구동부를 갖는다. 또한, 액정 표시장치는 상기 계조 전압군과 상기 2종의 게이트 전압을 생성하는 전압 생성부, RGB영상 신호 및 그 표시를 제어하는 입력 제어 신호를 받아, 조광동기 신호를 포함하는 복수의 제어 신호를 생성하고, 영상 신호를 상기 액정 표시부의 동작 조건에 맞도록 적절히 처리하고, 상기 복수의 제어 신호를 출력하는 신호 제어부, 복수의 방전판으로 구성되는 램프부, 상기 복수의 방전판에 교류 고전압을 공급하는 1개 이상의 인버터, 상기 조광동기 신호를 입력받아 체배하여 체배신호를 출력하는 체배회로, 상기 체배회로에 접속되어 상기 체배신호를 미분 하 는 미분 회로, 상기 미분 회로에 접속되어 상기 미분 회로에서 출력되는 신호에 의해 콘텐서에 저축된 전하의 충방전을 행하고, 상기 체배신호의 주파수가 변화해도 진폭이 일정한 거치상파를 발생시키는 거치상파 발생 회로, 제1 기준 전압을 발생하는 제1 기준 전압 발생 회로, 상기 거치상파 발생 회로에 접속되어 상기 거치상파 전압과 상기 제 1 기준 전압을 비교해 펄스 신호를 출력하는 비교 회로를 구비한다. 상기 제 1 기준 전압 발생 회로는 그 출력전압을 가변으로 하는 회로를 포함하고, 상기 체배회로는 그 체배수를 가변으로 하는 회로를 포 함하는 휘도 조정 장치를 갖는다.

- [0065] 본 발명의 실시의 형태에 대해, 이하, 도면을 참조해 설명한다. 단, 본 발명은 많은 다른 형태로 실시하는 것이 가능하고, 이하에 나타내는 실시의 형태 및 실시 예의 기재 내용에 한정해 해석되어 지는 것은 아니다.

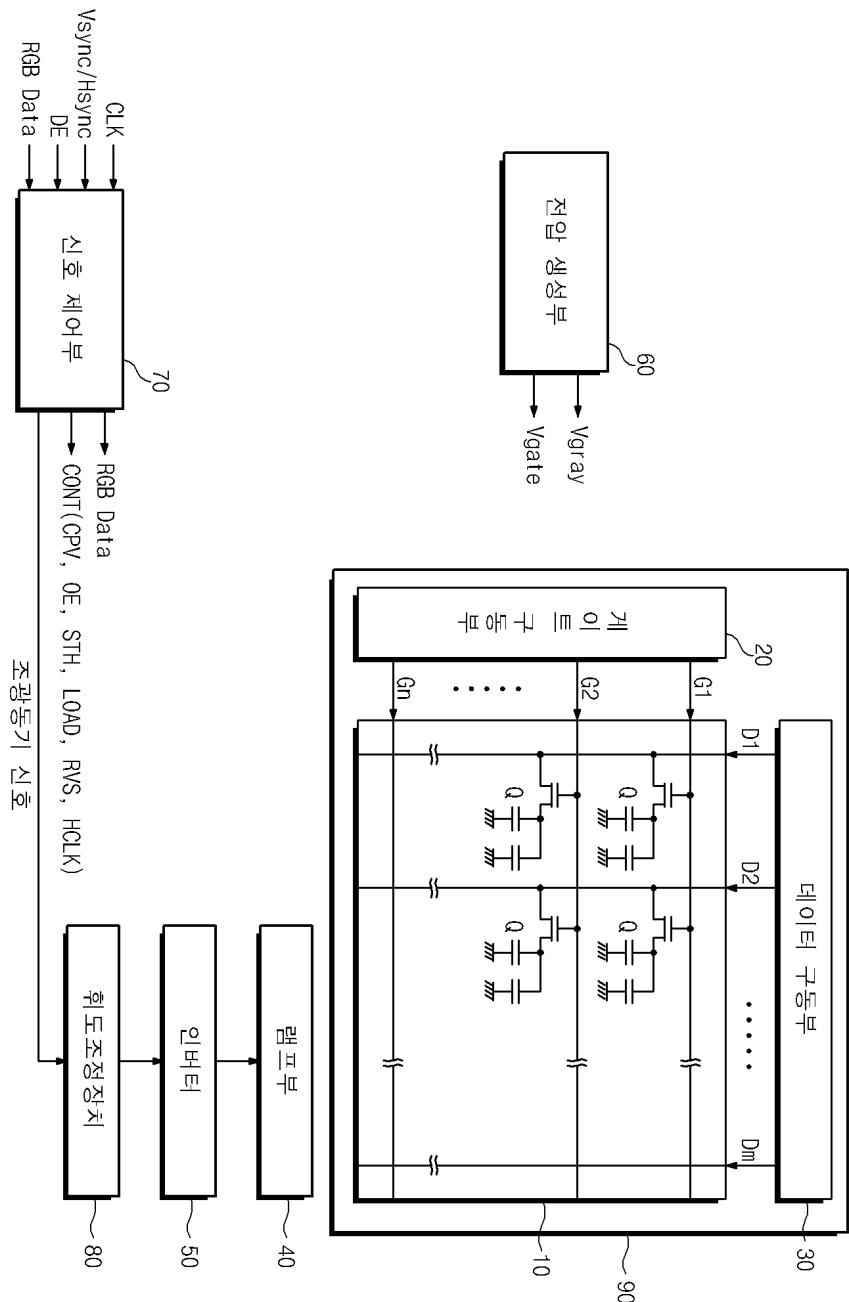

- [0066] 도 1은 본 발명의 일 실시 형태에 관한 액정표시장치의 블럭도이다.

- [0067] 도 1과 같이, 본 발명의 일 실시 형태에 관한 액정표시장치(1)은, 액정 표시부 (10) 및 이것에 연결된 게이트 구동부(20)과 데이터 구동부(30)을 포함한 액정 표시판(90), 게이트 구동부(20) 및 데이터 구동부(30)에 연결된 전압 생성부(60), 액정 표시부(10)에 빛을 조사하는 램프부(40), 램프부(40)에 연결되어 있는 인버터(50), 휘도 조정 장치(80), 그리고 인버터(50) 및 휘도 조정 장치(80)을 제어하는 신호 제어부(70)를 포함한다. 또한, 본 발 명의 일 실시 형태에 관한 액정표시장치는, 액정 표시부(10) 및 이것에 연결된 게이트 구동부(20)과 데이터 구동부(30)이 1개의 액정 표시판상에 배치되어 있지만, 액정 표시부(10)과 게이트 구동부(20)과 데이터 구동부(30)이 각각 별개의 기판상에 형성되어도 된다.

- [0068] 전압 생성부(60)은 화소의 투과율에 관련하고 있는 계조 전압군(Vgray)과 2종의 게이트 전압(Vgate)를 생성한다. 계조 전압(Vgray)은 두 조로 분류되고 두 조 중 한 조는 공통 전압(Vcom)에 대해서 플러스의 값을 가지고, 다른 한 조는 마이너스의 값을 가진다. 게이트 전압(Vgate)은 게이트 온 전압과 게이트 오프 전압을 포함 한다.

- [0069] 게이트 구동부(20)은, 액정 표시부(10)의 게이트선에 연결되고 전압 생성부 (60)로부터의 게이트 온 전압과 게 이트 오프 전압의 조합으로 이루어지는 게이트 신호를 게이트선에 인가한다.

- [0070] 데이터 구동부(30)은, 액정 표시부(10)의 데이터선에 연결되고 전압 생성부(60)로부터의 계조 전압(Vgray) 중에 서, 필요한 휘도와 반전 제어에 응답해서, 선택한 데이터 전압을 데이터 선에 인가한다.

- [0071] 신호 제어부(70)은 외부의 그래픽 제어기(도시하지 않음)로부터, RGB 영상 신호 및 그 표시를 제어하는 입력 제 어 신호, 예를 들면, 수직 동기 신호(Vsync)와 수평 동기 신호(Hsync), 메인 클록(CLK), 데이터 인에이블 신호 (DE) 등의 제공을 받는다. 신호 제어부(70)은 입력 제어 신호에 근거해 각종 제어 신호(CONT)를 생성하고, 영상 신호(RGBData)를 액정 표시부(10)의 동작 조건에 맞도록 적절히 처리한 후 제어 신호(CONT)를 게이트 구동부(20)과 데이터 구동부(30)에 보내고, 처리한 영상 신호(RGBData)는 데이터 구동부(30)에 보낸다.

- [0072] 제어 신호(CONT)는 게이트 온 전압(Von)의 출력 시기를 제어하는 게이트 클록 신호(CPV) 및 게이트 온 전압 (Von)의 폭을 한정하는 출력 인에이블 신호(OE) 등을 포함한다. 제어 신호(CONT)는 게다가 수평 주기의 개시를 알리는 수평 동기 개시 신호(STH)와 데이터 선에 해당 데이터 전압을 인가시키기 위한 로드 신호(명령)(LOAD), 공통 전압(Vcom)에 대한 데이터 전압의 극성 (이하, "공통전압에 대한 데이터 전압의 극성" 을 "데이터 전압의

극성"이라함.) 을 반전시키는 반전 신호(RVS) 및 데이터 클록 신호(HCLK) 등을 포함한다.

[0073] 데이터 구동부(30)은 신호 제어부(70)로부터의 제어 신호(CONT)에 의해 하나의 행 (통상은 수평주사선에 상당)의 화소에 대응하는 영상 데이터를 순차로 수신하고, 전압 생성부(60)로부터의 계조 전압(Vgray) 중 각 영상 데이터에 대응하는 전압을 선택하는 것에 의해, 영상 데이터를 액정에 인가하는 데이터 전압으로 변환한다.

[0074] 게이트 구동부(20)은 신호 제어부(70)로부터의 제어 신호(CONT)에 의해 전압 생성부(60)로부터의 게이트 온 전압을 게이트선에 인가하고, 이 게이트선에 연결된 모든 화소의 스위칭 소자(Q)를 도통시킨다.

[0075] 하나의 게이트선에 게이트 온 전압이 인가되고, 이것에 연결된 하나의 행의 스위칭 소자(Q) 전부가 도통되고 있는 동안 (이 기간을 "1H" 또는 "1수평주기"라 하고, 수평 동기 신호(Hsync), 데이터 인에이블 신호(DE), 게이트 클록(CPV)의 일주기와 같다.), 데이터 구동부(20)은 모든 데이터 선(D1-Dm)에 대응해 각 데이터 전압을 공급한다. 데이터선(D1-Dm)에 공급된 데이터 전압은 도통된 스위칭 소자(Q)를 통해서 해당 화소에 인가된다.

[0076] 휘도 조정 장치(80)은, 신호 제어부(70)로부터의 조광동기 신호 (예를 들면 수직 동기 개시 신호(STV))를 이용하여, 펠스 신호를 발생시키고, 인버터(50)에 공급한다. 인버터(50)에서 펠스 신호는, 램프점등 정현파 전압의 온 오프를 제어해 램프부(40)를 점멸시킨다.

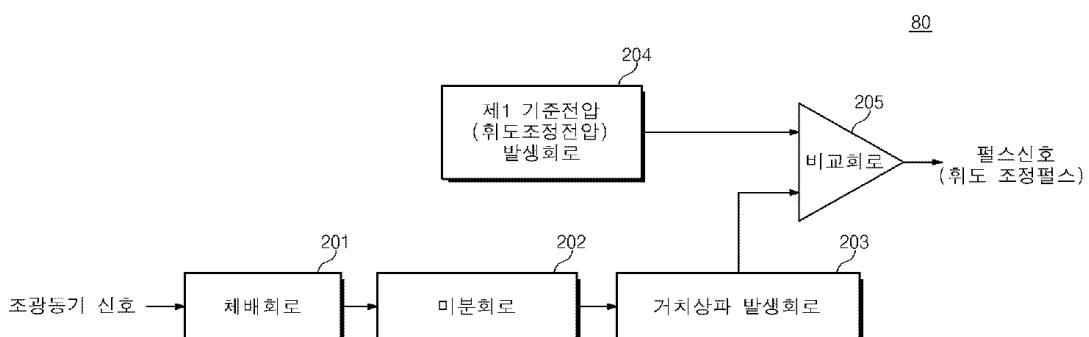

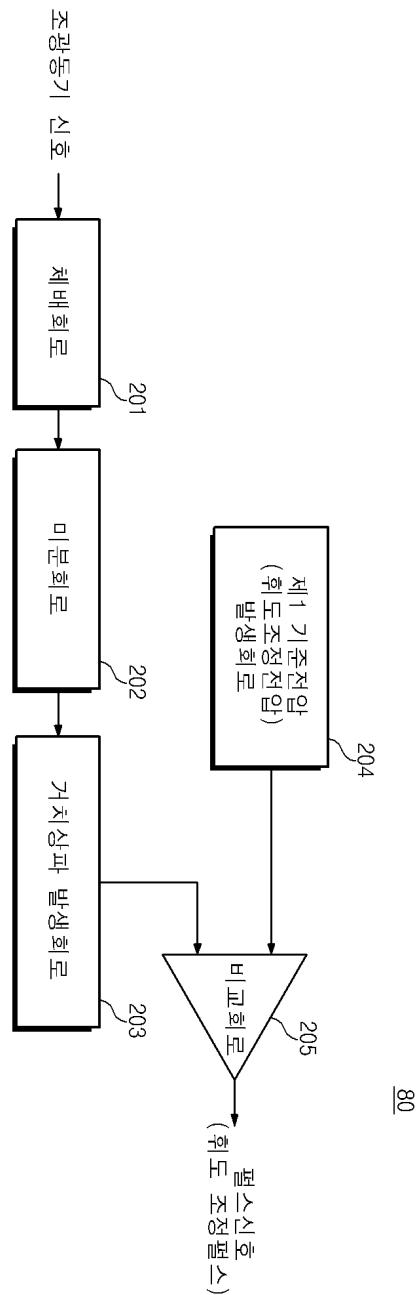

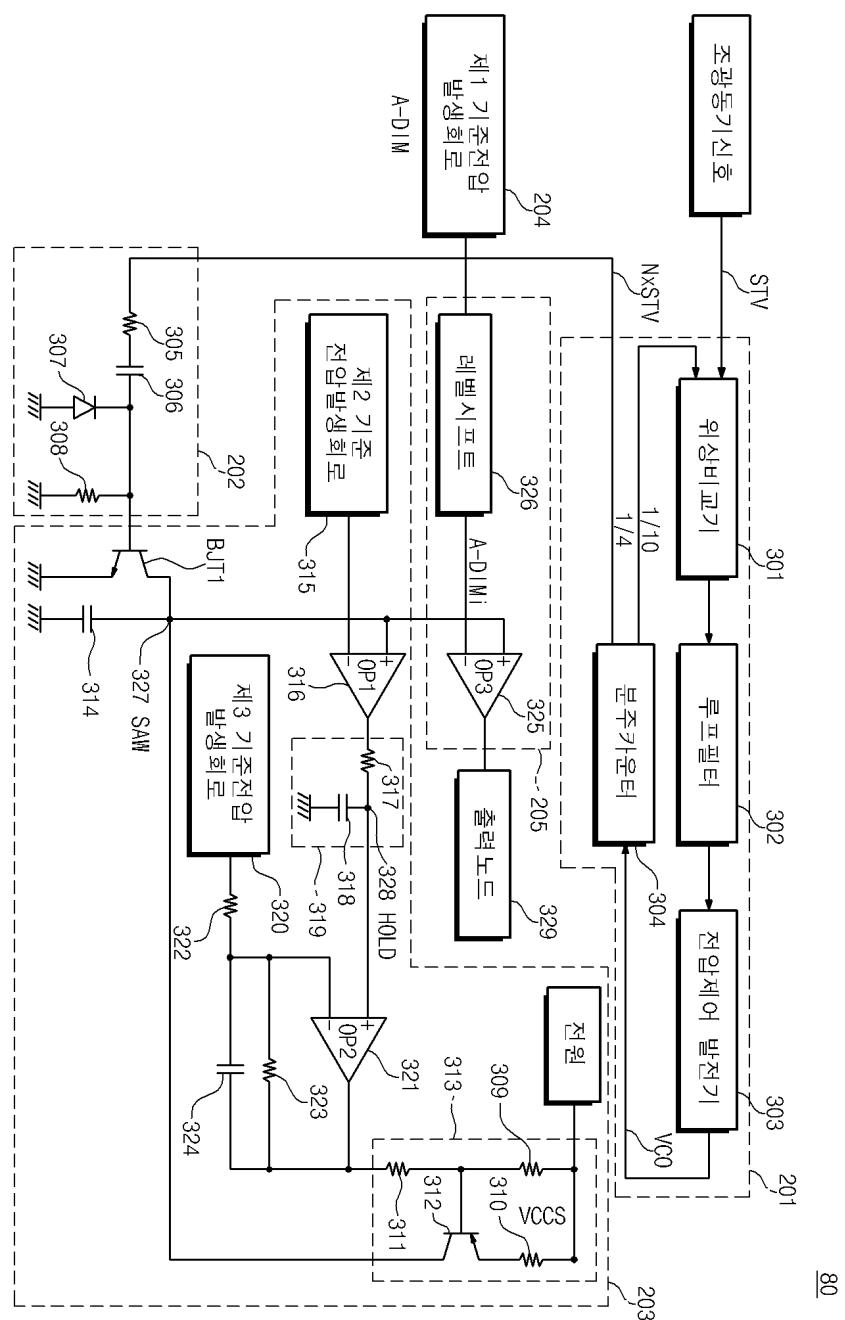

[0077] 도2는, 본 발명의 일 실시 형태에 관한 액정표시장치(1)에 사용되는 휘도 조정 장치(80)의 블록도이다.

[0078] 도2에 나타난 휘도 조정 장치(80)은, 신호 제어부(70)로부터 조광동기 신호를 입력받아 체배회로(201)와, 상기 체배신호를 미분하는 미분 회로(202)와, 상기 미분회로(202)로부터 출력되는 신호에 의해 콘덴서에 축적된 전하의 충방전을 행하고, 상기 체배신호의 주파수의 변화에 의해서도 진폭이 일정한 거치상파를 발생시키는 거치상파 발생 회로(203)과, 상기 거치상파 전압과 비교해 펠스 드티를 결정하는 제1기준 전압(휘도 조정 전압)을 발생하는 제1 기준 전압(휘도 조정 전압) 발생 회로(204)와, 상기 거치상파 전압과 상기 제1 기준 전압을 비교해 휘도 조정 펠스 신호를 출력하는 비교 회로(205)로 구성된다.

[0079] 본 발명의 일 실시 형태에 관한 액정표시장치(1)에 사용되는 휘도 조정 장치(80)은, 신호 제어부(70)로부터 받은 조광동기 신호를 수직 동기 개시 신호(STV)로 한다. 본 발명의 일 실시 형태에 관한 액정표시장치(1)에 사용되는 휘도 조정 장치(80)은, 이 수직 동기 개시 신호(STV)를 입력받아 체배하지만, 본 발명의 다른 실시 형태로서 수직 동기 개시 신호(STV)가 아닌, 수직 동기 신호(Vsync)를 입력받아 체배 또는 분주해도 되고, 또는 수평 동기 신호 (Hsync)를 입력받아 체배해도 된다.

[0080] 조광동기 신호로서 수직 동기 신호(Vsync) 또는 수직 동기 개시 신호(STV)를 사용하는 경우, 그 주파수는 NTSC 방식의 영상 신호시는 약 60Hz이며, PAL 또는 SECAM 방식의 영상 신호 시는 약 50Hz이다.

[0081] 도3은, 도2의 블럭도를 더욱 상세하게 한 개략 회로도이다. 체배회로 (201)은, 위상 비교기(301), 루프 필터 (302), 전압 제어 발진기(VCO,303), 분주 카운터(304)로 구성되는 이른바 PLL 회로이다.

[0082] 미분 회로(202)는, 저항기(305), 콘덴서(306), 다이오드(307), 저항기 (308)로 구성되고, 콘덴서(306)와 저항기 (308)의 값에 의해 시정수가 결정된다.

[0083] 거치상파 발생 회로(203)은, 저항기(309, 310, 311)와 PNP트랜지스터 (312)로 구성되는 전압 제어 전류원(313)과, 전압 제어 전류원(313)에서 공급되는 전류를 충전하는 콘덴서(314)와, 미분 회로(202)의 출력신호의 동작에 의해 콘덴서(314)에 충전된 전하를 방전하는 트랜지스터(BJT1)와, 제2 기준 전압 발생 회로(315)와, 제1 연산증폭기(316)와, 제1 연산증폭기(316)의 출력에 접속된 저항기(317)와 콘덴서(318)로 구성되는 적분 회로(319)와, 제3 기준 전압 발생 회로(320)과, 제2 연산증폭기(321)과, 제2 연산증폭기(321)에서 부입력 단자로 궤환되는 저항기(322, 323)와 콘덴서(324)로 구성된다.

[0084] 제1 기준 전압 발생 회로(204)의 상세한 구성에 대해서는 도시하지 않지만, 안정된 조정 가능 DC전압을 발생하는 회로이면 되고, 예를 들면, 정전압원을 가변 저항기로 분압한 전압을 출력하는 회로나, 여러 종류의 저항 값과 스위칭 트랜지스터에 의해 분압비를 선택 가능하도록 해서 여러 종류의 전압값을 선택적으로 출력하는 회로로 하여도 된다.

[0085] 비교 회로(205)는, 제3의 연산증폭기(325)이고, 정입력 단자는 콘덴서 (314)에 접속되고, 부입력 단자는, 제1 기준 전압 발생 회로에 접속되고, 노드 (SAW 327)의 전압과 제1 기준 전압 발생 회로에서 출력되는 기준이 되는 DC전압을 비교한 결과를 일정한 드티비의 펠스 신호로 출력한다. 더욱이, 제1 기준 전압 발생 회로(204)와, 비교 회로(205)인 제3의 연산증폭기(325)의 부입력 단자 사이에, 제1 기준 전압(DC전압)을 조정하기 위해서 레벨

쉬프트 회로(326)을 설치해도 된다.

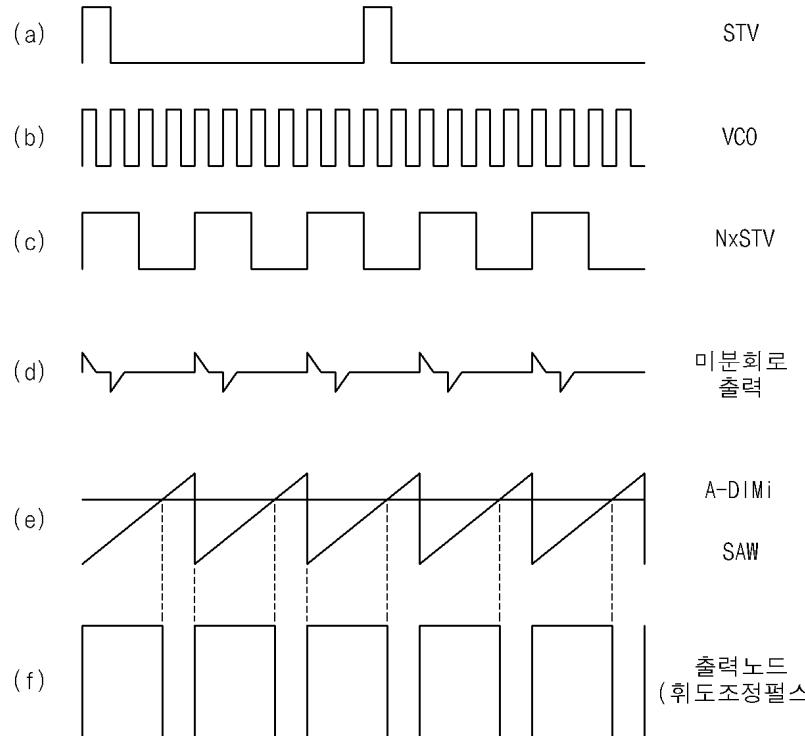

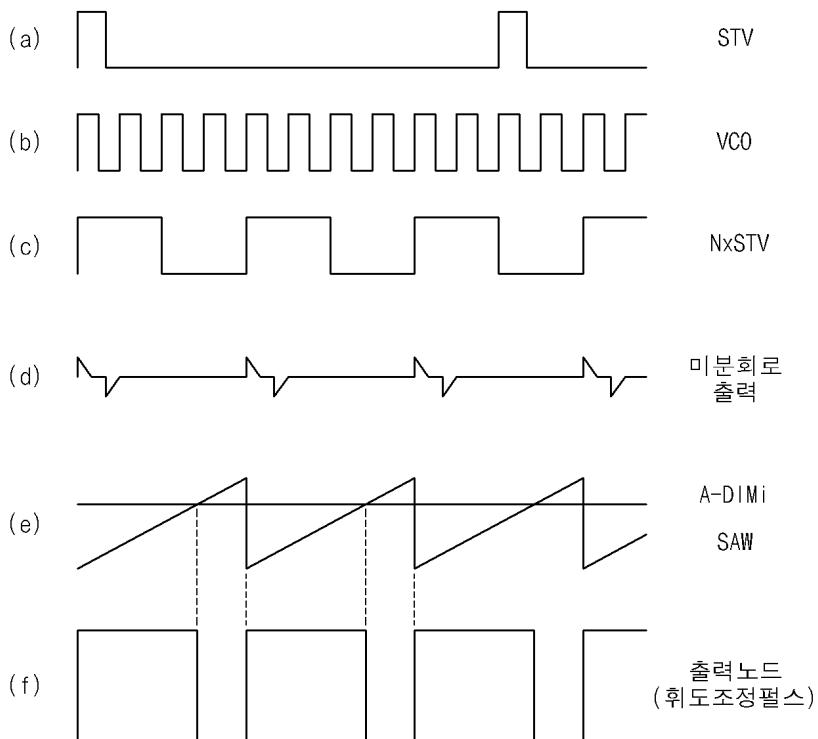

[0086] 도4는, 수직 동기 개시 신호(STV)의 주파수가 높을 때의 각 노드의 전압 파형을 나타낸 타이밍 차트도이다. 도5는, 수직 동기 개시 신호(STV)의 주파수가 낮을 때의 각 노드의 전압 파형을 나타낸 타이밍 차트도이다. 도4(a) 및 도5(a)는, 모두 수직 동기 개시 신호(STV)의 전압 파형을 나타낸 도이다. 도4(b) 및 도5(b)는, 모두 체배회로(201)을 구성하는 전압 제어 발진기(VCO, 303)의 출력 신호의 전압 파형을 나타낸 도이고, 수직 동기 개시 신호(STV)의 10배에 상당하는 주파수가 출력되고 있다. 도4(c) 및 도5(c)는, 모두 체배회로(201)을 구성하는 분주 카운터의 한쪽의 출력 신호의 전압 NxTV를 나타낸 도이고, VCO(303)의 출력 신호 주파수의 1/4이며, 수직 동기 개시 신호(STV)의 2.5배( $N=2.5$ )에 상당하는 주파수 신호의 전압 파형을 나타낸 도이다. 도4(d) 및 도5(d)는, 모두 트랜지스터(BJT1)의 베이스에 입력되는 미분 회로(202)의 출력 신호의 전압 파형이다. 도4(e) 및 도5(e)는, 모두 제3의 연산증폭기(325)의 부입력 단자에 입력되는 제1 기준 전압(A-DIMi)의 전압 파형과 정입력 단자에 입력되는 노드SAW(327)의 전압 파형을 나타낸 도이다. 도4(f) 및 도5(f)는, 모두 제3 연산증폭기(325)의 출력전압 파형을 나타낸 도이다.

[0087] 도4(a) 및 도5(a)에 나타나듯이, 수직 동기 신호(STV)의 주파수는 도 4(a)에서는 높고, 5(a)에서는 낮다. 그러나, 수직 동기 신호(STV)의 주파수의 높낮이에 의하지 않고, 도4(e) 및 도5(e)에 나타나는 제3 연산증폭기(325)의 정입력 단자에 입력되는 노드SAW(327)의 전압 파형의 진폭은 일정한다. 따라서, 도4(e) 및 도5(e)에 나타나는 제3 연산증폭기(325)의 부입력 단자에 입력되는 제1 기준 전압(A-DIMi)의 DC전압이 불변하면, 도4(f) 및 도 5(f)에 나타나는 출력되는 휘도 조정 펄스의 듀티비는 일정하다.

[0088] 도1에 나타낸 신호 제어부(70)로부터 출력되는 수직 동기 개시 신호(STV)는, 그 1배를 포함하는 고정의 배수가 되도록, 체배회로(201)로 체배 된다. 체배회로(201)는, 이른바 PLL를 이용한 주파수 신디사이저이고, 신호 제어부(70)로부터 출력되는 수직 동기 개시 신호(STV)와 루프내의 전압 제어 발진기(VCO, 303)와 분주 카운터(304)로 분주된 출력의 위상차가 일정하도록, 루프내 전압 제어 발진기(VCO, 303)에 피드백 제어를 걸어 발진시킨다. 이 PLL 회로를 이용함으로써, 신호 제어부(70)에서 출력되는 수직 동기 개시 신호(STV)에 동기하고, 혹은 고정 배수가 되는 주파수 신호 출력을 얻을 수 있다.

[0089] 체배수는 임의로 설정하는 것이 가능하고, 결정된 체배수에 근거해, 분주 카운터(304)의 분주비는 설정된다. 도 3및 도4에서는, 체배수가 2.5배로 설정되어진 예를 나타내고 있다. 위상 비교기(301)은, 신호 제어부 (70)에서 출력되는 수직 동기 개시 신호(STV)의 위상과 분주 카운터(304)의 다른쪽 출력 신호의 위상을 비교하고, 위상차 분을 펄스상의 위상차 신호로서 출력한다. 다음으로, 루프 필터(적분 회로/LPF) (302)는, 이 펄스상의 위상차신호의 고주파 성분을 차단해 직류화하고, 제어 전압으로서 전압 제어 발진기에 입력한다. 위상차가 없어질 때까지, 같은 동작이 행해진다. VCO(303) 출력으로부터의 신호 위상이 진행되고 있으면 발진 주파수를 내려 위상을 늦추고, 발진기 출력이 늦으면 발진 주파수를 올려 위상을 진행시키고, 수직 동기 개시 신호(STV)와 분주 카운터(304)의 다른쪽 출력 신호와 위상차이가 영(0)이 되도록 VCO를 제어한다.

[0090] 체배회로(201)에서 출력되는 신호는, 펄스 신호이기 때문에, 이 펄스 신호의 동작 개시 옛지를 검출해야 하므로, 미분 회로(202)가 설치되어 있다.

[0091] 이 미분 회로(202)에서 검출된 옛지를 트랜지스터(BJT1)의 베이스에 인가함으로써, 트랜지스터(BJT1)의 스위칭 동작이 행해진다. 트랜지스터(BJT1)의 컬렉터에 접속된 콘덴서(314)는, 전압 제어 전류원(313)에서 공급되는 일정 전류가 충전되고, 미분 회로(202)에서 검출된 옛지가 트랜지스터(BJT1)의 베이스에 인가되며, 트랜지스터(BJT1)가 온 함으로써, 충전된 전하가 방전된다.

[0092] 이같이 해서, 노드SAW(327)의 전압 파형은, 도4(e) 및 도5(e)에 나타나듯이 거치상파가 된다. 노드SAW(327)의 거치상파는, 제1의 연산증폭기(316)의 정입력 단자에 입력되고, 부입력 단자에 입력되는 제2 기준 전압 발생 회로에서 출력되는 기준 전압과 비교된 결과가, 펄스 신호로서 출력된다.

[0093] 이 펄스 신호는 적분 회로(319)에 의해 평활화된다. 평활화된 신호는, 제2 연산증폭기(321)의 정입력 단자에 입력되고, 부입력 단자에 입력되는 제3 기준 전압 발생 회로에서 발생된 기준 전압과 비교되어, 제2 연산증폭기(321)의 출력으로 전압 제어 전류원(313)을 제어한다.

[0094] 제2의 연산증폭기(321)의 동작에 의해, 정입력 단자에 입력되는 전압은, 제3 기준 전압 발생 회로에 의해 발생되는 기준 전압이 되도록 안정화 된다. 즉, 제2 연산증폭기(321)의 동작에 의해, 정입력 단자에 입력되는 노드 HOLD(328)의 전압이 일정 전압으로 유지되므로, 제1 연산증폭기(316)의 출력 구형파의 평균치는 일정하게 되고, 그 결과로서 노드 SAW(327)의 진폭은, 콘덴서(314)의 용량의 변화나, 수직 동기 개시 신호(STV)의 주파수나,

또, 체배회로에 의한 체배수에 의한 영향을 받지 않고, 항상 일정한 진폭을 유지한다.

[0095] 이상과 같이, 노드 SAW(327)의 거치상파는, 그 주파수 여하에 관계없이, 일정한 진폭이기 때문에, 제3 연산증폭기(325)에 의해 제1 기준 전압 발생 회로에서 출력되는 기준(역치)이 되는 DC전압(A-DIMi)와 비교하면, 제3 연산증폭기(325)의 출력 노드(329)에서 출력되는 휘도 조정 펄스 신호는, 수직 동기 개시 신호(STV)의 주파수나, 또, 체배회로에 의한 체배수에 의한 영향을 받지 않고 그 기준(역치)이 되는 DC전압 레벨로 듀티비가 고정되는 펄스 신호가 된다.

[0096] 또, 본 발명의 일 실시 형태에 의한 액정표시장치에 사용되는 휘도 조정 장치는, 상기했듯이 체배회로(201)을 구비하고 있으므로, 인버터의 점멸 주기를 변동시키고 휘도를 바꾸고 싶은 경우에는, 체배회로의 체배수를 바꾸는 것에 의해, 점멸 주기를 바꿀 수 있다.

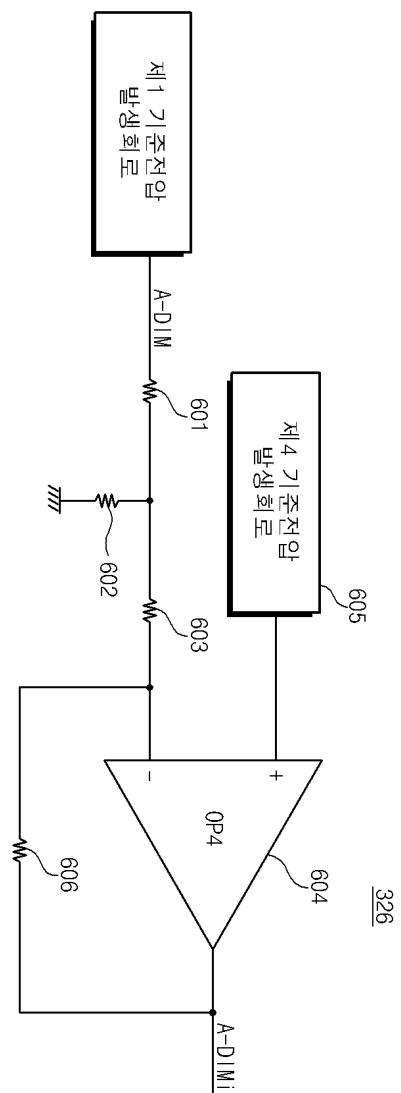

[0097] 또, 제3 연산증폭기(325)의 부입력 단자에 입력되는 제1 기준 전압 발생 회로에서 출력되는 기준(역치)이 되는 DC전압(A-DIMi)를 조정하기 위해서, 레벨 쉬프트 회로를 설치해도 된다. 도6은, 레벨 쉬프트 회로(326)의 일 예를 나타낸 도이다. 제1 기준 전압 발생 회로에서 출력된 전압은 저항기(601, 602)에 의해 분압되고 저항기(603)을 개재시켜 제4 연산증폭기(604)의 부입력 단자에 입력된다. 제4 연산증폭기(604)의 정입력 단자에는 제4 기준 전압 발생 회로(605)에서 출력되는 기준 전압이 입력되며, 제4 연산증폭기(604)의 출력으로부터는 저항기(606)을 개재시켜 부궤환을 걸 수 있다. 이 레벨 쉬프트 회로(326)에서, 저항기(601, 602, 603, 606)의 어느 쪽을 가변 저항기로서 조정하는 것에 의해, 제1 기준 전압을 조정하는 것이 가능해진다.

[0098] 이상을 정리하면, 본 발명의 일 실시 형태에 관한 액정표시장치는, 조광동기 신호, 예를 들면 액정 패널로의 표시 영상 신호의 수직 동기 주파수와 휘도 조정 펄스의 주파수와의 관계가 항상 설정한 원하는 배율로 고정되어 동기 되므로, 간접에 의한 노이즈를 회피하는 것이 가능해지며, 또한, 체배회로에 의한 체배수의 제어에 의해 출력되는 휘도 조정 펄스의 주파수를 바꿀 수 있다.

### 발명의 효과

[0099] 본 발명의 액정표시장치에 의하면, 조광동기 신호의 주파수와 휘도 조정 펄스의 주파수가 동기하여 항상 고정 배율이 되어서 간접에 의한 노이즈를 회피하며, 또한, 조광동기 신호의 주파수가 변동해도 휘도 조정 펄스의 듀티비는 변화하지 않음과 함께, 체배회로에 의한 체배수의 제어에 의해 출력되는 휘도 조정 펄스의 주파수를 바꿀 수 있다.

### 도면의 간단한 설명

[0001] 도1은 본발명의 일 실시 형태에 관한 액정표시장치의 블록도이다.

[0002] 도2는 본발명의 일 실시 형태에 관한 휘도 조정 장치의 블록도이다.

[0003] 도3은 본발명의 일 실시 형태에 관한 휘도 조정 장치의 개략 회로도이다.

[0004] 도4는 수직 동기 개시 신호의 주파수가 높을 때의 본 발명의 일 실시형태에 관한 휘도 조정 장치의 타이밍 차트도이다.

[0005] 도5는 수직 동기 개시 신호의 주파수가 낮을 때의 본 발명의 일 실시형태에 관한 휘도 조정 장치의 타이밍 차트도이다.

[0006] 도6은 레벨 쉬프트 회로의 회로도이다.

[0007] 도7은 종래의 휘도 조정 장치의 회로도이다.

[0008] 도8은 종래의 휘도 조정 펄스 발생 회로의 타이밍 차트도이다.

[0009] 도9는 종래의 다른 조광제어장치의 회로도이다.

[0010] \*부호의 설명

[0011] A-DIMi 기준 전압 (휘도 조정 전압)

[0012] BJT1, 312 트랜지스터

[0013] 1 액정표시장치

|        |                                                                |

|--------|----------------------------------------------------------------|

| [0014] | 10 액정 표시부                                                      |

| [0015] | 20 게이트 구동부                                                     |

| [0016] | 30 데이터 구동부                                                     |

| [0017] | 40 램프부                                                         |

| [0018] | 50 인버터                                                         |

| [0019] | 60 전압 생성부                                                      |

| [0020] | 70 신호 제어부                                                      |

| [0021] | 80 휘도 조정 장치                                                    |

| [0022] | 90 액정 표시판                                                      |

| [0023] | 201 체배 회로                                                      |

| [0024] | 202 미분 회로                                                      |

| [0025] | 203 거치상과 발생 회로                                                 |

| [0026] | 204 제1 기준 전압 발생 회로 (휘도 조정 전압 발생 회로)                            |

| [0027] | 205 비교 회로                                                      |

| [0028] | 301 위상 비교기                                                     |

| [0029] | 302 루프 필터                                                      |

| [0030] | 303 전압 제어 발진기                                                  |

| [0031] | 304 분주 카운터                                                     |

| [0032] | 305, 308, 309, 310, 311, 317, 322, 323, 601, 602, 603, 606 저항기 |

| [0033] | 306, 314, 318, 324 콘텐서                                         |

| [0034] | 307 다이오드                                                       |

| [0035] | 313 전압 제어 전류원                                                  |

| [0036] | 315 제2 기준 전압 발생 회로                                             |

| [0037] | 316 제1의 연산증폭기                                                  |

| [0038] | 319 적분 회로                                                      |

| [0039] | 320 제3 기준 전압 발생 회로                                             |

| [0040] | 321 제2의 연산증폭기                                                  |

| [0041] | 325 제3의 연산증폭기                                                  |

| [0042] | 326 레벨 쉬프트 회로                                                  |

| [0043] | 327 노드 SAW                                                     |

| [0044] | 328 노드 HOLD                                                    |

| [0045] | 329 출력 노드                                                      |

| [0046] | 604 제4의 연산증폭기                                                  |

| [0047] | 605 제4 기준 전압 발생 회로                                             |

도면

도면1

도면2

도면3

## 도면4

## 도면5

도면6

도면7

## 도면8

도면9