(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5210613号

(P5210613)

(45) 発行日 平成25年6月12日(2013.6.12)

(24) 登録日 平成25年3月1日(2013.3.1)

(51) Int.Cl.

F 1

|                    |                  |            |      |

|--------------------|------------------|------------|------|

| <b>G06K 19/077</b> | <b>(2006.01)</b> | G06K 19/00 | K    |

| <b>H01G 11/00</b>  | <b>(2013.01)</b> | H01G 9/00  | 301Z |

| <b>H01G 11/22</b>  | <b>(2013.01)</b> | H01G 9/00  | 301A |

| <b>H01G 11/54</b>  | <b>(2013.01)</b> | H01G 9/00  | 301D |

| <b>G06K 19/07</b>  | <b>(2006.01)</b> | G06K 19/00 | H    |

請求項の数 9 (全 42 頁) 最終頁に続く

(21) 出願番号

特願2007-320422 (P2007-320422)

(22) 出願日

平成19年12月12日(2007.12.12)

(65) 公開番号

特開2008-181493 (P2008-181493A)

(43) 公開日

平成20年8月7日(2008.8.7)

審査請求日

平成22年12月6日(2010.12.6)

(31) 優先権主張番号

特願2006-353336 (P2006-353336)

(32) 優先日

平成18年12月27日(2006.12.27)

(33) 優先権主張国

日本国(JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(74) 代理人 100103159

弁理士 加茂 裕邦

(72) 発明者 土屋 眞

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 梅沢 俊

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の基板上に設けられた充電用回路を有する信号処理回路と、

前記信号処理回路上に設けられたアンテナ回路および電気二重層コンデンサと、

前記アンテナ回路と前記電気二重層コンデンサ上に設けられた第2の基板と、を有し、

前記充電用回路はレギュレータと、ダイオードまたはスイッチの少なくとも一方と、を

有し、

前記電気二重層コンデンサは、前記充電用回路と重なる位置に設けられ、

前記アンテナ回路は、前記電気二重層コンデンサと重ならない位置に設けられ、

前記アンテナ回路は、前記信号処理回路と電気的に接続されており、

10

前記電気二重層コンデンサは、前記充電用回路と電気的に接続されており、

前記第1の基板及び前記第2の基板は、フレキシブル基板であることを特徴とする半導體装置。

## 【請求項 2】

第1の基板上に設けられた充電用回路を有する信号処理回路と、

前記信号処理回路上に設けられた絶縁膜と、

前記絶縁膜を介して、前記信号処理回路上に設けられたアンテナ回路および電気二重層コンデンサと、

前記アンテナ回路と電気二重層コンデンサ上に設けられた第2の基板と、を有し、

前記充電用回路はレギュレータと、ダイオードまたはスイッチの少なくとも一方と、を

20

有し、

前記電気二重層コンデンサは、前記充電用回路と重なる位置に設けられ、

前記アンテナ回路は、前記電気二重層コンデンサと重ならない位置に設けられ、

前記アンテナ回路は、前記絶縁膜を介して前記信号処理回路と電気的に接続されており、

前記電気二重層コンデンサは、前記絶縁膜を介して前記充電用回路と電気的に接続されており、

前記第1の基板及び前記第2の基板は、フレキシブル基板であることを特徴とする半導体装置。

**【請求項3】**

10

請求項1または2において、

前記電気二重層コンデンサは、少なくとも第1の電極と、第2の電極と、前記第1の電極および前記第2の電極の間に位置する電解液層と、を有し、前記第1の電極が前記充電用回路と電気的に接続されていることを特徴とする半導体装置。

**【請求項4】**

請求項3において、

前記第1の電極または前記第2の電極の少なくとも一方の前記電解液層側には、当該電極に接して、フラーレン、またはカーボンナノチューブからなる層が設けられていることを特徴とする半導体装置。

**【請求項5】**

20

請求項3において、

前記第1の電極または前記第2の電極の少なくとも一方は、フラーレン、またはカーボンナノチューブから形成されていることを特徴とする半導体装置。

**【請求項6】**

請求項3乃至請求項5のいずれか一項において、前記電気二重層コンデンサは、前記電解液層にセパレータを有することを特徴とする半導体装置。

**【請求項7】**

請求項3乃至請求項6のいずれか一項において、

前記電解液層は、架橋剤を有することを特徴とする半導体装置。

**【請求項8】**

30

請求項1乃至請求項7のいずれか一項において、

前記信号処理回路はトランジスタより構成されていることを特徴とする半導体装置。

**【請求項9】**

請求項8において、

前記トランジスタは薄膜トランジスタであることを特徴とする半導体装置。

40

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は半導体装置に関する。特に、電気二重層コンデンサと、充電用回路を含む信号処理回路を基板上に形成した半導体装置に関する。

**【背景技術】**

**【0002】**

近年、無線通信により情報伝達を行う半導体装置として、RFID (Radio Frequency Identification) タグが注目を集めている。RFIDタグ(以下、単にRFIDという)は、IC (Integrated Circuit) タグ

50

、 I C チップ、 R F タグ、無線タグ、電子タグとも呼ばれる。 R F I D は、個々の対象物の生産、管理等に役立ち始めており、個人認証への応用も期待されている。

#### 【 0 0 0 3 】

R F I D は、電源を内蔵するか、外部から電源供給を受けるかの違いにより、アクティブタイプ(能動タイプ)の R F I D と、パッシブタイプ(受動タイプ)の R F I D との二つのタイプに分けることができる(アクティブタイプに関しては特許文献1、パッシブタイプに関しては特許文献2を参照)。このうち、アクティブタイプの R F I D においては、R F I D を駆動するための電源を内蔵しており、電源として電池が備えられている。また、パッシブタイプにおいては、R F I D を駆動するための電源を外部からの電波または電磁波(搬送波)の電力を利用して作りだし、電池を備えることのない構成を実現している。

10

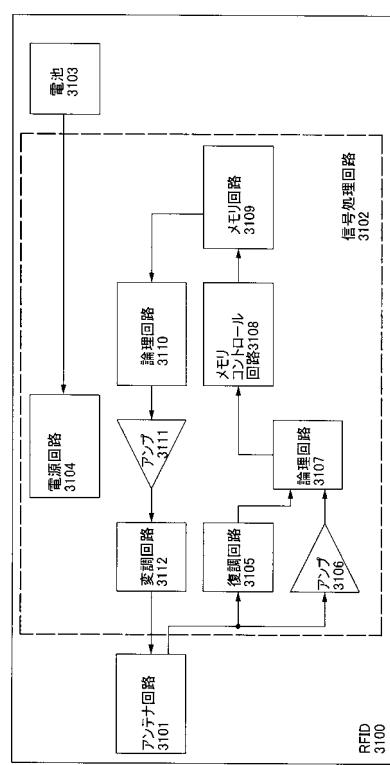

#### 【 0 0 0 4 】

図25にアクティブタイプの R F I D の具体的な構成についてブロック図を示す。図25のアクティブタイプの R F I D 3100では、アンテナ回路3101によって受信された通信信号が信号処理回路3102における復調回路3105、アンプ3106に入力される。通常、通信信号は13.56MHz、915MHzなどのキャリアをASK変調、PSK変調などの処理をおこなって送られてくる。ここで図25においては、通信信号として13.56MHzを用いた例について示す。図25において、信号を処理するためには基準となるクロック信号が必要であり、ここでは13.56MHzのキャリアをクロックに用いている。アンプ3106は13.56MHzのキャリアを増幅し、クロックとして論理回路3107に供給する。またASK変調やPSK変調された通信信号は復調回路3105で復調される。復調後の信号も論理回路3107に送られ解析される。論理回路3107で解析された信号はメモリコントロール回路3108に送られ、それに基づき、メモリコントロール回路3108はメモリ回路3109を制御し、メモリ回路3109に記憶されたデータを取り出し論理回路3110に送られる。論理回路3110でエンコード処理されたのちアンプ3111で増幅され、その信号によって、変調回路3112はキャリアに変調をかける。ここで図25における電源は、信号処理回路3102の外に設けられる電池3103によって電源回路3104を介して供給している。そして電源回路3104はアンプ3106、復調回路3105、論理回路3107、メモリコントロール回路3108、メモリ回路3109、論理回路3110、アンプ3111、変調回路3112などに電力を供給する。このようにしてアクティブタイプの R F I D は動作する。

20

#### 【 0 0 0 5 】

しかし、アクティブタイプの R F I D の場合、電池3103を内蔵しているため、電池の寿命が切れてしまうと使用できなくなる。従って、電池の寿命を把握する必要があり、また電池の寿命が切れてしまうと電池を交換する必要がある。さらに、 R F I D タグの動作が停止しても、使用する状況によっては交換を即座に行えない場合も想定される。

30

#### 【 0 0 0 6 】

またアクティブタイプの R F I D は、内蔵している電池の電気エネルギーが切れたとき、リーダからの問いかけに対して沈黙してしまう。この場合、電池切れにより沈黙しているのか、それとも電池以外の要因、例えば電波の状態が悪い、リーダに不具合が生じている等により沈黙しているのかが、使用者から一見して判別しにくいという問題があった。

40

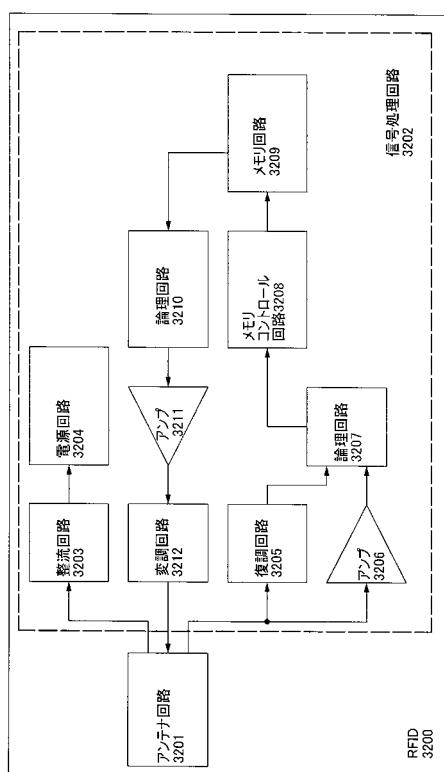

#### 【 0 0 0 7 】

次に、図26に、パッシブタイプの R F I D の具体的な構成についてブロック図を示す。図26のパッシブタイプの R F I D 3200では、アンテナ回路3201によって受信された通信信号が信号処理回路3202における復調回路3205、アンプ3206に入力される。通常、通信信号は13.56MHz、915MHzなどのキャリアをASK変調、PSK変調などの処理をおこなって送られてくる。図26においては、通信信号として13.56MHzを用いた例について示す。図26において、信号を処理するためには基準となるクロック信号が必要であり、ここでは13.56MHzのキャリアをクロックに用いている。アンプ3206は13.56MHzのキャリアを増幅し、クロックとして論

50

理回路 3207 に供給する。また A S K 変調や P S K 変調された通信信号は復調回路 3205 で復調される。復調後の信号も論理回路 3207 に送られ解析される。論理回路 3207 で解析された信号はメモリコントロール回路 3208 に送られ、それに基づき、メモリコントロール回路 3208 はメモリ回路 3209 を制御し、メモリ回路 3209 に記憶されたデータを取り出し論理回路 3210 に送られる。論理回路 3210 でエンコード処理されたのちアンプ 3211 で増幅され、その信号によって、変調回路 3212 はキャリアに変調をかける。一方、整流回路 3203 に入った通信信号は整流され、電源回路 3204 に入力される。電源回路 3204 はアンプ 3206、復調回路 3205、論理回路 3207、メモリコントロール回路 3208、メモリ回路 3209、論理回路 3210、アンプ 3211、変調回路 3212 などに電力を供給する。このようにしてパッシブタイプの R F I D は動作する。

10

#### 【 0 0 0 8 】

しかし、パッシブタイプの R F I D タグの場合、電力の送信元であるリーダライタからの電波または電磁波（搬送波）を受信できる距離でしか動作ができない、つまりリーダライタ近傍でしか動作することができないという問題がある。

#### 【 0 0 0 9 】

上記の問題を解決する手段として、R F I D に電力を供給するための電源としてバッテリーを設ける方法がある。これにより、外部より電波または電磁波（搬送波）を受信していない場合でも、R F I D を利用することができる。特に、R F I D を物流システムなどに利用する場合には、一般的にバッテリーとして、小型で大容量の電気二重層コンデンサなどが搭載される。

20

#### 【 0 0 1 0 】

このときに、R F I D が薄型で軽量であることが重要であるが、たとえ小さな電気二重層コンデンサを用いたとしても電気二重層コンデンサを R F I D に実装する場合、R F I D 自体の大きさや厚みが増してしまう。

#### 【 0 0 1 1 】

また、電気二重層コンデンサを R F I D に実装するために、熱や光により硬化する樹脂中に導電性スペーサが分散された異方性導電膜を用いる場合、R F I D が高温になったときの熱膨張や低温になったときの熱収縮の割合が電気二重層コンデンサと R F I D で異なるため、接続部分の信頼性が低くなってしまう。

30

#### 【 0 0 1 2 】

この問題を解決するために、電気二重層コンデンサを R F I D に一体に設ける方法が報告されており、C M O S により形成された信号処理回路に隣接して、電気二重層コンデンサを一体に形成している（特許文献 3）。

【特許文献 1】特開 2005 - 316724 号公報

【特許文献 2】特表 2006 - 503376 号公報

【特許文献 3】特開 2006 - 024087 号公報

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【 0 0 1 3 】

しかしながら、電気二重層コンデンサを信号処理回路に隣接して設ける場合、電気二重層コンデンサと信号処理回路を接続するための配線を引き回す必要がある。R F I D を物流システムなどに利用する場合は、球面を持っている対象物に R F I D を貼り付けることが多く、曲げることにより R F I D 自体に応力がかかる。以下、曲げることにより R F I D 自体にかかる応力を、曲げ応力という。特に、柔軟性を持ったフレキシブル基板で形成された R F I D では、電気二重層コンデンサと信号処理回路を接続するための配線にかかる曲げ応力は大きくなり、断線してしまうという課題があった。

40

#### 【 0 0 1 4 】

上記問題を鑑み、本発明は R F I D などの半導体装置において、基板上に設けられた充電用回路を有する信号処理回路上に、アンテナ回路および充電用の電気二重層コンデンサな

50

どを一体的に形成した、曲げ応力に強い半導体装置を提供することを課題とする。

【課題を解決するための手段】

【0015】

上述の諸問題を解決するため、本発明は基板上に充電用回路を有する信号処理回路を設け、前記信号処理回路上にアンテナ回路および充電用の電気二重層コンデンサなどを一体的に形成することを特徴とする。また本発明は、充電用回路と電気二重層コンデンサを接続するための配線を短くし、曲げ応力による充電用の電気二重層コンデンサと充電用回路を有する信号処理回路との間の断線を防ぐために、基板上に充電用回路を有する信号処理回路を形成し、その上に充電用の電気二重層コンデンサを設けたことを特徴とする。これにより、信号処理回路に隣接して充電用の電気二重層コンデンサを設ける場合に比べ、より小型の半導体装置を作製することができる。以下、本発明の具体的な構成について示す。10

【0016】

本発明の半導体装置の一は、充電用回路を有する信号処理回路と、前記信号処理回路上に設けられたアンテナ回路および電気二重層コンデンサとを有し、前記アンテナ回路は、前記信号処理回路と電気的に接続されており前記電気二重層コンデンサは、前記充電用回路と電気的に接続されていることを特徴とする。

【0017】

また、別の本発明の半導体装置の一は、第1の基板上に設けられた充電用回路を有する信号処理回路と、前記信号処理回路上に設けられたアンテナ回路および電気二重層コンデンサと、前記アンテナ回路と電気二重層コンデンサ上に設けられた第2の基板を有し、前記アンテナ回路は、前記信号処理回路と電気的に接続されており、前記電気二重層コンデンサは、前記充電用回路と電気的に接続されていることを特徴とする。20

【0018】

また、別の本発明の半導体装置の一は、充電用回路を有する信号処理回路と、前記信号処理回路上に設けられた絶縁膜と、前記絶縁膜上に設けられたアンテナ回路および電気二重層コンデンサとを有し、前記アンテナ回路は、前記絶縁膜を介して前記信号処理回路と電気的に接続されており、前記電気二重層コンデンサは、前記絶縁膜を介して前記充電用回路と電気的に接続されていることを特徴とする。

【0019】

また本発明における半導体装置は、上記の構成において、前記電気二重層コンデンサは、少なくとも第1の電極と、第2の電極と、前記第1の電極および前記第2の電極の間に位置する電解液層とを有し、前記第1の電極が前記充電用回路と電気的に接続されていることを特徴とする。30

【0020】

また本発明における半導体装置は、上記の構成において、前記第1の電極および前記第2の電極の少なくとも一方の前記電解液層側には、当該電極に接して活性炭、フラーレン、またはカーボンナノチューブからなる層が設けられていることを特徴とする。

【0021】

また本発明における半導体装置は、上記の構成において、前記第1の電極もしくは前記第2の電極の少なくとも一方は、活性炭、フラーレン、またはカーボンナノチューブから形成されていることを特徴とする。40

【0022】

また本発明における半導体装置は、上記の構成において、前記電気二重層コンデンサは、前記電解液層にセパレータを有してもよい。

【0023】

また本発明における半導体装置は、上記の構成において、前記電解液層は、架橋剤を有してもよい。

【0024】

また本発明における半導体装置は、上記の構成において、前記信号処理回路はトランジスタより構成されていることを特徴とする。50

**【 0 0 2 5 】**

また本発明における半導体装置は、上記の構成において、前記基板は、柔軟性を持ったフレキシブル基板を用いたものであってもよい。

**【 0 0 2 6 】**

また本発明における半導体装置は、上記の構成において、前記電気二重層コンデンサは、前記充電用回路と重なって位置することを特徴とする。

**【発明の効果】****【 0 0 2 7 】**

本発明により、基板上に充電用の電気二重層コンデンサをアンテナ回路、信号処理回路などと一緒に形成した半導体装置を簡便に得ることができる。このように、充電用回路を有する信号処理回路上に電気二重層コンデンサを設けることで、充電用回路と電気二重層コンデンサを接続するための配線を短くすることができる。さらに、充電用回路と電気二重層コンデンサを接続するための配線が短いために、曲げ応力により断線しない充電用の電気二重層コンデンサを有する半導体装置を提供することができる。なお、本発明は、R F I Dに限らず、薄型軽量な無線で充電するその他の電子機器にも適用することができる。10

**【発明を実施するための最良の形態】****【 0 0 2 8 】**

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従つて本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に説明する本発明の構成において、同じ物を指示示す符号は異なる図面間においても共通とする。20

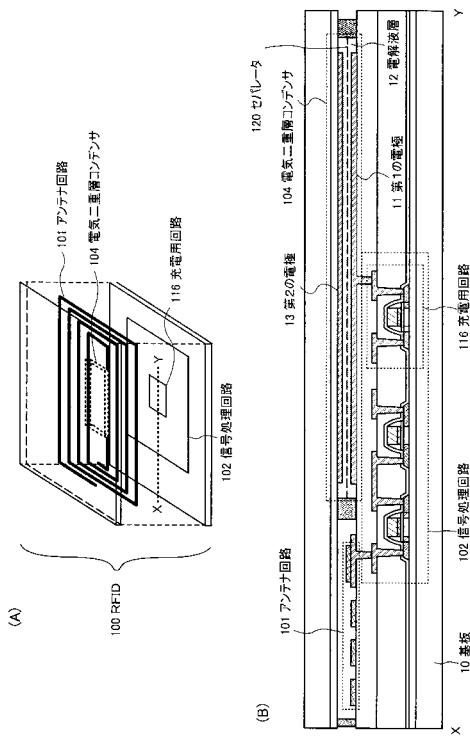

**【 0 0 2 9 】**

本発明のR F I Dに用いる半導体装置について、図1(A)の斜視図、図1(B)の断面図および図2のブロック図を用いて説明する。なお、図1(B)の断面図は、図1(A)のX Y間に相当する。

**【 0 0 3 0 】**

なお、本明細書でいう半導体装置とは、半導体特性を利用することで機能しうる装置全般を指すものとする。また、本明細書において、電極とは配線の一部であり、説明の便宜上、配線と電極と使い分けるが、配線という言葉には電極は常に含められているものとする。また、本明細書において、接続という言葉には電気的な接続は常に含められているものとする。30

**【 0 0 3 1 】**

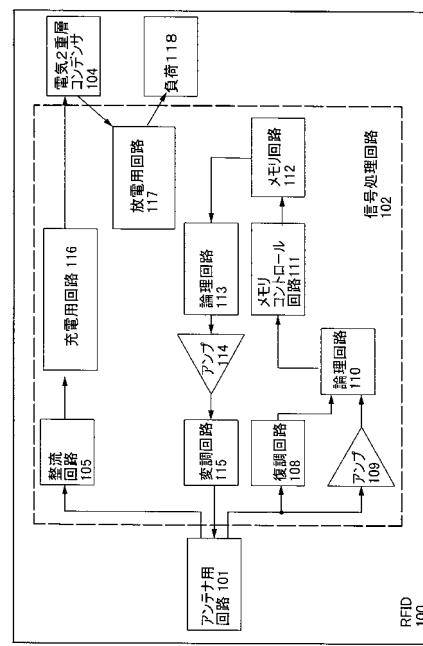

図1(A)、(B)のR F I D 1 0 0は、アンテナ回路1 0 1、充電用回路1 1 6を有する信号処理回路1 0 2及びセパレータ1 2 0を有する電気二重層コンデンサ1 0 4によって構成されている。図2に示すように、信号処理回路1 0 2は、整流回路1 0 5、レギュレータからなる充電用回路1 1 6、放電用回路1 1 7、復調回路1 0 8、アンプ1 0 9、論理回路1 1 0、メモリコントロール回路1 1 1、メモリ回路1 1 2、論理回路1 1 3、アンプ1 1 4、変調回路1 1 5によって構成される。40

**【 0 0 3 2 】**

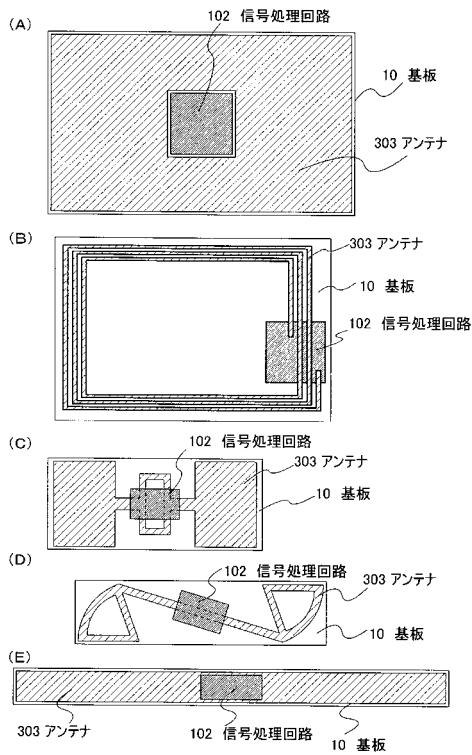

なおアンテナ回路1 0 1におけるアンテナの形状については、特に限定されない。例えば図3(A)のように基板1 0上の信号処理回路1 0 2の周りに一面のアンテナ3 0 3を配した構造を取っても良い。また、図3(B)のように基板1 0上の信号処理回路1 0 2に接続されたコイル状のアンテナ3 0 3でも良い。また、図3(C)のように基板1 0上の信号処理回路1 0 2に対して、高周波数の電磁波を受信するためのアンテナ3 0 3の形状をとってもよい。また、図3(D)のように基板1 0上の信号処理回路1 0 2に対して、180度無指向性(どの方向からでも同じく受信可能)なアンテナ3 0 3での形状をとってもよい。また、図3(E)のように、基板1 0上の信号処理回路1 0 2に対して、棒状に長く伸ばしたアンテナ3 0 3の形状をとってもよい。また、アンテナに必要な長さは受50

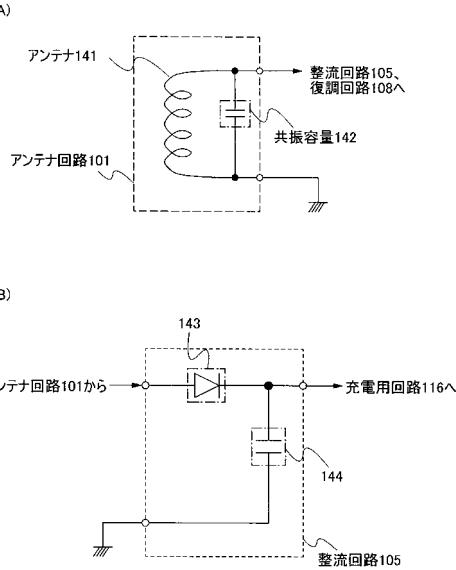

信に用いる周波数によって長さが異なる。例えば周波数が 2 . 4 5 G H z の場合は、半波長ダイポールアンテナを設けるなら約 6 0 m m ( 1 / 2 波長 ) 、モノポールアンテナを設けるなら約 3 0 m m ( 1 / 4 波長 ) とすれば良い。本実施の形態におけるアンテナ回路 1 0 1 は、図 4 ( A ) に示すようにアンテナ 1 4 1 、共振容量 1 4 2 によって構成されるものとして説明し、アンテナ 1 4 1 及び共振容量 1 4 2 を併せてアンテナ回路 1 0 1 ということにする。

#### 【 0 0 3 3 】

また、整流回路 1 0 5 は、アンテナ回路 1 0 1 が受信する電磁波により誘導される交流信号を直流信号に変換する回路であればよい。例えば、図 4 ( B ) に示すように、整流特性を有するダイオード 1 4 3 、平滑容量 1 4 4 によって整流回路 1 0 5 を構成すればよい。

10

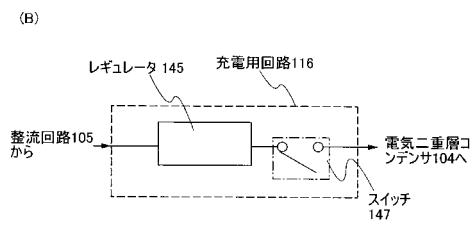

#### 【 0 0 3 4 】

充電用回路 1 1 6 は、整流回路 1 0 5 より入力された電気信号の電圧レベルを制御して電気二重層コンデンサ 1 0 4 に出力する回路であればよい。例えば、図 5 ( A ) に示すように、電圧を制御する回路であるレギュレータ 1 4 5 と整流特性を有するダイオード 1 4 6 で構成することができる。ダイオード 1 4 6 は、電気二重層コンデンサ 1 0 4 に充電された電力の漏洩を防止するものである。そのため、図 5 ( B ) に示すように、ダイオード 1 4 6 をスイッチ 1 4 7 に置き換えた構成としてもよい。スイッチ 1 4 7 を設ける場合、電気二重層コンデンサ 1 0 4 の充電が行われている状態ではオンにし、充電が行われていない状態ではオフとすることにより電気二重層コンデンサ 1 0 4 に充電された電力の漏洩を防止できる。

20

#### 【 0 0 3 5 】

図 2 に示すように、充電用回路 1 1 6 により電圧レベルが制御された電源電圧は、電気二重層コンデンサ 1 0 4 に入力され、電気二重層コンデンサ 1 0 4 に充電される。電気二重層コンデンサ 1 0 4 に充電された電力は、放電用回路 1 1 7 を介して負荷部 1 1 8 へ供給、つまり電気二重層コンデンサ 1 0 4 の放電が行われる。

#### 【 0 0 3 6 】

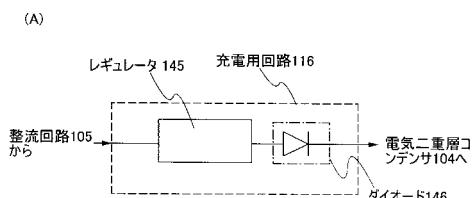

放電用回路 1 1 7 は、電気二重層コンデンサ 1 0 4 より出力された電圧レベルを制御して、電気二重層コンデンサ 1 0 4 の放電を制御する回路であればよい。例えば、図 6 ( A ) に示すように、スイッチ 5 0 1 と、電圧制御する回路であるレギュレータ 5 0 2 で構成することができる。スイッチ 5 0 1 のオン又はオフを制御することにより、電気二重層コンデンサ 1 0 4 から負荷部 1 1 8 への電力の供給の有無を制御することができる。

30

#### 【 0 0 3 7 】

また、電気二重層コンデンサ 1 0 4 の電圧値に応じてスイッチ 5 0 1 のオン又はオフを制御する構成としてもよい。例えば、図 6 ( A ) に示す構成にシュミットトリガー 5 0 3 を組み合わせた構成とすることができる(図 6 ( B ) 参照)。シュミットトリガー 5 0 3 は、スイッチング素子に履歴現象(ヒステリシス性)を持たせることができる。具体的には、入力電圧に対して上限値と下限値との2つのスレッショルドレベルを持ち、これらの値より入力が高くなるか、あるいは低くなるかによりオン、オフを制御することができる。例えば、電気二重層コンデンサ 1 0 4 の電圧値が 5 V 以上の場合にスイッチ 5 0 1 がオンし、3 V 以下でオフすることができる。つまり、電気二重層コンデンサ 1 0 4 に一定の電力が充電される場合に限って負荷部 1 1 8 に電力を供給する構成とすることができます。

40

#### 【 0 0 3 8 】

次に、R F I D 1 0 0 の基板上にアンテナ回路 1 0 1 、信号処理回路 1 0 2 と一体形成された充電用の電気二重層コンデンサ 1 0 4 について説明する。

#### 【 0 0 3 9 】

本実施の形態では、図 1 ( B ) のように基板 1 0 上に信号処理回路 1 0 2 を有する充電用回路 1 1 6 が形成されており、その上に電気二重層コンデンサ 1 0 4 が形成されている。電気二重層コンデンサ 1 0 4 の第 1 の電極 1 1 は、充電用回路 1 1 6 のトランジスタに電気的に接続されている。また、第 1 の電極 1 1 上には電解液層 1 2 が設けられていて、その上に第 2 の電極 1 3 が設けられている。つまり、少なくとも第 1 の電極 1 1 、電解液層

50

12、第2の電極13で電気二重層コンデンサ104を形成している。

**【0040】**

電気二重層コンデンサ104は、充電時は電極表面に電解液中のイオンを物理的に吸着し、放電時には電極表面のイオンを脱着させる。このように充放電に伴って電解液中のイオンは、電極界面に吸脱着する。そのため、電気化学反応を伴う二次電池と異なり充放電を繰り返しても、物質変化がない。したがって、二次電池に比べ、性能劣化が極めて少なく、また使用可能な温度範囲も広い。また、電気二重層コンデンサ104は、電極界面に電解液中のイオンが吸脱着することで充放電を行うため、放熱しない。そのため、充電用回路116を含む信号処理回路102上に電気二重層コンデンサ104を形成しても、充電用回路116のトランジスタや信号処理回路102のトランジスタへの熱による影響も抑制できる。

10

**【0041】**

なお、第1の電極11と第2の電極13は、化学的気相成長法(CVD法)やスパッタリング法等により、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pl)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層又は積層の導電膜から形成することができる。

**【0042】**

また、電気二重層コンデンサ104の電解液層12は、溶媒と電解質からなる電解液で構成される。電解質としては、溶媒中における解離度が高いこと、解離したイオンの移動度が高いこと、イオン種が酸化還元反応による分解などの副反応を受けにくいなどの性質を有するものを用いることが好ましい。たとえば、電解質として硫酸や水酸化カリウムなどを用いることができる。また溶媒としては、高い誘電率を持つこと、溶媒粘度が低いこと、酸化電位と還元電位の電位差が大きいなどの性質を有するものを用いることが好ましい。なお、溶媒は水溶液系と非水溶液系に分けることができる。水溶液系の溶媒の代表例は、水である。水溶液系は非水溶液系に比べ、電解液のコスト、安全性、充電の急速性の面で有利である。一方、非水溶液系の溶媒の代表例は、メタノール、アセトニトリル、プロピレンカーボネートなどである。非水溶液系は水溶液系に比べ、作動温度範囲が広いという面で有利である。また、電解液として、イオン性液体を用いても良い。ここでは、イオン性液体も電解液に含まれるものとする。また、電気二重層コンデンサの電解液層12としては、液漏れによる劣化故障を起こさず、イオン伝導度の低下が少ないゲル状固体電解液を用いることもできる。このゲル状固体電解液は、電解質と水に可溶であり酸性物質または塩基性物質に対してゲル状を呈する高分子化合物を有する。また、電気二重層コンデンサ104の電解液層12に、架橋剤などを混ぜておき加熱や紫外線照射をすることで、ゲル化することも可能である。このように、電気二重層コンデンサ104の電解液層12をゲル化することで、電解液が漏れることを容易に防ぐことができる。

20

30

**【0043】**

なお、電気二重層コンデンサ104による容量は、第1の電極11および第2の電極13と電解液層12との界面の面積に影響される。第1の電極11および第2の電極13の比表面積が大きいほど、電気二重層コンデンサ104による容量も大きくなる。そのため、第1の電極11および第2の電極13の上にこれら電極の比表面積を増大させる機能を有する層を設けても良い。当該層は、活性炭やナノレベルの炭素、例えばフラーレンや垂直配向したカーボンナノチューブ、や金属酸化物や導電性高分子等で形成することができる。例えば、電極上にスピンドル法などで金属触媒として機能する鉄、コバルト、ニッケル、銅などを塗布し、その後アーク放電法、レーザー蒸着法、レーザーアブレーション法、化学的気相成長法(CVD法)などにより、カーボンナノチューブなどのナノレベルの炭素を成長させることで、低抵抗であり、比表面積の大きい電極として機能させることができる。また、第1の電極11および第2の電極13を上述の材料を用いずに、上述の比表面積を増大させる機能を有する層で代用しても良い。

40

50

## 【0044】

セパレータ120は、電気二重層コンデンサ104の第1の電極11と第2の電極13の短絡を防ぐ役割を持つ。そのため、電解液中のイオンが通過することができる孔を有する多孔質の構造からなる。柔軟性があり、機械的強度があり、耐久性も高いポリエチレンまたはポリプロピレンなどの多孔性ポリマーフィルムなどを用いることができる。

## 【0045】

以上のように、充電用回路116上に電気二重層コンデンサ104を設けることで、電気二重層コンデンサをRFIDに実装する場合に比べて、薄型で軽量なRFIDを作製することができる。また、充電用回路116を有する信号処理回路102上に電気二重層コンデンサ104を設けることで、充電用回路116と電気二重層コンデンサ104を接続するための配線を短くすることができるため、電気二重層コンデンサ104と充電用回路116を有する信号処理回路102との間で生じる断線を防ぐことができる。10

## 【0046】

なお、本実施の形態は、本明細書中の実施例の記載と適宜組み合わせても良い。

## 【実施例1】

## 【0047】

本実施例では、上記実施の形態で示したRFIDの作製方法について説明する。

## 【0048】

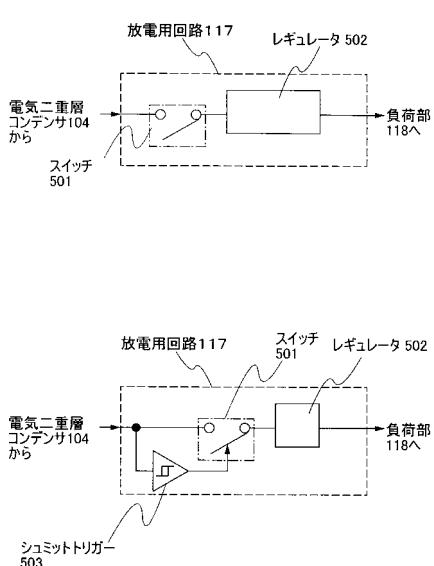

まず、図7(A)に示すように、基板701の一表面に下地膜として機能する絶縁膜704と半導体膜705(例えば、非晶質珪素を含む膜)を積層して形成する。なお、絶縁膜704および半導体膜705は、連続して形成することができる。20

## 【0049】

なお、基板701は、ガラス基板、石英基板、金属基板(例えばステンレス基板など)、セラミック基板、Si基板等の半導体基板から選択されるものである。他にもプラスチック基板として、ポリエチレンテレフタレート(PET)、ポリエチレンナフタレート(PEN)、ポリエーテルサルファン(PES)、アクリルなどの基板を選択することもできる。

## 【0050】

また、絶縁膜704は、化学的気相成長法(CVD法)やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x>y>0)、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x>y>0)等の絶縁材料を用いて形成する。例えば、絶縁膜704を2層構造とする場合、第1層目の絶縁膜として窒化酸化シリコン膜を形成し、第2層目の絶縁膜として酸化窒化シリコン膜を形成するとよい。また、第1層目の絶縁膜として窒化シリコン膜を形成し、第2層目の絶縁膜として酸化シリコン膜を形成してもよい。絶縁膜704は、基板701から半導体膜705への不純物元素が混入するのを防ぐプロッキング層として機能し、このように、プロッキング層として機能する絶縁膜704を形成することによって、基板701からNaなどのアルカリ金属やアルカリ土類金属が、半導体膜705に悪影響を与えることを防ぐことができる。なお、基板701として石英を用いるような場合には絶縁膜704を省略してもよい。30

## 【0051】

また、半導体膜705は、スパッタリング法、LPCVD法、プラズマCVD法等により、25~200nm(好ましくは30~150nm)の厚さで形成する。40

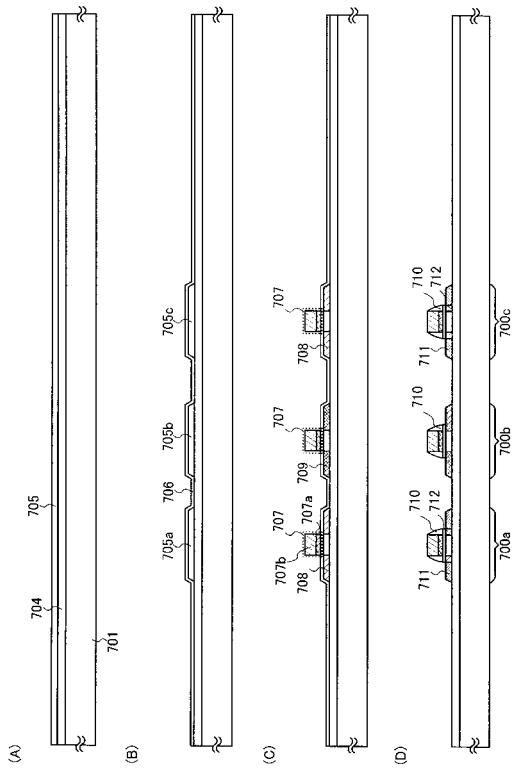

## 【0052】

次に、図7(B)に示すように、半導体膜705にレーザー光を照射して結晶化を行う。なお、レーザー光の照射と、RTA又はファーネスアニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法とを組み合わせた方法等により半導体膜705の結晶化を行ってもよい。その後、図7(B)に示すように、得られた結晶質半導体膜を所望の形状にエッチングして、結晶化した結晶質半導体膜705a~705cを形成し、当該結晶質半導体膜705a~705cを覆うようにゲート絶縁膜706を形成する。

## 【0053】

10

20

30

40

50

なお、ゲート絶縁膜706は、化学的気相成長法(CVD法)やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)( $x > y > 0$ )、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)( $x > y > 0$ )等の絶縁材料を用いて形成する。例えば、ゲート絶縁膜706を2層構造とする場合、第1層目の絶縁膜として酸化窒化シリコン膜を形成し、第2層目の絶縁膜として窒化酸化シリコン膜を形成するとよい。また、第1層目の絶縁膜として酸化シリコン膜を形成し、第2層目の絶縁膜として窒化シリコン膜を形成してもよい。

#### 【0054】

結晶質半導体膜705a～705cの作製工程の一例を以下に簡単に説明すると、まず、

10 プラズマCVD法を用いて、膜厚50～60nmの非晶質半導体膜を形成する。次に、結

晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体膜上に保持させた後、

非晶質半導体膜に脱水素化の処理(500、1時間)と、熱結晶化の処理(550、

4時間)を行って結晶質半導体膜を形成する。その後、レーザー光を照射し、フォトリソ

グラフィ法を用いることによって結晶質半導体膜705a～705cを形成する。なお、結

晶化を助長する金属元素を用いる熱結晶化を行わずに、レーザー光の照射だけで非晶質半

導体膜の結晶化を行ってもよい。

#### 【0055】

なお、結晶化に用いるレーザー発振器としては、連続発振型のレーザー(CWレーザー)

やパルス発振型のレーザー(パルスレーザー)を用いることができる。ここで用いること

ができるレーザービームは、Arレーザー、Krレーザー、エキシマレーザーなどの気体

レーザー、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、もしくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、ガラスレーザー、

ルビーレーザー、アレキサンンドライトレーザー、Ti:サファイアレーザー、銅蒸気レ

ーザーまたは金蒸気レーザーのうち一種または複数種から発振されるものを用いること

ができる。このようなレーザービームの基本波、及びこれらの基本波の第2高調波から第4高

調波のレーザービームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:

YVO<sub>4</sub>レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いること

ができる。このときレーザーのパワー密度は0.01～10

30 0MW/cm<sup>2</sup>程度(好ましくは0.1～10MW/cm<sup>2</sup>)が必要である。そして、走

査速度を10～2000cm/sec程度として照射する。なお、単結晶のYAG、YV

O<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、もしくは多結晶

(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパント

としてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加さ

れているものを媒質とするレーザー、Arイオンレーザー、またはTi:サファイアレ

ーザーは、連続発振をさせることができ、Qスイッチ動作やモード同期などを行

うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz

以上の発振周波数でレーザービームを発振させると、半導体膜がレーザーによって溶

融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波

数が低いパルスレーザーを用いる場合と異なり、半導体膜中において固液界面を連続的に

移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得

ることができる。

#### 【0056】

また、ゲート絶縁膜706は、半導体膜705a～705cに対し高密度プラズマ処理を行

い、表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xe

などの希ガスと、酸素、酸化窒素(NO<sub>2</sub>)、アンモニア、窒素、水素などの混合ガスを

導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入によ

り行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマ

で生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカル(NHラジ

50

カルを含む場合もある)によって、半導体膜の表面を酸化又は窒化することができる。

#### 【0057】

このような高密度プラズマを用いた処理により、1~20nm、代表的には5~10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜(結晶性シリコン、あるいは多結晶シリコン)の表面を直接酸化(もしくは窒化)するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの結晶粒界でも酸化が強くされることはないため、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相酸化することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。10

#### 【0058】

なお、ゲート絶縁膜706は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それにプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。

#### 【0059】

また、半導体膜に対し、連続発振レーザービームもしくは10MHz以上の周波数で発振するレーザービームを照射しながら一方向に走査して結晶化させて得られた半導体膜705a~705cは、そのビームの走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向(チャネル形成領域が形成されたときにキャリアが流れる方向)に合わせてトランジスタを配置し、上記ゲート絶縁層を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高い薄膜トランジスタ(TFT:Thin Film Transistor)を得ることができる。20

#### 【0060】

次に、ゲート絶縁膜706上に、第1の導電膜と第2の導電膜とを積層して形成する。ここでは、第1の導電膜は、化学的気相成長法(CVD法)やスパッタリング法等により、20~100nmの厚さで形成する。第2の導電膜は、100~400nmの厚さで形成する。第1の導電膜と第2の導電膜は、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素又はこれらの元素を主成分とする合金材料もしくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶硅素に代表される半導体材料により形成する。第1の導電膜と第2の導電膜の組み合わせの例を挙げると、窒化タンタル膜とタングステン膜、窒化タングステン膜とタングステン膜、窒化モリブデン膜とモリブデン膜等が挙げられる。タングステンや窒化タンタルは、耐熱性が高いため、第1の導電膜と第2の導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。30

#### 【0061】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、半導体膜705a~705cの上方にゲート電極707を形成する。ここでは、ゲート電極707として、第1の導電膜707aと第2の導電膜707bの積層構造で設けた例を示している。40

#### 【0062】

次に、図7(C)に示すように、ゲート電極707をマスクとして半導体膜705a~705cに、イオンドープ法またはイオン注入法により、n型を付与する不純物元素を低濃度に添加し、その後、フォトリソグラフィ法によりレジストからなるマスクを選択的に形成して、半導体膜705bにp型を付与する不純物元素を高濃度に添加する。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不50

純物元素としては、ボロン（B）やアルミニウム（Al）やガリウム（Ga）等を用いることができる。ここでは、n型を付与する不純物元素としてリン（P）を用い、 $1 \times 10^{15} \sim 1 \times 10^{17} / \text{cm}^3$  の濃度で含まれるように半導体膜705a～705cに選択的に導入し、n型を示す不純物領域708を形成する。また、p型を付与する不純物元素としてボロン（B）を用い、 $1 \times 10^{17} \sim 1 \times 10^{20} / \text{cm}^3$  の濃度で含まれるように選択的に半導体膜705bに導入し、p型を示す不純物領域709を形成する。

#### 【0063】

続いて、ゲート絶縁膜706とゲート電極707を覆うように、絶縁膜を形成する。絶縁膜は、プラズマCVD法やスパッタリング法等により、珪素、珪素の酸化物又は珪素の窒化物等の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。次に、絶縁膜を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、ゲート電極707の側面に接する絶縁膜710（サイドウォールともよばれる）を形成する。絶縁膜710は、LDD（Lightly Doped Drain）領域を形成する際のドーピング用のマスクとして用いる。

10

#### 【0064】

続いて、フォトリソグラフィ法により形成したレジストからなるマスクと、ゲート電極707および絶縁膜710をマスクとして用いて、半導体膜705a、705cにn型を付与する不純物元素を高濃度に添加して、n型を示す不純物領域711を形成する。ここでは、n型を付与する不純物元素としてリン（P）を用い、 $1 \times 10^{17} \sim 1 \times 10^{20} / \text{cm}^3$  の濃度で含まれるように半導体膜705a、705cに選択的に導入し、不純物領域708より高濃度のn型を示す不純物領域711を形成する。

20

#### 【0065】

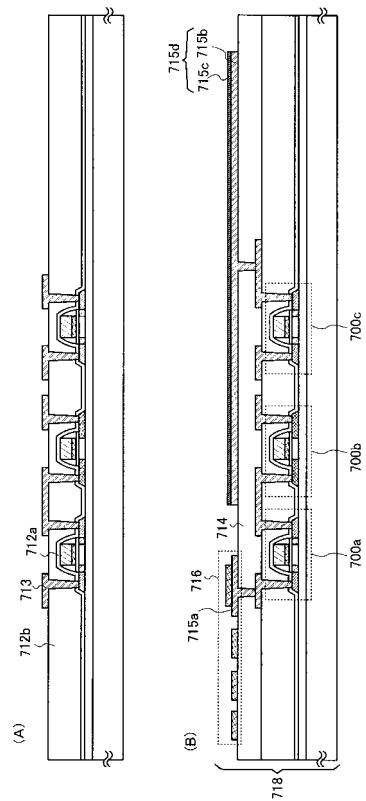

以上の工程により、図7（D）に示すように、nチャネル型薄膜トランジスタ700a、700cとpチャネル型薄膜トランジスタ700bが形成される。

#### 【0066】

なお、nチャネル型薄膜トランジスタ700aは、ゲート電極707と重なる半導体膜705aの領域にチャネル形成領域が形成され、ゲート電極707及び絶縁膜710と重ならない領域にソース領域又はドレイン領域を形成する不純物領域711が形成され、絶縁膜710と重なる領域であってチャネル形成領域と不純物領域711の間に低濃度不純物領域（LDD領域712）が形成されている。また、nチャネル型薄膜トランジスタ700cも同様にチャネル形成領域、低濃度不純物領域及び不純物領域711が形成されている。

30

#### 【0067】

また、pチャネル型薄膜トランジスタ700bは、ゲート電極707と重なる半導体膜705bの領域にチャネル形成領域が形成され、ゲート電極707と重ならない領域にソース領域又はドレイン領域を形成する不純物領域709が形成されている。なお、ここでは、pチャネル型薄膜トランジスタ700bには、LDD領域を設けていないが、pチャネル型薄膜トランジスタにLDD領域を設けてもよいし、nチャネル型薄膜トランジスタにLDD領域を設けない構成としてもよい。

40

#### 【0068】

次に、図8（A）に示すように、半導体膜705a～705c、ゲート電極707等を覆うように、絶縁膜を単層または積層して形成し、当該絶縁膜上に薄膜トランジスタ700a～700cのソース領域又はドレイン領域を形成する不純物領域709、711と電気的に接続する導電膜713を形成する。絶縁膜は、化学的気相成長法（CVD法）、スパッタリング法、SOG法、液滴吐出法、スクリーン印刷法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ等の有機材料やシリコサン材料等により、単層または積層で形成する。ここでは、当該絶縁膜を2層で設け、1層目の絶縁膜712aとして窒化酸化珪素膜で形成し、2層目の絶縁膜712bとして酸化窒化珪素膜で形成する。また、導電膜713は、半導体膜705a～705cのソース電極又はドレイン電極を形成する。

50

## 【0069】

なお、絶縁膜712a、712bを形成する前、または絶縁膜712a、712bのうちの1つまたは複数の薄膜を形成した後に、半導体膜の結晶性の回復や半導体膜に添加された不純物元素の活性化、半導体膜の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザーアニール法またはRTA法などを適用するとよい。

## 【0070】

また、導電膜713は、化学的気相成長法(CVD法)やスパッタリング法等により、アルミニウム(Al)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜713は、例えば、バリア膜とアルミニウムシリコン(Al-Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(Al-Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜713を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができるとよい。

10

## 【0071】

次に、導電膜713を覆うように、絶縁膜714を形成し、当該絶縁膜714上に、半導体膜705a～705cのソース電極又はドレイン電極を形成する導電膜713とそれぞれ電気的に接続する導電膜715a、715bを形成する。実施の形態で示したように、導電膜713とそれぞれ電気的に接続する導電膜715a、715bを、化学的気相成長法(CVD法)やスパッタリング法等により、アルミニウム(Al)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層又は積層で形成する。その後、導電膜715b上にスピンドル法などで金属触媒として機能する鉄、コバルト、ニッケル、銅などを形成する。そして、アーク放電法、レーザー蒸着法、レーザーアブレーション法、化学的気相成長法(CVD法)により、カーボンナノチューブなどのナノレベルの炭素を成長させることで、電極の比表面積を増大させる機能を有する層715cを形成する。これにより、低抵抗であり、比表面積の大きい電気二重層コンデンサの第1の電極を形成する。なお、この導電膜715bと層715cは、電気二重層コンデンサの第1の電極715dとして機能する。また、第1の電極715dは、導電膜715bを用いずに、第1の電極715dを活性炭やナノレベルの炭素、例えばフラーレンや垂直配向したカーボンナノチューブなど、や金属酸化物や導電性高分子などの層715cのみで形成しても良い。例えば、活性炭を材料として第1の電極715dを形成する場合は、例えば以下の方法により形成することができる。まず、活性炭粉末と導電剤であるアセチレンブラックの混合物に、粘結剤であるポリテトラフルオロエチレンを加えて混合した後、150℃で1時間ほど減圧乾燥し、導電膜713上に貼り付けることにより、第1の電極715dを形成することもできる。

20

## 【0072】

なお、導電剤としては、アセチレンブラック以外にも、ケッテンブラックなどのカーボンブラック、天然黒鉛、熱膨張黒鉛、炭素纖維、酸化ルテニウム、酸化チタン、アルミニ

30

40

50

ウム、ニッケルなどの金属ファイバーなどを用いることができる。アセチレンブラックを用いる場合には、効果的に導電性を向上できるため、活性炭の重量の10～15wt%程度を用いることが好ましい。

#### 【0073】

なお、粘結剤としては、ポリテトラフルオロエチレン以外にも、ポリフッ化ビニリデン、カルボキシメチルセルロース、フルオロオレフィン共重合体架橋ポリマー、ポリビニルアルコール、ポリアクリル酸、ポリイミド、フェノール樹脂などを用いることができる。

#### 【0074】

続いて、図8(B)に示すように、導電膜715aにアンテナとして機能する導電膜716が電気的に接続されるように形成する。ここでは、アンテナとして機能する導電膜716が上記実施の形態で示したアンテナ回路101のアンテナ303に相当する。

10

#### 【0075】

なお、絶縁膜714は、化学的気相成長法(CVD法)やスパッタ法等により、酸化珪素(SiO<sub>x</sub>)、窒化珪素(SiN<sub>x</sub>)、酸化窒化珪素(SiO<sub>x</sub>N<sub>y</sub>)(x>y)、窒化酸化珪素(SiN<sub>x</sub>O<sub>y</sub>)(x>y)等の酸素または窒素を有する絶縁膜やDLC(ダイヤモンドライカーボン)等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。なお、シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン(Si)と酸素(O)との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基(例えばアルキル基、アリール基)が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

20

#### 【0076】

また、導電膜716は、化学的気相成長法(CVD法)、スパッタリング法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム(Al)、チタン(Ti)、銀(Ag)、銅(Cu)、金(Au)、白金(Pt)、ニッケル(Ni)、パラジウム(Pd)、タンタル(Ta)、モリブデン(Mo)から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層構造又は積層構造で形成する。

30

#### 【0077】

例えば、スクリーン印刷法を用いてアンテナとして機能する導電膜716を形成する場合には、粒径が数nmから数十μmの導電体粒子を有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀(Ag)、金(Au)、銅(Cu)、ニッケル(Ni)、白金(Pt)、パラジウム(Pd)、タンタル(Ta)、モリブデン(Mo)およびチタン(Ti)等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコーン樹脂等の有機樹脂が挙げられる。また、導電膜の形成にあたり、導電性のペーストを押し出した後に焼成することが好ましい。例えば、導電性のペーストの材料として、銀を主成分とする微粒子(例えば粒径1nm以上100nm以下)を用いる場合、150～300の温度範囲で焼成することにより硬化させて導電膜を得ることができる。また、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよく、この場合は粒径20μm以下の微粒子を用いることが好ましい。はんだや鉛フリーはんだは、低コストであるといった利点を有している。

40

#### 【0078】

上述した方法で、図8(B)に示すように、薄膜トランジスタ700a～700c、導電膜716、電気二重層コンデンサ104の第1の電極715d等を含む層(以下、「素子形成層718」と記す)を作製することができる。

50

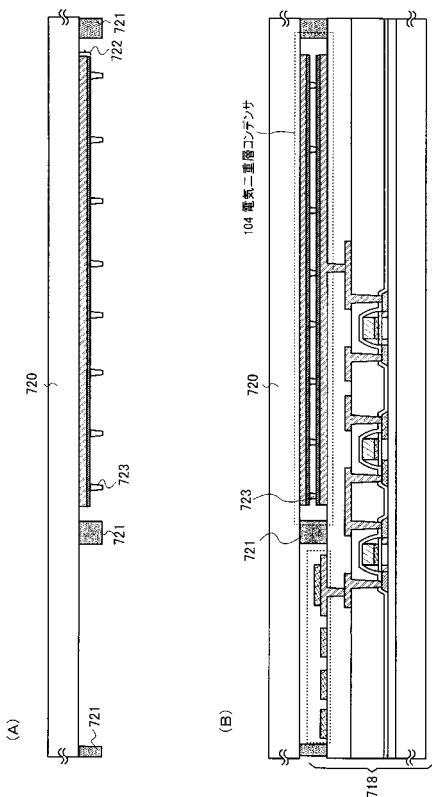

## 【0079】

次に、第2の基板720上に形成される電極722等について説明する(図9(A))。電極722は、電気二重層コンデンサの第2の電極として機能する。なお、電極722は、第1の電極715dと同じ材料、同じ方法で形成すればよい。また、第2の基板720と第2の電極722との間に、化学的気相成長法(CVD法)やスパッタリング法等で、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x>y>0)、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x>y>0)等の絶縁材料を用いて、絶縁膜を形成しても良い。

## 【0080】

さらに、第2の基板720上にシール材721を描画する。シール材721としては、アクリル系光硬化樹脂やアクリル系熱硬化樹脂を用いればよい。シール材721はフィラー(直径6μm~24μm)を含み、且つ、粘度40~400Pa·sのものを用い、アンテナ回路101のアンテナとして機能する導電膜716を形成する領域と電気二重層コンデンサ104を形成する領域に分ける。なお、シール材には注入口をあけておき、後で注入口から電解液を注入する。シール材721にフィラーを入れておくことで、電気二重層コンデンサの第1の電極715dと第2の電極722間のギャップを制御することが容易になる。特に、RFID100における電気二重層コンデンサ104の占有面積が大きい場合や第1の基板701と第2の基板720に柔軟性を有する基板を用いる場合には、第1の電極715d上に絶縁物からなるフィラーを設けたり、第1の電極715dと第2の電極722間にセパレータを設けることで、第1の電極715dと第2の電極722間の短絡を防ぐ。さらに、第1の電極715dと第2の電極722間のギャップを制御するために、スペーサ723を設けても良い。スペーサ723の作製方法としては、感光性アクリルなどの有機絶縁材料を第2の基板720の全面にスピンドルコート法により塗布し、これを一連のフォトリソグラフィの工程を行うことにより、第2の基板720上に残った感光性アクリルがスペーサとしての役割を果たす。この方法だと、露光時のマスクパターン次第でスペーサの配置したい場所に露光できるため、電気二重層コンデンサ104を形成する領域の所望の位置にスペーサ723を配置することができる。このように、スペーサ723を配置することで、第1の電極715dと第2の電極722間の短絡をさらに防ぐことが可能となる。

## 【0081】

次に、図9(B)に示すように、図8(B)に示す充電用回路116などを有する信号処理回路を有する素子形成層718と図9(A)に示す第2の電極722およびシール材721を有する第2の基板720を貼り合わせる。

## 【0082】

なお、シール材の注入口を2カ所以上開けておくことで、毛細管現象を利用して大気下で電解液を注入することができる。この場合、電解液の粘度は低い方が早く注入することができる。また、注入口を1カ所だけ開けておく場合には、減圧下で電解液を注入することができる。

## 【0083】

また、第2の基板720上にシール材721を描画する代わりに、図10(B)に示すように、充電用回路116などを有する信号処理回路102を有する第1の基板701上にシール材721を描画しても良い。この場合は、インクジェット法などの液滴吐出法を用いて、導電膜716を形成する領域以外の電気二重層コンデンサ104を形成する領域に電解質と溶媒からなる電解液を滴下し、電解液層12を形成する。例えば、ディスペンサにより、無駄なく必要な電解液の量だけを導電膜716を形成する領域以外の電気二重層コンデンサ104を形成する領域に、電解液を滴下すれば良い。電解液としては、実施の形態で示した滴下可能な粘度を有するの材料を用いればよい。なお、インクジェット法などの液滴吐出法を用いる場合は、電解液の粘度は大きい方が好ましい。

## 【0084】

次に、図10(C)に示すように、第2の電極722を有する第2の基板720(図10

(A) )とシール材721を描画した充電用回路116などを有する信号処理回路102を有する素子形成層718(図10(B))を貼り合わせる。

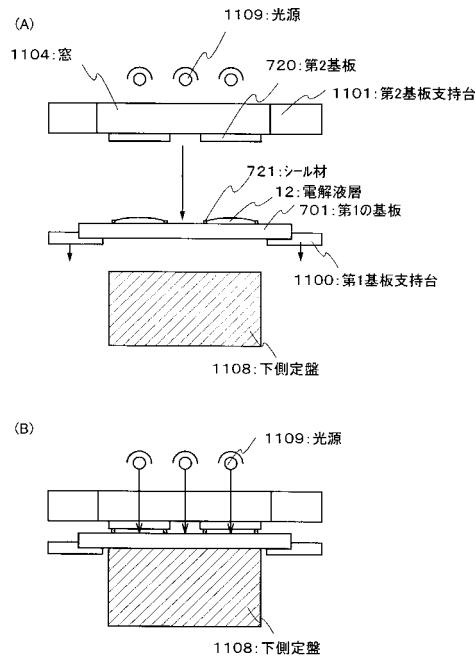

#### 【0085】

また、図11に貼り合わせ時または貼り合わせ後に紫外線照射や熱処理が可能な装置の例を示す。

#### 【0086】

図11は、1100は第1の基板701を保持する第1基板支持台、1101は第2の基板720を保持する第2基板支持台、1104は光源1109から紫外光などを透過させるための窓である。なお、上述したように、第1の基板701には既に、導電膜716を形成する領域以外の電気二重層コンデンサ104を形成する領域に、シール材721と電解液層12が形成されている。

10

#### 【0087】

下側定盤1108は加熱ヒータが内蔵されている。また、第2基板支持台には窓1104が設けられており、光源1109からの紫外光などを透過させるようになっている。ここでは図示していないが窓1104を通して基板の位置合わせを行う。また、対向基板となる第2の基板720は予め、第2基板支持台1101に固定しておく。図11(A)は貼り合わせ前の状態を示している。

20

#### 【0088】

貼り合わせ時には、第1基板支持台と第2基板支持台とを下降させた後、圧力をかけて第1の基板701と第2の基板720を貼り合わせ、紫外光を照射することによってシール材721を硬化させる。貼り合わせ時を図11(B)に示す。

#### 【0089】

なお、図11では、紫外線照射によりシール材721を硬化させたが、紫外線照射に加えて、熱処理を行ってもよい。

#### 【0090】

以上の工程により、電気二重層コンデンサの第1の電極715dと第2の電極722の間に電解液層12が保持される。本実施例では、電解液滴下、貼り合わせの工程を連続して行う。また、本実施例では、電解液に架橋剤などを混ぜておき熱処理や紫外線照射することで、シール材721の硬化と電気二重層コンデンサ104の電解液層12のゲル化を同時にできる。

30

#### 【0091】

このように、基板上に充電用の電気二重層コンデンサ104をアンテナ回路101、信号処理回路102などと一体的に形成した半導体装置を作製することができる。

#### 【0092】

なお、本実施例は、本明細書中の実施の形態及び他の実施例の記載と適宜組み合わせても良い。

#### 【実施例2】

#### 【0093】

本実施例では、特に充電用の電気二重層コンデンサ104をアンテナ回路101、信号処理回路102などと一体的に形成した半導体装置の作製方法について説明する。

40

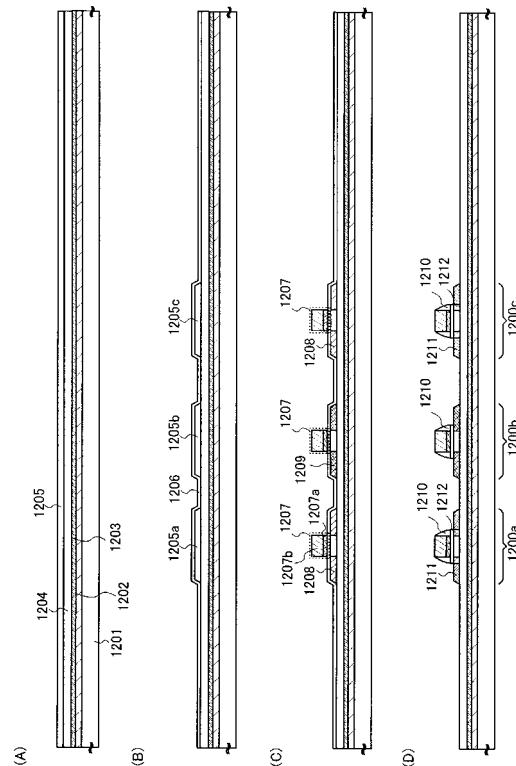

#### 【0094】

まず、図12(A)に示すように、基板1201の一表面に絶縁膜1202を介して剥離層1203を形成し、続けて下地膜として機能する絶縁膜1204と半導体膜1205(例えば、非晶質珪素を含む膜)を積層して形成する。なお、絶縁膜1202、剥離層1203、絶縁膜1204および半導体膜1205は、連続して形成することができる。

#### 【0095】

なお、基板1201は、ガラス基板、石英基板、金属基板(例えばステンレス基板など)、セラミック基板、Si基板等の半導体基板から選択されるものである。なお、本工程では、剥離層1203は、絶縁膜1202を介して基板1201の全面に設けているが、必要に応じて、基板1201の全面に剥離層を設けた後に、フォトリソグラフィ法により選

50

択的に設けてよい。

**【0096】**

また、絶縁膜1202、絶縁膜1204は、化学的気相成長法(CVD法)やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)(x > y > 0)、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)(x > y > 0)等の絶縁材料を用いて形成する。例えば、絶縁膜1202、1204を2層構造とする場合、第1層目の絶縁膜として窒化酸化シリコン膜を形成し、第2層目の絶縁膜として酸化窒化シリコン膜を形成するとよい。また、第1層目の絶縁膜として窒化シリコン膜を形成し、第2層目の絶縁膜として酸化シリコン膜を形成してもよい。絶縁膜1202は、基板1201から剥離層1203又はその上に形成される素子に不純物元素が混入するのを防ぐプロッキング層として機能し、絶縁膜1204は基板1201、剥離層1203からその上に形成される素子に不純物元素が混入するのを防ぐプロッキング層として機能する。このように、プロッキング層として機能する絶縁膜1202、1204を形成することによって、基板1201からNaなどのアルカリ金属やアルカリ土類金属や、剥離層1203から剥離層に含まれる不純物元素がこの上に形成する素子に悪影響を与えることを防ぐことができる。なお、基板1201として石英を用いるような場合には絶縁膜1202、1204を省略してもよい。10

**【0097】**

また、剥離層1203は、金属膜や金属膜と金属酸化膜の積層構造等を用いることができる。金属膜としては、タンゲステン(W)、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、ニオブ(Nb)、ニッケル(Ni)、コバルト(Co)、ジルコニウム(Zr)、亜鉛(Zn)、ルテニウム(Ru)、ロジウム(Rh)、パラジウム(Pd)、オスミウム(Os)、イリジウム(Ir)から選択された元素または当該元素を主成分とする合金材料もしくは化合物材料からなる膜を単層又は積層して形成する。また、これらの材料は、スパッタ法やプラズマCVD法等の各種CVD法等を用いて形成することができる。金属膜と金属酸化膜の積層構造としては、上述した金属膜を形成した後に、酸素雰囲気下またはN<sub>2</sub>O雰囲気下におけるプラズマ処理、酸素雰囲気下またはN<sub>2</sub>O雰囲気下における加熱処理を行うことによって、金属膜表面に当該金属膜の酸化物または酸化窒化物を設けることができる。例えば、金属膜としてスパッタ法や化学的気相成長法(CVD法)等によりタンゲステン膜を設けた場合、タンゲステン膜にプラズマ処理を行うことによって、タンゲステン膜表面にタンゲステン酸化物からなる金属酸化膜を形成することができる。また、この場合、タンゲステンの酸化物は、WO<sub>X</sub>で表され、Xは2~3であり、Xが2の場合(WO<sub>2</sub>)、Xが2.5の場合(W<sub>2</sub>O<sub>5</sub>)、Xが2.75の場合(W<sub>4</sub>O<sub>11</sub>)、Xが3の場合(WO<sub>3</sub>)などがある。タンゲステンの酸化物を形成するにあたり、上記に挙げたXの値に特に制約はなく、エッチングレート等を基に、どの酸化物を形成するかを決めるといい。また、プラズマ処理として、例えば上述した高密度プラズマ処理を行ってもよい。また、金属酸化膜の他にも、金属窒化物や金属酸化窒化物を用いてもよい。この場合、金属膜に窒素雰囲気下または窒素と酸素雰囲気下でプラズマ処理や加熱処理を行えばよい。30

**【0098】**

また、半導体膜1205は、スパッタリング法、LPCVD法、プラズマCVD法等により、25~200nm(好ましくは30~150nm)の厚さで形成する。40

**【0099】**

次に、半導体膜1205にレーザー光を照射して結晶化を行う。なお、レーザー光の照射と、RTA又はファーネスアニュール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法などを組み合わせた方法等により半導体膜1205の結晶化を行ってもよい。その後、図12(B)に示すように、得られた結晶質半導体膜を所望の形状にエッチングして、結晶化した結晶質半導体膜1205a~1205cを形成し、当該結晶質半導体膜1205a~1205cを覆うようにゲート絶縁膜1206を形成する。

**【0100】**

なお、ゲート絶縁膜1206は、化学的気相成長法(CVD法)やスパッタリング法等を用いて、酸化シリコン、窒化シリコン、酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>)( $x > y > 0$ )、窒化酸化シリコン(SiN<sub>x</sub>O<sub>y</sub>)( $x > y > 0$ )等の絶縁材料を用いて形成する。例えば、ゲート絶縁膜1206を2層構造とする場合、第1層目の絶縁膜として酸化窒化シリコン膜を形成し、第2層目の絶縁膜として窒化酸化シリコン膜を形成するとよい。また、第1層目の絶縁膜として酸化シリコン膜を形成し、第2層目の絶縁膜として窒化シリコン膜を形成してもよい。

#### 【0101】

結晶質半導体膜1205a～1205cの作製工程の一例を以下に簡単に説明すると、まず、プラズマCVD法を用いて、膜厚50～60nmの非晶質半導体膜を形成する。次に、結晶化を助長する金属元素であるニッケルを含む溶液を非晶質半導体膜上に保持させた後、非晶質半導体膜に脱水素化の処理(500、1時間)と、熱結晶化の処理(550、4時間)を行って結晶質半導体膜を形成する。その後、レーザー光を照射し、フォトリソグラフィ法を用いることによって結晶質半導体膜1205a～1205cを形成する。なお、結晶化を助長する金属元素を用いる熱結晶化を行わずに、レーザー光の照射だけで非晶質半導体膜の結晶化を行ってもよい。

10

#### 【0102】

なお、結晶化に用いるレーザー発振器としては、連続発振型のレーザー(CWレーザー)やパルス発振型のレーザー(パルスレーザー)を用いることができる。ここで用いることができるレーザービームは、Arレーザー、Krレーザー、エキシマレーザーなどの気体レーザー、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、もしくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、ガラスレーザー、ルビーレーザー、アレキサンンドライトレーザー、Ti:サファイアレーザー、銅蒸気レーザーまたは金蒸気レーザーのうち一種または複数種から発振されるものを用いることができる。このようなレーザービームの基本波、及びこれらの基本波の第2高調波から第4高調波のレーザービームを照射することで、大粒径の結晶を得ることができる。例えば、Nd:YVO<sub>4</sub>レーザー(基本波1064nm)の第2高調波(532nm)や第3高調波(355nm)を用いることができる。このときレーザーのパワー密度は0.01～100MW/cm<sup>2</sup>程度(好ましくは0.1～10MW/cm<sup>2</sup>)が必要である。そして、走査速度を10～2000cm/sec程度として照射する。なお、単結晶のYAG、YVO<sub>4</sub>、フォルステライト(Mg<sub>2</sub>SiO<sub>4</sub>)、YAlO<sub>3</sub>、GdVO<sub>4</sub>、もしくは多結晶(セラミック)のYAG、Y<sub>2</sub>O<sub>3</sub>、YVO<sub>4</sub>、YAlO<sub>3</sub>、GdVO<sub>4</sub>に、ドーパントとしてNd、Yb、Cr、Ti、Ho、Er、Tm、Taのうち1種または複数種添加されているものを媒質とするレーザー、Arイオンレーザー、またはTi:サファイアレーザーは、連続発振をさせることができ、Qスイッチ動作やモード同期などを行うことによって10MHz以上の発振周波数でパルス発振をさせることも可能である。10MHz以上の発振周波数でレーザービームを発振させると、半導体膜がレーザーによって溶融してから固化するまでの間に、次のパルスが半導体膜に照射される。従って、発振周波数が低いパルスレーザーを用いる場合と異なり、半導体膜中において固液界面を連続的に移動させることができるために、走査方向に向かって連続的に成長した結晶粒を得ることができる。

20

#### 【0103】

また、ゲート絶縁膜1206は、半導体膜1205a～1205cに対し前述の高密度プラズマ処理を行い、表面を酸化又は窒化することで形成しても良い。例えば、He、Ar、Kr、Xeなどの希ガスと、酸素、酸化窒素(NO<sub>2</sub>)、アンモニア、窒素、水素などの混合ガスを導入したプラズマ処理で形成する。この場合のプラズマの励起は、マイクロ波の導入により行うと、低電子温度で高密度のプラズマを生成することができる。この高密度プラズマで生成された酸素ラジカル(OHラジカルを含む場合もある)や窒素ラジカ

30

40

50

ル（N Hラジカルを含む場合もある）によって、半導体膜の表面を酸化又は窒化することができる。

#### 【0104】

このような高密度プラズマを用いた処理により、1~20nm、代表的には5~10nmの絶縁膜が半導体膜に形成される。この場合の反応は、固相反応であるため、当該絶縁膜と半導体膜との界面準位密度はきわめて低くすることができる。このような、高密度プラズマ処理は、半導体膜（結晶性シリコン、あるいは多結晶シリコン）を直接酸化（もしくは窒化）するため、形成される絶縁膜の厚さは理想的には、ばらつきをきわめて小さくすることができる。加えて、結晶性シリコンの結晶粒界でも酸化が強くされることがないため、非常に好ましい状態となる。すなわち、ここで示す高密度プラズマ処理で半導体膜の表面を固相酸化することにより、結晶粒界において異常に酸化反応をさせることなく、均一性が良く、界面準位密度が低い絶縁膜を形成することができる。10

#### 【0105】

なお、ゲート絶縁膜1206は、高密度プラズマ処理によって形成される絶縁膜のみを用いても良いし、それにプラズマや熱反応を利用したCVD法で酸化シリコン、酸窒化シリコン、窒化シリコンなどの絶縁膜を堆積し、積層させても良い。いずれにしても、高密度プラズマで形成した絶縁膜をゲート絶縁膜の一部又は全部に含んで形成されるトランジスタは、特性のばらつきを小さくすることができる。

#### 【0106】

また、半導体膜に対し、連続発振レーザービームもしくは10MHz以上の周波数で発振するレーザービームを照射しながら一方向に走査して結晶化させて得られた半導体膜1205a~1205cは、そのビームの走査方向に結晶が成長する特性がある。その走査方向をチャネル長方向（チャネル形成領域が形成されたときにキャリアが流れる方向）に合わせてトランジスタを配置し、上記ゲート絶縁層を組み合わせることで、特性ばらつきが小さく、しかも電界効果移動度が高い薄膜トランジスタ（TFT：Thin Film Transistor）を得ることができる。20

#### 【0107】

次に、ゲート絶縁膜1206上に、第1の導電膜と第2の導電膜とを積層して形成する。ここでは、第1の導電膜は、化学的気相成長法（CVD法）やスパッタリング法等により、20~100nmの厚さで形成する。第2の導電膜は、100~400nmの厚さで形成する。第1の導電膜と第2の導電膜は、タンタル（Ta）、タンゲステン（W）、チタン（Ti）、モリブデン（Mo）、アルミニウム（Al）、銅（Cu）、クロム（Cr）、ニオブ（Nb）等から選択された元素又はこれらの元素を主成分とする合金材料もしくは化合物材料で形成する。または、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成する。第1の導電膜と第2の導電膜の組み合わせの例を挙げると、窒化タンタル膜とタンゲステン膜、窒化タンゲステン膜とタンゲステン膜、窒化モリブデン膜とモリブデン膜等が挙げられる。タンゲステンや窒化タンタルは、耐熱性が高いため、第1の導電膜と第2の導電膜を形成した後に、熱活性化を目的とした加熱処理を行うことができる。また、2層構造ではなく、3層構造の場合は、モリブデン膜とアルミニウム膜とモリブデン膜の積層構造を採用するとよい。30

#### 【0108】

次に、フォトリソグラフィ法を用いてレジストからなるマスクを形成し、ゲート電極とゲート線を形成するためのエッチング処理を行って、半導体膜1205a~1205cの上方にゲート電極1207を形成する。ここでは、ゲート電極1207として、第1の導電膜1207aと第2の導電膜1207bの積層構造で設けた例を示している。

#### 【0109】

次に、図12（C）に示すように、ゲート電極1207をマスクとして半導体膜1205a~1205cに、イオンドープ法またはイオン注入法により、n型を付与する不純物元素を低濃度に添加し、その後、フォトリソグラフィ法によりレジストからなるマスクを選択的に形成して、半導体膜1205bにp型を付与する不純物元素を高濃度に添加する。40

n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用いることができる。ここでは、n型を付与する不純物元素としてリン(P)を用い、 $1 \times 10^{15} \sim 1 \times 10^{19} / \text{cm}^3$ の濃度で含まれるように半導体膜1205a～1205cに選択的に導入し、n型を示す不純物領域1208を形成する。また、p型を付与する不純物元素としてボロン(B)を用い、 $1 \times 10^{19} \sim 1 \times 10^{20} / \text{cm}^3$ の濃度で含まれるように選択的に半導体膜1205bに導入し、p型を示す不純物領域1209を形成する。

#### 【0110】

続いて、ゲート絶縁膜1206とゲート電極1207を覆うように、絶縁膜を形成する。

絶縁膜は、プラズマCVD法やスパッタリング法等により、珪素、珪素の酸化物又は珪素の窒化物等の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。次に、絶縁膜を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、ゲート電極1207の側面に接する絶縁膜1210(サイドウォールともよばれる)を形成する。絶縁膜1210は、LDD(Lightly Doped Drain)領域を形成する際のドーピング用のマスクとして用いる。

#### 【0111】

続いて、フォトリソグラフィ法により形成したレジストからなるマスクと、ゲート電極1207および絶縁膜1210をマスクとして用いて、半導体膜1205a、1205cにn型を付与する不純物元素を高濃度に添加して、n型を示す不純物領域1211を形成する。ここでは、n型を付与する不純物元素としてリン(P)を用い、 $1 \times 10^{19} \sim 1 \times 10^{20} / \text{cm}^3$ の濃度で含まれるように半導体膜1205a、1205cに選択的に導入し、不純物領域1208より高濃度のn型を示す不純物領域1211を形成する。

#### 【0112】

以上の工程により、図12(D)に示すように、nチャネル型薄膜トランジスタ1200a、1200cとpチャネル型薄膜トランジスタ1200bが形成される。

#### 【0113】

なお、nチャネル型薄膜トランジスタ1200aは、ゲート電極1207と重なる半導体膜1205aの領域にチャネル形成領域が形成され、ゲート電極1207及び絶縁膜1210と重ならない領域にソース領域又はドレイン領域を形成する不純物領域1211が形成され、絶縁膜1210と重なる領域であってチャネル形成領域と不純物領域1211の間に低濃度不純物領域(LDD領域1212)が形成されている。また、nチャネル型薄膜トランジスタ1200cも同様にチャネル形成領域、低濃度不純物領域1212及び不純物領域1211が形成されている。

#### 【0114】

また、pチャネル型薄膜トランジスタ1200bは、ゲート電極1207と重なる半導体膜1205cの領域にチャネル形成領域が形成され、ゲート電極1207と重ならない領域にソース領域又はドレイン領域を形成する不純物領域1209が形成されている。なお、ここでは、pチャネル型薄膜トランジスタ1200bには、LDD領域を設けていないが、pチャネル型薄膜トランジスタにLDD領域を設けてもよいし、nチャネル型薄膜トランジスタにLDD領域を設けない構成としてもよい。

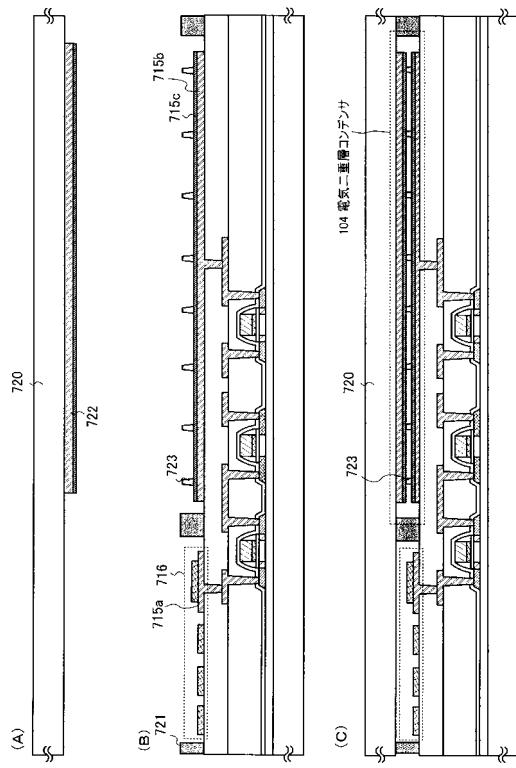

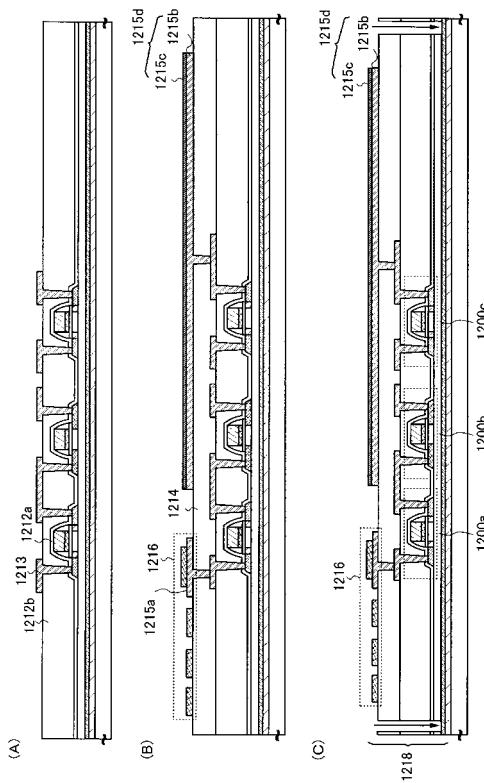

#### 【0115】

次に、図13(A)に示すように、半導体膜1205a～1205c、ゲート電極1207等を覆うように、絶縁膜を単層または積層して形成し、当該絶縁膜上に薄膜トランジスタ1200a～1200cのソース領域又はドレイン領域を形成する不純物領域1209、1211と電気的に接続する導電膜1213を形成する。絶縁膜は、化学的気相成長法(CVD法)、スパッタリング法、SOG法、液滴吐出法、スクリーン印刷法等により、珪素の酸化物や珪素の窒化物等の無機材料、ポリイミド、ポリアミド、ベンゾシクロブテン、アクリル、エポキシ等の有機材料やシリコサン材料等により、単層または積層で形成する。ここでは、当該絶縁膜を2層で設け、1層目の絶縁膜1212aとして窒化酸化

10

20

30

40

50

珪素膜で形成し、2層目の絶縁膜1212bとして酸化窒化珪素膜で形成する。また、導電膜1213は、半導体膜1205a～1205cのソース電極又はドレイン電極を形成する。

#### 【0116】

なお、絶縁膜1212a、1212bを形成する前、または絶縁膜1212a、1212bのうちの1つまたは複数の薄膜を形成した後に、半導体膜の結晶性の回復や半導体膜に添加された不純物元素の活性化、半導体膜の水素化を目的とした加熱処理を行うとよい。加熱処理には、熱アニール、レーザーアニール法またはRTA法などを適用するとよい。

#### 【0117】

また、導電膜1213は、化学的気相成長法(CVD法)やスパッタリング法等により、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Plt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜1213は、例えば、バリア膜とアルミニウムシリコン(A1-Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(A1-Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜1213を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。

#### 【0118】

次に、導電膜1213を覆うように、絶縁膜1214を形成し、当該絶縁膜1214上に、半導体膜1205a～1205cのソース電極又はドレイン電極を形成する導電膜1213とそれぞれ電気的に接続する導電膜1215a、1215bを形成する。実施例1で示したように、導電膜1213とそれぞれ電気的に接続する導電膜1215a、1215bを、化学的気相成長法(CVD法)やスパッタリング法等により、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Plt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層又は積層で形成する。その後、導電膜1215b上にスピンドル法などで金属触媒として機能する鉄、コバルト、ニッケル、銅などを形成する。そして、アーク放電法、レーザー蒸着法、レーザーアブレーション法、化学的気相成長法(CVD法)により、カーボンナノチューブなどのナノレベルの炭素を成長させることで、電極の比表面積を増大させる機能を有する層1215cを形成する。これにより、低抵抗であり、比表面積の大きい電気二重層コンデンサの第1の電極を作製できる。なお、この導電膜1215bと層1215cは、電気二重層コンデンサの第1の電極1215dとして機能する。また、第1の電極1215dは、導電膜1215bを用いずに、活性炭やナノレベルの炭素、例えばフラーレンや垂直配向したカーボンナノチューブなどや金属酸化物や導電性高分子などの層1215cのみで形成しても良い。

#### 【0119】

続いて、図13(B)に示すように、導電膜1215aにアンテナとして機能する導電膜1216が電気的に接続されるように形成する。ここでは、アンテナとして機能する導電

10

20

30

40

50

膜 1216 が上記実施の形態で示したアンテナ回路 101 のアンテナ 303 に相当する。

#### 【0120】

なお、絶縁膜 1214 は、化学的気相成長法（CVD法）やスパッタ法等により、酸化珪素（SiO<sub>x</sub>）、窒化珪素（SiN<sub>x</sub>）、酸化窒化珪素（SiO<sub>x</sub>N<sub>y</sub>）（x > y）、窒化酸化珪素（SiN<sub>x</sub>O<sub>y</sub>）（x > y）等の酸素または窒素を有する絶縁膜やDLC（ダイヤモンドライクカーボン）等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。なお、シロキサン材料とは、Si-O-Si結合を含む材料に相当する。シロキサンは、シリコン（Si）と酸素（O）との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基（例えばアルキル基、アリール基）が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。10

#### 【0121】

また、導電膜 1216 は、化学的気相成長法（CVD法）、スパッタリング法、スクリーン印刷やグラビア印刷等の印刷法、液滴吐出法、ディスペンサ法、メッキ法等を用いて、導電性材料により形成する。導電性材料は、アルミニウム（Al）、チタン（Ti）、銀（Ag）、銅（Cu）、金（Au）、白金（Pt）ニッケル（Ni）、パラジウム（Pd）、タンタル（Ta）、モリブデン（Mo）から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層構造又は積層構造で形成する。20

#### 【0122】

例えば、スクリーン印刷法を用いてアンテナとして機能する導電膜 1216 を形成する場合には、粒径が数 nm から数十 μm の導電体粒子を有機樹脂に溶解または分散させた導電性のペーストを選択的に印刷することによって設けることができる。導電体粒子としては、銀（Ag）、金（Au）、銅（Cu）、ニッケル（Ni）、白金（Pt）、パラジウム（Pd）、タンタル（Ta）、モリブデン（Mo）およびチタン（Ti）等のいずれか一つ以上の金属粒子やハロゲン化銀の微粒子、または分散性ナノ粒子を用いることができる。また、導電性ペーストに含まれる有機樹脂は、金属粒子のバインダー、溶媒、分散剤および被覆材として機能する有機樹脂から選ばれた一つまたは複数を用いることができる。代表的には、エポキシ樹脂、シリコーン樹脂等の有機樹脂が挙げられる。また、導電膜の形成にあたり、導電性のペーストを押し出した後に焼成することが好ましい。例えば、導電性のペーストの材料として、銀を主成分とする微粒子（例えば粒径 1 nm 以上 100 nm 以下）を用いる場合、150 ~ 300 の温度範囲で焼成することにより硬化させて導電膜を得ることができる。また、はんだや鉛フリーのはんだを主成分とする微粒子を用いてもよく、この場合は粒径 20 μm 以下の微粒子を用いることが好ましい。はんだや鉛フリーはんだは、低コストであるといった利点を有している。30

#### 【0123】

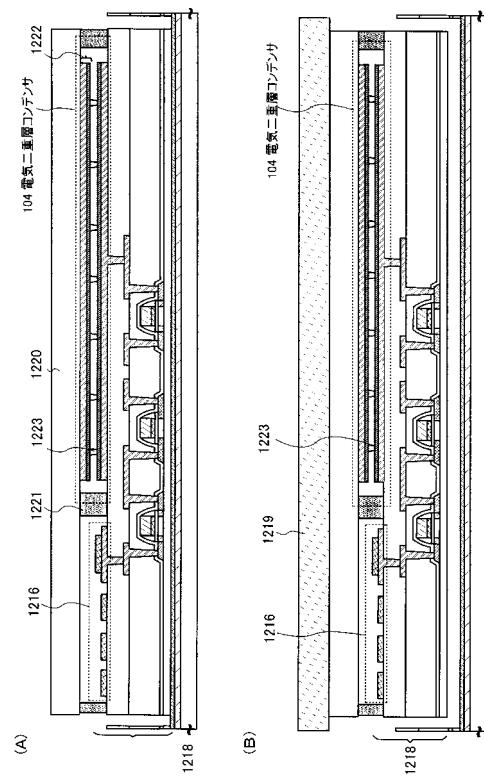

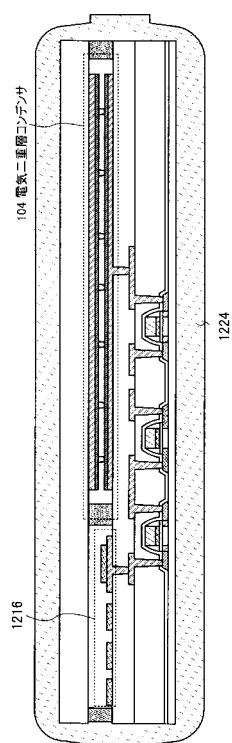

次に、薄膜トランジスタ 1200a ~ 1200c、導電膜 1216 等を含む層（以下、「素子形成層 1218」と記す）を基板 1201 から剥離する。ここでは、図 13 (C) に示すように、レーザー光（例えば UV 光）を照射することによって、薄膜トランジスタ 1200a ~ 1200c を避けた領域に開口部を形成する。その後、図 14 (B) に示すように、物理的な力を用いて基板 1201 から素子形成層 1218 を剥離することができる。ただし、基板 1201 から素子形成層 1218 を剥離する前に、実施例 1 と同様の方法で、図 14 (A) に示すように、導電膜を有するフレキシブル基板 1220 と素子形成層 1218 をシール材 1221 により貼り合わせる。なお、前記導電膜は電気二重層コンデンサの第 2 の電極 1222 として機能する。シール材 1221 にフィラーを入れておくことで、電気二重層コンデンサ 104 の第 1 の電極 1215d と第 2 の電極 1222 間のギャップを制御することが容易になる。また、上記の実施例 1 のように、第 1 の電極 1215d 上に絶縁物からなるフィラーを設けたり、第 1 の電極 1215d と第 2 の電極 1222 との間にセパレータを設けることで、第 1 の電極 1215d と第 2 の電極 1222 間の4050

短絡を防ぐことができる。さらに、第1の電極1215dと第2の電極1222間のギャップを制御するために、実施例1のように、スペーサ1223を設けても良い。なお、フレキシブル基板1220として、第1のシート材を用いることもできる。

#### 【0124】

また、基板1201から素子形成層1218を剥離する前に、形成した開口部にエッティング剤を導入して、剥離層1203を選択的に除去してもよい。エッティング剤は、フッ化ハロゲンまたはハロゲン間化合物を含む気体又は液体を使用する。例えば、フッ化ハロゲンを含む気体として三フッ化塩素(C1F<sub>3</sub>)を使用する。そうすると、図14(B)に示すように、素子形成層1218は、基板1201から剥離された状態となる。なお、剥離層1203は、全て除去せず一部分を残存させてもよい。こうすることによって、エッティング剤の消費量を抑え剥離層の除去に要する処理時間を短縮することが可能となる。また、剥離層1203の除去を行った後にも、基板1201上に素子形成層1218を保持しておくことも可能となる。また、素子形成層1218が剥離された基板1201を再利用することによって、コストの削減をすることができる。10

#### 【0125】

本実施例では、当該素子形成層1218の一方の面(フレキシブル基板1220の露出した面)に第1のシート材1219を貼り合わせた後、基板1201から素子形成層1218を剥離する。

#### 【0126】

次に、図15に示すように、素子形成層1218の他方の面(剥離により露出した面)に、第2のシート材1224を貼り合わせた後、加熱処理と加圧処理の一方又は両方を行って第2のシート材1224を貼り合わせる。この加熱処理により、シール材1221を硬化させる。なお、熱処理に加えて、紫外線照射を行ってもよい。これにより、電解液に架橋剤などを混ぜておき熱処理や紫外線照射をすることで、シール材1221の硬化と電気二重層コンデンサ104の電解液層12のゲル化同時に行うことができる。なお、第1のシート材1219、第2のシート材1224として、ホットメルトフィルム等を用いることができる。20

#### 【0127】

また、第1のシート材1219、第2のシート材1224として、静電気等を防止する帯電防止対策を施したフィルム(以下、帯電防止フィルムと記す)を用いることもできる。帯電防止フィルムとしては、帯電防止可能な材料を樹脂中に分散させたフィルム、及び帯電防止可能な材料が貼り付けられたフィルム等が挙げられる。帯電防止可能な材料が設けられたフィルムは、片面に帯電防止可能な材料を設けたフィルムであってもよいし、両面に帯電防止可能な材料を設けたフィルムであってもよい。さらに、片面に帯電防止可能な材料が設けられたフィルムは、帯電防止可能な材料が設けられた面をフィルムの内側になるように層に貼り付けてもよいし、フィルムの外側になるように貼り付けてもよい。なお、帯電防止可能な材料はフィルムの全面、あるいは一部に設けてあればよい。ここでの帯電防止可能な材料としては、金属、インジウムと錫の酸化物(ITO)、両性界面活性剤や陽イオン性界面活性剤や非イオン性界面活性剤等の界面活性剤を用いることができる。また、他にも帯電防止材料として、側鎖にカルボキシル基および4級アンモニウム塩基をもつ架橋性共重合体高分子を含む樹脂材料等を用いることができる。これらの材料をフィルムに貼り付けたり、練り込んだり、塗布することによって帯電防止フィルムとすることができます。帯電防止フィルムで封止を行うことによって、商品として取り扱う際に、外部からの静電気等によって半導体素子に悪影響が及ぶことを抑制することができる。3040

#### 【0128】

以上の工程により、導電膜1216を形成する領域以外の電気二重層コンデンサ104を形成する領域に、電気二重層コンデンサ104の第1の電極1215dと第2の電極1222の間に電解液層12が保持される。

#### 【0129】

このように、充電用の電気二重層コンデンサ104をアンテナ回路101、信号処理回路50

102などと一体的に形成した半導体装置を作製することができる。このように作製された半導体装置であるRFIDは、球面を有する物体に貼り付けても、また電気二重層コンデンサ104と信号処理回路102を接続するための導電膜1213と電気二重層コンデンサの第1の電極1215dにかかる曲げ応力は小さく、断線を防ぐことができる。さらに、従来のように電気二重層コンデンサ104をRFID100に実装するための異方性導電膜を用いる必要がなくなるため、RFID100を薄型化することができる。

#### 【0130】

なお、本実施例は、本明細書中の実施の形態および他の実施例の記載と適宜組み合わせても良い。

#### 【実施例3】

10

#### 【0131】

本実施例では、上記実施例1、2とは異なる本発明の半導体装置の作製方法について、図16乃至図18に示す部分断面図を用いて説明する。本発明の半導体装置におけるトランジスタは上記実施形態で説明した絶縁基板上の薄膜トランジスタの他、単結晶基板上のMOSトランジスタで構成することもできる。

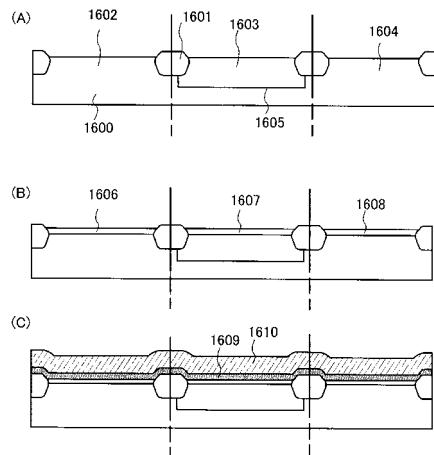

#### 【0132】

まず、半導体基板1600に素子を分離した領域1602、1603、1604（以下、領域1602、1603、1604とも記す）を形成する（図16（A）参照）。半導体基板1600に設けられた領域1602、1603、1604は、それぞれ絶縁膜1601（フィールド酸化膜ともいう）によって分離されている。なお、ここでは、半導体基板1600としてn型の導電型を有する単結晶Si基板を用い、半導体基板1600の領域1603にpウェル1605を設けた例を示している。

20

#### 【0133】

基板1600は、半導体基板であれば特に限定されず用いることができる。例えば、n型又はp型の導電型を有する単結晶Si基板、化合物半導体基板（GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板等）、貼り合わせ法またはSIMOX（Separation by Implanted Oxygen）法を用いて作製されたSOI（Silicon on Insulator）基板等を用いることができる。

#### 【0134】

30

素子分離領域1602、1603、1604は、選択酸化法（LOCOS（Local Oxidation of Silicon）法）又はトレンチ分離法等を適宜用いることができる。

#### 【0135】

また、半導体基板1600の領域1603に形成されたpウェル1605は、半導体基板1600にp型の導電型を有する不純物元素を選択的に導入することによって形成することができる。p型を示す不純物元素としては、ボロン（B）やアルミニウム（Al）やガリウム（Ga）等を用いることができる。

#### 【0136】

40

なお、本実施例では、半導体基板1600としてn型の導電型を有する半導体基板を用いているため、領域1602、1604には不純物元素の導入を行っていないが、n型を示す不純物元素を導入することにより領域1602、1604にnウェルを形成してもよい。n型を示す不純物元素としては、リン（P）やヒ素（As）等を用いることができる。一方、p型の導電型を有する半導体基板を用いる場合には、領域1602、1604にn型を示す不純物元素を導入してnウェルを形成し、領域1603には不純物元素の導入を行わない構成としてもよい。

#### 【0137】

次に、図16（B）に示すように領域1602、1603、1604を覆うように絶縁膜1606、1607、1608をそれぞれ形成する。

#### 【0138】

50

絶縁膜 1606、1607、1608は、例えば、熱処理を行い半導体基板1600に設けられた領域1602、1603、1604の表面を酸化させることにより酸化珪素膜で形成することができる。また、熱酸化法により酸化珪素膜を形成した後に、窒化処理を行うことによって酸化珪素膜の表面を窒化させることにより、酸化珪素膜と酸素と窒素を有する膜(酸窒化珪素膜)との積層構造で形成してもよい。

#### 【0139】

他にも、上述したように、プラズマ処理を用いて絶縁膜1606、1607、1608を形成してもよい。例えば、半導体基板1600に設けられた領域1602、1603、1604の表面に高密度プラズマ処理により酸化処理又は窒化処理を行うことにより、絶縁膜1606、1607、1608として酸化珪素(SiO<sub>x</sub>)膜又は窒化珪素(SiN<sub>x</sub>)膜で形成することができる。また、高密度プラズマ処理により領域1602、1603、1604の表面に酸化処理を行った後に、再度高密度プラズマ処理を行うことによって窒化処理を行ってもよい。この場合、領域1602、1603、1604の表面に接して酸化珪素膜が形成され、当該酸化珪素膜上に酸窒化珪素膜が形成され、絶縁膜1606、1607、1608は酸化珪素膜と酸窒化珪素膜とが積層された膜となる。また、熱酸化法により領域1602、1603、1604の表面に酸化珪素膜を形成した後に高密度プラズマ処理により酸化処理又は窒化処理を行ってもよい。10

#### 【0140】

なお、絶縁膜1606、1607、1608は、後に完成されるトランジスタにおいてゲート絶縁膜として機能する。20

#### 【0141】

次に、図16(C)に示すように領域1602、1603、1604の上方に形成された絶縁膜1606、1607、1608を覆うように導電膜を形成する。ここでは、導電膜として、導電膜1609と導電膜1610を順に積層して形成した例を示している。もちろん、導電膜は、単層又は3層以上の積層構造で形成してもよい。

#### 【0142】

導電膜1609、1610としては、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素またはこれらの元素を主成分とする合金材料もしくは化合物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。30

#### 【0143】

ここでは、導電膜1609として窒化タンタルを用いて形成し、その上に導電膜1610としてタングステンを用いて積層構造で設ける。また、他にも、導電膜1609として、窒化タングステン、窒化モリブデン又は窒化チタンから選ばれた単層又は積層膜を用い、導電膜1610として、タンタル、モリブデン、チタンから選ばれた単層又は積層膜を用いることができる。

#### 【0144】

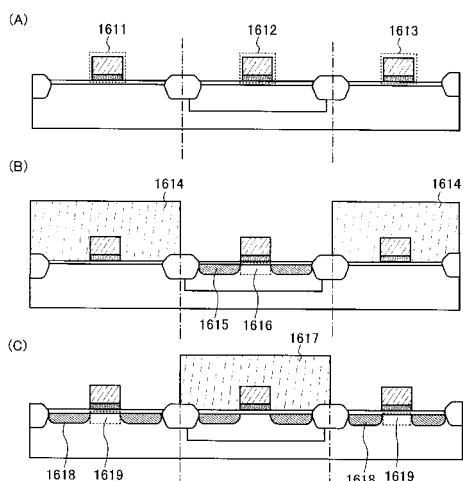

次に、積層して設けられた導電膜1609、1610を選択的にエッチングして除去することによって、領域1602、1603、1604の上方の一部に導電膜1609、1610を残存させ、図17(A)に示すようにそれぞれゲート電極1611、1612、1613を形成する。40

#### 【0145】

次に、領域1602、1604を覆うようにレジストマスク1614を選択的に形成し、当該レジストマスク1614、ゲート電極1612をマスクとして領域1603に不純物元素を導入することによって不純物領域を形成する(図17(B)参照)。不純物元素としては、n型を付与する不純物元素又はp型を付与する不純物元素を用いる。n型を示す不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を示す不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウム(Ga)等を用い50

ることができる。ここでは、不純物元素として、リン( P )を用いる。

**【 0 1 4 6 】**

不純物元素を導入することによって、図 17 ( B ) に示すように領域 1603 にソース領域又はドレイン領域を形成する不純物領域 1615 とチャネル形成領域 1616 が形成される。

**【 0 1 4 7 】**

次に、図 17 ( C ) に示すように領域 1603 を覆うようにレジストマスク 1617 を選択的に形成し、当該レジストマスク 1617 、ゲート電極 1611 、 1613 をマスクとして領域 1602 、 1604 に不純物元素を導入することによって不純物領域を形成する。不純物元素としては、 n 型を付与する不純物元素又は p 型を付与する不純物元素を用いる。<sup>10</sup> n 型を示す不純物元素としては、リン( P ) やヒ素( As ) 等を用いることができる。 p 型を示す不純物元素としては、ボロン( B ) やアルミニウム( Al ) やガリウム( Ga ) 等を用いることができる。ここでは、図 17 ( B ) で領域 1603 に導入した不純物元素と異なる導電型を有する不純物元素( 例えば、ボロン( B ) )を導入する。その結果、領域 1602 、 1604 にソース領域又はドレイン領域を形成する不純物領域 1618 とチャネル形成領域 1619 が形成される。

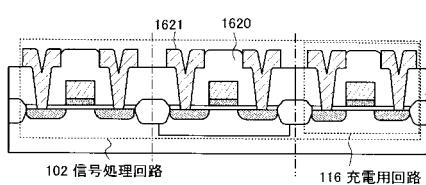

**【 0 1 4 8 】**

次に、図 18 に示すように絶縁膜 1606 、 1607 、 1608 とゲート電極 1611 、 1612 、 1613 を覆うように第 2 の絶縁膜 1620 を形成し、当該第 2 の絶縁膜 1620 上に領域 1602 、 1603 、 1604 にそれぞれ形成された不純物領域 1615 、 1618 と電気的に接続する配線 1621 を形成する。<sup>20</sup>

**【 0 1 4 9 】**

第 2 の絶縁膜 1620 は、化学的気相成長法( CVD 法) やスパッタ法等により、酸化珪素( SiO<sub>x</sub> ) 、窒化珪素( SiNx ) 、酸化窒化珪素( SiO<sub>x</sub>N<sub>y</sub> )( x > y ) 、窒化酸化珪素( SiN<sub>x</sub>O<sub>y</sub> )( x > y ) 等の酸素または窒素を有する絶縁膜や DLC ( ダイヤモンドライクカーボン ) 等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロオクテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。なお、シロキサン材料とは、 Si - O - Si 結合を含む材料に相当する。シロキサンは、シリコン( Si ) と酸素( O ) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基( 例えばアルキル基、アリール基 ) が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。<sup>30</sup>

**【 0 1 5 0 】**

配線 1621 は、化学的気相成長法( CVD 法) やスパッタリング法等により、アルミニウム( Al ) 、タンゲステン( W ) 、チタン( Ti ) 、タンタル( Ta ) 、モリブデン( Mo ) 、ニッケル( Ni ) 、白金( Pt ) 、銅( Cu ) 、金( Au ) 、銀( Ag ) 、マンガン( Mn ) 、ネオジム( Nd ) 、炭素( C ) 、シリコン( Si ) から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。配線 1621 は、例えば、バリア膜とアルミニウムシリコン( Al - Si ) 膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン( Al - Si ) 膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、配線 1621 を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていたとしても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタク<sup>40</sup>

トをとることができる。

**【0151】**

なお、トランジスタの構造は上記の構造に限定されるものではなく、例えば、逆スタガ構造、フィンFET構造等でも良い。なお、フィンFET構造では、トランジスタサイズの微細化に伴う短チャネル効果を抑制することができる。

**【0152】**

領域1604に形成されたトランジスタを用いて、実施の形態および実施例1、2で示した充電用回路116を形成することができる。また、領域1602、1603、1604に形成されたトランジスタを用いて、実施の形態および実施例1、2で示した信号処理回路102を形成することができる。なお、電気二重層コンデンサ104は、実施例1、2と同様に、領域1602、1603、1604に形成されたトランジスタ上に形成することができる。

10

**【0153】**

また、半導体基板1600を研磨することで、薄膜化された単結晶基板上のMOSトランジスタを作製することができる。

**【0154】**

また、本実施例は本明細書中の他の実施の形態および他の実施例の記載と適宜組み合わせても良い。

**【実施例4】**

**【0155】**

20

本実施例では、上記実施例3とは異なる本発明の半導体装置が有するトランジスタの作製方法について、図19乃至図22に示す部分断面図を用いて説明する。

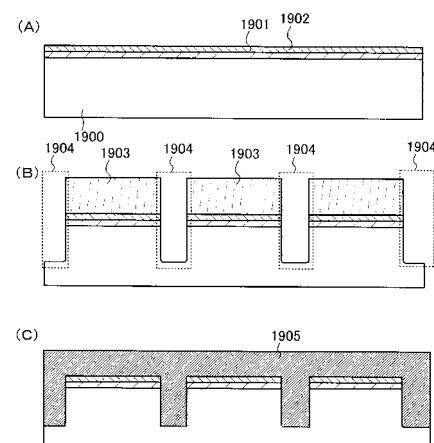

**【0156】**

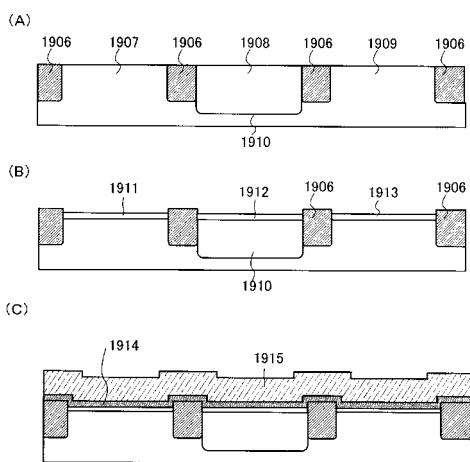

まず、図19(A)に示すように基板1900上に絶縁膜を形成する。ここでは、n型の導電型を有する単結晶Siを基板1900として用い、当該基板1900上に絶縁膜1901と絶縁膜1902を形成する。例えば、基板1900に熱処理を行うことにより絶縁膜1901として酸化珪素(SiO<sub>x</sub>)を形成し、当該絶縁膜1901上に化学的気相成長法(CVD法)を用いて窒化珪素(SiNx)を成膜する。

**【0157】**

また、基板1900は、半導体基板であれば特に限定されず用いることができる。例えば、n型又はp型の導電型を有する単結晶Si基板、化合物半導体基板(GaAs基板、InP基板、GaN基板、SiC基板、サファイア基板、ZnSe基板等)、貼り合わせ法またはSIMOX(Separation by Implanted Oxygen)法を用いて作製されたSOI(Silicon on Insulator)基板等を用いることができる。

30

**【0158】**

また、絶縁膜1902は、絶縁膜1901を形成した後に高密度プラズマ処理により当該絶縁膜1901を窒化することにより設けてもよい。なお、基板1900上に設ける絶縁膜は単層又は3層以上の積層構造で設けてもよい。

**【0159】**

40

次に、図19(B)に示すように絶縁膜1902上に選択的にレジストマスク1903のパターンを形成し、当該レジストマスク1903をマスクとして選択的にエッチングを行うことによって、基板1900に選択的に凹部1904を形成する。基板1900、絶縁膜1901、1902のエッチングとしては、プラズマを利用したドライエッチングにより行うことができる。

**【0160】**

次に、図19(C)に示すようにレジストマスク1903のパターンを除去した後、基板1900に形成された凹部1904を充填するように絶縁膜1905を形成する。

**【0161】**

絶縁膜1905は、化学的気相成長法(CVD法)やスパッタリング法等を用いて、酸

50

化シリコン、窒化シリコン、酸化窒化シリコン ( $\text{SiO}_x\text{N}_y$ ) ( $x > y > 0$ )、窒化酸化シリコン ( $\text{SiN}_x\text{O}_y$ ) ( $x > y > 0$ ) 等の絶縁材料を用いて形成する。ここでは、絶縁膜 1905 として、常圧 CVD 法または減圧 CVD 法により TEOS (テトラエトキシシラン) ガスを用いて酸化珪素膜を形成する。

#### 【0162】

次に、図 20 (A) に示すように研削処理、研磨処理又は CMP (Chemical Mechanical Polishing) 処理を行うことによって、基板 1900 の表面を露出させる。ここでは、基板 1900 の表面を露出させることにより、基板 1900 の凹部 1904 に形成された絶縁膜 1906 間に領域 1907、1908、1909 が設けられる。なお、絶縁膜 1906 は、基板 1900 の表面に形成された絶縁膜 1905 が研削処理、研磨処理又は CMP 処理により除去されることにより得られたものである。続いて、p 型の導電型を有する不純物元素を選択的に導入することによって、領域 1908 に p ウェル 1910 を形成する。

10

#### 【0163】

p 型を示す不純物元素としては、ボロン (B) やアルミニウム (Al) やガリウム (Ga) 等を用いることができる。ここでは、不純物元素として、ボロン (B) を領域 1908 に導入する。

#### 【0164】

なお、本実施例では、基板 1900 として n 型の導電型を有する半導体基板を用いているため、領域 1907、1909 には不純物元素の導入を行っていないが、n 型を示す不純物元素を導入することにより領域 1907、1909 に n ウェルを形成してもよい。n 型を示す不純物元素としては、リン (P) やヒ素 (As) 等を用いることができる。

20

#### 【0165】

一方、p 型の導電型を有する半導体基板を用いる場合には、領域 1907、1909 に n 型を示す不純物元素を導入して n ウェルを形成し、領域 1908 には不純物元素の導入を行わない構成としてもよい。

#### 【0166】

次に、図 20 (B) に示すように基板 1900 の領域 1907、1908、1909 の表面上に絶縁膜 1911、1912、1913 をそれぞれ形成する。

#### 【0167】

絶縁膜 1911、1912、1913 は、例えば、熱処理を行い基板 1900 に設けられた領域 1907、1908、1909 の表面を酸化させることにより酸化珪素膜で絶縁膜 1911、1912、1913 を形成することができる。また、熱酸化法により酸化珪素膜を形成した後に、窒化処理を行うことによって酸化珪素膜の表面を窒化させることにより、酸化珪素膜と酸素と窒素を有する膜 (酸窒化珪素膜) との積層構造で形成してもよい。

#### 【0168】

他にも、上述したように、プラズマ処理を用いて絶縁膜 1911、1912、1913 を形成してもよい。例えば、基板 1900 に設けられた領域 1907、1908、1909 の表面に高密度プラズマ処理により酸化処理又は窒化処理を行うことにより、絶縁膜 1911、1912、1913 として酸化珪素 ( $\text{SiO}_x$ ) 膜又は窒化珪素 ( $\text{SiN}_x$ ) 膜で形成することができる。また、高密度プラズマ処理により領域 1907、1908、1909 の表面に酸化処理を行った後に、再度高密度プラズマ処理を行うことによって窒化処理を行ってもよい。この場合、領域 1907、1908、1909 の表面に接して酸化珪素膜が形成され、当該酸化珪素膜上に酸窒化珪素膜が形成され、絶縁膜 1911、1912、1913 は酸化珪素膜と酸窒化珪素膜とが積層された膜となる。また、熱酸化法により領域 1907、1908、1909 の表面に酸化珪素膜を形成した後に高密度プラズマ処理により酸化処理又は窒化処理を行ってもよい。

40

#### 【0169】

なお、基板 1900 の領域 1907、1908、1909 に形成された絶縁膜 1911

50

、1912、1913は、後に完成されるトランジスタにおいてゲート絶縁膜として機能する。

#### 【0170】

次に、図20(C)に示すように基板1900に設けられた領域1907、1908、1909の上方に形成された絶縁膜1911、1912、1913を覆うように導電膜を形成する。ここでは、導電膜として、導電膜1914と導電膜1915を順に積層して形成した例を示している。もちろん、導電膜は、単層又は3層以上の積層構造で形成してもよい。

#### 【0171】

導電膜1914、1915としては、タンタル(Ta)、タングステン(W)、チタン(Ti)、モリブデン(Mo)、アルミニウム(Al)、銅(Cu)、クロム(Cr)、ニオブ(Nb)等から選択された元素またはこれらの元素を主成分とする合金材料もしくは化合物材料で形成することができる。また、これらの元素を窒化した金属窒化膜で形成することもできる。他にも、リン等の不純物元素をドーピングした多結晶珪素に代表される半導体材料により形成することもできる。

#### 【0172】

ここでは、導電膜1914として窒化タンタルを用いて形成し、その上に導電膜1915としてタングステンを用いて積層構造で設ける。また、他にも、導電膜1914として、窒化タンタル、窒化タングステン、窒化モリブデン又は窒化チタンから選ばれた単層又は積層膜を用い、導電膜1915として、タングステン、タンタル、モリブデン、チタンから選ばれた単層又は積層膜を用いることができる。

#### 【0173】

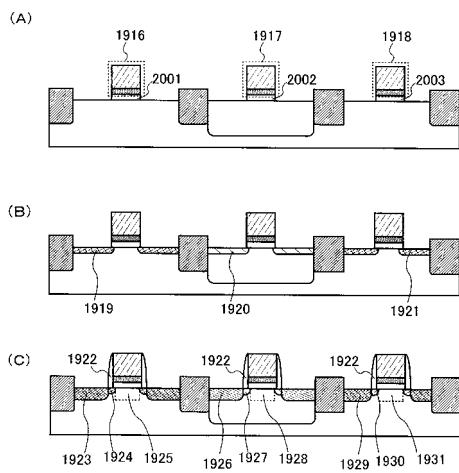

次に、図21(A)に示すように積層して設けられた導電膜1914、1915を選択的にエッティングして除去することによって、基板1900の領域1907、1908、1909の上方の一部に導電膜1914、1915を残存させ、それぞれゲート電極として機能する導電膜1916、1917、1918を形成する。また、ここでは、基板1900において、導電膜1916、1917、1918と重ならない領域1907、1908、1909の表面が露出するようとする。

#### 【0174】

具体的には、基板1900の領域1907において、導電膜1916の下方に形成された絶縁膜1911のうち当該導電膜1916と重ならない部分を選択的に除去し、導電膜1916と絶縁膜の端部が一致するように絶縁膜2001を形成する。また、領域1908において、導電膜1917の下方に形成された絶縁膜1912のうち当該導電膜1917と重ならない部分を選択的に除去し、導電膜1917と絶縁膜の端部が一致するように絶縁膜2002を形成する。また、領域1909において、導電膜1918の下方に形成された絶縁膜1913のうち当該導電膜1918と重ならない部分を選択的に除去し、導電膜1918と絶縁膜の端部が一致するように絶縁膜2003を形成する。

#### 【0175】

この場合、導電膜1916、1917、1918の形成と同時に重ならない部分の絶縁膜等を除去してもよいし、導電膜1916、1917、1918を形成後残存したレジストマスク又は当該導電膜1916、1917、1918をマスクとして重ならない部分の絶縁膜等を除去してもよい。

#### 【0176】

次に、図21(B)に示すように基板1900の領域1907、1908、1909に不純物元素を選択的に導入する。ここでは、領域1908に導電膜1917をマスクとしてn型を付与する低濃度の不純物元素を選択的に導入し、不純物領域1920を形成する。一方、領域1907、1909には導電膜1916、1918をマスクとしてp型を付与する低濃度の不純物元素を選択的に導入し、不純物領域1919、1921を形成する。n型を付与する不純物元素としては、リン(P)やヒ素(As)等を用いることができる。p型を付与する不純物元素としては、ボロン(B)やアルミニウム(Al)やガリウ

10

20

30

40

50

$\mu$  (G a) 等を用いることができる。

#### 【0177】

次に、導電膜 1916、1917、1918 の側面に接するサイドウォール 1922 を形成する。具体的には、プラズマ CVD 法やスパッタリング法等により、珪素、珪素の酸化物又は珪素の窒化物の無機材料を含む膜や、有機樹脂などの有機材料を含む膜を、単層又は積層して形成する。そして、当該絶縁膜を、垂直方向を主体とした異方性エッチングにより選択的にエッチングして、導電膜 1916、1917、1918 の側面に接するよう 10 に形成することができる。なお、サイドウォール 1922 は、LDD (Lightly Doped Drain) 領域を形成する際のドーピング用のマスクとして用いる。また、ここでは、サイドウォール 1922 は、導電膜 1916、1917、1918 の下方に形成された絶縁膜 2001、2002、2003 にも接するように形成されている。

#### 【0178】

続いて、当該サイドウォール 1922、導電膜 1916、1917、1918 をマスクとして基板 1900 の領域 1907、1908、1909 に不純物元素を導入することによって、ソース領域又はドレイン領域として機能する不純物領域を形成する（図 21 (C) 参照）。ここでは、基板 1900 の領域 1908 にサイドウォール 1922 と導電膜 1917 をマスクとして高濃度の n 型を付与する不純物元素を導入し、領域 1907、1909 にサイドウォール 1922 と導電膜 1916、1918 をマスクとして高濃度の p 型を付与する不純物元素を導入する。

#### 【0179】

その結果、基板 1900 の領域 1907 には、ソース領域又はドレイン領域を形成する不純物領域 1923 と、LDD 領域を形成する低濃度不純物領域 1924 と、チャネル形成領域 1925 が形成される。また、基板 1900 の領域 1908 には、ソース領域又はドレイン領域を形成する不純物領域 1926 と、LDD 領域を形成する低濃度不純物領域 1927 と、チャネル形成領域 1928 が形成される。また、基板 1900 の領域 1909 には、ソース領域又はドレイン領域を形成する不純物領域 1929 と、LDD 領域を形成する低濃度不純物領域 1930 と、チャネル形成領域 1931 が形成される。

#### 【0180】

なお、本実施例では、導電膜 1916、1917、1918 と重ならない基板 1900 の領域 1907、1908、1909 を露出させた状態で不純物元素の導入を行っている。従って、基板 1900 の領域 1907、1908、1909 にそれぞれ形成されるチャネル形成領域 1925、1928、1931 は導電膜 1916、1917、1918 と自己整合的に形成することができる。

#### 【0181】

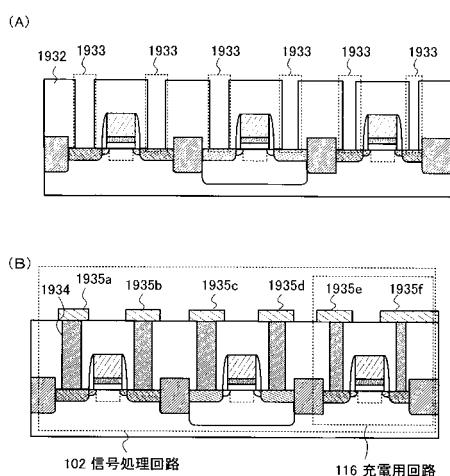

次に、図 22 (A) に示すように基板 1900 の領域 1907、1908、1909 上に設けられた絶縁膜や導電膜等を覆うように第 2 の絶縁膜 1932 を形成し、当該第 2 の絶縁膜 1932 に開口部 1933 を形成する。

#### 【0182】

第 2 の絶縁膜 1932 は、化学的気相成長法 (CVD 法) やスパッタ法等により、酸化珪素 (SiO<sub>x</sub>)、窒化珪素 (SiN<sub>x</sub>)、酸化窒化珪素 (SiO<sub>x</sub>N<sub>y</sub>) ( $x > y$ )、窒化酸化珪素 (SiN<sub>x</sub>O<sub>y</sub>) ( $x > y$ ) 等の酸素または窒素を有する絶縁膜や DLC (ダイヤモンドライクカーボン) 等の炭素を含む膜、エポキシ、ポリイミド、ポリアミド、ポリビニルフェノール、ベンゾシクロブテン、アクリル等の有機材料またはシロキサン樹脂等のシロキサン材料からなる単層または積層構造で設けることができる。なお、シロキサン材料とは、Si - O - Si 結合を含む材料に相当する。シロキサンは、シリコン (Si) と酸素 (O) との結合で骨格構造が構成される。置換基として、少なくとも水素を含む有機基 (例えばアルキル基、アリール基) が用いられる。置換基として、フルオロ基を用いることもできる。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

#### 【0183】

10

20

30

40

50

次に、図22(B)に示すように化学的気相成長法(CVD法)を用いて開口部1933に導電膜1934を形成し、当該導電膜1934と電気的に接続するように絶縁膜1932上に導電膜1935a～1935fを選択的に形成する。

#### 【0184】

導電膜1934、1935a～1935fは、化学的気相成長法(CVD法)やスパッタリング法等により、アルミニウム(A1)、タンゲステン(W)、チタン(Ti)、タンタル(Ta)、モリブデン(Mo)、ニッケル(Ni)、白金(Pt)、銅(Cu)、金(Au)、銀(Ag)、マンガン(Mn)、ネオジム(Nd)、炭素(C)、シリコン(Si)から選択された元素、又はこれらの元素を主成分とする合金材料もしくは化合物材料で、単層又は積層で形成する。アルミニウムを主成分とする合金材料とは、例えば、アルミニウムを主成分としニッケルを含む材料、又は、アルミニウムを主成分とし、ニッケルと、炭素と珪素の一方又は両方とを含む合金材料に相当する。導電膜1934、1935a～1935fは、例えば、バリア膜とアルミニウムシリコン(A1-Si)膜とバリア膜の積層構造、バリア膜とアルミニウムシリコン(A1-Si)膜と窒化チタン膜とバリア膜の積層構造を採用するとよい。なお、バリア膜とは、チタン、チタンの窒化物、モリブデン、又はモリブデンの窒化物からなる薄膜に相当する。アルミニウムやアルミニウムシリコンは抵抗値が低く、安価であるため、導電膜1934を形成する材料として最適である。また、上層と下層のバリア層を設けると、アルミニウムやアルミニウムシリコンのヒロックの発生を防止することができる。また、還元性の高い元素であるチタンからなるバリア膜を形成すると、結晶質半導体膜上に薄い自然酸化膜ができていても、この自然酸化膜を還元し、結晶質半導体膜と良好なコンタクトをとることができる。ここでは、導電膜1934は化学的気相成長法(CVD法)によりタンゲステン(W)を選択成長することにより形成することができる。10

#### 【0185】

以上の工程により、基板1900の領域1907、1909に形成されたp型のトランジスタと、領域1908に形成されたn型のトランジスタとを具備する半導体装置を得ることができる。

#### 【0186】

なお、トランジスタの構造は上記の構造に限定されるものではなく、例えば、逆スタガ構造、フィンFET構造等でも良い。なお、フィンFET構造では、トランジスタサイズの微細化に伴う短チャネル効果を抑制することができる。30

#### 【0187】

領域1909に形成されたトランジスタを用いて、実施の形態および実施例1、2で示した充電用回路116を形成することができる。また、領域1907、1908、1909に形成されたトランジスタを用いて、実施の形態および実施例1、2で示した信号処理回路102を形成することができる。なお、電気二重層コンデンサ104は、実施例1、2と同様に、領域1907、1908、1909に形成されたトランジスタ上に形成することができる。

#### 【0188】

また、半導体基板1900を研磨することで、薄膜化された単結晶基板上のMOSトランジスタを作製することができる。40

#### 【0189】

また、本実施例は本明細書中の実施の形態および他の実施例の記載と適宜組み合わせても良い。

#### 【実施例5】

#### 【0190】

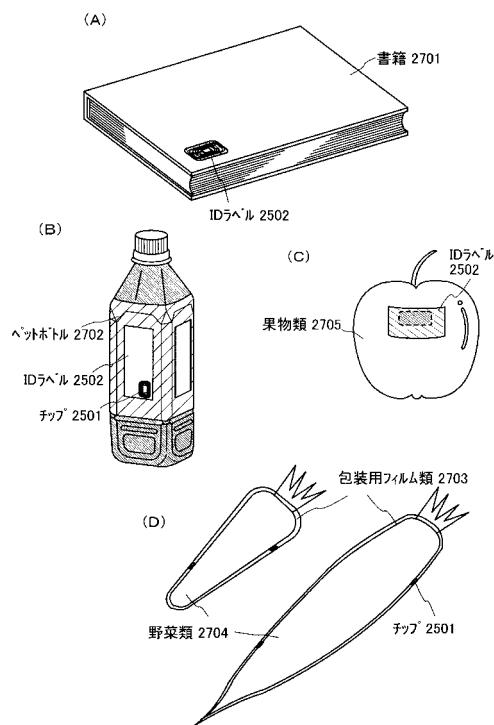

本実施例では、上記実施例1～4で作製された半導体装置の利用形態の一例であるRFIDの用途について説明する。RFIDは、例えば、紙幣、硬貨、有価証券類、無記名債券類、証書類(運転免許証や住民票等)、包装用容器類(包装紙やボトル等)、記録媒体(DVDソフトやビデオテープ等)、乗物類(自転車等)、身の回り品(鞄や眼鏡等)、50

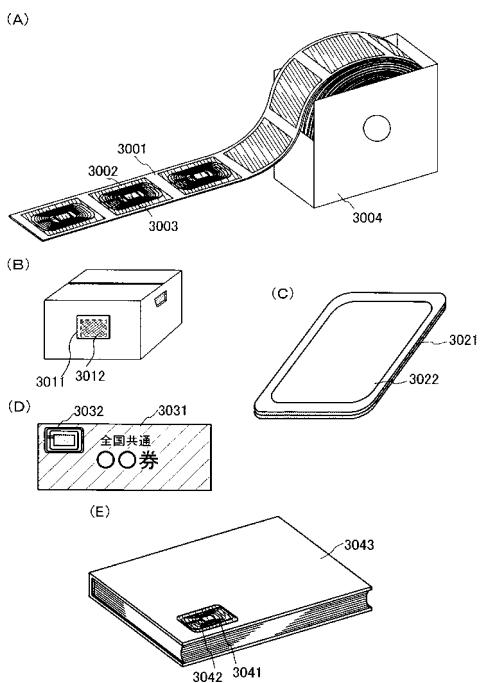

食品類、植物類、動物類、人体、衣類、生活用品類、電子機器等の商品や荷物の荷札等の物品に設けることができ、いわゆるIDラベル、IDタグ、IDカードとして使用することができる。電子機器とは、液晶表示装置、EL表示装置、テレビジョン装置（単にテレビ、テレビ受像機、テレビジョン受像機とも呼ぶ）及び携帯電話等を指す。以下に、図23を参照して、本発明の応用例、及びそれらを付した商品の一例について説明する。

#### 【0191】

図23(A)は、本発明に係るRFIDの完成品の状態の一例である。ラベル台紙3001(セパレート紙)上に、RFID3002を内蔵した複数のIDラベル3003が形成されている。IDラベル3003は、ボックス3004内に収納されている。また、IDラベル3003上には、その商品や役務に関する情報（商品名、ブランド、商標、商標権者、販売者、製造者等）が記されている。一方、内蔵されているRFIDには、その商品（又は商品の種類）固有のIDナンバーが付されており、偽造や、商標権、特許権等の知的財産権侵害、不正競争等の不法行為を容易に把握することができる。また、RFID内には、商品の容器やラベルに明記しきれない多大な情報、例えば、商品の产地、販売地、品質、原材料、効能、用途、数量、形状、価格、生産方法、使用方法、生産時期、使用時期、賞味期限、取扱説明、商品に関する知的財産情報等を入力しておくことができ、取引者や消費者は、簡易なリーダによって、それらの情報にアクセスすることができる。また、生産者側からは容易に書換え、消去等も可能であるが、取引者、消費者側からは書換え、消去等ができない仕組みになっている。なお、RFIDに表示部を設けこれらの情報を表示できる構成としてもよい。

10

20

#### 【0192】

図23(B)は、RFID3012を内蔵したラベル状のRFIDタグ3011を示している。RFIDタグ3011を商品に備え付けることにより、商品管理が容易になる。例えば、商品が盗難された場合に、商品の経路を辿ることによって、その犯人を迅速に把握することができる。このように、RFIDを備えることにより、所謂トレーサビリティに優れた商品を流通させることができる。

#### 【0193】

図23(C)は、RFID3022を内包したIDカード3021の完成品の状態の一例である。上記IDカード3021としては、キャッシュカード、クレジットカード、プリペイドカード、電子乗車券、電子マネー、テレフォンカード、会員カード等のあらゆるカード類が含まれる。また、IDカード3021の表面に表示部を設け様々な情報を表示させる構成としてもよい。

30

#### 【0194】

図23(D)は、無記名債券3031の完成品の状態を示している。無記名債券3031には、RFID3032が埋め込まれており、その周囲は樹脂によって成形され、RFIDを保護している。ここで、該樹脂中にはフィラーが充填された構成となっている。無記名債券3031は、本発明に係るRFIDと同じ要領で作成することができる。なお、上記無記名債券類には、切手、切符、チケット、入場券、商品券、図書券、文具券、ビル券、おこめ券、各種ギフト券、各種サービス券等が含まれるが、勿論これらに限定されるものではない。また、紙幣、硬貨、有価証券類、無記名債券類、証書類等に本発明のRFID3032を設けることにより、認証機能を設けることができ、この認証機能を活用すれば、偽造を防止することができる。

40

#### 【0195】

図23(E)はRFID3042を内包したIDラベル3041を貼付した書籍3043を示している。本発明のRFID3042は、表面に貼ったり、埋め込んだりして、物品に固定される。図23(E)に示すように、本なら紙に埋め込んだり、有機樹脂からなるパッケージなら当該有機樹脂に埋め込んだりして、各物品に固定される。本発明のRFID3042は、小型、薄型、軽量を実現するため、物品に固定した後も、その物品自体のデザイン性を損なうことがない。

#### 【0196】

50

また、ここでは図示しないが、包装用容器類、記録媒体、身の回り品、食品類、衣類、生活用品類、電子機器等に本発明のRFIDを設けることにより、検品システム等のシステムの効率化を図ることができる。また乗物類にRFIDを設けることにより、偽造や盗難を防止することができる。また、動物等の生き物に埋め込むことによって、個々の生き物の識別を容易に行うことができる。例えば、家畜等の生き物にRFIDを埋め込むことによって、生まれた年や性別または種類等を容易に識別することが可能となる。

#### 【0197】

図24(A)、(B)は、本発明に係るRFIDを含んだIDラベル2502を貼付した書籍2701、及びペットボトル2702を示している。本発明に用いられるRFIDは非常に薄いため、上記書籍等の物品にIDラベルを搭載しても、機能、デザイン性を損ねることがない。更に、非接触型薄膜集積回路装置の場合、アンテナとチップを一体形成でき、曲面を有する商品に直接転写することが容易になる。10

#### 【0198】

図24(C)は、果物類2705の生鮮食品に、直接RFIDを含んだIDラベル2502を貼り付けた状態を示している。また、図24(D)は、包装用フィルム類によって、野菜類2704の生鮮食品を包装した一例を示している。このように球面を有する果物類2705や野菜類2704に本発明に係る半導体装置を貼り付けても、また電気二重層コンデンサと信号処理回路を接続するための配線にかかる曲げ応力は小さく、断線を防ぐことができる。また、なお、チップ2501を商品に貼り付けた場合、剥がされる可能性があるが、包装用フィルム類によって商品をくるんだ場合、包装用フィルム2703類を剥がすのは困難であるため、防犯対策上多少のメリットはある。20

#### 【0199】

なお、上述した商品以外にも、あらゆる商品に、本発明に係る半導体装置を利用することができる。

#### 【0200】

なお、本実施例は、本明細書中の実施の形態および他の実施例の記載と適宜組み合わせても良い。

#### 【図面の簡単な説明】

#### 【0201】

【図1】本発明の半導体装置の一構成例を示す図。

30

【図2】本発明の半導体装置の一構成例を説明する図。

【図3】本発明の半導体装置が有するアンテナの構成例を示す図。

【図4】本発明の半導体装置を説明する図。

【図5】本発明の半導体装置を説明する図。

【図6】本発明の半導体装置の充放電を説明する図。

【図7】本発明の半導体装置の作製方法の一例を示す図。

【図8】本発明の半導体装置の作製方法の一例を示す図。

【図9】本発明の半導体装置の作製方法の一例を示す図。

【図10】本発明の半導体装置の作製方法の一例を示す図。

【図11】紫外線照射あるいは加熱するための装置の一例を示す図。

40

【図12】本発明の半導体装置の作製方法の一例を示す図。

【図13】本発明の半導体装置の作製方法の一例を示す図。

【図14】本発明の半導体装置の作製方法の一例を示す図。

【図15】本発明の半導体装置の作製方法の一例を示す図。

【図16】本発明の半導体装置の作製方法の一例を示す図。

【図17】本発明の半導体装置の作製方法の一例を示す図。

【図18】本発明の半導体装置の作製方法の一例を示す図。

【図19】本発明の半導体装置の作製方法の一例を示す図。

【図20】本発明の半導体装置の作製方法の一例を示す図。

【図21】本発明の半導体装置の作製方法の一例を示す図。

50

【図22】本発明の半導体装置の作製方法の一例を示す図。

【図23】本発明の半導体装置の使用形態の一例を示す図。

【図24】本発明の半導体装置の使用形態の一例を示す図。

【図25】アクティブタイプのRFIDの具体的な構成を示す図。

【図26】パッシブタイプのRFIDの具体的な構成を示す図。

【符号の説明】

【0202】

|       |             |    |

|-------|-------------|----|

| 1 0   | 基板          | 10 |

| 1 1   | 電極          |    |

| 1 2   | 電解液層        |    |

| 1 3   | 電極          |    |

| 1 0 0 | RFID        |    |

| 1 0 1 | アンテナ回路      |    |

| 1 0 2 | 信号処理回路      |    |

| 1 0 4 | 電気二重層コンデンサ  |    |

| 1 0 5 | 整流回路        |    |

| 1 0 8 | 復調回路        |    |

| 1 0 9 | アンプ         |    |

| 1 1 0 | 論理回路        |    |

| 1 1 1 | メモリコントロール回路 | 20 |

| 1 1 2 | メモリ回路       |    |

| 1 1 3 | 論理回路        |    |

| 1 1 4 | アンプ         |    |

| 1 1 5 | 変調回路        |    |

| 1 1 6 | 充電用回路       |    |

| 1 1 7 | 放電用回路       |    |

| 1 1 8 | 負荷部         |    |

| 1 2 0 | セパレータ       |    |

| 1 4 1 | アンテナ        |    |

| 1 4 2 | 共振容量        | 30 |

| 1 4 3 | ダイオード       |    |

| 1 4 4 | 平滑容量        |    |

| 1 4 5 | レギュレータ      |    |

| 1 4 6 | ダイオード       |    |

| 1 4 7 | スイッチ        |    |

| 3 0 3 | アンテナ        |    |

| 5 0 1 | スイッチ        |    |

| 5 0 2 | レギュレータ      |    |

| 5 0 3 | シュミットトリガー   |    |

| 7 0 1 | 基板          | 40 |

| 7 0 4 | 絶縁膜         |    |

| 7 0 5 | 半導体膜        |    |

| 7 0 6 | ゲート絶縁膜      |    |

| 7 0 7 | ゲート電極       |    |

| 7 0 8 | 不純物領域       |    |

| 7 0 9 | 不純物領域       |    |

| 7 1 0 | 絶縁膜         |    |

| 7 1 1 | 不純物領域       |    |

| 7 1 2 | 低濃度不純物領域    |    |

| 7 1 3 | 導電膜         | 50 |

|         |         |

|---------|---------|

| 7 1 4   | 絶縁膜     |

| 7 1 6   | 導電膜     |

| 7 1 8   | 素子形成層   |

| 7 1 8   | 素子形成層   |

| 7 2 0   | 基板      |

| 7 2 1   | シール材    |

| 7 2 2   | 電極      |

| 7 2 3   | スペーサ    |

| 9 1 1   | レジストマスク |

| 1 0 2 1 | I D カード |

| 1 1 0 1 | 基板支持台   |

| 1 1 0 4 | 窓       |

| 1 1 0 8 | 下側定盤    |

| 1 1 0 9 | 光源      |

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図19】

【図18】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

【図26】

---

フロントページの続き

(51)Int.Cl. F I

H 01 G 9/28 (2006.01) G 06 K 19/00 J

H 01 G 9/00 531

(56)参考文献 特開2006-127363(JP,A)

特開2001-195307(JP,A)

特開2006-121060(JP,A)

特開2002-075801(JP,A)

特開2004-221531(JP,A)

特開平02-125797(JP,A)

(58)調査した分野(Int.Cl., DB名)

G 06 K 19 / 077

G 06 K 19 / 07

H 01 G 9 / 28

H 01 G 11 / 00

H 01 G 11 / 22

H 01 G 11 / 54