(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4538209号

(P4538209)

(45) 発行日 平成22年9月8日(2010.9.8)

(24) 登録日 平成22年6月25日(2010.6.25)

(51) Int.Cl.

F 1

|                     |                  |             |      |

|---------------------|------------------|-------------|------|

| <b>H01L 21/3065</b> | <b>(2006.01)</b> | H01L 21/302 | 105A |

| <b>G03F 7/11</b>    | <b>(2006.01)</b> | H01L 21/302 | 104H |

| <b>G03F 7/40</b>    | <b>(2006.01)</b> | GO3F 7/11   | 503  |

| <b>H01L 21/027</b>  | <b>(2006.01)</b> | GO3F 7/40   | 521  |

|                     |                  | H01L 21/30  | 574  |

請求項の数 4 (全 15 頁) 最終頁に続く

(21) 出願番号

特願2003-303961 (P2003-303961)

(22) 出願日

平成15年8月28日 (2003.8.28)

(65) 公開番号

特開2005-72518 (P2005-72518A)

(43) 公開日

平成17年3月17日 (2005.3.17)

審査請求日

平成18年8月18日 (2006.8.18)

(73) 特許権者 501387839

株式会社日立ハイテクノロジーズ

東京都港区西新橋一丁目24番14号

(74) 代理人 100100310

弁理士 井上 学

(72) 発明者 根岸 伸幸

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 伊澤 勝

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 横川 賢悦

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】半導体装置の製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

半導体基板上に、単層または複数層の薄膜を介して被加工層を形成する工程と、

前記薄膜上に有機系反射防止層を形成する工程と、

該有機系反射防止層上にベンゼン環の重量比率が20%以下でC=O結合を有するレジストパターンを形成する工程と、

前記レジストパターンをマスクとして前記有機系反射防止膜をエッティングする工程と、

前記レジストパターンの残膜をマスクとして前記被加工層をエッティングする工程とを含み、

前記有機系反射防止膜のエッティングにおけるプラズマガスとして、Arガスと、フロロカーボンガスであるC<sub>x</sub>H<sub>y</sub>F<sub>z</sub>(x, z = 1~10, y = 0~10)との混合ガスを用い、

前記被加工層エッティングのプラズマガスとして、フロロカーボンガスであるC<sub>x</sub>H<sub>y</sub>F<sub>z</sub>(x, z = 1~10, y = 0~10)との混合ガスを用い、希釈ガスとしてXe、Krの内少なくとも1種類か、Xe、Krの内少なくとも1種類とArの混合ガスか、XeとKrの混合ガスを用いることを特徴とする半導体装置の製造方法。

## 【請求項 2】

請求項1に記載の半導体装置の製造方法において、

前記有機系反射防止膜のエッティングにおけるプラズマガスに、更にN<sub>2</sub>、O<sub>2</sub>、SF<sub>6</sub>、NF<sub>3</sub>、H<sub>2</sub>、CH<sub>4</sub>の少なくとも1つを混合して用いることを特徴とする半導体装置

の製造方法。

**【請求項 3】**

請求項 1 に記載の半導体装置の製造方法において、

前記被加工層エッティングの後に、エッティング装置内の残留ガスを回収することを特徴とする半導体装置の製造方法。

**【請求項 4】**

請求項 3 に記載の半導体装置の製造方法において、

前記回収した残留ガスから Xe と Kr を抽出することを特徴とする半導体装置の製造方法。

**【発明の詳細な説明】**

10

**【技術分野】**

**【0001】**

本発明は半導体製造装置、特にエッティング工程の中でも層間絶縁膜のエッティングに用いられる半導体装置の製造装置およびエッティング方法に関し、ArF リソグラフィー以降のレジストパターンを用いた、ビア形成、高アスペクト比コンタクト形成、自己整合コンタクト形成、トレンチ形成、ダマシン形成、ゲートマスク形成等においてレジストダメージを低減できる方法に関するものである。

**【背景技術】**

**【0002】**

半導体装置において、ウエハ上に形成されたトランジスタと金属配線間および金属配線間を電気的に接続するために、トランジスタ構造の上部および配線間に形成された層間絶縁膜に、プラズマを利用したドライエッティング方法でコンタクトホールを形成し、コンタクトホール内に、半導体もしくは金属を充填する。特に、90 nm ノード以降の高集積・高速 Logic デバイス製造では、誘電率が低い Low-k 材料である層間絶縁膜にドライエッティング方法にて溝やビアを形成し Cu を配線材料として埋め込むダマシン工程と、より微細なパターン形成を行うために 193 nm の光源を用いた ArF リソグラフィーが用いられている。ドライエッティング方法は、真空容器内に導入されたエッティングガスを外部から印加された高周波電力によりプラズマ化し、プラズマ中で生成された反応性ラジカルやイオンをウエハ上で高精度に反応させることで、レジストに代表されるマスク材料や、ビア、コンタクトホールの下にある配線層や下地基板に対し選択的に被加工膜をエッティングする技術である。

20

**【0003】**

通常、半導体回路の配線パターン形成の際には、被加工膜上に有機膜系反射防止膜 ( BARC ) が形成され、更にその上にレジスト膜が形成される。BARC は、リソグラフィの光源であるレーザ光の干渉による異常パターン形成を防止するために用いられる。レジストパターン形成後、BARC エッティングを行ない、その後、被加工膜のエッティング ( メインエッティング ) が行なわれる。BARC エッティングでは、BARC の材質がレジストと同様に C リッチであるために、CF<sub>4</sub>、CHF<sub>3</sub> 等の F リッチなフロロカーボンガス及び Ar に代表される希ガス及び酸素ガスの混合ガスを導入し、0.5 Pa から 10 Pa の圧力領域でプラズマを形成し、ウエハに入射するイオンエネルギーを 0.1 kV から 1.0 kV の範囲で制御してエッティングを行う。

30

**【0004】**

また、ビアやコンタクトホール形成では、プラズマガスとして、CF<sub>4</sub>、CHF<sub>3</sub>、C<sub>2</sub>F<sub>6</sub>、C<sub>3</sub>F<sub>6</sub>O、C<sub>4</sub>F<sub>8</sub>、C<sub>5</sub>F<sub>8</sub>、C<sub>4</sub>F<sub>6</sub> 等のフロロカーボンガス及び Ar に代表される希ガス及び酸素ガス及び CO ガス等の混合ガスを導入し、0.5 Pa から 10 Pa の圧力領域でプラズマを形成し、ウエハに入射するイオンエネルギーを 0.5 kV から 2.5 kV まで加速する。

40

**【発明の開示】**

**【発明が解決しようとする課題】**

**【0005】**

50

このような、エッティング工程において、ArFリソグラフィー以降のレジスト材料は、従来のKrFレジストやi線レジストに比べエッティングによるレジストレートが大きいこと、レジストダメージに起因する表面荒れが大きいことが問題となる。

KrFレジストではそのエッティング耐性がArFに比べ十分に大きく、また、デバイスの集積度もそれほど大きくなかったため、ストライエーションやラインエッジラフネスは大きな問題とはならなかった。しかしながら、特にゲート電極形成のためのSiO<sub>2</sub>に代表されるハードマスクエッティングや素子分離形成用マスクとして用いるSiNマスクエッティング等仕上り寸法精度が要求されるエッティングでは、エッティング後のレジスト粗さに起因するラインエッジラフネスの悪化はデバイス特性に大きな影響を与える。また、現在高集積Logicデバイス製造で導入が進められている層間絶縁膜であるLow-k材料(SiOC膜)のエッティングでは、比較的高いバイアスによる高エネルギーのイオン照射や、O<sub>2</sub>リッチなガス雰囲気でエッティング処理を行うため、パターン側壁のストライエーション発生に加え、パターンの無いところに局所的な穴があいてしまうレジスト突き抜け現象が発生する。10

そこで、本発明は、ArFリソグラフィー世代以降のレジストをマスクとして用いるエッティングプロセスにおいて、レジストのエッティング耐性を確保するエッティング方法ならびに本方法を実現するエッティング装置を提供することを目的とする。

#### 【課題を解決するための手段】

##### 【0006】

本明細書には少なくとも3つの発明が開示される。

20

第1の発明においては、ArFレジスト等、従来のレジスト材料に比べてエッティング耐性が低いレジスト材料を用いたエッティングプロセスにおいて、有機系反射防止膜のエッティングまたは被加工層の一部のエッティングにおけるプラズマガスとして、全プラズマガス流量に対するArの流量比率が10%以下(好ましく0)であるプラズマガスを用いることにより、前記の課題を解決する。

##### 【0007】

第2の発明においては、同一エッティング装置内でレジスト改質とエッティングを行ない、レジストを改質しながらエッティングを行なうことにより、前記の課題を解決する。

##### 【0008】

第3の発明においては、被加工層のエッティングにおいて、従来希釈ガスとして用いられているArに比べイオン化エネルギーの低いXeやKrといったガスを希釈ガスとして用いるか、またはArに添加することにより、前記の課題を解決する。30

#### 【発明の効果】

##### 【0009】

本発明により、エッティング耐性が弱いArFリソグラフィー以降のレジストを用いたパターン形成において問題となるレジストダメージを効率的に抑制でき、レジストダメージに起因するレジスト突き抜けやストライエーションを改善できる。また、レジスト改質とエッティングを交互に行なう方法および装置を適用することで、通常スタンドアローンでレジスト改質を行う場合に比べ、装置コスト及びスループットを改善でき、生産性の向上にも貢献できる。40

#### 【発明を実施するための最良の形態】

##### 【0010】

ArFリソグラフィー世代以降のレジストをマスクとして用いるエッティングプロセスにおいて、レジストのエッティング耐性を確保する手段として2種類の手段が考えられる。

##### 【0011】

1つは、エッティングガスに含まれるイオンスペック成分をレジストにストライエーションや大きなラインエッジラフネスが発生しない程度に低減することである。

ArFレジスト用材料が従来のレジスト(例えば、KrFレジストなど)に比べてエッティング耐性が異なる要因は以下の理由による。すなわち、ArFレジスト中には、従来のレジストとは異なり、ベンゼン環がなくカルボニル基(C=O結合)が多数存在する。力50

ルボニル基には、更にアダマンチル基等の分子数の大きいエッティング阻害基が結合している。O C - O 結合は結合エネルギーが小さく結合が不安定である。従って、エッティング中にレジスト表面に飛来するイオン、電子などのアタックに対し簡単に脱離する。その結果、局所的に C - C 結合を主体とするレジストの主鎖が選択的に残り、マイクロマスクとなって表面粗さが劣化すると考えられる。従って、エッティングガス中に含まれるイオンスパッタ成分を十分低減すれば、C - H 結合やO C - O 結合を切れにくくすることができ、結果的に、実用上問題無い程度にストライエーションや大きなラインエッジラフネスの発生を低減することができる。

「エッティングガスに含まれるイオンスパッタ成分」とは、従来使用されているエッティングガス（例えば、フロロカーボンガス、Ar、酸素ガス及びCOガスの混合ガス）でいえば

10、例えはArガスである。

なお、エッティングと同時ないしエッティングを行った後にレジスト表面をFやHを含むガスで処理することにより、レジスト表面の平坦性を更に向上去ることができる。これは、切れたカルボニル基に含まれるCの未結合手がFやHにより終端されるためC = C結合の発生が押さえられるためである。更に、B A R C エッティング後に、表面層に残留したC = C結合主体のCリッチなマイクロマスクを除去することによりレジスト表面ラフネスが抑制される。更にまた、B A R C エッティング後のメインエッティング工程で、プラズマ中のCラジカル、Oラジカルを抑制することにより、エッティング中に増幅されるレジスト変質に起因したストライエーション、レジスト突き抜けを低減することができる。

#### 【0012】

20

2つめは、レジストの改質である。しかしながら、従来のレジストの改質は、E B キュア装置でレジストの改質を行なった後、エッティング装置にウェハを搬送してエッティング処理を行なっており、製造コストやスループット向上の点で不利であった。また、レジスト全体をフルキュアするために。高エネルギー（4 keV程度）の電子線をレジスト全体に照射しており、ウェハにダメージを与える懸念があった。そこで、2つめの解決手段では、同一エッティング装置内でレジスト改質とエッティングを交互に行ない、レジストを改質しながらエッティングを行なうことを特徴とする。

#### 【0013】

30

本方法によれば、1サイクルでキュアすべきレジスト膜厚が薄いために、改質のために照射する電子線の加速エネルギーを押さえることが可能であり、ウェハへのダメージを低減することが可能である。併せて、レジスト表面改質をスタンドアローンの装置にて行う場合に比べ、スループットを高め生産性を向上させることが可能となる。

#### 【実施例1】

#### 【0014】

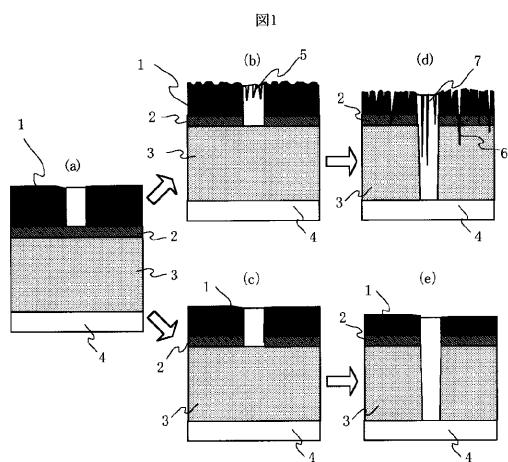

図1には、エキシマレーザを光源としたリソグラフィーにて形成したレジストパターンをマスクとしてコンタクトホールを形成する工程を示した断面図を示す。図1(a)は、本実施例のエッティング方法が適用される試料断面図の一例である。膜構造は、Ar F リソグラフィー対応レジスト1、レーザの反射干渉による異常パターン形成を抑制するための有機系反射防止膜(B A R C)2、被加工膜であるシリコン酸化膜3、下地シリコン基板4からなっている。ここでは、Ar F リソグラフィー対応レジストの膜厚を350 nm、B A R C 膜厚を60 nmとした。なお、図1(a)～(e)の各図において、レジスト1の中央部の白抜き部は、コンタクトホールの内壁を示している。

40

図1(b)、(d)には、図1(a)に示した試料に対して、従来技術によるエッティングプロセスを適用した際の試料断面、図1(c)、(e)には、本実施例で説明するエッティングプロセスを適用した際の試料断面それぞれ示した。

#### 【0015】

まず、B A R C 加工をプラズマエッティングにて行う。Ar F リソグラフィー世代以前のKr F リソグラフィー世代で用いていたB A R C 加工では、Ar / CF<sub>4</sub> 混合ガスを用いていた。エッティング条件は、例えは、ガス流量はAr = 500 ml / min、CF<sub>4</sub> = 125 ml / minで圧力は2 Paである。Arを添加することで、CF<sub>4</sub> の分圧を制御し

50

、B A R C 加工時の垂直形状を実現していた。その条件をA r F リソグラフィー世代に適用した場合を図1( b )に示す。K r F レジストでは問題にならなかったが、A r F レジストではレジスト表面に数10nmのラフネスが発生し、また特に密パターン部のレジストホール側壁には縦スジであるストライエーション5が発生した。一方、図1( c )に本発明のプロセス条件であるA r レス条件を適用した例を示す。この場合、C F<sub>4</sub>を100ml/minないし500ml/minで供給し、圧力を2Paないし10Paとした。さらに、半導体基板に印加する高周波バイアス電力を0.32W/cm<sup>2</sup>とした。本条件を用いると、スパッタ効率の高いA r イオンの入射を無くし、レジスト中のC - H結合及びO C - O結合の切断を抑制することで、図1( b )とは異なりレジスト表面のラフネス及びレジストパターン側壁のストライエーション5を改善できる。ここで、プラズマガスにA r を用いないことと、半導体基板に印加する高周波バイアスを抑制することがA r F レジストダメージを抑制する上で重要であることを示す。

## 【0016】

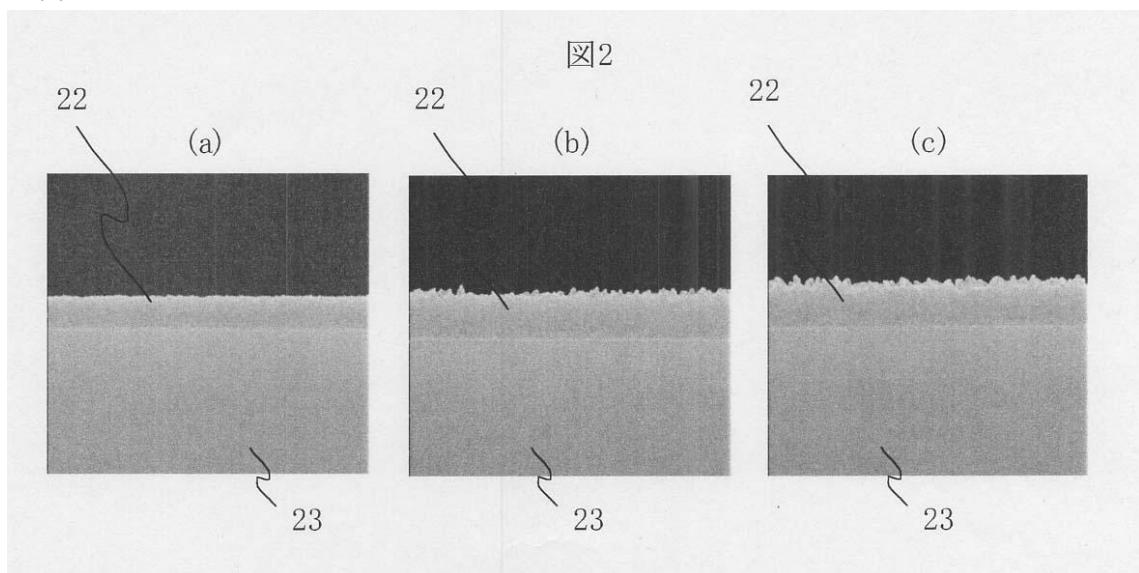

図2( a )はC F<sub>4</sub>単独ガスのプラズマで高周波バイアス電力を0.32W/cm<sup>2</sup>とした場合のA r F レジスト状態、図2( b )はA r とC F<sub>4</sub>混合ガス条件で高周波バイアス電力を0.32W/cm<sup>2</sup>とした場合のA r F レジスト状態、図2( c )は図2( b )と同一ガス条件で高周波バイアス電力を0.64W/cm<sup>2</sup>とした場合のA r F レジスト状態をそれぞれ示す断面SEM写真である。これらの観察結果から、A r ガスを用いずに且つ高周波バイアスを抑制した図2( a )が一番A r F レジスト表面が滑らかであることがわかる。また、図示していないが、本B A R C 加工ではA r ガスを用いない条件でも高周波バイアス電力を0.5W/cm<sup>2</sup>以上とすることで、レジスト表面荒れの発生が確認された。

次に図1( b )、図1( c )のB A R C 加工後のA r F レジストをマスクとして、被加工膜であるシリコン酸化膜のエッチングを行う。エッチング条件には、A r / C<sub>4</sub>F<sub>6</sub>/O<sub>2</sub>/COの混合ガス系を用いる。具体的には、例えばA r を300ml/minないし2000ml/min、C<sub>4</sub>F<sub>6</sub>を20ml/minないし70ml/min、O<sub>2</sub>を25ml/minないし100ml/min、COを0ml/mnないし300ml/minで供給する。そのときの圧力は1Paないし10Paに設定する。

## 【0017】

図1( d )は、図1( b )のB A R C 加工後に上記シリコン酸化膜加工を行った場合の断面図である。B A R C 加工後は数10nmであったレジスト表面ラフネスはシリコン酸化膜加工を行うことにより増幅されて、パターンのない部分でもレジストに微細孔が形成され、B A R C を突き抜けて被加工膜であるシリコン酸化膜まで達している。これを以下レジスト突き抜け6と呼ぶ。また、パターン側壁にはレジスト部の縦スジを反映してストライエーション7が発生している。本シリコン酸化膜加工条件は、対レジスト選択比を向上させるために、C<sub>4</sub>F<sub>6</sub>のようなC/F比の高いフロロカーボンガスやCOガスを用いている。したがって、シリコン酸化膜加工前のレジスト表面ラフネスが少しでもあると、エッチング中のC F ポリマー膜質が比較的Cリッチであるために、レジスト表面をポリマーが完全に覆えず、微細な窪み部はポリマーが少ないためにエッチングが進行しやすく、レジスト突き抜けが発生する。また、特にパターン側壁部では、入射イオンによるスパッタの影響で実効的なポリマー量自体が少なく、場所によるポリマーの有無は顕著となり、ストライエーションが発生し易い。

一方、図1( c )をマスクとしたシリコン酸化膜加工後の断面形状を図1( e )に示す。本条件では、シリコン酸化膜加工前のレジスト表面ラフネスが非常に小さいため、エッチング中のC F ポリマー量が多い本シリコン酸化膜加工条件においても、場所によるポリマー有無の差が小さく、レジスト変質は少ない。従って、図1( d )に示すようなレジスト突き抜け、ストライエーションの発生を抑制できる。

ここでは、B A R C 加工ガス条件としてC F<sub>4</sub>単体を用いた例を示したが、C F<sub>4</sub>単体に限らず、C F<sub>4</sub>などのC<sub>x</sub>H<sub>y</sub>F<sub>z</sub>(x, z = 1 ~ 10, y = 0 ~ 10)ガスにO<sub>2</sub>やS F<sub>6</sub>、N F<sub>3</sub>のようなOラジカルやFラジカルを供給できるガスを添加しても良い。この場

10

20

30

40

50

合は、レジストのC - H結合、O C - O結合の切断により発生するCリッチなダメージ層を上記OラジカルやFラジカルによって除去し、B A R C加工後のレジストダメージを抑制できる。

#### 【0018】

プロセスガスに含まれるフロロカーボン系のガスとしては、 $C_xH_yF_z$ (に含まれるCの数がなるべく少ない方がよい( $x = 1$ 、 $y = 0 \sim 10$ 、 $z = 1 \sim 10$ ))。被加工層の材質が無機低誘電率絶縁材(例えばSiOC)の場合、CH<sub>3</sub>などC成分を含有していることが多く、フロロカーボンガス中のC含有比率が小さいと、エッティング停止抑制とレジストダメージ改善の両立を図ることが可能であるためである。プロセスガスとしては、フロロカーボン系ガスに、N<sub>2</sub>、O<sub>2</sub>、SF<sub>6</sub>、NF<sub>3</sub>、H<sub>2</sub>、CH<sub>4</sub>の内少なくとも1種類のガスを混合して用いる。10

#### 【0019】

また本発明に係わる半導体装置の製造方法および半導体装置の製造装置は、前記被加工層エッティングにヨウ素を含むガスを添加することを特徴としている。これにより、質量の重いヨウ素イオンをエッティング中にレジスト表面に入射させることで、レジスト極表面層の改質効果を得ることが可能となる。

また、図1(b)のようにB A R C加工後にレジストダメージが発生しても、その後にO<sub>2</sub>、SF<sub>6</sub>、NF<sub>3</sub>等のプラズマによりOラジカルやFラジカル、Nラジカルを供給して、B A R C加工後に形成されたレジストダメージを取り除き、次にシリコン酸化膜加工を行っても同様の効果が得られる。さらに、B A R C加工時のレジスト表面温度を-40ないし0の低温に制御することで、レジストの反応自体を抑制し、レジストダメージを改善できることも言うまでもない。この場合、温度制御手段としては、ウエハとウエハを保持するステージ間に溜め込むガス圧力を制御することが考えられる。20

#### 【0020】

次に、シリコン酸化膜加工時のエッティング条件に絞って説明する。なお、以下に説明する実施例のB A R Cエッティングにおいても、上記で説明したB A R Cエッティング条件を適用したほうが望ましいことは言うまでもない。

#### 【0021】

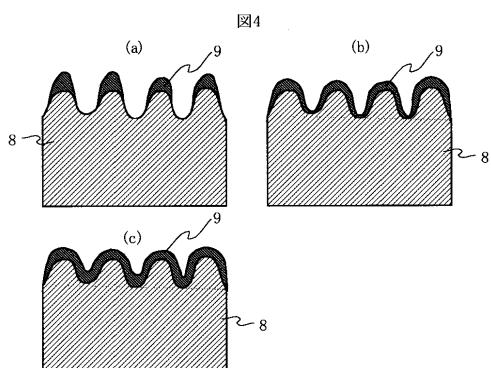

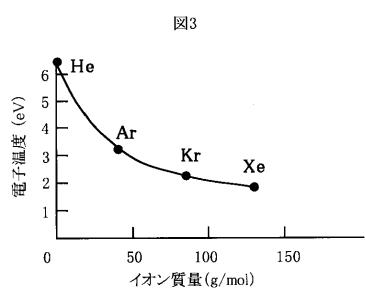

図3はシリコン酸化膜エッティング時に用いるプラズマガスにおける希釈ガスである希ガス種と電子温度の関係を示したものである。ガス条件として、希ガスを500ml/min、C<sub>4</sub>F<sub>6</sub>を30ml/min、O<sub>2</sub>を36ml/min、COを200ml/minとして、そのときのガス圧力を2Paに設定した。プラズマ発生用高周波電力は各条件とも一定の電力を用い、本条件では400Wである。この場合、希ガスとして通常用いるArよりもイオン化エネルギーが高いHeを用いると電子温度が高くなり、逆にイオン化エネルギーが低いXeを用いると電子温度が低くなる。電子温度はプラズマ中の解離度と密接に関係しており、Xeを用いた低電子温度条件にて解離が抑制されることとなる。30

#### 【0022】

図4に希ガス種によるレジスト表面8に堆積するCFポリマー9の様子を示す。図4(a)はHeの場合、図4(b)はArの場合、図4(c)はXeの場合を示す。HeやArを用いると、解離が進行するために堆積するCFポリマーのC/F比はCリッチとなり、実効的な付着係数は高くなる。従って、レジスト表面凹凸の凸部に選択的に堆積し、凹部にはあまり堆積しない。一方、Xeを用いた場合は、解離が抑制され、CF<sub>2</sub>に代表されるラジカルが多く入射しCFポリマーのC/F比をFリッチに制御でき、実効的な付着係数を低く抑えることが可能となる。この場合は、図4(c)に示すようにレジスト表面を万遍なく覆えるポリマー状態となり、シリコン酸化膜エッティング時のレジストダメージを抑制できる。一方、イオン種による散乱を考えると、質量の軽いHeでは入射角に対し散乱角は比較的ブロードに広がるが、Xeでは鏡面反射となり易い。つまり、レジストダメージとは逆に、HeやArに比べXeやKrのほうがイオン集中し易く、レジストダメージを被加工膜に転写し易いこととなる。従って、シリコン酸化膜加工時の希ガスとしてはXeとArの混合ガスとすることで、レジストダメージ抑制及びイオン集中抑制を両立4050

でき、シリコン酸化膜加工後のレジスト突き抜け及びストライエーションを改善できる。B A R C 加工または被加工層のエッティング工程でのウエハ温度は、-40から0に制御すると良い。B A R C 加工時のウエハ温度の高温度化を避けることで、気相中からのイオン及びラジカルとレジスト自体の物理及び化学反応の反応性が抑制され、レジストダメージが抑制される。

#### 【0023】

ウエハ温度を制御する方法としては、ウエハとウエハを支持するステージの間に導入するガスの圧力を制御する方法がある。ウエハを支持するステージを冷却する冷媒温度を例えば-20と設定した場合、B A R C のエッティング時には、ウエハに印加する高周波電力が低くプラズマからの入熱が小さいため、ウエハとウエハを支持するステージの間に導入するガスの圧力を低く設定し(例えば1kPa)、次の被加工層エッティング時は入熱が大きいため高く設定する(例えば1.5kPa)などすることにより、ウエハ表面の温度を所望の温度に簡便且つ瞬時に変更可能である。10

#### 【0024】

また、本実施例に係わる半導体装置の製造方法および半導体装置の製造装置では、前記被加工層エッティングの希釈ガスとして、Xe、Krの内少なくとも1種類か、Xe、Krの内少なくとも1種類とArの混合ガスか、XeとKrの混合ガスを用いる。XeやKrはArに比べ第一イオン化エネルギーが低いため、プラズマを維持するための電子温度を低くすることが可能であり、結果として、プラズマ中の解離を抑制し原料ガスであるフローポンガスからのC、O各ラジカルの発生を低減できる。それにより、エッティング中のレジストダメージ増幅を抑制することが可能となる。20

#### 【実施例2】

#### 【0025】

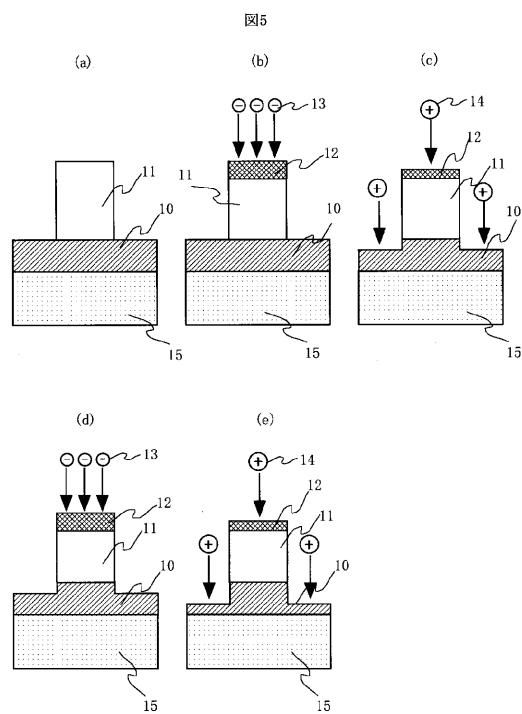

本実施例では、レジストダメージを抑制するために、レジスト改質とエッティングを同一装置内で行う実施例を説明する。通常、レジスト改質は改質専用装置にて行い、その後エッティング装置にてエッティングを行う。しかしながら、本発明の実施例では図5のゲートマスク加工工程の断面図に示すように、レジスト改質とエッティングを交互に行う。図5(a)は処理前の断面図であり、ArFレジスト11、反射防止膜10、シリコン酸化膜15の積層構造からなる。図5(b)、図5(d)はレジスト改質サイクルを示すが、一度のレジスト改質サイクルにて改質されるレジスト厚さ12を、次のエッティングサイクル(図5(c)、図5(e))にてレジストが削れる厚さよりも厚く設定することで、エッティング時には常にレジスト表面は改質されており、レジストダメージを抑制できる。30

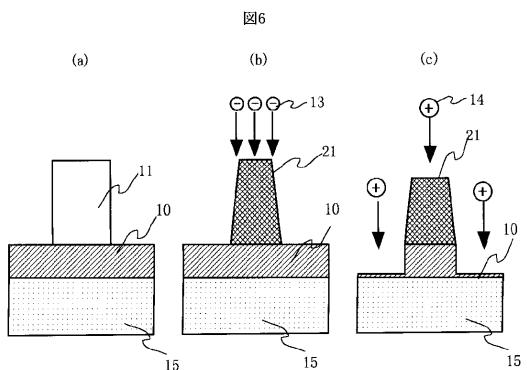

#### 【0026】

一方、スタンドアローン装置にてレジスト改質を行う場合は、図6(a)に示す初期形状を、レジスト改質装置を用いて図6(b)に示すようにレジスト全体を改質する。従って、レジストが横方向に縮み、これをマスクとしてエッティング装置にてエッティング処理を行うと、図6(c)に示すように寸法シフトが発生し、デバイスの電気的特性に対し大きな問題となる。従って、本発明の実施例では、常に次のエッティングサイクルにて削れるレジスト厚さよりも若干厚いレジストを改質することで、レジストの寸法シフト量を最小限に留めることができとなり、高精度な加工を実現できる。また本実施例ではレジスト改質とエッティングを同一装置内で行うために、装置コストの抑制及び高スループット化に貢献できる。40

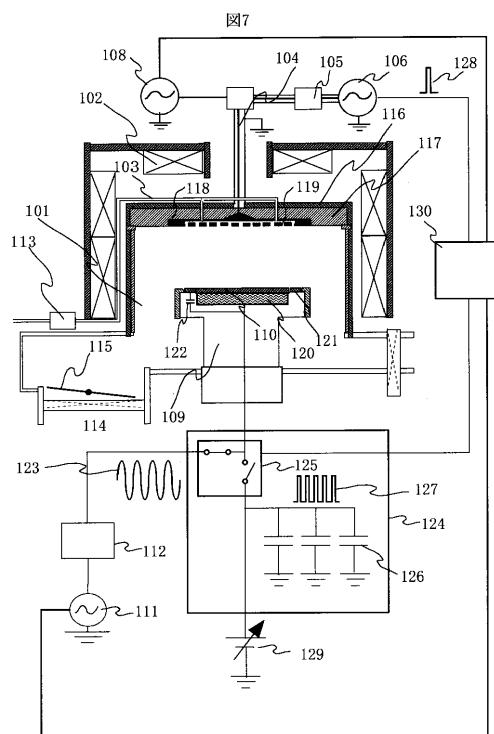

次に、本実施例のレジスト改質手段として電子ビームキュアを用いる場合を説明する。本実施例を実現するための装置概略図を図7に示す。本実施例ではプラズマ発生方式は問わないが、本実施例ではUHF-ECRプラズマ方式を用いた場合について説明する。

真空容器101の周囲に空心コイル102が設置されている。真空容器にはガス導入管103により原料ガスを導入し、同軸線路104、整合器105を介して電磁波放射アンテナに450MHz電源106にて発生した電磁波を供給して、前記空心コイルにより発生した磁場との相互作用によりプラズマを発生させる。また、同時に前記電磁波放射アンテナには13.56MHz電源108が設置されており、プロセスにより印加バイアスが50

変更可能である。真空容器には下部電極 109 があり、この上に被加工試料 110 を設置する。この下部電極には、レジスト改質、エッティングを交互に行えるミキシングバイアス部 124 が接続されている。ミキシングバイアス部 124 には、R F バイアスとパルスバイアスを切り替える高速スイッチ部 125 が組み込まれている。ミキシングバイアス部 124 と高速スイッチ部 125 とは、一つの筐体内に配置されており、図示されてはいないが、筐体は更にアースされている。通常のエッティングを行う場合には、800 KHz の高周波バイアス電力 123 を電源 111、整合器 112 を介して供給する。その場合、もう一方のコンデンサ側のスイッチは OFF として、R F バイアス供給側を ON にしておく。

レジスト改質を行う場合は、コンデンサ 126 に蓄えられた電荷をコンデンサに接続されたスイッチを ON することで瞬時に供給し、正のパルスバイアス 127 を発生させる。この場合は、R F 供給側のスイッチを OFF としておく。

10

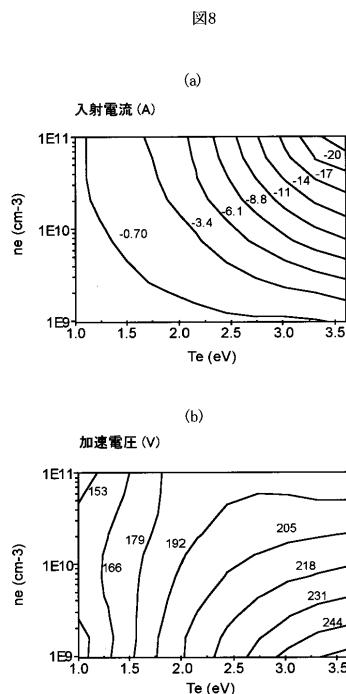

図 8 のシミュレーション結果に示すように、効率的に正のパルスバイアスをウエハに印加するにはプラズマ密度、電子温度の制御が必要となる。電子の加速エネルギーを得るためにのプラズマ状態は高電子温度、低密度状態が良く、一方、電子電流を確保するためにには高電子温度、高密度状態が良い。本実施例では正のパルスバイアスを印加する際のプラズマ密度を制御する手段として、パルスプラズマを用いた。プラズマ発生用の 450 MHz 電源 106 をパルス動作させ、レジスト改質サイクルでは 450 MHz 電源出力を OFF とする。450 MHz 電源 106 の ON、OFF をトリガ信号 128 として高速スイッチ 125 へ入力し、OFF してから正のパルスバイアスを印加するまでのディレイ時間を制御することで、所望のプラズマ密度を得ることが可能となる。これにより、プラズマ中で生成された電子を効率良くウエハ表面に入射させ、レジスト表面を改質することができる。

20

また、電子ビームキュアでは電子のドーズ量を確保することが極めて重要である。本実施例では、レジスト改質サイクル中にウエハに印加する正のパルスバイアスのパルス数を制御することで対応することが可能である。この場合、試料ステージ 120 と、アースされた筐体とを接続する伝送線上に抵抗を設けておく。抵抗を介してウェハにチャージされた電荷がリークするため、1つのパルスバイアスが印加後、次のパルスバイアスを印加できるまでの時間を短くすることができる。このため、レジスト改質サイクルにおける最大パルスバイアス数を増大できる。一方、電子の加速エネルギーを制御するためには正のパルスバイアスの波高を制御することが必要である。これは、コンデンサに電荷を供給する直流電源 129 の出力端電圧を制御することで可能となる。以上記載した制御動作は、全て制御用のコンピュータ 130 により実行される。

30

#### 【0027】

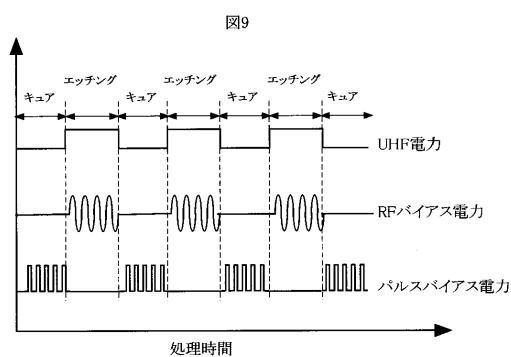

実際のプロセスでは、レジスト改質サイクルでは、プラズマ条件は次にくるエッティングサイクルと同条件を用いる。例えば、B A R C 加工とレジスト改質を繰り返す場合には C F<sub>4</sub> を 125 m l / min 導入しプラズマを発生させる。プラズマ密度を制御して電子を効率的にレジスト表面に入射させレジスト改質を行うために、プラズマを OFF してから 50 msec 後にパルスバイアスを印加し始める。次に B A R C エッティングサイクルでは、プラズマガスをそのまま維持してプラズマを発生させパルスバイアスの代わりに今度は R F バイアスを印加し、イオンを入射させる。これらを図 9 に示すように交互に繰り返し、B A R C 加工が終了した後は、エッティング条件を被加工層のエッティングに適した条件に変更し、同様にレジスト改質サイクルとエッティングサイクルを交互に行う。これにより、本発明に係わる A r F レジストをマスクとした被加工層のエッティングをレジスト突き抜け及びストライエーション無く行うことが可能となる。

40

#### 【0028】

レジスト表面改質を行う際の電子の入射エネルギーを 10 V から 1 kV の間とする。一度のレジスト表面改質工程で改質するレジスト膜厚は、電子の入射エネルギーにより制御する。これは、電子の入射エネルギーに応じて電子の非弾性衝突平均自由行程が変わるものである。一度の表面改質工程により改質する膜厚は、およそ数 nm から 50 nm 程度であるが、入射エネルギーが 10 V から 1 kV の範囲であれば、改質膜厚は上記の範囲に

50

収まる。

**【0029】**

レジスト表面改質を行う際のプラズマガスとしては、Ar、He、Xe、N<sub>2</sub>、Neの少なくとも1種類か、もしくはAr、He、Xe、N<sub>2</sub>、Neの少なくとも1種類とO<sub>2</sub>、SF<sub>6</sub>、NF<sub>3</sub>の少なくとも1種類の混合ガスを用いるとよい。レジスト表面改質を行う際のプラズマガスに堆積性ガスを用いないことで、効率的にレジストに電子を作用させ、改質効果を得ることができるためである。

**【0030】**

また、本実施例に係わる半導体装置の製造方法および半導体装置の製造装置においては、レジスト表面改質を行う際にプラズマ密度を制御して正のパルスバイアスを印加する。

10

上記手段によれば、プラズマ密度を制御することで、プラズマインピーダンスを制御でき効率的に電子を引き込むことが可能となる。例えば、電子の入射エネルギーを得るためにのプラズマ状態としては、高電子温度、低プラズマ密度が、電子電流を得るためにには、高電子温度、高プラズマ密度が良い。従って、電子の入射エネルギーを10Vから1kVの間で効率的に電子電流をウエハに入射させるためには、プラズマ密度の制御が必要となる。

**【0031】**

また、本実施例に係わる半導体装置の製造方法および半導体装置の製造装置においては、レジスト表面改質を行う際にプラズマ発生用高周波電力をOFFしてから正のパルスバイアス電圧を印加するまでのディレイ時間にてプラズマ密度を制御することを特徴としている。上記手段によれば、プラズマ発生用高周波電力をパルス変調し、OFFしてから任意のディレイ時間後にウエハに正のパルスバイアスを印加することで簡便にプラズマ密度を制御可能である。この場合、レジスト表面改質の後に行うエッチング工程は、プラズマ発生用高周波電力をONしてプラズマを発生させ、高周波バイアスを半導体基板に印加することで行う。

20

**【0032】**

レジスト表面改質を行う際に印加する正のパルスバイアス電圧の印加数は、1サイクル当たり10パルス以上の多パルスとすると良い。プラズマ状態にも依るが、通常1パルスで必要な電子の数（ドーズ量）を確保することは困難である。従って、レジスト改質工程においてプラズマ発生用高周波電力をOFFしてから半導体基板に印加する正のパルスバイアスの印加数を制御することで、レジスト改質に必要なドーズ量を確保することが可能となる。

30

また、本実施例に係わる半導体装置の製造方法および半導体装置の製造装置においては、半導体基板に高周波バイアスおよび正のパルスバイアスを印加する伝送線路の内導体とアース間を抵抗で接続することを特徴としている。上記手段によれば、レジスト改質工程において正のパルスバイアスを多パルス印加する際に、適当な抵抗で内導体とアース間を接続することで、1パルスで半導体基板および伝送線路内が蓄積する電荷をある時定数で放出し、次のパルス印加に備えることが可能となる。本手段により、1サイクルで印加できる最大パルス数を大きくすることができる。

**【実施例3】**

40

**【0033】**

本実施例では、先に説明した実施例2と実施例1を組み合わせた場合のプロセスについて説明する。まず、レジスト表面層のレジスト改質を、実施例2で説明した電子ビームキュア方式を用いて行う。その際、電子を発生させるプラズマガスとしては、堆積性ラジカルや反応性ラジカルを形成しない、希ガスを用いる。それにより、純粋に電子をレジスト表面に引き込み、レジスト改質効果を高めることが可能となる。本実施例では、Arを500mL/min供給し、圧力を2Paに設定した。レジスト改質サイクルでは、プラズマをOFFしてから50ms後から正のパルスバイアスを15000パルス印加した。電子加速電圧はおよそ100Vであり、ドーズ量はおよそ2000μC/cm<sup>2</sup>である。その際のレジスト改質厚さは10~20nm程度である。その後、実施例1で示した、

50

A r ガスを導入しない C F<sub>4</sub> 単独のプラズマを発生させて B A R C 加工を行い、レジストダメージを抑制した。また、被加工層であるシリコン酸化膜を X e、A r、C<sub>4</sub>F<sub>6</sub>、O<sub>2</sub>、C O 混合ガス系にてエッチングすることで、レジストダメージに起因したレジスト突き抜け、ストライエーションをより低減することが可能となる。

#### 【実施例 4】

##### 【0034】

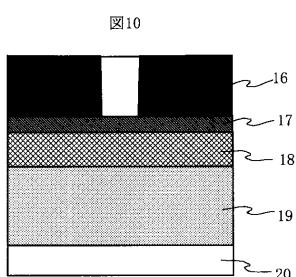

実施例 4 は、A r F レジストの負荷を低減する方法のひとつである多層レジスト加工の実施例である。図 10 は本実施例で用いられる試料の断面図であり、A r F エキシマレーザを光源としたリソグラフィーにて形成した A r F レジストパターンをマスクとしてノボラック樹脂をパターニングする多層レジスト構造を示している。膜構造は A r F レジスト 10

16、B A R C 17、SOG (Spin on glass) 18、ノボラック樹脂 19、被加工層 20 から成っている。本構造では、最終的に被加工層をエッチングするマスクとしてエッチング耐性に優れたノボラック樹脂を用いる。従って、パターン側壁のストライエーションが無く高精度にノボラック樹脂にパターン転写することが極めて重要である。

まず、実施例 1 で説明した C F<sub>4</sub> 単独のエッチング条件にて B A R C 加工を行う。これにより、B A R C 加工後の A r F レジストダメージを抑制できる。次に、SOG 加工を行う。SOG はシリコン酸化膜の一種であるため、フロロカーボンガスを含むガス系にてエッチングを行う。例えば、ガス系として X e、A r、C<sub>5</sub>F<sub>8</sub>、O<sub>2</sub> の混合ガス系を用いる。他にも希ガスとして X e や K r の単体や、K r と X e の混合ガス、若しくは K r と A r の混合ガスを用いることも効果的である。その後、SOG 加工後に残存した A r F レジスト、B A R C、SOG をマスクとしてノボラック樹脂を加工する。この場合は、N H<sub>4</sub> 20

単独か N<sub>2</sub> と H<sub>2</sub> の混合ガス系を用いる。

##### 【0035】

以上により、A r F レジストダメージを低減してノボラック樹脂の加工が完了するが、実施例 2 で説明したレジスト改質とエッチングの繰り返しプロセスを用いても A r F レジストダメージを抑制できることは言うまでもない。この場合は、B A R C 及び SOG 加工時に希ガスとして A r 単体を用いても良い。また、本発明は、本実施例で示した多層レジスト形成にとどまらず、ダマシン形成、セルフアラインコントラクト形成にも適用できることは言うまでもない。

#### 【実施例 5】

##### 【0036】

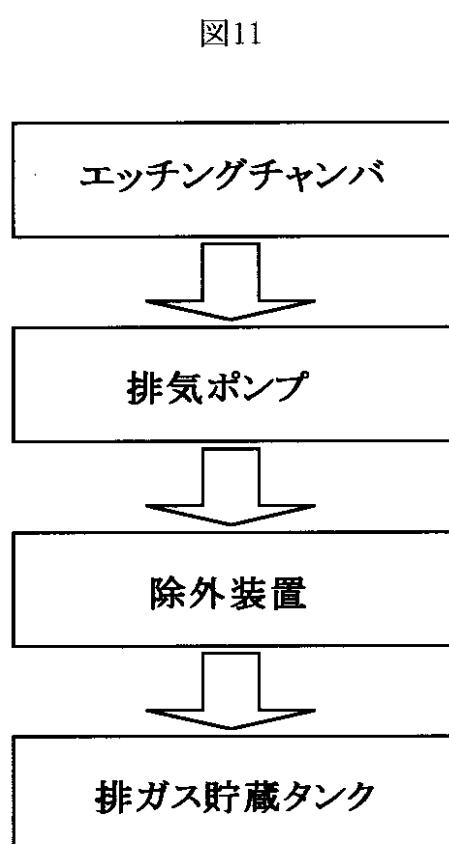

本実施例では、実施例 1 から 4 に係わるエッチング装置において、排気ガスを再生処理するための再生処理システムを組込んだ場合を詳しく説明する。実施例 1 で説明したように、コンタクトホールや V i a 加工におけるシリコン酸化膜のエッチングでは、A r F レジストのダメージを抑制するためには、希釈ガスとして電子温度を低減できる X e や K r などの希ガスを用いることが望ましい。しかしながら、X e や K r は大気中に存在する割合が非常に小さく大変高価である。従って、図 11 に示すようにシステムの最終段に再生用貯蔵タンクを設置した。再生用貯蔵タンクに蓄えられる排ガスは排気ポンプ及び除外装置を経ており、ハロゲンガス、一酸化炭素ガス、フロロカーボンガスなど人体及び環境に悪影響を及ぼす成分を取り除いたものである。回収された排ガスを再生処理業者に委託することで、再度 X e や K r を精製できる。このシステムを導入することで、X e や K r のコストを低減でき、同時に自然環境に配慮したエッチングプロセスが構築できる。また、例えばエッチングチャンバの定期メンテナンス時に本再生用貯蔵タンクを交換することで、生産性に及ぼす影響も最小限に留めることができる。

##### 【図面の簡単な説明】

##### 【0037】

【図 1】A r F エキシマレーザを光源としたリソグラフィーにて形成したレジストパターンをマスクとしてコンタクトホールを形成する工程を示した断面図。

【図 2】A r F レジストを各種条件にてエッチングした場合の断面 S E M 写真。

10

20

30

40

50

【図3】本発明で用いるコンタクトホールエッチング時の希ガス種と電子温度の関係を示す概念図。

【図4】希ガス種によるレジスト上に堆積するC Fポリマーの概念図。

【図5】本発明のレジスト改質とエッチングを交互に行う工程を示した断面図。

【図6】従来のレジスト改質工程による寸法シフトを示す断面図。

【図7】本発明のレジスト改質とエッチングを交互に行う工程を実現するためのエッチング装置概略図。

【図8】本発明のレジスト改質サイクルにて入射する電子の諸量とプラズマ密度、電子温度依存性を示す概念図((a) 加速エネルギー、(b) 電子電流)。

【図9】本発明のレジスト改質、エッチングシーケンスの概念図。 10

【図10】本発明の実施例の一つである多層レジスト加工の断面図。

【図11】本発明の実施例の一つである、システムに排ガス処理装置を組込んだ場合のシーケンス図。

【符号の説明】

【0038】

101. 真空容器、102. 空心コイル、103. ガス導入管、104. 同軸線路、105. 整合器、106. 450MHz電源、108. 13.56MHz電源、109. 下部電極、110. 被加工試料、111. 高周波バイアス電源、112. ブロッキングコンデンサ、113. ガス流量計、114. 真空排気系、115. コンダクタンスバルブ、116. アース電位導体板、117. 誘電体、118. 円板状導体板、119. シリコン円板、120. チャック部、121. フォーカスリング、122. コンデンサ、123. RFバイアス電力、124. ミキシングバイアス部、125. 高速スイッチ、126. コンデンサ、127. パルスバイアス、128. トリガ信号、129. 直流電源、130. 制御用コンピュータ、1. ArFレジスト、2. 有機系反射防止膜、3. シリコン酸化膜、4. シリコン基板、5. ストライエーション、6. レジスト突き抜け、7. ストライエーション、8. ArFレジスト、9. C Fポリマー、10. 反射防止膜、11. ArFレジスト、12. レジスト改質工程にて改質されたArFレジスト、13. 電子、14. イオン、15. シリコン酸化膜、16. ArFレジスト、17. 有機系反射防止膜、18. SOG、19. ノボラック樹脂、20. 被加工層、21. スタンドアローンのレジスト改質装置にて実施した場合の改質されたArFレジスト、22. ArFレジスト、23. シリコン基板。 20

10

20

30

【図1】

【図4】

【図3】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

---

フロントページの続き

(51)Int.Cl.

F I

H 01L 21/30 570

審査官 関根 崇

(56)参考文献 国際公開第03/007357(WO, A1)

特開2002-334879(JP, A)

特開平11-219942(JP, A)

特開平11-016885(JP, A)

特開2003-096136(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01L 21/3065

G 03F 7/11

G 03F 7/40

H 01L 21/027