**(19) 대한민국특허청(KR)**

**(12) 등록특허공보(B1)**

(51) . Int. Cl.<sup>8</sup>

G06F 13/28 (2006.01)

(45) 공고일자 2006년01월26일

(11) 등록번호 10-0546085

(24) 등록일자 2006년01월18일

|             |                   |             |                 |

|-------------|-------------------|-------------|-----------------|

| (21) 출원번호   | 10-2000-7013621   | (65) 공개번호   | 10-2001-0052493 |

| (22) 출원일자   | 2000년12월01일       | (43) 공개일자   | 2001년06월25일     |

| 번역문 제출일자    | 2000년12월01일       |             |                 |

| (86) 국제출원번호 | PCT/US1999/004610 | (87) 국제공개번호 | WO 1999/63447   |

| 국제출원일자      | 1999년03월01일       | 국제공개일자      | 1999년12월09일     |

(81) 지정국

국내특허 : 일본, 대한민국,

EP 유럽특허 : 오스트리아, 벨기에, 스위스, 독일, 덴마크, 스페인, 프랑스, 영국, 그리스, 아일랜드, 이탈리아, 룩셈부르크, 모나코, 네덜란드, 포르투칼, 스웨덴, 핀란드, 사이프러스,

(30) 우선권주장 09/088,133 1998년06월01일 미국(US)

(73) 특허권자 어드밴스드 마이크로 디바이시즈, 인코포레이티드

미국 캘리포니아 94088-3453 서니베일 원 에이 엠디 플레이스 메일 스톱68(72) 발명자 스피로데이빗에이.

미국텍사스78759오스틴발콘스우즈드라이브4200티팔도스멜라니디.

미국텍사스78610부다제리스레인700

(74) 대리인 박장원

**심사관 : 이상현****(54) 직접 메모리 액세스를 이용한 직렬 포트 데이터 및 상태의 압축 및 복원****요약**

マイクロ제어기(M)는 데이터를 압축 및 복원한 다음 한 메모리 블록으로부터 다른 메모리 블록으로 전송하는 직접 메모리 액세스 유닛을 포함한다. 구체적으로, 워드 사이즈 데이터가 판독되어, 한 바이트는 버려지고, 연속적으로 저장되어 바이트 사이즈 데이터가 된다. 이는 데이터와 함께 상태 정보를 저장하는 확장된 판독 및 확장된 기록 비동기 직렬 포트와 관련하여 이용된다. 일단 상태 정보가 처리되면, 이 상태는 "압축" DMA를 수행함으로써 스트리밍된다.

**내용**

도 4

**명세서**

## 기술분야

### 관련 출원

본 발명은, 1997년 8월 7일 Melanie D. Typaldos 및 Patrick E. Maupin에 의해 출원된 미국 특허 출원 제08/920,930호, 현재는 미국 특허 제5,958,024호인 "A METHOD AND APPARATUS FOR SUPPORTING HIGH DATA RATES OVER ON ASYNCHRONOUS SERIAL LINE USING DMA", 및 Melanie D. Typaldos에 의해 동시에 출원되어 현재 계류중인 미국 특허 출원 제09/888,610호인 "UART CHARACTER MATCHING USED FOR ADDRESS MATCHING ON A REGISTER-BY-REGISTER BASIS"와 관련되며, 이들은 본원의 참조로서 인용된다.

본 발명은 마이크로제어기들에 관한 것으로, 특히 직렬 인터페이스와 관련하여 이용되는 개량된 직접 메모리 액세스 제어 기기를 제공하는 마이크로제어기에 관한 것이다.

## 배경기술

통합된 통신 특징을 갖는 특화된 마이크로제어기들은 통신 응용들에 특히 매력적이다. 마이크로제어기 또는 내장 제어기 (embedded controller)는 모듈리식 반도체 기판(즉, 칩)에 기능성(functionality)을 결합하는 데에 독자적으로 적합하다. 단일 칩 내에 다양한 통신 특징들을 내장함으로써, 통신 마이크로제어기는 광범위한 통신 응용들을 지원할 수 있다.

마이크로제어기들은 수년간 많은 응용들에 이용되어 왔다. 다수의 이러한 응용들은 디지털 및 아날로그 포맷으로, 전화선들, 컴퓨터 네트워크들, 근거리 네트워크(LAN) 및 광역 네트워크(WAN)와 같은 전자 네트워크들을 통한 통신을 포함한다. 통신 응용들에서, 마이크로제어기는 일반적으로 실행 유닛 외에 다수의 통합된 통신 주변장치들을 갖는다. 이들은 저속 직렬 포트 및 고속 직렬 포트 뿐 아니라, 범용 직렬 버스(USB) 인터페이스 및 하이 레벨 데이터 링크 제어(HDLC) 채널들과 같은 보다 복잡한 통신 주변장치가 될 수 있다.

비동기 직렬 통신 포트는 마이크로제어기에 있어서 하나의 공통적인 부가 특징이다. 비동기 직렬 연결에 의해, 상기 마이크로제어기는 데이터 비트들을 순차적으로 송수신함으로써 데이터 라인들을 통해 다른 장치들과 통신할 수 있다. "비동기" 특성은 이러한 포트들이 데이터를 클럭하기 위해 개별적인 클럭 신호를 제공하지 않음을 나타낸다. 대신에, 데이터가 송수신되는 속도는 사전에 결정 또는 협정되어야 하며, 송신측과 수신측 모두에서 독립적으로 제어되어야 한다. 이러한 데이터 속도는 보드 속도(baud rate)로서 알려져있는바, 이는 1비트 주기의 역수이다. 이 보드 속도는 일반적으로 산업 표준인 다수의 미리 설정된 속도들중 하나이다. 이러한 속도들은 1200, 2400, 4800, 9600, 19.2K, 28.8K, 33.3K 및 54K의 보드 및 고속 데이터 전송 속도를 포함한다.

직렬 데이터 통신의 보급으로 인해, 많은 마이크로제어기들은 한번에 1비트를 전송 및 수신할 수 있는 1개 이상의 비동기 직렬 포트들(ASPS)을 포함한다. 이러한 마이크로제어기들은 전형적으로 인터럽트 신호들을 이용하여 마이크로프로세서 코어에 ASP가 서비스들을 요구한다는 것을 통지한다. ASP는 전형적으로, 데이터 유닛(data unit)이 ASP로 수신되고 이 데이터 유닛이 ASP로부터 외부 메모리 유닛으로 전송될 필요가 있을 때, ASP가 데이터 유닛의 전송을 완료하고 다음 데이터 유닛이 외부 메모리 유닛으로부터 ASP로 전송되어야 할 때, 또는 에러가 발생할 때에 인터럽트 요구 신호를 발행한다.

비록 역사적으로는 7 또는 8 데이터 비트들이 전형적인 값들이지만, ASP는 다양한 데이터 포맷들에 대해 구성될 수 있다. 그러나, 직접 메모리 액세스와 관련된 9비트 비동기 직렬 프로토콜을 포함하는 다수의 9 비트 직렬 프로토콜이 마이크로제어기들을 이용하여 개발되었다. 이러한 프로토콜들은 1997년 2월 4일 John P. Hansen 및 Melanie D. Typaldos에 의해 출원된 미국 특허 출원 제08/807,103호, 현재에는 미국 특허 제5,896,549호인 "A MICROCONTROLLER WHICH IS CONFIGURABLE TO TRANSFER DATA TO AND FROM ONE OR MORE ASYNCHRONOUS SERIAL PORTS USING DIRECT MEMORY ACCESS" 및 1997년 2월 4일 John P. Hansen, Ronald W. Stents 및 Melanie D. Typaldos에 의해 출원된 미국 특허 출원 제08/775,262호, 현재에는 미국 특허 제5,978,865호인 "A MICROCONTROLLER HAVING HARDWARE FEATURES SUPPORTING 9-BIT SERIAL PROTOCOLS DURING DMA DATA TRANSFERS TO AND FROM ONE OR MORE ASYNCHRONOUS SERIAL PORTS"에 개시되어 있는바, 이들은 공동으로 양도되었으며 본원의 참조로서 인용된다. 이러한 프로토콜들은 또한 캘리포니아 서니베일에 소재하는 어드밴스드 마이크로 디바이시즈 인코포레이티드의 Am186ES 사용자 매뉴얼 및 Am186ED 사용자 매뉴얼에 개시되어 있다. 상기 출원들에서 설명되는 바와 같이, 그리고 하기 설명되는 바와 같이, 데이터를 전송 및 수신하는 동안 개별적인 제어 비트가 세팅 또는 리셋되어 9번째 데이터 비트의 역할을 한다. 이러한 9-비트 프로토콜을 이용하여 DMA를 지원하기 위해, 그 특정 비트가 특정 값으로서 수신되면, 인터럽트가 발생하여 9번째 데이터 비트가 실제로 세팅되었음을 나타낸다.

US-A-5,737,638호는 데이터 처리 시스템을 개시하는바, 여기서 온보드 DMA 제어기는 호스트 메모리와 어댑터 메모리 간의 DMA 전송을 관리하고, 데이터 전송 동안 데이터는 압축(compression)되거나 복원(decompression)될 수 있다.

### 발명의 상세한 설명

본 발명에 따르면, 마이크로제어기는 데이터의 압축 및 복원을 제공하는 직접 메모리 액세스(DMA) 제어기를 포함한다. 구체적으로, 이 DMA 제어기는 소스 및 목적지 충분 값들을 갖는바, 이들은 조정될 수 있으며 전송 항목(transfer item)의 사이즈에 독립적이다. 소스 포인터 및 목적지 포인터가 메모리 내에 블록들로서 세팅될 수 있는바, 소스 블록은 그 선두 바이트(top byte)가 버려지는 워드 사이즈(word size)의 데이터를 포함한다. 소스는 각 전송 후에 2만큼 충분하도록 세팅되고, 목적지는 1만큼 충분하도록 세팅될 수 있다. 이후, DMA가 수행되어, 소스의 각 워드로부터 데이터 바이트를 전송하고, 다음 워드로 충분하고, 목적지에 대해 다음 바이트로 충분한다. 이러한 방식으로, 1바이트의 데이터가 프로세서의 개입이 거의 없이 DMA를 이용하여 각 워드로부터 스트리핑(striping)된다.

이는 DMA와 관련하여 확장된 판독을 지원하는 비동기 직렬 포트를 이용할 때에 특히 유용하다. 데이터 시퀀스들이 직렬 포트로부터 판독될 수 있는바, 각각의 7 또는 8 비트 값은 DMA 제어기에 의해 저장된 대응하는 상태 바이트를 갖는다. 일단 이러한 상태 바이트들이 어드레스 비트들 또는 에러 비트들에 대해 검사되면, DMA는 불필요한 데이터 바이트를 "스트리핑"하도록 프로그램될 수 있다.

유사하게, DMA 전송을 수행하기 전에, 바이트 레벨 데이터는 워드들로 확장될 수 있는바, 확장된 기록 바이트들은 이 확장된 기록들을 지원하는 비동기 직렬 포트들로의 DMA 제어기에 의한 전송을 위해 데이터의 앞에 부가된다.

### 도면의 간단한 설명

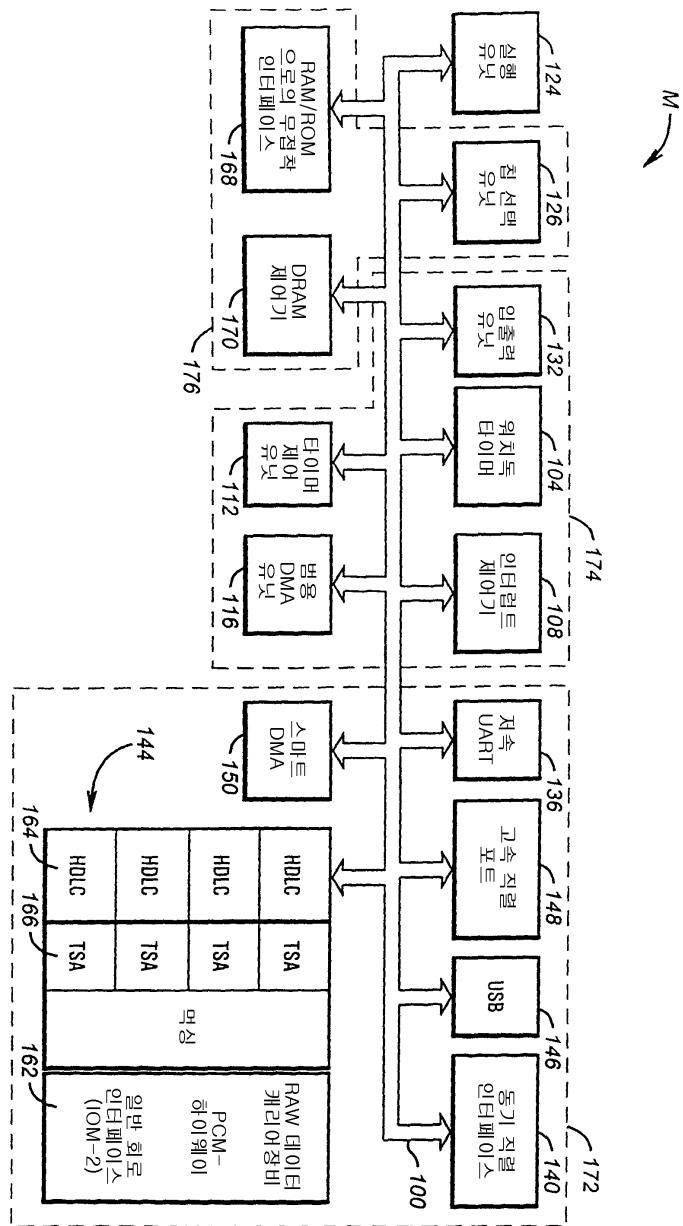

도 1A는 본 발명에 따라 구현되는 전형적인 마이크로제어기의 블록선도이다.

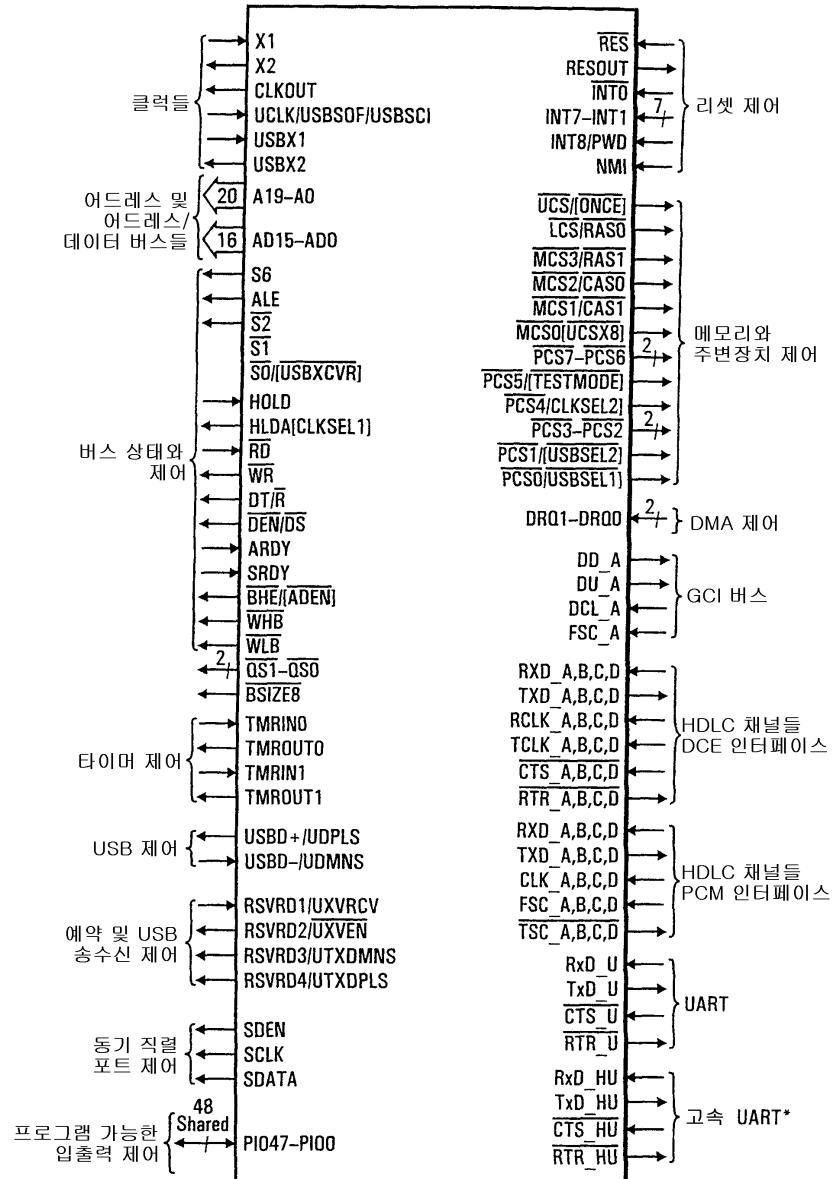

도 1B는 도 1A의 마이크로제어기에 대한 핀아웃들에 대한 개략적인 핀아웃 선도이다.

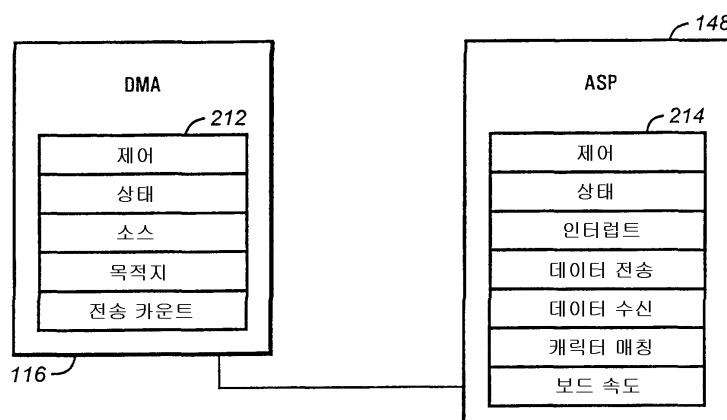

도 2는 비동기 직렬 포트, DMA 제어기, 및 도 1A, 도 1B의 마이크로제어기에 대한 그들의 레지스터들 간의 관계를 나타낸 블록선도이다.

도 3은 본 발명에 따른 비동기 직렬 프레임 내의 어드레스 비트들의 이용을 나타낸 타이밍도이다.

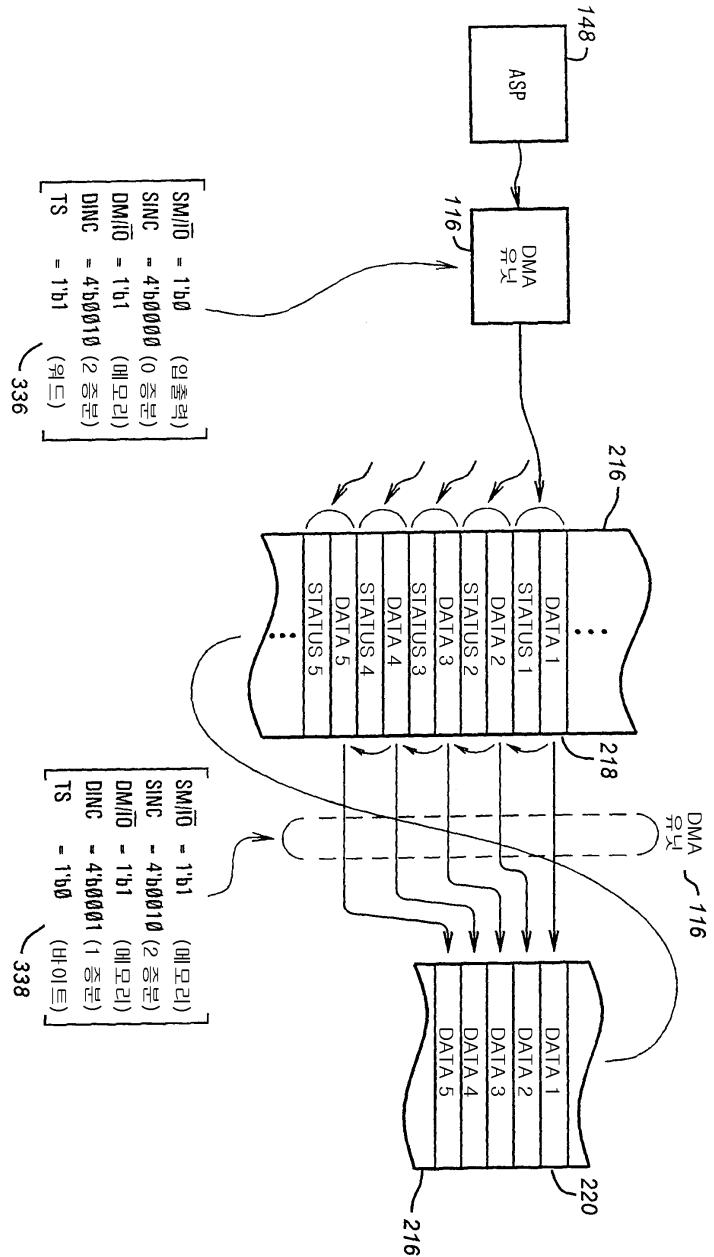

도 4는 본 발명에 따른 DMA 유닛 데이터 압축을 나타낸 선도이다.

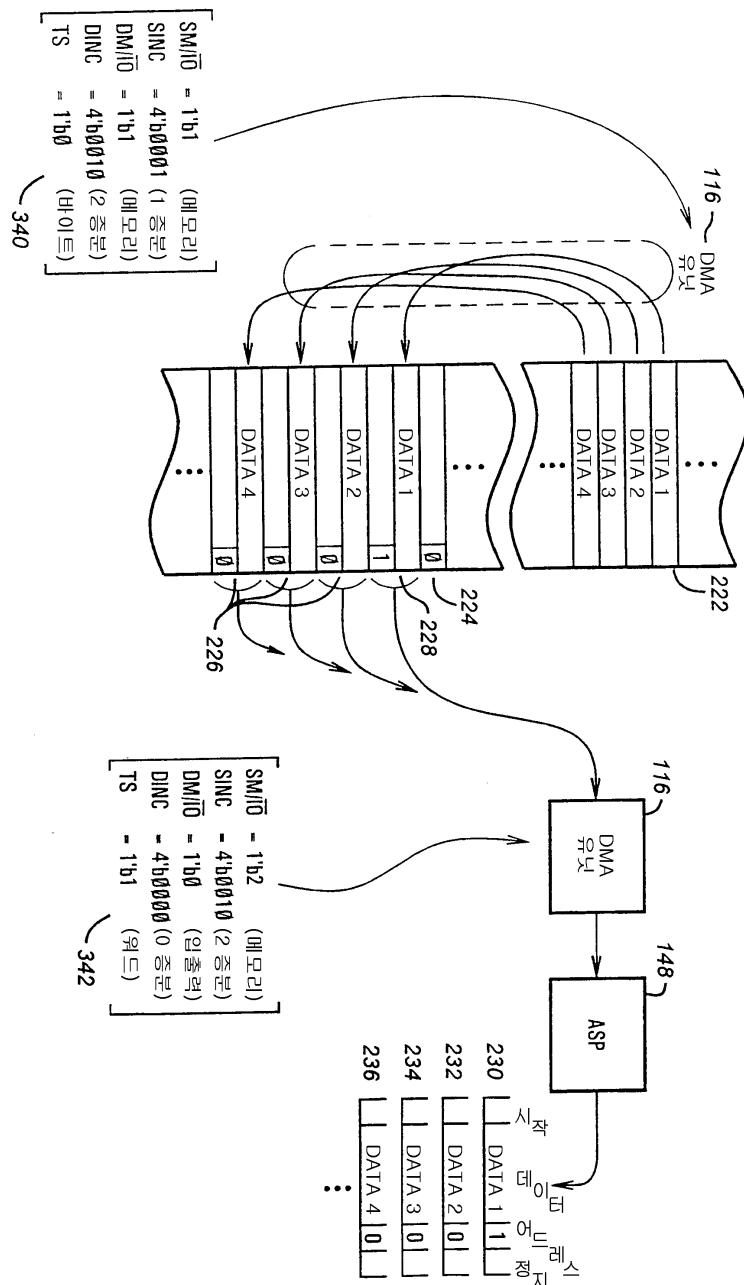

도 5는 본 발명에 따른 DMA 유닛 데이터 확장을 나타낸 선도이다.

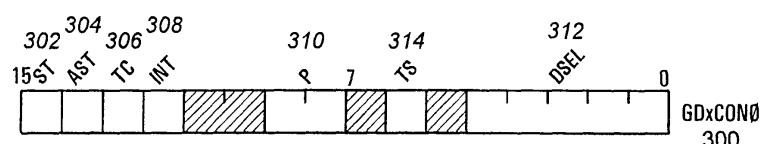

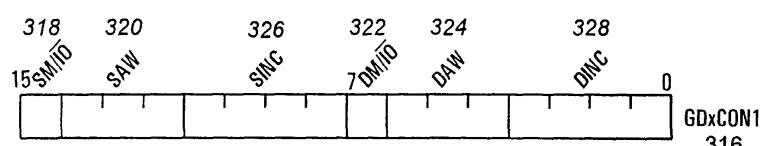

도 6A-6E는 본 발명에 따른 DMA 유닛의 레지스터 내용을 나타낸 블록선도이다.

도 7A-7G는 본 발명에 따른 비동기 직렬 포트의 레지스터 내용을 나타낸 블록선도이다.

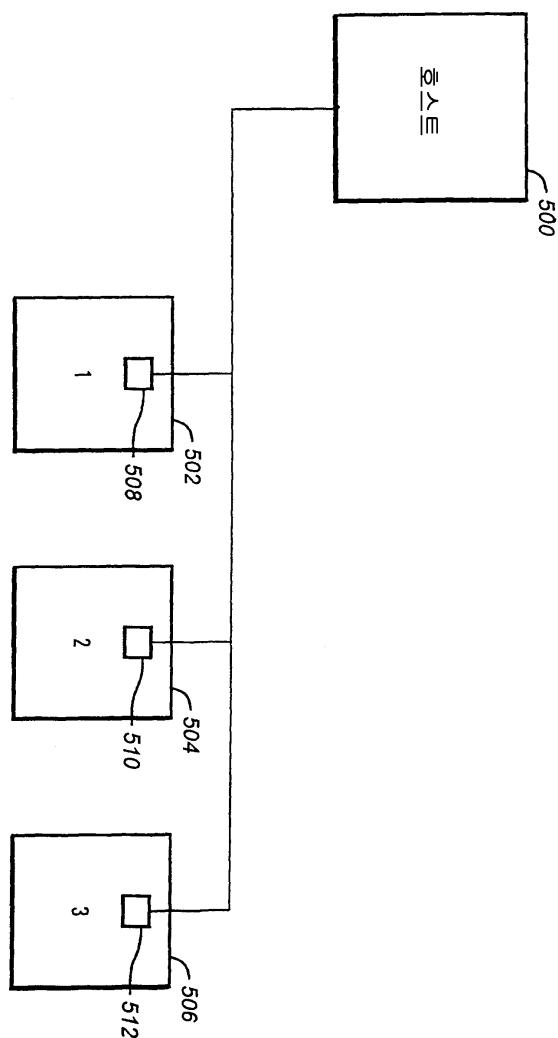

도 8은 멀티드롭 비동기 프로토콜의 구현을 나타낸 블록선도이다.

### 실시예

삭제

삭제

삭제

도 1A는 본 발명에 따라 구현된 전형적인 마이크로제어기(M)의 블록선도이다. 이러한 마이크로제어기는 바람직하게는 단일의 모놀리식 집적 회로 위에서 구현된다.

마이크로제어기(M)는 바람직하게는 실행 유닛(124), 시스템 주변장치들(174), 메모리 주변장치들(176) 및 직렬 통신 주변장치들(172)을 결합하는 내부 버스(100)를 포함한다. 개시된 실시예에서, 실행 유닛(124)은 캘리포니아주 서니베일에 소재하는 어드밴스드 마이크로 디바이시즈 인코포레이티드의 다양한 마이크로제어기들에서 구현되는 AM186 명령어 세트와 호환가능하다. 실행 유닛(124) 대신 다양한 다른 실행 유닛들이 이용될 수 있다. 상기 시스템 주변장치들(174)은 마스크불가능한 인터럽트(NMI)들, 마이크로제어기 리셋들 및 시스템 리셋들을 발생시키는 위치독 타이머(watch dog timer: WDT)(104)를 포함한다. 15 채널들을 이용하여 36개의 마스크가능한 인터럽트 소스들을 지원하는 인터럽트 제어기(108)가 또한 시스템 주변장치로서 제공된다. 하나의 개시된 시스템 주변장치는 3 채널 타이머 제어 유닛(112)이다. 이 타이머 제어 유닛(112)은 3개의 16 비트 프로그램가능한 타이머들을 포함한다. 다른 시스템 주변장치로는 4개의 채널들(0-3)을 갖는 범용 직접 메모리 액세스(DMA) 유닛(116)이 있다. 마이크로제어기(M)의 프로그램가능한 I/O 유닛(132)은 사용자 프로그램가능한 입/출력 신호(PIO)들을 지원한다. 개시된 실시예에서는, 48개의 PIO들이 제공된다.

개시된 마이크로프로세서의 메모리 주변장치들(176)은 DRAM 제어기(170), RAM 또는 ROM으로의 무접착 인터페이스 (glueless interface)(168) 및 칩 선택 유닛(126)을 포함한다. 개시된 실시예에서, DRAM 제어기(170)는 마이크로제어기 (M)에 완전히 통합된다. 또한, 개시된 실시예에서, 칩 선택 유닛(126)은 메모리 디바이스들과 이용하기 위한 6개의 칩 선택 출력들 및 주변장치들과 이용하기 위한 8개의 칩 선택 출력들을 제공한다.

범용 비동기 송/수신기(UART)(136)로서 구현된 저속 직렬 포트가 직렬 통신 주변장치로서 제공된다. 이 저속 UART(136)는 전형적으로 당업계에 알려져 있는 16550 UART 표준과 호환가능하다. 개시된 실시예에서, 다른 직렬 통신 주변장치로는 동기 직렬 인터페이스(SPI)(140)가 있다. 마이크로제어기(M)는 표준 동기 직렬 채널인 동기 직렬 인터페이스(140)에서 마스터의 역할을 한다.

개시된 실시예에서, 마이크로제어기(M)는 통신 환경들에 특히 적합하다. 이때문에, 마이크로제어기(M)의 직렬 통신 주변장치들(172)은 하이 레벨 데이터 링크 제어(HDLC) 제어기(144), 범용 직렬 버스(USB) 제어기(146) 및 고속 직렬 포트(HSUART)(148)를 포함하는 다수의 고속 통신 제어기들을 포함한다. 개시된 HDLC 제어기(144)는 4개의 HDLC 채널들(164)을 제공한다. HDLC 채널들(164) 및 USB 제어기(146)는 "스마트 DMA(smartDMA)" 유닛(150)에 의해 기록 및 판독될 수 있는바, 이 유닛은 DMA 채널들의 쌍들을 통해 액세스되는 연쇄 버퍼들(chained buffers)을 제공한다. 스마트 DMA 유닛(150)은 과도한 실행 유닛(124)의 중재없이 높은 정도의 패킷화된 전송을 허용한다. 스마트 DMA 유닛(150)은 바람직하게는 4개의 스마트 제어기들, 즉 SmartDMA(0-3)으로 이루어지는바, 이를 각각은 DMA 채널들의 쌍으로 이루어진다.

상기 HSUART(148)는 버스를 통해 마이크로제어기(M) 외부의 디바이스들에 대한 비동기 직렬 링크를 형성한다. 비동기 특성은 HSUART(148)가 데이터를 클럭하기 위해 개별적인 클럭 신호를 제공하지 않음을 나타낸다. 대신에, 데이터가 전송 및 수신되는 속도는 미리 결정되거나 또는 자동보딩(autobauding)에 의해 결정되어야 하고, 전송측 및 수신측에서 독립적으로 제어되어야 한다. 이러한 데이터 속도는 보드 속도로서 알려져 있다. 이해될 사항으로서, 마이크로제어기(M)는 다수의 HSUART(148)들을 포함할 수 있다.

개시된 HDLC 제어기(144)는 또한 인터페이스 멀티플렉서(162)를 포함한다. 이 멀티플렉서(162)는 4개의 HDLC 채널들(164), 4개의 시간 슬롯 할당기(time slot assignor: TSA)들(166) 및 다수의 외부 버스들을 결합한다. 구체적으로, 시간 슬롯 할당기들 또는 기타 다른 것을 이용하여, HDLC 채널들(164)은 펄스 코드 변조(PCM) 하이웨이, 범용 회로 인터페이스(GCI), ISDN 지향형 변조 인터페이스 개정 2(ISDN oriented modular interface revision 2: IOM-2) 직렬 버스, 데이터 캐리어 장비(DCE) 직렬 인터페이스, 및 패킷화된 통신을 빈번하게 이용하는 기타 범용 및 특정 인터페이스들에 선택적으로 결합될 수 있다. 또한, 이 HDLC 채널들(164)은 HDLC, SDLC, 평형 링크 액세스 절차들(Link Access Procedures Balanced: LAPB), D-채널 상에서의 링크 액세스 절차들(Link Access Procedures on the D-channel: LAPD) 및 PPP를 지원하는 바, 상기 설명한 바와 같이 이들 각각은 등시성(isochronous) 또는 등시성 탑입의 통신을 위해 각 HDLC에 직렬 프레임의 일부를 할당하는 독립적인 시간 슬롯 할당기(166)를 포함한다.

도 1B는 본 발명에 따라 구현된 마이크로제어기(M)에 대한 예시적인 핀아웃들을 도시한다. 클럭(102)에 대한 클럭 핀아웃들, 버스 인터페이스 유닛(120)에 대한 어드레스 및 어드레스/데이터 버스 핀아웃들, 이 또한 대체로 버스 인터페이스 유닛(120)에 대한 버스 상태 및 제어 핀아웃들, 타이머 제어 유닛(112)에 결합된 타이머 제어 핀아웃들, USB 제어기(146)에 대한 USB 제어 및 송수신기 제어 핀아웃들, 동기 직렬 인터페이스(140)에 대한 동기 직렬 제어기 핀아웃들, 프로그램 가능한 입출력 유닛(132)에 대한 프로그램 가능한 I/O 핀아웃들, 리셋 제어 핀아웃들, 칩 선택 유닛(126) 및 버스 인터페이스 유닛(120) 둘다에 결합된 메모리 및 주변장치 제어 핀아웃들, 범용 DMA 유닛(116) 및 스마트DMA 유닛(150)에 대한 DMA 제어 핀아웃들, HDLC 제어기(144)에 결합하기 위한 HDLC 채널/DCE 인터페이스/PCM 인터페이스 핀아웃들, 저속

UART(136)에 대한 UART 핀아웃들 및 HSUART(148)에 대한 고속 UART 핀아웃들이 도시되어 있다. 이러한 모든 핀아웃들은 물론 예시적인 것이며, 다양한 다른 기능 유닛들 및 관련된 핀아웃들이 본 발명의 정신을 벗어나지 않으면서 이용될 수 있다. 예를 들어, 본 발명의 정신을 벗어나지 않으면서, 도 1A의 다수의 통신들 및 범용 주변장치들은 제거 또는 부가될 수 있다.

본 발명에 따른 기술들 및 회로는 다양한 마이크로제어기들 및 다른 유사한 환경들에 적용될 수 있다. "마이크로제어기"라는 용어 자체는 당업계에서 다양한 정의들을 갖는다. 일부 회사들은 온보드 메모리를 갖지 않는 경우(I/O와 같은) 추가 특징들을 갖는 프로세서 코어를 "마이크로제어기"라 칭하며, 현재는 디지털 신호 프로세서(DSP)들이 특정 제어기 기능 및 범용 제어기 기능 모두에 이용된다. 따라서, 본원에서 이용되는 "마이크로제어기"라는 용어는 모든 제품들을 망라하며, 일반적으로는 모두 단일의 모놀리식 집적 회로에서 구현되는 부가 기능을 갖는 실행 유닛을 의미한다.

도 2는 DMA 유닛(116) 및 고속 UART(148)(본원에서는 비동기 직렬 포트(ASP)(148)로서 개시된다)를 도시한다. 이는 또한 상기 인용한 출원인 "A METHOD AND APPARATUS FOR SUPPORTING HIGH DATA RATES OVER ON ASYNCHRONOUS SERIAL LINE USING DMA"에 개시되어 있다. ASP(148)는 여분의 직렬 비트로서 "어드레스 비트"를 이용하는 비동기 직렬 프로토콜을 지원할 수 있다.

도 3은 이러한 프로토콜을 이용하는 비동기 직렬 전송을 예시한다. 시작 비트(200) 이후, ASP(148)는 7개 또는 8개의 데이터 비트들(202)을 전송 또는 수신한다. 이들은 비동기 프로토콜로 하위 비트가 먼저 전송되는 표준 데이터 비트들이다. 그러나, 7개 또는 8개의 데이터 비트들(202) 이후, ASP(148)에 의해 지원되는 어드레스 비트 프로토콜은 선택적인 어드레스 비트(AB)(204)를 제공한다. 이 어드레스 비트는 전형적으로 ASP(148)에 의해 전송 또는 수신되는 8번째 또는 9번째 비트 중 어느 하나이며, 전형적으로 1개의 마스터 디바이스가 다수의 슬레이브 디바이스들을 제어할 것을 요구하는 멀티 드롭(multi-drop) 응용들과 같은 응용들에서 이용된다. 비록 어드레스 비트라 칭해지지만, 이 비트는 흐름 및 다른 제어를 위해 슬레이브 디바이스들 내에서 인터럽트들을 효과적으로 야기시키는 확장 비트의 역할을 할 수 있다. 이러한 어드레스 비트 프로토콜은 당업계에서 알려져 있다.

상기 선택적인 어드레스 비트(AB)(204)의 뒤에는, 선택적인 패리티 비트 PB(206), 정지 비트(ST)(208) 및 선택적인 제 2 정지 비트(ST)(210)가 따른다.

도 2를 다시 참조하여, DMA 유닛(116) 및 ASP(148)는 도 3에 도시된 어드레스 비트(AB)(204)를 이용하는 데이터를 전송 및 수신하는 데에 유용한 본 발명에 다른 부가적인 특징들을 갖는다. 이러한 특징들은 DMA 유닛(116) 및 ASP(148) 내의 레지스터들의 세트(본원에서는 DMA 레지스터들(212) 및 ASP 레지스터들(214)로서 개시된다)를 검사함으로써 가장 잘 이해된다. DMA 레지스터들(212)은 도 6A-6E와 관련하여 하기에서 더 설명될 것이며, ASP 레지스터(214)는 도 7A-7G와 관련하여 하기에서 더 설명될 것이다.

#### 바이트에서 워드로의 확장 및 워드에서 바이트로의 압축 DMA 유닛

본 발명에 따른 마이크로제어기(M)의 일 양상에서, DMA 유닛(116)은 2개의 서로 다른 데이터 사이즈를 갖는 소스 및 목적지 간에 데이터를 전송하는 동안 이 데이터를 압축 및 복원할 수 있다. 예를 들어, DMA 유닛(116)은 소스 메모리 블록으로부터 데이터를 바이트 단위로 판독하고, 판독된 각 데이터 바이트를 연속 워드들의 하위(또는 상위) 바이트로서 목적지 메모리 블록에 기록할 수 있다. 역으로, DMA 유닛은 소스 블록으로부터 연속적인 데이터 워드들의 하위 바이트를 판독한 다음, 판독된 바이트들을 목적지 블록에 연속적으로 저장할 수 있다. 이는, ASP(148)와 관련하여, 이것이 확장된 판독 및 기록 모드에서 이용될 때에 특히 유용하다. 도 7A-7G와 관련하여 하기에서 더 설명되는 바와 같이, 그리고 상기 인용한 계류중인 출원인 "A METHOD AND APPARATUS FOR SUPPORTING HIGH DATA RATES OVER ON ASYNCHRONOUS SERIAL LINE USING DMA"에 개시된 바와 같이, ASP(148)는 직렬 라인을 통해 7 또는 8 비트 데이터 유닛들을 판독할 수 있지만, 그 I/O 판독에 대응하는 어드레스 비트 및 상태 비트들 모두와 함께 상기 데이터를 16 비트 워드에 저장한다. 이들은 하기에서 설명되는 도 7G에서 설명되지만, 요약하자면, 실제로 수신된 7 또는 8 비트의 데이터와 함께 패리티 에러, 오버런 에러(overrun error), 프레이밍 에러(framing error), 캐릭터 매칭(character match), 브레이크(break), 어드레스 비트 및 다른 상태가 저장될 수 있다. 이것이 DMA를 이용하여 수행되면, 실행 유닛(124)은 돌아가 수신된 데이터를 검사하여, 어떠한 에러가 발생했을 지도 모르는 장소 또는 어드레스 비트들이 세팅되었을 지도 모르는 장소를 결정한 다음, 그에 따라 데이터를 처리할 수 있다.

그러나, 일단 에러들이 검사되고 어드레스 비트들이 처리되면, 전형적으로 수신된 데이터는 더 이상 관련 상태를 필요로 하지 않는다. 즉, 실행 유닛(124)은 상기 데이터를 워드로서 대신 바이트들 내에 7 또는 8비트 데이터로서 저장할 수 있다.

DMA 유닛(116)이 특히 유익한 것은 이 점이다. 도 4는 설명되는 ASP 유닛(148)으로부터 데이터를 처리하는 DMA 유닛(116)을 도시한다. 이 DMA 유닛(116)은 상기 데이터를 블록(218) 내의 일련의 데이터 및 상태 바이트들(DATA1, STATUS1, DATA2, STATUS2 등으로서 나타냄)로서 메모리(216)에 저장한다. 따라서, 각각의 7 또는 8 비트 데이터 값(DATA1-DATAn)은 그의 관련된 상태 바이트들(STATUS1-STATUStn)과 결합될 때 16 비트들을 점유한다.

그러나, DMA 유닛(116)은 블록(218)으로부터 메모리(216) 내의 다른 블록(220)으로의 전송을 수행하도록 실행 유닛(124)에 의해 프로그램될 수 있지만, 이 블록은 관련된 상태없이 다수의 연속적인 데이터 값들(DATA1-DATAn) 만을 포함한다. DMA 유닛(116)은 먼저 제 1 데이터 항목(DATA1)을 판독한 다음, 블록(218)으로부터 이를 블록(220)의 목적지 위치(DATA1)에 기록한다. 그러나, DMA 유닛(116)은 이후 블록(220) 내의 목적지 어드레스를 1 만큼 증분시킴과 동시에, 블록(218)의 소스 어드레스를 2 만큼 증분시킨다. 따라서, 블록(218)으로부터 판독된 다음 데이터 항목은 DATA2(STATUS1은 건너뛴다)가 되는바, 이는 이후 제 1 데이터 항목(DATA1) 바로 직후 목적지 블록(220)에 바이트로서 기록된다. 이것을 반복함으로써, 원래의 16 비트 데이터 및 상태 값들이 단지 8비트 데이터 값들이 되도록 데이터를 압축한다.

도 5는 반대의 경우, 즉 ASP(148)에 의한 외부 데이터의 기록을 도시한다. 여기에서, 소스 데이터 블록(222)은 마이크로 제어기(M)가 외부의 비동기 직렬 라인으로 전송해야 하는 데이터를 포함한다. 이 데이터는 4개의 데이터 항목들(DATA4)을 포함하는바, 이들은 각각 메모리의 한 바이트 내에서 7 또는 8 비트들을 점유한다. DMA 유닛(116)은 먼저 블록(222)의 데이터 항목들중 첫 번째 항목(DATA1)을 판독한 다음, 이 데이터 항목(DATA1)을 목적지 블록(224)에 기록하도록 프로그램된다. 이후, 데이터 블록(222) 내의 소스 어드레스가 증분되지만, 목적지 블록(224) 내의 목적지 어드레스는 2만큼 증분된다. 따라서, 다음 데이터 항목(DATA2)이 소스 블록(222)으로부터 판독되지만, 2바이트 뒤에 이는 목적지 블록(224)에 기록된다.

상기 데이터가 실제로 전송되기 전에, 실행 유닛(124)은 목적지 블록(224)의 데이터 항목들(DATA1-DATA4)의 중재 바이트들에 저장된 어드레스 비트들을 클리어(clear)하는 것이 바람직하다. 여기에서는, 3개의 어드레스 비트들(226)이 클리어되고, 1개의 어드레스 비트(228)가 세팅되는 것으로 도시된다.

DMA 유닛(116)은 이후 ASP(148)의 확장된 기록 성능을 이용하여 ASP(148)에 대해 워드 사이즈의 기록을 수행하도록 프로그램된다. 상위 바이트의 하위 비트는 후속 데이터의 전송을 위한 어드레스 비트로서 이용되어, 4개의 예시된 데이터 항목들(230, 232, 234 및 236)을 야기시키는바, 이들중 첫 번째 항목은 그 어드레스 비트가 세팅되지만, 나머지 항목들은 세팅되지 않는다.

DMA 유닛(116)은 1개 이상의 DMA 채널들을 포함할 수 있으며, 이러한 DMA 채널들은 원형 버퍼들(circular buffers)로서 구현될 수 있다. 도 4에서는 또한, 제 1 채널이 ASP(148)로부터 확장 데이터를 읽은 다음, 이를 버퍼(218)로서 구현되는 원형 버퍼에 기록하고, 이후 제 2 채널이 버퍼(218)로부터 판독함으로써 목적지 버퍼(220) 내에 데이터를 압축하도록, 2개의 채널들을 구현할 수 있다.

DMA 유닛(116)에 의한 데이터의 압축 및 복원을 제공함으로써, 실행 유닛(124)은 DMA 유닛(116)이 ASP(148)로 데이터를 전송 또는 수신하기 전에 데이터로부터 불필요한 정보를 스트리밍하거나 데이터에 불필요한 정보를 부가하는 데에 필요한 오버헤드를 처리하는 것으로부터 해방된다.

도 6A-6E는 본 발명에 따라 압축 및 복원을 구현하는 데에 이용되는 5개의 DMA 레지스터들(212)을 도시한다. 도 6A는 범용 DMA 채널 "x" 제어 레지스터(GDxCON0)(300)를 도시한다. (주목할 사항으로서, 4개의 채널들이 있기 때문에, "x"는 1 내지 4가 된다.)

GDxCON0 레지스터(300)는 시작/정지 비트(ST)(302), 자동 시작 비트(AST)(304), 터미널 카운트 정지 비트(TC)(306), 인터럽트 인에이블 비트(INT)(308), 우선도 필드(priority field: P)(310) 및 DMA 요구 소스 필드(DSEL)(312)와 같은 다수의 표준 범용 DMA 제어 비트들을 포함한다.

GDxCON0 레지스터(300)는 또한 전송 사이즈 비트(TS)(314)를 포함한다. 이 비트는 채널이 한번에 데이터 바이트를 전송할지(TS = 0 또는 1'b0), 아니면 한번에 워드를 전송할지(TS = 1'b1)를 선택한다. 본 발명에 따른 압축 및 복원을 이용하게 되면, TS 비트(314)는 일반적으로 바이트 사이즈 전송에 대해 0으로 세팅될 것이다.

도 6B는 제 2 범용 DMA 제어 레지스터(GDxCON1)(316)를 도시한다. 이 GDxCON1 레지스터(316)는 또한 소스 어드레스 공간 선택 비트(SM/\*IO)(318), 소스 어드레스 래프 필드(source address wrap field)(SAW)(320), 목적지 어드레스 공간 선택 비트(DM/\*IO)(322) 및 목적지 어드레스 래프 필드(DAW)(324)와 같은 다수의 표준 DMA 비트들을 포함한다. SM/\*IO 비트(318) 및 DM/\*IO(322)는 소스 및 목적지 공간이 메모리가 되는지 아니면 I/O이 되는지를 선택한다.

소스 또는 목적지 어드레스 간격이 메모리 내에 있을 때, 일반적으로 데이터가 전송 또는 수신된 후 소스 및 목적지 어드레스를 증분 또는 감분시키는 것이 바람직하다. 이때문에, 2개의 필드들, 즉 소스 증분 필드(SINC)(326) 및 목적지 증분 필드(DINC)(328)가 제공된다. 이들은 각 전송 이후 소스 및 목적지 포인터에 부가되는 4비트의 2의 보수값(complement value)들이다. 예를 들어, SINC 필드(326) 또는 DINC 필드(328)가 0이면, 어떠한 증분도 없다. 이들이 2진수 1과 같거나, 또는 4'b0001이라면, 필드들은 1 만큼 증분된다. 이들이 4'b0010이라면, 포인터들은 2 바이트 만큼 증분되고, 4'b0011이라면, 3 바이트 만큼 증분된다. 음의 값들에 대해서는 반대가 된다. 예를 들어, 2의 보수 포맷을 이용하여, SINC 필드(326) 또는 DINC 필드(328)이 4'b1111이면, 소스 또는 목적지 어드레스는 전송 후에 1 만큼 감분될 것이다.

개별적인 SINC 필드(326) 및 DINC 필드(328)를 제공함으로써, 그리고 또한 증분 또는 감분의 양이 데이터 항목의 사이즈에 독립적이라고 가정하면, DMA를 이용한 데이터의 압축 또는 복원이 영향을 받을 수 있다. 이는 도 4 및 도 5와 관련하여 하기에서 다시 한번 설명된다.

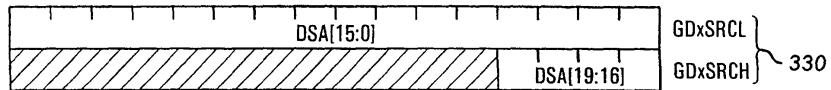

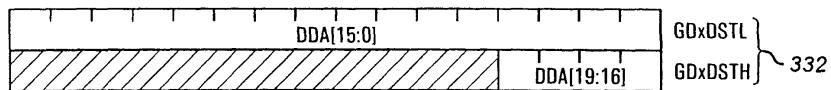

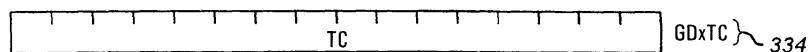

도 6C 및 6D는 소스 어드레스 레지스터(330) 및 목적지 어드레스 레지스터(332)를 도시한다. 마지막으로, 도 6E는 전송 카운트 레지스터(334)를 도시한다. 이들은 모두 DMA 설계와 관련하여 잘 이해된다.

도 4 및 5를 다시 참조하여, 그리고 도 6A 내지 6E에서 설명된 레지스터들이 주어지면, 압축을 위한 DMA 유닛(116)의 프로그래밍 및 동작이 더 잘 이해된다. 도 4에서, ASP(148)와 목적지 블록(218) 간의 전송에 대해, DMA 유닛(116)은 한 세트의 값들(336)로 프로그램된다. 구체적으로, 소스는 I/O 위치로부터 되도록 세팅되고 각 전송 후에 0 만큼 증분하도록(I/O 위치에 대해 적당하다) 세팅되며, 목적지는 메모리로 세팅되고 각 전송 후에 2 만큼 증분하도록 세팅된다. 또한, 데이터 사이즈는 워드로 세팅된다. 이에 의해, 각 전송은 ASP(148)로부터의 16 비트의 확장된 직렬 판독값이 될 것이며, 이는 목적지 블록(218)에 워드 단위로 저장된다.

압축 기능에 있어서, DMA 유닛(116)은 한 세트의 값들(338)로 프로그램된다. 구체적으로, 소스는 메모리에서 세팅되며 (그리고 소스 어드레스(330)는 소스 블록(218)의 시작으로 세팅될 것이며), 각 전송 후에 2 만큼 증분하도록 세팅된다. 목적지 또한 메모리에 세팅되지만, 목적지 어드레스는 각 전송 후에 단지 1 만큼 증분된다. 마지막으로, 전송 사이즈는 1 바이트에 대해 세팅된다. 이는 소스 블록(218)으로부터 1 바이트가 판독되어 목적지 블록(220)에 DATA1로서 기록될 것임을 의미한다. 그러나, 소스 어드레스(330)는 이후 2 만큼 증분되지만, 목적지 어드레스(332)는 단지 1 만큼 증분된다. 이후, 제 2 데이터 바이트(DATA2)가 소스 블록(218)으로부터 읽혀진 다음, 목적지 블록(220)에 상기 DATA1의 바로 뒤에 기록될 것이다. 따라서, STATUS1에 있어서의 불필요한 상태 정보는 건너뛴다.

주목할 사항으로서, 목적지 블록(220)은 실제로 소스 블록(218)에 의해 중복되도록 프로그램될 수 있는데, 그 이유는 데이터가 소스 블록(218)으로부터 판독된 후, 이는 더 이상 필요없기 때문이다. 따라서, 소스 버퍼가 글자 뜻대로 목적지 버퍼로서 이용되어, 메모리 공간을 절약할 수 있다.

도 5는 한 세트의 프로그램된 값들(340)에 의해 DMA 유닛(116)의 확장 성능을 도시한다. 여기서, 8비트 데이터의 소스 블록(222)은 메모리로부터 메모리로의 전송을 수행하도록 DMA 유닛(116)을 세팅시키고, SINC 필드(326)를 1의 값으로 세팅시키지만, DSINC 필드(328)는 2의 값으로 세팅시킴으로써 확장된다. 전송 사이즈 비트(TS)(314)는 0으로 세팅되며, 이에 따라 데이터는 한번에 한 바이트씩 전송된다. 이러한 프로그래밍을 이용하여, 데이터 바이트는 소스 블록(222)으로부터 판독된 다음 목적지 블록(224)에 기록되지만, 소스 블록(222)으로부터 연속적으로 판독되는 다음 데이터 바이트는 목적지 블록(224)에 2 바이트 후에 기록된다. 실행 유닛(124)은 이후 목적지 블록(224)에 있어서의 어드레스 비트들(AB)를 적절히 세팅 또는 리셋시키며, ASP(148)로 제 2 DMA 전송을 시작한다.

여기에서는, 한 세트의 프로그램된 값들(342)이 이용되는바, 이들은 메모리의 소스 및 I/O 공간의 목적지를 제공하고, 2의 소스 증분 SINC(326) 값을 제공하며, 어떠한 목적지 증분도 제공하지 않는다. 또한, 전송 사이즈 비트(TS)(314)는 워드 전송을 위해 1로 세팅된다. 결과적으로, 확장된 데이터가 ASP(148)에 기록되며, 이에 따라 직렬 데이터 전송에 있어서 9 번째 어드레스 비트를 제어할 수 있게 된다.

따라서, 전송되는 데이터의 사이즈가 독립적인 소스 충분 및 목적지 충분의 독립적인 제어성을 제공함으로써, 메모리의 압축 및 복원이 영향을 받을 수 있다. 이는, 워드 데이터를 바이트 데이터로 압축하거나, 반대로 바이트 데이터를 워드 데이터로 복원하는 것이 바람직한 다양한 다른 기능들에 이용될 수 있다.

### 어드레스 비트들을 이용한 캐릭터 매칭

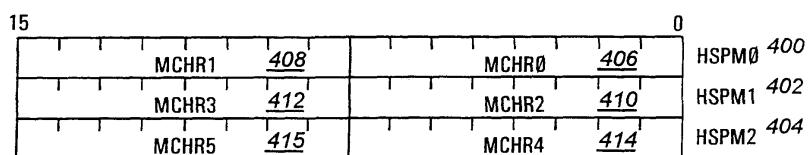

도 7A-7G는 본 발명에 따른 다른 특징을 구현하는 특정한 ASP 레지스터들(214)을 도시한다. 도 7A는 수신된 데이터의 캐릭터들을 매칭시키기 위해 ASP(148)에 의해 이용되는 6개의 캐릭터 매칭 바이트들을 도시한다. 구체적으로, 3개의 레지스터들(HSPM0(400), HSPM1(402) 및 HSPM2(404))이 6개의 캐릭터 매칭 값들(MCHRO(406) 내지 MCHR5(415))을 포함한다.

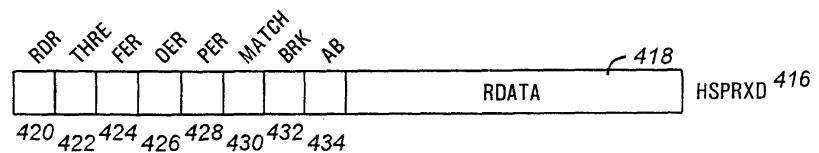

이러한 바이트 사이즈 값들(MCHRO(406) 내지 MCHR5(415))의 동작은 비동기 직렬 포트(418) 수신 레지스터 (HSPRXD)(416)를 도시하는 도 7G와 관련하여 보다 잘 이해된다. 이 레지스터는 7 또는 8 비트 값의 수신 데이터 (RDARA)(418)를 포함하며, 상태 비트들(420 내지 434)을 또한 포함한다.

역사적으로, 수신 데이터(RDATA)(418) 만이 매칭 캐릭터 값들(MCHRO(406) 내지 MCHR5(415))과 비교된다. RDATA 값(418)이 매칭 캐릭터 값들 중 하나에 매칭하면, 상태 레지스터에 상태 비트가 세팅되며(이는 도 7D와 관련하여 하기에서 설명된다), 적절한 마스크 값이 세팅되는 경우에는 인터럽트가 발생된다(이는 도 7E와 관련하여 하기에서 설명된다). 역사적으로, 어드레스 비트(AB)(204)는 HSPRXD 레지스터(416)의 확장 데이터 내의 제 1 비트로서 반영되고(여기에서는 어드레스 비트 값(AB)(434)), 또한 도 7D와 관련하여 하기 설명되는 상태 레지스터에서도 발견될 수 있다. 그러나, 어드레스 비트는 캐릭터 매칭 값들(MCHRO(406) 내지 MCHR5(415)) 중 하나와 매칭시키는 데에 이용되지 않는다.

본 발명에 따르면, 부가적인 비트들이 제공되는 바, 이들이 세팅되면, RDATA 값(RDATA)(418)에 부가하여 어드레스 비트 값(AB)(434)이 매칭된다.

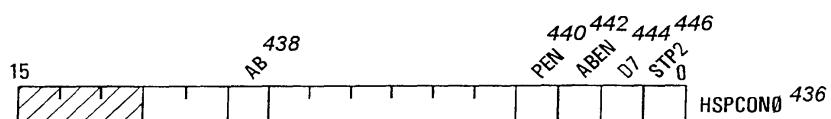

이는 도 7C에 도시된 고속 직렬 포트 제어 레지스터(HPCONO)(436)와 관련하여 보다 잘 이해된다. 이 레지스터는 어드레스 비트가 이용될 것이지(이는 ABEN 비트(442)에 의해 표시된다), 패리티 비트들(PB)(206)이 이용될 것이지(이는 패리티 인에이블 비트(REN)(440)에 의해 표시된다), 7 또는 8 비트의 데이터가 이용될 것인지 그리고 이에 따라 비트들(202)의 D7 비트가 이용될 것인지(이는 인에이블 비트(D7)(444)에 의해 표시된다), 그리고 제 2 정지 비트(ST2)(210)가 이용될 것인지(이는 제 2 정지 비트 인에이블 비트(STR2)(446)에 의해 표시된다)를 결정하기 위한 구성 세팅(configuration settings)을 부분적으로 제공한다. 데이터를 기록할 때, 어드레스 비트 세팅 또는 리셋 비트(AB)(438)는 (ABEN 비트(442)에 의해 제어되는) 어드레스 비트 통신이 인에이블되는 한, 전송되는 어드레스 비트를 세팅 또는 리셋시킨다.

이러한 모든 비트들(438 내지 446)은 전송되는 프레임의 길이에 영향을 미친다. 그러나, 개시된 실시예에서, 그리고 역사적으로, 수신 데이터(418)가 7 비트 데이터(D7 비트(444)가 거짓)이고 어드레스 비트가 인에이블(ABEN 비트(442)가 참)되더라도, RDATA(418)는 어드레스 비트를 포함하지 않는다. 대신에, 이는 여전히 HSPRXD 레지스터(416)의 상위 바이트에 어드레스 비트(AB)(434)로서 저장된다. 따라서, 이 비트는 매칭 캐릭터들(MCHRO(406) 내지 MCHR5(415)) 중 어느 것과도 결코 매칭하지 않는다.

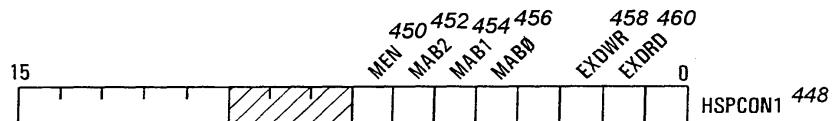

그러나, 본 발명에 따르면, 부가적인 매칭 캐릭터 어드레스 비트(MATCH)가 제 2 제어 레지스터(HSPCON1(448))에 제공된다. 구체적으로, 이 레지스터(448)는 매칭 인에이블 비트(MEN)(450)를 포함하는 바, 이것이 참일 때, MCHRO(406) 내지 MCHR5(415)의 캐릭터 매칭을 인에이블시킨다. 그러나, 본 발명에 따르면, 부가적인 캐릭터 매칭 비트들이 제공된다. 제어 레지스터(HSPCON0(436))의 ABEN 비트(442)에 의해 어드레스 비트가 인에이블될 때, 3개의 매칭 어드레스 비트들(MAB2(452), MAB1(454) 및 MAB0(456))은 효과적으로 3개의 매칭 레지스터들(HSPM0(400) 내지 HSPM2(404))에 대한 어드레스 비트 매칭 비트가 된다.

예를 들어, MAB2 비트(452)가 0이고 ABEN 비트(442)가 1일 때, 수신된 캐릭터는 HSPM2 레지스터(404) 내의 캐릭터에 매칭시키기 위해 그의 어드레스 비트(AB)(204)를 클리어해야 한다. MAB2 비트(452)가 세팅되고, ABEN 비트(442)가 참일 때, 수신된 캐릭터는 HSPM2 레지스터(404) 내의 캐릭터에 매칭시키기 위해 그의 어드레스 비트(AB)(204)를 세팅시켜야 한다. MAB1 비트(454) 및 MAB0 비트(456)는 유사하게 HSPM1 레지스터(402) 및 HSPM0 레지스터(400)에 대응한다.

따라서, HSPCON1 레지스터(448)의 이러한 부가적인 비트들은 HSPMO 레지스터(400) 내지 HSPM2 레지스터(404)중 대응하는 것들에 대한 어드레스 매칭을 제공한다. ASP(148)는, 레지스터들(HSPMO(400) 내지 HSPM2(404))중 하나가 캐릭터매칭을 위해 세팅되고 다른 2개가 어드레스 매칭을 위해 세팅되는 경우, 셋업될 수 있다.

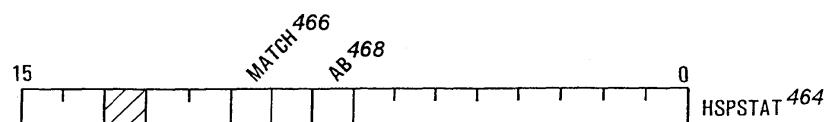

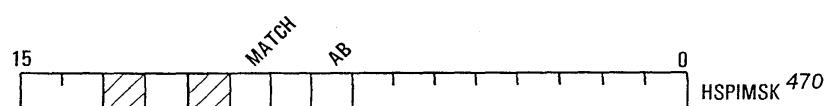

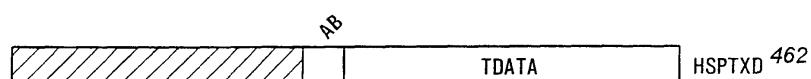

HSPCON1 레지스터(448)는 확장된 기록 비트(458) 및 확장된 판독 비트(460)를 더 포함하는바, 이들이 참이면, 16 비트 데이터가 전송 레지스터(HSPTXD)(462)(도 7F 참조)로부터 판독되거나, 수신 레지스터(HSPRXD)(416)(도 7G 참조)에 수신될 것이다. 이러한 값들이 디스에이블되면, 8 비트 데이터 만이 이를 레지스터들에 저장되며, 어드레스 비트 및 매칭 상태는 상태 레지스터(HSPTAT)(464)(도 7D 참조)를 판독함으로써만 결정될 수 있다. 특히, 이 상태 레지스터(464)는 유입 데이터(incoming data)가 HSPM0-HSPM2 레지스터들(400-402)중 하나에 대한 (적절한) 캐릭터 또는 어드레스 매칭인 경우 참으로 세팅되는 매칭 비트(MATCH)(466), 및 유입 데이터의 어드레스 비트가 세팅되는 경우 참으로 세팅되는 어드레스 비트(AB)(468)를 포함한다. 인터럽트 마스크 레지스터(HSPIMSK)(470)는 이에 대응하게 매칭 비트(MATCH)(466) 및 어드레스 비트(AB)(468)를 인터럽트들로서 통과시킨다.

도 8은 본 발명에 따른 어드레스 비트 매칭이 이용될 수 있는 멀티드롭 시스템을 도시한다. 호스트 시스템(500)은 직렬 데이터를 다수의 멀티드롭 주변장치들(502, 504 및 506)로 전송한다. 이러한 주변장치들 각각은 자신의 마이크로제어기(M)(508, 510 및 512)를 포함한다. 이들 각각은 주변장치들(502, 504 및 506)에 대해 유일한 어드레스(1, 2 및 3)를 갖도록 프로그램될 수 있다. 이들 각각은, 주변장치들중 하나가 어드레스 매칭을 가질 때 까지 수신 캐릭터들이 주변장치들(502, 504 및 506) 각각에 의해 효과적으로 덤프(dump)되는 아이들 모드(idle mode)에 놓여질 수 있다. 예를 들어, 주변장치(502)의 상기 마이크로제어기(508)는, MCHRO 바이트(406)가 주변장치(502)에 할당되는 "1" 어드레스를 포함하는 적절한 어드레싱 정보를 포함하고, 그의 관련된 어드레싱 매칭 비트(MAB0)(456)가 어드레스 비트 인에이블 비트(ABEN)(442)와 함께 세팅되도록 프로그램될 수 있다. 이러한 방식으로, 호스트(500)가 적절한 어드레스 매칭(MCHRO)(406)과 함께 비동기 데이터의 프레임을 주변장치(502)로 전송하면, 이 데이터는 MCHRO(406) 내의 캐릭터에 매칭되고, 세팅된 어드레스 비트는 MAB0(456) 비트에 매칭된다. 따라서, 매칭 비트(MATCH)(446)는 HPSTAT 레지스터(464)에 세팅되며, 그리고 매칭 인터럽트가 HSPIMSK 레지스터(470)에서 통과하는 것으로 설정되었다고 가정하면, 인터럽트가 실행 유닛(124)으로 전달되어 후속 데이터를 처리하도록 주변장치(502)를 설정한다.

따라서, 특정한 매칭 어드레스 레지스터들에 대해 캐릭터 매칭 및 어드레스 매칭을 독립적으로 제공함으로써, 본 발명에 따른 비동기 직렬 포트는 매칭 가능한 캐릭터 데이터에 기초하여 데이터 프레임들의 시작 및 끝을 검출할 수 있을 뿐 아니라, 어드레스 비트를 또한 매칭시킴으로써 멀티드롭 시스템에서 특정 마이크로제어기가 어드레스되는 때를 검출할 수 있다. 이는 마이크로제어기(M)의 응용들에 유연성을 부여한다.

본 발명에 따른 기술들은 비동기 통신 포트들에 관련하여 설명되었지만, 이들은 압축, 복원 및 어드레스 매칭을 위해 동기 통신 포트들에 관련해서도 마찬가지로 이용될 수 있다.

본 발명의 상기 개시 및 설명은 단지 예시적인 것으로서, 본 발명의 정신을 벗어나지 않으면서 예시된 장치, 구성 및 동작 방법의 세부사항들에 대한 많은 변형들이 이루어질 수 있다.

## 작제

### (57) 청구의 범위

#### 청구항 1.

명령어들을 실행하는 실행 유닛과;

소스 어드레스 레지스터, 목적지 어드레스 레지스터, 소스 증분 필드 및 목적지 증분 필드를 포함하는 직접 메모리 액세스(DMA) 제어기와; 그리고

상기 DMA 제어기에 결합되어 직렬 데이터를 수신 및 전송하는 직렬 포트를 포함하며;

상기 소스 증분 필드 및 상기 목적지 증분 필드는 상기 소스 어드레스 레지스터 및 상기 목적지 어드레스 레지스터의 증분을 독립적으로 제어하고,

상기 소스 어드레스 레지스터 및 상기 목적지 어드레스 레지스터의 증분은 DMA 전송 동안 데이터가 압축 또는 팽창될 수 있도록 전송 사이즈에도 독립적이며, 그리고

상기 DMA 제어기는 상기 직렬 데이터를 상기 직렬 포트로부터 메모리로 그리고 상기 메모리로부터 상기 직렬 포트로 전송하도록 구성될 수 있는 것을 특징으로 하는 마이크로제어기.

## 청구항 2.

제 1 항에 있어서,

상기 DMA 제어기는 수신된 데이터의 상태 부분이 버려지는 경우 메모리로부터 메모리로 후속 DMA를 수행하도록 구성될 수 있는 것을 특징으로 하는 마이크로제어기.

## 청구항 3.

제 2 항에 있어서,

상기 직렬 포트는 비동기 직렬 포트인 것을 특징으로 하는 마이크로제어기.

## 청구항 4.

제 2 항에 있어서,

상기 직렬 포트에 의해 수신된 상태 정보는 또한 어드레스 비트 상태 정보를 포함하는 것을 특징으로 하는 마이크로제어기.

## 청구항 5.

제 4 항에 있어서,

상기 직렬 포트는 동기 직렬 포트인 것을 특징으로 하는 마이크로제어기.

## 청구항 6.

제 1 항에 있어서,

상기 DMA 제어기는 소스 어드레스로부터 목적지 어드레스로의 각각의 데이터 바이트 전송에 대해 상기 소스 어드레스를 2 만큼 증분시키고 상기 목적지 어드레스를 1 만큼 증분시키도록 구성될 수 있는 것을 특징으로 하는 마이크로제어기.

## 청구항 7.

직접 메모리 액세스(DMA) 시스템에 있어서,

소스 어드레스 레지스터, 목적지 어드레스 레지스터, 소스 증분 필드 및 목적지 증분 필드를 포함하는 직접 메모리 액세스 (DMA) 제어기와; 그리고

상기 DMA 제어기에 결합되어 직렬 데이터를 수신 및 전송하는 직렬 포트를 포함하며;

상기 소스 증분 필드 및 상기 목적지 증분 필드는 상기 소스 어드레스 레지스터 및 상기 목적지 어드레스 레지스터의 증분을 독립적으로 제어하고,

상기 소스 어드레스 레지스터 및 상기 목적지 어드레스 레지스터의 증분은 상기 데이터가 DMA 전송 동안 압축 또는 팽창될 수 있도록 전송 사이즈에도 독립적이며, 그리고

상기 DMA 제어기는 상기 직렬 데이터를 상기 직렬 포트로부터 메모리로 그리고 상기 메모리로부터 상기 직렬 포트로 전송하도록 구성될 수 있는 것을 특징으로 하는 DMA 시스템.

#### 청구항 8.

제 7 항에 있어서,

상기 DMA 제어기는 수신된 데이터의 상태 부분이 버려지는 경우 메모리로부터 메모리로 후속 DMA를 수행하도록 구성될 수 있는 것을 특징으로 하는 DMA 시스템.

#### 청구항 9.

제 8 항에 있어서,

상기 직렬 포트는 비동기 직렬 포트인 것을 특징으로 하는 DMA 시스템.

#### 청구항 10.

제 8 항에 있어서,

상기 직렬 포트에 의해 수신되는 상태 정보는 또한 어드레스 비트 상태 정보를 포함하는 것을 특징으로 하는 DMA 시스템.

#### 청구항 11.

제 10 항에 있어서,

상기 직렬 포트는 동기 직렬 포트인 것을 특징으로 하는 DMA 시스템.

#### 청구항 12.

제 7 항에 있어서,

상기 DMA 제어기는 소스 어드레스로부터 목적지 어드레스로의 각각의 데이터 바이트 전송에 대해 상기 소스 어드레스를 2 만큼 증분시키고 상기 목적지 어드레스를 1 만큼 증분시키도록 구성될 수 있는 것을 특징으로 하는 DMA 시스템.

#### 청구항 13.

소스 어드레스 레지스터와;

목적지 어드레스 레지스터와;

메모리로부터 직렬 포트로 데이터를 전송하도록 구성될 수 있는 수단과;

상기 직렬 포트로부터 상기 메모리로 데이터를 전송하도록 구성될 수 있는 수단과; 그리고

소스 어드레스에 의해 지시되는 블록 내에 위치하는 데이터의 일부가 상기 소스 어드레스로부터 목적지 어드레스로 전송하는 동안 스트리밍될 수 있도록, 상기 소스 어드레스로부터 상기 목적지 어드레스로 데이터를 전송한 다음, 상기 소스 어드레스 및 상기 목적지 어드레스를 변경하는 수단을 포함하는 것을 특징으로 하는 DMA 제어기.

#### 청구항 14.

소스 어드레스 레지스터와;

목적지 어드레스 레지스터와;

메모리로부터 직렬 포트로 데이터를 전송하도록 구성될 수 있는 수단과;

상기 직렬 포트로부터 상기 메모리로 데이터를 전송하도록 구성될 수 있는 수단과; 그리고

목적지 어드레스에 의해 지시되는 블록 내에 위치하는 데이터의 일부가 소스 어드레스로부터 상기 목적지 어드레스로 전송하는 동안 스트리밍될 수 있도록, 상기 소스 어드레스로부터 상기 목적지 어드레스로 데이터를 전송한 다음, 상기 소스 어드레스 및 상기 목적지 어드레스를 변경하는 수단을 포함하는 것을 특징으로 하는 DMA 제어기.

#### 청구항 15.

DMA 제어기를 이용하여 메모리 내의 데이터를 압축하는 방법에 있어서,

소스 어드레스 블록 및 목적지 어드레스 블록을 지시하도록 상기 DMA 제어기를 세팅시키는 단계와;

상기 소스 어드레스 블록으로부터 상기 목적지 어드레스 블록으로의 각각의 전송에 대해 소스 어드레스를 2 바이트 만큼 증분시키고 목적지 어드레스를 2 바이트 만큼 증분시키도록 상기 DMA 제어기를 세팅시키는 단계와;

전송 마다 1 바이트의 정보를 전송하도록 상기 DMA 제어기를 세팅시키는 단계와; 그리고

상기 소스 어드레스 블록으로부터의 모든 다른 바이트 정보가 상기 목적지 어드레스 블록에 기록될 때에 버려질 수 있도록 상기 DMA를 수행하는 단계를 포함하는 것을 특징으로 하는 방법.

#### 청구항 16.

제 15 항에 있어서,

상기 소스 어드레스는 상기 목적지 어드레스와 동일한 위치로 세팅되는 것을 특징으로 하는 방법.

#### 청구항 17.

확장된 수신 직렬 데이터를 압축하는 방법에 있어서,

비동기 직렬 포트를 통해 직렬 데이터 및 관련 상태를 수신하는 단계와;

상기 직렬 데이터 및 관련 상태를 메모리 위치로 전송하는 단계와;

다수의 메모리 위치들에 대한 다수의 데이터 및 상태에 대해 상기 수신 및 전송 단계를 반복하여, 상기 데이터 및 상태를 상기 다수의 메모리 위치들에 저장하는 단계와; 그리고

상기 데이터와 관련된 상태를 버린 다음, 상기 상태없이 상기 데이터를 목적지 메모리 위치에 저장함으로써, 상기 다수의 메모리 위치들로부터 데이터의 직접 메모리 액세스 전송을 수행하는 단계를 포함하는 것을 특징으로 하는 방법.

### 청구항 18.

제 17 항에 있어서,

상기 상태는 8 비트들로 저장되고, 상기 데이터는 8 비트들로 저장되며, 그리고

상기 DMA 전송은 소스로부터 목적지로 1 바이트의 데이터를 전송하고, 소스 어드레스 포인터를 2 만큼 증분시키고 목적지 어드레스 포인터를 1 만큼 증분시킨 다음, 상기 전송 단계를 반복함으로써, 상기 데이터로부터 상기 상태를 스트리밍하는 것을 특징으로 하는 방법.

도면

도면 1a

도면1b

도면2

도면3

도면4

도면5

도면6a

도면6b

도면6c

도면6d

도면6e

도면7a

도면7b

도면7c

도면7d

도면7e

도면7f

도면7g

도면8