(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4355445号

(P4355445)

(45) 発行日 平成21年11月4日(2009.11.4)

(24) 登録日 平成21年8月7日(2009.8.7)

|                      |              |

|----------------------|--------------|

| (51) Int.Cl.         | F 1          |

| HO4N 7/30 (2006.01)  | HO4N 7/133 Z |

| GO6T 3/40 (2006.01)  | GO6T 3/40 A  |

| HO3M 7/30 (2006.01)  | HO3M 7/30 A  |

| HO4N 1/393 (2006.01) | HO4N 1/393   |

| HO4N 1/41 (2006.01)  | HO4N 1/41 B  |

請求項の数 13 (全 19 頁)

(21) 出願番号 特願2000-400034 (P2000-400034)

(22) 出願日 平成12年12月28日 (2000.12.28)

(65) 公開番号 特開2002-204454 (P2002-204454A)

(43) 公開日 平成14年7月19日 (2002.7.19)

審査請求日 平成19年7月20日 (2007.7.20)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100090273

弁理士 國分 孝悦

(72) 発明者 芦ヶ原 篤之

東京都大田区下丸子3丁目30番2号 キ

ャノン株式会社内

審査官 金田 孝之

(56) 参考文献 特開平06-325163 (JP, A)

特開平11-065551 (JP, A)

最終頁に続く

(54) 【発明の名称】画像処理装置、画像処理システム、画像処理方法、及び記憶媒体

## (57) 【特許請求の範囲】

## 【請求項1】

プロック単位の直交変換処理及び符号化処理により得られた符号化データを復号する画像処理装置であって、

上記符号化データを可変長復号する可変長復号手段と、

上記可変長復号手段での復号後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大手段と、

上記拡大手段での処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換手段と、

上記逆変換手段での処理後のデータに対して、各プロックの境界線上に一列の補間画素が位置するように全画素を用いて元のサイズに縮小処理する縮小手段とを備えることを特徴とする画像処理装置。

## 【請求項2】

プロック単位の直交変換処理及び符号化処理により得られた符号化データを復号する画像処理装置であって、

上記符号化データを可変長復号する可変長復号手段と、

上記可変長復号手段での復号後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大手段と、

上記拡大手段での処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換手段と、

10

20

上記逆変換手段での処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小手段とを備えることを特徴とする画像処理装置。

【請求項3】

画像の拡大処理を行なう画像処理装置であって、

対象画像データに対して直交変換処理を施す直交変換手段と、

上記直交変換手段での処理後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大手段と、

上記拡大手段での処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換手段と、

上記逆変換手段での処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小手段とを備えることを特徴とする画像処理装置。

【請求項4】

上記縮小手段は、縮小処理前後の画素の面積比に基づく線形縮小処理を実行することを特徴とする請求項1～3の何れか1項に記載の画像処理装置。

【請求項5】

上記縮小手段は、ブロック境界付近の補間画素において、ブロック境界の格子点の周囲の4画素で、且つブロック境界線に隣接する画素の面積比を最も均等にする位置で、補完画素値を生成することを特徴とする請求項4記載の画像処理装置。

【請求項6】

上記縮小手段は、縮小処理前後の画素の位置関係に基づく線形縮小処理を実行することを特徴とする請求項1～3の何れか1項に記載の画像処理装置。

【請求項7】

上記縮小手段は、ブロック境界付近の補間画素において、ブロック境界の格子点の周囲の4画素で、且つブロック境界線に隣接する画素の中心との距離比を最も均等にする位置で、補完画素値を生成することを特徴とする請求項6記載の画像処理装置。

【請求項8】

複数の機器が互いに通信可能に接続されてなる画像処理システムであって、

上記複数の機器のうち少なくとも1つの機器は、請求項1～7の何れか1項に記載の画像処理装置の機能を有することを特徴とする画像処理システム。

【請求項9】

ブロック単位の直交変換処理及び符号化処理により得られた符号化データを復号するための画像処理方法であって、

上記符号化データを、可変長復号する可変長復号ステップと、

上記可変長復号ステップでの復号化後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大ステップと、

上記拡大ステップでの処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換ステップと、

上記逆変換ステップでの処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて元のサイズに縮小処理する縮小ステップとを含むことを特徴とする画像処理方法。

【請求項10】

ブロック単位の直交変換処理及び符号化処理により得られた符号化データを復号するための画像処理方法であって、

上記符号化データを、可変長復号する可変長復号ステップと、

上記可変長復号ステップでの復号化後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大ステップと、

上記拡大ステップでの処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換ステップと、

10

20

30

40

50

上記逆変換ステップでの処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小ステップとを含むことを特徴とする画像処理方法。

【請求項 1 1】

画像の拡大処理を行なうための画像処理方法であって、

対象画像データに対して直交変換処理を施す直交変換ステップと、

上記直交変換ステップでの処理後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大ステップと、

上記拡大ステップでの処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換ステップと、

上記逆変換ステップでの処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小ステップとを含むことを特徴とする画像処理方法。

【請求項 1 2】

請求項 1 ~ 7 の何れか 1 項に記載の画像処理装置、又は請求項 8 記載の画像処理システムの各手段としてコンピュータを機能させるためのプログラムを記憶したことを特徴とするコンピュータ読取可能な記憶媒体。

【請求項 1 3】

請求項 9 ~ 1 1 の何れか 1 項に記載の画像処理方法の各ステップをコンピュータに実行させるためのプログラムを記憶したことを特徴とするコンピュータ読取可能な記憶媒体。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は、例えば、画像信号の復号化処理や拡大処理等の画像処理を行なう装置或はシステムに用いられる、画像処理装置、画像処理システム、画像処理方法、及びそれを実施するための処理ステップをコンピュータが読出可能に格納した記憶媒体に関するものである。

【0 0 0 2】

【従来の技術】

従来より例えば、ブロック単位の直交変換による符号化方式としては、M P E G 等がある。このような符号化方式により得られた符号化データを復号する際、ブロックの境界部分に格子状のエッジが発生してしまう。このようなエッジの発生は、所謂“ブロック歪み”と呼ばれる。これは、復号化画像の画質低下を招く。

また、復号時において、周波数領域での“0”挿入等による画像拡大処理を行なう場合、上記ブロック歪みがより強調されてしまい、さらに画質が低下してしまう。

【0 0 0 3】

そこで、上記の問題を解決するために、例えば、ブロックの境界部分に対して、ローパスフィルタ処理を施すことで、ブロック歪みを低減する画像処理方法が提案されている。

【0 0 0 4】

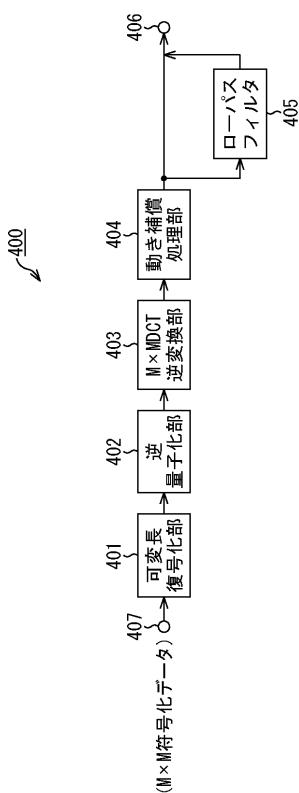

具体的には例えば、上記の画像処理方法を適用した装置としては、特開平 5 - 1 4 7 3 5 号公報等に記載されている。図 1 4 は、当該装置（画像処理装置）4 0 0 の構成の一例を示したものである。

画像処理装置 4 0 0 は、上記図 1 4 に示すように、入力端子 4 0 7 、可変長復号化部 4 0 1 、逆量子化部 4 0 2 、D C T 逆変換部 4 0 3 、動き補償処理部 4 0 4 、ローパスフィルタ 4 0 5 、及び出力端子 4 0 6 を備えている。

【0 0 0 5】

上記図 1 4 の画像処理装置 4 0 0 において、入力端子 4 0 7 には、M P E G 等の符号化方式により得られた、ブロックサイズが  $M \times M$  画素の符号化データが入力される。ここでは、説明の簡単のため、 $M = 8$  として、8 画素  $\times$  8 画素のブロックサイズとする。

【0 0 0 6】

可変長復号化部 401 は、入力端子 407 に入力された符号化データを可変長復号化する。

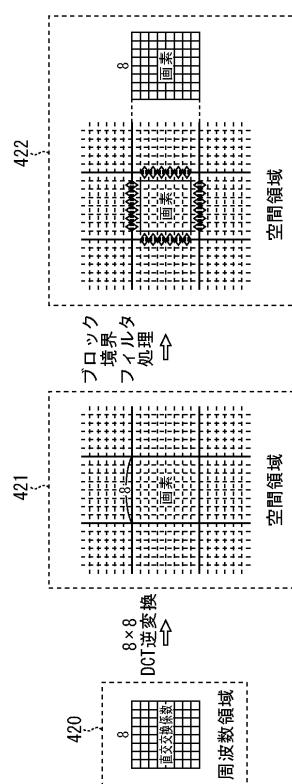

逆量子化部 402 は、可変長復号化部 401 での復号化後のデータを逆量子化して、図 15 の “420” に示すように、ブロック毎の DCT 係数を取得する。DCT 逆変換部 403 は、上記図 15 の “421” に示すように、逆量子化部 402 で得られたブロック毎の DCT 係数を、8 画素 × 8 画素の空間領域データに変換する。

#### 【0007】

動き補償処理部 404 は、DCT 逆変換部 403 で得られたデータに対して動き補償処理を施す。

ローパスフィルタ 405 は、上記図 15 の “422” に示すように、動き補償処理部 404 での処理後のデータにおいて、ブロック境界の画素データにローパスフィルタによるフィルタ処理を施し、その処理結果である画素値を出力端子 406 に対して出力する。

#### 【0008】

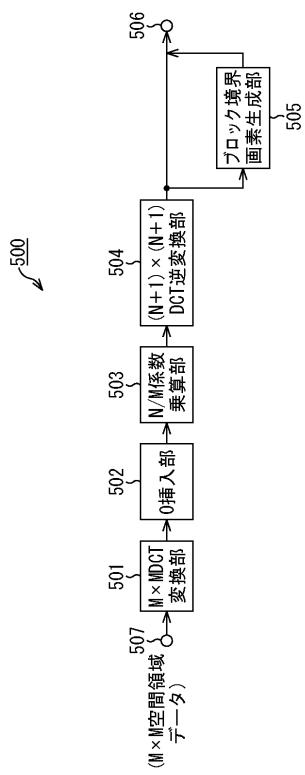

また、例えば、特開平 6 - 325163 号公報等には、ブロックの境界部分の高周波成分を維持することを考慮しつつ、ブロック歪みを低減する画像処理方法が提案されている。図 16 は、当該装置（画像処理装置）400 の構成の一例を示したものである。

画像処理装置 500 は、上記図 16 に示すように、入力端子 507、M × M DCT 変換部 501、0 挿入部 502、N / M 係数乗算部 503、DCT 逆変換部 504、ブロック境界画素生成部 505、及び出力端子 506 を備えている。

#### 【0009】

上記図 16 の画像処理装置 400 において、例えば、M = 8、N = 9 として、5 / 4 倍の拡大画像を経由して 9 / 8 倍の拡大画像を出力する場合、先ず、入力端子 507 には、処理対象画像の空間領域データが入力される。

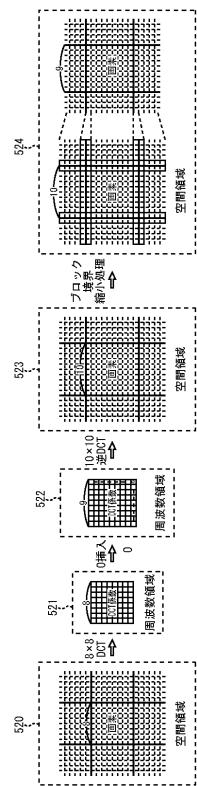

DCT 変換部 501 は、図 17 の “520” に示すように、入力端子 507 に入力された空間領域データを、8 画素 × 8 画素のブロックに分割し、同図の “521” に示すように、当該ブロック単位の DCT 係数を取得する。

#### 【0010】

0 挿入部 502 は、上記図 17 の “522” に示すように、DCT 変換部 501 で得られた DCT 係数において、高周波成分に対応する 17 個の DCT 係数を “0” として、9 画素 × 9 画素のブロックを生成する。

N / M 係数乗算部 503 は、0 挿入部 502 で得られたブロックの DCT 係数に対して、9 / 8 を乗算する。

#### 【0011】

DCT 逆変換部 504 は、上記図 17 の “523” に示すように、N / M 係数乗算部 503 で乗算処理されたブロックに対して、位相のずれた DCT 変換を施し、10 画素 × 10 画素のブロックサイズの空間領域データを生成する。

ブロック境界画素生成部 505 は、上記図 17 の “524” に示すように、DCT 逆変換部 504 で得られた空間領域データにおいて、ブロック境界周辺の画素のみ自ブロックの 36 個の境界部画素と周辺ブロックの 44 個の境界部画素より画素値を算出し、その結果を出力端子 506 に対して出力する。

したがって、出力端子 506 からは、ブロックサイズが 9 画素 × 9 画素の空間領域データが出力される。

#### 【0012】

##### 【発明が解決しようとする課題】

しかしながら、上記図 14 に示したような従来の画像処理装置 400 は、ブロックの境界部分にローパスフィルタによる処理を施す構成であるため、ブロックの境界部分の高周波成分が低下してしまう。

また、上記図 16 に示したような画像処理装置 500 は、目的の拡大倍率 N / M よりも M 分の 1 大きい拡大処理の後、ブロック中心の (N - 1) × (N - 1) 個の画素をそのまま用いて処理（拡大処理）し、ブロック境界部周辺の画素については、自ブロックと隣接す

10

20

30

40

50

るブロックとのブロック境界部の画素を用いて処理（縮小処理）する構成であるため、これを再生した場合、空間的に歪んだ画像になってしまう。

【0013】

そこで、本発明は、上記の欠点を除去するために成されたもので、ブロック単位の直交変換による符号化方式で得られた符号化データを復号する際、ブロック境界の高周波成分を低下させることなく、且つ画像全体を歪ませることなく、ブロック歪みを低減し良好な画質の画像を提供できる、画像処理装置、画像処理システム、画像処理方法、及びそれを実施するための処理ステップをコンピュータが読み出可能に格納した記憶媒体を提供することを目的とする。

【0014】

また、本発明は、上記の欠点を除去するために成されたもので、画像を拡大する際、ブロック境界の高周波成分を低下させることなく、且つ画像全体を歪ませることなく、ブロック歪みを低減し良好な画質の画像を提供できる、画像処理装置、画像処理システム、画像処理方法、及びそれを実施するための処理ステップをコンピュータが読み出可能に格納した記憶媒体を提供することを目的とする。

【0015】

【課題を解決するための手段】

斯かる目的下において、第1の発明は、ブロック単位の直交変換処理及び符号化処理により得られた符号化データを復号する画像処理装置であって、上記符号化データを可変長復号する可変長復号手段と、上記可変長復号手段での復号後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大手段と、上記拡大手段での処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換手段と、上記逆変換手段での処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて元のサイズに縮小処理する縮小手段とを備えることを特徴とする。

【0016】

第2の発明は、ブロック単位の直交変換処理及び符号化処理により得られた符号化データを復号する画像処理装置であって、上記符号化データを可変長復号する可変長復号手段と、上記可変長復号手段での復号後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大手段と、上記拡大手段での処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換手段と、上記逆変換手段での処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小手段とを備えることを特徴とする。

【0017】

第3の発明は、画像の拡大処理を行なう画像処理装置であって、対象画像データに対して直交変換処理を施す直交変換手段と、上記直交変換手段での処理後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大手段と、上記拡大手段での処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換手段と、上記逆変換手段での処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小手段とを備えることを特徴とする。

【0019】

第4の発明は、上記第1～3の何れかの発明において、上記縮小手段は、縮小処理前後の画素の面積比に基づく線形縮小処理を実行することを特徴とする。

【0020】

第5の発明は、上記第4の発明において、上記縮小手段は、ブロック境界付近の補間画素において、ブロック境界の格子点の周囲の4画素で、且つブロック境界線に隣接する画素の面積比を最も均等にする位置で、補完画素値を生成することを特徴とする。

【0021】

第6の発明は、上記第1～3の何れかの発明において、上記縮小手段は、縮小処理前後

10

20

30

40

50

の画素の位置関係に基づく線形縮小処理を実行することを特徴とする。

【0022】

第7の発明は、上記第6の発明において、上記縮小手段は、ブロック境界付近の補間画素において、ブロック境界の格子点の周囲の4画素で、且つブロック境界線に隣接する画素の中心との距離比を最も均等にする位置で、補完画素値を生成することを特徴とする。

【0023】

第8の発明は、複数の機器が互いに通信可能に接続されてなる画像処理システムであつて、上記複数の機器のうち少なくとも1つの機器は、上記の何れかに記載の画像処理装置の機能を有することを特徴とする。

【0024】

第9の発明は、ブロック単位の直交変換処理及び符号化処理により得られた符号化データを復号するための画像処理方法であつて、上記符号化データを、可変長復号する可変長復号ステップと、上記可変長復号ステップでの復号化後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大ステップと、上記拡大ステップでの処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換ステップと、上記逆変換ステップでの処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて元のサイズに縮小処理する縮小ステップとを含むことを特徴とする。

【0025】

第10の発明は、ブロック単位の直交変換処理及び符号化処理により得られた符号化データを復号するための画像処理方法であつて、上記符号化データを、可変長復号する可変長復号ステップと、上記可変長復号ステップでの復号化後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大ステップと、上記拡大ステップでの処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換ステップと、上記逆変換ステップでの処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小ステップとを含むことを特徴とする。

【0026】

第11の発明は、画像の拡大処理を行なうための画像処理方法であつて、対象画像データに対して直交変換処理を施す直交変換ステップと、上記直交変換ステップでの処理後のデータに対して、上記直交変換による係数の高周波成分に対して"0"を挿入することにより拡大処理を施す拡大ステップと、上記拡大ステップでの処理後のデータに対して、上記直交変換の逆変換処理を施す逆変換ステップと、上記逆変換ステップでの処理後のデータに対して、各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて任意のサイズに縮小処理する縮小ステップとを含むことを特徴とする。

【0027】

第12の発明は、上記の何れかに記載の画像処理装置、又は上記画像処理システムの各手段としてコンピュータを機能させるためのプログラムをコンピュータ読取可能な記憶媒体に記憶したことを特徴とする。

【0028】

第13の発明は、上記の何れかに記載の画像処理方法の各ステップをコンピュータに実行させるためのプログラムをコンピュータ読取可能な記憶媒体に記憶したことを特徴とする。

【0029】

【発明の実施の形態】

以下、本発明の実施の形態について図面を用いて説明する。

【0030】

[第1の実施の形態]

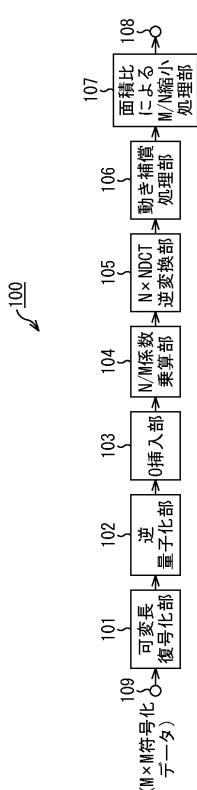

本発明は、例えば、図1に示すような画像処理装置100に適用される。

本実施の形態の画像処理装置100は、ブロック単位の直交変換を用いて符号化された画

10

20

30

40

50

像データを復号する装置であり、特に、当該画像データに対して、可変長復号化、逆量子化、周波数領域拡大、直交逆変換、及び動き補償の各処理を施した後、補間画素が各ブロックの境界上に位置するように、元のサイズに縮小する機能を有する。

【0031】

<画像処理装置100の全体構成>

画像処理装置100は、上記図1に示すように、入力端子109、可変長復号化部101、逆量子化部102、0挿入部103、N/M(M < N)係数乗算部104、DCT逆変換部105、動き補償処理部106、縮小処理部107、及び出力端子108を備えている。

【0032】

<画像処理装置100の動作：例1>

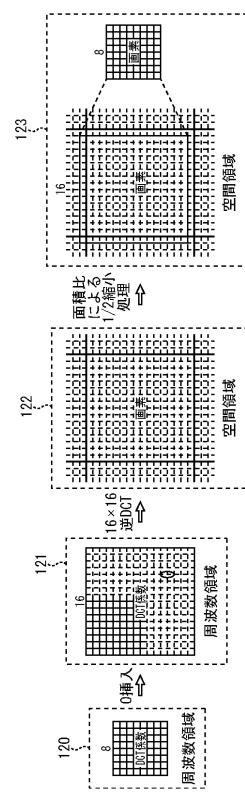

ここでは、本実施の形態では説明の簡単のため、例えば、M=8、N=16とし、ブロックサイズが8画素×8画素の入力符号化データに対して、2倍の拡大画像を経由して復号画像を出力するものとした場合、画像処理装置100の動作について説明する。

【0033】

先ず、入力端子109には、MPEG等の符号化方式により得られた、ブロックサイズがM×M画素(8画素×8画素)の符号化データが入力される。

【0034】

可変長復号化部101は、入力端子109に入力された符号化データを可変長復号化する。

逆量子化部102は、可変長復号化部101での復号化後のデータを逆量子化して、図2の“120”に示すように、ブロック毎のDCT係数を取得する。

【0035】

0挿入部103は、上記図2の“121”に示すように、逆量子化部102で得られたDCT係数において、高周波成分に対応する192個のDCT係数を“0”として、16画素×16画素のブロックを生成する。

N/M係数乗算部104は、0挿入部103で得られたブロックのDCT係数に対して、N/M=16/8=2を乗算する。

【0036】

DCT逆変換部105は、上記図2の“122”に示すように、N/M係数乗算部104で乗算処理されたブロックから、16画素×16画素のブロックサイズの空間領域データを生成する。

動き補償処理部106は、DCT逆変換部105で得られたデータに対して動き補償処理を施す。

【0037】

縮小処理部107は、面積比によるM/N(=8/16=1/2)倍線形縮小処理を行なうものであり、上記図2の“123”に示すように、動き補償処理部106での処理後のデータに対して、当該1/2倍線形縮小処理を施す。

したがって、出力端子108からは、ブロックサイズが8画素×8画素の復号化データが40出力される。

【0038】

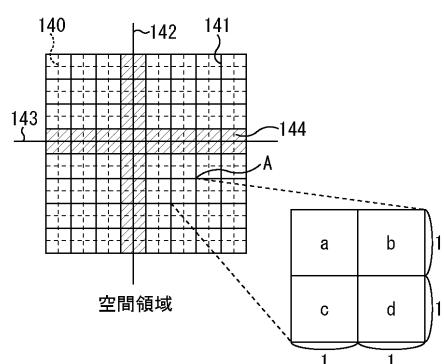

図3は、縮小処理部107での処理を具体的に示したものである。

縮小処理部107での処理では、2画素×2画素から1画素を生成する。

【0039】

上記図3において、点線の画素枠140は、縮小処理前の画素配置を示し、線細の画素枠141は、縮小処理後の画素配置を示す。また、太線142、143は、縮小処理前の16画素×16画素のブロックの境界を示す。

上記図3に示されるように、縮小処理後の画素枠は、縮小処理前の画素枠の1/2倍となり、縮小処理前の16画素×16画素の画素枠の面積と、縮小処理後の8画素×8画素の画素枠の面積とが同じになる。

10

20

30

40

50

## 【0040】

ここで、上記図3の“144”（斜線部分）で示される縮小処理後の画素枠において、16画素×16画素のブロックの境界142, 143を境に、左右又は上下の方向に同じ面積となるように、縮小処理前の16画素×16画素の画素枠と、縮小処理後の8画素×8画素の画素枠とを配置する。

## 【0041】

上述のような画素の位置関係において、縮小処理前の画素枠内に位置する画素の値及び面積に基づいて、縮小処理後の画素の値を算出する。具体的には、上記図3に示すように、縮小処理後の画素Aは、縮小処理前の画素a, b, c, dの上に位置しており、これらの面積比は、1:1:1:1であるので、縮小処理後の画素Aの値は、

10

$$(\text{画素Aの値}) = \{ (\text{画素aの値}) \times 1 + (\text{画素bの値}) \times 1 +$$

$$(\text{画素cの値}) \times 1 + (\text{画素dの値}) \times 1 \} \div 4$$

なる式により得られる。

## 【0042】

<画像処理装置100の動作：例2>

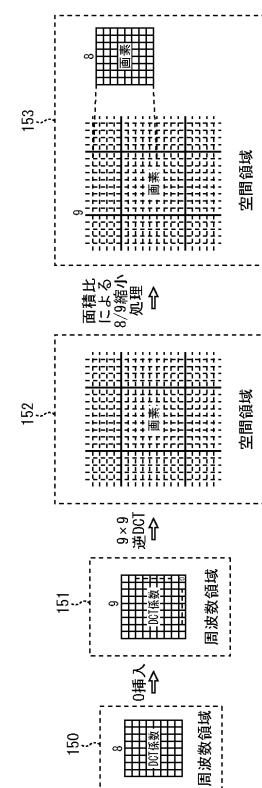

ここでは、本実施の形態では説明の簡単のため、例えば、M=8、N=9とし、ブロックサイズが8画素×8画素の入力符号化データに対して、9/8倍の拡大画像を経由して復号画像を出力するものとした場合、画像処理装置100の動作について説明する。

## 【0043】

先ず、入力端子109には、MPEG等の符号化方式により得られた、ブロックサイズがM×M画素（8画素×8画素）の符号化データが入力される。

20

## 【0044】

可変長復号化部101は、入力端子109に入力された符号化データを可変長復号化する。

逆量子化部102は、可変長復号化部101での復号化後のデータを逆量子化して、図4の“150”に示すように、ブロック毎のDCT係数を取得する。

## 【0045】

0挿入部103は、上記図4の“151”に示すように、逆量子化部102で得られたDCT係数において、高周波成分に対応する17個のDCT係数を“0”として、9画素×9画素のブロックを生成する。

30

N/M係数乗算部104は、0挿入部103で得られたブロックのDCT係数に対して、 $N/M = 9/8$ を乗算する。

## 【0046】

DCT逆変換部105は、上記図4の“152”に示すように、N/M係数乗算部104で乗算処理されたブロックから、9画素×9画素のブロックサイズの空間領域データを生成する。

動き補償処理部106は、DCT逆変換部105で得られたデータに対して動き補償処理を施す。

## 【0047】

縮小処理部107は、面積比によるM/N（=8/9）倍線形縮小処理を行なうものであり、上記図4の“153”に示すように、動き補償処理部106での処理後のデータに対して、当該8/9倍線形縮小処理を施す。

40

したがって、出力端子108からは、ブロックサイズが8画素×8画素の復号化データが

出力される。

## 【0048】

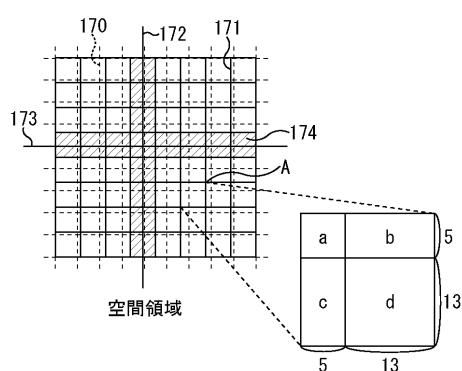

図5は、縮小処理部107での処理を具体的に示したものである。

縮小処理部107での処理では、9画素×9画素から8画素×8画素を生成する。

## 【0049】

上記図5において、点線の画素枠170は、縮小処理前の画素配置を示し、線細の画素枠171は、縮小処理後の画素配置を示す。また、太線172, 173は、縮小処理前の9

50

画素×9画素のブロックの境界を示す。

上記図5に示されるように、縮小処理後の画素枠は、縮小処理前の画素枠の8/9倍となり、縮小処理前の9画素×9画素の画素枠の面積と、縮小処理後の8画素×8画素の画素枠の面積とが同じになる。

【0050】

ここで、上記図5の“174”(斜線部分)で示される縮小処理後の画素枠において、9画素×9画素のブロックの境界172, 173を境に、左右又は上下の方向に同じ面積となるように、縮小処理前の9画素×9画素の画素枠と、縮小処理後の8画素×8画素の画素枠とを配置する。

【0051】

上述のような画素の位置関係において、縮小処理前の画素枠内に位置する画素の値及び面積に基づいて、縮小処理後の画素の値を算出する。具体的には、上記図5に示すように、縮小処理後の画素Aは、縮小処理前の画素a, b, c, dの上に位置しており、これらの面積比は、25:65:65:169であるので、縮小処理後の画素Aの値は、

(画素Aの値) = { (画素aの値) × 25 + (画素bの値) × 65 +

(画素cの値) × 65 + (画素dの値) × 169 } ÷ 324なる式により得られる。

【0052】

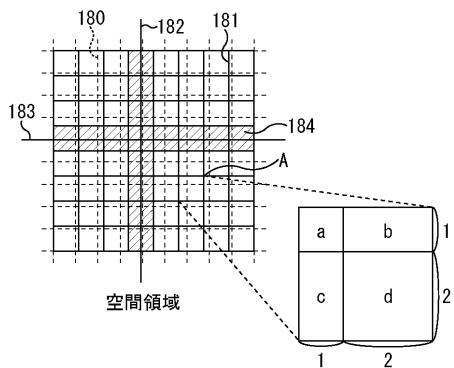

ここで、上述のような、9画素×9画素から8画素×8画素を生成する縮小処理部107での処理として、図6に示されるような処理を適用することで、画素値の算出処理量を削減することが可能となる。

【0053】

具体的には、上記図6において、点線の画素枠180は、縮小処理前の画素配置を示し、線細の画素枠181は、縮小処理後の画素配置を示す。また、太線182, 183は、縮小処理前の9画素×9画素のブロックの境界を示す。

上記図6に示されるように、縮小処理後の画素枠は、縮小処理前の画素枠の8/9倍となり、縮小処理前の9画素×9画素の画素枠の面積と、縮小処理後の8画素×8画素の画素枠の面積とが同じになる。

【0054】

ここで、上記図6の“184”(斜線部分)で示される縮小処理後の画素枠において、9画素×9画素のブロックの境界182, 183を境に、左右又は上下の方向に分けた面積が最も近い値となるように、縮小処理前の9画素×9画素の画素枠と、縮小処理後の8画素×8画素の画素枠とを重ね合わせる。さらに、縮小処理前の9画素×9画素の画素枠と、縮小処理後の8画素×8画素の画素枠とを、余す所なく重ね合わせるようにする。

【0055】

上述のような画素の位置関係において、縮小処理前の画素枠内に位置する画素の値及び面積に基づいて、縮小処理後の画素の値を算出する。具体的には、上記図6に示すように、縮小処理後の画素Aは、縮小処理前の画素a, b, c, dの上に位置しており、これらの面積比は、1:2:2:4であるので、縮小処理後の画素Aの値は、

$$(画素Aの値) = \{ (画素aの値) \times 1 + (画素bの値) \times 2 +

(画素cの値) \times 2 + (画素dの値) \times 4 \} \div 9$$

なる式により得られる。

【0056】

[第2の実施の形態]

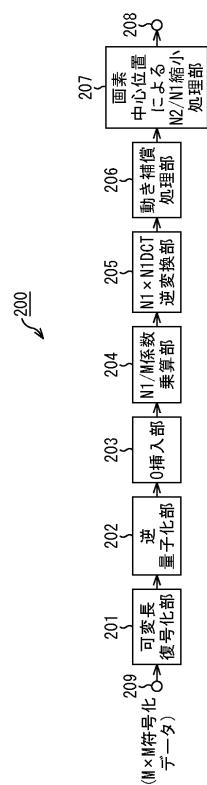

本発明は、例えば、図7に示すような画像処理装置200に適用される。

本実施の形態の画像処理装置200は、ブロック単位の直交変換を用いて符号化された画像データを復号する装置であり、特に、当該画像データに対して、可変長復号化、逆量子化、周波数領域拡大、直交逆変換、及び動き補償の各処理を施した後、補間画素が各ブロックの境界上に位置するように、目的のサイズに縮小する機能を有する。

【0057】

<画像処理装置200の全体構成>

10

20

30

40

50

画像処理装置 200 は、上記図 7 に示すように、入力端子 209、可変長復号化部 201、逆量子化部 202、0 挿入部 203、N1 / M (M < N1) 係数乗算部 204、DCT 逆変換部 205、動き補償処理部 206、縮小処理部 207、及び出力端子 208 を備えている。

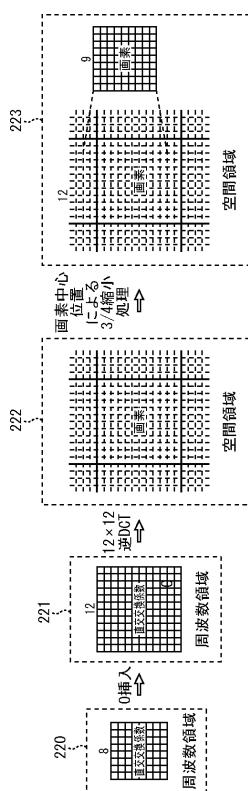

【0058】

<画像処理装置 200 の動作>

ここでは、本実施の形態では説明の簡単のため、例えば、M = 8、N1 = 12、N2 = 9 とし、ブロックサイズが 8 画素 × 8 画素の入力符号化データに対して、3 / 2 倍の拡大画像を経由して 9 / 8 倍の拡大復号画像を出力するものとした場合、画像処理装置 200 の動作について説明する。

10

【0059】

先ず、入力端子 209 には、MPEG 等の符号化方式により得られた、ブロックサイズが M × M 画素 (8 画素 × 8 画素) の符号化データが入力される。

【0060】

可変長復号化部 201 は、入力端子 209 に入力された符号化データを可変長復号化する。

逆量子化部 202 は、可変長復号化部 201 での復号化後のデータを逆量子化して、図 8 の “220” に示すように、ブロック毎の DCT 係数を取得する。

【0061】

0 挿入部 203 は、上記図 8 の “221” に示すように、逆量子化部 202 で得られた DCT 係数において、高周波成分に対応する 80 個の DCT 係数を “0” として、12 画素 × 12 画素のブロックを生成する。

20

N1 / M 係数乗算部 204 は、0 挿入部 103 で得られたブロックの DCT 係数に対して、N1 / M = 12 / 8 = 3 / 2 を乗算する。

【0062】

DCT 逆変換部 205 は、上記図 8 の “222” に示すように、N1 / M 係数乗算部 204 で乗算処理されたブロックから、12 画素 × 12 画素のブロックサイズの空間領域データを生成する。

動き補償処理部 206 は、DCT 逆変換部 205 で得られたデータに対して動き補償処理を施す。

30

【0063】

縮小処理部 207 は、面積比による M / N2 (= 9 / 12 = 3 / 4) 倍線形縮小処理を行なうものであり、上記図 8 の “223” に示すように、動き補償処理部 206 での処理後のデータに対して、当該 3 / 4 倍線形縮小処理を施す。

したがって、出力端子 208 からは、ブロックサイズが 9 画素 × 9 画素の復号化データが出力される。

【0064】

図 9 は、縮小処理部 207 での処理を具体的に示したものである。

縮小処理部 207 での処理では、4 画素 × 4 画素から 3 画素 × 3 画素を生成する。

40

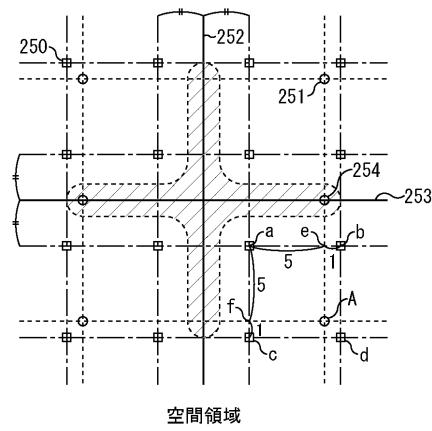

【0065】

上記図 9 において、四角群 250 は、縮小処理前の画素配置を示し、丸印群 251 は、縮小処理後の画素配置を示す。また、太線 252, 253 は、4 画素 × 4 画素のブロックの境界を示す。

【0066】

ここで、上記図 9 の “254” で示される斜線部分の画素が、4 画素 × 4 画素のブロックの境界 252, 253 を境に、左右又は上下の方向に同じ距離となるように、縮小処理前の 4 画素 × 4 画素の画素配置と、縮小処理後の 3 画素 × 3 画素の画素配置とを重ね合わせる。

【0067】

上述のような画素の位置関係において、縮小処理前の画素の近隣の 4 つの画素 (但し、縮

50

小前の画素間線分上にある時は 2 つの画素、画素上にあるときは 1 つの画素 ) の画素値と、画素中心の位置関係とに基づいて、縮小処理後の画素の値を算出する。

【 0 0 6 8 】

具体的には、上記図 9 に示すように、縮小処理後の画素 A の近隣には、縮小処理前の画素 a , b , c , d が存在する。そこで、線分 a b , a c と、画素 A から線分 a b , a c への垂線との交点をそれぞれ、 e , f とすると、線分 a e : 線分 e b = 5 : 1 、線分 a f : 線分 f c = 5 : 1 となる。この場合、縮小処理後の画素 A の値は、

( 画素 A の値 )

$$= \{ ( \text{画素 a の値} ) \times 1 / 6 + ( \text{画素 b の値} ) \times 5 / 6 \} \times 1 / 6 \\ + \{ ( \text{画素 c の値} ) \times 1 / 6 + ( \text{画素 d の値} ) \times 5 / 6 \} \times 5 / 6$$

なる式により得られる。

【 0 0 6 9 】

[ 第 3 の実施の形態 ]

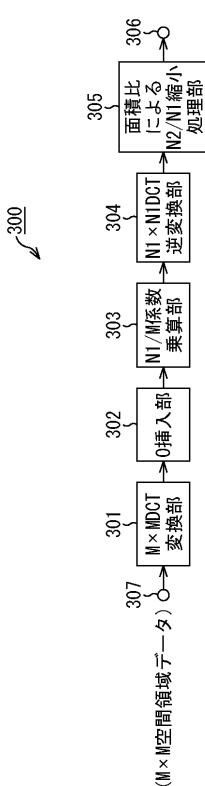

本発明は、例えば、図 10 に示すような画像処理装置 300 に適用される。

本実施の形態の画像処理装置 300 は、画像拡大する装置であり、特に、処理対象の画像データに対して、直交変換、周波数領域拡大、及び直交逆変換の各処理を施した後、補間画素が各ブロックの境界上に位置するように、目的のサイズに縮小する機能を有する。

【 0 0 7 0 】

< 画像処理装置 300 の全体構成 >

画像処理装置 300 は、上記図 10 に示すように、入力端子 307 、 D C T 変換部 301 、 0 挿入部 302 、 N1 / M ( M < N1 ) 係数乗算部 303 、 D C T 逆変換部 304 、縮小処理部 305 、及び出力端子 306 を備えている。

【 0 0 7 1 】

< 画像処理装置 300 の動作 >

ここでは、本実施の形態では説明の簡単のため、例えば、 M = 5 、 N1 = 10 、 N2 = 9 とし、ブロックサイズが 5 画素 × 5 画素の入力符号化データに対して、 10 / 5 倍の拡大画像を経由して 9 / 5 倍の拡大復号画像を出力するものとした場合、画像処理装置 300 の動作について説明する。

【 0 0 7 2 】

先ず、入力端子 307 には、図 11 の “ 320 ” に示すように、処理対象の画像データが、 M × M 画素 ( 5 画素 × 5 画素 ) のブロックに分割されて入力される。

D C T 変換部 301 は、上記図 11 の “ 321 ” に示すように、入力端子 307 に入力されたデータ ( ブロックデータ ) から、当該ブロック単位の D C T 係数を取得する。

【 0 0 7 3 】

0 挿入部 302 は、上記図 11 の “ 322 ” に示すように、 D C T 変換部 301 で得られた D C T 係数において、高周波成分に対応する 75 個の D C T 係数を “ 0 ” として、 10 画素 × 10 画素のブロックを生成する。

N1 / M 係数乗算部 303 は、 0 挿入部 302 で得られたブロックの D C T 係数に対して、 N1 / M ( = 10 / 5 = 2 ) を乗算する。

【 0 0 7 4 】

D C T 逆変換部 304 は、上記図 11 の “ 323 ” に示すように、 N1 / M 係数乗算部 303 で乗算処理されたブロックから、 10 画素 × 10 画素のブロックサイズの空間領域データを生成する。

【 0 0 7 5 】

縮小処理部 305 は、面積比による N2 / N1 ( = 9 / 10 ) 倍線形縮小処理を行なうものであり、上記図 11 の “ 324 ” に示すように、 D C T 逆変換部 304 で得られたデータに対して、当該 9 / 10 倍線形縮小処理を施す。

したがって、出力端子 306 からは、ブロックサイズが 9 画素 × 9 画素の空間領域データが出力される。

【 0 0 7 6 】

10

20

30

40

50

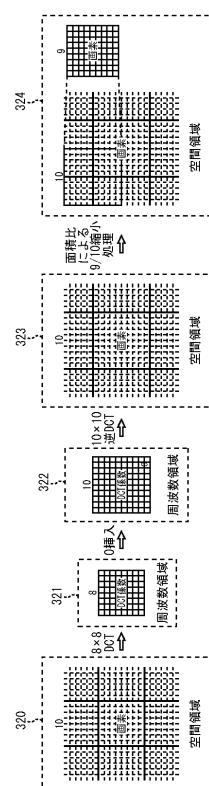

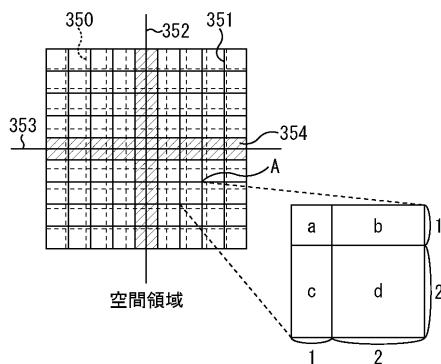

図12は、縮小処理部305での処理を具体的に示したものである。

縮小処理部305での処理では、10画素×10画素から9画素×9画素を生成する。

【0077】

上記図12において、点線の画素枠350は、縮小処理前の画素配置を示し、線細の画素枠351は、縮小処理後の画素配置を示す。また、太線352, 353は、縮小処理前の10画素×10画素のブロックの境界を示す。

上記図12に示されるように、縮小処理後の画素枠は、縮小処理前の画素枠の9/10倍となり、縮小処理前の10画素×9画素の画素枠の面積と、縮小処理後の9画素×9画素の画素枠の面積とが同じになる。

【0078】

ここで、上記図12の“354”(斜線部分)で示される縮小処理後の画素枠において、10画素×10画素のブロックの境界352, 353を境に、左右又は上下の方向に同じ面積となるように、縮小処理前の10画素×10画素の画素枠と、縮小処理後の9画素×9画素の画素枠とを重ね合わせる。

【0079】

上述のような画素の位置関係において、縮小処理前の画素枠内に位置する画素の値及び面積に基づいて、縮小処理後の画素の値を算出する。具体的には、上記図12に示すように、縮小処理後の画素Aは、縮小処理前の画素a, b, c, dの上に位置しており、これらの面積比は、1:2:2:4であるので、縮小処理後の画素Aの値は、

$$(画素Aの値) = \{ (画素aの値) \times 1 + (画素bの値) \times 2 +$$

$$(画素cの値) \times 2 + (画素dの値) \times 4 \} \div 9$$

なる式により得られる。

【0080】

尚、本発明の目的は、第1～第3の実施の形態のホスト及び端末の機能を実現するソフトウェアのプログラムコードを記憶した記憶媒体を、システム或いは装置に供給し、そのシステム或いは装置のコンピュータ(又はCPUやMPU)が記憶媒体に格納されたプログラムコードを読みだして実行することによっても、達成されることは言うまでもない。

この場合、記憶媒体から読み出されたプログラムコード自体が第1～第3の実施の形態の機能を実現することとなり、そのプログラムコードを記憶した記憶媒体は本発明を構成することとなる。

プログラムコードを供給するための記憶媒体としては、ROM、フロッピーディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、磁気テープ、不揮発性のメモリカード等を用いることができる。

また、コンピュータが読みだしたプログラムコードを実行することにより、第1～第3の実施の形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼動しているOS等が実際の処理の一部又は全部を行い、その処理によって第1～第3の実施の形態の機能が実現される場合も含まれることは言うまでもない。

さらに、記憶媒体から読み出されたプログラムコードが、コンピュータに挿入された拡張機能ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書き込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部又は全部を行い、その処理によって第1～第3の実施の形態の機能が実現される場合も含まれることは言うまでもない。

【0081】

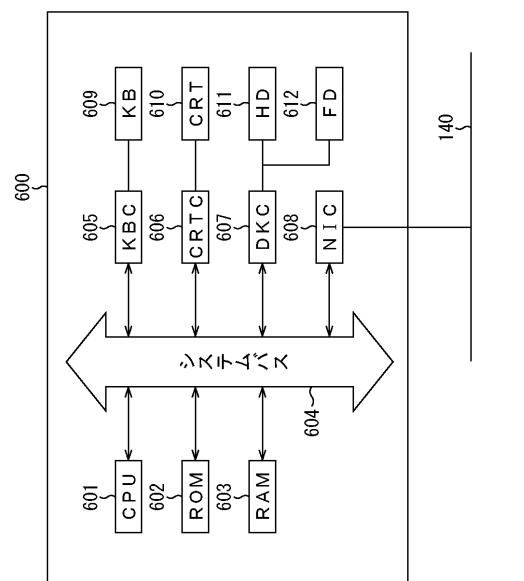

図13は、上記コンピュータ600の構成の一例を示したものである。

コンピュータ600は、上記図13に示すように、CPU601と、ROM602と、RAM603と、キーボード(KB)609のキーボードコントローラ(KBC)605と、表示部としてのCRTディスプレイ(CRT)610のCRTコントローラ(CRTC)606と、ハードディスク(HD)611及びフロッピーディスク(FD)612のディスクコントローラ(DKC)607と、ネットワークインターフェースカード(NIC)608とが、システムバス604を介して互いに通信可能に接続された構成としている

10

20

30

40

50

。

### 【0082】

CPU601は、ROM602或いはHD611に記憶されたソフトウェア、或いはFD612より供給されるソフトウェアを実行することで、システムバス604に接続された各構成部を総括的に制御する。

すなわち、CPU601は、所定の処理シーケンスに従った処理プログラムを、ROM602、或いはHD611、或いはFD612から読み出して実行することで、第1～第3の実施の形態での動作を実現するための制御を行う。

### 【0083】

RAM603は、CPU601の主メモリ或いはワークエリア等として機能する。 10

KBC605は、KB609や図示していないポインティングデバイス等からの指示入力を制御する。

CRTC606は、CRT610の表示を制御する。

DKC607は、ブートプログラム、種々のアプリケーション、編集ファイル、ユーザファイル、ネットワーク管理プログラム、及び第1～第3の実施の形態における上記処理プログラム等を記憶するHD611及びFD612とのアクセスを制御する。

NIC608は、ネットワーク140上の装置或はシステムと双方向にデータをやりとりする。

### 【0084】

#### 【発明の効果】

20

以上説明したように本発明では、MPEG等により得られた符号化データを復号する際、可変長復号化処理及び逆量子化処理等を施した後のデータに対して、拡大処理（周波数領域で元の或は目的とするサイズより大きいブロックサイズへの拡大処理等）を施し、その後、逆変換処理を施して、空間領域で各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて元のサイズ或は目的のサイズに縮小処理するように構成した。

これにより、従来のようにブロック境界の高周波成分を低下させることなく、且つ画像全体を歪ませることなく、ブロック歪みを低減した良好な画質の復号画像を提供することができる。

### 【0085】

また、本発明では、画像データを拡大する際、直交変換後の処理対象画像データに対して、拡大処理（周波数領域で目的とするサイズより大きいブロックサイズへの拡大処理等）を施し、その後、逆変換処理を施して、空間領域で各ブロックの境界線上に一列の補間画素が位置するように全画素を用いて目的のサイズに縮小処理するように構成した。 30

これにより、いかなる有理数倍の画像拡大であっても、従来のようにブロック境界の高周波成分を低下させることなく、且つ画像全体を歪ませることなく、ブロック歪みを低減した良好な画質の拡大画像を提供することができる。

#### 【図面の簡単な説明】

【図1】第1の実施の形態において、本発明を適用した画像処理装置の構成を示すプロック図である。

【図2】上記画像処理装置の動作（例1）を説明するための図である。 40

【図3】上記画像処理装置の動作（例1）において、縮小処理部の動作を説明するための図である。

【図4】上記画像処理装置の動作（例2）を説明するための図である。

【図5】上記画像処理装置の動作（例2）において、縮小処理部の動作（例1）を説明するための図である。

【図6】上記縮小処理部の動作（例2）を説明するための図である。

【図7】第2の実施の形態において、本発明を適用した画像処理装置の構成を示すプロック図である。

【図8】上記画像処理装置の動作を説明するための図である。

【図9】上記画像処理装置の動作において、縮小処理部の動作を説明するための図である

50

。

【図10】第3の実施の形態において、本発明を適用した画像処理装置の構成を示すブロック図である。

【図11】上記画像処理装置の動作を説明するための図である。

【図12】上記画像処理装置の動作において、縮小処理部の動作を説明するための図である。

【図13】第1～第3の実施の形態を、記憶媒体から読み出したプログラムを実行することで実現するためのコンピュータの構成の一例を説明するための図である。

【図14】従来の画像処理装置の構成(例1)を示すブロック図である。

【図15】上記画像処理装置の動作を説明するための図である。

【図16】従来の画像処理装置の構成(例2)を示すブロック図である。

【図17】上記画像処理装置の動作を説明するための図である。

【符号の説明】

- |     |                |

|-----|----------------|

| 100 | 画像処理装置         |

| 101 | 可変長復号化部        |

| 102 | 逆量子化部          |

| 103 | 0挿入部           |

| 104 | N/M係数乗算部       |

| 105 | N×NDCT逆変換部     |

| 106 | 動き補償処理部        |

| 107 | 面積比によるM/N縮小処理部 |

| 108 |                |

| 109 | 入力端子           |

| 100 | 出力端子           |

【図1】

【図2】

10

20

【図3】

【図4】

【図5】

【図7】

【図6】

【 8 】

【 四 9 】

【図10】

【 図 1 1 】

【図12】

【図13】

【図14】

【 図 15 】

【図16】

【図17】

---

フロントページの続き

(58)調査した分野(Int.Cl. , DB名)

G06T 3/40

H03M 7/30- 7/50

H04N 1/38- 1/393

H04N 1/41- 1/419

H04N 7/12

H04N 7/26- 7/32