(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4386978号

(P4386978)

(45) 発行日 平成21年12月16日(2009.12.16)

(24) 登録日 平成21年10月9日(2009.10.9)

(51) Int.Cl.

F 1

H01L 21/336 (2006.01)

H01L 29/78 (2006.01)

617S

H01L 29/786 (2006.01)

H01L 29/78

616A

H01L 29/78

617J

H01L 29/78

627G

請求項の数 10 (全 15 頁)

(21) 出願番号

特願平10-223883

(22) 出願日

平成10年8月7日(1998.8.7)

(65) 公開番号

特開2000-58841 (P2000-58841A)

(43) 公開日

平成12年2月25日(2000.2.25)

審査請求日

平成17年7月13日(2005.7.13)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 山崎 舜平

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 中嶋 節男

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 河崎 律子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 河本 充雄

最終頁に続く

(54) 【発明の名称】 半導体装置の作製方法

(57) 【特許請求の範囲】

【請求項 1】

基板上にゲート配線を形成し、

前記ゲート配線上に、ゲート絶縁膜、第1の半導体膜及び第1の保護膜を順次大気開放しないで積層形成し、

前記第1の保護膜上から、前記第1の半導体膜に対して紫外光又は赤外光を照射して、結晶を含む第2の半導体膜を形成し、

前記第1の保護膜をパターニングして第2の保護膜を形成し、前記第2の保護膜をマスクとして前記第2の半導体膜に一对の不純物領域を形成し、

前記第2の半導体膜を島状にパターニングして前記一对の不純物領域を含む活性層を形成することを特徴とする半導体装置の作製方法。 10

【請求項 2】

基板上にゲート配線を形成し、

前記ゲート配線上に、ゲート絶縁膜、第1の半導体膜及び第1の保護膜を順次大気開放しないで積層形成し、

前記第1の保護膜上から、前記第1の半導体膜に対して紫外光又は赤外光を照射して、結晶を含む第2の半導体膜を形成し、

前記第1の保護膜をパターニングして第2の保護膜を形成し、前記第2の保護膜をマスクとして前記第2の半導体膜に一对の第1の不純物領域を形成し、

前記第2の保護膜をパターニングして第3の保護膜を形成し、前記第3の保護膜をマス

10

20

クとして前記第2の半導体膜に前記第1の不純物領域より低不純物濃度かつ同一導電型の一対の第2の不純物領域を形成し、

前記第2の半導体膜を島状にパターニングして前記一対の第1の不純物領域と前記一対の第2の不純物領域を含む活性層を形成することを特徴とする半導体装置の作製方法。

【請求項3】

基板上にゲート配線を形成し、

前記ゲート配線上に、ゲート絶縁膜、第1の半導体膜及び第1の保護膜を順次大気開放しないで積層形成し、

前記第1の保護膜上から、前記第1の半導体膜に対して紫外光又は赤外光を照射して、結晶を含む第2の半導体膜を形成し、

10

前記第1の保護膜をパターニングして第2の保護膜を形成し、前記第2の保護膜をマスクとして前記第2の半導体膜に一対の不純物領域を形成し、

前記第2の保護膜上にレジストマスクを形成し、

前記レジストマスクを用いて、前記第2の半導体膜を島状にパターニングして前記一対の不純物領域を含む活性層を形成し、

前記レジストマスクを用いて、前記ゲート絶縁膜をエッチングして、前記活性層が設けられている領域以外の領域の前記ゲート配線を露呈させ、

露呈させた前記ゲート配線上に層間絶縁膜を形成し、

前記層間絶縁膜のコンタクトホールを介して、前記ゲート配線に接続された配線を形成することを特徴とする半導体装置の作製方法。

20

【請求項4】

基板上にゲート配線を形成し、

前記ゲート配線上に、ゲート絶縁膜、第1の半導体膜及び第1の保護膜を順次大気開放しないで積層形成し、

前記第1の保護膜上から、前記第1の半導体膜に対して紫外光又は赤外光を照射して、結晶を含む第2の半導体膜を形成し、

前記第1の保護膜をパターニングして第2の保護膜を形成し、前記第2の保護膜をマスクとして前記第2の半導体膜に一対の第1の不純物領域を形成し、

前記第2の保護膜をパターニングして第3の保護膜を形成し、前記第3の保護膜をマスクとして前記第2の半導体膜に前記第1の不純物領域より低不純物濃度かつ同一導電型の一対の第2の不純物領域を形成し、

30

前記第3の保護膜上にレジストマスクを形成し、

前記レジストマスクを用いて、前記第2の半導体膜を島状にパターニングして前記一対の第1の不純物領域と前記一対の第2の不純物領域を含む活性層を形成し、

前記レジストマスクを用いて、前記ゲート絶縁膜をエッチングして、前記活性層が設けられている領域以外の領域の前記ゲート配線を露呈させ、

露呈させた前記ゲート配線上に層間絶縁膜を形成し、

前記層間絶縁膜のコンタクトホールを介して、前記ゲート配線に接続された配線を形成することを特徴とする半導体装置の作製方法。

【請求項5】

40

請求項1または請求項2において、

前記ゲート配線上に前記ゲート絶縁膜を形成する前に、前記ゲート配線を酸化して、前記ゲート配線の表面にゲート酸化膜を形成することを特徴とする半導体装置の作製方法。

【請求項6】

請求項3または請求項4において、

前記ゲート配線上に前記ゲート絶縁膜を形成する前に、前記ゲート配線を酸化して、前記ゲート配線の表面にゲート酸化膜を形成し、

前記レジストマスクを用いて前記ゲート絶縁膜をエッチングする際に、前記レジストマスクを用いて前記ゲート酸化膜をエッチングして、前記活性層が設けられている領域以外の領域の前記ゲート配線を露呈させることを特徴とする半導体装置の作製方法。

50

**【請求項 7】**

請求項 5 または請求項 6 において、

前記ゲート酸化膜は、プラズマ酸化法により形成されることを特徴とする半導体装置の作製方法。

**【請求項 8】**

請求項 1 乃至請求項 7 のいずれか一項において、

前記ゲート配線として、タンタル膜又はタンタル膜と窒化タンタル膜を含む積層膜を形成することを特徴とする半導体装置の作製方法。

**【請求項 9】**

請求項 1 乃至請求項 8 のいずれか一項において、

10

前記ゲート絶縁膜として、窒化シリコン膜を含む積層膜を形成することを特徴とする半導体装置の作製方法。

**【請求項 10】**

請求項 1 乃至請求項 9 のいずれか一項において、

前記ゲート絶縁膜として、BCB (ベンゾシクロブテン) を含む積層膜を形成することを特徴とする半導体装置の作製方法。

**【発明の詳細な説明】****【0001】****【発明が属する技術分野】**

本願発明は半導体薄膜を用いた薄膜トランジスタ (以下、TFTと呼ぶ) を構成に含む半導体装置及びその作製方法に関する。なお、本明細書中において半導体装置とは半導体特性を利用することで機能しうる装置全般を指し、本明細書中における半導体回路、電気光学装置および電子機器は全て半導体装置である。

20

**【0002】****【従来の技術】**

近年、ポリシリコン膜を利用したTFTで回路を組んだアクティブマトリクス型液晶表示装置が注目されている。これはマトリクス状に配置された複数の画素によって液晶にかかる電界をマトリクス状に制御し、高精細な画像表示を実現するものである。

**【0003】**

アクティブマトリクス型液晶表示装置では、各画素毎に形成された画素TFTで液晶に印加される電圧を制御して画像表示を行っている。現在では画素だけでも100万個以上の画素を有するため、膨大な数の画素TFTの特性ばらつきを抑えつつ歩留まり良く形成しなくてはならない。

30

**【0004】**

TFT特性を最も左右するパラメータの一つとして活性層とゲート絶縁膜の界面が挙げられる。この界面が汚染されていると、忽ちTFT特性に悪影響を与える。従って、活性層と他の絶縁膜とが接する界面の清浄化が、良好なTFT特性を得るために必要である。

**【0005】****【発明が解決しようとする課題】**

本願発明は活性層と絶縁膜との界面を清浄化するために必要な技術を開示するものであり、その様な技術を用いて良好な電気特性を示すTFTを形成することを課題とする。そして、その様なTFTを用いた半導体回路、電気光学装置及び電子機器等の半導体装置を提供することを課題とする。

40

**【0006】****【課題を解決するための手段】**

本明細書で開示する発明の構成は、

ゲート配線が形成された基板上にゲート絶縁膜、半導体膜及び保護膜を順次大気開放しないで積層形成する工程と、

前記半導体膜に対して紫外光又は赤外光を照射して結晶を含む半導体膜を形成する工程と、

50

前記保護膜をマスクとして前記結晶を含む半導体膜に不純物領域を形成する工程と、前記結晶を含む半導体膜を島状にパターニングして活性層を形成する工程と、を含むことを特徴とする。

【0007】

また、他の発明の構成は、

ゲート配線が形成された基板上にゲート絶縁膜、半導体膜及び保護膜を順次大気開放しないで積層形成する工程と、

前記半導体膜に対して紫外光又は赤外光を照射して結晶を含む半導体膜を形成する工程と、

前記保護膜をマスクとして前記結晶を含む半導体膜に不純物領域を形成する工程と、

前記結晶を含む半導体膜を島状にパターニングして活性層を形成する工程と、

前記活性層をマスクとして前記ゲート絶縁膜をエッチングする工程と、

を含むことを特徴とする。

【0008】

また、他の発明の構成は、

基板上にゲート配線を形成する工程と、

前記ゲート配線を酸化して当該ゲート配線の表面にゲート酸化膜を形成する工程と、

前記ゲート配線が形成された基板上にゲート絶縁膜、半導体膜及び保護膜を順次大気開放しないで積層形成する工程と、

前記半導体膜に対して紫外光又は赤外光を照射して結晶を含む半導体膜を形成する工程と、

前記保護膜をマスクとして前記結晶を含む半導体膜に不純物領域を形成する工程と、

前記結晶を含む半導体膜を島状にパターニングして活性層を形成する工程と、

を含むことを特徴とする。

【0009】

また、他の発明の構成は、

基板上にゲート配線を形成する工程と、

前記ゲート配線を酸化して当該ゲート配線の表面にゲート酸化膜を形成する工程と、

前記ゲート配線が形成された基板上にゲート絶縁膜、半導体膜及び保護膜を順次大気開放しないで形成する工程と、

前記半導体膜に対して紫外光又は赤外光を照射して結晶を含む半導体膜を形成する工程と、

前記保護膜をマスクとして前記結晶を含む半導体膜に不純物領域を形成する工程と、

前記結晶を含む半導体膜を島状にパターニングして活性層を形成する工程と、

前記活性層をマスクとして前記ゲート絶縁膜及び前記ゲート酸化膜を順次エッチングする工程と、

を含むことを特徴とする。

【0010】

なお、本明細書中において「結晶を含む半導体膜」とは、単結晶半導体膜、結晶粒界を含む結晶半導体膜（多結晶半導体膜及び微結晶半導体膜を含む）を指し、全域に渡って非晶質状態である半導体膜（非晶質半導体膜）との区別を明確にしている。勿論、「半導体膜」と記載されていれば、結晶を含む半導体膜以外に非晶質半導体膜も含まれることは言うまでもない。

【0011】

また、上記構成において、前記ゲート配線はタンタル膜単体で形成しても良いし、タンタル膜と窒化タンタル膜との積層膜で形成しても良い。勿論、これらの膜に他の導電膜やシリコン膜などを積層しても良い。

【0012】

また、上記構成において、前記ゲート絶縁膜として窒化シリコン膜をいずれかの層に含む積層膜（例えば酸化シリコン膜と窒化シリコン膜との積層膜）を用いることは有効である

10

20

30

40

50

。この構成では窒化シリコン膜によって基板からの汚染物質の拡散を防止する効果がある。

#### 【0013】

また、前記ゲート絶縁膜として、BCB（ベンゾシクロブテン）をいずれかの層に含む積層膜を用いることは有効である。BCBは非常に平坦性が高いため、ゲート配線による段差をなくして、BCB膜の上方に形成される全ての薄膜の平坦性を高めることができる。

#### 【0014】

また、上記構成において、前記ゲート酸化膜はプラズマ酸化法、熱酸化法、陽極酸化法のいずれかの手段により形成することができる。特に、プラズマ酸化法は工程が簡易であるのでスループットの向上という面で有効である。

10

#### 【0015】

本願発明の要旨は、ボトムゲート構造（代表的には逆スタガ構造）のTFTを形成するにあたって、活性層となる半導体膜の少なくともチャネル形成領域を一度たりとも大気開放させない点にある。この様な構成により活性層界面の汚染を防ぎ、安定且つ良好な電気特性を示すTFTを実現する。

#### 【0016】

##### 【発明の実施の形態】

本願発明の実施形態について以下に示す実施例でもって詳細な説明を行うこととする。

#### 【0017】

##### 【実施例】

20

##### 【実施例1】

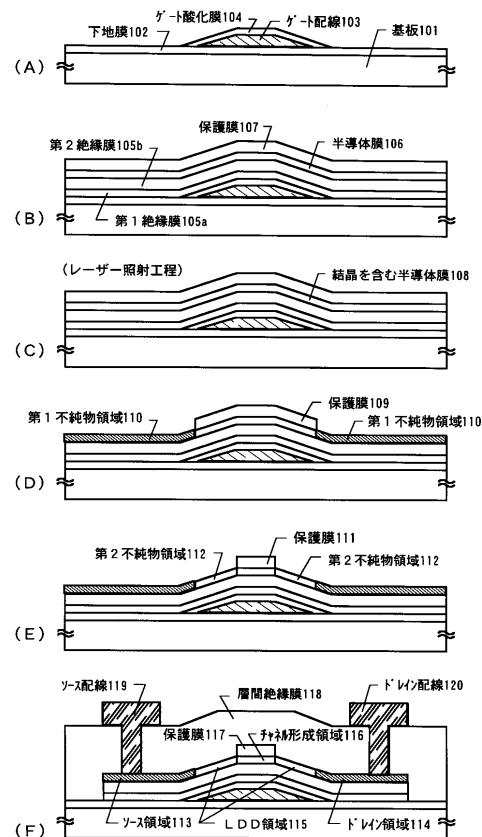

本実施例では本願発明を用いて逆スタガ型TFTを作製する場合の例について説明する。なお、本実施例では一つのTFTに注目して説明を行うが同一基板上に複数個を同時形成することもできることは言うまでもない。また、説明には図1～図3を用いる。

#### 【0018】

まず、TFT形成部の断面を図1に示す。まず、基板101としてガラス基板を用意する。ガラス以外にも石英基板、セラミックス基板、ステンレス基板、金属（タンタル、タンゲステン、モリブデンなど）基板、半導体基板、プラスチック基板（ポリエチレンテレフタレート基板など）を用いることもできる。

#### 【0019】

30

その上に下地膜102として絶縁膜を形成する。本実施例では窒化シリコン膜を用いてガラス基板101からの汚染物質の拡散を防止する。さらに、基板101と下地膜102との間に金属膜や窒化アルミニウム膜等の放熱層を設ける構成とすることも有効である。

#### 【0020】

次に、窒化タンタル膜でタンタル膜を挟んだ積層構造を有するゲート配線103を形成する。タンタル膜と窒化タンタル膜との積層構造でも良い。また、他の導電性材料を用いることも可能である。

#### 【0021】

次に、ゲート配線103を酸化して表面にゲート酸化膜104を形成する。ゲート酸化膜104の形成方法としては、プラズマ酸化法、陽極酸化法又は熱酸化法のいずれかの手段を用いれば良い。ただしスループットを考慮するとプラズマ酸化法が好ましいと言える。

40

#### 【0022】

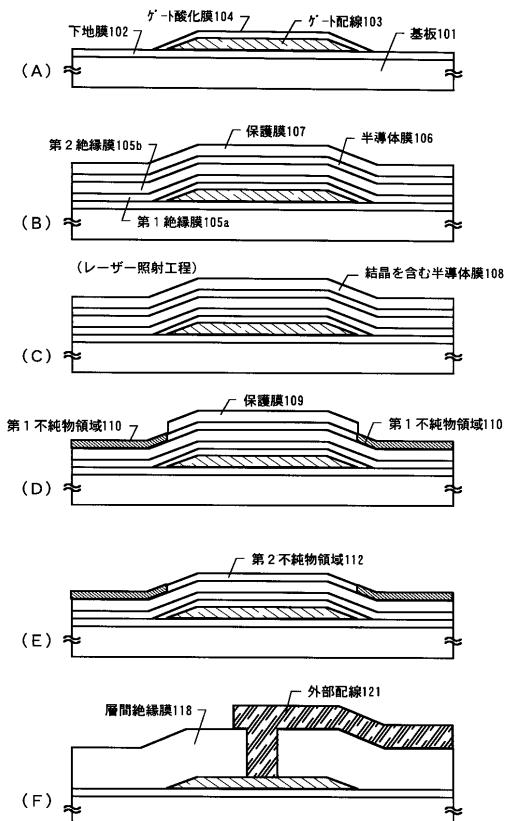

こうして図1(A)の状態が得られる。この時、ゲート配線103は基板上を縦横に走り、最終的にはゲートコンタクト部に到達する。ゲートコンタクト部とは、ゲート配線と外部配線とを接続するためのコンタクト部であり、同一基板上に形成される。このゲートコンタクト部の断面を図2に示す。

#### 【0023】

図2(A)は図1(A)の状態が得られたのと同時期のゲートコンタクト部の断面構造である。従って、図2(A)で用いられている符号が図1(A)で用いられている符号と同じ箇所を示す。

50

**【 0 0 2 4 】**

こうして図1(A)の状態が得られたら、第1絶縁膜105a、第2絶縁膜105b、半導体膜106、保護膜107を順次大気開放しないで積層形成する。この時、成膜手段としてはプラズマCVD法、スパッタ法のいずれの手段を用いても良いが、完全に高真空環境下におき、大気に触れさせない様にすることでいずれの層の界面にも大気からの汚染物質が付着しない様にすることができます。その結果、非常に清浄化された界面を実現することができる。

**【 0 0 2 5 】**

なお、本実施例では第1絶縁膜105aとして50nm厚の窒化シリコン膜、第2絶縁膜105bとして150nm厚の酸化シリコン膜、半導体膜106として50nm厚の非晶質シリコン膜、保護膜107として100nm厚の酸化シリコン膜を用いる。それぞれの膜厚は本実施例に限定される必要はなく、実施者が適宜決定すれば良い。

10

**【 0 0 2 6 】**

また、本実施例では第1絶縁膜105aと第2絶縁膜105bとの積層膜をゲート絶縁膜として採用しているが、第1絶縁膜又は第2絶縁膜を省いて単層としても構わないし、三層以上の積層構造としても良い。

**【 0 0 2 7 】**

また、本実施例では半導体膜106として非晶質シリコン膜を用いているが、微結晶シリコン膜を用いても良いし、この時点で結晶を含む半導体膜（多結晶シリコン膜など）を形成しても良い。さらに、本実施例ではシリコンを例示しているが化合物半導体（代表的にはシリコンゲルマニウム）などの半導体であっても良い。

20

**【 0 0 2 8 】**

こうして図1(B)の状態が得られる。この時、ゲートコンタクト部は図2(B)に示す様な構造となっている。用いられている符号は図1(B)で用いられている符号と同一である。

**【 0 0 2 9 】**

こうして図1(B)の状態が得られたら、半導体膜106に対して紫外光又は赤外光の照射を行う。本実施例ではエキシマレーザー光を照射する。本実施例ではエキシマレーザー光を線状にビーム形成して照射する。照射条件はパルス周波数が30Hz、レーザーエネルギー密度が100～500mJ/cm<sup>2</sup>であり、本実施例では350mJ/cm<sup>2</sup>とする。

30

**【 0 0 3 0 】**

この工程により半導体膜106は結晶化され、結晶を含む半導体膜108に変化する。本実施例において結晶を含む半導体膜とは具体的には多結晶シリコン膜である。この時、レーザー光の照射は保護膜107上から行われるので半導体膜106中に処理雰囲気から汚染物質が混入する恐れがない。即ち、半導体膜106の界面の清浄性を保ったまま、半導体膜106の結晶化を行うことができる。

**【 0 0 3 1 】**

なお、本実施例ではレーザー照射前の段階（成膜段階）で非晶質シリコン膜であったので結晶化という文言を用いたが、成膜段階で多結晶シリコン膜や微結晶シリコン膜であった場合には不適切である。その場合には、結晶性の改善化といった方が適切であろう。即ち、レーザー照射を行うことにより、より高い結晶性を有する半導体膜に変化すると言える。

40

**【 0 0 3 2 】**

こうして図1(C)の状態が得られる。この時、ゲートコンタクト部は図2(C)に示す様な構造となっている。用いられている符号は図1(C)で用いられている符号と同一である。

**【 0 0 3 3 】**

こうして図1(C)の状態が得られたら、次に保護膜107をパターニングして保護膜109を形成する。この時、パターニングには裏面露光法を用い、ゲート配線103を用いて自己整合的に保護膜109を形成する。

50

## 【0034】

保護膜109を形成したら、N型を付与する不純物イオンとしてリンイオンをプラズマドーピング法、イオンインプランテーション法又は気相拡散法により添加して第1不純物領域110を形成する。この時、保護膜109によって結晶を含む半導体膜108の一部が保護される。

## 【0035】

なお、本実施例ではNチャネル型TFTの場合を例示しているが、Pチャネル型TFTにするならばこの工程でP型を付与する不純物イオンとしてボロンイオ

## 【0036】

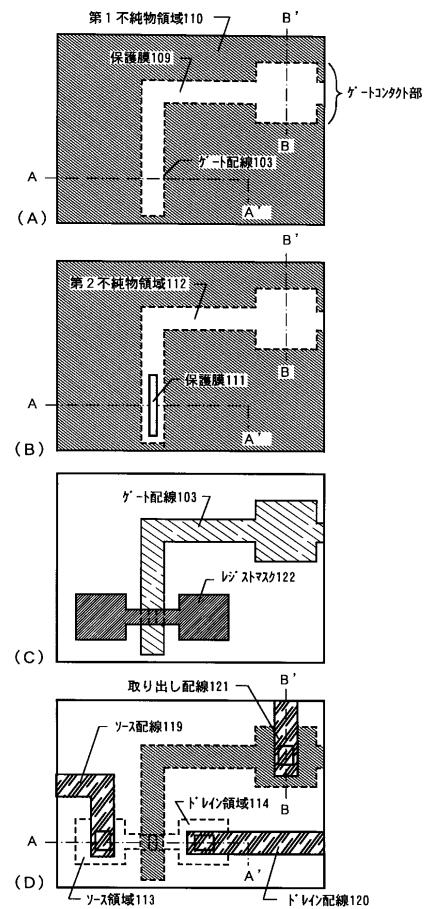

こうして図1(D)の状態が得られる。この時、ゲートコンタクト部は図2(D)に示す様な構造となっている。使われている符号は図1(D)と同一である。また、この時、図1(D)及び図2(D)を上面から見た図を図3(A)に示す。なお、図3(A)においてA-A'で切った断面に相当するのが図1(D)であり、B-B'で切った断面に相当するのが図2(D)である。また、図3(A)に用いられている符号は図1(D)及び図2(D)に用いられている符号と同一である。

## 【0037】

こうして図1(D)の状態が得られたら、再度保護膜109をパターニングして保護膜111を形成する。この時はマスク合わせを行う必要がある。そして再びリンイオンを、前回よりも低濃度に添加する。こうして第2不純物領域112が形成される。この時も保護膜111によって結晶を含む半導体膜108の一部が保護される。なお、第1不純物領域110にもリンイオンは添加されるが、2~3桁も少ない量が添加されるだけなので実質的に変化はないと考えて良い。

## 【0038】

この2回の不純物添加工程によって後にソース領域及びドレイン領域となる領域(第1不純物領域110の一部)と、後にLDD領域(第2不純物領域111の一部)が形成される。不純物領域を形成した後で、ファーネスアニール又はレーザーアニール等の手段により不純物イオンの活性化を行っておく。

## 【0039】

こうして図1(E)の状態が得られる。この時、ゲートコンタクト部の断面は図2(E)に示す状態、上面図は図3(B)に示す状態である。保護膜111は少なくともチャネル形成領域となる部分を覆う様に残してあれば良い。

## 【0040】

こうして図1(E)の状態が得られたら、結晶を含む半導体膜108をパターニングして活性層を形成する。本実施例の場合、活性層はソース領域113、ドレイン領域114、LDD領域115及びチャネル形成領域116から成り立つ。チャネル形成領域116の界面(保護膜117又は第2絶縁膜105bと接する界面)はここまで一度たりとも大気に触れておらず、非常に清浄である。

## 【0041】

次に、活性層をパターニングする際に用いたレジストマスクをそのままマスクとして第2絶縁膜105b、第1絶縁膜105a及びゲート酸化膜104を順次エッティングする。この工程が終了した時点の状態を図3(C)に示す(図1及び図2には示さない)。この状態ではレジストマスク122で覆われた部分(活性層に相当する)以外の領域においてゲート配線103が露呈する。

## 【0042】

次に、層間絶縁膜118として50nm厚の窒化シリコン膜と900nm厚の酸化シリコン膜とでなる積層膜を形成する。勿論、他の絶縁膜として樹脂材料(ポリイミドやアクリルなど)を用いても構わない。

## 【0043】

層間絶縁膜118を形成したら、コンタクトホールを形成して導電膜を形成し、導電膜をパターニングしてソース配線119、ドレイン配線120を形成する。この際、ゲートコ

10

20

30

40

50

ンタクト部ではゲート配線の表面に自然酸化膜が形成されていることがあるので、前処理によって除去しておくことが望ましい。（図1（F））

【0044】

またこの時、ゲートコンタクト部ではゲート配線103に接続する様に外部配線121が、ソース配線119やドレイン配線120と同一の材料で形成される。（図2（F））

【0045】

そして、この時の上面図は図3（D）に示される様になる。勿論、A-A'で切った断面に相当するのが図1（F）であり、B-B'で切った断面に相当するのが図2（F）である。

【0046】

この後、300～2時間の水素化処理を行い、図1（F）に示す様な断面構造を有するTFTが完成する。勿論、本実施例のTFT構造は本願発明のTFT構造を限定するものではない。

10

【0047】

本実施例の第1の特徴は、半導体膜106と接する絶縁膜を全て大気開放しないまま連続的に積層形成する点にある。こうすることで活性層界面の清浄化が保たれ、良好な電気特性を示すTFTが実現される。

【0048】

また、第2の特徴としてゲート配線103をゲート酸化膜104で覆うことにより結晶を含む半導体膜108の結晶粒径を均一なものにすることができる。実際、ゲート酸化膜を設けない場合には、ゲート配線と重なる部分の粒径だけ極端に小さくなってしまうことが確認されているが、ゲート酸化膜104を設けることでその様な現象を防ぐことができる。

20

【0049】

さらに、第3の特徴としてレジストマスク122をマスクとして第2絶縁膜105b、第1絶縁膜105a、ゲート酸化膜104をエッチングすることは、ゲート配線103と外部配線121との良好なオーミックコンタクトを確保する上で有効である。

【0050】

ゲートコンタクト部においてゲート配線103上にゲート酸化膜、第1絶縁膜及び第2絶縁膜が存在すると、ソース領域、ドレイン領域及びゲート配線の上に同時にコンタクトホールを形成することが困難になるからである。ところが、上記工程を行っておくことで、層間絶縁膜118をエッチングするだけで、ソース領域、ドレイン領域及びゲート配線を露呈させることができる。

30

【0051】

また、本実施例の様にゲート配線103としてタンタル系材料を用いた場合、ゲート酸化膜はタンタルオキサイドであり、非常にエッチングが困難であるという問題を生じる。さらに、タンタルオキサイドをエッチングしている最中に基板のどこかでシリコン膜が露呈していると、そのシリコン膜までエッチングされてしまう。そういう問題を避けるために、予めゲート酸化膜104を除去しておくことは極めて有効である。

【0052】

40

以上の様な構成でなる本実施例を実施することで図1（F）に示す様な基本的なTFT構造が完成するが、必要に応じてさらにTFT構造を変えることは本願発明の効果を何ら妨げるものではない。

【0053】

即ち、同一基板上にNチャネル型TFT及びPチャネル型TFTを作製してCMOS回路を形成することも可能である。この様なCMOS回路はアクティブマトリクス型液晶表示装置のドライバー回路や信号処理回路を構築する。また、絶縁膜で分離された状態でドレイン配線120と接続する様に画素電極を形成すれば、アクティブマトリクス型液晶表示装置の画素マトリクス回路を構築することが可能である。

【0054】

50

以上の様に、公知の手段を用いれば本願発明を用いてアクティブマトリクス型液晶表示装置を形成することは容易である。また、液晶表示装置等の電気光学装置に限らず、ロジック回路のみを構成した半導体回路を形成することも可能である。

#### 【0055】

(実施例2)

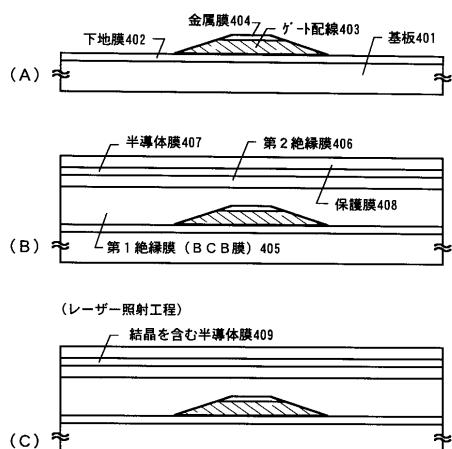

本実施例では実施例1と異なる構造のTFTを作製した場合の例について図4を用いて説明する。

#### 【0056】

本実施例では基板401としてPET(ポリエチレンテレフタレート)基板、下地膜402として酸化窒化シリコン(SiO<sub>x</sub>N<sub>y</sub>で示される)、ゲート配線403としてタンタル膜と窒化タンタル膜との積層膜、金属膜404としてチタン膜を形成する。ゲート配線403と金属膜404とは積層形成しておいて、ゲート配線のパターンを形成する際に一括でエッティングしてしまえば良い。

10

#### 【0057】

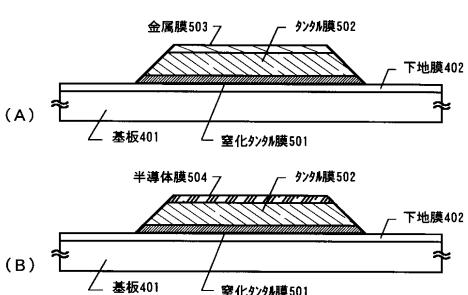

ここでゲート配線403及び金属膜404に注目した拡大図を図5(A)、(B)に示す。図5(A)では基板401上に下地膜402が形成され、その上に窒化タンタル膜501、タンタル膜502、金属膜(チタン膜)503が積層形成されている。

#### 【0058】

金属膜503(図4(A)では404で示される)の形成にはタンタル膜又は窒化タンタル膜の表面層が酸化されたり、水素を吸収したりすることを防ぐ目的がある。同様の効果を持つ金属であればチタン以外の金属膜を用いることもできる。また、図5(B)に示す様に、シリコン膜やシリコンゲルマニウム膜などの半導体膜504を用いても同様の効果が得られる。

20

#### 【0059】

図1(A)の状態が得られたら、第1絶縁膜405としてBCB(ベンゾシクロブテン)膜を100nm~1μm(好ましくは500~800nm)の厚さで形成する。この工程ではゲート配線403による段差を完全に平坦化する程度の膜厚が必要である。BCB膜の平坦化効果は大きいので、さほど膜厚を厚くしなくとも十分な平坦化が可能である。

#### 【0060】

第1絶縁膜405を形成したら、次に第2絶縁膜(窒化シリコン膜)406、半導体膜(非晶質シリコン膜)407、保護膜(酸化シリコン膜)408を順次大気開放しないで積層形成する。こうして連続成膜された絶縁膜及び半導体膜は平坦面上に形成されるため全て平坦である。こうして図1(B)の状態を得る。

30

#### 【0061】

次に、保護膜408の上からエキシマレーザー光を照射することによって、半導体膜407が結晶を含む半導体膜(多結晶シリコン膜)409に変化する。このレーザー結晶化工程の条件は実施例1と同様で良い。この時、半導体膜407が平坦であるので結晶粒径の均一な多結晶シリコン膜が得られる。

#### 【0062】

以上の様に、第1絶縁膜405として平坦化に有利なBCB膜を用いることで平坦面を有する半導体膜を得ることができる。そのため、半導体膜の全域に渡って均一な結晶性を確保することができる。

40

#### 【0063】

また、ゲート配線403の上面を金属膜(チタン膜)404で保護しているため、ゲート配線403が酸化したり水素を吸収したりして配線抵抗が高くなる様な問題を防ぐことができる。さらに、ゲートコンタクト部では容易にゲート配線403を露呈させることができるので、コンタクトホールの形成に有利である。

#### 【0064】

図4(C)以降の工程は実施例1に従えばTFTが完成する。本実施例を実施して作製されたTFTはよりばらつきの少ない電気特性を示す。従って、本実施例を実施例1と組み

50

合わせることは可能である。

【0065】

(実施例3)

本実施例では、図1(C)の工程においてエキシマレーザー光を面状に加工して照射する場合の例について説明する。

【0066】

レーザー光を面状に加工する場合は数十  $\text{cm}^2$  程度（好ましくは 10  $\text{cm}^2$  以上）の面積を一括照射できる様にレーザー光を加工する必要がある。そして照射面全体を所望のレーザーエネルギー密度でアニールするためには、トータルエネルギーが 5 J 以上、好ましくは 10 J 以上の出力のレーザー装置を用いる。

10

【0067】

その場合、エネルギー密度は 100 ~ 800 mJ/cm<sup>2</sup> とし、出力パルス幅は 100 nsec 以上、好ましくは 200 nsec ~ 1 msec とすることが好ましい。200 nsec ~ 1 msec というパルス幅を実現するにはレーザー装置を複数台連結し、各レーザー装置の同期をずらすことによって複数パルスの混合した状態を作れば良い。

【0068】

本実施例の様な面状のビーム形状を有するレーザー光を照射することにより大面積に均一なレーザー照射を行うことが可能である。即ち、活性層の結晶性（結晶粒径や欠陥密度等を含む）が均質なものとなり、TFT 間の電気特性のばらつきを低減することができる。

【0069】

なお、本実施例は実施例1、実施例2との組み合わせが容易であり、その組み合わせ方は自由である。

20

【0070】

(実施例4)

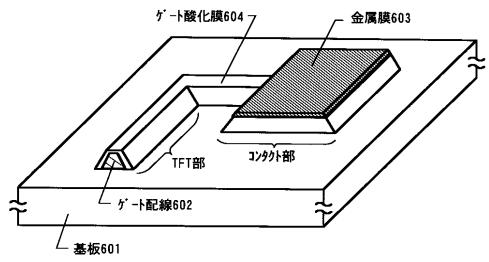

本実施例ではゲートコンタクト部（ゲート配線と外部配線とが電気的に接続する部分）と TFT 部（TFT が形成される部分）とでゲート配線を覆う材料を異なるものとする構成について説明する。説明には図6を用いる。

【0071】

まず、基板601として下地膜を設けたガラス基板を用意する。その上に窒化タンタル膜、タンタル膜、金属膜（本実施例ではチタン膜）を積層形成して、パターニングによりゲート配線602のパターンを形成する。

30

【0072】

次に、金属膜のパターニングを行い、ゲートコンタクト部のみに金属膜603が残る様にする。そして、金属膜603を形成した後でプラズマ酸化を行い、ゲート配線602の表面にゲート酸化膜（本実施例の場合はタンタルオキサイド膜）604を形成する。勿論、熱酸化法や陽極酸化法を用いても良い。

【0073】

この後は実施例1に示した様な工程で TFT を作製すれば良い。本実施例の構成を実施することで、次の様な効果を得ることができる。

1. TFT 部ではゲート酸化膜604を設けた効果により活性層を形成する結晶を含む半導体膜の結晶粒径が均一になる。

40

2. ゲートコンタクト部ではコンタクトホールを形成する際に金属膜603（又は金属膜603の酸化物）が容易に除去できるので、オームックコンタクトを得やすい。

【0074】

以上の様な効果が得られるので、高い歩留まりで高性能な TFT を作製することが可能となり、延いてはその様な TFT で形成された回路を含む半導体装置の性能向上、歩留まり向上を実現することができる。

【0075】

なお、本実施例は実施例1～実施例3のどの実施例とも組み合わせることが可

【0076】

50

## (実施例 5 )

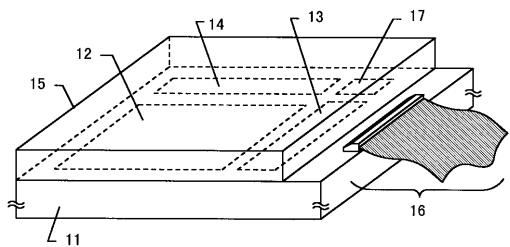

本実施例では、本願発明によって作製された液晶表示装置の例を図 7 に示す。画素 TFT (画素スイッチング素子) の作製方法やセル組工程は公知の手段を用いれば良いので詳細な説明は省略する。

## 【 0 0 7 7 】

図 7 において 1 1 は絶縁表面を有する基板 (酸化シリコン膜を設けたプラスチック基板) 、 1 2 は画素マトリクス回路、 1 3 はソースドライバー回路、 1 4 はゲイドライバー回路、 1 5 は対向基板、 1 6 は F P C (フレキシブルプリントサーチット) 、 1 7 は信号処理回路である。信号処理回路 1 7 としては、 D / A コンバータ、 補正回路、 信号分割回路などの従来 I C で代用していた様な処理を行う回路を形成することができる。勿論、 基板上に I C チップを設けて、 I C チップ上で信号処理を行うことも可能である。

10

## 【 0 0 7 8 】

さらに、本実施例では液晶表示装置を例に挙げて説明しているが、 アクティブマトリクス型の表示装置であれば E L (エレクトロルミネッセンス) 表示装置や E C (エレクトロクロミックス) 表示装置に本願発明を適用することも可能であることは言うまでもない。

## 【 0 0 7 9 】

また、本願発明を用いて作製できる液晶表示装置は透過型か反射型かは問わない。どちらを選択するのも実施者の自由である。この様に本願発明はあらゆるアクティブマトリクス型の電気光学装置 (半導体装置) に対して適用することが可能である。

## 【 0 0 8 0 】

20

なお、本実施例に示した半導体装置を作製するにあたって、実施例 1 ~ 実施例 4 のどの構成を採用しても良いし、各実施例を自由に組み合わせて用いることが可能である。

## 【 0 0 8 1 】

## (実施例 6 )

本願発明は従来の I C 技術全般に適用することが可能である。即ち、現在市場に流通している全ての半導体回路に適用できる。例えば、ワンチップ上に集積化された R I S C プロセッサ、 A S I C プロセッサ等のマイクロプロセッサに適用しても良いし、液晶用ドライバー回路 (D / A コンバータ、 補正回路、 信号分割回路等) に代表される信号処理回路や携帯機器 (携帯電話、 P H S 、 モバイルコンピュータ) 用の高周波回路に適用しても良い。

30

## 【 0 0 8 2 】

また、マイクロプロセッサ等の半導体回路は様々な電子機器に搭載されて中枢回路として機能する。代表的な電子機器としてはパーソナルコンピュータ、 携帯型情報端末機器、 その他あらゆる家電製品が挙げられる。また、車両 (自動車や電車等) の制御用コンピュータなども挙げられる。本願発明はその様な半導体装置に対しても適用可能である。

## 【 0 0 8 3 】

なお、本実施例に示した半導体装置を作製するにあたって、実施例 1 ~ 実施例 4 のどの構成を採用しても良いし、各実施例を自由に組み合わせて用いることが可能である。

## 【 0 0 8 4 】

40

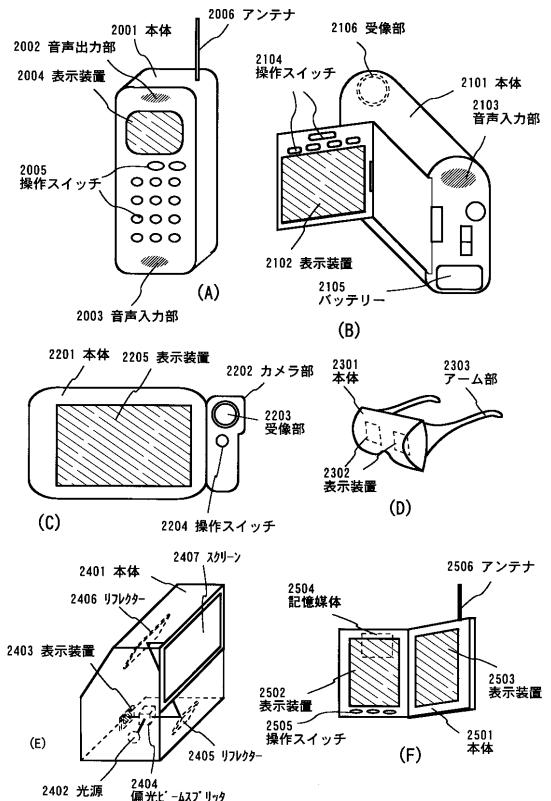

## (実施例 9 )

本願発明の電気光学装置は、様々な電子機器のディスプレイとして利用される。その様な電子機器としては、ビデオカメラ、 デジタルカメラ、 プロジェクター、 プロジェクション T V 、 ゴーグルディスプレイ、 カーナビゲーション、 パーソナルコンピュータ、 携帯情報端末 (モバイルコンピュータ、 携帯電話、 電子書籍等) などが挙げられる。それらの一例を図 7 に示す。

## 【 0 0 8 5 】

図 7 ( A ) は携帯電話であり、 本体 2 0 0 1 、 音声出力部 2 0 0 2 、 音声入力部 2 0 0 3 、 表示装置 2 0 0 4 、 操作スイッチ 2 0 0 5 、 アンテナ 2 0 0 6 で構成される。本願発明を音声出力部 2 0 0 2 、 音声入力部 2 0 0 3 、 表示装置 2 0 0 4 やその他の信号制御回路に適用することができる。

50

## 【0086】

図7( B )はビデオカメラであり、本体2101、表示装置2102、音声入力部2103、操作スイッチ2104、バッテリー2105、受像部2106で構成される。本願発明を表示装置2102、音声入力部2103やその他の信号制御回路に適用することができる。

## 【0087】

図7( C )はモバイルコンピュータ(モービルコンピュータ)であり、本体2201、カメラ部2202、受像部2203、操作スイッチ2204、表示装置2205で構成される。本願発明は表示装置2205やその他の信号制御回路に適用できる。

## 【0088】

図7( D )はゴーグルディスプレイであり、本体2301、表示装置2302、アーム部2303で構成される。本発明は表示装置2302やその他の信号制御回路に適用することができる。

## 【0089】

図7( E )はリア型プロジェクターであり、本体2401、光源2402、表示装置2403、偏光ビームスプリッタ2404、リフレクター2405、2406、スクリーン2407で構成される。本発明は表示装置2403やその他の信号制御回路に適用することができる。

## 【0090】

図7( F )は携帯書籍(電子書籍)であり、本体2501、表示装置2502、2503、記憶媒体2504、操作スイッチ2505、アンテナ2506で構成される。本発明は表示装置2502、2503やその他の信号制御回路に適用することができる。

## 【0091】

以上の様に、本願発明の適用範囲は極めて広く、あらゆる分野の電子機器に適用することができる。

## 【0092】

なお、本実施例に示した半導体装置を作製するにあたって、実施例1～実施例4のどの構成を採用しても良いし、各実施例を自由に組み合わせて用いることが可能である。また、実施例5、実施例6に示した電気光学装置や半導体回路をその様に組み合わせて用いても良い。

## 【0093】

## 【発明の効果】

本願発明を実施することで、TFTの心臓部である活性層の界面(主表面側及び裏面側)を一度も大気に触れされる事なく工程が終了するため、極めて清浄な界面を実現することができる。

## 【0094】

この様な構成により、特にTFTの電気特性を左右する活性層とゲート絶縁膜との界面を清浄なものとすることができるので、ばらつきが少なく、且つ、良好な電気特性を示すTFTが実現される。この時、TFTの代表的なパラメータであるしきい値電圧はNチャネル型TFTで-0.5～2V、Pチャネル型TFTで0.5～-2Vを実現できる。また、サブスレッシュホールド係数(S値)は0.1～0.3V/decadeを実現できる。

## 【図面の簡単な説明】

【図1】 TFTの作製工程を示す図。

【図2】 TFTの作製工程を示す図。

【図3】 TFTの作製工程を示す図。

【図4】 TFTの作製工程を示す図。

【図5】 ゲート配線の構造を示す図。

【図6】 ゲート配線の構造を示す図。

【図7】 半導体装置(液晶表示装置)の構成を示す図。

【図8】 半導体装置(電子機器)の例を示す図。

10

20

30

40

50

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

11:絶縁表面を有する基板 12:画素マトリクス回路

13:ゲート駆動回路 14:ゲートライド回路 15:FPC

16:信号処理回路 17:信号処理回路

【図8】

---

フロントページの続き

(56)参考文献 特開平10-275916 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H01L 29/786

H01L 21/336

G02F 1/1368