(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2012-504263

(P2012-504263A)

(43) 公表日 平成24年2月16日(2012.2.16)

| (51) Int.Cl.                 | F 1        | テーマコード (参考) |

|------------------------------|------------|-------------|

| <b>G06F 12/00</b> (2006.01)  | GO6F 12/00 | 564A        |

| <b>G11C 16/02</b> (2006.01)  | G11C 17/00 | 601D        |

| <b>G11C 11/413</b> (2006.01) | GO6F 12/00 | 550K        |

|                              | G11C 11/34 | J           |

審査請求 未請求 予備審査請求 未請求 (全 42 頁)

|               |                              |          |                                                                                    |

|---------------|------------------------------|----------|------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2011-528145 (P2011-528145) | (71) 出願人 | 508034325<br>モサイド・テクノロジーズ・インコーポレーテッド<br>カナダ・オンタリオ・K2K・2X1・オタワ・ハインズ・ロード・11・スイート・203 |

| (86) (22) 出願日 | 平成21年9月17日 (2009.9.17)       | (74) 代理人 | 100108453<br>弁理士 村山 靖彦                                                             |

| (85) 翻訳文提出日   | 平成23年2月28日 (2011.2.28)       | (74) 代理人 | 100064908<br>弁理士 志賀 正武                                                             |

| (86) 國際出願番号   | PCT/CA2009/001271            | (74) 代理人 | 100089037<br>弁理士 渡邊 隆                                                              |

| (87) 國際公開番号   | W02010/037205                | (74) 代理人 | 100140534<br>弁理士 木内 敬二                                                             |

| (87) 國際公開日    | 平成22年4月8日 (2010.4.8)         |          |                                                                                    |

| (31) 優先権主張番号  | 12/241, 960                  |          |                                                                                    |

| (32) 優先日      | 平成20年9月30日 (2008.9.30)       |          |                                                                                    |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                    |

| (31) 優先権主張番号  | 12/241, 832                  |          |                                                                                    |

| (32) 優先日      | 平成20年9月30日 (2008.9.30)       |          |                                                                                    |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                    |

最終頁に続く

(54) 【発明の名称】出力遅延調整によるシリアル接続のメモリシステム

## (57) 【要約】

クロックデューティサイクルを訂正し、出力遅延調整を実行するシステム及び方法が、スレーブデバイスとして動作するシリアル接続のデバイス用に提供される。マスタデバイスは第1のスレーブデバイスにクロックを供給する。各スレーブデバイスは、クロックを順に次のスレーブデバイスに送る。最下位のスレーブデバイスは、クロックをマスタデバイスに戻す。マスタデバイスは、送出クロックと帰還クロックとを比較し、デューティサイクル訂正又は出力遅延調整が必要かどうかを判定する。必要ならば、マスタデバイスは、スレーブデバイスに対するコマンドを生成し、出力して、デューティサイクル又は出力遅延調整を実行する。スレーブデバイスはそれぞれ、デューティサイクル訂正又は出力遅延調整を実行する回路を有する。実装形態では、各スレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

**【特許請求の範囲】****【請求項 1】**

複数のシリアル接続のスレーブデバイスのうちのあるスレーブデバイスにおける方法であって、

クロックデューティサイクルに対する調整を指定するマスタデバイスからのコマンドを受け取るステップと、

入力クロック信号を受け取るステップと、

前記コマンドにより、前記入力クロック信号から、デューティサイクル訂正されたクロック信号を生成するステップと、

前記デューティサイクル訂正されたクロック信号を出力するステップと

を含む方法。

**【請求項 2】**

前記スレーブデバイスはメモリデバイスであり、前記マスタデバイスはメモリコントローラである、請求項1に記載の方法。

**【請求項 3】**

前記スレーブデバイスによって出力される少なくとも1つの信号に印加すべき遅延を前記スレーブデバイスがどのように調整すべきかを指定するマスタデバイスからのコマンドを受け取るステップと、

少なくとも1つの入力信号を受け取るステップであって、前記少なくとも1つの入力信号は、少なくとも前記入力クロック信号を有する、ステップと、

前記少なくとも1つの入力信号のそれぞれごとに

前記コマンドにより前記入力信号の遅延されたバージョンを生成するステップと、

前記入力信号の前記遅延されたバージョンを出力するステップであって、前記入力クロック信号の前記遅延されたバージョンは、前記デューティサイクル訂正されたクロック信号の遅延されたバージョンを有する、ステップと

をさらに含む請求項1に記載の方法。

**【請求項 4】**

クロックデューティサイクルに対する調整を指定するマスタデバイスからのコマンドを受け取るステップは、前記コマンドをデューティサイクル訂正コマンドと見なすコマンド識別子を含むコマンドを受け取るステップを含み、前記コマンドは、前記デューティサイクルをどのように調整すべきかを示すデータをさらに含む、請求項1に記載の方法。

**【請求項 5】**

コマンドを受け取るステップは、スレーブデバイスとして働くどのデバイスが、前記コマンドを実行すべきかを示すデバイスアドレスを受け取るステップをさらに含む、請求項4に記載の方法。

**【請求項 6】**

前記コマンドが前記スレーブデバイスのデバイスアドレスに一致するデバイスアドレスを有する場合、前記コマンドにより、前記デューティサイクル訂正されたクロック信号を生成する前記ステップを実行するステップと、

前記コマンドがブロードキャストデバイスアドレスであるデバイスアドレスを有する場合、前記コマンドにより、前記デューティサイクル訂正されたクロック信号を生成する前記ステップを実行するステップと

をさらに含む、請求項5に記載の方法。

**【請求項 7】**

デューティサイクル訂正されたクロック信号を生成するステップは、

a)前記入力クロック信号から半レートクロック信号を生成するステップと、

b)前記半レートクロック信号を複数の遅延のうちの選択された1つによって遅延させて、遅延された半レートクロック信号を生成するステップと、

c)前記半レートクロック信号を前記遅延された半レートクロック信号と結合して、前記デューティサイクル訂正されたクロック信号を生成するステップと

10

20

30

40

50

を含む、請求項4に記載の方法。

【請求項8】

前記デューティサイクル訂正をどのように調整すべきかを示す前記データは、前記複数の遅延のうちの前記選択された1つの指示を含む、請求項7に記載の方法。

【請求項9】

マスタデバイスと、少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含む複数のシリアル接続のスレーブデバイスとを備えるメモリシステムにおける方法であって、

前記マスタデバイスにおいて、

a)前記第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を出力するステップと、

b)前記最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受けるステップと、

c)前記第2のクロック信号のデューティサイクルに応じてデューティサイクル訂正コマンドを生成し、前記デューティサイクル訂正コマンドを出力するステップと、

前記複数のシリアル接続のスレーブデバイスのうちの前記第1のスレーブデバイスにおいて、

a)前記第1のスレーブデバイスの前記入力クロック信号として、前記マスタデバイスから前記第1のクロック信号を受け取るステップと、

b)前記入力信号から出力クロック信号を生成するステップと、

前記複数のシリアル接続のスレーブデバイスの他のそれぞれのスレーブデバイスにおいて、

a)前記スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの前記出力クロック信号を受け取るステップと、

b)前記入力クロック信号から出力クロック信号を生成するステップと、

スレーブデバイスとして働く前記複数のシリアル接続のデバイスのうちの少なくとも1つのそれぞれにおいて、

a)前記デューティサイクル訂正コマンドを受け取るステップと、

b)前記デューティサイクル訂正コマンドにより、前記入力クロック信号からデューティサイクル訂正されたクロック信号を生成するステップと、

c)前記スレーブデバイスの前記出力クロック信号として、前記デューティサイクル訂正されたクロック信号を出力するステップと

を含む方法。

【請求項10】

それぞれのスレーブデバイスはメモリデバイスであり、前記マスタデバイスはメモリコントローラである、請求項9に記載の方法。

【請求項11】

前記マスタデバイスにおいて、

a)少なくとも1つの出力信号を出力するステップであって、前記少なくとも1つの出力信号は、前記第1のスレーブデバイスの入力クロック信号として機能する前記第1のクロック信号を含む、ステップと、

b)前記最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受けるステップと、

c)前記第1のクロック信号および前記第2のクロック信号の間の位相オフセットの量を確定するステップと、

d)前記第1のクロック信号および前記第2のクロック信号の間の前記位相オフセットに応じて出力遅延調整コマンドを生成し、前記出力遅延調整コマンドを出力するステップとをさらに含む、請求項9または10に記載の方法。

【請求項12】

前記第2のクロック信号のデューティサイクルに応じてデューティサイクル訂正コマン

10

20

30

40

50

ドを生成し、前記デューティサイクル訂正コマンドを出力するステップは、前記複数のシリアル接続のスレーブデバイスのうちのいずれか指定された1つによって実行するためのデューティサイクル訂正コマンドを生成するステップを含む、請求項9または10に記載の方法。

【請求項 13】

前記第2のクロック信号のデューティサイクルに応じてデューティサイクル訂正コマンドを生成し、前記デューティサイクル訂正コマンドを出力するステップは、前記複数のシリアル接続のスレーブデバイスのすべてによって実行するためのデューティサイクル訂正コマンドを生成するステップを含む、請求項12に記載の方法。

【請求項 14】

前記デューティサイクル訂正コマンドを受け取るステップは、前記コマンドをデューティサイクル訂正コマンドと見なすコマンド識別子を含み、かつ前記デューティサイクルをどのように調整すべきかを示すデータを含むコマンドを受け取るステップを含む、請求項9に記載の方法。

10

【請求項 15】

デューティサイクル訂正されたクロック信号を生成するステップは、

a)前記入力クロック信号から半レートクロック信号を生成するステップと、

b)前記半レートクロック信号を複数の遅延のうちの選択された1つによって遅延させて、遅延された半レートクロック信号を生成するステップと、

c)前記半レートクロック信号を前記遅延された半レートクロック信号と結合して、前記デューティサイクル訂正されたクロック信号を生成するステップとを含む、請求項14に記載の方法。

20

【請求項 16】

前記デューティサイクル訂正をどのように調整すべきかを示す前記データは、前記複数の遅延のうちの前記選択された1つの指示を含む、請求項15に記載の方法。

【請求項 17】

複数のシリアル接続のスレーブデバイスを備える構成で使用するためのスレーブデバイスであって、

デューティサイクルに対する調整を指定するマスタデバイスからのコマンドを受け取るためのコマンド入力と、

30

入力クロック信号を受け取るためのクロック入力と、

前記制御コマンドにより、クロック入力からデューティサイクル訂正されたクロック信号を生成するためのディーティサイクル訂正回路と、

前記デューティサイクル訂正されたクロック信号を出力するためのクロック出力とを備えるスレーブデバイス。

【請求項 18】

前記スレーブデバイスはメモリデバイスである、請求項17に記載のスレーブデバイス。

【請求項 19】

前記コマンド入力はまた、出力遅延に対する調整を指定する前記マスタデバイスからのコマンドを受け取るためのものであり、

40

出力遅延調整回路は、前記コマンドにより、前記デューティサイクル訂正されたクロック信号から、遅延されたクロック信号を生成するためのものであり、

前記デューティサイクル訂正されたクロック信号を出力するための前記クロック出力は、前記遅延されたクロック信号を出力する、

請求項17または18に記載のスレーブデバイス。

【請求項 20】

前記コマンドを処理するコマンド処理回路をさらに備え、

前記コマンドは、

前記コマンドをデューティサイクル訂正コマンドと見なすコマンド識別子と、

50

前記デューティサイクルをどのように調整すべきかを示すデータと

を含む、

請求項17または18に記載のスレーブデバイス。

【請求項 2 1】

デバイスアドレスレジスタをさらに備え、

前記コマンドは、どのスレーブデバイスが前記コマンドを実行すべきかを示すデバイスアドレスをさらに含み、前記スレーブデバイスは、前記デバイスアドレスが前記デバイスアドレスレジスタのコンテンツに一致する場合、前記コマンドを実行するように構成されている、

請求項20に記載のスレーブデバイス。

【請求項 2 2】

前記デューティサイクル訂正回路は、

- a)前記入力クロック信号から半レートクロック信号を生成するクロック分周器回路と、

- b)前記半レートクロック信号を複数の遅延のうちの選択された1つによって遅延させて、遅延された半レートクロック信号を生成する遅延回路と、

- c)前記半レートクロック信号を前記遅延された半レートクロック信号と結合して、前記デューティサイクル訂正されたクロック信号を生成する結合器と

- を備える、請求項17から21のいずれか一項に記載のスレーブデバイス。

【請求項 2 3】

前記遅延回路は、 $M \geq 2$ のM個のユニット遅延要素を備え、前記デューティサイクル訂正回路は、

前記半レートクロック信号を遅延させて、前記遅延された半レートクロック信号を生成する際に、前記ユニット遅延要素のうちの何個がアクティブであるべきかの選択に、 $N \geq 1$ のN個の入力線上で受け取られた信号をデコードするN対Mデコーダをさらに備える、請求項22に記載のスレーブデバイス。

【請求項 2 4】

少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含む請求項17に記載のスレーブデバイスとして働く複数のシリアル接続のデバイスと、

前記第1のスレーブデバイスおよび前記最下位のスレーブデバイスに接続されているマスタデバイスであって、

前記第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を出力するように構成されている、マスタデバイスと、

前記最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受け取るためのクロック入力と、

前記第2のクロック信号のデューティサイクルを確定するデューティ検出器と、

前記第2のクロック信号の前記デューティサイクルに応じて、クロックデューティサイクルに対する調整を指定するデューティサイクル訂正コマンドを生成するコマンドジェネレータと

を備えるシステムであって、

スレーブデバイスとして働く前記複数のシリアル接続のデバイスの前記第1のスレーブデバイスは、

a)前記第1のスレーブデバイスの前記入力クロック信号として、前記マスタデバイスから前記第1のクロック信号を受け取り、

b)前記入力クロック信号から出力クロック信号を生成し、

スレーブデバイスとして働く前記複数のシリアル接続のデバイスの他のそれぞれのスレーブデバイスは、

a)前記スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの前記出力クロック信号を受け取り、

b)前記入力クロック信号から出力クロック信号を生成し、

前記複数のシリアル接続のスレーブデバイスのうちの少なくとも1つは、

a)前記デューティサイクル訂正コマンドを受け取り、

10

20

30

40

50

- b)前記制御コマンドにより、デューティサイクル訂正されたクロック信号を生成し、

c)前記スレーブデバイスの前記出力クロック信号として、前記デューティサイクル訂正されたクロック信号を出力する、

システム。

**【請求項 25】**

前記システムはメモリシステムであり、それぞれのスレーブデバイスはメモリデバイスであり、前記マスタデバイスはメモリコントローラである、請求項24に記載のシステム。

**【請求項 26】**

前記第1のクロック信号および前記第2のクロック信号の間の位相オフセットの量を確定する位相検出器をさらに備え、

前記コマンドジェネレータはまた、位相オフセットの前記量に応じて、出力遅延調整コマンドを生成し、

前記複数のシリアル接続のスレーブデバイスのうちの前記第1のスレーブデバイスは、

a)前記第1のスレーブデバイスの前記入力クロック信号として、前記マスタデバイスから前記第1のクロック信号を受け取り、

b)前記入力クロック信号から出力クロック信号を生成し、

前記複数のシリアル接続のスレーブデバイスの他のそれぞれのスレーブデバイスは、

a)前記スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの前記出力クロック信号を受け取り、

b)前記入力クロック信号から出力クロック信号を生成し、

前記複数のシリアル接続のスレーブデバイスのうちの少なくとも1つは、

a)前記出力遅延調整コマンドを受け取り、

b)前記制御コマンドにより、前記デバイスの前記入力クロック信号を遅延させることによって、前記デバイスの前記出力クロック信号を生成する、

請求項24または25に記載のメモリシステム。

**【請求項 27】**

前記コマンドジェネレータは、前記第2のクロック信号のデューティサイクルに応じて、デューティサイクル訂正コマンドを生成し、スレーブデバイスとして働く前記複数のシリアル接続のデバイスの指定された1つによって実行するためのデューティサイクル訂正コマンドを生成することによって、前記デューティサイクル訂正コマンドを出力するように構成されている、請求項24または25に記載のメモリシステム。

**【請求項 28】**

前記コマンドジェネレータは、前記第2のクロック信号のデューティサイクルに応じて、デューティサイクル訂正コマンドを生成し、スレーブデバイスとして働く前記複数のシリアル接続のデバイスのすべてによって実行するためのデューティサイクル訂正コマンドを生成することによって、前記デューティサイクル訂正コマンドを出力するように構成されている、請求項24または25に記載のメモリシステム。

**【請求項 29】**

前記デューティサイクル訂正コマンドを受け取ることは、前記コマンドをデューティサイクル訂正コマンドと見なすコマンド識別子を含み、かつ前記デューティサイクルをどのように調整すべきかを示すデータを含むコマンドを受け取ることを含む、請求項24から28のいずれか一項に記載のメモリシステム。

**【請求項 30】**

複数のシリアル接続のスレーブデバイスのうちのあるスレーブデバイスにおける方法であって、

前記スレーブデバイスによって出力される少なくとも1つの信号に印加すべき遅延を前記スレーブデバイスが、どのように調整すべきかを指定するマスタデバイスからのコマンドを受け取るステップと、

少なくとも1つの入力信号を受け取るステップであって、前記少なくとも1つの入力信号は、少なくとも入力クロック信号を含む、ステップと、

10

20

30

40

50

前記少なくとも1つの入力信号のそれぞれごとに、

前記コマンドにより前記入力信号の遅延されたバージョンを生成するステップと、

前記入力信号の前記遅延されたバージョンを出力するステップと

を含む方法。

【請求項 3 1】

前記スレーブデバイスはメモリデバイスであり、前記マスタデバイスはメモリコントローラである、請求項30に記載の方法。

【請求項 3 2】

データ出力信号を出力するステップであって、

前記入力信号のうちの少なくとも1つは、データ入力信号を含み、前記データ入力信号の前記遅延されたバージョンを出力するステップは、前記データ出力信号を出力するステップの一部として実行され、それにより、

10

a) 時には、前記データ出力信号は、前記データ入力信号の前記遅延されたバージョンになり、

b) 時には、前記データ出力信号は、前記コマンドにより、前記スレーブデバイスにとって局所的に生成された信号に前記遅延を印加した後に、前記スレーブデバイスにとって局所的に生成された前記信号の遅延されたバージョンになる、

ステップを含む、請求項30または31に記載の方法。

【請求項 3 3】

前記スレーブデバイスによって出力される少なくとも1つの信号に印加すべき遅延に対する調整を指定するマスタデバイスからのコマンドを受け取るステップは、前記コマンドを出力遅延調整コマンドと見なすコマンド識別子を含むコマンドを受け取るステップを含み、前記コマンドは、前記遅延をどのように調整すべきかを示すデータをさらに含む、請求項30または31に記載の方法。

20

【請求項 3 4】

コマンドを受け取るステップは、スレーブデバイスとして働くどのデバイスが、前記コマンドを実行すべきかを示すデバイスアドレスを受け取るステップをさらに含む、請求項33に記載の方法。

【請求項 3 5】

前記コマンドが前記スレーブデバイスのデバイスアドレスに一致するデバイスアドレスを有する場合、前記少なくとも1つの入力信号のそれぞれごとに、前記コマンドにより前記入力信号の遅延されたバージョンを生成する前記ステップを実行するステップと、

30

前記コマンドがブロードキャストデバイスアドレスであるデバイスアドレスを有する場合、前記少なくとも1つの入力信号のそれぞれごとに、前記コマンドにより前記入力信号の遅延されたバージョンを生成する前記ステップを実行するステップと

をさらに含む、請求項34に記載の方法。

【請求項 3 6】

それぞれの入力信号ごとに、前記入力信号の遅延されたバージョンを生成するステップは、

a) 複数の遅延のうちの選択された1つによって、前記入力信号を遅延させて、前記入力信号の前記遅延されたバージョンを生成するステップを

含む、

40

請求項33に記載の方法。

【請求項 3 7】

前記遅延をどのように調整すべきかを示す前記データは、前記複数の遅延のうちの前記選択された1つの指示を含む、請求項36に記載の方法。

【請求項 3 8】

前記複数の入力信号は、

クロック信号と、

コマンドストローブ信号と、

50

データストローブ信号と、

コマンドおよびデータを含むデータ信号と

を含む、請求項30の方法。

【請求項 39】

マスタデバイスと、少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含むスレーブデバイスとして働く複数のシリアル接続のデバイスとを備えるメモリシステムにおける方法であって、

前記マスタデバイスにおいて、

a)少なくとも1つの出力信号を出力するステップであって、前記少なくとも1つの出力信号は、前記第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を含む、ステップと、

b)前記最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受けるステップと、

c)前記第1のクロック信号および前記第2のクロック信号の間の位相オフセットの量を確定するステップと、

d)前記第1のクロック信号および前記第2のクロック信号の間の前記位相オフセットに応じて、出力遅延調整コマンドを生成し、前記出力遅延調整コマンドを出力するステップとを含む方法。

【請求項 40】

それぞれのスレーブデバイスはメモリデバイスであり、前記マスタデバイスはメモリコントローラである、請求項39に記載の方法。

【請求項 41】

スレーブデバイスとして働く前記複数のシリアル接続のデバイスの前記第1のスレーブデバイスにおいて、

a)前記第1のスレーブデバイスの対応する少なくとも1つの入力信号として、前記マスタデバイスから前記少なくとも1つの出力信号を受け取るステップと、

b)それぞれの入力信号ごとに、前記入力信号に基づいて出力信号を生成するステップと、

スレーブデバイスとして働く前記複数のシリアル接続のデバイスの他のそれぞれのスレーブデバイスにおいて、

a)前記スレーブデバイスの少なくとも1つの入力信号に対応する先行するスレーブデバイスの出力信号を受け取るステップと、

b)それぞれの入力信号ごとに、前記入力信号に基づいて出力信号を生成するステップと、

前記スレーブデバイスのうちの少なくとも1つにおいて、

a)前記出力遅延調整コマンドを受け取るステップと、

b)前記出力遅延調整コマンドにより、前記入力信号の遅延されたバージョンを生成することによって、前記出力信号を生成するステップと

をさらに含む、請求項39または40に記載の方法。

【請求項 42】

前記マスタデバイスの前記少なくとも1つの出力信号が、複数の出力信号を含む、請求項41に記載の方法。

【請求項 43】

遅延調整コマンドを生成するステップは、前記複数のシリアル接続のスレーブデバイスのうちの指定された1つによって実行するための遅延調整コマンドを生成するステップを含む、請求項39または40に記載の方法。

【請求項 44】

遅延調整コマンドを生成するステップは、前記複数のシリアル接続のスレーブデバイスのすべてによって実行するための遅延調整コマンドを生成するステップを含む、請求項39または40に記載の方法。

10

20

30

40

50

**【請求項 4 5】**

前記出力遅延調整コマンドにより、前記入力信号の遅延されたバージョンを生成するステップは、複数の遅延のうちの選択された1つによって遅延された前記入力信号の遅延されたバージョンを生成するステップを含む、請求項41に記載の方法。

**【請求項 4 6】**

遅延調整コマンドを生成するステップは、前記コマンドを出力遅延調整コマンドと見なすコマンド識別子を含み、かつ前記遅延をどのように調整すべきかを示すデータを含むコマンドを生成するステップを含む、請求項45に記載の方法。

**【請求項 4 7】**

前記遅延をどのように調整すべきかを示す前記データは、前記複数の遅延のうちの前記選択された1つの指示を含む、請求項46に記載の方法。 10

**【請求項 4 8】**

前記位相オフセットが許容可能になるまで、前記マスタデバイスが、一度に、1つのスレーブデバイスにおける1つのユニット遅延要素に遅延を加えることによって、遅延を調整する出力遅延調整コマンドを出力するステップをさらに含む、請求項39または40に記載の方法。

**【請求項 4 9】**

前記複数の入力信号は、

クロック信号と、

コマンドストローブ信号と、

データストローブ信号と、

コマンドおよびデータを含むデータ信号と

を含む、請求項39または40に記載の方法。 20

**【請求項 5 0】**

複数のシリアル接続のスレーブデバイスを備える構成で使用するためのスレーブデバイスであって、

出力遅延調整をどのように実行すべきかを指定するマスタデバイスからのコマンドを受け取るためのコマンド入力と、

入力クロック信号を受け取るためのクロック入力と、

前記コマンドにより、前記クロック入力から、遅延されたクロック信号を生成するための出力遅延調整回路と、 30

前記遅延されたクロック信号を出力するためのクロック出力と

を備える、スレーブデバイス。

**【請求項 5 1】**

前記スレーブデバイスはメモリデバイスである、請求項50に記載のスレーブデバイス。

**【請求項 5 2】**

前記コマンドを処理するコマンド処理回路を備え、前記コマンドは、前記コマンドを出力遅延調整コマンドと見なすコマンド識別子を含み、前記出力遅延をどのように調整すべきかを示すデータを含む、

請求項50または51に記載のスレーブデバイス。 40

**【請求項 5 3】**

デバイスアドレスレジスタをさらに備え、

前記コマンドは、どのスレーブデバイスが前記コマンドを実行すべきかを示すデバイスアドレスをさらに含み、前記スレーブデバイスは、前記デバイス識別子が、前記デバイスアドレスレジスタのコンテンツに一致する場合、前記コマンドを実行するように構成されている、

請求項52に記載のスレーブデバイス。

**【請求項 5 4】**

前記出力遅延調整回路は、

前記入力クロック信号を含めて複数の入力信号のそれぞれごとに、複数の遅延のうちの 50

選択された1つによって、前記入力信号を遅延させて、前記入力信号の遅延されたバージョンを生成する遅延回路を

備える、請求項50または51に記載のスレーブデバイス。

【請求項 5 5】

それぞれの出力遅延回路は、 $M \geq 2$ のM個のユニット遅延要素を備え、前記デューティサイクル訂正回路は、

前記入力信号の前記遅延されたバージョンを生成する際に、前記ユニット遅延要素のうちの何個がアクティブであるべきかの選択に、 $N \geq 1$ のN個の入力線上で受け取られた信号をデコードするN対Mデコーダを

さらに備える、請求項54に記載のスレーブデバイス。

10

【請求項 5 6】

少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含む請求項47に記載の複数のシリアル接続のスレーブデバイスと、

前記第1のスレーブデバイスおよび前記最下位のスレーブデバイスに接続されているマスタデバイスであって、

前記第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を出力するように構成されている、マスタデバイスと、

前記最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受け取るためのクロック入力と、

前記第1のクロック信号および前記第2のクロック信号の間の位相オフセットの量を確定する位相検出器と、

位相オフセットの前記量に応じて、出力遅延調整コマンドを生成するコマンドジェネレータと

を備えるメモリシステムであって、

前記複数のシリアル接続のスレーブデバイスのうちの前記第1のスレーブデバイスは、

a)前記第1のスレーブデバイスの前記入力クロック信号として、前記マスタデバイスから前記第1のクロック信号を受け取り、

b)前記入力クロック信号から出力クロック信号を生成し、

前記複数のシリアル接続のスレーブデバイスの他のそれぞれのスレーブデバイスは、

a)前記スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの前記出力クロック信号を受け取り、

b)前記入力クロック信号から出力クロック信号を生成し、

前記複数のシリアル接続のスレーブデバイスのうちの少なくとも1つは、

a)前記出力遅延調整コマンドを受け取り、

b)前記制御コマンドにより、前記デバイスの前記入力クロック信号を遅延させることによって、前記デバイスの前記出力クロック信号を生成する、

メモリシステム。

【請求項 5 7】

前記システムはメモリシステムであり、それぞれのスレーブデバイスはメモリデバイスであり、前記マスタデバイスはメモリコントローラである、請求項56に記載のシステム。

【請求項 5 8】

前記コマンドジェネレータは、前記複数のシリアル接続のスレーブデバイスのうちの指定された1つによって実行するための前記出力遅延調整コマンドを生成するように構成されている、請求項56または57に記載のメモリシステム。

【請求項 5 9】

前記コマンドジェネレータは、前記複数のシリアル接続のスレーブデバイスのすべてによって実行するための前記出力遅延調整コマンドを生成するように構成されている、請求項56または57に記載のメモリシステム。

【請求項 6 0】

出力遅延調整コマンドを生成することは、前記コマンドを出力遅延調整コマンドと見な

20

30

40

50

すコマンド識別子を含み、かつ前記出力遅延をどのように調整すべきかを示すデータを含むコマンドを生成することを含む、請求項56または57に記載のメモリシステム。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、一般に、一連のシリアル接続のメモリデバイスを特徴とする固体メモリシステムに関するものである。

【背景技術】

【0002】

従来のNANDフラッシュメモリシステムは、コマンド動作、アドレス動作、およびデータ転送動作に多数のパラレル信号を使用する。これは、メモリシステムを構成する非常に普及しているやり方であり、非常に速いシステム動作をもたらす。これは、DRAM(ダイナミックランダムアクセスメモリ)、SRAM(静态ランダムアクセスメモリ)などのようなランダムアクセスメモリデバイスには特に当てはまる。

【0003】

多数のパラレル信号線が、メモリシステムにおけるありとあらゆるメモリデバイスにルーティングされる必要があるという点で、この手法からは欠点が生じる。また、システム電力供給は、パラレル信号伝達用に、より高いピーク電力を供給するために、より高い容量を有する必要がある。従来のNANDフラッシュメモリについての書き込み/読み取りループットは、より高い動作周波数を使用することによって、ダイレクトに増加可能である。例えば、約40MHz(=NAND FlashではtRCに対して25ns)の現在の動作周波数は、約100~200MHzに増加可能である。この手法は、簡単なように思われるが、そのような高周波数では信号品質に伴う重大な問題があり、その問題によって、従来のNANDフラッシュメモリの動作周波数に実際上の制限が課されている。

【0004】

具体的には、従来のNANDフラッシュメモリは、コマンド命令を受け取り、入力データを受け取り、出力データを供給する所望のワード構成に応じて8または16の番号付けをした一連の並列の入力/出力(I/O)ピンを使用して、他の構成要素と通じている。これは一般に、パラレルインターフェースとして知られている。高速動作は、例えば、信号品質を劣化させるクロストーク、信号スキュー、および信号減衰などのよく知られている通信劣化効果をもたらすことになる。このようなパラレルインターフェースは、多数のピンを使用して、データを読み取り、書き込む。入力ピンおよびワイヤの数が増加するにつれて、望ましくない効果の数も増加する。これらの効果は、符号間干渉、信号スキュー、およびクロストークを含む。

【0005】

これらの欠点のうちのいくつかに対処するために、環状に接続されている一連のメモリデバイスを特徴とする複数のシリアル接続のシステム構成が提供されている。これらは、「Multiple Independent Serial Link Memory」(米国特許出願公開第20070076479A1号、「Daisy Chain Cascading Devices」(米国特許出願公開第20070109833A1号、「Memory with Output Control」(米国特許出願公開第20070153576A1号、「Daisy chain cascade configuration recognition technique」(米国特許出願公開第2007233903A1号、および「Independent Link and Bank Selection」(米国特許出願公開第2007143677A1号を含み、それらのすべては、本願と同一の出願人に譲渡され、その全体を参照によって、本明細書により組み込まれる。これらのシステムは一般的に、メモリコントローラにシリアルデータ通信の最大の柔軟性をもたらすために、シリアル入力ポートおよびシリアル出力ポートをそれぞれイネーブルし、ディスエーブルするための2つの制御信号とともに、直列のイン/アウトのデータピンを有する。これらのメモリシステム構成のうちのいくつかは、システムクロックの分散のための共有バストポロジを使用し、それを「共通クロックシステム」または「マルチドロップクロックシステム」と呼ぶ。これらのアーキテクチャのうちのいくつかは、一方が、先行するデバイスまたはコントローラから受け取られる入力クロック

10

20

30

40

50

クであり、他方が、次のデバイスに伝送される出力クロックである2つのクロック信号をそれぞれのメモリデバイスにおいて同期させるために、それぞれのメモリチップにおけるDLL(遅延ロックループ)またはPLL(位相ロックループ)を特徴とするポイントツーポイントシリアル接続のクロッキングアーキテクチャを使用する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】米国特許出願公開第20070076479A1号明細書

【特許文献2】米国特許出願公開第20070109833A1号明細書

10

【特許文献3】米国特許出願公開第20070153576A1号明細書

【特許文献4】米国特許出願公開第2007233903A1号明細書

【特許文献5】米国特許出願公開第2007143677A1号明細書

【特許文献6】国際公開第2008/070978号

【特許文献7】米国特許出願第12/018,272号明細書

【発明の概要】

【課題を解決するための手段】

【0007】

1つの広範な態様によれば、本発明は、複数のシリアル接続のスレーブデバイスのうちのあるスレーブデバイスにおける方法を提供し、この方法は、クロックデューティサイクルに対する調整を指定するマスタデバイスからのコマンドを受け取るステップと、入力クロック信号を受け取るステップと、コマンドにより、入力クロック信号から、デューティサイクル訂正されたクロック信号を生成するステップと、デューティサイクル訂正されたクロック信号を出力するステップとを含む。

20

【0008】

いくつかの実施形態においては、スレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

【0009】

いくつかの実施形態においては、この方法は、スレーブデバイスによって出力される少なくとも1つの信号に印加すべき遅延をスレーブデバイスがどのように調整すべきかを指定するマスタデバイスからのコマンドを受け取るステップと、少なくとも1つの入力信号を受け取るステップであって、少なくとも1つの入力信号は、少なくとも入力クロック信号を有する、ステップと、少なくとも1つの入力信号のそれぞれごとに、コマンドにより入力信号の遅延されたバージョンを生成するステップと、入力信号の遅延されたバージョンを出力するステップであって、入力クロック信号の遅延されたバージョンは、デューティサイクル訂正されたクロック信号の遅延されたバージョンを有する、ステップとをさらに含む。

30

【0010】

いくつかの実施形態においては、クロックデューティサイクルに対する調整を指定するマスタデバイスからのコマンドを受け取るステップは、そのコマンドをデューティサイクル訂正コマンドと見なすコマンド識別子を含むコマンドを受け取るステップを含み、コマンドは、デューティサイクルをどのように調整すべきかを示すデータをさらに含む。

40

【0011】

いくつかの実施形態においては、コマンドを受け取るステップは、スレーブデバイスとして働くどのデバイスが、そのコマンドを実行すべきかを示すデバイスアドレスを受け取るステップをさらに含む。

【0012】

いくつかの実施形態においては、この方法は、コマンドがスレーブデバイスのデバイスアドレスに一致するデバイスアドレスを有する場合、そのコマンドにより、デューティサイクル訂正されたクロック信号を生成するステップを実行するステップと、コマンドがブロードキャストデバイスアドレスであるデバイスアドレスを有する場合、そのコマンドに

50

より、デューティサイクル訂正されたクロック信号を生成するステップを実行するステップとをさらに含む。

【0013】

いくつかの実施形態においては、デューティサイクル訂正されたクロック信号を生成するステップは、a)入力クロック信号から半レートクロック信号を生成するステップと、b)その半レートクロック信号を複数の遅延のうちの選択された1つによって遅延させて、遅延された半レートクロック信号を生成するステップと、c)半レートクロック信号を遅延された半レートクロック信号と結合して、デューティサイクル訂正されたクロック信号を生成するステップとを含む。

【0014】

いくつかの実施形態においては、デューティサイクル訂正をどのように調整すべきかを示すデータは、複数の遅延のうちの選択された1つの指示を含む。

【0015】

別の広範な態様によれば、本発明は、マスタデバイスと、少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含む複数のシリアル接続のスレーブデバイスとを備えるメモリシステムにおける方法を提供し、この方法は、マスタデバイスにおいて、a)第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を出力するステップと、b)最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受け取るステップと、c)第2のクロック信号のデューティサイクルに応じてデューティサイクル訂正コマンドを生成し、そのデューティサイクル訂正コマンドを出力するステップと、複数のシリアル接続のスレーブデバイスのうちの第1のスレーブデバイスにおいて、a)第1のスレーブデバイスの入力クロック信号として、マスタデバイスから第1のクロック信号を受け取るステップと、b)入力信号から出力クロック信号を生成するステップと、複数のシリアル接続のスレーブデバイスの他のそれぞれのスレーブデバイスに、a)スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの出力クロック信号を受け取るステップと、b)入力クロック信号から出力クロック信号を生成するステップと、スレーブデバイスとして働く複数のシリアル接続のデバイスのうちの少なくとも1つのそれぞれにおいて、a)デューティサイクル訂正コマンドを受け取るステップと、b)デューティサイクル訂正コマンドにより、入力クロック信号からデューティサイクル訂正されたクロック信号を生成するステップと、c)スレーブデバイスの出力クロック信号として、デューティサイクル訂正されたクロック信号を出力するステップとを含む。

【0016】

いくつかの実施形態においては、それぞれのスレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

【0017】

いくつかの実施形態においては、この方法は、マスタデバイスにおいて、a)少なくとも1つの出力信号を出力するステップであって、少なくとも1つの出力信号は、第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を含む、ステップと、b)最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受け取るステップと、c)第1のクロック信号および第2のクロック信号の間の位相オフセットの量を確定するステップと、d)第1のクロック信号および第2のクロック信号の間の位相オフセットに応じて出力遅延調整コマンドを生成し、出力遅延調整コマンドを出力するステップとをさらに含む。

【0018】

いくつかの実施形態においては、第2のクロック信号のデューティサイクルに応じてデューティサイクル訂正コマンドを生成し、デューティサイクル訂正コマンドを出力するステップは、複数のシリアル接続のスレーブデバイスのうちのいずれか指定された1つによって実行するためのデューティサイクル訂正コマンドを生成するステップを含む。

【0019】

いくつかの実施形態においては、第2のクロック信号のデューティサイクルに応じてデ

10

20

30

40

50

デューティサイクル訂正コマンドを生成し、デューティサイクル訂正コマンドを出力するステップは、複数のシリアル接続のスレーブデバイスのすべてによって実行するためのデューティサイクル訂正コマンドを生成するステップを含む。

【0020】

いくつかの実施形態においては、デューティサイクル訂正コマンドを受け取るステップは、そのコマンドをデューティサイクル訂正コマンドと見なすコマンド識別子を含み、かつデューティサイクルをどのように調整すべきかを示すデータを含むコマンドを受け取るステップを含む。

【0021】

いくつかの実施形態においては、デューティサイクル訂正されたクロック信号を生成するステップは、a)入力クロック信号から半レートクロック信号を生成するステップと、b)半レートクロック信号を複数の遅延のうちの選択された1つによって遅延させて、遅延された半レートクロック信号を生成するステップと、c)半レートクロック信号を遅延された半レートクロック信号と結合して、デューティサイクル訂正されたクロック信号を生成するステップとを含む。

10

【0022】

いくつかの実施形態においては、デューティサイクル訂正をどのように調整すべきかを示すデータは、複数の遅延のうちの選択された1つの指示を含む。

【0023】

別の広範な態様によれば、本発明は、複数のシリアル接続のスレーブデバイスを備える構成で使用するためのスレーブデバイスを提供し、このスレーブデバイスは、デューティサイクルに対する調整を指定するマスタデバイスからのコマンドを受け取るためのコマンド入力と、入力クロック信号を受け取るためのクロック入力と、制御コマンドにより、クロック入力からデューティサイクル訂正されたクロック信号を生成するためのデューティサイクル訂正回路と、デューティサイクル訂正されたクロック信号を出力するためのクロック出力とを備える。

20

【0024】

いくつかの実施形態においては、スレーブデバイスはメモリデバイスである。

【0025】

いくつかの実施形態においては、コマンド入力はまた、出力遅延に対する調整を指定するマスタデバイスからのコマンドを受け取るためのものであり、出力遅延調整回路は、そのコマンドにより、デューティサイクル訂正されたクロック信号から、遅延されたクロック信号を生成するためのものであり、デューティサイクル訂正されたクロック信号を出力するためのクロック出力は、遅延されたクロック信号を出力する。

30

【0026】

いくつかの実施形態においては、スレーブデバイスは、コマンドを処理するコマンド処理回路をさらに備え、コマンドは、そのコマンドをデューティサイクル訂正コマンドと見なすコマンド識別子と、デューティサイクルをどのように調整すべきかを示すデータとを含む。

【0027】

いくつかの実施形態においては、スレーブデバイスは、デバイスアドレスレジスタをさらに備え、コマンドは、どのスレーブデバイスがコマンドを実行すべきかを示すデバイスアドレスをさらに含み、スレーブデバイスは、デバイスアドレスがデバイスアドレスレジスタのコンテンツに一致する場合、コマンドを実行するように構成されている。

40

【0028】

いくつかの実施形態においては、デューティサイクル訂正回路は、a)入力クロック信号から半レートクロック信号を生成するクロック分周器回路と、b)半レートクロック信号を複数の遅延のうちの選択された1つによって遅延させて、遅延された半レートクロック信号を生成する遅延回路と、c)半レートクロック信号を遅延された半レートクロック信号と結合して、デューティサイクル訂正されたクロック信号を生成する結合器とを備える。

50

## 【0029】

いくつかの実施形態においては、遅延回路は、 $M \geq 2$ のM個のユニット遅延要素を備え、デューティサイクル訂正回路は、半レートクロック信号を遅延させて、遅延された半レートクロック信号を生成する際に、ユニット遅延要素のうちの何個がアクティブであるべきかの選択に、 $N \geq 1$ のN個の入力線上で受け取られた信号をデコードするN対Mデコーダをさらに備える。

## 【0030】

別の広範な態様によれば、本発明は、少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含む請求項13に記載のスレーブデバイスとして働く複数のシリアル接続のデバイスと、第1のスレーブデバイスおよび最下位のスレーブデバイスに接続されているマスタデバイスであって、第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を出力するように構成されている、マスタデバイスと、最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受け取るためのクロック入力と、第2のクロック信号のデューティサイクルを確定するデューティ検出器と、第2のクロック信号のデューティサイクルに応じて、クロックデューティサイクルに対する調整を指定するデューティサイクル訂正コマンドを生成するコマンドジェネレータとを備えるシステムを提供し、スレーブデバイスとして働く複数のシリアル接続のデバイスの第1のスレーブデバイスは、a)第1のスレーブデバイスの入力クロック信号として、マスタデバイスから第1のクロック信号を受け取り、b)入力クロック信号から出力クロック信号を生成し、スレーブデバイスとして働く複数のシリアル接続のデバイスの他のそれぞのスレーブデバイスは、a)スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの出力クロック信号を受け取り、b)入力クロック信号から出力クロック信号を生成し、複数のシリアル接続のスレーブデバイスのうちの少なくとも1つは、a)デューティサイクル訂正コマンドを受け取り、b)制御コマンドにより、デューティサイクル訂正されたクロック信号を生成し、c)スレーブデバイスの出力クロック信号として、デューティサイクル訂正されたクロック信号を出力する。

## 【0031】

いくつかの実施形態においては、このシステムはメモリシステムであり、それぞれのスレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

## 【0032】

いくつかの実施形態においては、メモリシステムは、第1のクロック信号および第2のクロック信号の間の位相オフセットの量を確定する位相検出器をさらに備え、コマンドジェネレータはまた、位相オフセットの量に応じて、出力遅延調整コマンドを生成し、複数のシリアル接続のスレーブデバイスのうちの第1のスレーブデバイスは、a)第1のスレーブデバイスの入力クロック信号として、マスタデバイスから第1のクロック信号を受け取り、b)入力クロック信号から出力クロック信号を生成し、複数のシリアル接続のスレーブデバイスの他のそれぞのスレーブデバイスは、a)スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの出力クロック信号を受け取り、b)入力クロック信号から出力クロック信号を生成し、複数のシリアル接続のスレーブデバイスのうちの少なくとも1つは、a)出力遅延調整コマンドを受け取り、b)制御コマンドにより、デバイスの入力クロック信号を遅延させることによって、デバイスの出力クロック信号を生成する。

## 【0033】

いくつかの実施形態においては、コマンドジェネレータは、第2のクロック信号のデューティサイクルに応じて、デューティサイクル訂正コマンドを生成し、スレーブデバイスとして働く複数のシリアル接続のデバイスの指定された1つによって実行するためのデューティサイクル訂正コマンドを生成することによって、デューティサイクル訂正コマンドを出力するように構成されている。

## 【0034】

いくつかの実施形態においては、コマンドジェネレータは、第2のクロック信号のデューティサイクルに応じて、デューティサイクル訂正コマンドを生成し、スレーブデバイス

10

20

30

40

50

として働く複数のシリアル接続のデバイスのすべてによって実行するためのデューティサイクル訂正コマンドを生成することによって、デューティサイクル訂正コマンドを出力するように構成されている。

【0035】

いくつかの実施形態においては、デューティサイクル訂正コマンドを受け取ることは、そのコマンドをデューティサイクル訂正コマンドと見なすコマンド識別子を含み、かつデューティサイクルをどのように調整すべきかを示すデータを含むコマンドを受け取ることを含む。

【0036】

1つの広範な態様によれば、本発明は、複数のシリアル接続のスレーブデバイスのうちのあるスレーブデバイスにおける方法を提供し、この方法は、スレーブデバイスによって出力される少なくとも1つの信号に印加すべき遅延をスレーブデバイスがどのように調整すべきかを指定するマスタデバイスからのコマンドを受け取るステップと、少なくとも1つの入力信号を受け取るステップであって、少なくとも1つの入力信号は、少なくとも入力クロック信号を含む、ステップと、少なくとも1つの入力信号のそれぞれごとに、コマンドにより入力信号の遅延されたバージョンを生成するステップと、入力信号の遅延されたバージョンを出力するステップとを含む。

【0037】

いくつかの実施形態においては、スレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

【0038】

いくつかの実施形態においては、この方法は、データ出力信号を出力するステップを含み、入力信号のうちの少なくとも1つは、データ入力信号を含み、データ入力信号の遅延されたバージョンを出力するステップは、データ出力信号を出力するステップの一部として実行され、それにより、a)時には、データ出力信号は、データ入力信号の前記遅延されたバージョンになり、b)時には、データ出力信号は、コマンドにより、スレーブデバイスにとって局的に生成された信号に遅延を印加した後に、スレーブデバイスにとって局的に生成された信号の遅延されたバージョンになる。

【0039】

いくつかの実施形態においては、スレーブデバイスによって出力される少なくとも1つの信号に印加すべき遅延に対する調整を指定するマスタデバイスからのコマンドを受け取るステップは、そのコマンドを出力遅延調整コマンドと見なすコマンド識別子を含むコマンドを受け取るステップを含み、そのコマンドは、遅延をどのように調整すべきかを示すデータをさらに含む。

【0040】

いくつかの実施形態においては、コマンドを受け取るステップは、スレーブデバイスとして働くどのデバイスが、コマンドを実行すべきかを示すデバイスアドレスを受け取るステップをさらに含む。

【0041】

いくつかの実施形態においては、この方法は、コマンドがスレーブデバイスのデバイスアドレスに一致するデバイスアドレスを有する場合、コマンドにより、少なくとも1つの入力信号のそれぞれごとに、入力信号の遅延されたバージョンを生成するステップを実行するステップと、コマンドがブロードキャストデバイスアドレスであるデバイスアドレスを有する場合、コマンドにより、少なくとも1つの入力信号のそれぞれごとに、入力信号の遅延されたバージョンを生成するステップを実行するステップとをさらに含む。

【0042】

いくつかの実施形態においては、それぞれの入力信号ごとに、入力信号の遅延されたバージョンを生成するステップは、a)複数の遅延のうちの選択された1つによって、入力信号を遅延させて、入力信号の遅延されたバージョンを生成するステップを含む。

【0043】

10

20

30

40

50

いくつかの実施形態においては、遅延をどのように調整すべきかを示すデータは、複数の遅延のうちの選択された1つの指示を含む。

【0044】

いくつかの実施形態においては、複数の入力信号は、クロック信号と、コマンドストローブ信号と、データストローブ信号と、コマンドおよびデータを含むデータ信号とを含む。

【0045】

別の広範な態様によれば、本発明は、マスタデバイスと、少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含むスレーブデバイスとして働く複数のシリアル接続のデバイスとを備えるメモリシステムにおける方法を提供し、この方法は、マスタデバイスにおいて、a)少なくとも1つの出力信号を出力するステップであって、少なくとも1つの出力信号は、第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を含む、ステップと、b)最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受け取るステップと、c)第1のクロック信号および第2のクロック信号の間の位相オフセットの量を確定するステップと、d)第1のクロック信号および第2のクロック信号の間の位相オフセットに応じて、出力遅延調整コマンドを生成し、出力遅延調整コマンドを出力するステップとを含む。

10

【0046】

いくつかの実施形態においては、それぞれのスレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

20

【0047】

いくつかの実施形態においては、この方法は、スレーブデバイスとして働く複数のシリアル接続のデバイスのうちの第1のスレーブデバイスにおいて、a)第1のスレーブデバイスの対応する少なくとも1つの入力信号として、マスタデバイスから少なくとも1つの出力信号を受け取るステップと、b)それぞれの入力信号ごとに、入力信号に基づいて出力信号を生成するステップと、スレーブデバイスとして働く複数のシリアル接続のデバイスの他のそれぞれのスレーブデバイスにおいて、a)スレーブデバイスの少なくとも1つの入力信号に対応する先行するスレーブデバイスの出力信号を受け取るステップと、b)それぞれの入力信号ごとに、入力信号に基づいて出力信号を生成するステップと、スレーブデバイスのうちの少なくとも1つに、a)出力遅延調整コマンドを受け取るステップと、b)出力遅延調整コマンドにより、入力信号の遅延されたバージョンを生成することによって、出力信号を生成するステップとをさらに含む。

30

【0048】

いくつかの実施形態においては、マスタデバイスの少なくとも1つの出力信号は、複数の出力信号を含む。

【0049】

いくつかの実施形態においては、遅延調整コマンドを生成するステップは、複数のシリアル接続のスレーブデバイスのうちの指定された1つによって実行するための遅延調整コマンドを生成するステップを含む。

40

【0050】

いくつかの実施形態においては、遅延調整コマンドを生成するステップは、複数のシリアル接続のスレーブデバイスのすべてによって実行するための遅延調整コマンドを生成するステップを含む。

【0051】

いくつかの実施形態においては、出力遅延調整コマンドにより、入力信号の遅延されたバージョンを生成するステップは、複数の遅延のうちの選択された1つによって遅延された入力信号の遅延されたバージョンを生成するステップを含む。

【0052】

いくつかの実施形態においては、遅延調整コマンドを生成するステップは、そのコマンドを出力遅延調整コマンドと見なすコマンド識別子を含み、かつ遅延をどのように調整す

50

べきかを示すデータを含むコマンドを生成するステップを含む。

【0053】

いくつかの実施形態においては、遅延をどのように調整すべきかを示すデータは、複数の遅延のうちの選択された1つの指示を含む。

【0054】

いくつかの実施形態においては、この方法は、位相オフセットが許容可能になるまで、マスタデバイスが、一度に、1つのスレーブデバイスにおける1つのユニット遅延要素に遅延を加えることによって、遅延を調整する出力遅延調整コマンドを出力するステップをさらに含む。

【0055】

いくつかの実施形態においては、複数の入力信号は、クロック信号と、コマンドストローブ信号と、データストローブ信号と、コマンドおよびデータを含むデータ信号とを含む。

【0056】

別の広範な態様によれば、本発明は、複数のシリアル接続のスレーブデバイスを備える構成で使用するためのスレーブデバイスを提供し、このスレーブデバイスは、出力遅延調整をどのように実行すべきかを指定するマスタデバイスからのコマンドを受け取るためのコマンド入力と、入力クロック信号を受け取るためのクロック入力と、コマンドにより、クロック入力から、遅延されたクロック信号を生成するための出力遅延調整回路と、遅延されたクロック信号を出力するためのクロック出力とを備える。

10

20

30

40

50

いくつかの実施形態においては、スレーブデバイスはメモリデバイスである。

【0058】

いくつかの実施形態においては、スレーブデバイスは、コマンドを処理するコマンド処理回路を備え、コマンドは、そのコマンドを出力調整コマンドと見なすコマンド識別子を含み、出力遅延をどのように調整すべきかを示すデータを含む。

【0059】

いくつかの実施形態においては、スレーブデバイスは、デバイスアドレスレジスタをさらに備え、コマンドは、どのスレーブデバイスがコマンドを実行すべきかを示すデバイスアドレスをさらに含み、スレーブデバイスは、デバイス識別子が、デバイスアドレスレジスタのコンテンツに一致する場合、コマンドを実行するように構成されている。

【0060】

いくつかの実施形態においては、出力遅延調整回路は、入力クロック信号を含めて複数の入力信号のそれぞれごとに、複数の遅延のうちの選択された1つによって、入力信号を遅延させて、入力信号の遅延されたバージョンを生成する遅延回路を備える。

【0061】

いくつかの実施形態においては、それぞれの出力遅延回路は、 $M \geq 2$ のM個のユニット遅延要素を備え、デューティサイクル訂正回路は、入力信号の遅延されたバージョンを生成する際に、ユニット遅延要素のうちの何個がアクティブであるべきかの選択に、 $N \geq 1$ のN個の入力線上で受け取られた信号をデコードするN対Mデコーダをさらに備える。

【0062】

別の広範な態様によれば、本発明は、少なくとも第1のスレーブデバイスおよび最下位のスレーブデバイスを含む複数のシリアル接続のスレーブデバイスと、第1のスレーブデバイスおよび最下位のスレーブデバイスに接続されているマスタデバイスであって、第1のスレーブデバイスの入力クロック信号として機能する第1のクロック信号を出力するように構成されている、マスタデバイスと、最下位のスレーブデバイスの出力クロック信号である第2のクロック信号を受け取るためのクロック入力と、第1のクロック信号および第2のクロック信号の間の位相オフセットの量を確定する位相検出器と、位相オフセットの量に応じて、出力遅延調整コマンドを生成するコマンドジェネレータとを備えるメモリシステムを提供し、複数のシリアル接続のスレーブデバイスうちの第1のスレーブデバイス

は、a)第1のスレーブデバイスの入力クロック信号として、マスタデバイスから第1のクロック信号を受け取り、b)入力クロック信号から出力クロック信号を生成し、複数のシリアル接続のスレーブデバイスの他のそれぞれのスレーブデバイスは、a)スレーブデバイスの入力クロック信号として、先行するスレーブデバイスの出力クロック信号を受け取り、b)入力クロック信号から出力クロック信号を生成し、複数のシリアル接続のスレーブデバイスのうちの少なくとも1つは、a)出力遅延調整コマンドを受け取り、b)制御コマンドにより、デバイスの入力クロック信号を遅延させることによって、デバイスの出力クロック信号を生成する。

【0063】

いくつかの実施形態においては、このシステムはメモリシステムであり、それぞれのスレーブデバイスはメモリデバイスであり、マスタデバイスはメモリコントローラである。

【0064】

いくつかの実施形態においては、コマンドジェネレータは、複数のシリアル接続のスレーブデバイスのうちの指定された1つによって実行するための出力遅延調整コマンドを生成するように構成されている。

【0065】

いくつかの実施形態においては、コマンドジェネレータは、複数のシリアル接続のスレーブデバイスのすべてによって実行するための出力遅延調整コマンドを生成するように構成されている。

【0066】

いくつかの実施形態においては、出力遅延調整コマンドを生成することは、そのコマンドを出力遅延調整コマンドと見なすコマンド識別子を含み、かつ出力遅延をどのように調整すべきかを示すデータを含むコマンドを生成することを含む。

【0067】

クロックデューティサイクル訂正および/または位相同期化の方法ならびに装置が提供され、それらには、典型的に、環状構成で接続されているメモリコントローラおよび複数のメモリチップを含むシリアル接続のメモリシステムに対するDLLまたはPLLが必要でない。いくつかの実施形態においては、メモリコントローラは、環状に移動した後のクロック信号の位相およびデューティサイクルを検出するための位相/デューティサイクル検出器を有し、それぞれのメモリデバイスは、クロックの位相および/またはデューティサイクルを調整するために使用される1つまたは複数のコントローラプログラミング可能遅延線を有する。これらは、メモリコントローラによって検出された位相およびデューティサイクルが許容可能になるまで、メモリコントローラから送られるコマンドによって調整される。

【0068】

本明細書に説明する方法および装置は、隣接するデバイス間の共通のインターフェースを有するシリアル接続の構成で、スレーブデバイスとして任意の種類の半導体集積回路デバイスを有する任意の種類の半導体集積回路システムに適用可能である。集積回路のタイプの例は、中央処理装置と、グラフィックス処理装置と、ディスプレイコントローラICと、ディスクドライブICと、NAND Flash EEPROM、NOR Flash EEPROM、AND Flash EEPROM、D iNOR Flash EEPROM、Serial Flash EEPROM、DRAM、SRAM、ROM、EPROM、FRAM、MRAM、PCRAMなどのようなメモリデバイスとを含む。

【図面の簡単な説明】

【0069】

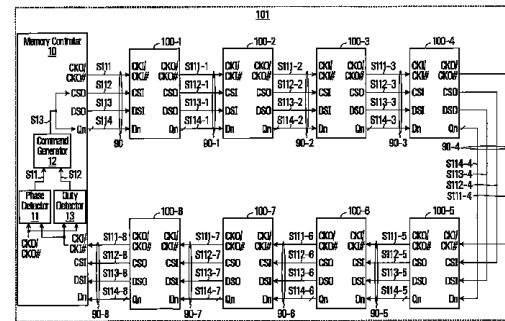

【図1】コントローラプログラミング可能デューティサイクル訂正スキームを有するシリアル接続のメモリシステムのシステムブロック図である。

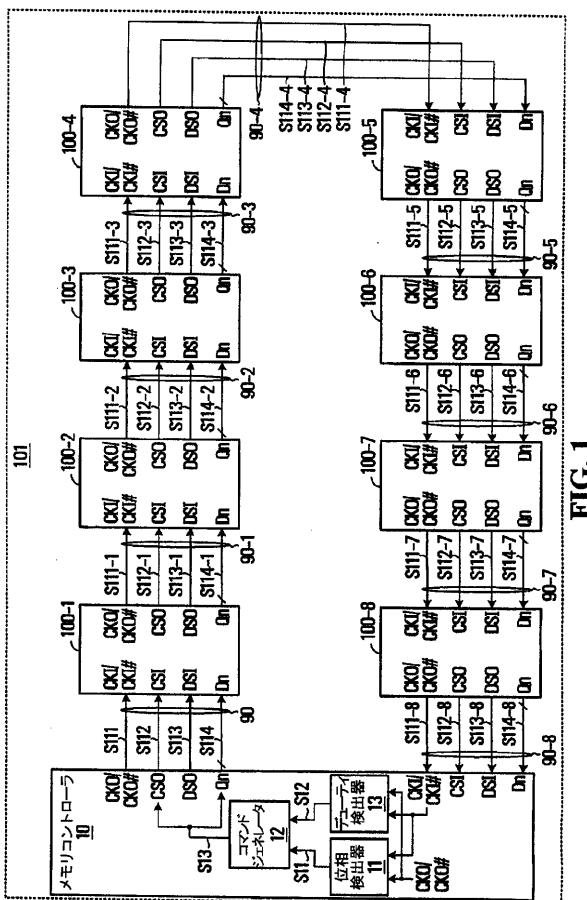

【図2】コントローラプログラミング可能デューティサイクル訂正スキームを有するメモリデバイスのブロック図である。

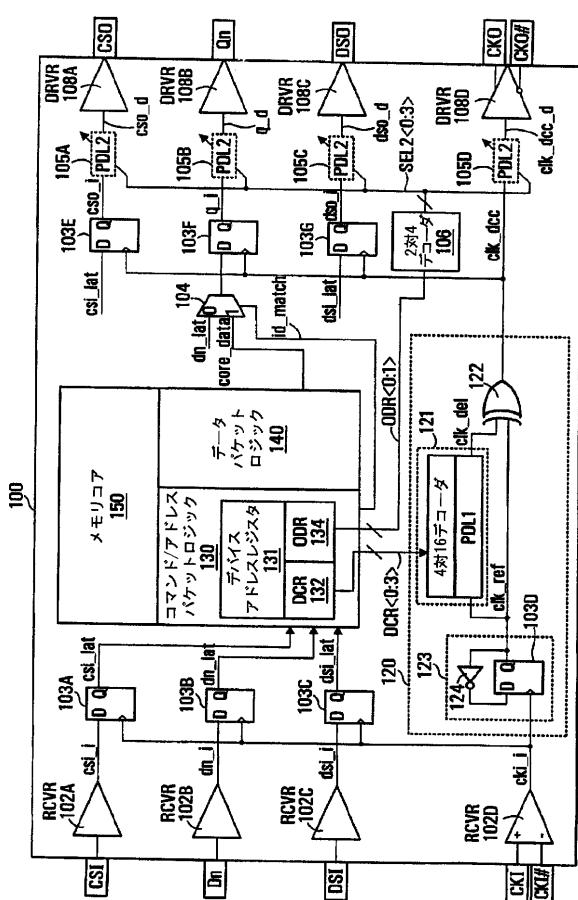

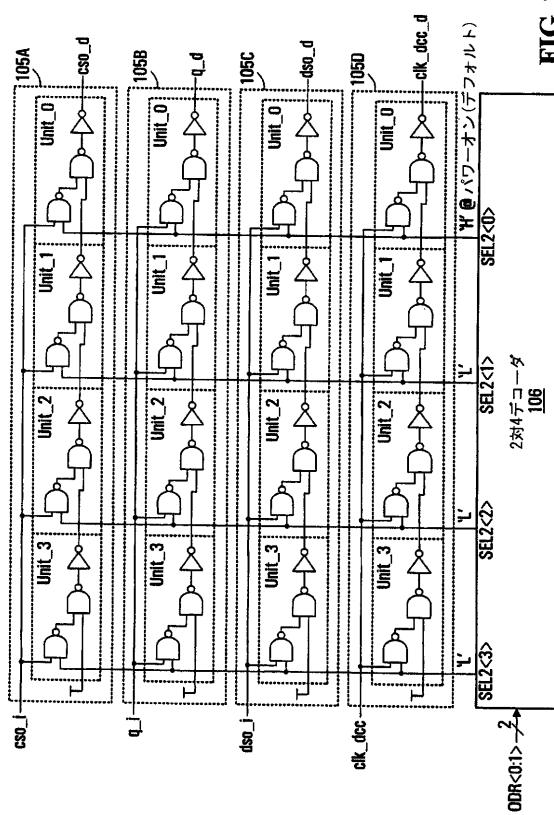

【図3】デューティサイクル訂正のためのプログラミング可能遅延線のブロック図である。

10

20

30

40

50

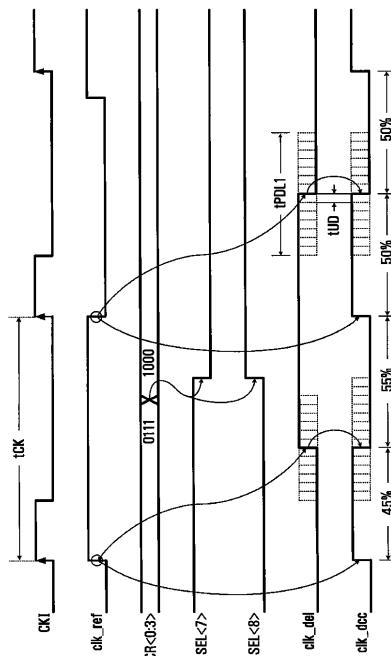

【図4】コントローラプログラミング可能デューティサイクル訂正のタイミング図である。

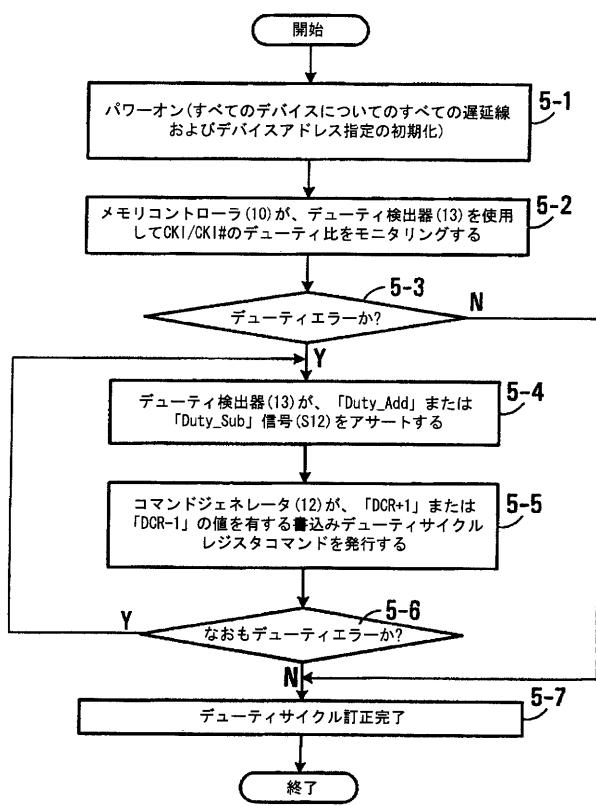

【図5】デューティサイクル訂正の方法の流れ図である。

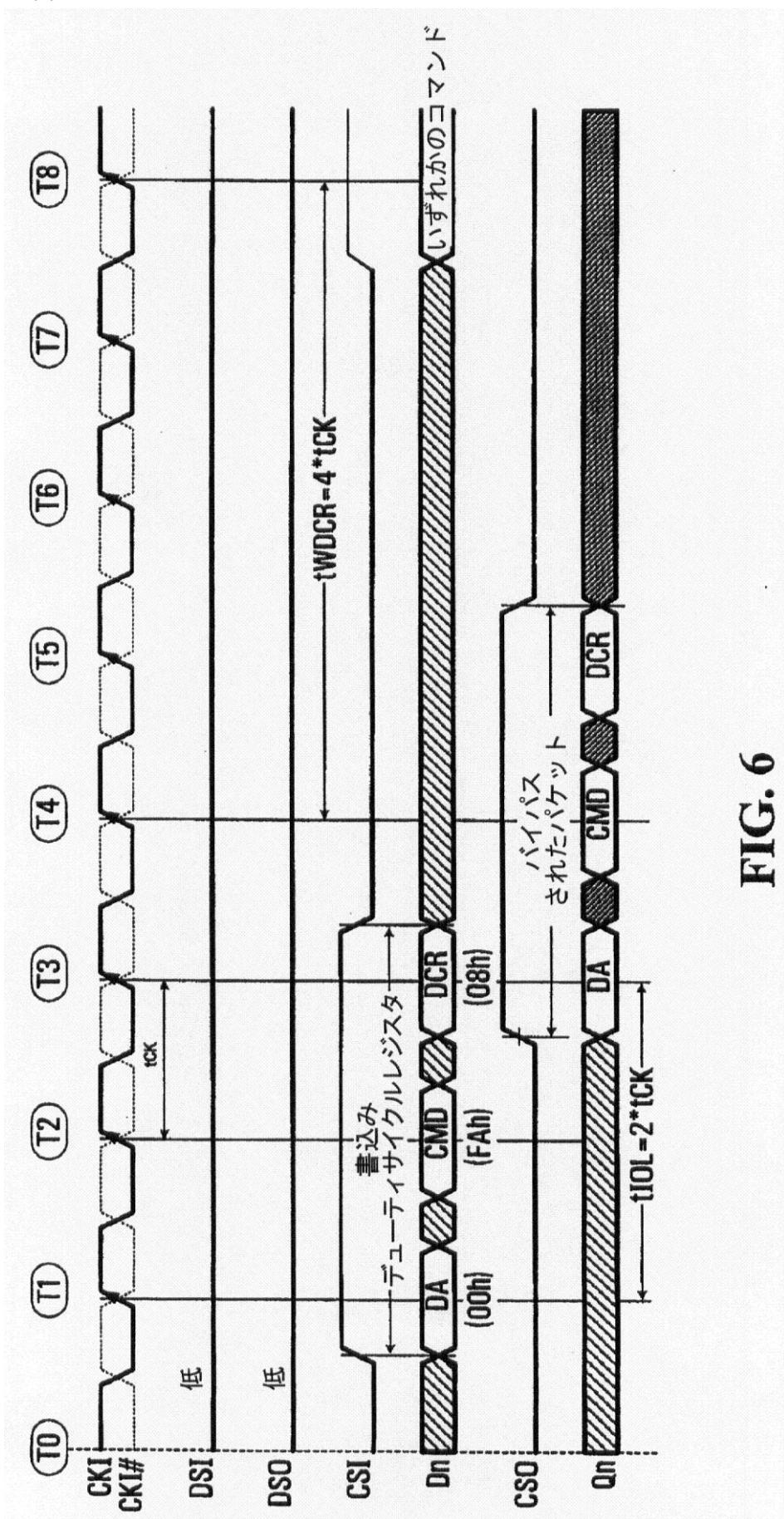

【図6】書込みデューティサイクルレジスタコマンドに関するタイミング図である。

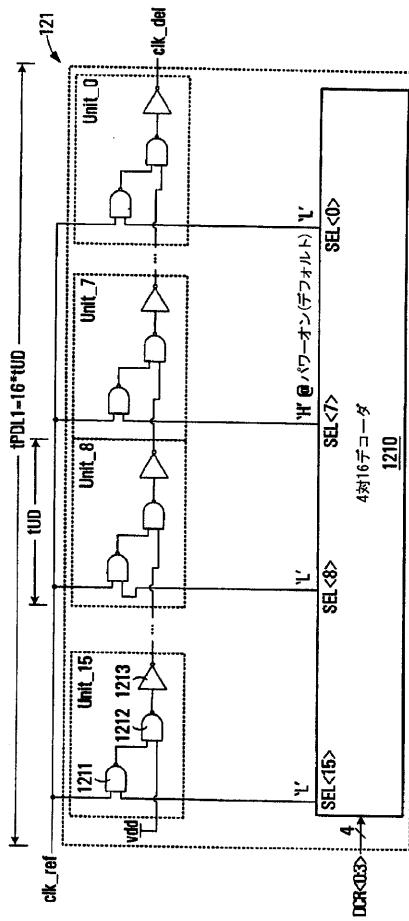

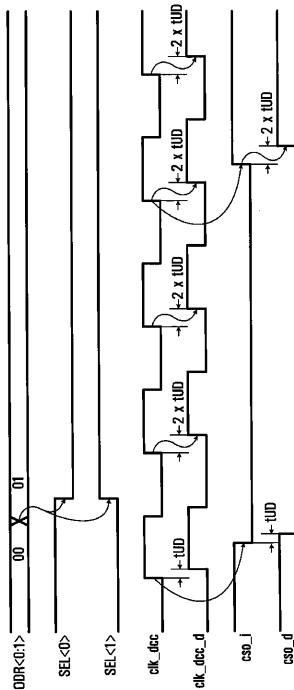

【図7】出力遅延調整のためのプログラミング可能遅延線のブロック図である。

【図8】コントローラプログラミング可能出力遅延調整のタイミング図である。

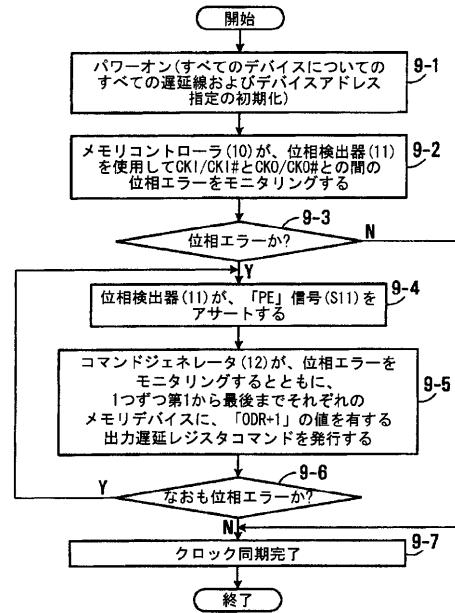

【図9】出力遅延調整を実行する方法の流れ図である。

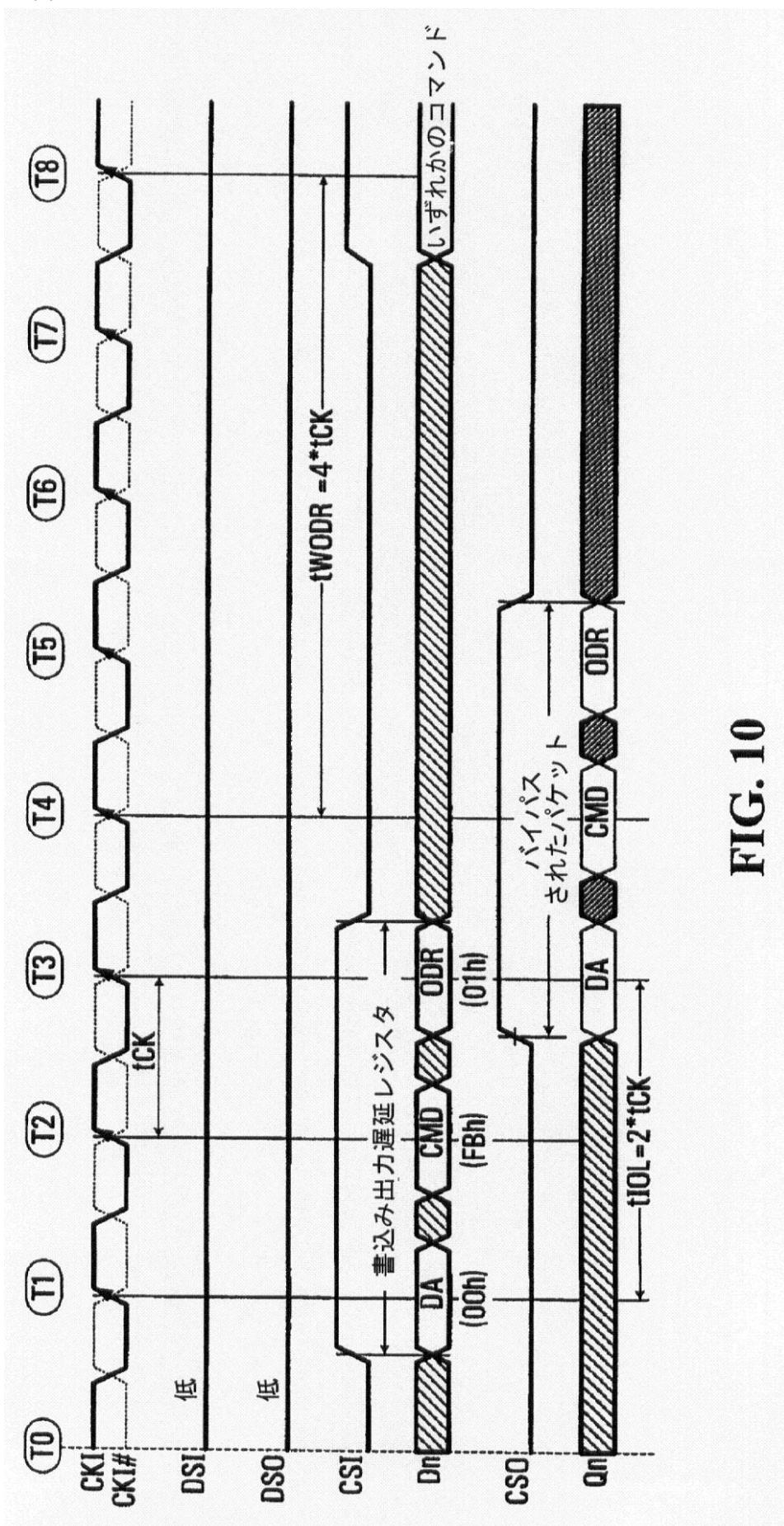

【図10】書込み出力遅延レジスタコマンドに関するタイミング図である。

【発明を実施するための形態】

【0070】

本発明のサンプル実施形態の以下の詳細な説明では、本明細書の一部を形成する添付の図面を参照し、その中で、本発明が実施可能な具体的なサンプル実施形態を例として示す。これらの実施形態を、当業者が本発明を実施できるように十分詳細に説明し、他の実施形態が使用可能であること、ならびに本発明の範囲から逸脱することなく、論理的な、機械的な、電気的な、および他の変更がなされ得ることを認識すべきである。そのため、以下の詳細な説明を、限定する意味で解釈すべきではなく、本発明の範囲は、添付の特許請求の範囲によって定められる。

【0071】

背景において参照したメモリシステム構成のうちのいくつかは、システムクロック分散のための共有バストポロジを使用し、それを「共通クロックシステム」または「マルチドロップクロッキングシステム」と呼ぶ。システムクロックが、あまりに多くの並列でのメモリデバイスに印加され、クロック信号がクロック源から、典型的にはメモリコントローラから、あまりに離れて移動する場合、最大動作クロック周波数は、クロック信号の総負荷と、クロック信号がメモリシステムの物理的レイアウト内を移動する距離とによって制限される場合がある。

【0072】

背景において参照したメモリシステム構成のうちのいくつかは、一方は、先行するデバイスまたはコントローラから受け取られる入力クロックであり、他方は、次のデバイスに伝送される出力クロックである、メモリデバイスにおける2つのクロック信号を同期化するために、それぞれのメモリデバイスにおけるDLLまたはPLLを特徴とするポイントツーポイントシリアル接続のクロッキングアーキテクチャを使用する。しかし、それぞれのメモリデバイスにオンチップのDLLまたはPLLを含むことは、かなりの量の電力消費の原因になり得る。オンチップDLLまたはPLLにより、(マルチチップのスタッキングまたはパッケージなどの様々な相互接続負荷および種々のワイヤボンディング負荷によって生じる)様々なチップツーチップのクロック遅延は、多数のシリアル接続のデバイス全体にわたって蓄積し、システム動作に許容できない場合がある。

【0073】

次に、図1を参照すると、コントローラプログラミング可能デューティサイクル訂正スキームを使用する全体的に101で示すシリアル接続のメモリシステムのシステムブロック図を示している。メモリシステム101は、第1のメモリデバイス100-1に接続されているマスタデバイスとしてメモリコントローラ10を含む。メモリデバイス100-1は、環状構成で接続されているデバイス100-1から100-8を含む一連のスレーブデバイスのうちの第1のものであり、最下位のデバイス100-8は、メモリコントローラ10に戻って接続されている。図示の例では、高度に多重化された単方向のポイントツーポイントのバスアーキテクチャが、メモリコントローラ10からのコマンド、アドレス、およびデータなどの情報をメモリデバイス100-1から100-8に転送するように設けられている。このバスアーキテクチャは、メモリコントローラ10から第1のメモリデバイス100-1へのリンク90と、隣接するメモリデバイスのそれぞれの対の間の各リンクとを含み、これらは、リンク90-1から90-7と、最下位のメモリデバイス100-8およびメモリコントローラ10の間のリンク90-8とを含む。

【0074】

10

20

30

40

50

図示の例では、それぞれのリンクは、先行するデバイス(メモリコントローラ10、またはメモリデバイス)によって出力されて、後続のデバイスによって受け取られる一連の信号を含む。それぞれのリンクは、先行するデバイスの一連の出力ポートと、後続のデバイスの一連の入力ポートと、出力ポートおよび入力ポートの間の一連の物理的な相互接続とを含む。便宜上、出力ポートには、それらが outputする信号と同じ名称を与えることにし、入力ポートには、それらが受け取る信号と同じ名称を与えることにする。図示の例では、先行するデバイスの信号(および出力ポート)を、CSO(Command Strobe Output)と、DSO(Data Strobe Output)と、Qn(Data Output)と、CK0/CK0#(差動クロック出力信号)と呼ぶ。後続のデバイスの対応する信号(および入力ポート)を、CSI(Command Strobe Input)と、DSI(Data Strobe Input)と、Dn(Data Input)と、CK1/CK1#(差動クロック入力信号)と呼ぶ。よりよく理解するために、かつ簡単にするために、図示していない追加のポートまたは信号(例えば、CE#(チップイネーブル)またはRST#(リセット)、あるいは電源ピン)がある場合がある。物理的な相互接続は、差動クロック信号に対するS111、S111-1からS111-8、コマンドストローブに対するS112、S112-1からS112-8、データストローブに対するS113、S113-1からS113-8、データに対するS114、S114-1からS114-8の差動クロックバスを含む。

10

## 【0075】

いくつかの実施形態においては、データ出力Qnおよびデータ入力Dnは、差動データ幅が、1ビットLink設定についてはn=0であり、2ビットLink設定についてはn=0、1であり、4ビットLink設定についてはn=0、1、2、3であり、8ビットLink設定についてはn=0、1、2、3、4、5、6、7であることなどが可能である。いくつかの実施形態においては、リンクの幅は、デバイスパッケージの利用可能なデータ入力および出力のピンの1、2、4、または8を使用するように、リンク構成レジスタを通じてプログラミング可能である。この機能は、これらのメモリデバイスがすべて、同じリンク幅を使用するようにプログラミングされるならば、より小さいか、またはより大きい最大リンク幅を有するデバイスとともに環状構成でそれらが動作することを可能にする。例えば、その全体を参照によって本明細書に組み込む「Switching Method of Link and Bit Width」(国際公開第2008/070978号)を参照されたい。

20

## 【0076】

CK1/CK1#は、入力クロックである。CSIによって示されるDnポート上のCommand/Address Packetは、CK1の立上がりエッジか、またはCK1#の立下がりエッジ上でラッチされる。DSIによって示されるDn上のWrite Data Packetは、CK1の立上がりエッジか、またはCK1#の立下がりエッジ上でラッチされる。

30

## 【0077】

CK0/CK0#は、CK1/CK1#の遅延されたバージョンである出力クロックである。CSO、DSO、およびQnの信号は、CK0の立上がりエッジか、またはCK0#の立下がりエッジに参照され、例えば、DSOによって示されるQn上のRead Data Packetは、CK0の立上がりエッジか、またはCK0#の立下がりエッジにおいて参照される。

## 【0078】

Command Strobe Input(CSI)がHIGHであるとき、Dnを介するCommand/Address Packetsは、CK1の立上がりエッジか、またはCK1#の立下がりエッジ上でラッチされる。

40

## 【0079】

Command Strobe Output(CSO)は、CSIのエコー信号である。それは、特定の実装形態において、CK0の立上がりエッジにか、またはCK0#の立下がりエッジに参照される2つのクロックサイクル待ち時間である待ち時間tIOLによりCSI遷移をエコーする。2つのクロックサイクル待ち時間は、実装形態の詳細であり、より概括的には、それは、所与の設計に適切な任意の数のクロックサイクルになり得る。

## 【0080】

メモリデバイスが「Read-Mode」にあり、Data Strobe Input(DSI)がHIGHであるとき、それは、読み取りデータ出力経路およびQnバッファ(図示せず)をイネーブルする。DSIがLOWである場合、Qnバッファは、アクセスされた以前のデータを保持する。メモリデバイ

50

スが「Write-Mode」にあり、DSIがHIGHである場合、それは、Dnバッファーをイネーブルし、CKIの立上がりエッジか、またはCKI#の立下がりエッジ上のWrite Data Packetを受ける。

#### 【0081】

Data Strobe Output(DSO)は、DSIのエコー信号である。それは、CKOの立上がりエッジにか、またはCKO#の立下がりエッジに参照される待ち時間tIOLによりDSI遷移をエコーする。前述したように、tIOLは、特定の実装形態において2つのクロックサイクルである。

#### 【0082】

Data Input信号Dn(n=0、1、2、3、4、5、6、または7)は、コマンド、アドレス、および/または入力データ情報を伝える。チップが、「1ビットLinkモード」で構成されている場合、D0は、唯一の有効信号であり、8つのクロックサイクルにおいて1バイトのパケットを受け取る。チップが、「2ビットLinkモード」で構成されている場合、D0&D1は、有効信号であり、4つのクロックサイクルで1バイトのパケットを受け取る。チップが「4ビットLinkモード」で構成されている場合、D0、D1、D2&D3は、有効信号であり、2つのクロックサイクルで1バイトのパケットを受け取る。チップが「8ビットLinkモード」で構成されている場合、D0、D1、D2、D3、D4、D5、D6&D7はすべて、有効信号であり、1つのクロックサイクルで1バイトのパケットを受け取る。

10

#### 【0083】

Data Output信号Qn(n=0、1、2、3、4、5、6、または7)は、読み取り動作中に出力データを伝えるか、またはDn上で受け取られたコマンド、アドレス、もしくは入力データをバイパスする。チップが「1ビットLinkモード」で構成されている場合、Q0は、唯一の有効信号であり、8つのクロックサイクルで1バイトのパケットを伝送する。チップが「2ビットLinkモード」で構成されている場合、Q0&Q1は、有効信号であり、4つのクロックサイクルで1バイトのパケットを伝送する。チップが「4ビットLinkモード」で構成されている場合、Q0、Q1、Q2&Q3は、有効信号であり、2つのクロックサイクルで1バイトのパケットを伝送する。チップが「8ビットLinkモード」で構成されている場合、Q0、Q1、Q2、Q3、Q4、Q5、Q6&Q7はすべて、有効信号であり、1つのクロックサイクルで1バイトのパケットを伝送する。

20

#### 【0084】

デバイスの隣接する対と、シリアル接続のメモリシステムとの間の伝送用にそれらが含むポートの数ならびに信号は、実装形態の詳述であり、必ずしも図1に示すものであるとは限らないことをはっきりと認識すべきである。より概括的には、少なくともクロック信号が、連続するデバイスのそれぞれの対の間で伝達される。連続するデバイス間で伝達される追加の信号がある場合があり、これらの具体的な例は、上述済みである。また、メモリデバイスの特定の数、図1の例での8つは、実装形態の具体的な詳細であることも留意する。任意の適切な数のデバイスが、シリアル接続のアーキテクチャにおいて相互接続可能である。この文脈における表現「シリアル接続の」は、順々のメモリデバイスのシリアル構成を示しており、本質的には、直列であっても、または並列であってもよい隣接するデバイスのそれぞれの対の間のリンクの性質を示していないことに留意されたい。

30

#### 【0085】

メモリコントローラ10は、位相検出器11、デューティ検出器13、およびコマンドジェネレータ12を含む。いくつかの実施形態においては、メモリコントローラ10は、位相検出器11のみを含み、その場合には、出力遅延調整のみが実行される。いくつかの実施形態においては、メモリコントローラ10は、デューティ検出器13のみを含み、その場合には、デューティサイクル訂正のみが実行される。いくつかの実施形態においては、位相検出器11およびデューティ検出器13はともに含まれ、その場合には、出力遅延調整およびデューティサイクル訂正はともに実行される。この最後のケースが、続く詳細な説明で想定される。位相検出器11およびデューティ検出器13は、信号バスS11およびS12をそれぞれ通じてコマンドジェネレータ12に接続されている。コマンドジェネレータ12は、CS0ポートおよびQnポートに接続されている出力信号バスS13を有し、それを通じてコマンドを出力すること

40

50

が可能である。

【0086】

メモリコントローラ10は、そのポートCK0/CK0#から差動クロックバスS111を駆動し、8つのメモリデバイス100-1～100-8はすべて、差動クロックバスを、一連のフロースルーのやり方で、前のデバイスのCK0/CK0#ポートからそれら自体のクロックポートCK1/CK1#を通じて受け取る。メモリコントローラ10は、そのポートCS0、DS0、およびQnをそれぞれ通じて、3つ異なるバスS112、S113、およびS114を駆動する。第1のメモリデバイス100-1は、3つのバスS112、S113、およびS114を、そのポートCSI、DSI、およびDnをそれぞれ通じて受け取り、第1のメモリデバイス100-1は、3つの対応するバスS112-1、S113-1、およびS114-1を2つのクロックサイクルの待ち時間( $=t_{IOL}$ )により、その出力ポートCS0、DS0、およびQnをそれぞれ通じて再駆動する(エコーする)。第2のメモリデバイス100-2は、3つのバスS112-1、S113-1、およびS114-1を、その入力ポートCSI、DSI、およびDnをそれぞれ通じて受け取る。この手法は、8つのメモリデバイス100-1～100-8のすべてに適用し、最終バスS112-8、S113-8、およびS114-8は、メモリコントローラの入力ポートCSI、DSI、およびDnをそれぞれ通じて、メモリコントローラ10に戻って接続されている。10

【0087】

動作中、デューティサイクル訂正の場合、デューティ検出器13は、環状にデバイス100-1から100-8のすべての間を通過した後のクロック入力であるCK1/CK1#のデューティ比をモニタリングする。デューティ検出器13がCK1/CK1#からデューティエラー、すなわち、所望のデューティサイクルからデューティサイクルにおける偏差を検出する場合、それは、デューティサイクルが所望のデューティサイクルよりも短く、長くすべきであることを示す「Duty\_Add」か、またはデューティサイクルが所望のデューティサイクルよりも長く、短くすべきであることを示す「Duty\_Sub」かのいずれかを、信号バスS12を通じてアサートする。それに応答して、コマンドジェネレータ12は、適切な「Write Duty Cycle Register」コマンドパケットを生成する。20

【0088】

動作中、出力遅延調整の場合、位相検出器11は、CK1/CK1#の位相をモニタリングする。位相検出器11がCK1/CK1#と、CK0/CK0#との間の位相エラー(PE)を検出する場合、それは、信号バスS11を通じて「PE」信号をアサートする。それに応答して、コマンドジェネレータ12は、適切な「Write Output Delay Register」コマンドパケットを生成する。30

【0089】

コマンドジェネレータ12は、S11およびS12上の受信信号により適切なコマンドパケットを発行し、信号バスS13、およびCS0ポート、Qnポートを通じてコマンド情報を送る。

【0090】

次に、図2を参照すると、図1のメモリデバイス100-1から100-8の例示的な実装形態のブロック図を示している。全体的に100で示すデバイスは、メモリコア150と、コマンド/アドレスパケットロジック130と、データパケットロジック140と、デューティサイクル訂正ロジック120とを含む。メモリコア150は、メモリセルアレイの単一のバンクであってよく、または設計変更に応じて、メモリセルアレイの複数のバンクになり得る。データパケットロジック140は、すべての必要なデータ転送情報を処理し、保存する。コマンド/アドレスパケットロジック130は、以下に詳述する内部制御信号「csi\_lat」により、内部信号「dn\_lat」を通じて入ってくるすべてのコマンド命令および/またはアドレス情報を処理する。40

【0091】

クロック入力処理

デバイス100は、例えば、差動クロック入力CK1&CK1#を扱う差動タイプの入力バッファーであることが可能なCK1/CK1#に対するクロック入力受信器102Dを含む。クロック入力受信器102Dは、CK1/CK1#信号の外部インターフェースレベルを内部クロック信号「cki\_i」の内部ロジックレベルに変換する。内部クロック信号「cki\_i」は、様々な動作に向けて、他の内部ロジックブロックにおいて使用可能である。詳細に後述するように、デューティ

10

20

30

40

50

イサイクル訂正ロジック120は、内部クロック信号`cki_i`を取り込み、デューティサイクル訂正されたクロック信号`clk_dcc`を生成する。デューティサイクル訂正されたクロック信号「`clk_dcc`」は、コントローラプログラミング可能遅延線PDL2、105Dによって遅延され、その遅延された信号「`clk_dcc_d`」は、最終的に、出力ドライバブロック108Dの入力ポートに駆動され、それは外部クロック出力信号CK0/CK0#を出力する。

#### 【0092】

##### コマンドストローブ入力処理

デバイス100は、CSI入力信号からバッファーされた信号「`csi_i`」を生成するコマンドストローブ受信器102Aを含む。バッファーされた信号`csi_i`は、D型フリップフロップ103AのDポートに接続される。フリップフロップ103Aは、クロック信号「`cki_i`」によって駆動され、「`cki_i`」のあらゆる立上がりエッジで「`csi_i`」信号のステータスをラッチする。ラッチされた信号「`csi_lat`」は、コマンド/アドレスパケットロジック130に供給され、また、別のフリップフロップ103EのDポートにも供給され、そのクロック入力ポートは、デューティ訂正されたクロック信号`clk_dcc`によって駆動される。フリップフロップ103Eの出力信号「`cso_i`」は、コントローラプログラミング可能遅延線PDL2、105Aによって遅延され、その遅延された信号「`cso_d`」は、最終的に、出力ドライバブロック108Aの入力ポートに駆動され、それは、次いで、外部信号CS0を出力する。フリップフロップロジック103Aおよび103Eの2つの段階は、2つのクロックサイクルの入力から出力の待ち時間(=t<sub>OL</sub>)をもたらして、CSIからCS0にバイパスする。

10

#### 【0093】

##### データストローブ入力処理

デバイス100は、DSI入力信号から、バッファーされた信号「`dsi_i`」を生成するデータストローブ入力受信器102Cを含む。バッファーされた信号「`dsi_i`」は、D型フリップフロップ103CのDポートに接続される。フリップフロップ103Cは、クロック信号「`cki_i`」によって駆動され、「`cki_i`」のあらゆる立上がりエッジで「`dsi_i`」信号のステータスをラッチする。ラッチされた信号「`dsi_lat`」は、コマンド/アドレスパケットロジック130と、データパケットロジック140とに供給され、また、別のフリップフロップ103GのDポートにも供給され、そのクロック入力ポートは、デューティ訂正されたクロック信号`clk_dcc`によって駆動される。フリップフロップ103Gの出力信号「`dso_i`」は、コントローラプログラミング可能遅延線PDL2、105Cによって遅延され、その遅延された信号「`dso_d`」は、最終的に、出力ドライバブロック108Cの入力ポートに駆動され、それは、外部信号DS0を出力する。フリップフロップロジック103Cおよび103Gの2つの段階は、2つのクロックサイクルの同じ入力から出力の待ち時間(=t<sub>OL</sub>)をもたらして、DSIからDS0にバイパスする。

20

30

#### 【0094】

##### データ処理

デバイス100は、外部信号Dnを受け取るためのデータ受信器102Bを含む。受信器102Bの数は、Dnポートのビット幅により、1つまたは複数であることが可能であることに留意する。例えば、Dnポートが、8ビットワイドデータ入力/出力の実装形態について、D0、D1、～D7に指定される場合、受信器102Bは、8回繰り返されることになる。受信器102Bの出力「`dn_i`」は、D型フリップフロップ103BのDポートに供給される。フリップフロップ103Bは、クロック信号「`cki_i`」によって駆動され、「`cki_i`」のあらゆる立上がりエッジで「`dn_i`」信号のステータスをラッチする。ラッチされた信号「`dn_lat`」は、コマンド/アドレスパケットロジック130に供給され、また、データパケットロジック140にも供給される。ラッチされた信号「`dn_lat`」はまた、マルチプレクサ104の一方の入力ポートに供給される。マルチプレクサ104の他方のポートは、データパケットロジック140からの信号「`core_data`」によって駆動される。マルチプレクサ104の出力は、フリップフロップ103FのD入力ポートに接続され、そのクロック入力ポートは、デューティ訂正されたクロック信号`clk_dcc`によって駆動され、「`clk_dcc`」のあらゆる立上がりエッジでマルチプレクサ104の出力のステータスをラッチする。ラッチされた信号「`q_i`」は、別のコントローラプログラミング可能遅延線PDL2、105Bによって遅延され、その遅延された信号「`q_d`」は、最終

40

50

的に、出力ドライバブロック108Bの入力ポートに駆動され、それは、外部信号Qnを出力する。フリップフロップロジック103Bおよび103Fの2つの段階は、2つのクロックサイクルの同じ入力から出力の待ち時間(=t<sub>10L</sub>)をもたらして、DnからQnにバイパスする。

#### 【0095】

内部信号dn\_iは、存在する場合、(コマンドストローブ入力によって示す)コマンドコンテンツ、および(データストローブ入力によって示す)データ入力の双方を含む。それぞれのデバイスは、いくつかの実施形態においては、デバイスアドレスレジスタ131内に保存されているデバイスアドレスを有する。それぞれのコマンドは、コマンドがそれに対してアドレスされるメモリデバイスのうちの1つのデバイスアドレスを含むDevice Address部分を含む。また、すべてのデバイスによって処理すべきコマンドを必要とするブロードキャストアドレスもある場合がある。メモリデバイス100は、Device Address部分を検証することによって、それぞれのコマンドを処理する。受け取られたコマンド/アドレスパケットにおけるDevice Address情報が、メモリデバイス100自体の保存されているデバイスアドレスに一致する場合、コマンド/アドレスパケットロジック130は、コマンドを処理し、また、コマンドがそのメモリデバイス向けであることを表す「id\_match」信号を発行する。id\_match信号は、マルチプレクサ104のデータフロー経路を導くために使用される。

「id\_match」が、デバイスアドレスマッチングプロセスの結果として、HIGHロジック状態に(しかし、より概括的には、定められている「一致状態」に)ある場合、マルチプレクサ104は、出力すべき「core\_data」を選択し、それにより、メモリコア150からのデータは、フリップフロップ103Fに転送可能になる。一方、「id\_match」が、デバイスアドレスマッチングプロセスの結果として、LOWロジック状態に(しかし、より概括的には、定められている「一致していない状態」に)ある場合、マルチプレクサ104は、出力すべき「dn\_lat」を選択し、それにより、データ入力Dnから受け取られるデータは、フリップフロップ103Fに転送されて、出力Qnでエコー可能になる。

#### 【0096】

したがって、マルチプレクサ104は、a)マルチプレクサ104のdn\_lat入力を選択することによって、データ入力Dnから受け取られるデータをバイパスすることと、b)マルチプレクサ104のcore\_data入力を選択することによって、core\_dataを出力することとの間の選択を可能にする。信号「core\_data」は通常、例えば、メモリコントローラ10からの要求に応じて「PAGE READ」動作の一部として、メモリコア150からデータパケットロジック140に転送される。次いで、「PAGE READ」動作が行われた後、メモリコントローラ10は、そのメモリデバイスにアドレスされるコマンドにより、メモリデバイスに「BURST READ」動作を要求することが可能である。その場合には、メモリデバイスは、「BURST READ」コマンドと、Device Address部分を含む対応するアドレス情報とを処理する。受け取られたコマンド/アドレスパケットにおけるDevice Address情報が、メモリデバイス100自体の保存されているデバイスアドレスに一致する場合、コマンド/アドレスパケットロジック130は、マルチプレクサ104のデータフロー経路を導くために、「id\_match」信号を発行する。「id\_match」が、デバイスアドレスマッチングプロセスの結果として、HIGHロジック状態にある場合、マルチプレクサ104は、出力すべき「core\_data」を選択し、それにより、メモリコア150からデータパケットロジック140にあらかじめ転送されているデータは、フリップフロップ103Fに転送可能になる。

#### 【0097】

コマンドがメモリデバイスにアドレスされるが、そのコマンドがBURST READコマンドでない場合に、いくつかの実施形態においては、マルチプレクサ104のcore\_data入力は、出力するデータがなくても、なおも選択されることに留意されたい。core\_data信号は、このような場合には、静的信号であってよい。これは、次のデバイスにエコーされないデータ入力Dnをもたらす。これは、後続のデバイスが、それらにアドレスされないコマンドと関連するデータを処理する必要をなくすことによって、それらのデバイスにおける電力消費を抑える効果を持つことが可能である。これについては、「Semiconductor Device and Method for Reducing Power Consumption in a System Having Interconnected Devices

10

20

30

40

50

」と題された2008年1月23日出願の米国特許出願第12/018,272号にさらに詳細に記載されている。

#### 【 0 0 9 8 】

したがって、いくつかの実施形態においては、データ入力信号Dnの遅延されたバージョンが、データ出力信号(Qn)の1つのコンポーネントとして生成される。時には、データ出力信号は、データ入力信号の遅延されたバージョンである。説明した実施形態では、これは、特定のメモリデバイス向けではないデータ入力信号上にコンテンツがある場合になるが、他のシナリオが可能である。さらには、時には、データ出力信号は、コマンドによりメモリデバイスにとって局所的に生成された信号への遅延の印加後、メモリデバイスにとって局所的に生成された信号の遅延されたバージョンを含む。説明した実装形態では、メモリデバイスにとって局所的に生成された信号は、データパケットロジック140からのいわゆるcore\_data出力であるが、他のシナリオが可能である。

10

#### 【 0 0 9 9 】

コマンド/アドレスパケットロジック130は、デューティサイクル訂正回路120への出力DCR<0:3>を生成して、以下に詳述するように実行されるデューティサイクル訂正の量を制御するDCR(デューティサイクル訂正レジスタ)132を備え、パケット遅延線105A、105B、105C、105Dへの出力ODR<0:1>を生成して、以下に詳述するように印加される出力遅延の量を制御するODR(出力遅延レジスタ)134を備える。使用可能なコマンドのうちの1つは、値をDCR132に書き込むための「Write Duty Cycle Correction Register」コマンドである。同様に、使用可能なコマンドのうちの1つは、値をODR134に書き込むための「Write Output Delay Register」コマンドである。

20

#### 【 0 1 0 0 】

##### 書き込みデューティサイクル訂正レジスタコマンド

「Write Duty Cycle Correction Register」コマンドの使用は、本明細書に説明するように、ある実装形態を想定し、デューティサイクル訂正を実行する際に印加すべき遅延の量が、値をデューティサイクル訂正レジスタに書き込むことによって制御される。より概括的には、本明細書においてデューティサイクル訂正コマンドと呼ぶ任意のコマンドが使用可能であり、それは、デューティサイクル訂正をどのように実行すべきかをデバイスに設定させる効果を有する。したがって、説明した「Write Duty Cycle Correction Register」コマンドは、デューティサイクル訂正コマンドの具体的な例と見なすべきである。

30

#### 【 0 1 0 1 】

##### 書き込み出力遅延レジスタコマンド

「Write Output Delay Register」コマンドの使用は、説明するように、ある実装形態を想定し、印加すべき遅延の量が、値を出力遅延レジスタに書き込むことによって制御される。より概括的には、本明細書において出力遅延調整コマンドと呼ぶ任意のコマンドが使用可能であり、それは、印加すべき遅延の量をデバイスに設定させる効果を有する。したがって、説明した「Write Output Delay Register」コマンドは、出力遅延調整コマンドの具体的な例と見なすべきである。

30

#### 【 0 1 0 2 】

##### デューティサイクル訂正

図示の例において、デューティサイクル訂正回路120は、クロック分周器123と、「4対16Decoder」ブロックおよび「Programmable Delay Line(PDL1)」を含むコントローラプログラミング可能遅延線121とを有する。クロック分周器123およびコントローラプログラミング可能遅延線121のそれぞれの出力clk\_ref、clk\_delは、XORゲート122に入力され、その出力は、デューティサイクル訂正されたクロックclk\_dccである。

40

#### 【 0 1 0 3 】

クロック分周器123は、入力「cki\_i」信号の周波数の半分の周波数を有する出力信号「clk\_ref」を抽出する。クロック分周器回路は、当技術分野においてよく知られている。図示の特定の例においては、クロック分周器123は、内部クロック信号cki\_iによって、そのクロック入力ポートを通じて駆動されるD型フリップフロップ103Dを含む。D型Flip-Flo

50

p 103Dの出力ポートQは、半分の周波数出力信号を得るために、インバータロジック124を通じて入力ポートDに接続されている。

【0104】

コントローラプログラミング可能遅延線121は、clk\_refの遅延されたバージョンである出力信号clk\_delを生成する。遅延の量は、「4対16Decoder」ロジックブロックの選択信号によって確定され、それは、コマンド/アドレスパケットロジック130から受け取られるDCR<0:3>信号情報によって制御される。XORロジックゲート122は、2つの半クロック信号clk\_refとclk\_delとを受け取り、デューティサイクル調整された全クロック信号clk\_dccを出力する。

【0105】

図3は、例えば、図2のデューティサイクル訂正回路120において使用可能なデューティサイクル訂正のためのプログラミング可能遅延線121の実装形態の例のブロック図である。半周波数クロック信号clk\_refは、16個のユニット遅延ブロックUNIT\_0～UNIT\_15のそれぞれの各入力に駆動される。それぞれのユニット遅延ブロックは同一構造を有し、ユニット遅延ブロックUNIT\_15を例として説明する。ユニット遅延ブロックは、2つのNANDロジックゲート1211および1212と、1つのインバータロジックゲート1213とから成る。第1のNANDロジックゲート1211は、その第1の入力でclk\_ref入力を受け取り、その第2の入力で4対16デコーダ1210から出力を受け取る。第1のNANDロジックゲート1211の出力は、第2のロジックNANDゲート1212の第1の入力に入力される。ユニット遅延ブロックUNIT\_15の場合、第2のロジックNANDゲート1212の第2の入力は、Vddに接続されている。最右のユニット遅延ブロックUNIT\_0を除くすべてのユニット遅延ブロックの場合、第2のNANDゲート1212の出力は、次のユニット遅延ブロックにおける第2のNANDゲート1212の第2の入力にインバータ1213を通じて接続されている。最右のユニット遅延ブロックUNIT\_0の第2のNANDゲートの出力は、インバータを通じて接続され、全体の出力クロックclk\_del信号を生成する。4対16Decoderブロック1210は、その入力として4ビットワイド入力バスDCR<0:3>を有する。デコーダブロック1210は、入力をデコードし、16ビットワイドバスSEL<15:0>を出力し、バスの1つの線は、16個のユニット遅延ブロックのそれぞれに接続されている。示されているユニット遅延ロジックは、レジスタ制御された遅延ロックループを生成するために使用されている既知の回路技術の一例である。あるいは、他のユニット遅延ロジックが使用可能である。16個のユニット遅延ブロックの使用は、具体的な実装形態である。例えば、より概説的には、N対Mデコーダを使用して、M個のユニット遅延ブロックに対してM個の制御信号に、N個の入力線上で受け取られた信号をデコードすることがあり得、ただし、N>=1およびM>=2である。

【0106】

動作中、「4対16Decoder」ロジック1210は、16SEL<15:0>出力を生成し、それにより、16個の選択信号のうちの1つのみが、HIGHロジック状態にあるようになり、他の15個すべての選択信号は、LOWロジック状態にあるようになる。そのため、1つのユニット遅延ブロックのみが、選択されたユニット遅延ブロックの右手へのユニット遅延ブロックを通じて、「clk\_ref」信号を転送するように選択される。制御入力DCR<0:3>は、どのユニット遅延ブロックがclk\_ref入力を処理することになるかを選択するために使用される。最小遅延は、最右ユニット遅延ブロックUNIT\_0を選択することによって選択され、その場合には、clk\_delは、1つのユニット遅延ブロックによって遅延されたclk\_ref信号であり、一方、最大遅延は、最左ユニット遅延ブロックUNIT\_15を選択することによって選択され、その場合には、clk\_delは、16個すべてのユニット遅延ブロックによって遅延されたclk\_ref信号である。

【0107】

大抵のプロセス技術の場合、図示のユニット遅延ブロックのユニット遅延量は、約100ps～150psである。しかし、いくつかの実施形態においては、より精巧なユニット遅延回路ブロックは、より精巧な遅延同調性能により、はるかにより高い動作周波数向けに使用される。ユニット遅延時間を図3では「tUD」と示し、全プログラミング可能遅延線に対する

10

20

30

40

50

総遅延時間を「tUD」の16倍である「tPDL1」と示す。

【0108】

いくつかの実施形態においては、パワーオン初期化のためのデフォルト設定は、遅延線の中央位置にあるように、ロジックHIGH状態をSEL<7>ビット上有することである。しかし、他の設計変形態においては、デフォルト設定は、異なってよく、最大周波数での動作の準備ができている状態にするために、最小遅延設定を有することが推奨される場合がある。

【0109】

図4は、コントローラプログラミング可能遅延デューティサイクル訂正手順のタイミング図の一例であり、すべての信号は、デューティ訂正されることになる生の入力クロック信号であるCKIを除いて、図3に示すものである。タイミング図は、単に例示目的のために、1つの非常に歪んだクロック入力信号CKIを上部に示している。半クロック信号clk\_refは、図2の「クロック分周器」ブロック123から抽出され、その立上がりリエッジおよび立下がリエッジは、CKIの2つの立上がりリエッジと位置合わせされる。この例では、例えば、最初に「0111b」に設定されると示されているDCR<0:3>値に対しても、この変化もない場合、クロック信号clk\_dccは、45%オン、55%オフなど、歪んだデューティ比を有することになると想定される。DCR<0:3>値が「1000b」に変更された後、クロック信号clk\_dccのデューティサイクルは、イネーブルされているSEL(7)からイネーブルされているSEL(8)へのコントローラプログラミング可能遅延線121の選択におけるシフトの結果として、50%オンおよび50%オフであるように訂正される。

10

20

20

【0110】

デューティサイクル訂正の制御

DCR132のコンテンツが、デューティサイクル訂正回路120におけるコントローラプログラミング可能遅延線121によって導入される遅延の量を制御するために使用され、それによって、デューティサイクル訂正を制御することを思い出されたい。上述したように、DCR132のコンテンツは、「Write Duty Cycle Register」コマンドにより書き込み可能である。

30

【0111】

図5は、コントローラの視点からのデューティサイクル訂正手順に関する流れ図である。方法は、ブロック5-1において、デバイスのパワーオンから開始する。この時点で、すべての遅延線が初期化され、すべてのデバイスに対するデバイスアドレスが割り当てられる。ブロック5-2において、メモリコントローラ10は、デューティ検出器13を使用して、CKI/CKI#のデューティ比をモニタリングする。デューティサイクルエラーがある場合には(yes経路ブロック5-3)、ブロック5-4で、デューティ検出器13は、「Duty\_Add」または「Duty\_Sub」信号S12をアサートする。この後、コマンドジェネレータ12は、「DCR+1」の値または「DCR-1」の値を有する「Write Duty Cycle Register」コマンドを発行する。なおもデューティサイクルエラーがある場合には(yes経路ブロック5-6)、方法は、デューティサイクルレジスタに対するさらなる調整をステップ5-4に戻って継続する。もはやデューティサイクルエラーがない場合には(no経路ブロック5-6)、デューティサイクル訂正は、5-7において完了される。同様に、デューティサイクルエラーがブロック5-3で検出されなかった場合には、その時点で、方法はやはり、5-7において完了される。

40

【0112】

以下のTable 1(表1)は、Duty Cycle Register(DCR)に書き込むためのコマンドパケット定義の例である。第1のバイトは、「Device Address(=DA)」部分であり、第2のバイトは、コマンドコード(=CMD=FAh)であり、第3のバイトは、Register Values(=DCR<0:3>)を含む。いくつかの実施形態においては、ブロードキャストアドレスが、例えば、FFhと規定される。DAがブロードキャストアドレスに設定される場合、それは、コマンドがブロードキャスティングコマンドであることを意味し、それにより、あらゆるメモリデバイスがコマンドを実行すると予測されることになる。そうでなければ、DAに一致している特定のメモリデバイスのみが、コマンドを実行することになる。いくつかの実施形態においては、

50

「Read Duty Cycle Register」コマンドもまた、コントローラ10に対して、より柔軟性を与えるために実装される。

【0 1 1 3】

【表1】

Table 1. デューティサイクルレジスタに関する例示的なコマンドパケット定義

| コマンド                  | 第1の<br>バイト | 第2の<br>バイト | 第3の<br>バイト |

|-----------------------|------------|------------|------------|

| 書込みデューティサイクルレジスタ(DCR) | DA         | FAh        | DCR<0:3>   |

10

\*注釈

1)DA(デバイスアドレス)が FFh(=255d)である場合、それは、プロードキャスティングコマンドであり、それにより、あらゆるデバイスがそのコマンドに応答することになる。

2)DA=デバイスアドレス

【0 1 1 4】

Table 2(表2)は、Duty Cycle Register(=DCR)のビット定義の例である。それは、純粋に定義の例を示しており、そのため、システム構成が、ユニット遅延調整に対して、より詳細な粒度を必要とする場合、この表は、プログラミング可能遅延線に関して、さらなる管理可能性に対応するために容易に拡張可能である。例えば、Bit<7:0>が、コントローラから「0000 1000b=08h」と入力される場合、DCR<0:3>は、有効レジスタ値に対してBit<3:0>(=「1000b」)のみを許容していることになり、より上位の4つのビットBit<7:4>は、無視されることになる。しかし、他の設計変更形態においては、より精巧なユニット遅延回路が、より高い周波数動作向けに実装可能であり、追加のビット割当ても使用可能である。

20

【0 1 1 5】

【表2】

Table 2. デューティサイクルレジスタと出力遅延レジスタの例示的なビット定義

| 内容               | ビット7          | ビット6 | ビット5   | ビット4   | ビット3   | ビット2   | ビット1 | ビット0 |

|------------------|---------------|------|--------|--------|--------|--------|------|------|

| デューティサイクルレジスタビット | 将来使用のための予備(低) |      | DCR<3> | DCR<2> | DCR<1> | DCR<0> |      |      |

30

【0 1 1 6】

図6は、SDR(Single Data Rate)動作に基づく「Write Duty Cycle Register」コマンドパケットシーケンスのタイミング図の一例である。このタイミング図においては、時間T1で、CK1の立上がりエッジまたはCK1#の立下がりエッジは、CSIのHIGH状態をラッチし、同時に、Dnポート上のDA(=Device Address=00h)情報をラッチする。DAがFFh(=10進法で255)と設定される場合、これは、「Write Duty Cycle Register」コマンドが、プロードキャスティングコマンドであることを意味し、それにより、あらゆるメモリデバイスがコマンドを実行すると予測されることになる。いくつかの実施形態においては、プロードキャスティングコマンドは、Duty Cycle Correction動作に使用される。しかし、開示する回路はまた、個々のデバイス内でデューティサイクル訂正動作のより柔軟な調整を可能にする。次の立上がりエッジ時間T2においては、メモリデバイスは、CMD(=Command=FAh)情報をラッチし、第3の立上がりエッジT3上で、DCR(=Duty Cycle Register Value=08h)情報をラッチする。CS0出力およびQn出力ポートは、tIOL(=InputからOutputの待ち時間)の2つのクロック待ち時間により、CSI入力信号およびDn入力信号をそれぞれエコーする。tWDCR(=Write Duty Cycle Register Latency)である別の待ち時間指定があり、それは、メモリチップにおけるWrite Duty Cycle Registerパケットの処理時間に関するもの、およびデュー

40

50

ティサイクル訂正回路120内のController Programmable Delay Line 121におけるDuty Cycle調整の処理時間に関するものである。いくつかの実施形態においては、tWDCR値は、図6に示す4つのクロックサイクルとして設定される。(例えば、T8における)tWDCR後、メモリコントローラ10は、任意の他のコマンドパケットをメモリデバイスに発行することが可能である。

#### 【0117】

説明した実施形態は、シリアル接続のアーキテクチャにおけるデバイスのすべてが、デューティサイクル訂正を実装すると想定している。より概略的には、デバイスのうちの少なくとも1つが、デューティサイクル訂正を実装する。

#### 【0118】

##### 出力遅延調整

再度、図1を参照すると、説明したプログラミング可能遅延線105A、105B、105C、105Dは、位相訂正を可能にするために、出力信号CS0、Qn、DS0、およびCK0/CK0#をプログラミング可能に遅延させることを可能にするように設けられる。図1はまた、2対4Decoderロジックブロック106に接続されている出力遅延レジスタ信号バスODR<0:1>を示している。2対4Decoderロジック106は、4つの選択信号バスSEL2 <0:3>を出力する。それらのSEL2<0:3>選択信号は、4つのコントローラプログラミング可能遅延線105A、105B、105C、および105Dにすべて接続されている。

#### 【0119】

図7は、出力遅延調整のための例示的な回路ブロックの実装形態を示している。図示の例においては、プログラミング可能遅延線105A、105B、105C、および105Dは、図3において使用するものと同じである4つのユニット遅延要素から成る。これは、出力のための遅延調整の範囲が、デューティサイクルの遅延調整の範囲の4/16だけであることを意味する。しかし、これは、詳細な実装形態であり、他の数の遅延要素が、代替として使用可能である。それぞれのプログラミング可能遅延線105A、105B、105C、105Dは、遅延線の入力として、それぞれの信号cso\_i、q\_i、dso\_i、およびclk\_dccを受け取り、それぞれの遅延された出力cso\_d、q\_d、dso\_d、およびclk\_dcc\_dを生成する。メモリシステムが、マルチビット出力構成、例えば、8ビットワイドI/O構成を有する場合、q\_i信号およびq\_d信号は、例えば、数字上で8であるように、対応して増加することになり、q\_iおよびq\_dに対する遅延線ブロックの数は、例えば、数字上で8であるように、対応して増加することになる。

#### 【0120】

動作中、「2対4Decoder」ロジック106は、SEL2<0:3>出力を生成し、それにより、4つの選択信号のうちの1つのみが、HIGHロジック状態にあるようになり、他の3つすべての選択信号は、ロジックLOW状態にあるようになる。選択されたユニット遅延ブロックのみが、選択されたユニット遅延ブロックの右手への残りのユニット遅延ブロックを通じて、それぞれの入力信号を転送する。制御入力ODR<0:1>は、どのユニット遅延ブロックがそれぞれの入力を処理することになるかを選択するために使用される。最小遅延は、最右ユニット遅延ブロックUNIT\_0を選択することによって選択され、その場合には、それぞれの出力信号は、1つのユニット遅延ブロックによって遅延されたそれぞれの入力信号であり、一方、最大遅延は、最左ユニット遅延ブロックUNIT\_3を選択することによって選択され、その場合には、それぞれの出力信号は、4つの遅延ユニットブロックによって遅延されたそれぞれの入力信号である。

#### 【0121】

4つのユニット遅延ブロックを有する「2対4デコーダ」ロジック106は、この例の回路設計において実装される。しかし、より概略的には、任意の所要の数の遅延ユニットおよび対応するデコーダロジックが使用可能である。デフォルト遅延設定は、パワーオン初期化期間中に使用可能である。この例においては、デフォルト選択は、例えば、SEL2<0>に設定されることがあり得、メモリデバイスは、パワーオン、またはいくつかの他の設計変更形態においてはハードリセット後に、それぞれの出力経路に対して最小量の遅延を有する

ことになる。4つのユニット遅延ブロックの使用は、具体的な実装形態である。例えば、より概略的には、N対Mデコーダを使用して、M個のユニット遅延ブロックに対してM個の制御信号に、N個の入力線上で受け取られた信号をデコードすることがあり得、ただし、 $N \geq 1$ および $M \geq 2$ である。

#### 【0122】

図8は、コントローラプログラミング可能出力遅延調整のためのタイミング図の例である。出力遅延レジスタのコンテンツにおける変化前後のデューティサイクル訂正されたクロックclk\_dccと、その遅延されたバージョンclk\_dcc\_dとが示されている。値「00b=0d」から「01b=1d」への出力遅延レジスタにおける変化後、遅延されたクロックは、量 $2 \times tUD$ だけ遅延されるが、調整前には、 $1 \times tUD$ だけ遅延されていたことが分かる。また、遅延調整後出力される前のコマンドストローブ出力cso\_i、および遅延調整の出力cso\_dも示されている。やはりまた、出力遅延レジスタに対する変化前には、遅延されたコマンドストローブは、 $1 \times tUD$ だけ遅れている。出力遅延レジスタに対する変化後には、遅延されたコマンドストローブは、量 $2 \times tUD$ だけ遅れている。

10

#### 【0123】

##### 出力遅延調整の制御

ODR134のコンテンツが、遅延線105A、105B、105C、105Dによって導入される遅延の量を制御するために使用され、それによって、出力遅延調整の量を制御することを思い出されたい。上述したように、ODR134のコンテンツは、「Write Output Delay Register」コマンドにより書き込み可能である。

20

#### 【0124】

メモリコントローラ10における位相検出器11が、そのCKI/CKI#信号と、CKO/CKO#信号との間の許容できない位相差を検出すると、コントローラ10は、図1のまさに第1のメモリデバイス100-1を可能にする1つの追加のユニット遅延量により、1つの「Write Output Delay Register」コマンドパケットを発行することになる。例えば、tWODR(Write Output Delay Register待ち時間)、および図10に関して後述する総tIOL待ち時間の間、第1のメモリデバイスに対する十分なクロックサイクル後、なおも許容できない位相差がある場合、コントローラ10は、第2のメモリデバイス、例えば、図1の第2のメモリデバイス100-2に別の「Write Output Delay Register」コマンドパケットを発行することが可能である。この一連の動作は、メモリコントローラ10が許容可能な位相差を得るまで継続可能である。最下位のメモリデバイスがその出力遅延を調整するように命令された後、次いでメモリコントローラ10は、コマンドパケット内の1つのさらなる追加のユニット遅延値により、まさに第1のメモリデバイスに向き、位相差が許容可能な範囲に到達するまで、残りのメモリデバイスについて継続する。

30

#### 【0125】

上述の手順を図9の流れ図に示している。方法は、ブロック9-1において、パワーオンから開始する。この時点で、すべての遅延線およびデバイスアドレスが初期化される。ブロック9-2においては、メモリコントローラ10は、位相検出器11を使用して、CKI/CKI#と、CKO/CKO#との間の位相エラーをモニタリングする。位相エラーがある場合には(yes経路9-3)、位相検出器11は、ブロック9-4で「PE」信号S11をアサートする。その後、コマンドジェネレータ12は、位相エラーをモニタリングしている間に1つずつ、第1から最下位までのそれぞれのメモリデバイスに、「ODR+1」の値を有する「書き込み出力遅延レジスタ」コマンドを発行する。ブロック9-6で、なおも位相エラーがある場合には(yes経路)、方法は、ブロック9-4に戻って継続する。位相エラーがない場合には(no経路ブロック9-6)、位相訂正是、ブロック9-7において完了される。同様に、位相エラーがブロック9-3で検出されなかつた場合には、方法は終了し、位相訂正是、ブロック9-7において完了されている。

40

#### 【0126】

Table 3(表3)は、Write Output Delay Registerコマンドに対するコマンドパケット定義の例である。第1のバイトは、「Device Address(=DA)」部分であり、第2のバイトは、Commandコード(=CMD=FBh)を含み、第3のバイトは、Register Values(ODR<0:1>)を含む。い

50

いくつかの実施形態においては、ブロードキャストアドレスが、例えば、FFhと規定される。DAがブロードキャストアドレスに設定される場合、それは、コマンドがブロードキャストイングコマンドであることを意味し、それにより、あらゆるメモリデバイスがコマンドを実行すると予測される。そうでなければ、DAに一致している特定のメモリデバイスのみが、コマンドを実行することになる。いくつかの実施形態においては、「Read Output Delay Register」が、コントローラ10に、より柔軟性を与えるために実装される。例えば、これは、メモリデバイスのすべてからの値を読み取り、次いで、必要に応じて、デバイス間の設定を適切に再構成するために、コントローラによって使用可能である。

【0127】

【表3】

10

Table 3. コントローラプログラミング可能遅延線レジスタに関する例示的なコマンドパケット定義

| コマンド             | 第1の<br>バイト | 第2の<br>バイト | 第3の<br>バイト |

|------------------|------------|------------|------------|

| 書込み出力遅延レジスタ(ODR) | DA         | FBh        | ODR<0:1>   |

\*注釈

1)DA(デバイスアドレス)が FFh(=255d)である場合、それは、ブロードキャストコマンドであり、それにより、あらゆるデバイスがコマンドに応答することになる。

20

2)DA=デバイスアドレス

【0128】

Table 4(表4)は、Output Delay Register(=ODR)のビット定義の例である。それは、純粋に定義の例を示しており、そのため、システム構成が、ユニット遅延調整に対して、より詳細な粒度を必要とする場合、この表は、プログラミング可能遅延線に関して、さらなる管理可能性に対応するために容易に拡張可能である。

【0129】

【表4】

30

Table 4. デューティサイクルレジスタと出力遅延レジスタの例示的なビット定義

| 内容              | ビット7 | ビット6 | ビット5 | ビット4 | ビット3          | ビット2 | ビット1   | ビット0   |

|-----------------|------|------|------|------|---------------|------|--------|--------|

| 出力遅延レジ<br>スタビット |      |      |      |      | 将来使用のための予備(低) |      | ODR<1> | ODR<0> |

【0130】

図10は、SDR(Single Data Rate)動作に基づく「Write Output Delay Register」コマンドパケットシーケンスのタイミング図の一例である。このタイミング図においては、時間T1で、CKIの立上がりエッジまたはCKI#の立下がりエッジは、CSIのHIGH状態をラッチし、同時に、Dnポート上のDA(=Device Address=00h)情報をラッチする。次の立上がりエッジ時間T2においては、メモリデバイスは、CMD(=Command=FBh)情報をラッチし、第3の立上がりエッジ上で、ODR(=Output Delay Register Value=01h)情報をラッチする。CSO出力ポートおよびQn出力ポートは、tIOL(=Input-to-Output Latency)の2つのクロック待ち時間により、CSI入力信号およびDn入力信号をそれぞれエコーしている。tWODR(=Write Output Delay Register Latency)である別の待ち時間指定があり、それは、メモリチップにおけるWrite Output Delay Registerパケットの処理時間に関するもの、およびController Programmable Delay Line 2(=PDL2 105A～D)におけるOutput Delay調整の処理時間に関するものである。いくつかの実施形態においては、tWODR値は、図10に示す4つのクロックサイクルとして設定される。(例えば、T8における)tWODR後、メモリコントローラ10は、任意の他のコマンドパケットをメモリデバイスに発行することが可能である。

40

50

## 【0131】

より概説的には、本出願の実施形態が、出力遅延調整実施形態を実行する方法および回路を提供し、少なくとも1つの入力信号の遅延されたバージョンが生成され、少なくとも1つの入力信号は、少なくともクロック信号を含む。出力遅延調整を受けない、デバイス間で伝達される追加の入力信号がある場合がある。いくつかの信号の場合、出力のための入力信号の遅延されたバージョンを生成することは、出力のための入力信号の遅延されたバージョンを条件付きで生成することを含む。すなわち、信号のうちのいくつかは、隣接するデバイス間で、条件付きで伝達可能である。メモリデバイスの入力データ信号が、時には、次のメモリデバイスに伝達される具体的な例を以下に詳述する。

## 【0132】

上述した実施形態は、同一のユニット遅延ブロックから成るプログラミング可能遅延線の使用を想定している。いくつかの実施形態においては、プログラミング可能遅延線は、「Coarse」および「Fine」遅延線など、2つ以上の部分に分割されて、デューティサイクル訂正および/または出力遅延調整のための遅延調整のさらなるプログラミング可能性を可能にする。

## 【0133】

説明した詳細な例においては、それぞれの信号ごとに入力付近に第1のFlip-Flopが、出力付近に第2のFlip-Flopがある。これは、2つのクロックサイクル待ち時間をもたらすものである。もちろん、他のクロック待ち時間が入力と出力との間に異なる機能を含むことによって生じる場合があることを認識すべきである。

## 【0134】

説明した実施形態においては、出力遅延線は、それぞれの信号ごとに出力付近に配置されている最下位のFlip-Flopの後に配置される。いくつかの実施形態においては、出力遅延線は、最下位のフリップフロップの前に配置される。

## 【0135】

いくつかの実施形態においては、シリアル接続のやり方で接続されているデバイスは、実質的には、同一であると想定される。いくつかの実施形態においては、これらは、実質的には、同一のメモリデバイスである。他の実施形態においては、種々のタイプのメモリデバイスが互換性のあるシリアルインターフェースである限り、それらは使用可能である。

## 【0136】

詳述した実施形態は、種々のクロック信号が使用されると想定している。より概説的には、シングルエンドの、または差動のクロック信号が使用可能である。同様に、任意の他の入力/出力信号は、シングルエンドであっても、または差動であってもよい。

## 【0137】

いくつかの実施形態においては、説明したように動作可能な複数のメモリデバイスと、コントローラとを含む単一のMCP(マルチチップパッケージ)が提供される。

## 【0138】

本明細書に記載の方法および装置は、環状に接続されているコントローラおよび一連のメモリデバイスを特徴とするシリアル接続のアーキテクチャを想定している。このような実施形態においては、メモリデバイスはスレーブデバイスであり、メモリコントローラはマスタデバイスである。より概説的には、本明細書に説明した方法および装置は、隣接するデバイス間の共通のインターフェースと、スレーブデバイスによって実行されるデューティサイクル訂正および/または位相訂正を制御するマスタデバイスとして働くように構成されているデバイスとのシリアル接続の構成で、スレーブデバイスとして構成されている任意の種類の半導体集積回路デバイスを有する任意の種類の半導体集積回路システムに適用可能である。集積回路タイプの例は、中央処理ユニットと、グラフィック処理ユニットと、ディスプレイコントローラICと、ディスクドライブICと、NAND Flash EEPROM、NOR Flash EEPROM、AND Flash EEPROM、DiNOR Flash EEPROM、Serial Flash EEPROM、DRAM、SRAM、ROM、EPROM、FRAM、MRAM、PCRAMなどのようなメモリデバイスとを含む。

10

20

30

40

50

## 【0139】

本明細書に説明した実施形態のうちのいくつかは、单一データレート動作を想定している。より概括的には、実施形態は、他のデータレート、例えば、この開示を読むと当業者には理解されるであろう適切な修正形態によるダブルレート動作を有するシステムに適用可能である。

## 【0140】

本発明の多数の修正形態および変更形態が、上述の教示に照らして可能である。そのため、添付の特許請求の範囲の中で、本発明は、本明細書に具体的に説明する以外の他の形で実施可能であることを認識すべきである。

## 【符号の説明】

## 【0141】

- |      |                    |    |

|------|--------------------|----|

| 10   | メモリコントローラ          | 10 |

| 11   | 位相検出器              |    |

| S11  | 信号バス               |    |

| 12   | コマンドジェネレータ         |    |

| S12  | 信号バス               |    |

| 13   | デューティ検出器           |    |

| S13  | 信号バス               |    |

| 90   | リンク                |    |

| 100  | メモリデバイス            | 20 |

| 101  | メモリシステム            |    |

| 102A | コマンドストローブ受信器       |    |

| 102B | データ受信器             |    |

| 102C | データストローブ入力処理受信器    |    |

| 102D | クロック入力受信器          |    |

| 103A | フリップフロップ           |    |

| 103B | フリップフロップ           |    |

| 103C | フリップフロップ           |    |

| 103D | フリップフロップ           |    |

| 103E | フリップフロップ           | 30 |

| 103F | フリップフロップ           |    |

| 103G | フリップフロップ           |    |

| 104  | マルチプレクサ            |    |

| 105A | コントローラプログラミング可能遅延線 |    |

| 105B | コントローラプログラミング可能遅延線 |    |

| 105C | コントローラプログラミング可能遅延線 |    |

| 105D | コントローラプログラミング可能遅延線 |    |

| 106  | 2対4Decoderロジック     |    |

| 108A | 出力ドライバブロック         |    |

| 108B | 出力ドライバブロック         | 40 |

| 108C | 出力ドライバブロック         |    |

| 108D | 出力ドライバブロック         |    |

| S111 | 差動クロックバス           |    |

| S112 | 差動クロックバス           |    |

| S113 | 差動クロックバス           |    |

| S114 | 差動クロックバス           |    |

| 120  | デューティサイクル訂正回路      |    |

| 121  | コントローラプログラミング可能遅延線 |    |

| 122  | XORゲート             |    |

| 123  | クロック分周器            | 50 |

- 124 インバータロジック

130 コマンド/アドレスパケットロジック

131 デバイスアドレスレジスタ

132 デューティサイクル訂正レジスタ

134 出力遅延レジスタ

140 データパケットロジック

150 メモリコア

1210 4対16デコーダ

1211 NANDロジックゲート

1212 NANDロジックゲート

1213 インバータロジックゲート

10

【 図 1 】

FIG. 1

【 四 2 】

FIG. 2

【図3】

FIG. 3

【 図 4 】

FIG. 4

【 図 5 】

【 四 7 】

FIG 7

【図8】

FIG. 8

【図9】

FIG. 9

【図 6】

FIG. 6

【図 10】

FIG. 10

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                            | International application No.<br>PCT/CA2009/001271                                                                                                                                                                                           |                                           |                                                                                    |                                                                                                                                                                                                 |                                                                                                          |                                                                                        |                                                                                                                                                                          |                                                                                           |     |                                                                                                                                                                                                                                              |                                                                                                                                                                         |                                                                                            |                                           |                                                                              |                                                                       |      |                                                                                                        |                                                                       |      |   |                                                                       |      |   |                                                                |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------|---|-----------------------------------------------------------------------|------|---|----------------------------------------------------------------|------|

| <p><b>A. CLASSIFICATION OF SUBJECT MATTER</b><br/> <b>IPC: G11C 7/22 (2006.01), G11C 16/32 (2006.01), G11C 5/02 (2006.01)</b><br/>           According to International Patent Classification (IPC) or to both national classification and IPC</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                            |                                                                                                                                                                                                                                              |                                           |                                                                                    |                                                                                                                                                                                                 |                                                                                                          |                                                                                        |                                                                                                                                                                          |                                                                                           |     |                                                                                                                                                                                                                                              |                                                                                                                                                                         |                                                                                            |                                           |                                                                              |                                                                       |      |                                                                                                        |                                                                       |      |   |                                                                       |      |   |                                                                |      |

| <p><b>B. FIELDS SEARCHED</b><br/>           Minimum documentation searched (classification system followed by classification symbols)<br/> <b>IPC: G11C</b></p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                            |                                                                                                                                                                                                                                              |                                           |                                                                                    |                                                                                                                                                                                                 |                                                                                                          |                                                                                        |                                                                                                                                                                          |                                                                                           |     |                                                                                                                                                                                                                                              |                                                                                                                                                                         |                                                                                            |                                           |                                                                              |                                                                       |      |                                                                                                        |                                                                       |      |   |                                                                       |      |   |                                                                |      |