(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3667136号

(P3667136)

(45) 発行日 平成17年7月6日(2005.7.6)

(24) 登録日 平成17年4月15日(2005.4.15)

(51) Int.C1.<sup>7</sup>

F 1

H O 1 L 21/60

H O 1 L 21/60 301A

請求項の数 23 (全 12 頁)

(21) 出願番号 特願平11-41045

(22) 出願日 平成11年2月19日(1999.2.19)

(65) 公開番号 特開2000-243779(P2000-243779A)

(43) 公開日 平成12年9月8日(2000.9.8)

審査請求日 平成16年5月20日(2004.5.20)

早期審査対象出願

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区丸の内二丁目4番1号

(74) 代理人 100080001

弁理士 筒井 大和

(74) 代理人 100068504

弁理士 小川 勝男

(72) 発明者 加賀谷 修

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

(72) 発明者 関根 健治

東京都国分寺市東恋ヶ窪一丁目280番地

株式会社日立製作所中央研究所内

最終頁に続く

(54) 【発明の名称】高周波電力増幅器モジュール

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、

前記基板の1つの面に配置される第1および第2の電極と、

前記基板に搭載され、入力端子および出力端子を有する第1および第2のトランジスタを有して成る四辺形状の半導体チップと、

前記第1の電極と前記第1のトランジスタの前記入力端子とを電気的に接続する第1の接続導体と、

前記第2の電極と前記第2のトランジスタの前記出力端子とを電気的に接続する第2の接続導体とを具備して成り、

前記半導体チップは、前記第1のトランジスタの前記入力端子と前記第1の電極とが対向し、前記第2のトランジスタの前記出力端子と前記第2の電極とが対向するように配置され、

前記第1の接続導体は第1の方向に延在し、前記第2の接続導体は前記第1の方向とは異なる第2の方向に延在し、

前記第1の方向と前記第2の方向との成す角は、前記基板の前記1つの面を平面図として見た場合に72~180度の範囲内であり、

前記第1のトランジスタの前記入力端子に入力された信号を電圧増幅し、前記第2のトランジスタの前記出力端子から、電圧増幅された前記信号を出力することを特徴とする高周波電力増幅器モジュール。

**【請求項 2】**

請求項 1 において、

前記第 1 のトランジスタの前記出力端子と前記第 2 のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。

**【請求項 3】**

請求項 1 において、

前記第 1 および第 2 のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第 1 のトランジスタの前記入力端子は、前記第 1 のトランジスタの前記電界効果トランジスタの前記ゲートであり、

前記第 2 のトランジスタの前記出力端子は、前記第 2 のトランジスタの前記電界効果トランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。

**【請求項 4】**

請求項 1 において、

前記第 1 および第 2 のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。

**【請求項 5】**

請求項 1 において、

前記第 1 のトランジスタの前記入力端子と前記第 2 のトランジスタの前記出力端子とのボンディング部間の距離は 0.3 mm 以上であり、前記第 1 および第 2 のトランジスタの安定係数は 1 以上であることを特徴とする高周波電力増幅器モジュール。

**【請求項 6】**

基板と、

前記基板の 1 つの面に配置される第 1 および第 2 の電極と、

前記基板に搭載され、入力端子および出力端子を有する第 1 および第 2 のトランジスタを有して成る四辺形状の半導体チップと、

前記第 1 の電極と前記第 1 のトランジスタの前記入力端子とを電気的に接続する第 1 の接続導体と、

前記第 2 の電極と前記第 2 のトランジスタの前記出力端子とを電気的に接続する第 2 の接続導体とを具備して成り、

前記半導体チップは、前記第 1 のトランジスタの前記入力端子と前記第 1 の電極とが対向し、前記第 2 のトランジスタの前記出力端子と前記第 2 の電極とが対向するように配置され、

前記第 1 の接続導体の両端のボンディング部間を結ぶ第 1 の補助線で定義される第 1 の方向と、前記第 2 の接続導体の両端のボンディング部間を結ぶ第 2 の補助線で定義される第 2 の方向との成す角は、72 ~ 180 度の範囲内であり、

前記第 1 のトランジスタの前記入力端子に入力された信号を電圧増幅し、前記第 2 のトランジスタの前記出力端子から、電圧増幅された前記信号を出力することを特徴とする高周波電力増幅器モジュール。

**【請求項 7】**

請求項 6 において、

前記第 1 のトランジスタの前記出力端子と前記第 2 のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。

**【請求項 8】**

請求項 6 において、

前記第 1 および第 2 のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第 1 のトランジスタの前記入力端子は、前記第 1 のトランジスタの前記電界効果トランジスタの前記ゲートであり、

前記第 2 のトランジスタの前記出力端子は、前記第 2 のトランジスタの前記電界効果ト

10

20

30

40

50

ランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。

**【請求項 9】**

請求項 6において、

前記第1および第2のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。

**【請求項 10】**

請求項 6において、

前記第1のトランジスタの前記入力端子と前記第2のトランジスタの前記出力端子とのボンディング部間の距離は0.3mm以上であり、前記第1および第2のトランジスタの安定係数は1以上であることを特徴とする高周波電力増幅器モジュール。 10

**【請求項 11】**

基板と、

前記基板の1つの面に配置される第1および第2の電極と、

前記基板に搭載され、入力端子および出力端子を有する第1および第2のトランジスタを有して成る四辺形状の半導体チップと、

前記第1の電極と前記第1のトランジスタの前記入力端子とを電気的に接続する第1の接続導体と、

前記第2の電極と前記第2のトランジスタの前記出力端子とを電気的に接続する第2の接続導体とを具備して成り、

前記半導体チップは、前記第1のトランジスタの前記入力端子と前記第1の電極とが対向し、前記第2のトランジスタの前記出力端子と前記第2の電極とが対向するように配置され、 20

前記第1の接続導体は第1の方向に延在し、前記第2の接続導体は前記第1の方向とは異なる第2の方向に延在し、

前記第1の方向と前記第2の方向との成す角が、前記基板の前記1つの面を平面図として見た場合に72~180度の範囲内であることにより、前記第2のトランジスタの前記出力端子から出力される信号から前記第1のトランジスタの前記入力端子に入力される信号へ正帰還が働くことを防止し、

前記第1のトランジスタの前記入力端子に入力された信号を電圧増幅し、前記第2のトランジスタの前記出力端子から、電圧増幅された前記信号を出力することを特徴とする高周波電力増幅器モジュール。 30

**【請求項 12】**

請求項 11において、

前記第1のトランジスタの前記出力端子と前記第2のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。

**【請求項 13】**

請求項 11において、

前記第1および第2のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第1のトランジスタの前記入力端子は、前記第1のトランジスタの前記電界効果トランジスタの前記ゲートであり、 40

前記第2のトランジスタの前記出力端子は、前記第2のトランジスタの前記電界効果トランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。

**【請求項 14】**

請求項 11において、

前記第1および第2のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。

**【請求項 15】**

請求項 11において、

前記第1のトランジスタの前記入力端子と前記第2のトランジスタの前記出力端子との 50

ポンディング部間の距離は 0 . 3 mm 以上であり、前記第 1 および第 2 のトランジスタの安定係数は 1 以上であることを特徴とする高周波電力増幅器モジュール。

**【請求項 1 6】**

請求項 1 において、

前記第 1 の方向と前記第 2 の方向との成す角は、前記基板の前記 1 つの面を平面図として見た場合に略 90 度であることを特徴とする高周波電力増幅器モジュール。

**【請求項 1 7】**

請求項 1 6 において、

前記第 1 のトランジスタの前記出力端子と前記第 2 のトランジスタの前記入力端子とは整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。 10

**【請求項 1 8】**

請求項 1 6 において、

前記第 1 および第 2 のトランジスタの各々は、ゲート、ソース、およびドレインを有する電界効果トランジスタを含んで成り、

前記第 1 のトランジスタの前記入力端子は、前記第 1 のトランジスタの前記電界効果トランジスタの前記ゲートであり、

前記第 2 のトランジスタの前記出力端子は、前記第 2 のトランジスタの前記電界効果トランジスタの前記ドレインであることを特徴とする高周波電力増幅器モジュール。

**【請求項 1 9】**

請求項 1 6 において、

前記第 1 および第 2 のトランジスタの各々は、バイポーラトランジスタであることを特徴とする高周波電力増幅器モジュール。 20

**【請求項 2 0】**

請求項 1 6 において、

前記第 1 のトランジスタの前記入力端子と前記第 2 のトランジスタの前記出力端子とのポンディング部間の距離は 0 . 3 mm 以上であり、前記第 1 および第 2 のトランジスタの安定係数は 1 以上であることを特徴とする高周波電力増幅器モジュール。

**【請求項 2 1】**

基板と、

前記基板の 1 つの面に配置される第 1 および第 2 の電極と、

前記基板に搭載され、入力端子および出力端子を有する第 1 および第 2 のトランジスタを有して成る四辺形状の半導体チップと、

前記第 1 の電極と前記第 1 のトランジスタの前記入力端子とを電気的に接続する第 1 の接続導体と、

前記第 2 の電極と前記第 2 のトランジスタの前記出力端子とを電気的に接続する第 2 の接続導体とを具備して成り、

前記半導体チップは、前記第 1 のトランジスタの前記入力端子と前記第 1 の電極とが対向し、前記第 2 のトランジスタの前記出力端子と前記第 2 の電極とが対向するように配置され、

前記第 2 のトランジスタは電界効果トランジスタであり、

前記第 2 のトランジスタの前記出力端子は、前記第 1 のトランジスタの前記入力端子に

入力された信号を出力する前記第 2 のトランジスタのドレイン端子であり、

前記第 1 の接続導体は第 1 の方向に延在し、前記第 2 の接続導体は前記第 1 の方向とは異なる第 2 の方向に延在し、

前記第 1 の方向と前記第 2 の方向との成す角は、前記基板の前記 1 つの面を平面図として見た場合に 72 ~ 180 度の範囲内であることを特徴とする高周波電力増幅器モジュール。

**【請求項 2 2】**

請求項 2 1 において、

前記第 1 のトランジスタの前記出力端子と前記第 2 のトランジスタの前記入力端子とは

20

30

40

50

整合回路を介して互いに接続されていることを特徴とする高周波電力増幅器モジュール。

【請求項 2 3】

請求項 2 1 において、

前記第 1 のトランジスタの前記入力端子と前記第 2 のトランジスタの前記出力端子とのボンディング部間の距離は 0 . 3 m であり、前記第 1 および第 2 のトランジスタの安定係数は 1 以上であることを特徴とする高周波電力増幅器モジュール。

【発明の詳細な説明】

【0 0 0 1】

【発明の属する技術分野】

本発明は U H F からマイクロ波帯の信号の増幅を行う高周波電力増幅器モジュールに係り 10 、特に小型化の必要な携帯電話機に用いられる高周波電力増幅器モジュールに関する。

【0 0 0 2】

【従来の技術】

トランジスタを用いた高周波電力増幅器モジュールは P D C ( P e r s o n a l D i g i t a l C e l l u l a r ) 方式、 G S M ( G r o b a l S y s t e m f o r M o b i l e c o m m u n i c a t i o n s ) 方式等の移動体通信の携帯電話機のキーデバイスであり、その需要は近年急激に伸びている。また、その仕様としては、移動体通信システムに対する高周波特性の他、小型、低価格であることが要求されている。

【0 0 0 3】

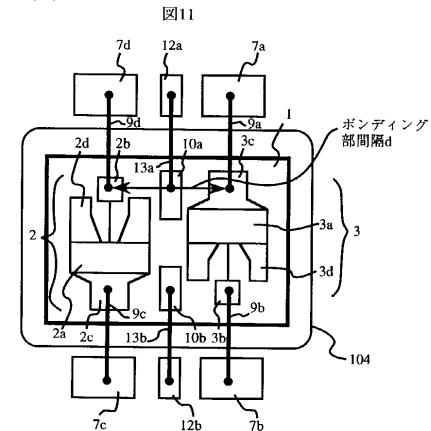

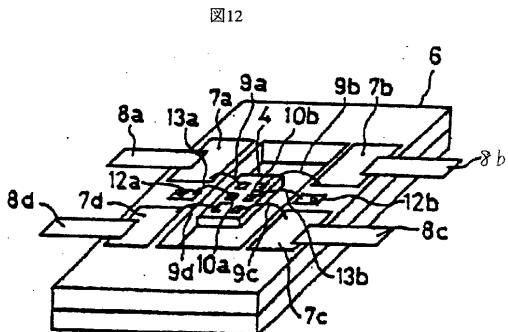

この要求に応える一つの方法が特許公報第 2 7 5 5 2 5 0 号に記載されている。図 1 1 の平面図、図 1 2 の斜視図に示すように、1 つの半導体チップ 1 上に 2 個のトランジスタ 2 , 3 を近接して配置することにより、小型、低価格化している。また、初段トランジスタ 2 のボンディング用入力電極 2 b と配線基板のボンディング用電極 7 d は入力ボンディングワイヤ 9 d で接続されている。2 段目トランジスタ 3 のボンディング用出力電極 3 c と配線基板 6 のボンディング用電極 7 a は出力ボンディングワイヤ 9 a で接続されている。半導体チップ 1 上のボンディング用電極 1 0 a と配線基板 6 のボンディング用電極 1 2 a はシールド用ボンディングワイヤ 1 3 a で接続されている。シールド用ボンディングワイヤ 1 3 a は入力ボンディングワイヤ 9 d と出力ボンディングワイヤ 9 a との間に設けられており、かつその両端のボンディング用電極 1 0 a と 1 2 a は各々半導体チップ 1 および配線基板に形成されたバイアホール ( V i a H o l e ( 図示せず ) ) を通して高周波的に接地されている。このシールド用ボンディングワイヤ 1 3 a を設けることにより、入力ボンディングワイヤ 9 d と出力ボンディングワイヤ 9 a との間の相互インダクタンスによる結合が低減して高周波入出力端子間のアイソレーション劣化を改善することができ、高周波特性が向上する。 30

【0 0 0 4】

入力ボンディングワイヤ 9 d と出力ボンディングワイヤ 9 a との間の相互インダクタンスによる結合の問題は、初段トランジスタ 2 と 2 段目トランジスタ 3 とが、入出力の位置を逆にして並置されているため、両者が近接する結果生じる。この問題は特に、初段トランジスタ 2 の入力ボンディングワイヤ 9 d と、2 段目トランジスタ 3 の出力ボンディングワイヤ 9 a の間で顕著である。これは初段トランジスタ 2 に入力される高周波信号電力に比べ、2 段目トランジスタ 3 から出力される高周波信号電力の方が 2 0 d B ~ 3 0 d B ( 1 0 0 ~ 1 0 0 0 倍 ) 大きく、出力から入力への正帰還が働くことによる。一方、初段トランジスタ 2 の出力ボンディングワイヤ 9 c と 2 段目トランジスタ 3 の入力ボンディングワイヤ 9 b も近接しているが、両者に流れる高周波信号電力の比は 0 d B ( 1 倍 ) 以下と小さく、高周波特性劣化の問題は生じない。 40

【0 0 0 5】

なお、図 1 1 , 1 2 において、2 a , 3 a はトランジスタの本体部分、2 d , 3 d はトランジスタのソース電極、2 c は初段トランジスタ 2 のボンディング用出力電極、3 b は 2 段目トランジスタ 3 のボンディング用入力電極、4 は接地電極、7 b , 7 c は配線基板 6 のボンディング用電極、8 a ~ 8 d はリード電極、1 0 4 はキャビティである 50

。

**【0006】****【発明が解決しようとする課題】**

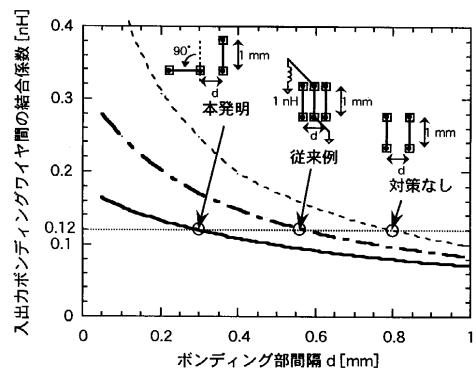

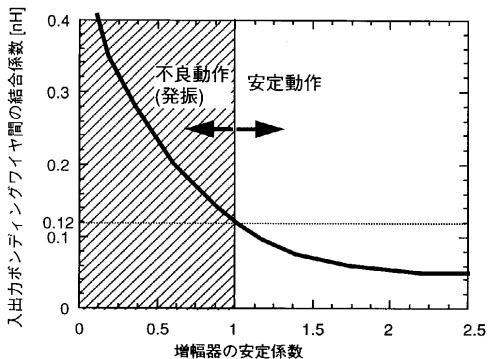

上記従来技術のシールド用ボンディングワイヤ13aの効果を図5により説明する。図5は、増幅器の入出力ボンディングワイヤ間の結合係数（相互インダクタンス（単位：nH））を、長さ1mm（実物に近い長さ）の平行した2本の入出力ボンディングワイヤのボンディング部の間隔dに対し、算出したものである。ここで、結合係数0.12の個所を示す破線は、結合係数が0.12以下のとき増幅器が安定に動作することを示す。この0.12という値は、結合係数と増幅器の安定係数の関係を示す図6から求めた。安定係数が1以上で増幅器は安定に動作する。ここで、ボンディング部の間隔dは、最も近接した2つのボンディングワイヤのボンディング部の中心間の距離で定義される。10

**【0007】**

図5に示されるように、シールド用ボンディングワイヤを設けるという対策を施している上記従来技術の場合は、そうでない場合（図中、「対策なし」と表示）に比べて、結合係数が小さくなっている。また、結合係数が0.12以下のボンディング部の間隔dの範囲が広がり、設計の自由度が増している。さらには、ボンディング部の間隔dを0.55mmまで小さくすることが可能となるため、チップ面積を小さくでき、モジュールの小型化、コストの低減が可能となる。

**【0008】**

しかし、現実には、シールド用ボンディングワイヤ13aの両端にバイアホールによるインダクタンスが直列に加わるため、上記従来技術では充分な高周波特性の向上が得られない。20

**【0009】**

本発明の目的は、より高周波特性を向上させることができる高周波電力増幅器モジュールを提供することにある。

**【0010】****【課題を解決するための手段】**

上記目的は、誘電体材料を基体とする配線基板上に半導体チップが設置された高周波電力増幅器モジュールにおいて、半導体チップに、2段以上の増幅段トランジスタ、これらの増幅段トランジスタへ高周波電力を入力するためのボンディング用入力電極、およびこれらの増幅段トランジスタから高周波電力を出力するためのボンディング用出力電極を設け、ある一つの増幅段トランジスタに対応するボンディング用入力電極と配線基板を接続する入力ボンディングワイヤの両端のボンディング部同士を結ぶ第1の補助線と、この一つの増幅段トランジスタの次段に位置する増幅段トランジスタに対応するボンディング用出力電極と配線基板を接続する出力ボンディングワイヤの両端のボンディング部（その中心部）同士を結ぶ第2の補助線のなす角度が、72~180°の範囲に入るように、かつボンディング用入力電極とボンディング用出力電極のボンディング部の間隔が0.3mm以上0.8mm未満の範囲に入るように高周波電力増幅器モジュールを設計することにより達成できる。30

**【0011】**

ここで、0.3mm以上0.8mm未満というボンディング部間隔の条件にかかわらず、上記2つの増幅段トランジスタの安定係数が1以上となるように高周波電力増幅器モジュールを設計すれば上記目的を達成できる。40

**【0012】****【発明の実施の形態】**

図5に示されるように、本発明の場合は上記従来技術の場合より更に結合係数が小さくなっている。また、結合係数が0.12以下（安定係数が1以上）のボンディング部の間隔dの範囲も更に広がり、設計の自由度が増している。さらには、ボンディング部の間隔dを0.3mmまで小さくすることが可能となるため、チップ面積を更に小さくでき、更なるモジュールの小型化、コストの低減が可能となる。50

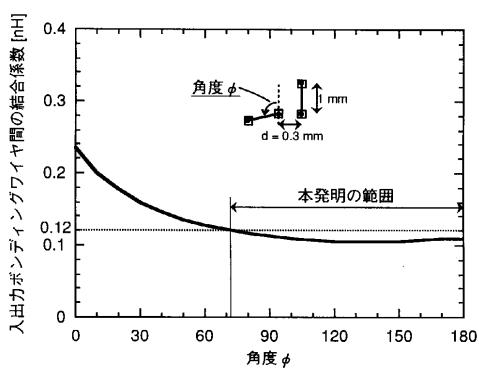

## 【0013】

また、図5は入出力ボンディングワイヤ間のなす角度が $90^\circ$ の場合であるが、図7に示されるように、この角度は $72 \sim 180^\circ$ の範囲にあれば良い。また、角度が $140^\circ$ のとき結合係数が最小になっており、極小点が存在することが分かる。

## 【0014】

本発明の高周波電力増幅器モジュールの具体的設計に当たっては、以上のことと踏まえて、ボンディング部間隔dと角度を選ぶことになる。

## 【0015】

さらには、以上の説明から明らかなように、本発明は角度を従来のように $0^\circ$ にしないことがその根底にある。したがって、角度が $72 \sim 180^\circ$ の範囲にあり、入出力ボンディングワイヤに対応する2つの増幅段トランジスタの安定係数が1以上となるように高周波電力増幅器モジュールを設計しても良い。10

## 【0016】

## 実施例1

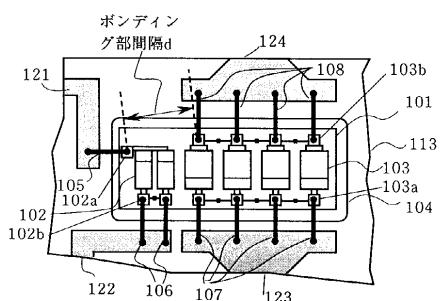

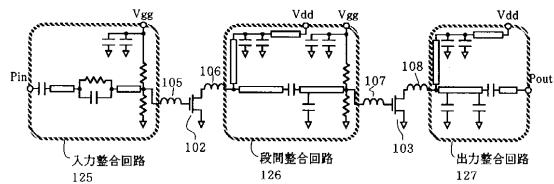

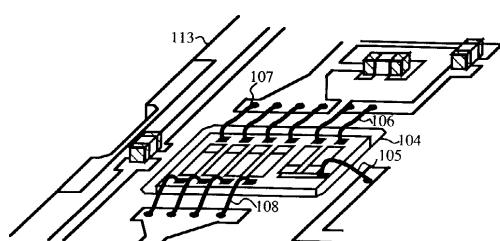

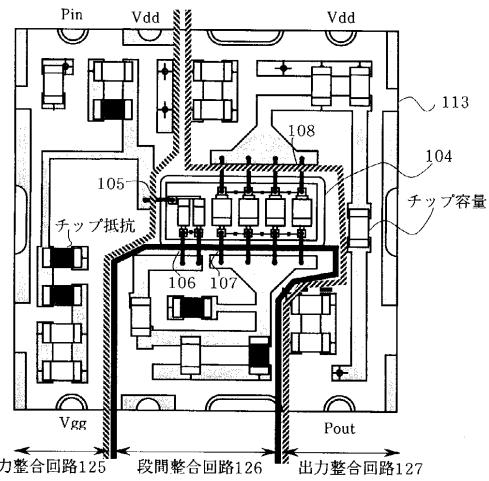

本発明の実施例1の2段電力増幅器モジュールを図1～図4により説明する。図1は要部平面図、図2は等価回路図、図3は外観構成を示す平面図、図4は要部斜視図である。

## 【0017】

図1に示されるように、初段と2段目のMOSFETで構成されたトランジスタ102、103を一つのシリコンチップ101上に近接して形成する。初段トランジスタ102のゲート電極102aからドレイン電極102bへの高周波信号の流れの向きと、2段目トランジスタ103のゲート電極103aからドレイン電極103bへの高周波信号の流れの向きが反対となるようにこれらのトランジスタは配置する。20

## 【0018】

高周波入力端子であるゲート電極102aは、1本の入力ボンディングワイヤ105により、配線基板113上の入力整合回路125の端部121に接続されている。高周波出力端子であるドレイン電極103bは、4本の出力ボンディングワイヤ108により、配線基板113上の出力整合回路127の端部124に接続されている。ゲート電極102aはシリコンチップ101の左側の一辺に沿って配置し、ドレイン電極103bはシリコンチップ101の上側の一辺に沿って配置する。入力ボンディングワイヤ105と出力ボンディングワイヤ108のなす角度は約 $90^\circ$ にする。ボンディングワイヤ106、107は、ドレイン電極102b、ゲート電極103aを、配線基板113上の段間整合回路126の両端部122および123に各々接続されている。初段トランジスタ102のゲート電極102a(ボンディング用入力電極)と2段目トランジスタ103のドレイン電極103b(ボンディング用出力電極)のボンディング部の間隔dは約0.6mmにする。30

## 【0019】

シリコンチップ101は、配線基板113に形成されたキャビティ104の中に搭載する。シリコンチップ101の裏面には、初段トランジスタ102のソース電極および2段目トランジスタ103のソース電極として金属膜を被着し、キャビティ104内の配線を介して接地電位に接続する。配線基板113の材料としては、ガラスセラミックスやアルミニナなどの誘電体基板を用いる。また、その配線には銅や銀、銀白金などを用いる。40

## 【0020】

図2および図3において、記号Pin、Pout、Vgg、Vddはそれぞれ高周波信号入力端子、高周波信号出力端子、ゲート電圧印加端子、ドレイン電圧印加端子であり、これらは電力増幅器モジュールの外部接続端子である。図3において、入力整合回路125、段間整合回路126および出力整合回路127の領域の境界を補助線で示す。また、図4にキャビティ104近辺の立体的様子を示す。

## 【0021】

本実施例において、入力ボンディングワイヤ105と出力ボンディングワイヤ108のなす角度を約 $90^\circ$ としたが、この角度は $72^\circ \sim 180^\circ$ の範囲で選ぶことができる。

## 【0022】

10

20

30

40

50

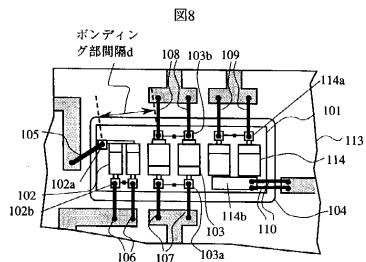

## 実施例 2

本発明の実施例 2 の 3 段電力増幅器モジュールを図 8 の要部平面図により説明する。初段、2 段目、出力段の M O S F E T で構成されたトランジスタ 1 0 2 , 1 0 3 , 1 1 4 を一つのシリコンチップ 1 0 1 上に近接して形成する。初段トランジスタ 1 0 2 のゲート電極 1 0 2 a からドレイン電極 1 0 2 b への高周波信号の流れの向きと、2 段目トランジスタ 1 0 3 のゲート電極 1 0 3 a からドレイン電極 1 0 3 b への高周波信号の流れの向きが反対となるようにこれらのトランジスタは配置する。また、出力段トランジスタ 1 1 4 を、そのゲート電極 1 1 4 a からドレイン電極 1 1 4 b への高周波信号の流れの向きが 2 段目トランジスタ 1 0 3 とは反対の向きとなるように配置する。

### 【 0 0 2 3 】

実施例 1 との違いは、初段トランジスタ 1 0 2 の入力ボンディングワイヤ 1 0 5 と 2 段目トランジスタ 1 0 3 の出力ボンディングワイヤ 1 0 8 とのなす角度を約 1 4 0 ° とした点、および出力段トランジスタ 1 1 4 を同一チップ上に設け、このトランジスタの出力ボンディングワイヤ 1 1 0 と 2 段目トランジスタ 1 0 3 の入力ボンディングワイヤ 1 0 7 とのなす角度を約 9 0 ° 、 2 段目トランジスタ 1 0 3 のゲート電極 1 0 3 a ( ボンディング用入力電極 ) と出力段トランジスタ 1 1 4 のドレイン電極 1 1 4 b ( ボンディング用出力電極 ) のボンディング部の間隔 d を約 0 . 7 m m とし、ここにも本発明を適用した点にある。

### 【 0 0 2 4 】

本実施例によれば、図 7 に示すように、初段と 2 段目の入出力ボンディングワイヤ間の結合係数を最小にでき、アイソレーションをさらに改善できる。また、本発明を適用したので、2 段目と出力段の入出力ボンディングワイヤ間も十分なアイソレーションを確保できる。したがって、半導体チップ面積の縮小の為に同一チップ上に 3 段のトランジスタを形成した本実施例場合でも、これらトランジスタ間の距離が短くなるにもかかわらず、高周波特性を改善できる。

### 【 0 0 2 5 】

## 実施例 3

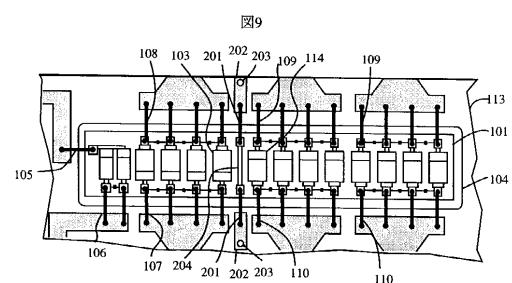

本発明の実施例 3 の 3 段電力増幅器モジュールを図 9 の要部平面図により説明する。実施例 2 との違いは、2 段目トランジスタ 1 0 3 と出力段トランジスタ 1 1 4 との間に、従来技術であるシールド技術を応用して、シールド用ボンディングワイヤ 2 0 1 とシールド配線 2 0 4 を設け、これらの両端を配線基板上の電極 2 0 2 およびバイアホール 2 0 3 を介して接地電位に接続した点にある。

### 【 0 0 2 6 】

本実施例では、初段と 2 段目の間に従来技術であるシールド技術を適用したが、これらのトランジスタ領域は元々面積が広く、高周波特性を改善できる。

### 【 0 0 2 7 】

## 実施例 4

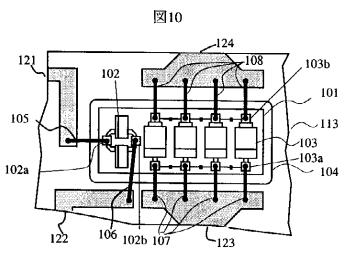

本発明の実施例 4 の 2 段電力増幅器モジュールを図 1 0 の要部平面図により説明する。

### 【 0 0 2 8 】

実施例 1 との違いは、初段トランジスタ 1 0 2 自体の方向を 9 0 ° 回転した点にある。

### 【 0 0 2 9 】

本実施例は、初段と 2 段目との入出力ボンディングワイヤのボンディング部の位置をチップの辺の中央部に移動できるので、ボンディング部間隔をさらに広げることが可能となり（実施例 1 で 0 . 6 m m だったものが 0 . 7 5 m m になる。）、入出力間のアイソレーションをさらに改善できる。

### 【 0 0 3 0 】

以上、本発明を実施例を基に説明したが、本発明は上記実施例に限定されるものではなく、トランジスタの電極数、ボンディングワイヤの本数等はその主旨を逸脱しない範囲において種々変更可能である。また、トランジスタは M O S F E T に限らず他の電界効果トランジスタ、ヘテロ接合バイポーラトランジスタ（ H B T ）等のトランジスタを用いても良

い。

**【0031】**

**【発明の効果】**

本発明によれば、高周波電力増幅器モジュールの高周波特性をより向上させることができ、これに伴い電力増幅器モジュールの小型化、またこれを用いた携帯電話端末の小型・薄型化が可能となる。

**【図面の簡単な説明】**

【図1】本発明の実施例1の2段電力増幅器モジュールの要部平面図である。

【図2】本発明の実施例1の2段電力増幅器モジュールの等価回路図である。

【図3】本発明の実施例1の2段電力増幅器モジュールの外観構成を示す平面図である。 10

【図4】本発明の実施例1の2段電力増幅器モジュールの要部斜視図である。

【図5】本発明および従来技術の入出力ボンディングワイヤ間の結合係数とボンディング部間隔の関係を示す図である。

【図6】入出力ボンディングワイヤ間の結合係数と増幅器の安定係数の関係を示す図である。

【図7】本発明の入出力ボンディングワイヤ間の結合係数と角度の関係を示す図である。

【図8】本発明の実施例2の3段電力増幅器モジュールの要部平面図である。

【図9】本発明の実施例3の3段電力増幅器モジュールの要部平面図である。

【図10】本発明の実施例4の2段電力増幅器モジュールの要部平面図である。

【図11】従来技術の2段電力増幅器モジュールの平面図である。 20

【図12】従来技術の2段電力増幅器モジュールの斜視図である。

**【符号の説明】**

1 … 半導体チップ， 2 … 初段トランジスタ， 2 a … トランジスタの本体部分， 2 b … ボンディング用入力電極， 2 c … ボンディング用出力電極， 2 d … ソース電極， 3 … 2段目トランジスタ， 3 a … トランジスタの本体部分， 3 b … ボンディング用入力電極， 3 c … ボンディング用出力電極， 3 d … ソース電極， 4 … 接地電極， 6 … 配線基板， 7 a ~ 7 d … 配線基板6のボンディング用電極， 8 a ~ 8 d … リード電極， 9 a … 出力ボンディングワイヤ， 9 b … 入力ボンディングワイヤ， 9 c … 出力ボンディングワイヤ， 9 d … 入力ボンディングワイヤ， 10 a， 10 b … ボンディング用電極， 12 a， 12 b … ボンディング用電極， 13 a， 13 b … シールド用ボンディングワイヤ， 101 … シリコンチップ， 102 … 初段トランジスタ， 102 a … ゲート電極（入力電極）， 102 b … ドレイン電極（出力電極）， 103 … 2段目トランジスタ， 103 a … ゲート電極（入力電極）， 103 b … ドレイン電極（出力電極）， 104 … キャビティ， 105 … 入力ボンディングワイヤ， 106 … 出力ボンディングワイヤ， 107 … 入力ボンディングワイヤ， 108 … 出力ボンディングワイヤ， 109 … 入力ボンディングワイヤ， 110 … 出力ボンディングワイヤ， 113 … 配線基板， 114 … 出力段トランジスタ， 114 a … ゲート電極（入力電極）， 114 b … ドレイン電極（出力電極）， 121 … 入力整合回路の端部， 122 … 段間整合回路の端部， 123 … 段間整合回路の端部， 124 … 出力整合回路の端部， 125 … 入力整合回路， 126 … 段間整合回路， 127 … 出力整合回路， Pin … 高周波信号入力端子， Pout … 高周波信号出力端子， Vgg … ゲート電圧印加端子， Vdd … ドレイン電圧印加端子， 201 … シールド用ボンディングワイヤ， 202 … 電極， 203 … バイアホール， 204 … シールド配線。 40

【 図 1 】

図 1

【 図 2 】

☒ 2

【図4】

図4

【 図 5 】

5

【 四 3 】

四 3

【 四 6 】

図6

〔四七〕

四七

【図8】

【図10】

【図9】

【図11】

【図12】

---

フロントページの続き

(72)発明者 長谷 英一

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 山下 喜市

東京都国分寺市東恋ヶ窪一丁目280番地 株式会社日立製作所中央研究所内

(72)発明者 近藤 静雄

東京都小平市上水本町五丁目20番1号 株式会社日立製作所半導体事業本部内

審査官 池渕 立

(56)参考文献 実開昭60-030539(JP,U)

特開昭50-147652(JP,A)

特開平09-027507(JP,A)

(58)調査した分野(Int.Cl.<sup>7</sup>, DB名)

H01L 21/60 301

H01L 21/60 311

H03F 3/00-3/72