(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2005-528596

(P2005-528596A)

(43) 公表日 平成17年9月22日(2005.9.22)

(51) Int.CI.<sup>7</sup>G01R 31/3183

G11C 29/00

F 1

G01R 31/28

G11C 29/00Q

651P

テーマコード(参考)

2G132

5L106

審査請求 未請求 予備審査請求 未請求 (全 18 頁)

|               |                              |

|---------------|------------------------------|

| (21) 出願番号     | 特願2004-502010 (P2004-502010) |

| (86) (22) 出願日 | 平成15年5月6日 (2003.5.6)         |

| (85) 翻訳文提出日   | 平成17年1月11日 (2005.1.11)       |

| (86) 國際出願番号   | PCT/US2003/014328            |

| (87) 國際公開番号   | W02003/093845                |

| (87) 國際公開日    | 平成15年11月13日 (2003.11.13)     |

| (31) 優先権主張番号  | 60/378,488                   |

| (32) 優先日      | 平成14年5月6日 (2002.5.6)         |

| (33) 優先権主張國   | 米国(US)                       |

| (81) 指定国      | JP, KR                       |

|          |                                                                                     |

|----------|-------------------------------------------------------------------------------------|

| (71) 出願人 | 504133464<br>ネクステスト システムズ コーポレイション<br>アメリカ合衆国 カリフォルニア州 95112 サン ホセ モンタレイ ハイウェイ 1901 |

| (74) 代理人 | 100082005<br>弁理士 熊倉 複男                                                              |

| (74) 代理人 | 100067013<br>弁理士 大塚 文昭                                                              |

| (74) 代理人 | 100074228<br>弁理士 今城 俊夫                                                              |

| (74) 代理人 | 100086771<br>弁理士 西島 孝喜                                                              |

最終頁に続く

(54) 【発明の名称】マルチタスク・アルゴリズミック・パターン・ジェネレータを有する半導体試験システム

## (57) 【要約】

【課題】 集積回路( I C )を試験するためのシステム、特にメモリアレイを有する I C を高速試験する方法及び装置を提供する。

【解決手段】 半導体デバイスを試験するためのテスター及び方法。一般的に、本発明のテスターは、マルチタスク・アルゴリズミック・パターン・ジェネレータ( A P G ) ( 201 )を含む。一実施形態では、本発明のテスターは、被試験デバイスタスクレジスタ( 280 )、MicroRAM( 204 )、分歧論理回路( 212 )、データバッファメモリ( 232 )、及びアドレス・トポロジカル・スクランブラー( 222 )を含む。読み取りに対してプログラミングに必要な遅いサイクル速度のために、本発明のテスターは、フラッシュメモリを試験するのに特に有利である。任意的に、より高い処理量に対して、 A P G は、フラッシュの読み取りサイクル中に A P G の最大作動周波数までのロックステップで作動させることができる。

**【特許請求の範囲】****【請求項 1】**

第1及び第2の半導体デバイスを試験するためのマルチタスク装置であって、

第1の半導体デバイスに結合するように構成された第1の組のピン、及び第2の半導体デバイスに結合するように構成された第2の組のピンと、

前記第1の組のピンに結合した少なくとも1つの第1のシグナルジェネレータ、及び前記第2の組のピンに結合した少なくとも1つの第2のシグナルジェネレータと、

前記少なくとも1つの第1のシグナルジェネレータと前記少なくとも1つの第2のシグナルジェネレータとに結合し、前記第1の半導体デバイスに関連するデータを収容する第1のストレージ要素と前記第2の半導体デバイスに関連するデータを収容する第2のストレージ要素とを有するストレージ構成要素と、

前記第1の半導体デバイスが検査を受けている時に、処理及び誘導のためにアクセスされている前記第1のストレージ要素からデータを前記第1の組のピンまで誘導し、前記第2の半導体デバイスが検査を受けている時に、処理及び誘導のためにアクセスされている前記第2のストレージ要素からデータを前記第2の組のピンまで誘導するための、前記ストレージ構成要素に結合したタスクセレクタと、

を含むことを特徴とする装置。

**【請求項 2】**

前記少なくとも1つの第1のシグナルジェネレータは、前記第1の組のピンの各ピンに結合した第1のシグナルジェネレータを含み、

前記少なくとも1つの第2のシグナルジェネレータは、前記第2の組のピンの各ピンに結合した第2のシグナルジェネレータを含み、

前記ストレージ構成要素は、前記第1及び第2のシグナルジェネレータの各々に結合される、

ことを特徴とする請求項1に記載の装置。

**【請求項 3】**

前記第1のストレージ要素はレジスタであり、前記第2のストレージ要素もレジスタであることを特徴とする請求項1に記載の装置。

**【請求項 4】**

前記第1の半導体デバイスに関連する付加的なデータを収容する第1のストレージ要素と、前記第2の半導体デバイスに関連する付加的なデータを収容する第2のストレージ要素とを有する付加的なストレージ構成要素を更に含み、

前記タスクセレクタは、前記第1の半導体デバイスが検査を受けている時に、処理及び誘導のためにアクセスされている前記第1のストレージ要素から前記付加的なデータを前記第1の組のピンまで誘導し、前記第2の半導体デバイスが検査を受けている時に、処理及び誘導のためにアクセスされている前記第2のストレージ要素から該付加的なデータを前記第2の組のピンまで誘導するために前記付加的なストレージ構成要素に結合される、

ことを特徴とする請求項1に記載の装置。

**【請求項 5】**

複数の半導体デバイスを試験するための試験装置であって、

複数の半導体デバイスに結合するようになったマルチタスク・アルゴリズミック・パターン・ジェネレータ(APG)、

を含み、

前記マルチタスクAPGは、第1の時間領域において前記複数の半導体デバイスの第1のものに第1の試験パターンを供給し、第2の時間領域において該複数の半導体デバイスの第2のものに第2の試験パターンを供給するように構成される、

ことを特徴とする装置。

**【請求項 6】**

前記第1の時間領域において前記複数の半導体デバイスの前記第1のものに結合した前記第1の試験パターンは、前記第2の時間領域において前記複数の半導体デバイスの前記

10

20

30

40

50

第2のものに結合した前記第2の試験パターンとは異なることを特徴とする請求項5に記載の試験装置。

【請求項7】

前記第1の時間領域は、前記第2の時間領域と異なる持続時間を含むことを特徴とする請求項5に記載の試験装置。

【請求項8】

前記マルチタスクAPGは、n個のいくつかのストレージ要素と、該いくつかのストレージ要素が前記複数の半導体デバイスに結合される時に経由するセレクタ要素とを有する少なくとも1つのレジスタを含むことを特徴とする請求項5に記載の試験装置。

【請求項9】

前記マルチタスクAPGは、最大n個の異なる試験パターンを最大n個の異なる時間領域における前記複数の半導体デバイスに結合するようになっていることを特徴とする請求項8に記載の試験装置。

【請求項10】

前記マルチタスクAPGは、

MicroRAMアドレスレジスタ、

ループカウンタ及びスタックレジスタ、

アドレス・ジェネレータ、及び

データ・ジェネレータ、

から成る群から選択されたレジスタを含むことを特徴とする請求項8に記載の試験装置

20

。

【請求項11】

前記マルチタスクAPGは、前記少なくとも1つのレジスタに結合した被試験デバイスタスクレジスタを更に含み、

前記被試験デバイスタスクレジスタは、前記第1の時間領域において前記複数の半導体デバイスの前記第1のものに結合される前記いくつかのストレージ要素の1つと、前記第2の時間領域において前記複数の半導体デバイスの前記第2のものに結合される前記いくつかのストレージ要素の1つとを選択するようになっている、

ことを特徴とする請求項8に記載の試験装置。

【請求項12】

前記複数の半導体デバイスの各々が前記いくつかのストレージ要素に結合される時に経由する複数のタイミング及びフォーマット設定回路(T/F)とピン・エレクトロニクス(PE)チャンネルとを更に含み、

前記被試験デバイスタスクレジスタは、前記第1の時間領域において前記複数の半導体デバイスの前記第1のものに結合したT/F及びPEチャンネルのみ、及び前記第2の時間領域において前記複数の半導体デバイスの前記第2のものに結合したT/F及びPEチャンネルのみを使用可能にするようになっている、

ことを特徴とする請求項11に記載の試験装置。

【請求項13】

マルチタスク・アルゴリズミック・パターン・ジェネレータ(APG)を有する試験装置を用いて複数の半導体デバイスを試験する方法であって、

i. APGからの第1の試験パターンの少なくとも一部分を、nを1よりも大きい整数とした時にn個のいくつかの時間領域の第1のものにおける複数の半導体デバイスの少なくとも1つの第1の組に供給する段階と、

ii. 前記APGからの前記第1の試験パターンを前記複数の半導体デバイスの前記第1の組から取り除く段階と、

iii. 前記APGからの第2の試験パターンの少なくとも一部分を、第2の時間領域における前記複数の半導体デバイスの少なくとも1つの第2の組に供給する段階と、

iv. 前記APGからの前記第2の試験パターンを前記複数の半導体デバイスの前記第2の組から取り除く段階と、

40

50

v . 全ての第 1 及び第 2 の試験パターンが前記第 1 及び第 2 の複数の半導体デバイスに印加されるまで、段階 i から i v を繰り返す段階と、

を含むことを特徴とする方法。

**【請求項 1 4】**

前記第 2 の試験パターンを複数の半導体デバイスの第 2 の組に供給する段階は、前記第 1 の試験パターンと異なる第 2 の試験パターンを該複数の半導体デバイスの該第 2 の組に供給する段階を含むことを特徴とする請求項 1 3 に記載の方法。

**【請求項 1 5】**

前記第 2 の試験パターンを第 2 の時間領域において複数の半導体デバイスの第 2 の組に供給する段階は、前記第 1 の試験パターンが前記第 1 の時間領域において前記複数の半導体デバイスの前記第 1 の組に供給される期間と異なる期間に亘って、該第 2 の試験パターンを該複数の半導体デバイスの該第 2 の組に供給する段階を含むことを特徴とする請求項 1 3 に記載の方法。

**【請求項 1 6】**

前記マルチタスク A P G は、少なくとも n 個のストレージ要素と、該ストレージ要素が前記複数の半導体デバイスに結合される時に経由するセレクタ要素とを有する少なくとも 1 つのレジスタを含み、

前記第 1 の試験パターンを複数の半導体デバイスの第 1 の組に供給する段階は、前記第 1 の時間領域において前記複数の半導体デバイスの前記第 1 の組に結合される前記 n 個のストレージ要素の 1 つを選択する段階を含む、

ことを特徴とする請求項 1 3 に記載の方法。

**【請求項 1 7】**

前記マルチタスク A P G は、少なくとも n 個のストレージ要素と、該ストレージ要素が前記複数の半導体デバイスに結合される時に経由するセレクタ要素とを有する少なくとも 1 つのレジスタを含み、

前記第 2 の試験パターンを複数の半導体デバイスの第 2 の組に供給する段階は、前記第 2 の時間領域において前記複数の半導体デバイスの前記第 2 の組に結合される前記 n 個のストレージ要素の 1 つを選択する段階を含む、

ことを特徴とする請求項 1 6 に記載の方法。

**【請求項 1 8】**

前記試験装置は、前記複数の半導体デバイスの各々が前記 n 個のストレージ要素に結合される時に経由する複数のタイミング及びフォーマット設定回路 ( T / F ) とピン・エレクトロニクス ( P E ) チャンネルとを更に含み、

前記第 1 の試験パターンを複数の半導体デバイスの第 1 の組に供給する段階は、前記第 1 の時間領域において該複数の半導体デバイスの該第 1 の組に結合した T / F 及び P E チャンネルのみを使用可能にする段階を含み、

前記第 2 の試験パターンを複数の半導体デバイスの第 2 の組に供給する段階は、前記第 2 の時間領域において該複数の半導体デバイスの該第 2 の組に結合した T / F 及び P E チャンネルのみを使用可能にする段階を含む、

ことを特徴とする請求項 1 3 に記載の方法。

**【請求項 1 9】**

時間領域の数 n を指定し、

前記複数の半導体デバイスの各々を該複数の半導体デバイスの n 組の 1 つに割り当て、前記複数の半導体デバイスの前記 n 組の各々を前記 n 個の時間領域の 1 つに関連付ける、

初期段階を更に含むことを特徴とする請求項 1 3 に記載の方法。

**【請求項 2 0】**

請求項 1 3 に記載の方法に従って試験されたことを特徴とする半導体デバイス。

**【発明の詳細な説明】**

**【技術分野】**

10

20

30

40

50

**【 0 0 0 1 】****関連出願**

本出願は、本明細書においてその全内容が引用により組み込まれている2002年5月6日出願のマルチタスク・アルゴリズミック・パターン・ジェネレータという名称の米国特許仮出願出願番号第60/378,488号に対する優先権を請求するものである。

本発明は、一般的に、集積回路（I C）を試験するためのシステム、より具体的には、メモリアレイを有するI Cを高速試験する方法及び装置に関する。

**【背景技術】****【 0 0 0 2 】**

電子機器業界の製造業者は、試験システム又はテスターを用いて様々な電子構成要素及び集積回路（I C）を自動的に試験し、欠陥デバイスすなわち欠陥I Cを取り除く。大雑把に言って、フラッシュメモリ又はランダム・アクセス・メモリ（R A M）のようなメモリアレイ又は回路の試験に適するもの、及び、マイクロコントローラ、特定用途向けI C（A S I C）、及びプログラマブル・ロジック・デバイス（P L D）のような論理回路の試験に適するものの2種類のデジタルテスターが存在する。一般的に、I Cがまだウェーハ又は基板の一部である間やデバイスをパッケージ化する後だがモジュール、カード、又はボード上に装着、組み立てする前を含む製造工程の間のいくつかのポイントでI Cを試験することが望ましい。この反復的な試験のためには、テスターは高速かつ高い精度で試験を自動的に実行することが必要となる。更に、電子機器業界は、電子デバイス及び回路の小型化を更に進め、それによってより複雑なI Cを可能にしようとする傾向にある。すなわち、I Cがより複雑になると、それにしたがってテスターもより複雑にならなければならない。

10

20

30

**【 0 0 0 3 】**

I Cの機能性を試験するために、タイミング・ジェネレータ及びピン・エレクトロニクス・チャンネルを通じて、特定のタイミング及び電圧設定で被試験デバイス（D e v i c e U n d e r T e s t , D U T）にデータパターンが供給され、次に、被試験デバイスが正しく応答するように、データが特定のタイミング及び電圧設定で被試験デバイスから読み取られる。ピン・エレクトロニクス・チャンネル内の比較器は、被試験デバイス出力信号を予想出力信号と比較し、比較の結果をエラー捕捉メモリに再度結合する。

**【 0 0 0 4 】**

論理回路の被試験デバイスの試験に関しては、データパターンは、一般的にテスター内部の大型半導体メモリに記憶される。メモリ試験に関しては、データパターンは、一般的にテスターに記憶するにはあまりにも長すぎる。メモリの被試験デバイスの規則的なアレイ構造のために、データパターンは、アルゴリズミック・パターン・ジェネレータ（A P G）として公知の特別製コンピュータを用いてアルゴリズム的に生成することができる。この技術は、多年に亘って実施されており、メモリ試験データパターンを生成する業界標準方法である。

30

**【 0 0 0 5 】**

フラッシュメモリの被試験デバイスの試験は、他の種類のメモリデバイスの試験に比べて独特な一組の難問を呈する。フラッシュメモリは、各デバイス上の各セルに異なるプログラミング時間及び電圧を要求することがあるプログラム可能デバイスである。プログラミングは、アルゴリズミック・パターン・ジェネレータを通じて行われるので、最高の処理量は、各被試験デバイスがその独自のA P Gを有する時に得ることができると現時点では考えられている。

40

**【 0 0 0 6 】**

多くの従来技術のメモリテスターは、いくつかの被試験デバイスを同時に試験するため、多くのタイミング・ジェネレータ及びピン・エレクトロニクス・チャンネルに論理出力される1つのA P Gを有してきた。この手法を用いてフラッシュメモリが試験される時、フラッシュメモリが、その読み取りサイクルに比べて非常に遅い速度でプログラムし、A P Gが先に進むことができる前に全ての被試験デバイスは最も遅い被試験デバイスがブ

50

プログラミングを終えるのを待つ必要があるために、試験時間が極度に増大する。すなわち、プログラミング中は、A P G は、一般的に遅いサイクル速度で実行され、テスターリソースの効率及び利用度を減少させる。テスター内により多くのA P G を置き、各被試験デバイスに独立性を与えることによってこの問題に対処するために、専用の従来型フラッシュメモリテスターが試してきた。

#### 【0007】

少数の物理的ピンを包含し、多くの信号がこれらのピン上に多重化されたフラッシュの被試験デバイスは、ますます一般的になっている。このようなフラッシュの被試験デバイスの例は、典型的に16ピンを有するN A N D フラッシュの被試験デバイスである。小型ピンカウントプログラム可能メモリのより極端な例は、単に4つの信号ピンを有する直列E E P R O Mである。これらの被試験デバイスの生産は、費用重視的であり、非常に廉価なテスターの使用だけをサポートすることができる。しかし、被試験デバイス毎の独立性の増大をもたらすためにテスター内のA P G の数を増すことは、テスターのコストを法外に増大させる。すなわち、A P G の数の増加は、完全に満足できる解決策ではない。

#### 【0008】

従って、A P G の利用を最大化することによりテスターリソースの効率及び利用度を増加させるテスター及びそれを使用する方法に対する必要性が存在する。複数の被試験デバイスを独立に試験する時に被試験デバイス毎の効率を増大し、A P G の最大サイクル速度でのロックステップにおいて、例えば、フラッシュの被試験デバイスの読み取りサイクル中に複数の被試験デバイスを試験することもできるテスター及び方法に対する更なる必要性も存在する。

本発明のシステム及び方法は、従来技術を超える上記及び他の利点を提供する。

#### 【0009】

【特許文献1】米国特許仮出願一連番号第60/378,488号

【特許文献2】米国特許出願一連番号第09/895,439号

【特許文献3】米国特許出願一連番号第10/039,738号

【特許文献4】米国特許出願一連番号第10/170,916号

#### 【発明の開示】

#### 【0010】

本発明は、メモリアレイを有するI C の高速試験のための装置及び方法に関する。

本発明の一態様によれば、半導体デバイスを試験するための半導体試験装置又はテスターが提供される。一般的に、テスターは、マルチタスク・アルゴリズミック・パターン・ジェネレータ(A P G )を含む。マルチタスク機能は、A P G に单一のパターン・ジェネレータ上で複数のプログラムを同時に実行させる。一実施形態では、マルチタスクA P G は、最大8つの経路までタイムスライスされ、单一A P G を用いて128ピン試験サイト上の8つの独立16ピンの被試験デバイス上で最大8つの試験プログラムまでを独立かつ同時に実行することを可能にする。マルチタスク法は、パターンを進む前にどの被試験デバイスも別の被試験デバイスが作動を終了するのを待たないように各被試験デバイスに対して独立に検査を提供することにより、パターン実行におけるデッドサイクルを排除することによってテスターリソースの効率及び利用度を増大させる。

#### 【0011】

別の態様では、本発明は、マルチタスクA P G を有する装置又はテスターを用いて被試験デバイスを試験する方法に関する。

更に別の態様では、本発明は、本発明の方法に従ってマルチタスクA P G を有する装置又はテスターを用いて試験された半導体デバイスに関する。

本発明の上記及び様々な他の特徴及び利点は、添付図面と共に以下の詳細説明を読むと明らかになるであろう。

#### 【発明を実施するための最良の形態】

#### 【0012】

本発明は、マルチタスク・アルゴリズミック・パターン・ジェネレータ(A P G )を有

10

20

30

40

50

するテスターを用いて集積回路（ＩＣ）を効率的かつ高速で試験するためのシステム及び方法に関する。

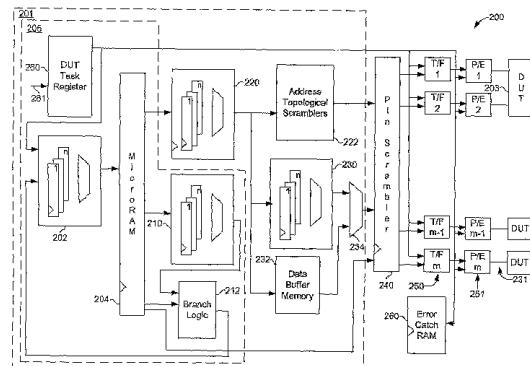

1つ又はそれ以上の被試験デバイス（被試験デバイス203）を試験するための本発明の一実施形態によるマルチタスクＡＰＧ201を有する試験システム又はテスター200を、ここで図1を参照して以下に説明する。被試験デバイス203により、任意の電子構成要素モジュール、又は、論理回路、メモリアレイ、又はその両方を有するＩＣを意味する。被試験デバイス203は、例えば、ダイ及びパッケージとすることができる、又は、基板上のいくつかのデバイスの1つとすることができる。被試験デバイス203は、いくつかのピン231を通じて又は基板（図示しない）上のパッドを接続するプローブ（図示しない）を通じて試験システム200に結合することができる。ただ1つの被試験デバイスが示されているが、試験システム200は、複数の被試験デバイス203を並行試験するのに十分に大きないくつかの試験サイトを含むことができ、また、好ましくはそれを含むことが認められるであろう。

10

#### 【0013】

明確にするために、公知で本発明に関連のないテスターの詳細の多くは省略されている。テスターは、例えば、本出願人に譲渡されて現在特許申請中の「二重データ速度ピンスクランブルを有する半導体試験システム」という名称の2001年6月29日出願の米国特許出願一連番号第09/895,439号、「半導体デバイスを試験するためのパターンスクランブラーを有する装置及びそれを作動する方法」という名称の2002年1月4日出願の米国特許出願一連番号第10/039,738号、及び「スタッカ可能半導体試験システム及びそれを作動する方法」という名称の2002年6月12日出願の米国特許出願一連番号第10/170,916号に更に詳細に説明されており、その各々の全内容は、本明細書において引用により組み込まれている。

20

#### 【0014】

図1を参照すると、テスター200は、一般的に、マルチタスクＡＰＧ201に加えて、ピン・スクランブラー240、いくつかのタイミング・ジェネレータ及びフォーマット回路（Ｔ／Ｆ250）、及びＴ／Ｆと被試験デバイス203のピン231との間に結合したいくつかのピン・エレクトロニクス（ＰＥ）回路又はチャンネル251を含む。試験サイトコンピュータ（図示しない）及びクロックは、クロックサイクルを有するタイミング又はクロック信号を供給するため及びその作動を制御するために、マルチタスクＡＰＧ201内の他の全ての構成部品又は要素、ピン・スクランブラー240、及びＴ／Ｆ250に結合する。

30

#### 【0015】

ピン・スクランブラー回路240は、マルチタスクＡＰＧ201のいくつかの出力のいずれか、及びＴ／Ｆ250のいずれかに結合し、Ｔ／Ｆを通じていずれかの被試験デバイス203上のピン231のいずれかに結合する。ピン・スクランブラー240の機能は、被試験デバイス203のピン231のいずれもが各クロックサイクルでＡＰＧ201内のどのパターンソースからも駆動されることを可能にすることである。更に、被試験デバイス203の各ピン231に結合したマルチタスクＡＰＧ201の出力は、サイクル毎に決めるか又は選択することができる。すなわち、マルチタスクＡＰＧ201からの試験信号又はパターンは、特定の被試験デバイス203上の特定のピン231に結合することができ、被試験デバイスへの接続の再配線又はマルチタスクＡＰＧ201の大規模な再プログラミングなしにオンザフライで切り換えるか又は変えることができる。図1に示すテスター200では、ピン・スクランブラー240は、マルチタスクＡＰＧ201によって制御され（制御用の接続は示していない）、例えば、サイクル毎に被試験デバイス203の各ピン231上の64の異なるパターンマッピングを可能にるように設計することができる。ピン・スクランブラー240を有するテスター200は、米国カリフォルニア州サンホセ所在のネクステスト・システムズ・インコーポレーテッドから市販されており、より詳細には、本出願人に譲渡されて現在申請中の米国特許出願一連番号第09/895,439号に説明されている。

40

50

## 【0016】

T/F250は、試験パターンの様々な信号、すなわち、マルチタスクAPG201から受信した駆動／予測データ信号、ストローブ制御信号、及び入力／出力(I/O)制御信号のタイミング及びフォーマット設定を調節し、マルチタスクAPGからの出力をPEチャンネル251を通じて被試験デバイス203に結合する。

各PEチャンネル251は、一般的に、試験パターン又は信号の3ビット部分をマルチタスクAPG201からT/F250を通じて受け取り、各3ビット信号は、駆動／予測データ信号、ストローブ制御信号、及びI/O制御信号を含む。いくつかの試験システムは、これらの(典型的には)3ビットを8つのPE制御機能の組合せに符号化する。各PEチャンネル251は、一般的に、信号を被試験デバイス203のピン231に結合することができるPEドライバ(図示しない)、出力信号を予測出力信号と比較するための比較器(図示しない)、及び比較の結果をマルチタスクAPG201を通じてエラー捕捉RAM260に再度結合するためのエラー論理回路(図示しない)を含む。一般的に、PEドライバ及び比較器は、ピン231がデータ又は制御信号を受信するか又は所定の時間に結果を送信するかのいずれかであるから、PEチャンネル251においては同時に作動しない。

## 【0017】

マルチタスクAPG201は、制御部分205、レジスタベースのアルゴリズミック・アドレス・ジェネレータ220、アドレス・トポロジカル・スクランブラー222、データ・ジェネレータ230、及びデータマルチプレクサ234を含む。マルチタスクAPG201は、デッドサイクルなしに作動の全てのクロックサイクル毎にデータパターンを生成する能力を有し、デッドサイクルとは、マルチタスクAPGは計算するが、被試験デバイス203に対してデータを何も発生しないサイクルである。データパターンにデッドサイクルがないということは、被試験デバイス203がその最も厳しいタイミング限界で実施されるので、最も厳しい試験を受けることを意味する。デッドサイクルは、より緩い試験をもたらすであろう。更に、デッドサイクルは、試験時間を増大させる。

## 【0018】

マルチタスクAPG201の制御部分205は、マルチタスクAPG、ピン・スクランブラー240、T/F250、及びPEチャンネル251の作動を制御し、MicroRAMアドレスレジスタ202、MicroRAM204、ループカウンタ及びスタックリジスタ又はレジスタベースのループカウンタ及びスタックリ210、分岐論理回路212、及び被試験デバイスタスクレジスタ280のようなタスクセレクタから成ることができる。制御部分205は、実行が開始されるとそれ自体を制御する閉ループシステムである。通常の作動では、テスター200のユーザは、ホストコンピュータ(図示しない)によってMicroRAM204に読み込まれるアルゴリズム的パターンを書き込む。MicroRAM204は、一般的に、幅が100から200ビットであり、深さが数百から数万ワードである。MicroRAM204からのビットのいくつかは、マルチタスクAPG201のプログラムの流れを制御し、同時にMicroRAMからの他のビットは、被試験デバイス203に対するデータパターンを発生するレジスタを制御する。

## 【0019】

MicroRAM204にユーザ書き込みプログラムがロードされた状態で、マルチタスクAPG201は、クロックを発生させることにより実行が開始される。MicroRAMアドレスレジスタ202は、実行される次の命令を指すようにMicroRAM204をアドレス指定する。MicroRAM204は、制御ビットをループカウンタ及びスタックリ210と分岐論理回路212とに出力する。ループカウンタ及びスタックリ210は、分岐論理回路212と共に、MicroRAMアドレスレジスタ202の中にロードする次のMicroRAMアドレスを判断する。ループカウンタは、カウント値に達するまで命令を実行させ、次に、分岐論理回路212は、新しいMicroRAMアドレスレジスタ値をロードする。スタックリは、サブルーチンが実行された時に、戻りMicroRAMアドレスを供給する。分岐論理回路212は、一般的に、上述のループカウンタを含む

10

20

30

40

50

様々な条件に基づいて、ジャンプ、サブルーチンコール、及びサブルーチンリターンを可能にする。パターンを実行するこの処理は、分岐論理回路 212 がマルチタスク APG 201 の停止専用の MicroRAM 204 ビットコードにより中断するように命令されるまで続けられる。

#### 【0020】

制御部分 205 が上述のように実行されている間、MicroRAM 204 からの追加のビットは、被試験デバイスアドレス、被試験デバイスデータ、及び恐らくは他の機能をアルゴリズム的に発生させるために、マルチタスク APG 201 の他の部分に同時に送られている。図 1 は、MicroRAM 204 によって駆動されているレジスタベースのアルゴリズミック・アドレス・ジェネレータ 220 を示している。アドレス・ジェネレータ 220 の出力は、アドレス・トポロジカル・スクランブラー 222 及びデータ・ジェネレータ 230 を駆動する。アドレス・トポロジカル・スクランブラー 222 は、一般的にランダム・アクセス・メモリであり、これは、トポロジー的に真のデータパターンを、被試験デバイス 203 のピン 231 に印加されたアドレスをしばしばスクランブル処理する被試験デバイスのアドレス符号器（図示しない）に通した後に、被試験デバイスの内部アレイ（図示しない）に供給する。

#### 【0021】

レジスタベースのデータ・ジェネレータ 230 は、被試験デバイス 203 に対するデータパターンをアルゴリズム的に発生し、アドレス・ジェネレータ 220 によって送られるアドレスに基づいて、パターンを条件付で反転させることができる。アルゴリズム的データに加えて、いくつかの被試験デバイス 203 は、記憶された応答データパターンを被試験デバイスアドレスの関数として要求する。この例は、データパターンが永久的に被試験デバイス 203 内にプログラムされる読み出し専用メモリ（ROM）であろう。データバッファメモリ 232 は、ランダム・アクセス・メモリであり、これは、アドレス・ジェネレータ 220 からのアドレスの関数として供給された記憶応答データパターンを保持する。MicroRAM 204 を通じての試験プログラムは（制御用の接続は示していない）、どのデータソースがデータマルチプレクサ 234 を通して被試験デバイスに送られるかを制御することができる。

図 1 に示すテスター 200 は、アドレス・トポロジカル・スクランブラー 222、データマルチプレクサ 234、及び他のマルチタスク APG データソースの出力をピン・スクランブラー 240 を通じて経路指定する。

#### 【0022】

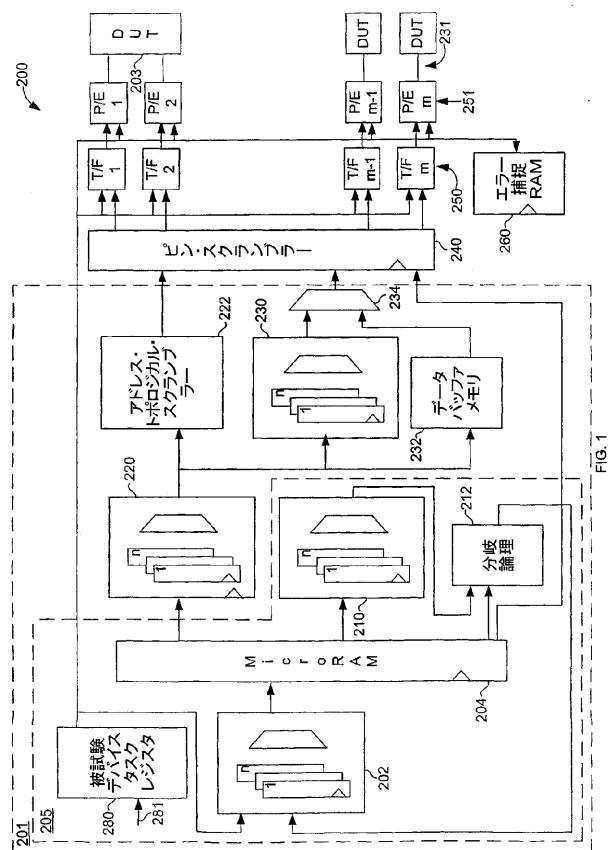

microRAM アドレスレジスタ 202、ループカウンタ及びスタッカ 210、アドレス・ジェネレータ 220、及びデータ・ジェネレータ 230 で使用するためのストレージ構成要素又はレジスタを、ここで図 2 を参照して以下に更に詳細に説明する。図 2 は、本発明のマルチタスク APG 201 で使用するためのマルチタスク APG ストレージ構成要素又はレジスタ 270 の実施形態のブロック図である。本発明によると、マルチタスク APG レジスタ 270 は、n 個のストレージ要素又はレジスタ 272、273、及び 274 と、レジスタ 272、273、及び 274 から供給されるマルチプレクサ 276 のようなセレクタ要素又は機構とで構成される。各レジスタ 272、273、及び 274 は、マルチプレクサの選択と同期した別々のクロックイネーブル（図示しない）を有する。例えば、マルチプレクサ 276 が第 1 の入力を選択する時は、第 1 のレジスタ 272 のクロックだけが使用可能にされる。マルチプレクサが n 番目の入力を選択する時は、n 番目のレジスタ 274 のクロックだけが使用可能にされる。すなわち、マルチタスク APG 201 内のレジスタ 272、273、及び 274 は、各被試験デバイス 203 に対して別々の値を保持することができる。

#### 【0023】

本発明のマルチタスク APG 201 は、遅い速度の作動に対して独立した APG 機能を与えることにより、ピン数の少ない被試験デバイス 203 を試験するためのテスター 200 のハードウェアコストを低減する。高速作動が必要な時は、被試験デバイスを最大 AP

G速度のロックステップで作動し、処理量を最大にして、低速APGが与えるものよりも厳しい試験条件を提供することができる。すなわち、フラッシュメモリのような被試験デバイス203をプログラムする際には、マルチタスクAPG201は、試験パターンが被試験デバイスをプログラムするのに必要である限りにおいてのみ各被試験デバイスに対して独立にブロードキャストされるか又は書き込まれるマルチタスクモードで作動される。対照的に、プログラミングに適用される従来のテスターは、最後の最も遅い被試験デバイスがプログラムされるまで、全ての被試験デバイスに対して同時にパターンを試験する。試験パターンを各被試験デバイス203に書き込むことは、それ独自でいくつかの有益な効果をもたらす。第1に、所定の期間により多数の被試験デバイス203の並行試験を可能にすることによってテスター200の処理量を最大にするマルチタスクAPG201リソースのより効率的な利用法が存在する。これは、プログラミングが、一般的に、いくつかのパターンを各被試験デバイス203に書き込むことを伴うからである。例えば、いくつかの被試験デバイス203を並行にプログラムすることは、デバイスのメモリセルを覆って対角線状パターンを各被試験デバイスに書き込み、次に、いくつかの縞を書き込むことを含むであろう。すなわち、より迅速にプログラムする被試験デバイス203に対しては、テスターは、最も遅い被試験デバイスが対角線状パターンをプログラムするのを待つのではなく、以前にプログラムされた対角線状パターンの上への縞パターンの書き込みを始めることができる。第2に、プログラミング信号又は試験パターンは、被試験デバイスをプログラムすることが必要であるかぎりにおいてのみ各被試験デバイス203に適用されるので、各被試験デバイスは、デバイスに対する閾値をちょうど超えた蓄積電荷を使用してプログラムされ、その後の被試験デバイス電荷又はプログラム保持能力の試験は、より高い初期電荷で開始した被試験デバイスのいくつかによる誤ったポジティブな結果を生み出す可能性が低いことになる。

#### 【0024】

全ての被試験デバイス203が問題なくプログラムされた後で、マルチタスクAPG201は、プログラムされたパターンを全ての被試験デバイスから同時に読み戻すために最大APG速度のロックステップで作動され、それによって処理量を最大にできる。

上述の通り、フラッシュメモリは、それらの讀取サイクルに比べて非常に遅い速度でプログラムする。すなわち、プログラミング中は、APGは、一般的に遅いサイクル速度で作動する。この事実を利用して、ハードウェアを時間多重化して出力を適切な被試験デバイスに誘導することにより、また、各被試験デバイス又はタスクに対してAPG時間をタイム・シェアリング又はタイムスライスすることにより、高速マルチタスクAPG201を複数の独立したより遅いAPGに見えるようにすることができます。例えば、20ナノ秒のサイクル速度で作動するAPGは、連続するサイクルにおいて4つの被試験デバイスの各々を順次駆動することができるであろう。第1の被試験デバイスは、情報が計算されて最初の20ナノ秒サイクルで起動され、第2の被試験デバイスは、2番目の20ナノ秒サイクルで、第3の被試験デバイスは、3番目の20ナノ秒サイクルで、第4の被試験デバイスは、4番目の20ナノ秒サイクルで起動される。最初の被試験デバイスに再度戻った時には80ナノ秒が過ぎており、従って、第1の被試験デバイスは、80ナノ秒の有効サイクル時間を見ることになり、他の被試験デバイスの各々も、時間が交互するが同様である。

#### 【0025】

これは、従来技術のAPGに使用される従来のレジスタがレジスタのようなマルチタスクAPGストレージ構成要素270によって置き換えられた図1に見ることができる。MicrORAMアドレスレジスタ202、ループカウンタ及びスタッカ210、アドレス・ジェネレータ220、データ・ジェネレータ230は、全てマルチタスクAPG201におけるマルチタスクAPGレジスタ270である。これらのマルチタスクAPGレジスタ202、210、212、及び220は、どの被試験デバイス203がアクティブなタイムスライスにおいて検査を行うかを指定する被試験デバイスタスクレジスタ280のよ

10

20

30

30

40

50

うなタスクセレクタから制御を受ける。被試験デバイスタスクレジスタ280には、マルチタスクモードで検査を受けることになる被試験デバイスの数を含む情報がホストコンピュータ（図示しない）から入力又はコンピュータバス281を通じてロードされる。

#### 【0026】

一実施形態では、被試験デバイスタスクレジスタ280は、基本的には、検査を受ける被試験デバイス203の数をnとする時に1からnまで計数するカウンタである。被試験デバイスタスクレジスタ280の出力は、バイナリコード、n個の独立したイネーブルの組、又は、何らかの他のフォーマット又はフォーマットの組合せとしてブロードキャストすることができる。

代替的に、被試験デバイスタスクレジスタ280は、サイクル速度（周期）と、被試験デバイス203が試験されるサイクル開始時間又は順番と、各被試験デバイスに適用される試験パターンとを独立に検査することができるインテリジェントコントローラである。すなわち、各被試験デバイス203は、その独自の周期（サイクル速度）を有することができ、各被試験デバイスサイクルの始めは、時間が交互していない（又は、交互する必要はない）。被試験デバイスサイクルの始めは、他の被試験デバイスに対するタイミングに関わらず、時間のどこからでも起こる可能性がある。この実施形態では、被試験デバイスタスクレジスタ280は、各被試験デバイス203に対して次に来るサイクルの周期を見て、所定の判断基準に基づき（i）次に来るサイクルでどの被試験デバイスがマルチタスクAPG201を使用するようになるか、及び（ii）その特定の被試験デバイスに対してT/F250を通じて何時データを伝達させるかを決めることができるインテリジェントコントローラである。所定の判断基準は、例えば、データをT/F250に伝達させるためのリアルタイムで変化する可変長さのバイオペラインと、各被試験デバイス203のサイクル速度又は周期とを含むことができる。この実施形態の1つの好ましいバージョンでは、被試験デバイスタスクレジスタ280は、3ビットコードではなくT/F250に対する別々のイネーブルを使用し、それによってデータが必要に応じて各被試験デバイスに独立に移動することを可能にする。

#### 【0027】

従来技術のAPGにおけるように、マルチタスクAPG201は、アルゴリズム的にパターンを計算するために、著しい量の組合せ論理回路及びRAMを含む。また、アドレス・トポロジカル・スクランbler222及びデータバッファメモリ232にも、かなりのRAMがある。組合せ論理回路又はRAMのいずれもマルチタスクAPG201内で反復されず、それによってかなりのハードウェアコストを節約する。

#### 【0028】

被試験デバイスタスクレジスタ280はまた、ピン・スクランbler240及びT/F250に接続される。タイミングが取られフォーマット設定された信号は、被試験デバイスに到達する前の正確な電圧調整のためにピン・エレクトロニクス・チャンネル（P/E251）を通過する。ピン・エレクトロニクス・チャンネル251は、一般的に、試験ベクトルやデータを被試験デバイス203のピンに印加するためのPEドライバ、被試験デバイス出力信号を予測出力信号と比較するための比較器、及び比較結果をエラー捕捉メモリ又はエラー捕捉RAM260に再度結合するためのエラー論理回路を含む。

#### 【0029】

APG201内のこの点では、信号は、被試験デバイス203あたりのピンレベルで分離される。ピン・スクランbler240は切り換わることができるが、被試験デバイスタスクレジスタ280は、タイミング・ジェネレータ及びフォーマット設定器250に対して、計時してアクティブな被試験デバイスに対してのみ送信するように命令することになる。非アクティブな被試験デバイス203上のタイミング・ジェネレータ及びフォーマット設定器250は、新しいデータをラッチするためのイネーブルを受け取らないことになり、従って、それらが行っていた作動がどれであれ、それを継続することになる。

#### 【0030】

エラー捕捉RAM260は、エラー捕捉メモリのどの部分をエラー記録のために使用す

10

20

30

40

50

るかを教える被試験デバイスタスクレジスタ280信号を受け取る。エラー捕捉RAM260は、単に、被試験デバイスタスクレジスタ280をポインタとして用いて被試験デバイス203毎に再分割することができる大型ランダム・アクセス・メモリである。

マルチタスクAPG201は、テスター200が単一のパターン・ジェネレータ上で複数のプログラムを同時に実行することを可能にする。プログラムを同時に実行する間、マルチタスク作動システムは、マルチタスクAPG201作動をタイムスライスし、プログラムが終了するまで、連続ループで小さな時間区分の間、各プログラムに対してマルチタスクAPGリソースを与える。プログラムに対する処理は、時間的にインターリーブされる。

#### 【0031】

一実施形態では、マルチタスクAPG201のハードウェア又はリソースは、最大8つの経路にタイムスライスされ、最大8つの試験プログラムが、単一APG上で独立かつ同時に実行されることを可能にする。例えば、マルチタスクAPG201を有するテスター200の128ピン試験サイトは、最大8つの経路に分割され、最大8つの独立した16ピンの被試験デバイス試験サイトをもたらす。各16ピン被試験デバイス試験サイトに対するタイミング及びフォーマット設定は、T/F250を通じて独立に分配される。

#### 【0032】

マルチタスクAPG201が試験信号又はパターンを被試験デバイス203にブロードキャストする準備ができた時は、その被試験デバイスのみ（他の被試験デバイスではなく）に付随する試験サイト上のタイミングシステムがロードされる。この試験サイトのタイミングシステム又はT/F250がこのロードした被試験デバイスサイクルを実行している間に、マルチタスクAPG201は、引き続いて他の被試験デバイスサイトに対して同じことを行う。

#### 【0033】

マルチタスク機能は、パターン実行におけるいかなるデッドサイクルも発生させない。パターンは、ちょうど従来のAPG上で実行されるように実行される。ユーザは、従来のAPGを用いて行うように、ホストコンピュータ（図示しない）からマルチタスクAPG201に全ての試験パターンを書き込み、マルチタスク・ハードウェアのどれも管理する必要はない。ユーザが認識する必要がある唯一のものは、試験される被試験デバイス203の数又はマルチタスクAPG201リソースが分割される時間領域、及びマルチタスクモードで利用可能な最大サイクル時間である。

#### 【0034】

並行して試験される被試験デバイス203の数又は時間領域がマルチタスクモードにおいて増加すると、特定の被試験デバイス又は試験サイトでの最大サイクル速度が減少する。これは、試験サイトの増加がマルチタスクAPG201からより多くのタイムスライスを要求し、全てのプログラムを処理するのにより多くの合計時間がかかるからである。これは、被試験デバイスアレイ読み取りに対して被試験デバイスプログラミングに必要なサイクル時間とサイトの独立性との性質から、フラッシュメモリ試験に対しては恩典である。

#### 【0035】

一実施形態では、マルチタスクAPG201は、20ナノ秒周期である50MHzの最大サイクル速度を有する。以下の表1は、被試験デバイスサイト上で利用可能な例示的な最大サイクル速度をマルチタスクされる被試験デバイスの数に対して示すものである。

#### 【0036】

【表1】

| マルチタスク被試験デバイス | 最大被試験デバイスサイト周波数（周期） |

|---------------|---------------------|

| 1             | 50MHz (20ナノ秒)       |

| 2             | 25MHz (40ナノ秒)       |

| 4             | 12.5MHz (80ナノ秒)     |

| 8             | 6.25MHz (160ナノ秒)    |

| n             | 最大周波数/n             |

## 【0037】

遅いサイクル速度でのフラッシュメモリプログラミングに対しては、マルチタスクを用いて独立の被試験デバイスサイトによる最大の処理量を達成することができる。高速の被試験デバイスアレイ読み取り（より高速のためにより高い処理量を意味する）に対しては、被試験デバイスサイトは、最大50MHzのロックステップで実行することができる。すなわち、このようなマルチタスクAPGは、独立した16ピンの被試験デバイスサイトを、従来の並行試験モードでの最大6.25MHz及び最大50MHzの作動で全て1つのハードウェアから供給する。

## 【0038】

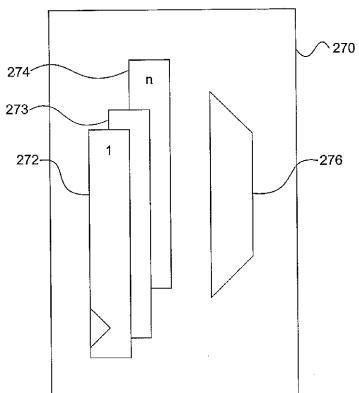

第1及び第2の被試験デバイス203を試験するための処理又は方法の実施形態を、ここで図3を参照して以下に説明する。図3は、いくつかの被試験デバイス203に対してマルチタスクモードで並行して書き込むか又はプログラムするマルチタスクAPG201を有するテスターを作動するための処理の実施形態を示す流れ図である。

図3を参照すると、処理は、被試験デバイス203を試験するためのいくつかのビットを含む試験信号又はパターンをマルチタスクAPG201にロードすることにより始まる（段階300）。これは、ホストコンピュータからMicroRAMアドレスレジスタ202及び被試験デバイスタスクレジスタ280へ、それぞれコンピュータバス282及びコンピュータバス281を通じてロードすることにより達成される。一般的に、これは、試験パターンをMicroRAMアドレスレジスタ202に、また、マルチタスクAPG201が分割されることになる時間領域の数と各時間領域において検査を受けることになる被試験デバイスのPEチャンネルの数及びアイデンティティとを含む情報を被試験デバイスタスクレジスタ280にロードする段階を伴う。次に、第1の試験パターンは、いくつかの時間領域の最初の時間領域において、被試験デバイス203の少なくとも1つの第1の組に結合されるか又はそれに供給される（段階305）。試験パターンは、1ビットからPEチャンネル251又は被試験デバイス203上のピン231の数に等しい幅までの幅を有することができる。第1の試験パターンが関連T/F250を通じて第1の組の被試験デバイス203に完全に供給された後に、第1の試験パターンは、第1の組の被試験デバイスから分離されるか又は取り除かれ（段階310）、第2の試験パターンが、第2の時間領域において第2の組の被試験デバイスに結合されるか又はそれに供給される（段階315）。ここでもまた、第2の試験パターンが関連T/F250を通じて第2の組の被試験デバイス203に完全に供給された後に、第2の試験パターンは、第2の組の被試験デバイスから分離されるか又は取り除かれ（段階320）、第1及び第2の試験パターン全体が第1及び第2の組の被試験デバイスに印加されるか又は供給されるまで、すなわち、全ての被試験デバイス203が完全にプログラムされるまで、段階305から320が繰り返される（段階325）。

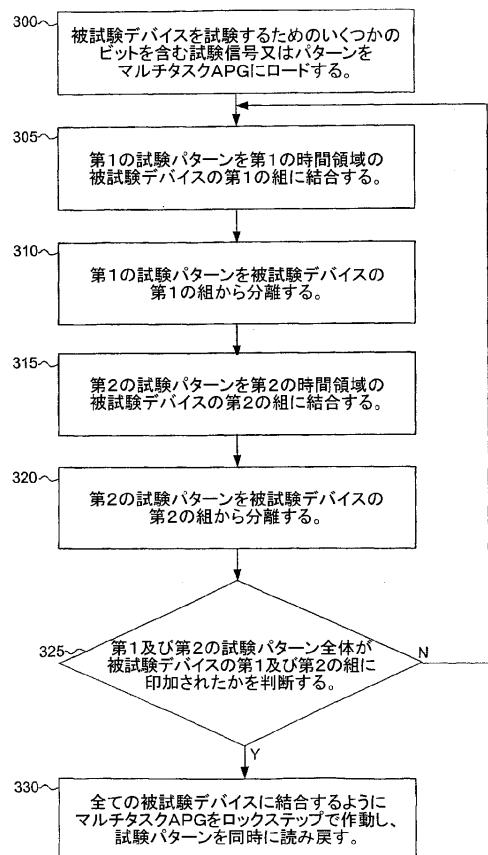

## 【0039】

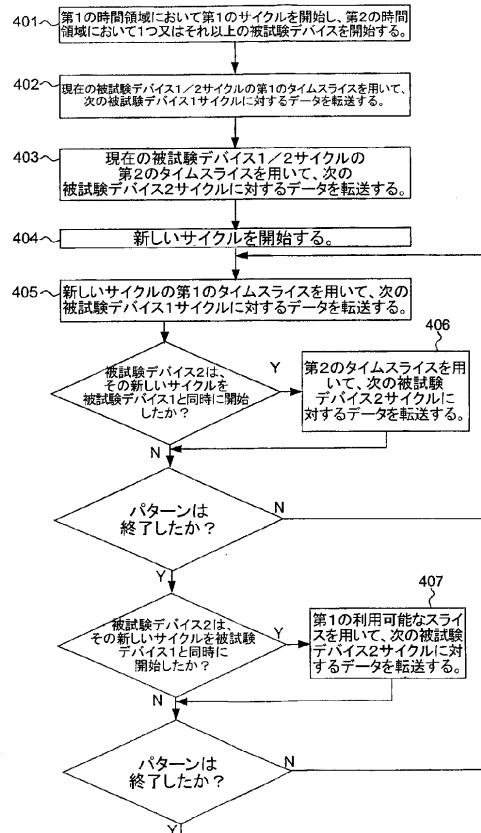

第1及び第2の被試験デバイス203を試験するための処理又は方法の実施形態を、ここで図4を参照して以下に説明する。図4は、いくつかの被試験デバイス203に対してマルチタスクモードで並行して書き込むか又はプログラムするマルチタスクAPG201を有するテスターを作動するための処理の実施形態を示す流れ図である。

図4を参照すると、処理は、いずれもその第1のサイクルを開始する第1の時間領域に

10

20

30

40

50

おける 1 つ又はそれ以上の被試験デバイス 2 0 3 ( 被試験デバイス 1 ) と、第 2 の時間領域における 1 つ又はそれ以上の被試験デバイス ( 被試験デバイス 2 ) とによって始まる ( 段階 4 0 1 ) 。現在の被試験デバイス 1 / 2 サイクルの第 1 のタイムスライスを用いて、次の被試験デバイス 1 サイクルに対するデータを転送する ( 段階 4 0 2 ) 。全てのタイムスライスは、20 ナノ秒の持続時間を有する。現在の被試験デバイス 1 / 2 サイクルの第 2 のタイムスライスを用いて、次の被試験デバイス 2 サイクルに対するデータを転送する ( 段階 4 0 3 ) 。次の被試験デバイス 1 又は ( 被試験デバイス 1 及び被試験デバイス 2 ) は、新しいサイクルを開始する ( 段階 4 0 4 ) 。新しいサイクルの第 1 のタイムスライスを用いて、次の被試験デバイス 1 サイクルに対するデータを転送する ( 段階 4 0 5 ) 。被試験デバイス 2 が被試験デバイス 1 と同時にその新しいサイクルを開始した場合、第 2 のタイムスライスを用いて、次の被試験デバイス 2 サイクルに対するデータを転送する ( 段階 4 0 6 ) 。パターンが終了していない場合は、段階 4 0 4 ~ 4 0 6 を繰り返す。それ以外は、被試験デバイス 1 及び被試験デバイス 2 サイクルの長さが符合せず、スライスの割り振りは、この時点では被試験デバイス数ではなく優先順位に基づくことになり、すなわち、コントローラである被試験デバイスタスクレジスタ 2 8 0 は、実際に本実施形態のカウンタのように見えない。被試験デバイス 2 が被試験デバイス 1 の前に新しいサイクルを開始した場合、第 1 の利用可能なスライス ( この例では、前のスライスの開始後少なくとも 20 ナノ秒として定義された ) を用いて、次の被試験デバイス 2 サイクルに対するデータを転送する ( 段階 4 0 6 ) 。パターンが完了しない場合は、段階 4 0 7 を繰り返し、それ以外は段階 4 0 4 へ進む。

10

20

30

#### 【 0 0 4 0 】

被試験デバイスタスクレジスタ 2 8 0 がストレージ要素 2 7 2 、 2 7 3 、及び 2 7 4 のいずれかを選択して特定時間領域内の被試験デバイス 2 0 3 に結合させ、その時間領域内の被試験デバイスの個々を個々に使用可能にすることができるために、異なる時間領域の被試験デバイスに書き込まれた試験パターンは同じである必要はなく、各時間領域の期間も同じである必要はないことが理解されるであろう。例えば、一実施形態では、マルチタスク A P G 2 0 1 は、特定時間領域の全ての被試験デバイス 2 0 3 が何時プログラムされたかを認識して、試験パターンが残りの時間領域の被試験デバイスに結合される周期又は周波数を調節し、それによってテスター 2 0 0 の効率を最大にすることができる。更に、被試験デバイス 2 0 3 又は時間領域は、規則的又は連続的に交互する順番で検査を受ける必要はなく、優先順位に基づいて必要な任意の順番で被試験デバイス又は時間領域に検査を提供するためにストレージ要素 2 7 2 、 2 7 3 、及び 2 7 4 のいずれかを選択することができる。例えば、サイクル時間が 80 ナノ秒、 100 ナノ秒、 80 ナノ秒、及び 200 ナノ秒である次に来るサイクルを有するか又はそれを要求する 4 つの時間領域において複数の被試験デバイスが試験される場合、被試験デバイスタスクレジスタ 2 8 0 は、ストレージ要素 2 7 2 、 2 7 3 、及び 2 7 4 を選択し、被試験デバイスに対して第 1 の時間領域、次に第 3 の時間領域、第 2 の時間領域、最後に第 4 の時間領域で検査を提供することができる。更に、試験の順番は、その次に来るサイクルで変えることができる。

任意的に、同じ試験パターンが異なる時間領域の全ての被試験デバイスに書き込まれるか又はプログラムされた時、本方法は、マルチタスク A P G 2 0 1 をロックステップで作動して全ての被試験デバイスに結合させ、試験パターンをマルチタスク A P G の最大周波数又は速度で読み戻す付加的な段階を更に含む ( 段階 3 3 0 ) 。

40

#### 【 0 0 4 1 】

本発明の以上の特定実施形態の記述は、例証及び説明のためのものである。それらは網羅的ではなく、また、本発明を開示した正確な形態に限定しないものであり、明らかに、以上の教示に照らして多くの修正及び変形が可能である。実施形態は、本発明の原理及びその実際的応用を最もよく説明し、それによって当業者が本発明と想定される特定の用途に適するような修正を有する様々な実施形態とを最もよく使用することができるよう選ばれて説明されたものである。本発明の範囲は、本明細書に添付した特許請求の範囲及びその均等物によって規定されるものとする。

50

## 【図面の簡単な説明】

## 【0042】

【図1】本発明の実施形態によるマルチタスクアルゴリズミック・パターン・ジェネレータを有する、集積回路を試験するためのテスターのレジスタレベルのブロック図である。

【図2】本発明の実施形態によるマルチタスクアルゴリズミック・パターン・ジェネレータを有する、集積回路を試験するためのテスターにおいて使用するためのマルチタスク・アルゴリズミック・パターン・ジェネレータレジスタのブロック図である。

【図3】本発明の実施形態によるマルチタスクアルゴリズミック・パターン・ジェネレータを有するテスターを作動させる方法の流れ図である。

【図4】本発明の実施形態によるマルチタスクアルゴリズミック・パターン・ジェネレータを有するテスターを作動させる別の方法の流れ図である。 10

## 【符号の説明】

## 【0043】

200 試験システム又はテスター

201 マルチタスク・アルゴリズミック・パターン・ジェネレータ (A P G )

203 被試験デバイス

204 M i c r o R A M

212 分岐論理回路

222 アドレス・トポロジカル・スクランブル

232 データバッファメモリ

280 被試験デバイスタスクレジスタ

20

【図1】

【図2】

FIG. 2

【図3】

Fig. 3

【図4】

Fig. 4

## 【国際調査報告】

| INTERNATIONAL SEARCH REPORT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                    | International application No.<br>PCT/US03/14328                                            |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------|-----------------------|---|---------------------------------------------------------------------|------|---|-----------------------------------------------------------------------|------|---|---------------------------------------------------------------------------------|---------|---|------------------------------------------------------------------------------------|---------|

| <b>A. CLASSIFICATION OF SUBJECT MATTER</b><br>IPC(7) : G01R 31/28, G06F 11/34, G06F 11/00, G06F 17/50, G06F 9/44<br>US CL : 714/738,395/183.08,714/32,716/6,703/20<br>According to International Patent Classification (IPC) or to both national classification and IPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                                                            |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| <b>B. FIELDS SEARCHED</b><br>Minimum documentation searched (classification system followed by classification symbols)<br>U.S. : 714/738,395/183.08,714/32,716/6,703/20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                    |                                                                                            |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                    |                                                                                            |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)<br>EAST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    |                                                                                            |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| <b>C. DOCUMENTS CONSIDERED TO BE RELEVANT</b> <table border="1" style="width: 100%; border-collapse: collapse;"> <thead> <tr> <th style="text-align: left; padding: 2px;">Category *</th> <th style="text-align: left; padding: 2px;">Citation of document, with indication, where appropriate, of the relevant passages</th> <th style="text-align: left; padding: 2px;">Relevant to claim No.</th> </tr> </thead> <tbody> <tr> <td style="padding: 2px;">X</td> <td style="padding: 2px;">US 5,572,666 A (Whitman) 05 November 1996 (05.11.1996), Figures 1-8</td> <td style="padding: 2px;">1-20</td> </tr> <tr> <td style="padding: 2px;">X</td> <td style="padding: 2px;">US 6,243,665 B1 (Nagoya et al) 05 June 2001 (05.06.2001), Figure 1-22</td> <td style="padding: 2px;">1-20</td> </tr> <tr> <td style="padding: 2px;">T</td> <td style="padding: 2px;">US 6,571,365 B1 (Rhodes et al) 27 May 2003 (27.05.2003), column 4, lines 11-54.</td> <td style="padding: 2px;">1 and 5</td> </tr> <tr> <td style="padding: 2px;">X</td> <td style="padding: 2px;">US 6,363,510 B1 (Rhodes et al.) 26 March 2002 (26.04.2002), column 2, lines 34-56.</td> <td style="padding: 2px;">1 and 5</td> </tr> </tbody> </table> |                                                                                    |                                                                                            | Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. | X | US 5,572,666 A (Whitman) 05 November 1996 (05.11.1996), Figures 1-8 | 1-20 | X | US 6,243,665 B1 (Nagoya et al) 05 June 2001 (05.06.2001), Figure 1-22 | 1-20 | T | US 6,571,365 B1 (Rhodes et al) 27 May 2003 (27.05.2003), column 4, lines 11-54. | 1 and 5 | X | US 6,363,510 B1 (Rhodes et al.) 26 March 2002 (26.04.2002), column 2, lines 34-56. | 1 and 5 |

| Category *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No.                                                                      |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 5,572,666 A (Whitman) 05 November 1996 (05.11.1996), Figures 1-8                | 1-20                                                                                       |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 6,243,665 B1 (Nagoya et al) 05 June 2001 (05.06.2001), Figure 1-22              | 1-20                                                                                       |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 6,571,365 B1 (Rhodes et al) 27 May 2003 (27.05.2003), column 4, lines 11-54.    | 1 and 5                                                                                    |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | US 6,363,510 B1 (Rhodes et al.) 26 March 2002 (26.04.2002), column 2, lines 34-56. | 1 and 5                                                                                    |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| <input type="checkbox"/> Further documents are listed in the continuation of Box C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                    | <input type="checkbox"/> See patent family annex.                                          |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| * Special categories of cited documents:<br>"A" document defining the general state of the art which is not considered to be of particular relevance<br>"E" earlier application or patent published on or after the international filing date<br>"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)<br>"O" document referring to an oral disclosure, use, exhibition or other means<br>"P" document published prior to the international filing date but later than the priority date claimed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                    |                                                                                            |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| Date of the actual completion of the international search<br>01 July 2003 (01.07.2003)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                    | Date of mailing of the international search report<br>24 JUL 2003                          |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

| Name and mailing address of the ISA/US<br>Mail Stop PCT, Attn: JSA/US<br>Commissioner for Patents<br>P.O. Box 1450<br>Alexandria, Virginia 22313-1450<br>Facsimile No. (703)305-3230                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                    | Authorized officer<br>Albert Decady <i>James R. Matteson</i><br>Telephone No. 703-305-3900 |            |                                                                                    |                       |   |                                                                     |      |   |                                                                       |      |   |                                                                                 |         |   |                                                                                    |         |

---

フロントページの続き

(72)発明者 ホームズ ジョン エム

アメリカ合衆国 カリフォルニア州 95008 キャンベル ペギー アベニュー 1381

F ターム(参考) 2G132 AA08 AE11 AE18 AF18 AG02 AG08 AL09 AL26

5L106 DD04 DD06 DD24