(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6137797号

(P6137797)

(45) 発行日 平成29年5月31日(2017.5.31)

(24) 登録日 平成29年5月12日(2017.5.12)

|               |           |

|---------------|-----------|

| (51) Int.Cl.  | F 1       |

| HO 1 L 29/786 | (2006.01) |

| HO 1 L 21/336 | (2006.01) |

| HO 1 L 29/49  | (2006.01) |

| HO 1 L 29/423 | (2006.01) |

| HO 1 L 29/417 | (2006.01) |

|               |           |

| HO 1 L        | 29/78     |

| HO 1 L        | 29/58     |

請求項の数 5 (全 39 頁) 最終頁に続く

|              |                              |

|--------------|------------------------------|

| (21) 出願番号    | 特願2012-205883 (P2012-205883) |

| (22) 出願日     | 平成24年9月19日(2012.9.19)        |

| (65) 公開番号    | 特開2013-80918 (P2013-80918A)  |

| (43) 公開日     | 平成25年5月2日(2013.5.2)          |

| 審査請求日        | 平成27年8月31日(2015.8.31)        |

| (31) 優先権主張番号 | 特願2011-208232 (P2011-208232) |

| (32) 優先日     | 平成23年9月23日(2011.9.23)        |

| (33) 優先権主張国  | 日本国 (JP)                     |

|           |                                                |

|-----------|------------------------------------------------|

| (73) 特許権者 | 000153878<br>株式会社半導体エネルギー研究所<br>神奈川県厚木市長谷398番地 |

| (72) 発明者  | 山崎 舜平<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 磯部 敦生<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内   |

| (72) 発明者  | 岡崎 豊<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内    |

| (72) 発明者  | 波多野 剛久<br>神奈川県厚木市長谷398番地 株式会社<br>半導体エネルギー研究所内  |

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁表面を有する基板上に設けられた酸化物半導体層と、

前記酸化物半導体層上に部分的に設けられた第1の導電層と、

前記第1の導電層上に部分的に設けられた第2の導電層と、

前記酸化物半導体層上、前記第1の導電層上及び前記第2の導電層上に設けられた絶縁層と、

前記絶縁層を介して前記酸化物半導体層上に設けられたゲート電極層と、

を有し、

前記第1の導電層は、前記酸化物半導体層と重なる領域を有し、前記第1の導電層は、

前記酸化物半導体層と前記第1の導電層とが重なる領域において前記ゲート電極層と重なる領域を有し、

前記第2の導電層は、前記酸化物半導体層と重なる領域を有し、前記第2の導電層は、

前記酸化物半導体層と前記第2の導電層とが重なる領域において前記ゲート電極層と重なる領域を有し。

## 【請求項 2】

絶縁表面を有する基板上に設けられた酸化物半導体層と、

前記酸化物半導体層上に部分的に設けられた第1の導電層と、

前記第1の導電層上に部分的に設けられた第2の導電層と、

前記第2の導電層上に設けられた第1の絶縁層と、

10

20

前記酸化物半導体層上、前記第1の導電層上、前記第2の導電層上及び前記第1の絶縁層上に設けられた第2の絶縁層と、

前記第2の絶縁層を介して前記酸化物半導体層上に設けられたゲート電極層と、

を有し、

前記第1の導電層は、前記酸化物半導体層と重なる領域を有し、前記第1の導電層は、

前記酸化物半導体層と前記第1の導電層とが重なる領域において前記ゲート電極層と重なる領域を有し、

前記第2の導電層は、前記酸化物半導体層と重なる領域を有し、前記第2の導電層は、

前記酸化物半導体層と前記第2の導電層とが重なる領域において前記ゲート電極層と重なる領域を有し、

前記第2の導電層は、前記酸化物半導体層と重なる領域を有し、前記第2の導電層は、

前記酸化物半導体層と前記第2の導電層とが重なる領域において前記ゲート電極層と重なる領域を有し、

10

【請求項3】

請求項1又は2において、

前記絶縁表面を有する基板上に、バッファ層が設けられている半導体装置。

【請求項4】

請求項3において、

前記バッファ層は、アルミニウム、ガリウム、ジルコニウム、ハフニウム、又は希土類元素から選択された一以上の元素の酸化物を含む層である半導体装置。

【請求項5】

請求項1乃至請求項4のいずれか一において、

前記酸化物半導体層は、c軸配向した結晶を含む半導体装置。

20

【発明の詳細な説明】

【技術分野】

【0001】

半導体装置及び半導体装置の作製方法に関する。

【0002】

なお、本明細書中において半導体装置とは、半導体特性を利用することで機能しうる装置全般を指し、電気光学装置、半導体回路および電子機器は全て半導体装置である。

【背景技術】

【0003】

絶縁表面を有する基板上に形成された半導体薄膜を用いてトランジスタ（薄膜トランジスタ（TFT）ともいう）を構成する技術が注目されている。該トランジスタは集積回路（IC）や画像表示装置（表示装置）のような電子デバイスに広く応用されている。トランジスタに適用可能な半導体薄膜としてシリコン系半導体材料が広く知られているが、その他の材料として酸化物半導体が注目されている。

30

【0004】

例えば、トランジスタの活性層として、インジウム（In）、ガリウム（Ga）、及び亜鉛（Zn）を含む非晶質酸化物を用いたトップゲート型でコプレナー型（Coplanar Type）のトランジスタが開示されている（特許文献1参照）。

【先行技術文献】

【特許文献】

40

【0005】

【特許文献1】特開2006-165528号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

トランジスタのオン特性（例えば、オン電流や電界効果移動度）を向上させて、半導体装置の高速応答、高速駆動を実現するためには、活性層のチャネル形成領域となる領域に対して、ゲート電極を確実に重畠させる構造が好適である。該構造により、ゲート電圧をソース、ドレイン間に有するチャネル形成領域に確実に印加することができ、ソース、ドレイン間の抵抗を低減することができる。

50

## 【0007】

コプレナー型のトランジスタで、トランジスタのゲート電極の両側に離間してソース電極及びドレイン電極を設ける場合、上面または断面を見た際、ゲート電極と、ソース電極及びドレイン電極との間で間隙が形成されることとなる。該間隙は、トランジスタを動作させる際に抵抗になる。

## 【0008】

そのためシリコン系半導体材料では、前述の間隙となる半導体領域に不純物を注入し、該間隙の領域の低抵抗化を図ることで、活性層のチャネル形成領域となる領域に対して、ゲート電極を確実に重畳させ、オン特性の向上を図る構成がとられている。一方、酸化物半導体を半導体材料に用いる場合は、該領域の低抵抗化を図るために、活性層のチャネル形成領域となる領域に対して、ソース電極及びドレイン電極の端部と、ゲート電極の端部とを一致または重畳して設ける構造が好適である。10

## 【0009】

しかしながら、上面または断面を見た際、トランジスタのソース電極及びドレイン電極の端部と、ゲート電極の端部とを一致又は重畳する構成では、該電極間の短絡が問題となる。この電極間の短絡は、ゲート絶縁層の、ソース電極及びドレイン電極、及び酸化物半導体層に対するカバレッジ不良に起因する。特にトランジスタの微細化に伴うゲート絶縁層の薄膜化時においては、カバレッジ不良が顕在化しやすい。

## 【0010】

ソース電極及びドレイン電極上、及び酸化物半導体層上に形成されるゲート絶縁層は、特にチャネル形成領域となる酸化物半導体層と接する領域において、カバレッジ不良などにより短絡を生じやすくなってしまう。ソース電極及びドレイン電極は、オン特性の向上を図るために、ゲート絶縁層と比べて厚膜化して設けることが多い。そのため、ゲート絶縁層を薄膜化して形成する場合には、ソース電極及びドレイン電極の厚膜化に伴い、ソース電極及びドレイン電極の端部におけるカバレッジ不良をさらに増加させてしまう。その結果、電極間の短絡を生じやすくなり、信頼性の低下に繋がることとなる。20

## 【0011】

そこで本発明の一態様では、トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供することを課題の一つとする。

## 【課題を解決するための手段】

## 【0012】

本発明の一態様では、酸化物半導体層、第1の導電層及び第2の導電層の積層によって構成されるソース電極層又はドレイン電極層、ゲート絶縁層、及びゲート電極層が順に積層されたトランジスタにおいて、ゲート電極層は、第1の導電層とゲート絶縁層を介して重畳し、第2の導電層とゲート絶縁層を介して非重畳とする半導体装置とする。30

## 【0013】

本発明の一態様は、絶縁表面を有する基板上に設けられた酸化物半導体層と、酸化物半導体層上に部分的に設けられた第1の導電層と、第1の導電層上に部分的に設けられた第2の導電層と、酸化物半導体層上、第1の導電層上及び第2の導電層上に設けられたゲート絶縁層と、ゲート絶縁層を介して酸化物半導体層上に設けられたゲート電極層と、を有し、ゲート電極層は、第1の導電層とゲート絶縁層を介して重畳し、第2の導電層とゲート絶縁層を介して非重畳とする半導体装置である。40

## 【0014】

本発明の一態様は、絶縁表面を有する基板上に設けられた酸化物半導体層と、酸化物半導体層上に部分的に設けられた第1の導電層と、第1の導電層上に部分的に設けられた第2の導電層と、第2の導電層上に設けられた絶縁層と、酸化物半導体層上、第1の導電層上、第2の導電層上及び絶縁層上に設けられたゲート絶縁層と、ゲート絶縁層を介して酸化物半導体層上に設けられたゲート電極層と、を有し、ゲート電極層は、第1の導電層とゲート絶縁層を介して重畳し、第2の導電層とゲート絶縁層を介して非重畳とする半導体装置である。50

## 【0015】

本発明の一態様は、絶縁表面を有する基板上に設けられた酸化物半導体層と、酸化物半導体層上に部分的に設けられた第1の導電層と、第1の導電層上に部分的に設けられた絶縁層と、絶縁層上に部分的に設けられ、絶縁層の開口部において第1の導電層に接して設けられた第2の導電層と、酸化物半導体層上、第1の導電層上、第2の導電層上及び絶縁層上に設けられたゲート絶縁層と、ゲート絶縁層を介して酸化物半導体層上に設けられたゲート電極層と、を有し、ゲート電極層は、第1の導電層とゲート絶縁層を介して重畠し、第2の導電層とゲート絶縁層を介して非重畠とする半導体装置である。

## 【0016】

本発明の一態様は、絶縁表面を有する基板上の、埋め込み導電層を部分的に有する絶縁層上に設けられた酸化物半導体層と、酸化物半導体層上に部分的に設けられた第1の導電層と、第1の導電層上に部分的に設けられた第2の導電層と、酸化物半導体層上、第1の導電層上及び第2の導電層上に設けられたゲート絶縁層と、ゲート絶縁層を介して酸化物半導体層上に設けられたゲート電極層と、を有し、ゲート電極層は、第1の導電層とゲート絶縁層を介して重畠し、第2の導電層とゲート絶縁層を介して非重畠とする半導体装置である。

10

## 【0017】

本発明の一態様において、埋め込み導電層を部分的に有する絶縁層は、酸化物半導体層の開口部において、埋め込み導電層が第1の導電層に接して設けられている半導体装置が好ましい。

20

## 【0018】

本発明の一態様において、埋め込み導電層を部分的に有する絶縁層は、埋め込み導電層上に、埋め込み酸化物半導体層を有する半導体装置が好ましい。

## 【0019】

本発明の一態様において、埋め込み導電層及び埋め込み酸化物半導体層を部分的に有する絶縁層は、酸化物半導体層の開口部において、埋め込み酸化物半導体層が第1の導電層に接して設けられている半導体装置が好ましい。

## 【0020】

本発明の一態様において、第1の導電層の膜厚は、5 nm以上20 nm以下である半導体装置が好ましい。

30

## 【0021】

本発明の一態様において、ゲート絶縁層の膜厚は、10 nm以上20 nm以下である半導体装置が好ましい。

## 【0022】

本発明の一態様において、酸化物半導体層の膜厚は、5 nm以上20 nm以下である半導体装置が好ましい。

## 【0023】

本発明の一態様において、絶縁表面を有する基板上には、バッファ層が設けられている半導体装置が好ましい。

## 【0024】

本発明の一態様において、バッファ層は、アルミニウム、ガリウム、ジルコニウム、ハフニウム、又は希土類元素から選択された一以上の元素の酸化物を含む層である半導体装置が好ましい。

40

## 【0025】

本発明の一態様において、酸化物半導体層は、c軸配向した結晶を含む半導体装置が好ましい。

## 【発明の効果】

## 【0026】

より高性能な半導体装置を実現するため、トランジスタのオン特性（例えば、オン電流や電界効果移動度）を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼

50

性の高い構成を提供することができる。

【図面の簡単な説明】

【0027】

【図1】半導体装置の一形態を説明する図。

【図2】半導体装置の作製方法の一形態を説明する図。

【図3】半導体装置の一形態を説明する図。

【図4】半導体装置の一形態を説明する図。

【図5】半導体装置の一形態を説明する図。

【図6】半導体装置の一形態を説明する図。

【図7】半導体装置の一形態を説明する図。

10

【図8】半導体装置の一形態を示す断面図、平面図及び回路図。

【図9】半導体装置の一形態を示す回路図及び斜視図。

【図10】半導体装置の一形態を示す断面図及び平面図。

【図11】半導体装置の一形態を示す回路図。

【図12】半導体装置の一形態を示すブロック図。

【図13】半導体装置の一形態を示すブロック図。

【図14】半導体装置の一形態を示すブロック図。

【図15】半導体装置を用いた電子機器の一形態を示す図。

【発明を実施するための形態】

【0028】

20

以下、本発明の実施の形態について図面を参照しながら説明する。但し、本発明の構成は多くの異なる態様で実施することが可能であり、本発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を々々に変更し得ることは当業者であれば容易に理解される。したがって本実施の形態の記載内容に限定して解釈されるものではない。

【0029】

なお、各実施の形態の図面等において示す各構成の、大きさ、層の厚さ、または領域は、明瞭化のために誇張されて表記している場合がある。よって、必ずしもそのスケールに限定されない。

【0030】

30

なお本明細書にて用いる第1、第2、第3、乃至第N（Nは自然数）という用語は、構成要素の混同を避けるために付したものであり、数的に限定するものではないことを付記する。

【0031】

（実施の形態1）

本実施の形態では、開示する発明の一態様にかかる半導体装置及び半導体装置の作製方法について、図1乃至図4を用いて説明する。

【0032】

40

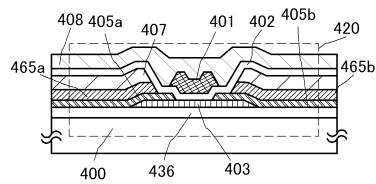

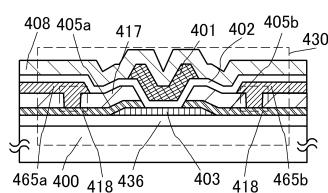

図1は、半導体装置の構成の一例であるトランジスタ420の断面図である。なおトランジスタ420はチャネル形成領域が1つ形成されるシングルゲート構造を示すが、チャネル形成領域が2つ形成されるダブルゲート構造もしくは3つ形成されるトリブルゲート構造であってもよい。

【0033】

トランジスタ420は、絶縁表面を有する基板400上に、バッファ層436と、酸化物半導体層403と、第1の導電層405a、405bと、第2の導電層465a、465bと、絶縁層407と、ゲート絶縁層402と、ゲート電極層401と、層間絶縁層408と、を有する（図1参照）。

【0034】

本実施の形態で開示する図1の構造は、トランジスタ420のソース電極及びドレイン電極として機能する第1の導電層405a、405bを、酸化物半導体層403と重畳する領域において、ゲート絶縁層402を介してゲート電極層401と重畳させる。また本実

50

施の形態で開示する図1の構造は、トランジスタ420のソース電極及びドレイン電極として機能する第2の導電層465a、465bを、酸化物半導体層403と重畠する領域において、ゲート絶縁層402を介してゲート電極層401と重畠させない。

【0035】

本実施の形態で開示する図1の構造は、トランジスタ420のソース電極及びドレイン電極となる第1の導電層405a、405bの端部と、ゲート電極となるゲート電極層401の端部とを重畠して設けることができる。そのため、トランジスタのオン特性（例えば、オン電流や電界効果移動度）を向上させて、半導体装置の高速応答、高速駆動を実現することができる。

【0036】

また本実施の形態で開示する図1の構造は、トランジスタのソース電極及びドレイン電極となる第1の導電層405a、405bを薄膜化することができる。第1の導電層405a、405bを薄膜化することで、特に酸化物半導体層403のチャネル形成領域周辺での、ゲート絶縁層402を形成する際の表面の段差を小さくすることができる。従って、ゲート絶縁層402は、カバレッジを良好にして形成することができる。カバレッジ不良を低減することで、電極間の短絡の発生を抑制し、信頼性の向上を図ることができる。加えて、本実施の形態で開示する図1の構造は、トランジスタのソース電極及びドレイン電極となる第2の導電層465a、465bの端部と、ゲート電極となるゲート電極層401の端部とを重畠させないで設けることができる。そのため、第1の導電層405a、405bに比べて第2の導電層465a、465bを厚膜化しても、電極間の短絡がない。したがって、第2の導電層465a、465bを厚膜化することで、電極間での短絡を引き起こすことなく、ソース電極及びドレイン電極を流れる電流を大きくすることができる。

【0037】

また本実施の形態で開示する図1の構造は、第1の導電層405a、405bを薄膜化することで、エッティング等の工程により第1の導電層405a、405bを加工する際の所要期間を短くすることができる。そのため第1の導電層405a、405bをエッティング等の工程で加工する際に生じる、酸化物半導体層403へのダメージを低減することができる。そのため、信頼性の向上を図ることができる。

【0038】

また本実施の形態で開示する図1の構造は、ゲート絶縁層402を薄膜化したコプレナー構造とすることことができ、平坦性を高めたバッファ層436上に、酸化物半導体層403を薄膜化して形成することができる。ゲート絶縁層402及び酸化物半導体層403を薄膜化することで、オン特性の向上が図れるとともに、トランジスタを完全空乏型で動作させることも可能である。トランジスタを完全空乏型で動作させることで、高集積化、高速駆動化、低消費電力化を図ることができる。

【0039】

また、本実施の形態で開示する図1の構造は、第2の導電層465a、465bと絶縁層407とを重畠して設け、側面をエッティング等の加工によりテーパー状とすることができる。そのため第2の導電層465a、465bを厚膜化しても、カバレッジを良好にすることができる。

【0040】

以上説明したように、本実施の形態で開示する図1の構成では、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畠して設けることができ、オン特性を向上させることができる。さらに本実施の形態で開示する図1の構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。この場合、酸化物半導体をチャネル形成領域に設けるトランジスタを微細化して形成することができ好適である。

【0041】

10

20

30

40

50

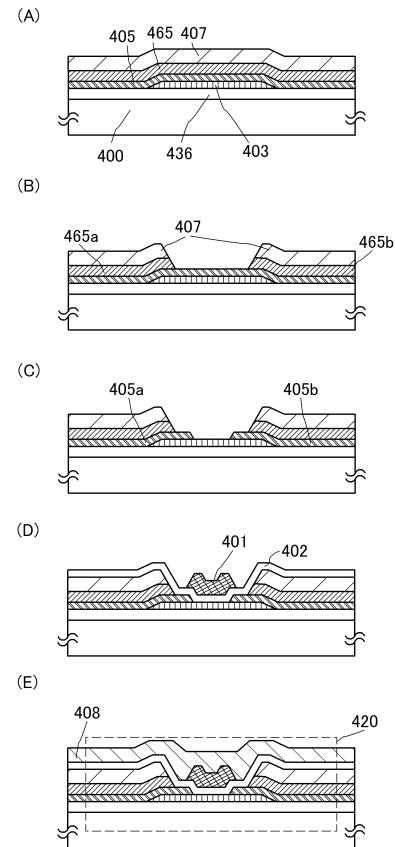

次いで、図2(A)乃至(E)に、図1で示したトランジスタ420の作製方法の一例を示す。

【0042】

まず、絶縁表面を有する基板400上にバッファ層436を形成する。バッファ層436は、バッファ層436上に形成される酸化物半導体層403と絶縁表面を有する基板400との反応を抑制するための層である。

【0043】

絶縁表面を有する基板400に使用することができる基板に大きな制限はないが、少なくとも、後の熱処理に耐えうる程度の耐熱性を有していることが必要となる。例えば、バリウムホウケイ酸ガラスやアルミニノホウケイ酸ガラスなどのガラス基板、セラミック基板、石英基板、サファイア基板などを用いることができる。また、シリコンや炭化シリコンなどの単結晶半導体基板、多結晶半導体基板、シリコンゲルマニウムなどの化合物半導体基板、SOI基板などを適用することもでき、これらの基板上に半導体素子が設けられたものを、基板400として用いてもよい。

10

【0044】

バッファ層436は、酸化物半導体層403と接する層であるため、酸化物半導体層403と同種の成分でなる酸化物を用いるのが好ましい。具体的には、アルミニウム(A1)、ガリウム(Ga)、ジルコニウム(Zr)、ハフニウム(Hf)等の酸化物半導体層403の構成元素、または、アルミニウム、ガリウム等と同族の元素である希土類元素、から選択された一以上の元素の酸化物を含む層とするのが好ましい。また、これらの元素のうち、III族元素であるアルミニウム、ガリウム、または希土類元素の酸化物を用いるのがより好ましい。また、希土類元素としてはスカンジウム(Sc)、イットリウム(Y)、セリウム(Ce)、サマリウム(Sm)またはガドリニウム(Gd)を用いるのが好ましい。このような材料は、酸化物半導体層403と相性がよく、これをバッファ層436に用いることで、酸化物半導体層403との界面の状態を良好にすることができます。また、酸化物半導体層403の結晶性を向上させることができる。

20

【0045】

なお、酸化物半導体層403をトランジスタ420の活性層として用いるため、バッファ層436のエネルギーギャップは酸化物半導体層403よりも大きいことが求められ、バッファ層436は絶縁性を有するのが好ましい。

30

【0046】

バッファ層436は、単層でも積層でもよい。

【0047】

バッファ層436の作製方法としては特に限定はなく、プラズマCVD法又はスパッタリング法等を用いて形成することができる。

【0048】

バッファ層436の表面は、平坦化処理を行ってもよい。平坦化処理としては、特に限定されないが、研磨処理(例えば、化学的機械研磨(Chemical Mechanical Polishing: CMP)法)、ドライエッティング処理、プラズマ処理を用いることができる。

40

【0049】

次に、バッファ層436上に酸化物半導体層403を形成する。

【0050】

酸化物半導体層403を形成する際、できる限り酸化物半導体層403に含まれる水素濃度を低減させることが好ましい。水素濃度を低減させるには、例えば、スパッタリング法を用いて成膜を行う場合には、スパッタリング装置の処理室内に供給する雰囲気ガスとして、水素、水、水酸基または水素化物などの不純物が除去された高純度の希ガス(代表的にはアルゴン)、酸素、および希ガスと酸素との混合ガスを適宜用いる。

【0051】

また、酸化物半導体層403、バッファ層436を大気に解放せずに連続的に形成するこ

50

とが好ましい。酸化物半導体層403、バッファ層436を大気に曝露せずに連続して形成すると、これらの界面に水素や水分などの不純物が吸着することを防止することができる。

【0052】

また、基板400を高温に保持した状態で酸化物半導体層403を形成することも、酸化物半導体層403中に含まれうる不純物濃度を低減するのに有効である。基板400を加熱する温度としては、150以上450以下とすればよく、好ましくは基板温度が200以上350以下とすればよい。また、酸化物半導体層403の形成時に基板400を高温で加熱することで、結晶性を有する酸化物半導体層を形成することができる。

【0053】

酸化物半導体層403に用いる酸化物半導体としては、少なくともインジウム(Indium)あるいは亜鉛(Zinc)を含むことが好ましい。特にIndiumとZincを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Gallium)を有することが好ましい。また、スタビライザーとしてスズ(Silver)を有することが好ましい。また、スタビライザーとしてハフニウム(Hafnium)を有することが好ましい。また、スタビライザーとしてアルミニウム(Aluminum)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zirconium)を有することが好ましい。

10

【0054】

また、他のスタビライザーとして、ランタノイドである、ランタン(Lanthanum)、セリウム(Cerium)、プラセオジム(Praseodymium)、ネオジム(Neodimium)、サマリウム(Samarium)、ユウロピウム(Europium)、ガドリニウム(Gadolinium)、テルビウム(Terbium)、ジスプロシウム(Dysprosium)、ホルミウム(Holmium)、エルビウム(Erbium)、ツリウム(Triplum)、イッテルビウム(Ytterbium)、ルテチウム(Lutetium)のいずれか一種あるいは複数種を有してもよい。

20

【0055】

例えば、酸化物半導体として、酸化インジウム、酸化スズ、酸化亜鉛、二元系金属の酸化物であるIndium-Zinc系酸化物、Silver-Zinc系酸化物、Aluminum-Zinc系酸化物、Zinc-Magnesium系酸化物、Silver-Magnesium系酸化物、Indium-Gallium系酸化物、三元系金属の酸化物であるIndium-Gallium-Zinc系酸化物(IGZOとも表記する)、Indium-Aluminum-Zinc系酸化物、Indium-Silver-Zinc系酸化物、Silver-Gallium-Zinc系酸化物、Aluminum-Gallium-Zinc系酸化物、Silver-Aluminum-Zinc系酸化物、Indium-Hafnium-Zinc系酸化物、Indium-Lanthanum-Zinc系酸化物、Indium-Cerium-Zinc系酸化物、Indium-Praseodymium-Zinc系酸化物、Indium-Neodimium-Zinc系酸化物、Indium-Samarium-Zinc系酸化物、Indium-Europium-Zinc系酸化物、Indium-Gadolinium-Zinc系酸化物、Indium-Terbium-Zinc系酸化物、Indium-Dysprosium-Zinc系酸化物、Indium-Holmium-Zinc系酸化物、Indium-Erbium-Zinc系酸化物、Indium-Triplum-Zinc系酸化物、Indium-Ytterbium-Zinc系酸化物、Indium-Lutetium-Zinc系酸化物、四元系金属の酸化物であるIndium-Silver-Gallium-Zinc系酸化物、Indium-Hafnium-Gallium-Zinc系酸化物、Indium-Aluminum-Gallium-Zinc系酸化物、Indium-Silver-Aluminum-Zinc系酸化物、Indium-Silver-Hafnium-Zinc系酸化物、Indium-Hafnium-Aluminum-Zinc系酸化物を用いることができる。

30

【0056】

なお、ここで、例えば、Indium-Gallium-Zinc系酸化物とは、IndiumとGalliumとZincを有する酸化物という意味であり、IndiumとGalliumとZincの比率は問わない。また、IndiumとGalliumとZinc以外の金属元素が入っていてもよい。

40

【0057】

なお、酸化物半導体層403は、形成時に酸素が多く含まれるような条件(例えば、酸素100%の雰囲気下でスパッタリング法で形成するなど)で形成し、酸素を多く含む(好ましくは酸化物半導体が結晶状態における化学量論的組成に対し、酸素の含有量が過剰な領域が含まれている)ことが好ましい。

【0058】

また酸化物半導体層403の形成時に用いるスパッタリングガスは水素、水、水酸基又は

50

水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0059】

なお、電子供与体（ドナー）となる水分または水素などの不純物が低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体（purified Oxide Semiconductor）は、i型（真性半導体）又はi型に限りなく近い。そのため、上記酸化物半導体を用いたトランジスタは、オフ電流が著しく低いという特性を有する。また、酸化物半導体のバンドギャップは、2eV以上、好ましくは2.5eV以上、より好ましくは3eV以上である。水分または水素などの不純物濃度が十分に低減され、なおかつ酸素欠損が低減されることにより高純度化された酸化物半導体層を用いることにより、トランジスタのオフ電流を下げることができる。

10

【0060】

なお、特に断りがない限り、本明細書でオフ電流とは、nチャネル型トランジスタにおいては、ドレイン端子をソース端子とゲートよりも高い電位とした状態において、ソース端子の電位を基準としたときのゲートの電位が0以下であるときに、ソース端子とドレイン端子の間に流れる電流のことを意味する。

【0061】

なお酸化物半導体は、単結晶、多結晶（ポリクリスタルともいう。）または非晶質などの状態を探ることができる。特に酸化物半導体層403として用いる酸化物半導体は、結晶領域及びアモルファス領域を含む混合層であり、結晶性を有する酸化物半導体とすることが好ましい。

20

【0062】

結晶性を有する酸化物半導体では、よりバルク内欠陥を低減することができ、表面の平坦性を高めればより高い移動度を得ることができる。表面の平坦性を高めるためには、平坦な表面上に酸化物半導体を形成することが好ましく、具体的には、平均面粗さ（Ra）が1nm以下、好ましくは0.3nm以下、より好ましくは0.1nm以下の表面上に形成するとよい。

【0063】

なお、Raは、JIS B 0601:2001（ISO 4287:1997）で定義されている算術平均粗さを曲面に対して適用できるよう三次元に拡張したものであり、「基準面から指定面までの偏差の絶対値を平均した値」と表現でき、以下の式にて定義される。

30

【0064】

【数1】

$$Ra = \frac{1}{S_0} \int_{y_1}^{y_2} \int_{x_1}^{x_2} |f(x, y) - Z_0| dx dy$$

【0065】

ここで、指定面とは、粗さ計測の対象となる面であり、座標（（x<sub>1</sub>, y<sub>1</sub>, f(x<sub>1</sub>, y<sub>1</sub>））（x<sub>1</sub>, y<sub>2</sub>, f(x<sub>1</sub>, y<sub>2</sub>））（x<sub>2</sub>, y<sub>1</sub>, f(x<sub>2</sub>, y<sub>1</sub>））（x<sub>2</sub>, y<sub>2</sub>, f(x<sub>2</sub>, y<sub>2</sub>））の4点で表される四角形の領域とし、指定面をxy平面に投影した長方形の面積をS<sub>0</sub>、基準面の高さ（指定面の平均の高さ）をZ<sub>0</sub>とする。Raは原子間力顕微鏡（AFM: Atomic Force Microscope）にて評価可能である。

40

【0066】

結晶性を有する酸化物半導体は、好ましくは、CAAC-OS（C Axis Aligned Crystalline Oxide Semiconductor）とする。

【0067】

CAAC-OSは、完全な単結晶ではなく、完全な非晶質でもない。CAAC-OSは、非晶質相に数nmから数十nmの結晶部及び非晶質を有する結晶-非晶質混相構造の酸化

50

物半導体である。なお、透過型電子顕微鏡 (TEM: Transmission Electron Microscope) による CAAc-OS に含まれる非晶質部と結晶部との境界は明確ではない。また、 CAAc-OS には粒界 (グレインバウンダリーともいう。) は確認できない。 CAAc-OS が粒界を有さないため、粒界に起因する電子移動度の低下が起こりにくい。

【0068】

CAAc-OS に含まれる結晶部は、c 軸が CAAc-OS の被形成面または表面に垂直な方向に揃い、かつ a b 面に垂直な方向から見て三角形状または六角形状の原子配列を有し、c 軸に垂直な方向から見て金属原子が層状または金属原子と酸素原子とが層状に配列している。なお、結晶部同士は、それぞれ a 軸および b 軸の向きが異なっていてもよい。

10

【0069】

なお、 CAAc-OS 中の、非晶質部および結晶部の占める割合が均一でなくてもよい。例えば、 CAAc-OS の表面側から結晶成長させる場合、 CAAc-OS の表面の近傍は結晶部の占める割合が高くなり、被形成面の近傍は非晶質部の占める割合が高くなることがある。

【0070】

CAAc-OS に含まれる結晶部の c 軸は、 CAAc-OS の被形成面または表面に垂直な方向に揃うため、 CAAc-OS 形状 (被形成面の断面形状または表面の断面形状) によって、結晶部同士の c 軸の方向が異なることがある。なお、結晶部の c 軸の方向は、 CAAc-OS が形成されたときの被形成面または表面に垂直な方向となる。結晶部は、成膜後または成膜後に加熱処理などの結晶化処理を行うことで形成される。

20

【0071】

CAAc-OS を用いることで、可視光や紫外光の照射によるトランジスタの電気特性の変動が低減されるため、信頼性の高いトランジスタを得ることができる。

【0072】

上述した酸化物半導体層 403 の一例としては、 In (インジウム)、 Ga (ガリウム)、及び Zn (亜鉛) を含むターゲットを用いたスパッタリング法で形成した In - Ga - Zn 系酸化物があげられる。酸化物半導体層 403 は、 1 nm 以上 30 nm 以下 (好ましくは 5 nm 以上 20 nm 以下) として形成することができる。

30

【0073】

なお CAAc-OS を成膜する場合は、例えば、多結晶である酸化物半導体スパッタリング用ターゲットを用い、スパッタリング法によって成膜する。当該スパッタリング用ターゲットにイオンが衝突すると、スパッタリング用ターゲットに含まれる結晶領域が a - b 面から劈開し、 a - b 面に平行な面を有する平板状またはペレット状のスパッタリング粒子として剥離することがある。この場合、当該平板状のスパッタリング粒子が、結晶状態を維持したまま基板に到達することで、 CAAc-OS を成膜することができる。

【0074】

In - Ga - Zn 系酸化物をスパッタリング法で形成する場合、好ましくは、原子数比が In : Ga : Zn = 1 : 1 : 1、 4 : 2 : 3、 3 : 1 : 2、 1 : 1 : 2、 2 : 1 : 3、 または 3 : 1 : 4 で示される In - Ga - Zn 系酸化物のターゲットを用いる。前述の原子数比を有する In - Ga - Zn 系酸化物のターゲットを用いて酸化物半導体層を形成することで、多結晶または CAAc-OS が形成されやすくなる。また、 In、 Ga、及び Zn を含むターゲットの充填率は 90 % 以上 100 % 以下、好ましくは 95 % 以上 100 % 未満である。充填率の高いターゲットを用いることにより、形成した酸化物半導体層は緻密な層となる。

40

【0075】

そして酸化物半導体層は、減圧状態に保持された処理室内に基板を保持し、処理室内の残留水分を除去しつつ水素及び水分が除去されたスパッタガスを導入し、上記ターゲットを用いて形成すればよい。形成時に、基板温度を 100 以上 600 以下、好ましくは 200 以上 400 以下としても良い。基板を加熱しながら形成することにより、形成し

50

た酸化物半導体層に含まれる不純物濃度を低減することができる。また、スパッタリングによる損傷が軽減される。処理室の残留水分を除去するためには、吸着型の真空ポンプを用いることが好ましい。例えば、クライオポンプ、イオンポンプ、チタンサブリメーションポンプを用いることが好ましい。また、排気手段としては、ターボポンプにコールドトラップを加えたものであってもよい。クライオポンプを用いて形成室を排気すると、例えば、水素原子、水( $H_2O$ )など水素原子を含む化合物(より好ましくは炭素原子を含む化合物も)等が排気されるため、当該処理室で形成した酸化物半導体層に含まれる不純物の濃度を低減できる。

#### 【0076】

なお、スパッタリング法等で形成された酸化物半導体層中には、不純物としての水分または水素(水酸基を含む)が多量に含まれていることがある。そのため酸化物半導体層中の水分または水素などの不純物を低減(脱水化または脱水素化)するために、酸化物半導体層に対して、減圧雰囲気下、窒素や希ガスなどの不活性ガス雰囲気下、酸素ガス雰囲気下、または超乾燥エア(CRDS(キャビティリングダウンレーザー分光法)方式の露点計)を用いて測定した場合の水分量が20 ppm(露点換算で-55)以下、好ましくは1 ppm以下、好ましくは10 ppb以下の空気)雰囲気下で、加熱処理を施す。

10

#### 【0077】

酸化物半導体層に加熱処理を施すことで、酸化物半導体層中の水分または水素を脱離させることができる。具体的には、250以上750以下、好ましくは400以上基板の歪み点未満の温度で加熱処理を行えば良い。例えば、500、3分間以上6分間以下程度で行えばよい。加熱処理にRTA法を用いれば、短時間に脱水化または脱水素化が行えるため、ガラス基板の歪点を超える温度でも処理することができる。

20

#### 【0078】

なお、酸化物半導体層中の水分または水素を脱離させるための熱処理は、酸化物半導体層403の形成後であって後に形成する層間絶縁層408の形成前であれば、トランジスタ420の作製工程においてどのタイミングで行ってもよい。また、脱水化又は脱水素化のための熱処理は、複数回行ってもよく、他の加熱処理と兼ねてもよい。

#### 【0079】

また、上記加熱処理により、酸化物半導体層から酸素が脱離し、酸化物半導体層内に酸素欠損が形成される場合がある。よって、後の工程で酸化物半導体層と接するゲート絶縁層として、酸素を含むゲート絶縁層を用いることが好ましい。そして、酸素を含むゲート絶縁層を形成した後、加熱処理を施すことで、上記ゲート絶縁層から酸化物半導体層に酸素が供与されるようにする。上記構成により、ドナーとなる酸素欠損を低減し、酸化物半導体層に含まれる酸化物半導体の、化学量論的組成を満たすことができる。その結果、酸化物半導体層をi型に近づけることができ、酸素欠損によるトランジスタの電気的特性のばらつきを軽減し、電気的特性の向上を実現することができる。

30

#### 【0080】

なお、酸素を酸化物半導体層に供与するための加熱処理は、窒素、超乾燥空気、または希ガス(アルゴン、ヘリウムなど)の雰囲気下において、好ましくは200以上400以下、例えば250以上350以下で行う。上記ガスは、水の含有量が20 ppm以下、好ましくは1 ppm以下、より好ましくは10 ppb以下であることが望ましい。

40

#### 【0081】

また、脱水化又は脱水素化処理を行った酸化物半導体層に、酸素(少なくとも、酸素ラジカル、酸素原子、酸素イオン、のいずれかを含む)を導入して層内に酸素を供給してもよい。

#### 【0082】

脱水化又は脱水素化処理を行った酸化物半導体層403に、酸素を導入して層内に酸素を導入することによって、酸化物半導体層403を高純度化、及びi型化することができる。高純度化し、i型化した酸化物半導体層403を有するトランジスタは、電気特性変動が抑制されており、電気的に安定である。

50

## 【0083】

酸素の導入方法としては、イオン注入法、イオンドーピング法、プラズマイマージョンイオンインプランテーション法、プラズマ処理などを用いることができる。

## 【0084】

酸化物半導体層403は、層状の酸化物半導体層をフォトリソグラフィ工程により島状の酸化物半導体層403に加工して形成することができる。

## 【0085】

なお、酸化物半導体層403のエッチングは、ドライエッチングでもウェットエッチングでもよく、両方を用いてもよい。例えば、酸化物半導体層403のウェットエッチングに用いるエッチング液としては、磷酸と酢酸と硝酸を混ぜた溶液などを用いることができる。また、ITO07N（関東化学社製）を用いてもよい。

10

## 【0086】

なお図2(A)では、島上の酸化物半導体層403は端部に20度乃至50度のテープーを有している。端部が垂直であると酸素が抜けやすく酸素欠陥を生じやすいが、端部にテープーを有することで酸素欠陥を抑制することができる。該酸素欠陥の抑制により、トランジスタ420のリーク電流（寄生チャネル）の発生を低減することができる。

## 【0087】

次いで、酸化物半導体層403上及びバッファ層436上に、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる第1の導電層405を形成する。

## 【0088】

該第1の導電層405は後の加熱処理に耐えられる材料を用いる。ソース電極層、及びドレイン電極層に用いる第1の導電層405としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、又は上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンクスチタン膜）等を用いることができる。

20

## 【0089】

なお、Al、Cuなどの金属膜を第1の導電層405として用いる場合には、該金属膜の下側又は上側の一方又は双方にTi、Mo、Wなどの高融点金属膜又はそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンクスチタン膜）を積層させた構成とすることが好ましい。

30

## 【0090】

また、ソース電極層、及びドレイン電極層に用いる第1の導電層405としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）、酸化亜鉛（ZnO）、酸化インジウム酸化スズ（In<sub>2</sub>O<sub>3</sub>SnO<sub>2</sub>、ITOと略記する）、酸化インジウム酸化亜鉛（In<sub>2</sub>O<sub>3</sub>ZnO）又はこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

## 【0091】

上述した第1の導電層405は、後に形成する第2の導電層465よりも薄膜化しておくことが好ましい。具体的には、後に形成するゲート絶縁層402がカバレッジ不良を起こさない程度に薄膜化しておくことが好ましく、1nm以上30nm以下（好ましくは10nm以上20nm以下）として形成すればよい。

40

## 【0092】

次いで、第1の導電層405上に、ソース電極層及びドレイン電極層（これと同じ層で形成される配線を含む）となる第2の導電層465を形成する。

## 【0093】

該第2の導電層465は後の加熱処理に耐えられる材料を用いる。ソース電極層、及びドレイン電極層に用いる第2の導電層465としては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、又は上述した元素を成分とする金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンクスチタン膜）等を用いることができる。

50

## 【0094】

また、Al、Cuなどの金属膜の下側又は上側の一方又は双方にTi、Mo、Wなどの高融点金属膜又はそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）を積層させた構成としても良い。

## 【0095】

また、ソース電極層、及びドレイン電極層に用いる第2の導電層465としては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム（In<sub>2</sub>O<sub>3</sub>）、酸化スズ（SnO<sub>2</sub>）、酸化亜鉛（ZnO）、酸化インジウム酸化スズ（In<sub>2</sub>O<sub>3</sub>SnO<sub>2</sub>、ITOと略記する）、酸化インジウム酸化亜鉛（In<sub>2</sub>O<sub>3</sub>ZnO）又はこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

10

## 【0096】

なお第2の導電層465にAl、Cuなどの金属膜を単層で用いる場合には、特に、第1の導電層405には、Ti、Mo、Wなどの高融点金属膜又はそれらの金属窒化物膜（窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜）を用いる構成が好ましい。該構成により、第2の導電層465にAl、Cuを用いることで配線抵抗を低減することができるとともに、酸化物半導体層とAl、Cuとが直接接触することでAl、Cuが酸化してしまい抵抗が増加するといった不具合を低減することができる。また第2の導電層465は、後の工程（図2（B）での工程）でエッティングを行う際、第1の導電層405より選択比が高い条件となる材料を選択しておくことが好ましい。

## 【0097】

20

上述した第2の導電層465は、第1の導電層405よりも厚膜化しておくことが好ましい。具体的には第2の導電層465は、ソース電極またはドレイン電極として機能する際、配線抵抗が大きくならない程度として形成すればよく、厚さは特に限定されない。

## 【0098】

次いで、第2の導電層465上に絶縁層407を形成する。なお、絶縁層407は必須の構成要素ではないが、後の工程で第1の導電層405及び第2の導電層465を加工する際のマスクとして、またはソース電極またはドレイン電極の上面を保護する保護層として有効である。

## 【0099】

30

絶縁層407は、CVD法やスパッタリング法等を用いて成膜することができる。また、絶縁層407は、酸化珪素、窒化珪素、酸化窒化珪素、窒化酸化珪素、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどを含むように成膜するのが好適である。なお、絶縁層407は、単層構造としても良いし、積層構造としても良い。なお、絶縁層407の厚さは特に限定されない。

## 【0100】

以上が図2（A）までの工程の説明である。

## 【0101】

40

次いで、フォトリソグラフィ工程により絶縁層407上にレジストマスクを形成し、第2の導電層465及び絶縁層407に対し、部分的にエッティング処理を行って第2の導電層465a、465bを形成した後、レジストマスクを除去する。該エッティング処理により、第2の導電層465及び絶縁層407が酸化物半導体層403上で分離される。分離された第2の導電層465a、465bは、トランジスタ420のソース電極層、ドレイン電極層となる。

## 【0102】

以上が図2（B）までの工程の説明である。

## 【0103】

50

次いで、フォトリソグラフィ工程により第1の導電層405上にレジストマスクを形成し、部分的にエッティング処理を行って第1の導電層405a、405bを形成した後、レジストマスクを除去する。該エッティング処理により、第1の導電層405が酸化物半導体層403上で分離される。分離された第1の導電層405a、405bは、トランジスタ4

20のソース電極層、ドレイン電極層となる。

【0104】

なお第1の導電層405を第2の導電層465よりも薄膜化して形成しておくことで、酸化物半導体層403上に形成された第1の導電層405の厚さを均一にしておくことが可能になる。また第1の導電層405を薄膜化して形成しておくことで、前述のエッティング工程により第1の導電層405を加工する際の所要期間を短くすることができる。そのため第1の導電層405を加工する際に生じる、酸化物半導体層403へのダメージを低減することができる。そのため、信頼性の向上を図ることができる。

【0105】

以上が図2(C)までの工程の説明である。

10

【0106】

次いで、酸化物半導体層403、第1の導電層405a、405b、第2の導電層465a、465b及び絶縁層407を覆うゲート絶縁層402を形成する。

【0107】

ゲート絶縁層402は、1nm以上20nm以下、より好ましくは10nm以上20nm以下の厚さとし、スパッタリング法、MBE法、CVD法、パルスレーザ堆積法、ALD法等を適宜用いて形成することができる。また、ゲート絶縁層402は、スパッタリングターゲット表面に対し、概略垂直に複数の基板表面がセットされた状態で成膜を行うスパッタ装置を用いて形成してもよい。

【0108】

20

ゲート絶縁層402の材料としては、酸化シリコン膜、酸化ガリウム膜、酸化アルミニウム膜、窒化シリコン膜、酸化窒化シリコン膜、酸化窒化アルミニウム膜、又は窒化酸化シリコン膜を用いて形成することができる。

【0109】

ゲート絶縁層402は、酸化物半導体層403と接する部分において酸素を含むことが好ましい。特に、ゲート絶縁層402は、層内(バルク中)に少なくとも化学量論的組成を超える量の酸素が存在することが好ましく、例えば、ゲート絶縁層402として、酸化シリコンを用いる場合には、 $\text{SiO}_{2+x}$ (ただし、 $x > 0$ )とする。

【0110】

本実施の形態では、ゲート絶縁層402として、 $\text{SiO}_{2+x}$ (ただし、 $x > 0$ )である酸化シリコンを用いる。この酸化シリコンをゲート絶縁層402として用いることで、酸化物半導体層403に酸素を供給することができ、特性を良好にすることができます。

30

【0111】

また、ゲート絶縁層402の材料として酸化ハフニウム、酸化イットリウム、ハフニウムシリケート( $\text{HfSi}_{x,y}$  ( $x > 0$ ,  $y > 0$ ))、窒素が添加されたハフニウムシリケート( $\text{HfSiO}_{x,y}$  ( $x > 0$ ,  $y > 0$ ))、ハフニウムアルミネート( $\text{HfAl}_{x,y}$  ( $x > 0$ ,  $y > 0$ ))、酸化ランタンなどのhigh-k材料を用いることでゲートリーアク電流を低減できる。さらに、ゲート絶縁層402は、単層構造としても良いし、積層構造としても良い。

【0112】

40

そして、ゲート電極層401をプラズマCVD法又はスパッタリング法等により、ゲート絶縁層402上に形成する。

【0113】

ゲート電極層401の材料は、モリブデン、チタン、タンタル、タングステン、アルミニウム、銅、クロム、ネオジム、スカンジウム等の金属材料又はこれらを主成分とする合金材料を用いて形成することができる。また、ゲート電極層401としてリン等の不純物元素をドーピングした多結晶シリコン膜に代表される半導体膜、ニッケルシリサイドなどのシリサイド膜を用いてもよい。ゲート電極層401は、単層構造としてもよいし、積層構造としてもよい。

【0114】

50

また、ゲート電極層401の材料は、インジウム錫酸化物、酸化タンゲステンを含むインジウム酸化物、酸化タンゲステンを含むインジウム亜鉛酸化物、酸化チタンを含むインジウム酸化物、酸化チタンを含むインジウム錫酸化物、インジウム亜鉛酸化物、酸化シリコンを添加したインジウム錫酸化物などの導電性材料を適用することもできる。また、上記導電性材料と、上記金属材料の積層構造とすることもできる。

【0115】

また、ゲート絶縁層402と接するゲート電極層401の一層として、窒素を含む金属酸化物、具体的には、窒素を含むIn-Ga-Zn-O膜や、窒素を含むIn-Sn-O膜や、窒素を含むIn-Ga-O膜や、窒素を含むIn-Zn-O膜や、窒素を含むSn-O膜や、窒素を含むIn-O膜や、金属窒化膜(InN, SnNなど)を用いることができる。これらの膜は5eV(電子ボルト)、好ましくは5.5eV(電子ボルト)以上の仕事関数を有し、ゲート電極層として用いた場合、トランジスタの電気特性のしきい値電圧をプラスにすることができ、所謂ノーマリーオフのスイッチング素子を実現できる。

10

【0116】

以上が図2(D)までの工程の説明である。

【0117】

次いで、ゲート絶縁層402、ゲート電極層401上に層間絶縁層408を形成する(図2(E)参照)。

【0118】

層間絶縁層408は、プラズマCVD法、スパッタリング法、又は蒸着法等により形成することができる。層間絶縁層408は、代表的には酸化シリコン、酸化窒化シリコン、酸化窒化アルミニウム、又は酸化ガリウムなどの無機絶縁層などを用いることができる。

20

【0119】

また、層間絶縁層408として、酸化アルミニウム、酸化ハフニウム、酸化マグネシウム、酸化ジルコニウム、酸化ランタン、酸化バリウム、又は金属窒化物(例えば、窒化アルミニウム膜)も用いることができる。

【0120】

層間絶縁層408は、単層でも積層でもよく、例えば酸化シリコン膜及び酸化アルミニウム膜の積層を用いることができる。

【0121】

層間絶縁層408は、スパッタリング法など、層間絶縁層408に水、水素等の不純物を混入させない方法を適宜用いて形成することが好ましい。また、層間絶縁層408は、酸素を過剰に含む膜とすると、酸化物半導体層403に接するゲート絶縁層402を介した酸化物半導体層403への酸素の供給源となるために好ましい。

30

【0122】

本実施の形態では、層間絶縁層408として膜厚100nmの酸化シリコン膜を、スパッタリング法を用いて成膜する。酸化シリコン膜のスパッタリング法による成膜は、希ガス(代表的にはアルゴン)雰囲気下、酸素雰囲気下、又は希ガスと酸素の混合雰囲気下において行うことができる。

【0123】

酸化物半導体層の成膜時と同様に、層間絶縁層408の成膜室内の残留水分を除去するためには、吸着型の真空ポンプ(クライオポンプなど)を用いることが好ましい。クライオポンプを用いて排気した成膜室で成膜した層間絶縁層408に含まれる不純物の濃度を低減できる。また、層間絶縁層408の成膜室内の残留水分を除去するための排気手段としては、ターボ分子ポンプにコールドトラップを加えたものであってもよい。

40

【0124】

層間絶縁層408を、成膜する際に用いるスパッタガスとしては、水素、水、水酸基又は水素化物などの不純物が除去された高純度ガスを用いることが好ましい。

【0125】

酸化物半導体層403上に設けられる層間絶縁層408として用いることのできる酸化ア

50

ルミニウム膜は、水素、水分などの不純物、及び酸素の両方に対して膜を通過させない遮断効果（ブロック効果）が高い。

【0126】

従って、酸化アルミニウム膜は、作製工程中及び作製後において、変動要因となる水素、水分などの不純物の酸化物半導体層403への混入、及び酸化物半導体を構成する主成分材料である酸素の酸化物半導体層403からの放出を防止する保護膜として機能する。

【0127】

また、トランジスタ起因の表面凹凸を低減するために平坦化絶縁膜を形成してもよい。平坦化絶縁膜としては、ポリイミド、アクリル、ベンゾシクロブテン系樹脂、等の有機材料を用いることができる。また上記有機材料の他に、低誘電率材料（low-k材料）等を用いることができる。なお、これらの材料で形成される絶縁膜を複数積層させることで、平坦化絶縁膜を形成してもよい。

10

【0128】

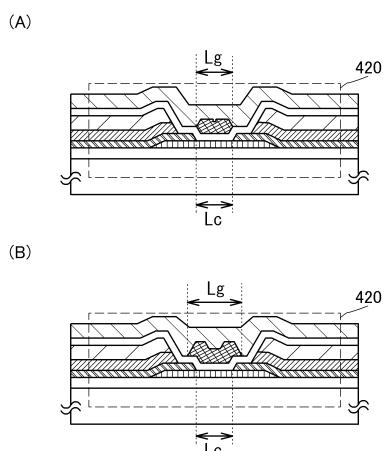

なお本実施の形態で開示するトランジスタの構造では、ソース電極及びドレイン電極となる第1の導電層405a及び第1の導電層405b間の距離Lcがトランジスタ420のチャネル長となる。本実施の形態で開示する構造において、ゲート電極層401のチャネル長方向の長さをLgとし、チャネル長をLcとすると、図3(A)に示すように同じ長さとなるか、若しくは図3(B)に示すようにLgがLcより長くなるように設けることができる。つまり、本実施の形態で開示するトランジスタの構造は、トランジスタのソース電極及びドレイン電極となる第1の導電層405a、405bの端部と、ゲート電極となるゲート電極層401の端部とを重畳して設けることができる構造である。そのため、トランジスタのオン特性（例えば、オン電流や電界効果移動度）を向上させて、半導体装置の高速応答、高速駆動を実現することができる。

20

【0129】

以上の工程で、本実施の形態のトランジスタ420が作製される（図2(E)参照）。インジウム、亜鉛、及び酸素を少なくとも含む酸化物半導体層403を用い、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畳して設け、且つカバーレッジを良好にしたトランジスタを実現できる。そして、トランジスタのオン特性を向上させて、半導体装置の高速応答、高速駆動を実現する際に、信頼性の高い構成を提供することができる。

30

【0130】

ここで、図1に示したトランジスタ420の変形例について、図4を用いて説明する。図4の説明において、図1と同一部分又は同様な機能を有する部分については、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

【0131】

図4に示すトランジスタの構造は、第1の導電層と第2の導電層とを直接積層する図1のトランジスタの構造と異なり、第1の導電層と第2の導電層との間に絶縁層を設ける構造である。

【0132】

図4は、図1のトランジスタ420の構成とは異なる一例であるトランジスタ430の断面図である。

40

【0133】

トランジスタ430は、絶縁表面を有する基板400上に、バッファ層436と、酸化物半導体層403と、第1の導電層405a、405bと、第2の導電層465a、465bと、絶縁層417と、ゲート絶縁層402と、ゲート電極層401と、層間絶縁層408と、を有する（図4参照）。

【0134】

図4の構造は、図1の構造と同様に、トランジスタ430のソース電極及びドレイン電極として機能する第1の導電層405a、405bを、酸化物半導体層403と重畳する領域において、ゲート絶縁層402を介してゲート電極層401と重畳させている。また図

50

4の構造は、図1の構造と同様に、トランジスタ430のソース電極及びドレイン電極として機能する第2の導電層465a、465bを、酸化物半導体層403と重畠する領域において、ゲート絶縁層402を介してゲート電極層401と重畠させない。

【0135】

そのため図4の構造は、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畠して設けることができ、オン特性を向上させることができる。さらに図4の構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。

【0136】

また特に、図4の構造は、第1の導電層405a、405bと第2の導電層465a、465bとの間に絶縁層417を設け、開口部418において直接接続している。当該構造とすることで、トランジスタ430を作製する際、第1の導電層と第2の導電層とのエッチングの選択比が小さくても所定の形状に加工することができる。そのため、第1の導電層と第2の導電層に同じ材料を用いる構成とすることも可能である。

【0137】

以上説明したように、本実施の形態で開示する構成では、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畠して設けることができ、オン特性を向上させることができる。さらに本実施の形態で開示する構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。この場合、酸化物半導体をチャネル形成領域に設けるトランジスタを微細化して形成することができ好適である。

【0138】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0139】

(実施の形態2)

本実施の形態では、半導体装置の他の一形態を、図5及び図6を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

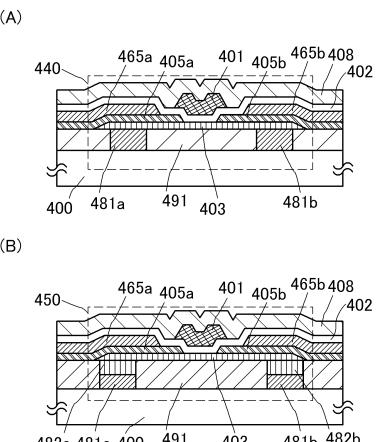

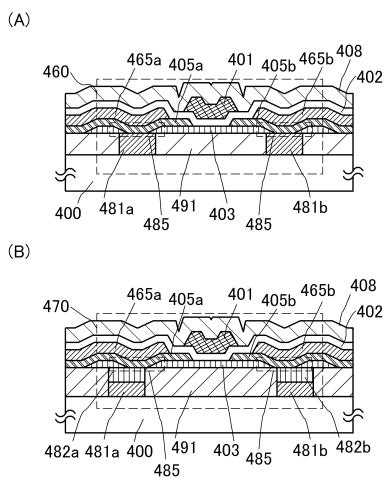

【0140】

図5(A)は、実施の形態1で示した半導体装置の構成とは異なる一例であるトランジスタ440の断面図である。

【0141】

トランジスタ440は、絶縁表面を有する基板400上に、埋め込み導電層481a、481bが設けられた絶縁層491と、酸化物半導体層403と、第1の導電層405a、405bと、第2の導電層465a、465bと、ゲート絶縁層402と、ゲート電極層401と、層間絶縁層408と、を有する(図5(A)参照)。

【0142】

図5(A)の構造は、図1の構造と同様に、トランジスタ440のソース電極及びドレイン電極として機能する第1の導電層405a、405bを、酸化物半導体層403と重畠する領域において、ゲート絶縁層402を介してゲート電極層401と重畠させている。また図5(A)の構造は、図1の構造と同様に、トランジスタ440のソース電極及びドレイン電極として機能する第2の導電層465a、465bを、酸化物半導体層403と重畠する領域において、ゲート絶縁層402を介してゲート電極層401と重畠させない。

【0143】

そのため図5(A)の構造は、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畠して設けることができ、オン特性を向上させることができる。さらに図5(A)の構

10

20

30

40

50

成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。

【0144】

また特に、本実施の形態で開示する図5(A)の構造は、トランジスタ440の下部に埋め込み導電層481a、481bが設けられた絶縁層491を設け、埋め込み導電層481a、481bが、酸化物半導体層403を介して、第1の導電層405a、405bと、第2の導電層465a、465bとに重畳して設けられている。トランジスタ440の下部に埋め込み導電層481a、481bを設ける構成とすることで、ゲート絶縁層402及び層間絶縁層408に開口部を設けることなく、トランジスタ間及び外部に設けられた制御回路と接続することができる。埋め込み導電層481a、481bは、トランジスタ440との接触面積を大きくとることができるために、コンタクト抵抗を低減することができる。

10

【0145】

なお埋め込み導電層481a、481bは、絶縁層491を形成した後に開口部を設け、該開口部を埋めるように埋め込み導電層を設けた後に、表面にCMP法による研磨を行つて形成すればよい。

【0146】

埋め込み導電層481a、481bとしては、例えば、Al、Cr、Cu、Ta、Ti、Mo、Wから選ばれた元素を含む金属膜、又は上述した元素を成分とする金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜)等を用いることができる。

20

【0147】

なお、Al、Cuなどの金属膜を埋め込み導電層481a、481bとして用いる場合には、該金属膜の下側又は上側の一方又は双方にTi、Mo、Wなどの高融点金属膜又はそれらの金属窒化物膜(窒化チタン膜、窒化モリブデン膜、窒化タンゲステン膜)を積層させた構成とすることが好ましい。

【0148】

また、埋め込み導電層481a、481bとしては、導電性の金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ( $In_2O_3$   $SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛( $In_2O_3$   $ZnO$ )又はこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

30

【0149】

絶縁層491は、CVD法やスパッタリング法等を用いて成膜することができる。また、絶縁層491は、酸化シリコン、窒化シリコン、酸化窒化シリコン、窒化酸化シリコン、酸化アルミニウム、酸化ハフニウム、酸化タンタルなどを含むように成膜するのが好適である。なお、絶縁層491は、単層構造としても良いし、積層構造としても良い。

【0150】

また図5(B)は、図5(A)と異なる構成である、トランジスタ450の断面図である。

【0151】

トランジスタ450は、絶縁表面を有する基板400上に、埋め込み導電層481a、481b及び埋め込み酸化物半導体層482a、482bが設けられた絶縁層491と、酸化物半導体層403と、第1の導電層405a、405bと、第2の導電層465a、465bと、ゲート絶縁層402と、ゲート電極層401と、層間絶縁層408と、を有する(図5(B)参照)。

40

【0152】

図5(B)の構造は、図1の構造と同様に、トランジスタ450のソース電極及びドレイン電極として機能する第1の導電層405a、405bを、酸化物半導体層403と重畳する領域において、ゲート絶縁層402を介してゲート電極層401と重畳させている。

また図5(B)の構造は、図1の構造と同様に、トランジスタ450のソース電極及びド

50

レイン電極として機能する第2の導電層465a、465bを、酸化物半導体層403と重畠する領域において、ゲート絶縁層402を介してゲート電極層401と重畠させない。

【0153】

そのため図5(B)の構造は、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畠して設けることができ、オン特性を向上させることができる。さらに図5(B)の構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。

【0154】

また特に、本実施の形態で開示する図5(B)の構造は、トランジスタ450の下部に埋め込み導電層481a、481b及び埋め込み酸化物半導体層482a、482bが設けられた絶縁層491を設け、埋め込み導電層481a、481b及び埋め込み酸化物半導体層482a、482bが、酸化物半導体層403を介して、第1の導電層405a、405bと、第2の導電層465a、465bとに重畠して設けられている。トランジスタ450の下部に埋め込み導電層481a、481bを設ける構成とすることで、ゲート絶縁層402及び層間絶縁層408に開口部を設けることなく、トランジスタ間及び外部に設けられた制御回路と接続することができる。また埋め込み導電層481a、481bとトランジスタ450との間に埋め込み酸化物半導体層482a、482bを設ける構成とすることで、埋め込み導電層481a、481bとトランジスタ450との接続を良好なものとすることができる。埋め込み導電層481a、481bは、トランジスタ450との接触面積を大きくとることができ、加えて埋め込み酸化物半導体層482a、482bはトランジスタ450との接続を良好なものとするため、コンタクト抵抗を低減することができる。

10

【0155】

埋め込み酸化物半導体層482a、482bとしては、少なくともインジウム(In)あるいは亜鉛(Zn)を含むことが好ましい。特にInとZnを含むことが好ましい。また、該酸化物半導体を用いたトランジスタの電気特性のばらつきを減らすためのスタビライザーとして、それらに加えてガリウム(Ga)を有することが好ましい。また、スタビライザーとしてスズ(Sn)を有することが好ましい。また、スタビライザーとしてハフニウム(Hf)を有することが好ましい。また、スタビライザーとしてアルミニウム(Al)を有することが好ましい。また、スタビライザーとしてジルコニウム(Zr)を有することが好ましい。

20

【0156】

また、埋め込み酸化物半導体層482a、482bとしては、酸化物半導体層に導電性を付与した金属酸化物で形成しても良い。導電性の金属酸化物としては酸化インジウム( $In_2O_3$ )、酸化スズ( $SnO_2$ )、酸化亜鉛( $ZnO$ )、酸化インジウム酸化スズ( $In_2O_3$   $SnO_2$ 、ITOと略記する)、酸化インジウム酸化亜鉛( $In_2O_3$   $ZnO$ )又はこれらの金属酸化物材料に酸化シリコンを含ませたものを用いることができる。

30

【0157】

また図6(A)は図5(A)で示した半導体装置の構成とは異なる一例であるトランジスタ460の断面図である。

40

【0158】

トランジスタ460は、絶縁表面を有する基板400上に、埋め込み導電層481a、481bが設けられた絶縁層491と、酸化物半導体層403と、第1の導電層405a、405bと、第2の導電層465a、465bと、ゲート絶縁層402と、ゲート電極層401と、層間絶縁層408と、を有する(図6(A)参照)。

【0159】

図6(A)の構造は、図1の構造と同様に、トランジスタ460のソース電極及びドレイン電極として機能する第1の導電層405a、405bを、酸化物半導体層403と重畠

50

する領域において、ゲート絶縁層 402 を介してゲート電極層 401 と重畳させている。また図 6 (A) の構造は、図 1 の構造と同様に、トランジスタ 460 のソース電極及びドレイン電極として機能する第 2 の導電層 465a、465b を、酸化物半導体層 403 と重畳する領域において、ゲート絶縁層 402 を介してゲート電極層 401 と重畳させない。

【0160】

そのため図 6 (A) の構造は、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畳して設けることができ、オン特性を向上させることができる。さらに図 6 (A) の構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。

【0161】

また特に、本実施の形態で開示する図 6 (A) の構造は、図 5 (A) の構造と同様に、トランジスタ 460 の下部に埋め込み導電層 481a、481b が設けられた絶縁層 491 を設け、埋め込み導電層 481a、481b が、酸化物半導体層 403 を介して、第 1 の導電層 405a、405b と、第 2 の導電層 465a、465b とに重畳して設けられている。トランジスタ 460 の下部に埋め込み導電層 481a、481b を設ける構成とすることで、ゲート絶縁層 402 及び層間絶縁層 408 に開口部を設けることなく、トランジスタ間及び外部に設けられた制御回路とを接続することができる。埋め込み導電層 481a、481b は、トランジスタ 460 との接触面積を大きくとることができるために、コントラクト抵抗を低減することができる。

【0162】

また特に、本実施の形態で開示する図 6 (A) の構造は、酸化物半導体層 403 に開口部 485 を設け、第 1 の導電層 405a、405b と、埋め込み導電層 481a、481b とを直接接続する構造としている。該構造とすることにより、トランジスタのソース電極及びドレイン電極となる第 1 の導電層、第 2 の導電層及び埋め込み導電層を流れる電流を大きくすることができる。

【0163】

また図 6 (B) は、図 6 (A) と異なる構成である、トランジスタ 470 の断面図である。

【0164】

トランジスタ 470 は、絶縁表面を有する基板 400 上に、埋め込み導電層 481a、481b 及び埋め込み酸化物半導体層 482a、482b が設けられた絶縁層 491 と、酸化物半導体層 403 と、第 1 の導電層 405a、405b と、第 2 の導電層 465a、465b と、ゲート絶縁層 402 と、ゲート電極層 401 と、層間絶縁層 408 と、を有する(図 6 (B) 参照)。

【0165】

図 6 (B) の構造は、図 1 の構造と同様に、トランジスタ 470 のソース電極及びドレイン電極として機能する第 1 の導電層 405a、405b を、酸化物半導体層 403 と重畳する領域において、ゲート絶縁層 402 を介してゲート電極層 401 と重畳させる。また図 6 (B) の構造は図 1 の構造と同様に、トランジスタ 470 のソース電極及びドレイン電極として機能する第 2 の導電層 465a、465b を、酸化物半導体層 403 と重畳する領域において、ゲート絶縁層 402 を介してゲート電極層 401 と重畳させない。

【0166】

そのため図 6 (B) の構造は、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畳して設けることができ、オン特性を向上させることができる。さらに図 6 (B) の構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。

【0167】

10

20

30

40

50

また特に、本実施の形態で開示する図6(B)の構造は、トランジスタ470の下部に埋め込み導電層481a、481b及び埋め込み酸化物半導体層482a、482bが設けられた絶縁層491を設け、埋め込み導電層481a、481b及び埋め込み酸化物半導体層482a、482bが、酸化物半導体層403を介して、第1の導電層405a、405bと、第2の導電層465a、465bとに重畳して設けられている。トランジスタ470の下部に埋め込み導電層481a、481bを設ける構成とすることで、ゲート絶縁層402及び層間絶縁層408に開口部を設けることなく、トランジスタ間及び外部に設けられる制御回路と接続することができる。また埋め込み導電層481a、481bとトランジスタ470との間に埋め込み酸化物半導体層482a、482bを設ける構成とすることで、埋め込み導電層481a、481bとトランジスタ470との接続を良好なものとすることができます。埋め込み導電層481a、481bは、トランジスタ470との接触面積を大きくとることができ、加えて埋め込み酸化物半導体層482a、482bはトランジスタ470との接続を良好なものとすることができるため、コンタクト抵抗を低減することができる。

#### 【0168】

また特に本実施の形態で開示する図6(B)の構造は、酸化物半導体層403に開口部485を設け、第1の導電層405a、405bと、埋め込み酸化物半導体層482a、482bとを直接接続する構造としている。該構造とすることにより、トランジスタのソース電極及びドレイン電極となる第1の導電層、第2の導電層、埋め込み酸化物半導体層及び埋め込み導電層を流れる電流を大きくすることができる。

#### 【0169】

以上説明したように、本実施の形態の構成では、上記実施の形態1と同様に、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畳して設けることができ、オン特性を向上させることができます。さらに本実施の形態の構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。この場合、酸化物半導体をチャネル形成領域に設けるトランジスタを微細化して形成することができ好適である。また、特に本実施の形態の構成では、埋め込み導電層を設け、トランジスタとのコンタクト抵抗を低減することができる。

#### 【0170】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

#### 【0171】

##### (実施の形態3)

本実施の形態では、半導体装置の他の一形態を、図7を用いて説明する。上記実施の形態と同一部分又は同様な機能を有する部分、及び工程は、上記実施の形態と同様に行うことができ、繰り返しの説明は省略する。また同じ箇所の詳細な説明は省略する。

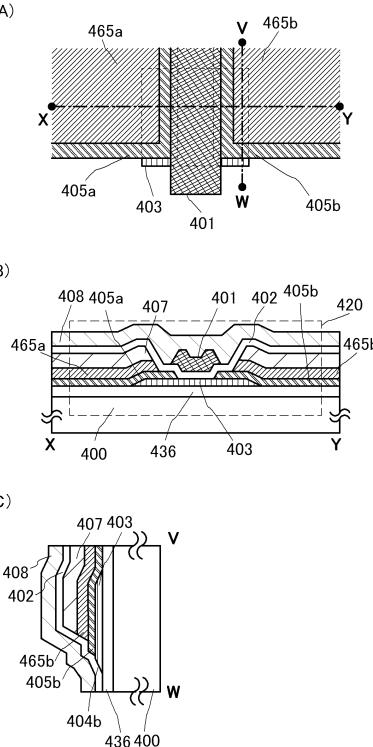

#### 【0172】

本実施の形態において図7(A)は、実施の形態1で示した図1によるトランジスタ420の平面図であり、図7(B)は、図7(A)のX-Yにおける断面図であり、図7(C)は、図7(A)のV-Wにおける断面図である。

#### 【0173】

図7(A)乃至(C)に示すトランジスタ420の構成は、図1と同様に、絶縁表面を有する基板400上に、バッファ層436と、酸化物半導体層403と、第1の導電層405a、405bと、第2の導電層465a、465bと、絶縁層407と、ゲート絶縁層402と、ゲート電極層401と、層間絶縁層408と、を有する。

#### 【0174】

本実施の形態で開示する図7(A)乃至(C)の構造は、図1と同様に、トランジスタ420のソース電極及びドレイン電極として機能する第1の導電層405a、405bを、酸化物半導体層403と重畳する領域において、ゲート絶縁層402を介してゲート電極層401と重畳させている。また本実施の形態で開示する図7(A)乃至(C)の構造は

10

20

30

40

50

、トランジスタ420のソース電極及びドレイン電極として機能する第2の導電層465a、465bを、酸化物半導体層403と重疊する領域において、ゲート絶縁層402を介してゲート電極層401と重疊させない。

【0175】

本実施の形態で開示する図7(A)乃至(C)の構造は、トランジスタのソース電極及びドレイン電極となる第1の導電層405a、405bの端部と、ゲート電極となるゲート電極層401の端部とを重疊して設けることができる。そのため、トランジスタのオン特性(例えば、オン電流や電界効果移動度)を向上させて、半導体装置の高速応答、高速駆動を実現することができる。

【0176】

また本実施の形態で開示する図7(A)乃至(C)の構造は、トランジスタのソース電極及びドレイン電極となる第1の導電層405a、405bを薄膜化することができる。第1の導電層405a、405bを薄膜化することで、特に酸化物半導体層403のチャネル形成領域周辺での、ゲート絶縁層402を形成する際の表面の段差を小さくすることができる。従って、ゲート絶縁層402は、カバレッジを良好にして形成することができる。カバレッジ不良を低減することで、電極間の短絡の発生を抑制し、信頼性の向上を図ることができる。

【0177】

また、第1の導電層405a、405bを薄膜化することで、酸化物半導体層403上に形成された第1の導電層405の厚さを均一にしておくことが可能になる。また第1の導電層405を薄膜化して形成しておくことで、エッティング等の工程により第1の導電層405a、405bを加工する際の所要期間を短くすることができる。そのため第1の導電層405a、405bをエッティング等の工程で加工する際に生じる、酸化物半導体層403へのダメージを低減することができる。そのため、信頼性の向上を図ることができる。

【0178】

また本実施の形態で開示する図7(A)乃至(C)の構造は、ゲート絶縁層402を薄膜化するとともに、酸化物半導体層403を薄膜化することができる。ゲート絶縁層402及び酸化物半導体層403を薄膜化することで、オン特性の向上が図れるとともに、トランジスタを完全空乏型で動作させることも可能である。トランジスタを完全空乏型で動作させることで、高集積化、高速駆動化、低消費電力化を図ることができる。

【0179】

加えて、本実施の形態で開示する図7(A)乃至(C)の構造は、トランジスタのソース電極及びドレイン電極となる第2の導電層465a、465bの端部と、ゲート電極となるゲート電極層401の端部とを重疊させないで設けることができる。そのため、第1の導電層405a、405bに比べて第2の導電層465a、465bを厚膜化しても、電極間の短絡がない。したがって、第2の導電層465a、465bを厚膜化することで、電極間での短絡を引き起こすことなく、ソース電極及びドレイン電極を流れる電流を大きくすることができる。

【0180】

また本実施の形態で開示する図7(A)乃至(C)の構造は、第2の導電層465a、465bと絶縁層407とを重疊して設け、側面をエッティング等の加工によりテーパー状とすることができます。そのため第2の導電層465a、465bを厚膜化しても、カバレッジを良好にすることができます。

【0181】

以上説明したように、本実施の形態で開示する図7(A)乃至(C)の構成では、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重疊して設けることができ、オン特性を向上させることができる。さらに本実施の形態で開示する図7(A)乃至(C)の構成では、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができる。この場合、酸化物半導体をチャネル形成領域に設けるトランジスタ

10

20

30

40

50

ンジスタを微細化して形成することができ好適である。

【0182】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0183】

(実施の形態4)

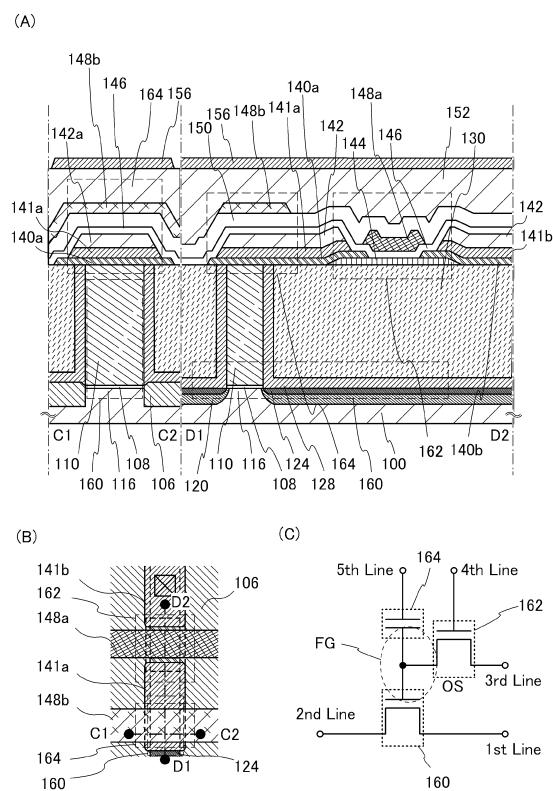

本実施の形態では、実施の形態1乃至3に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置の一例を、図面を用いて説明する。なお、本実施の形態の半導体装置は、トランジスタ162として実施の形態1乃至3に記載のトランジスタを適用して構成される。

【0184】

10

トランジスタ162は、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作を必要としない、或いは、リフレッシュ動作の頻度が極めて少ない半導体記憶装置とすることが可能となるため、消費電力を十分に低減することができる。

【0185】

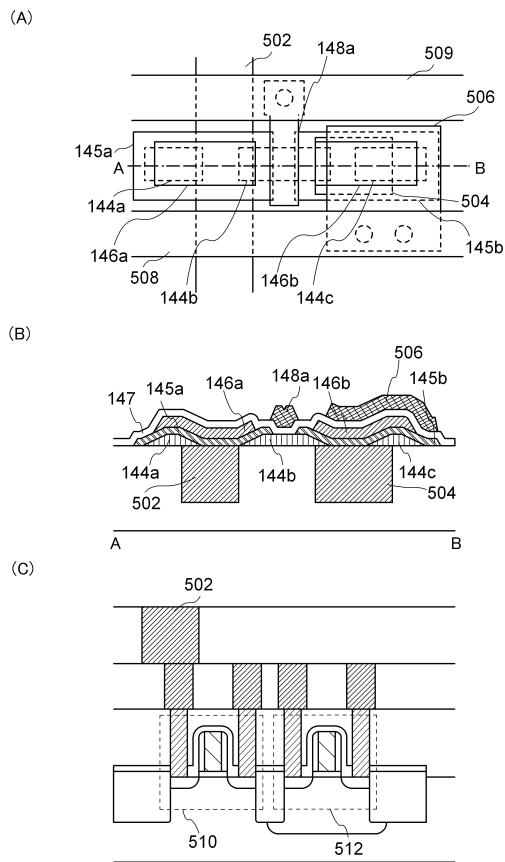

図8は、半導体装置の構成の一例である。図8(A)に、半導体装置の断面図を、図8(B)に半導体装置の平面図を、図8(C)に半導体装置の回路図をそれぞれ示す。ここで、図8(A)は、図8(B)のC1-C2、及びD1-D2における断面に相当する。

【0186】

20

図8(A)及び図8(B)に示す半導体装置は、下部に第1の半導体材料を用いたトランジスタ160を有し、上部に第2の半導体材料を用いたトランジスタ162を有するものである。トランジスタ162は、実施の形態1乃至3で示した構成と同一の構成とすることができます。

【0187】

ここで、第1の半導体材料と第2の半導体材料は異なる禁制帯幅を持つ材料とすることが望ましい。例えば、第1の半導体材料を酸化物半導体以外の半導体材料(シリコンなど)とし、第2の半導体材料を酸化物半導体とすることができます。酸化物半導体以外の材料を用いたトランジスタは、高速動作が容易である。一方で、酸化物半導体を用いたトランジスタは、その特性により長時間の電荷保持を可能とする。

【0188】

30

なお、上記トランジスタは、いずれもnチャネル型トランジスタであるものとして説明するが、pチャネル型トランジスタを用いることができるのはいうまでもない。また、開示する発明の技術的な本質は、情報を保持するために酸化物半導体をトランジスタ162に用いる点にあるから、半導体装置に用いられる材料や半導体装置の構造など、半導体装置の具体的な構成をここで示すものに限定する必要はない。

【0189】

図8(A)におけるトランジスタ160は、半導体材料(例えば、シリコンなど)を含む基板100に設けられたチャネル形成領域116と、チャネル形成領域116を挟むように設けられた不純物領域120と、不純物領域120に接する金属間化合物領域124と、チャネル形成領域116上に設けられたゲート絶縁層108と、ゲート絶縁層108上に設けられたゲート電極層110と、を有する。

40

【0190】

基板100上にはトランジスタ160を囲むように素子分離絶縁層106が設けられており、トランジスタ160を覆うように絶縁層128及び層間絶縁層130が設けられている。なお、高集積化を実現するためには、図8(A)に示すようにトランジスタ160がサイドウォール絶縁層を有しない構成とすることが望ましい。一方で、トランジスタ160の特性を重視する場合には、ゲート電極層110の側面にサイドウォール絶縁層を設け、不純物濃度が異なる領域を含む不純物領域120としてもよい。

【0191】

図8(A)に示すトランジスタ162は、酸化物半導体をチャネル形成領域に用いたトランジ

50

ンジスタである。ここで、トランジスタ 162 に含まれる酸化物半導体層 144 は、高純度化されたものであることが望ましい。高純度化された酸化物半導体を用いることで、極めて優れたオフ特性のトランジスタ 162 を得ることができる。

【0192】

トランジスタ 162 上には、絶縁層 150 が単層又は積層で設けられている。また、絶縁層 150 を介して、トランジスタ 162 の電極層となる第 1 の導電層 140a 及び第 2 の導電層 141a と重畳する領域には、導電層 148b が設けられており、第 1 の導電層 140a 及び第 2 の導電層 141a と、絶縁層 142 及び絶縁層 150 と、導電層 148b とによって、容量素子 164 が構成される。すなわち、トランジスタ 162 の第 1 の導電層 140a 及び第 2 の導電層 141a は、容量素子 164 の一方の電極として機能し、導電層 148b は、容量素子 164 の他方の電極として機能する。なお、容量が不要の場合には、容量素子 164 を設けない構成とすることもできる。また、容量素子 164 は、別途、トランジスタ 162 の上方に設けてよい。

【0193】

トランジスタ 162 および容量素子 164 の上には絶縁層 152 が設けられている。そして、絶縁層 152 上にはトランジスタ 162 と、他のトランジスタを接続するための配線 156 が設けられている。図 8 (A) には図示しないが、配線 156 は、絶縁層 150、絶縁層 152 及びゲート絶縁層 146 などに形成された開口に形成された電極を介して第 2 の導電層 141a 及び第 2 の導電層 141b に接続される。

【0194】

ここで、第 1 の導電層 140a 及び第 1 の導電層 140b は、実施の形態 1 で説明したように、トランジスタ 162 のゲート電極となる導電層 148a の一部と重畳するように設ける。また第 2 の導電層 141a 及び第 2 の導電層 141b は、実施の形態 1 で説明したように、トランジスタ 162 のゲート電極となる導電層 148a の一部と重畳しないように設ける。その結果、トランジスタのソース電極及びドレイン電極を流れる電流を低減させることなく、トランジスタのソース電極及びドレイン電極と、ゲート電極とを重畳して設けることができ、オン特性を向上させることができる。また、ゲート絶縁層のカバレッジ不良を低減することで、酸化物半導体層及びゲート絶縁層を薄膜化することができ、トランジスタを微細化して形成することができる。

【0195】

図 8 (A) 及び図 8 (B) において、トランジスタ 160 と、トランジスタ 162 とは、少なくとも一部が重畳するように設けられており、トランジスタ 160 のソース領域又はドレイン領域と酸化物半導体層 144 の一部が重畳するように設けられているのが好ましい。また、トランジスタ 162 及び容量素子 164 が、トランジスタ 160 の少なくとも一部と重畳するように設けられている。例えば、容量素子 164 の一方の電極である第 1 の導電層 140a は、トランジスタ 160 のゲート電極層 110 と少なくとも一部が重畳して設けられている。このような平面レイアウトを採用することにより、半導体装置の占有面積の低減を図ることができるため、高集積化を図ることができる。

【0196】

次に、図 8 (A) 及び図 8 (B) に対応する回路構成の一例を図 8 (C) に示す。

【0197】

図 8 (C) において、第 1 の配線 (1st Line) は、トランジスタ 160 のソース電極に接続されている。また第 2 の配線 (2nd Line) は、トランジスタ 160 のドレイン電極に接続されている。また、第 3 の配線 (3rd Line) は、トランジスタ 162 のソース電極又はドレイン電極の一方に接続されている。また第 4 の配線 (4th Line) は、トランジスタ 162 のゲート電極に接続されている。またトランジスタ 160 のゲート電極は、トランジスタ 162 のソース電極又はドレイン電極の一方と、容量素子 164 の電極の一方とに接続されている。また第 5 の配線 (5th Line) は、容量素子 164 の電極の他方に接続されている。

【0198】

10

20

30

40

50

図8(C)に示す半導体装置では、トランジスタ160のゲート電極の電位が保持可能という特徴を生かすことで、次のように、情報の書き込み、保持、読み出しが可能である。

#### 【0199】

情報の書き込みおよび保持について説明する。まず、第4の配線の電位を、トランジスタ162がオン状態となる電位にして、トランジスタ162をオン状態とする。これにより、第3の配線の電位が、トランジスタ160のゲート電極、および容量素子164の一方の電極に与えられる。すなわち、トランジスタ160のゲート電極には、所定の電荷が与えられる(書き込み)。ここでは、異なる二つの電位レベル(Hレベル、Lレベル)のいずれかが与えられるものとする。その後、第4の配線の電位を、トランジスタ162がオフ状態となる電位にして、トランジスタ162をオフ状態とすることにより、トランジスタ160のゲート電極に与えられた電位が保持される(保持)。

10

#### 【0200】

トランジスタ162のオフ電流は極めて小さいため、トランジスタ160のゲート電極の電荷は長時間にわたって保持される。

#### 【0201】

次に情報の読み出しについて説明する。第1の配線に所定の電位(定電位)を与えた状態で、第5の配線に適切な電位(読み出し電位)を与えると、トランジスタ160のゲート電極の電位に応じて、第2の配線は異なる電位をとる。該異なる電位は、トランジスタ160をnチャネル型とすると、トランジスタ160のゲート電極にHレベルが与えられている場合の見かけのしきい値電圧 $V_{th\_H}$ が、トランジスタ160のゲート電極にLレベルが与えられている場合の見かけのしきい値電圧 $V_{th\_L}$ より低くなるためである。ここで、見かけのしきい値電圧とは、トランジスタ160を「オン状態」とするために必要な第5の配線の電位をいうものとする。したがって、第5の配線の電位を $V_{th\_H}$ と $V_{th\_L}$ の間の電位 $V_0$ とすることにより、トランジスタ160のゲート電極に与えられた電荷を判別できる。例えば、書き込みにおいて、Hレベルが与えられていた場合には、第5の配線の電位が $V_0$  ( $> V_{th\_H}$ )となれば、トランジスタ160は「オン状態」となる。Lレベルが与えられていた場合には、第5の配線の電位が $V_0$  ( $< V_{th\_L}$ )となっても、トランジスタ160は「オフ状態」のままである。このため、第2の配線の電位を見ることで、保持されている情報を読み出すことができる。

20

#### 【0202】

30

なお、メモリセルをアレイ状に配置して用いる場合、所望のメモリセルの情報のみを読み出せることが必要になる。このように情報を読み出さない場合には、ゲート電極の状態にかかわらずトランジスタ160が「オフ状態」となるような電位、つまり、 $V_{th\_H}$ より小さい電位を第5の配線に与えればよい。又は、ゲート電極の状態にかかわらずトランジスタ160が「オン状態」となるような電位、つまり、 $V_{th\_L}$ より大きい電位を第5の配線に与えればよい。

#### 【0203】

本実施の形態に示す半導体装置では、チャネル形成領域に酸化物半導体を用いたオフ電流の極めて小さいトランジスタを適用することで、極めて長期にわたり記憶内容を保持することが可能である。つまり、リフレッシュ動作が不要となるか、又は、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合(ただし、電位は固定されていることが望ましい)であっても、長期にわたって記憶内容を保持することが可能である。

40

#### 【0204】

また、本実施の形態に示す半導体装置では、情報の書き込みに高い電圧を必要とせず、素子の劣化の問題もない。例えば、従来の不揮発性メモリのように、フローティングゲートへの電子の注入や、フローティングゲートからの電子の引き抜きを行う必要がないため、ゲート絶縁層の劣化といった問題が全く生じない。すなわち、開示する発明に係る半導体装置では、従来の不揮発性メモリで問題となっている書き換え可能回数に制限はなく、信頼性が飛躍的に向上する。さらに、トランジスタのオン状態、オフ状態によって、情報の

50

書き込みが行われるため、高速な動作も容易に実現しうる。

【0205】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0206】

(実施の形態5)

本実施の形態においては、実施の形態1乃至3に示すトランジスタを使用し、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い半導体装置について、実施の形態4に示した構成と異なる構成を図9及び図10を用いて説明する。なお、本実施の形態の半導体装置は、トランジスタ162として実施の形態1乃至3に記載のトランジスタを適用して構成される。

10

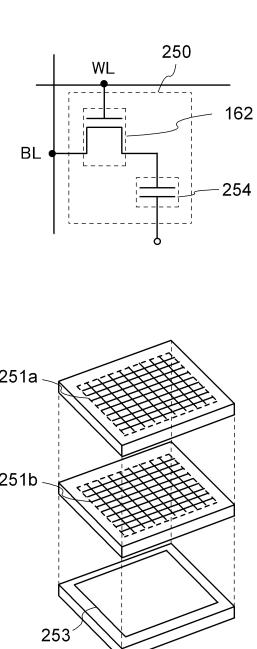

【0207】

図9(A)は、半導体装置の回路構成の一例を示し、図9(B)は半導体装置の一例を示す概念図である。まず、図9(A)に示す半導体装置について説明を行い、続けて図9(B)に示す半導体装置について、以下説明を行う。

【0208】

図9(A)に示す半導体装置において、ビット線BLは、トランジスタ162のソース電極又はドレイン電極となる一方の電極に接続される。ワード線WLは、トランジスタ162のゲート電極に接続される。トランジスタ162のソース電極又はドレイン電極となる他方の電極は、容量素子254の一方の電極に接続される。

20

【0209】

酸化物半導体を用いたトランジスタ162は、オフ電流が極めて小さいという特徴を有している。このため、トランジスタ162をオフ状態とすることで、容量素子254の一方の電極の電位(あるいは、容量素子254に蓄積された電荷)を極めて長時間にわたって保持することが可能である。

【0210】

次に、図9(A)に示す半導体装置(メモリセル250)に、情報の書き込みおよび保持を行う場合について説明する。

【0211】

まず、ワード線WLの電位を、トランジスタ162がオン状態となる電位として、トランジスタ162をオン状態とする。これにより、ビット線BLの電位が、容量素子254の一方の電極に与えられる(書き込み)。その後、ワード線WLの電位を、トランジスタ162がオフ状態となる電位として、トランジスタ162をオフ状態とすることにより、容量素子254の一方の電極の電位が保持される(保持)。

30

【0212】

トランジスタ162のオフ電流は極めて小さいため、容量素子254の一方の電極の電位(あるいは容量素子に蓄積された電荷)は長時間にわたって保持することができる。

【0213】

次に、情報の読み出しについて説明する。トランジスタ162がオン状態となると、浮遊状態であるビット線BLと容量素子254の一方の電極とが導通し、ビット線BLと容量素子254の一方の電極の間で電荷が再分配される。その結果、ビット線BLの電位が変化する。ビット線BLの電位の変化量は、容量素子254の一方の電極の電位(あるいは容量素子254に蓄積された電荷)によって、異なる値をとる。

40

【0214】

例えば、容量素子254の一方の電極の電位をV、容量素子254の静電容量をC、ビット線BLが有する静電容量成分(以下、ビット線容量とも呼ぶ)をCB、電荷が再分配される前のビット線BLの電位をV<sub>B0</sub>とすると、電荷が再分配された後のビット線BLの電位は、 $(C_B \times V_{B0} + C \times V) / (C_B + C)$ となる。したがって、メモリセル250の状態として、容量素子254の一方の電極の電位がV<sub>1</sub>とV<sub>0</sub>(V<sub>1</sub> > V<sub>0</sub>)の2状態をとるとすると、電位V<sub>1</sub>を保持している場合のビット線BLの電位(= C<sub>B</sub> × V<sub>B0</sub> + C × V<sub>1</sub>) / (C<sub>B</sub> + C)は、電位V<sub>0</sub>を保持している場合のビット線BLの電位(= C<sub>B</sub> × V<sub>B0</sub> + C × V<sub>0</sub>) / (C<sub>B</sub> + C)である。

50

$= C_B \times V_B 0 + C \times V 0) / (C_B + C)$  よりも高くなることがわかる。

【0215】

そして、ビット線 B\_L の電位を所定の電位と比較することで、情報を読み出すことができる。

【0216】

このように、図9(A)に示す半導体装置は、トランジスタ162のオフ電流が極めて小さいという特徴から、容量素子254に蓄積された電荷は長時間にわたって保持することができる。つまり、リフレッシュ動作が不要となるか、又は、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、電力の供給がない場合であっても、長期にわたって記憶内容を保持することが可能である。

10

【0217】

次に、図9(B)に示す半導体装置について、説明を行う。

【0218】

図9(B)に示す半導体装置は、上部に記憶回路として図9(A)に示したメモリセル250を複数有するメモリセルアレイ251a及び251bを有し、下部に、メモリセルアレイ251a及びメモリセルアレイ251bを動作させるために必要な周辺回路253を有する。なお、周辺回路253は、メモリセルアレイ251(メモリセルアレイ251a及び251b)に接続されている。

20

【0219】

図9(B)に示した構成とすることにより、周辺回路253をメモリセルアレイ251の直下に設けることができるため半導体装置の小型化を図ることができる。

【0220】

周辺回路253に設けられるトランジスタは、トランジスタ162とは異なる半導体材料を用いるのがより好ましい。例えば、シリコン、ゲルマニウム、シリコンゲルマニウム、炭化シリコン、又はガリウムヒ素等を用いることができ、単結晶半導体を用いることが好ましい。他に、有機半導体材料などを用いてもよい。このような半導体材料を用いたトランジスタは、十分な高速動作が可能である。したがって、該トランジスタにより、高速動作が要求される各種回路(論理回路、駆動回路など)を好適に実現することができる。

30

【0221】

なお、図9(B)に示した半導体装置では、2つのメモリセルアレイ(メモリセルアレイ251aと、メモリセルアレイ251b)が積層された構成を例示したが、積層するメモリセルアレイの数はこれに限定されない。3つ以上のメモリセルアレイを積層する構成としても良い。

【0222】

次に、図9(A)に示したメモリセル250の具体的な構成について図10を用いて説明を行う。

【0223】

図10は、メモリセル250の構成の一例である。図10(A)に、メモリセル250の平面図を、図10(B)に図10(A)の線分A-Bにおける断面図をそれぞれ示す。

40

【0224】

図10(A)及び図10(B)に示すトランジスタ162は、実施の形態1乃至3で示したトランジスタの構成と同一の構成とすることができる。

【0225】

図10(B)に示すように、埋め込み導電層502及び埋め込み導電層504上にトランジスタ162が設けられている。埋め込み導電層502は、図10(A)におけるビット線B\_Lとして機能する配線であり、トランジスタ162の第1の導電層145aと接して設けられている。また、埋め込み導電層504は、図10(A)における容量素子254の一方の電極として機能し、トランジスタ162の第1の導電層145bと接して設けら

50

れている。また、トランジスタ 162 の第 1 の導電層 145a 上には、第 2 の導電層 146a が接して設けられている。また、トランジスタ 162 の第 1 の導電層 145b 上には、第 2 の導電層 146b が接して設けられている。またトランジスタ 162 上において、第 2 の導電層 146b は、容量素子 254 の一方の電極として機能する。またトランジスタ 162 上において、第 2 の導電層 146b と重畳する領域に設けられた導電層 506 は、容量素子 254 の他方の電極として機能する。

【0226】

また、図 10 (A) に示すように、容量素子 254 の他方の導電層 506 は、容量線 508 に接続される。ゲート絶縁層 147 を介して酸化物半導体層 144 上に設けられたゲート電極として機能する導電層 148a は、ワード線 509 に接続される。

10

【0227】

また、図 10 (C) に、メモリセルアレイ 251 と、周辺回路との接続部における断面図を示す。周辺回路は、例えば n チャネル型トランジスタ 510 及び p チャネル型トランジスタ 512 を含む構成とすることができる。n チャネル型トランジスタ 510 及び p チャネル型トランジスタ 512 に用いる半導体材料としては、酸化物半導体以外の半導体材料 (シリコンなど) を用いるのが好ましい。このような材料を用いることで、周辺回路に含まれるトランジスタの高速動作を図ることができる。

【0228】

図 10 (A) に示す平面レイアウトを採用することにより、半導体装置の占有面積の低減を図ることができるため、高集積化を図ることができる。

20

【0229】

以上のように、上部に多層に形成された複数のメモリセルは、酸化物半導体を用いたトランジスタにより形成されている。インジウム、亜鉛、及び酸素を少なくとも含む非単結晶の酸化物半導体を用いたトランジスタは、オフ電流が小さいため、これを用いることにより長期にわたり記憶内容を保持することができる。つまり、リフレッシュ動作の頻度を極めて低くすることが可能となるため、消費電力を十分に低減することができる。また、容量素子 254 は、図 10 (B) で示すように埋め込み導電層 504、酸化物半導体層 144、ゲート絶縁層 147、導電層 506 が積層されることによって形成される。

【0230】

このように、酸化物半導体以外の材料を用いたトランジスタを用いた周辺回路と、酸化物半導体を用いたトランジスタを用いた記憶回路とを一体に備えることで、これまでにない特徴を有する半導体装置を実現することができる。また、周辺回路と記憶回路を積層構造とすることにより、半導体装置の集積化を図ることができる。

30

【0231】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【0232】

(実施の形態 6)

本実施の形態では、先の実施の形態で示した半導体装置を携帯電話、スマートフォン、電子書籍などの携帯機器に応用した場合の例を図 11 乃至図 14 を用いて説明する。

【0233】

40

携帯電話、スマートフォン、電子書籍などの携帯機器においては、画像データの一時記憶などに S R A M 又は D R A M が使用されている。S R A M 又は D R A M が使用される理由としてはフラッシュメモリでは応答が遅く、画像処理では不向きであるためである。一方で、S R A M 又は D R A M を画像データの一時記憶に用いた場合、以下の特徴がある。

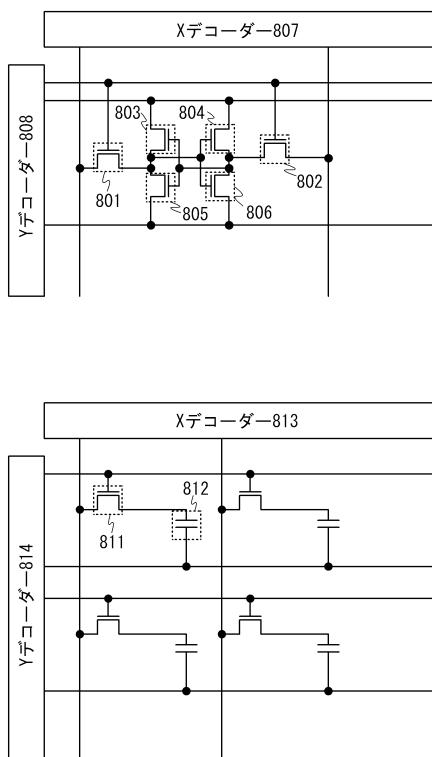

【0234】

通常の S R A M は、図 11 (A) に示すように 1 つのメモリセルがトランジスタ 801 ~ 806 の 6 個のトランジスタで構成されており、それを X デコーダー 807、Y デコーダー 808 にて駆動している。トランジスタ 803 とトランジスタ 805、トランジスタ 804 とトランジスタ 806 はインバータを構成し、高速駆動を可能としている。しかし 1 つのメモリセルが 6 トランジスタで構成されているため、セル面積が大きいという欠点が

50

ある。デザインルールの最小寸法を  $F$  としたときに S R A M のメモリセル面積は通常  $100 \sim 150 F^2$  である。このため S R A M はビットあたりの単価が各種メモリの中で最も高い。

### 【 0 2 3 5 】

それに対して、D R A M はメモリセルが図 1 1 ( B ) に示すようにトランジスタ 8 1 1、保持容量 8 1 2 によって構成され、それを X デコーダー 8 1 3、Y デコーダー 8 1 4 にて駆動している。1 つのセルが 1 トランジスタ 1 容量の構成になっており、面積が小さい。D R A M のメモリセル面積は通常  $10 F^2$  以下である。ただし、D R A M は常にリフレッシュが必要であり、書き換えをおこなわない場合でも電力を消費する。

### 【 0 2 3 6 】

しかし、先の実施の形態で説明した半導体装置のメモリセル面積は、 $10 F^2$  前後であり、且つ頻繁なリフレッシュは不要である。したがって、メモリセル面積が縮小され、且つ消費電力が低減することができる。

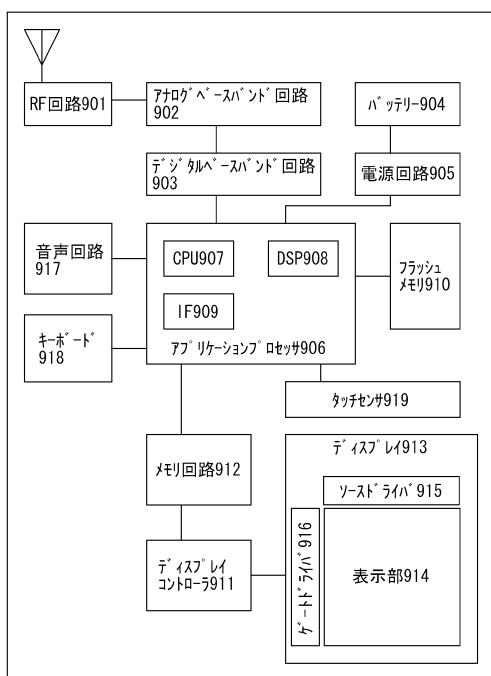

### 【 0 2 3 7 】

図 1 2 に携帯機器のブロック図を示す。図 1 2 に示す携帯機器は R F 回路 9 0 1、アナログベースバンド回路 9 0 2、デジタルベースバンド回路 9 0 3、バッテリー 9 0 4、電源回路 9 0 5、アプリケーションプロセッサ 9 0 6、フラッシュメモリ 9 1 0、ディスプレイコントローラ 9 1 1、メモリ回路 9 1 2、ディスプレイ 9 1 3、タッチセンサ 9 1 9、音声回路 9 1 7、キーボード 9 1 8 などより構成されている。ディスプレイ 9 1 3 は表示部 9 1 4、ソースドライバ 9 1 5、ゲートドライバ 9 1 6 によって構成されている。アプリケーションプロセッサ 9 0 6 は C P U 9 0 7、D S P 9 0 8、インターフェイス 9 0 9 を有している。一般にメモリ回路 9 1 2 は S R A M 又は D R A M で構成されており、この部分に先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

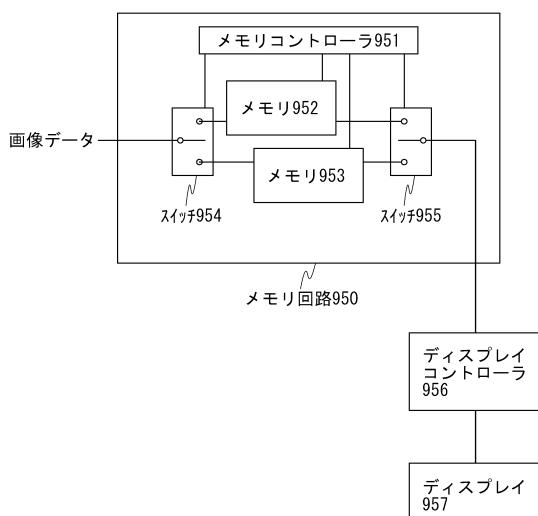

### 【 0 2 3 8 】

図 1 3 に、ディスプレイのメモリ回路 9 5 0 に先の実施の形態で説明した半導体装置を使用した例を示す。図 1 3 に示すメモリ回路 9 5 0 は、メモリ 9 5 2、メモリ 9 5 3、スイッチ 9 5 4、スイッチ 9 5 5 およびメモリコントローラ 9 5 1 により構成されている。また、メモリ回路は、画像データ（入力画像データ）を送る 信号線、メモリ 9 5 2、及びメモリ 9 5 3 に記憶されたデータ（記憶画像データ）を読み出し、及び制御を行うディスプレイコントローラ 9 5 6 と、ディスプレイコントローラ 9 5 6 からの信号により表示するディスプレイ 9 5 7 が接続されている。

### 【 0 2 3 9 】

まず、ある画像データがアプリケーションプロセッサ（図示しない）によって、形成される（入力画像データ A）。入力画像データ A は、スイッチ 9 5 4 を介してメモリ 9 5 2 に記憶される。そしてメモリ 9 5 2 に記憶された画像データ（記憶画像データ A）は、スイッチ 9 5 5、及びディスプレイコントローラ 9 5 6 を介してディスプレイ 9 5 7 に送られ、表示される。

### 【 0 2 4 0 】

入力画像データ A に変更が無い場合、記憶画像データ A は、通常  $30 \sim 60 \text{ Hz}$  程度の周期でメモリ 9 5 2 からスイッチ 9 5 5 を介して、ディスプレイコントローラ 9 5 6 から読み出される。

### 【 0 2 4 1 】

次に、例えばユーザーが画面を書き換える操作をしたとき（すなわち、入力画像データ A に変更が有る場合）、アプリケーションプロセッサは新たな画像データ（入力画像データ B）を形成する。入力画像データ B はスイッチ 9 5 4 を介してメモリ 9 5 3 に記憶される。この間も定期的にメモリ 9 5 2 からスイッチ 9 5 5 を介して記憶画像データ A は読み出されている。メモリ 9 5 3 に新たな画像データ（記憶画像データ B）が記憶し終わると、ディスプレイ 9 5 7 の次のフレームより、記憶画像データ B は読み出され、スイッチ 9 5

10

20

30

40

50

5、及びディスプレイコントローラ 956 を介して、ディスプレイ 957 に記憶画像データ B が送られ、表示がおこなわれる。この読み出しあはさらに次に新たな画像データがメモリ 952 に記憶されるまで継続される。

【0242】

このようにメモリ 952 及びメモリ 953 は交互に画像データの書き込みと、画像データの読み出しを行うことによって、ディスプレイ 957 の表示をおこなう。なお、メモリ 952 及びメモリ 953 はそれぞれ別のメモリには限定されず、1つのメモリを分割して使用してもよい。先の実施の形態で説明した半導体装置をメモリ 952 及びメモリ 953 に採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

10

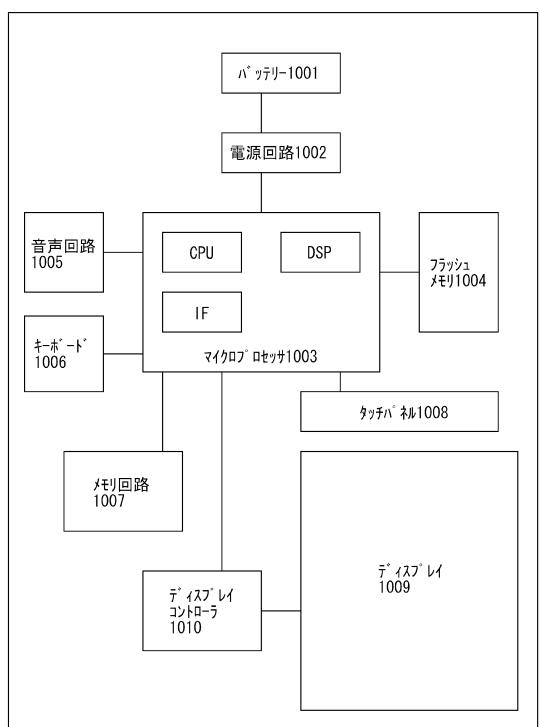

【0243】

図 14 に電子書籍のブロック図を示す。図 14 に示す電子書籍はバッテリー 1001、電源回路 1002、マイクロプロセッサ 1003、フラッシュメモリ 1004、音声回路 1005、キーボード 1006、メモリ回路 1007、タッチパネル 1008、ディスプレイ 1009、ディスプレイコントローラ 1010 によって構成される。

【0244】

ここでは、図 14 のメモリ回路 1007 に先の実施の形態で説明した半導体装置を使用することができる。メモリ回路 1007 の役割は書籍の内容を一時的に保持する機能を持つ。機能の例としては、ユーザーがハイライト機能を使用する場合などがある。ユーザーが電子書籍を読んでいるときに、特定の箇所にマーキングをしたい場合がある。このマーキング機能をハイライト機能と言い、表示の色を変える、アンダーラインを引く、文字を太くする、文字の書体を変えるなどによって、周囲との違いを示すことである。ユーザーが指定した箇所の情報を記憶し、保持する機能である。この情報を長期に保存する場合にはフラッシュメモリ 1004 にコピーしても良い。このような場合においても、先の実施の形態で説明した半導体装置を採用することによって、情報の書き込みおよび読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力が十分に低減することができる。

20

【0245】

以上のように、本実施の形態に示す携帯機器には、先の実施の形態に係る半導体装置が搭載されている。このため、読み出しが高速で、長期間の記憶保持が可能で、且つ消費電力を低減した携帯機器が実現される。

30

【0246】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することが可能である。

【0247】

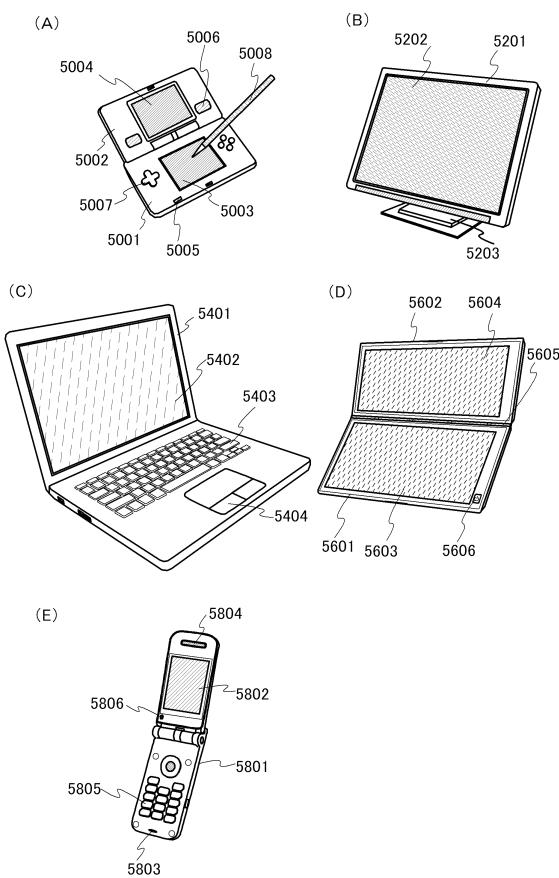

(実施の形態 7)

本発明の一態様に係る半導体装置は、表示機器、パーソナルコンピュータ、記録媒体を備えた画像再生装置（代表的にはDVD：Digital Versatile Disc 等の記録媒体を再生し、その画像を表示しうるディスプレイを有する装置）に用いることができる。その他に、本発明の一態様に係る半導体装置を用いることができる電子機器として、携帯電話、携帯型を含むゲーム機、携帯情報端末、電子書籍、ビデオカメラやデジタルスチルカメラ等のカメラ、ゴーグル型ディスプレイ（ヘッドマウントディスプレイ）、ナビゲーションシステム、音響再生装置（カーオーディオ、デジタルオーディオプレイヤー等）、複写機、ファクシミリ、プリンター、プリンター複合機、現金自動預け入れ払い機（ATM）、自動販売機などが挙げられる。これら電子機器の具体例を図 15 に示す。

40

【0248】

図 15 (A) は携帯型ゲーム機であり、筐体 5001、筐体 5002、表示部 5003、表示部 5004、マイクロホン 5005、スピーカー 5006、操作キー 5007、スタイルス 5008 等を有する。携帯型ゲーム機の駆動回路に、本発明の一態様に係る半導体装置を用いることで、動作速度の速い携帯型ゲーム機を提供することができる。或いは、本発明の一態様に係る半導体装置を用いることで、携帯型ゲーム機の小型化を実現するこ

50

とができる。なお、図15(A)に示した携帯型ゲーム機は、2つの表示部5003と表示部5004とを有しているが、携帯型ゲーム機が有する表示部の数は、これに限定されない。

【0249】

図15(B)は表示機器であり、筐体5201、表示部5202、支持台5203等を有する。表示機器の駆動回路に、本発明の一態様に係る半導体装置を用いることで、動作速度の速い表示機器を提供することができる。或いは、本発明の一態様に係る半導体装置を用いることで、表示機器の小型化を実現することができる。なお、表示機器には、パーソナルコンピュータ用、TV放送受信用、広告表示用などの全ての情報表示用表示機器が含まれる。

10

【0250】

図15(C)はノート型パーソナルコンピュータであり、筐体5401、表示部5402、キーボード5403、ポインティングデバイス5404等を有する。ノート型パーソナルコンピュータの駆動回路に、本発明の一態様に係る半導体装置を用いることで、動作速度の速いノート型パーソナルコンピュータを提供することができる。或いは、本発明の一態様に係る半導体装置を用いることで、ノート型パーソナルコンピュータの小型化を実現することができる。

【0251】

図15(D)は携帯情報端末であり、第1筐体5601、第2筐体5602、第1表示部5603、第2表示部5604、接続部5605、操作キー5606等を有する。第1表示部5603は第1筐体5601に設けられており、第2表示部5604は第2筐体5602に設けられている。そして、第1筐体5601と第2筐体5602とは、接続部5605により接続されており、第1筐体5601と第2筐体5602との間の角度は、接続部5605により可動となっている。第1表示部5603における映像の切り替えを、接続部5605における第1筐体5601と第2筐体5602との間の角度に従って、切り替える構成としても良い。また、第1表示部5603及び第2表示部5604の少なくとも一方に、位置入力装置としての機能が付加された半導体表示装置を用いるようにしても良い。なお、位置入力装置としての機能は、半導体表示装置にタッチパネルを設けることでも、付加することができる。或いは、位置入力装置としての機能は、フォトセンサとも呼ばれる光電変換素子を半導体表示装置の画素部に設けることでも、付加することができる。携帯情報端末の駆動回路に、本発明の一態様に係る半導体装置を用いることで、動作速度の速い携帯情報端末を提供することができる。或いは、本発明の一態様に係る半導体装置を用いることで、携帯情報端末の小型化を実現することができる。

20

【0252】

図15(E)は携帯電話であり、筐体5801、表示部5802、音声入力部5803、音声出力部5804、操作キー5805、受光部5806等を有する。受光部5806において受信した光を電気信号に変換することで、外部の画像を取り込むことができる。携帯電話の駆動回路に、本発明の一態様に係る半導体装置を用いることで、動作速度の速い携帯電話を提供することができる。或いは、本発明の一態様に係る半導体装置を用いることで、携帯電話の小型化を実現することができる。

30

【0253】

本実施の形態は、他の実施の形態と適宜組み合わせて実施することができる。

【符号の説明】

【0254】

100 基板

106 素子分離絶縁層

108 ゲート絶縁層

110 ゲート電極層

116 チャネル形成領域

120 不純物領域

40

50

|         |          |    |

|---------|----------|----|

| 1 2 4   | 金属間化合物領域 |    |

| 1 2 8   | 絶縁層      |    |

| 1 3 0   | 層間絶縁層    |    |

| 1 4 0 a | 導電層      |    |

| 1 4 0 b | 導電層      |    |

| 1 4 1 a | 導電層      |    |

| 1 4 1 b | 導電層      |    |

| 1 4 2   | 絶縁層      |    |

| 1 4 4   | 酸化物半導体層  |    |

| 1 4 5 a | 導電層      | 10 |

| 1 4 5 b | 導電層      |    |

| 1 4 6   | ゲート絶縁層   |    |

| 1 4 8 a | 導電層      |    |

| 1 4 8 b | 導電層      |    |

| 1 5 0   | 絶縁層      |    |

| 1 5 2   | 絶縁層      |    |

| 1 5 3   | 導電層      |    |

| 1 5 6   | 配線       |    |

| 1 6 0   | トランジスタ   |    |

| 1 6 2   | トランジスタ   | 20 |

| 1 6 4   | 容量素子     |    |

| 2 5 0   | メモリセル    |    |

| 2 5 1   | メモリセルアレイ |    |

| 2 5 1 a | メモリセルアレイ |    |

| 2 5 1 b | メモリセルアレイ |    |

| 2 5 3   | 周辺回路     |    |

| 2 5 4   | 容量素子     |    |

| 4 0 0   | 基板       |    |

| 4 0 1   | ゲート電極層   |    |

| 4 0 2   | ゲート絶縁層   | 30 |

| 4 0 3   | 酸化物半導体層  |    |

| 4 0 5   | 導電層      |    |

| 4 0 5 a | 導電層      |    |

| 4 0 5 b | 導電層      |    |

| 4 0 7   | 絶縁層      |    |

| 4 0 8   | 層間絶縁層    |    |

| 4 1 7   | 絶縁層      |    |

| 4 1 8   | 開口部      |    |

| 4 2 0   | トランジスタ   |    |

| 4 3 0   | トランジスタ   | 40 |

| 4 3 6   | バッファ層    |    |

| 4 4 0   | トランジスタ   |    |

| 4 5 0   | トランジスタ   |    |

| 4 6 0   | トランジスタ   |    |

| 4 6 5   | 導電層      |    |

| 4 6 5 a | 導電層      |    |

| 4 6 5 b | 導電層      |    |

| 4 7 0   | トランジスタ   |    |

| 4 8 1 a | 埋め込み導電層  |    |

| 4 8 1 b | 埋め込み導電層  | 50 |

|         |               |    |

|---------|---------------|----|

| 4 8 2 a | 酸化物半導体層       |    |

| 4 8 2 b | 酸化物半導体層       |    |

| 4 8 5   | 開口部           |    |

| 4 9 1   | 絶縁層           |    |

| 5 0 2   | 埋め込み導電層       |    |

| 5 0 4   | 埋め込み導電層       |    |

| 5 0 6   | 導電層           |    |

| 5 0 8   | 容量線           |    |

| 5 0 9   | ワード線          |    |

| 5 1 0   | n チャネル型トランジスタ | 10 |

| 5 1 2   | p チャネル型トランジスタ |    |

| 8 0 1   | トランジスタ        |    |

| 8 0 3   | トランジスタ        |    |

| 8 0 4   | トランジスタ        |    |

| 8 0 5   | トランジスタ        |    |

| 8 0 6   | トランジスタ        |    |

| 8 0 7   | X デコーダー       |    |

| 8 0 8   | Y デコーダー       |    |

| 8 1 1   | トランジスタ        |    |

| 8 1 2   | 保持容量          | 20 |

| 8 1 3   | X デコーダー       |    |

| 8 1 4   | Y デコーダー       |    |

| 9 0 1   | R F 回路        |    |

| 9 0 2   | アナログベースバンド回路  |    |

| 9 0 3   | デジタルベースバンド回路  |    |

| 9 0 4   | バッテリー         |    |

| 9 0 5   | 電源回路          |    |

| 9 0 6   | アプリケーションプロセッサ |    |

| 9 0 7   | C P U         |    |

| 9 0 8   | D S P         | 30 |

| 9 0 9   | インターフェイス      |    |

| 9 1 0   | フラッシュメモリ      |    |

| 9 1 1   | ディスプレイコントローラ  |    |

| 9 1 2   | メモリ回路         |    |

| 9 1 3   | ディスプレイ        |    |

| 9 1 4   | 表示部           |    |

| 9 1 5   | ソースドライバ       |    |

| 9 1 6   | ゲートドライバ       |    |

| 9 1 7   | 音声回路          |    |

| 9 1 8   | キーボード         | 40 |

| 9 1 9   | タッチセンサ        |    |

| 9 5 0   | メモリ回路         |    |

| 9 5 1   | メモリコントローラ     |    |

| 9 5 2   | メモリ           |    |

| 9 5 3   | メモリ           |    |

| 9 5 4   | スイッチ          |    |

| 9 5 5   | スイッチ          |    |

| 9 5 6   | ディスプレイコントローラ  |    |

| 9 5 7   | ディスプレイ        |    |

| 1 0 0 1 | バッテリー         | 50 |

|         |              |    |

|---------|--------------|----|

| 1 0 0 2 | 電源回路         |    |

| 1 0 0 3 | マイクロプロセッサ    |    |

| 1 0 0 4 | フラッシュメモリ     |    |

| 1 0 0 5 | 音声回路         |    |

| 1 0 0 6 | キー ボード       |    |

| 1 0 0 7 | メモリ回路        |    |

| 1 0 0 8 | タッチパネル       |    |

| 1 0 0 9 | ディスプレイ       |    |

| 1 0 1 0 | ディスプレイコントローラ |    |

| 5 0 0 1 | 筐体           | 10 |

| 5 0 0 2 | 筐体           |    |

| 5 0 0 3 | 表示部          |    |

| 5 0 0 4 | 表示部          |    |

| 5 0 0 5 | マイクロホン       |    |

| 5 0 0 6 | スピーカー        |    |

| 5 0 0 7 | 操作キー         |    |

| 5 0 0 8 | スタイルス        |    |

| 5 2 0 1 | 筐体           |    |

| 5 2 0 2 | 表示部          |    |

| 5 2 0 3 | 支持台          | 20 |

| 5 4 0 1 | 筐体           |    |

| 5 4 0 2 | 表示部          |    |

| 5 4 0 3 | キー ボード       |    |

| 5 4 0 4 | ポインティングデバイス  |    |

| 5 6 0 1 | 筐体           |    |

| 5 6 0 2 | 筐体           |    |

| 5 6 0 3 | 表示部          |    |

| 5 6 0 4 | 表示部          |    |

| 5 6 0 5 | 接続部          |    |

| 5 6 0 6 | 操作キー         | 30 |

| 5 8 0 1 | 筐体           |    |

| 5 8 0 2 | 表示部          |    |

| 5 8 0 3 | 音声入力部        |    |

| 5 8 0 4 | 音声出力部        |    |

| 5 8 0 5 | 操作キー         |    |

| 5 8 0 6 | 受光部          |    |

【図1】

【図2】

【図3】

【図5】

【図4】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

## フロントページの続き

| (51)Int.Cl. |                   | F I                  |

|-------------|-------------------|----------------------|

| H 01 L      | 21/28 (2006.01)   | H 01 L 29/50 M       |

| H 01 L      | 21/8242 (2006.01) | H 01 L 21/28 3 0 1 B |

| H 01 L      | 27/108 (2006.01)  | H 01 L 27/10 3 2 1   |

| H 01 L      | 27/105 (2006.01)  | H 01 L 27/10 4 4 1   |

| H 01 L      | 27/115 (2017.01)  | H 01 L 27/10 4 3 4   |

| H 01 L      | 27/10 (2006.01)   | H 01 L 27/10 6 7 1 Z |

| H 01 L      | 29/788 (2006.01)  | H 01 L 27/10 6 2 1 Z |

| H 01 L      | 29/792 (2006.01)  | H 01 L 27/10 6 8 1 F |

| C 23 C      | 14/08 (2006.01)   | H 01 L 27/10 4 9 5   |

|             |                   | H 01 L 27/10 6 8 1 A |

|             |                   | H 01 L 27/10 6 8 1 B |

|             |                   | H 01 L 29/78 3 7 1   |

|             |                   | H 01 L 27/10 4 6 1   |

|             |                   | H 01 L 27/10 4 8 1   |

|             |                   | H 01 L 27/10 6 5 1   |

|             |                   | C 23 C 14/08 K       |

(72)発明者 手塚 祐朗

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 本堂 英

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

(72)発明者 斎藤 利彦

神奈川県厚木市長谷398番地 株式会社半導体エネルギー研究所内

審査官 竹口 泰裕

(56)参考文献 特開2010-232651(JP, A)

特開2011-124557(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21/336、29/786