(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4497636号

(P4497636)

(45) 発行日 平成22年7月7日(2010.7.7)

(24) 登録日 平成22年4月23日(2010.4.23)

|                      |                |

|----------------------|----------------|

| (51) Int.Cl.         | F 1            |

| HO4N 5/228 (2006.01) | HO4N 5/228 Z   |

| GO6T 1/20 (2006.01)  | GO6T 1/20 B    |

| GO6T 1/60 (2006.01)  | GO6T 1/60 450E |

| GO6T 3/00 (2006.01)  | GO6T 3/00 400Z |

| HO4N 1/19 (2006.01)  | HO4N 1/04 103A |

請求項の数 4 (全 15 頁) 最終頁に続く

|              |                               |                                                      |

|--------------|-------------------------------|------------------------------------------------------|

| (21) 出願番号    | 特願2000-70728 (P2000-70728)    | (73) 特許権者 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成12年3月14日 (2000.3.14)        | (74) 代理人 100076428<br>弁理士 大塚 康徳                      |

| (65) 公開番号    | 特開2000-312308 (P2000-312308A) | (74) 代理人 100112508<br>弁理士 高柳 司郎                      |

| (43) 公開日     | 平成12年11月7日 (2000.11.7)        | (74) 代理人 100116894<br>弁理士 木村 秀二                      |

| 審査請求日        | 平成19年3月14日 (2007.3.14)        | (74) 代理人 100115071<br>弁理士 大塚 康弘                      |

| (31) 優先権主張番号 | 09/267781                     |                                                      |

| (32) 優先日     | 平成11年3月15日 (1999.3.15)        |                                                      |

| (33) 優先権主張国  | 米国 (US)                       |                                                      |

最終頁に続く

(54) 【発明の名称】 画像処理装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数のセグメントに分割され、各セグメントの複数の画素に発生した画素データを出力するセンサアレイと、各セグメントから出力された画素データのうち、セグメント間の境界における重複領域の画素データを複製する複製手段と、各セグメントに対応して設けられ、対応するセグメントから出力され前記複製手段で複製された画素データを含む画素データを格納する複数のパイプラインとを有するセンサチップと、

前記複数のパイプラインに格納された各セグメントの画素データをデジタル画素データに変換するA/D変換器と、

前記複製手段で複製され前記A/D変換器で変換されたデジタル画素データに基づいて前記セグメント間における画素データの不連続を補正するプロセッサと、

前記プロセッサで補正された各セグメントに対応する画像データを再結合して全体画像を形成する再結合手段と、

を有することを特徴とする画像処理装置。

## 【請求項 2】

複数のセグメントに分割され、各セグメントの複数の画素に発生した画素データを出力するセンサアレイと、各セグメントに対応して設けられ、対応するセグメントから出力された画素データのうち、セグメント間の境界における重複領域以外の画素データを格納する複数のパイプラインとを有するセンサチップと、

前記セグメント間の境界における重複領域の画素データを格納する中間バッファと、

10

20

前記複数のパイプライン及び前記中間バッファに格納された画素データをデジタル画素データに変換するA/D変換器と、

前記中間バッファに格納され前記A/D変換器で変換されたデジタル画素データに基づいて前記セグメント間ににおける画素データの不連続を補正するプロセッサと、

前記プロセッサで補正された各セグメントに対応する画像データを再結合して全体画像を形成する再結合手段と、

を有することを特徴とする画像処理装置。

【請求項3】

前記中間バッファは、前記センサアレイと別のチップで構成されることを特徴とする請求項2記載の画像処理装置。

10

【請求項4】

複数のセグメントに分割され、各セグメントの複数の画素に発生した画素データを出力するセンサアレイと、各セグメントに対応して設けられ、対応するセグメントから出力された画素データを格納する複数のパイプラインとを有するセンサチップと、

前記複数のパイプラインに格納された画素データをデジタル画素データに変換するA/D変換器と、

前記A/D変換器で変換された各セグメントに対応するデジタル画素データを入力するとともに、セグメント間の境界における重複領域の画素データに対応する重複データを相互に通信することによって前記セグメント間ににおける画素データの不連続を補正する複数のプロセッサと、

20

前記複数のプロセッサで補正された各セグメントに対応する画像データを再結合して全体画像を形成する再結合手段と、

を有することを特徴とする画像処理装置。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】

本発明は、複数のセグメントに分割され、セグメントごとに複数の出力パイプラインのうち1つが対応している、電荷結合素子(CCD)などの電子イメージングセンサ、当該センサを備えた画像処理装置に関する。

【0002】

30

【従来の技術】

最近、CCDのような電子イメージングセンサの製造プロセスが進歩を遂げたため、電子イメージングセンサは二次元アレイを成して配列された数百万の画素を有する構成をとるようになっている。しかしながら、画素数が多いことから、電子イメージングセンサからデータをシフトするだけでも、その処理に長い時間を要するという不都合が見られるようになった。

【0003】

シフトアウトの時間の長さという問題に対処するため、いくつかの方法が提案されている。そのような方法の1つによれば、電子イメージングセンサを複数の異なる分離した領域、例えば、左半分と右半分とに分割する。電子イメージングセンサの各セグメントは独自の出力パイプラインを具備している。このような構成をとれば、セグメントの数に比例してシフトアウト時間を短縮することが可能である。例えば、電子イメージングセンサを互いに分離した左半分と、右半分とに分割した場合、シフトアウト時間を二分の一に短縮することができる。

40

【0004】

【発明が解決しようとする課題】

分割形電子イメージングセンサを使用する際に起こる問題の1つは、それぞれのセグメントの境界に画像データの不連続が形成されてしまうことである。各セグメントからシフトしたデータが如何なる処理の前にも直ちに再結合されるならば、プロセッサが画像全体の画像データを利用できるので、そのような不連続の影響を最小限に抑えることができる。

50

しかしながら、現在では出力パイプラインごとに別個のプロセッサを設けることが一般的になっている。それらのプロセッサは、互いに独立し、その出力パイプラインに対応する電子イメージングセンサのセグメントのデータに対して動作する。従って、各プロセッサにより個別に処理された画像データを再結合して画像を形成すると、センサセグメントにおける不連続はそのまま現れてしまう。

【0005】

本発明の目的は、個々のセグメント間の不連続を含む重複領域の画像データを複製し、且つ複製された画像データを重複領域に近い電子イメージングセンサの各セグメントの出力パイプラインに供給することにより分割形電子イメージングセンサの各セグメントでの不連続を減少させることである。

10

【0006】

【課題を解決するための手段】

本発明の画像処理装置は、複数のセグメントに分割され、各セグメントの複数の画素に発生した画素データを出力するセンサアレイと、各セグメントから出力された画素データのうち、セグメント間の境界における重複領域の画素データを複製する複製手段と、各セグメントに対応して設けられ、対応するセグメントから出力された画素データを複製する複製手段で複製された画素データを含む画素データを格納する複数のパイプラインとを有するセンサチップと、前記複数のパイプラインに格納された各セグメントの画素データをデジタル画素データに変換するA/D変換器と、前記複製手段で複製された前記A/D変換器で変換されたデジタル画素データに基づいて前記セグメント間における画素データの不連続を補正するプロセッサと、前記プロセッサで補正された各セグメントに対応する画像データを再結合して全体画像を形成する再結合手段と、を有することを特徴とする。

20

【0007】

また、本発明の画像処理装置は、複数のセグメントに分割され、各セグメントの複数の画素に発生した画素データを出力するセンサアレイと、各セグメントに対応して設けられ、対応するセグメントから出力された画素データのうち、セグメント間の境界における重複領域以外の画素データを格納する複数のパイプラインとを有するセンサチップと、前記セグメント間の境界における重複領域の画素データを格納する中間バッファと、前記複数のパイプライン及び前記中間バッファに格納された画素データをデジタル画素データに変換するA/D変換器と、前記中間バッファに格納された前記A/D変換器で変換されたデジタル画素データに基づいて前記セグメント間における画素データの不連続を補正するプロセッサと、前記プロセッサで補正された各セグメントに対応する画像データを再結合して全体画像を形成する再結合手段と、を有することを特徴とする。

30

【0008】

更に、本発明の画像処理装置は、複数のセグメントに分割され、各セグメントの複数の画素に発生した画素データを出力するセンサアレイと、各セグメントに対応して設けられ、対応するセグメントから出力された画素データを格納する複数のパイプラインとを有するセンサチップと、前記複数のパイプラインに格納された画素データをデジタル画素データに変換するA/D変換器と、前記A/D変換器で変換された各セグメントに対応するデジタル画素データを入力するとともに、セグメント間の境界における重複領域の画素データに対応する重複データを相互に通信することによって前記セグメント間における画素データの不連続を補正する複数のプロセッサと、前記複数のプロセッサで補正された各セグメントに対応する画像データを再結合して全体画像を形成する再結合手段と、を有することを特徴とする。

40

【0012】

【発明の実施の形態】

以下、図面を参照しながら本発明に係る実施の形態を詳細に説明する。

【0013】

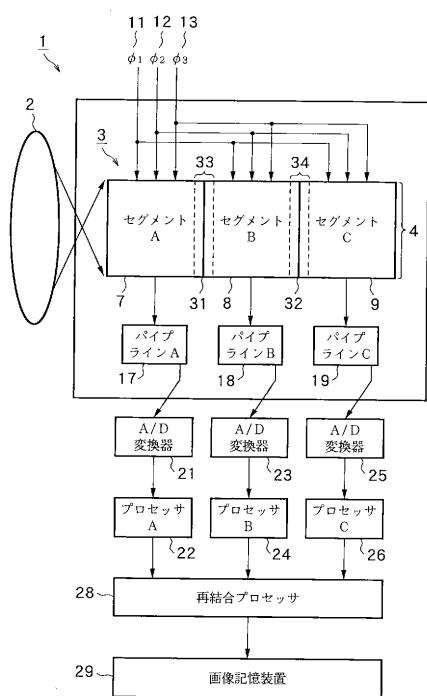

図1は、実施形態における電子イメージングセンサを利用可能な画像記憶装置を示す図である。図1には、電化結合素子(CCD)チップなどの電子イメージングセンサチップ1

50

と、そのセンサチップ1のマスクで覆われていない領域4にあるセンサアレイ3に画像の入射光を集束させるレンズ系2とが示されている。センサアレイ3は複数の互いに分離されたセンサセグメントを含む。図1に示すように、それらのセグメントにはセグメントA7と、セグメントB8と、セグメントC9とがある。

【0014】

各センサセグメントは、複数行の感光セルを含むのが好ましい。各々のセルは、センサチップ1によって生成される画像データの1つの画素に対応しているのが好ましい。それらのセルの1つに光が入射されると、その光は対応する画素に対してセル内に電荷又は電圧を発生する。

【0015】

1つの画像に相当する所定時間に渡り光がこれらの電荷又は電圧を発生させると、電荷又は電圧がセンサアレイ3上に集束された画像の画像データを提供するように各センサからシフトアウトされる。その電荷又は電圧は各セグメントから行ごとにシフトアウトされるのが好ましい。更に、センサセグメントは物理的に又は電子的に遮断されるのが好ましく、これにより、シフト動作の間に電荷又は電圧は入射光により生成されなくなる。この遮断により、電荷又は電圧がセンサセグメントからシフトアウトされるときに入射光によって生成される電荷に起因して起こりうる画像の汚れはなくなるか、又は減少する傾向にある。

【0016】

当該技術分野における公知の技法を使用して各センサセグメントから電荷又は電圧をシフトアウトするために、位相クロック1(11)、2(12)及び3(13)が提供されるのが好ましい。位相クロックの各々は、1/3デューティサイクルを有しており、且つその他のクロックからずれているのが好ましい。これらのクロックを使用してセンサセグメントの中のセルを順次クロッキングすることにより、電荷又は電圧がそのセグメントからシフトアウトされる。電荷又は電圧は、センサセグメントの各々に対応するパイプラインへ一度に1行ずつシフトアウトされるのが好ましい。即ち、複数行分の電荷又は電圧がセグメントA7からパイプラインA17へ、セグメントB8からパイプラインB18へ、そして、セグメントC9からパイプラインC19へ1行ずつシフトされる。

【0017】

1行分の電荷又は電圧がパイプラインへシフトされると、その行の電荷又は電圧は、好ましくは電荷又は電圧をデジタル画素データに変換するA/D変換器を介してイメージプロセッサへ順次出力される。イメージプロセッサは画素データを処理して、例えば白バランス修正を実行する。

【0018】

このように、電荷又は電圧はパイプラインA17からA/D変換器21へ順次出力されてデジタル画素データに変換され、そのデータはプロセッサA22へ送られて処理される。パイプラインB18からA/D変換器23へ順次出力された電荷又は電圧はデジタル画素データに変換され、そのデータはプロセッサB24へ送られて処理される。同様に、パイプラインC19からA/D変換器25へ順次出力された電荷又は電圧はデジタル画素データに変換され、そのデータはプロセッサC26へ送られて処理される。

【0019】

次に、ほかの行の電荷又は電圧がセンサセグメントからパイプラインへシフトされ、全ての行のセンサセグメントについて画素データが生成されるまで、このプロセスが繰り返される。そして、再結合プロセッサ28がプロセッサA22、プロセッサB24及びプロセッサC26からの画素データを結合する。或いは、再結合プロセッサ28は、プロセッサA22、プロセッサB24及びプロセッサC26により生成されたままの状態で画素データを処理する。再結合プロセッサ28からの画像データは画像記憶装置29に格納されるのが好ましい。

【0020】

画像全体が処理された後、センサアレイ3の遮断を(物理的に又は電子的に)解除し、別

10

20

30

40

50

の画像を処理するのが好ましい。

【0021】

実施形態によれば、センサセグメントの境界を含む重複領域について複製画素値が生成される。それぞれの重複領域は、対応する境界の両側に、画素数個分の幅に相当するセル、例えば、画素6つ分又は8つ分のセルを含む。

【0022】

図1において、セグメントの境界はセグメントA7とセグメントB8との境界31と、セグメントB8とセグメントC9との境界32である。これに対応する重複領域は、それぞれ、重複領域33と、重複領域34である。

【0023】

プロセッサA22、B24及びC26は、センサセグメント間の不連続を複製画素値を使用して補正する。例えば、プロセッサA22、B24及びC26がそれぞれのセンサセグメントの白バランスを修正する場合、プロセッサA22、B24及びC26は重複領域の複製画素値を白バランス計算に利用する。その結果、センサセグメントの画像データ間の不連続を最小限に抑えるような、より好ましい白バランスが得られる。

【0024】

以下、複製画素値を生成するための本発明に係る3つの実施形態を説明する。以下の3つの実施形態について詳細に説明するが、本発明はそれらの実施形態にのみ限定されるものではない。

【0025】

[第1の実施形態]

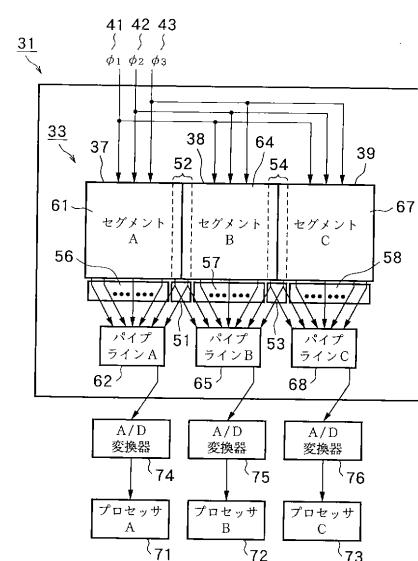

図2は、本発明に係る第1の実施形態における電子イメージングセンサを示す図である。

【0026】

簡単に言えば、第1の実施形態によれば、電子イメージングセンサは、複数の互いに分離したセグメントに分割されたセンサアレイと、各々がセンサアレイの複数のセグメントの各々に対応する複数の出力パイプラインと、セグメント間の境界ごとに重複領域の画像データを複製する回路とを含む。この回路は、重複領域の画素ごとに複数の出力を得る、電荷又は電圧複製回路を含む。その複製回路は複数の出力のそれぞれを、重複領域に境界を有する出力パイplineの各々に供給する。

【0027】

更に詳細に説明すると、図2は、図中の符号37、38及び39で指示される複数の互いに分離したセンサセグメントA、B及びCを含むセンサアレイ33を有する電子イメージングセンサチップ31を示す。各々のセンサセグメントは、先に図1を参照して説明したように、位相クロック1(41)、2(42)及び3(43)に従ってセンサセグメント上に集束された画像について複数行の電荷又は電圧を出力する。

【0028】

本発明の第1の実施形態によれば、重複領域の電荷又は電圧を複製する回路によって重複領域の画像データが複製される。この回路はセンサチップ31の上に形成されているのが好ましい。

【0029】

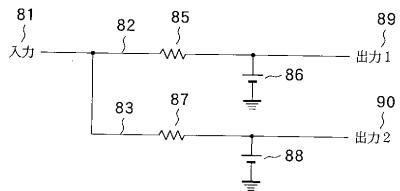

図2において、回路51は重複領域52の電荷又は電圧を複製し、回路53は重複領域54の電荷又は電圧を複製する。回路51及び53の各々について実施可能な構造の1つを、図3Aを参照して後述する。

【0030】

重複領域以外では電圧又は電荷は複製されないので、回路56、57及び58は、センサセグメントの各々について、重複領域以外の重複していない領域からの電荷又は電圧を複製せずにそれぞれ対応するパイplineに供給する。即ち、回路56は重複していない領域61からの電荷又は電圧をパイpline A62に供給し、回路57は重複していない領域64からの電荷又は電圧をパイpline B65に供給し、回路58は重複していない領域67からの電荷又は電圧をパイpline C68に供給する。回路56、57及び58の

10

20

30

40

50

各々について実施可能な構造の 1 つを、図 3 B を参照して後述する。

【 0 0 3 1 】

パイプラインの各々は、プロセッサ A 7 1、プロセッサ B 7 2 及びプロセッサ C 7 3 のそれぞれ対応する 1 つに接続されている。パイプライン A 6 2 は A / D 変換器 7 4 を介してプロセッサ A 7 1 に接続され、パイプライン B 6 5 は A / D 変換器 7 5 を介してプロセッサ B 7 2 に接続され、パイプライン C 6 8 は A / D 変換器 7 6 を介してプロセッサ C 7 3 に接続されているのが好ましい。

【 0 0 3 2 】

図 3 A は、センサセグメントの重複領域のための電荷複製回路の概略図である。図 3 A に示すように、重複領域から電荷 8 1 が入力される。電荷 8 1 は分岐路 8 2 及び 8 3 を共に通過する。分岐路 8 2 には抵抗器 8 5 及びコンデンサ 8 6 が設けられ、分岐路 8 3 には抵抗器 8 7 及びコンデンサ 8 8 が設けられている。これらの抵抗器とコンデンサは、入力電荷 8 1 から複製出力電荷 8 9 及び 9 0 を発生するように均衡されているのが好ましい。抵抗器 - コンデンサ回路網によって発生する減衰を補正するように、必要な増幅を行うための補正回路（図示せず）が設けられている。

10

【 0 0 3 3 】

図 3 B は、センサセグメントの重複していない領域のための電荷回路の概略図である。この回路は、重複していない領域からの入力電荷 9 1 を複製しない。従って、図 3 B の回路は抵抗器 9 3 及びコンデンサ 9 4 を含む 1 つの分岐路 9 2 を有し、それらの抵抗器 9 3 及びコンデンサ 9 4 は入力電荷 9 1 から出力電荷 9 5 を発生するように動作する。

20

【 0 0 3 4 】

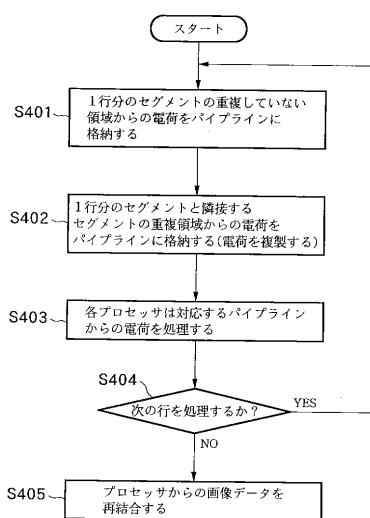

図 4 は、センサアレイ上に形成された画像の電荷から画像データの生成を説明するためのフローチャートである。この場合、画像データは、第 1 の実施形態によるセンサアレイの 2 つの互いに分離したセグメントの境界における重複領域のために複製される。

20

【 0 0 3 5 】

簡単に言えば、電子イメージングセンサは、複数の互いに分離したセグメントを伴うセンサアレイを有する。複数のセグメントは、境界により分離された第 1 のセグメントと、第 2 のセグメントとを少なくとも含む。第 1 のセグメントの重複していない領域からの電荷又は電圧はパイプラインに格納される。第 1 のセグメントと第 2 のセグメントの重複領域からの電荷又は電圧もパイプラインに格納される。パイプラインに格納された電荷又は電圧は、その後、プロセッサに供給される。

30

【 0 0 3 6 】

更に詳細に説明すると、ステップ S 4 0 1 では、1 行分のセンサセグメントの重複していない領域からの電荷又は電圧をパイプラインに格納する。即ち、重複していない領域 6 1 からの電荷又は電圧はパイプライン A 6 2 に格納され、重複していない領域 6 4 からの電荷又は電圧はパイプライン B 6 5 に格納され、重複していない領域 6 7 からの電荷又は電圧はパイプライン C 6 8 に格納される。

40

【 0 0 3 7 】

ステップ S 4 0 2 では、ある 1 つの行の 1 つのセグメントと隣接するセグメントの重複領域からの電荷又は電圧を複製回路により複製し、複製された電荷又は電圧をそれらのセグメントに対応するパイプラインに格納する。即ち、重複領域 5 2 からの電荷又は電圧は回路 5 1 により複製されて、パイプライン A 6 2 及び B 6 5 に格納され、重複領域 5 4 からの電荷又は電圧は回路 5 3 により複製されて、パイプライン B 6 5 及び C 6 8 に格納される。

【 0 0 3 8 】

ステップ S 4 0 3 では、パイプラインからの電荷又は電圧をそれぞれ対応するプロセッサにより処理する。即ち、パイプライン A 6 2 からの電荷又は電圧は、A / D 変換器 7 4 によりデジタル画素データに変換された後、プロセッサ A 7 1 により処理される。パイプライン B 6 5 からの電荷又は電圧は A / D 変換器 7 5 によりデジタル画素データに変換された後、プロセッサ B 7 2 により処理され、パイプライン C 6 8 からの電荷又は電圧は A /

50

D変換器76によりデジタル画素データに変換された後、プロセッサC73により処理される。

【0039】

ステップS404では、画像の処理を完了するために、処理される必要がある行があれば、処理はステップS401に戻る。そうでなければ、処理はステップS405へ進み、プロセッサからの画像データを再結合し、センサアレイ33上に集束された画像に相当する全体画像を形成する。

【0040】

上述したように、1つのセグメントに対応するプロセッサは、それぞれ隣接する1つ又は複数のセグメントの重複領域における画素の画像データを受信する。その結果、各々のセグメントに対応するプロセッサはセグメント間の画像の不連続を補正することができる。例えば、カラー画像の赤、緑及び青の色成分を調整するための白バランス修正を各々のプロセッサ71、72及び73で実行して、全体としての白バランスをより容易に実現することができる。

【0041】

[第2の実施形態]

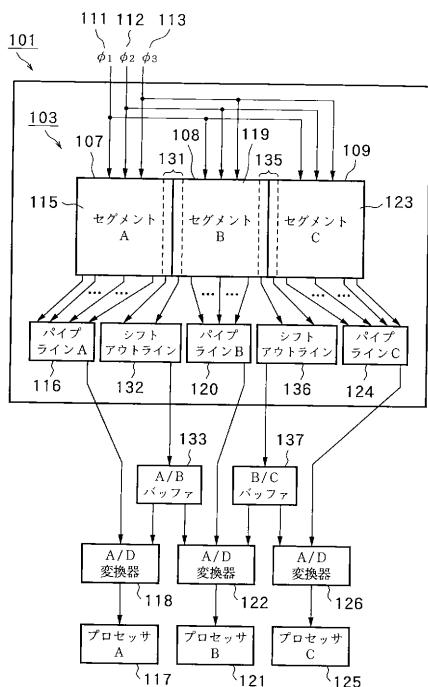

図5は、本発明に係る第2の実施形態における電子イメージングセンサを示す図である。

【0042】

簡単に言うと、第2の実施形態によれば、電子イメージングセンサは、複数の互いに分離したセグメントに分割されたセンサアレイと、各々がセンサアレイの複数のセグメントの各々に対応する複数の出力パイプラインと、対応する複数のプロセッサとを含む。各プロセッサは、出力パイプラインの対応する1つに結合している。電子イメージングセンサは、重複領域の画素の画素値を中間バッファへ出力する出力パイプライン又はシフトアウトラインを更に含む。中間バッファは、重複領域にセグメントの境界を有する各プロセッサに複製画素値を供給する。

【0043】

更に詳細に説明すると、図5は、センサセグメントA107、センサセグメントB108及びセンサセグメントC109を含むセンサアレイ103を有する電子イメージングセンサチップ101を示す。これらのセンサセグメントの各々は、先に図1を参照して説明したように、セグメント上に集束された画像に対応する複数行分の電荷又は電圧を位相クロック1(111)、2(112)及び3(113)に従って出力する。

【0044】

本発明の第2の実施形態によれば、重複領域の画像データは、重複領域の電荷又は電圧をシフトアウトラインに格納し、次に中間バッファに格納し、中間バッファが電荷を重複領域のセグメントに対応するプロセッサに供給することにより複製される。シフトアウトラインはセンサチップ101上に設けられ、中間バッファはセンサチップ101の外部に設けられるのが好ましい。

【0045】

図5において、重複していない領域115からの電荷又は電圧はパイプラインA116に格納され、このパイプラインA116はそれらの電荷又は電圧をA/D変換器118を介してプロセッサA117に供給するのが好ましい。同様に、重複していない領域119からの電荷又は電圧はパイプラインB120に格納され、パイプラインB120はそれらの電荷又は電圧をA/D変換器122を介してプロセッサB121に供給するのが好ましく、また重複していない領域123からの電荷又は電圧はパイプラインC124に格納され、パイプラインC124はそれらの電荷又は電圧をA/D変換器126を介してプロセッサC125に供給するのが好ましい。

【0046】

重複領域131からの電荷又は電圧はシフトアウトライン132へ送られ、中間のA/Bバッファ133に格納される。このバッファ133は、それらの電荷又は電圧を好ましくはA/D変換器118とA/D変換器122とをそれぞれ介してプロセッサA117及び

10

20

30

40

50

プロセッサ B 1 2 1 に供給する。同様に、重複領域 1 3 5 からの電荷又は電圧はシフトアウトライン 1 3 6 へ送られ、中間の B / C バッファ 1 3 7 に格納される。このバッファ 1 3 7 は、それらの電荷又は電圧を好ましくは A / D 変換器 1 2 2 と A / D 変換器 1 2 6 とをそれぞれ介してプロセッサ B 1 2 1 及びプロセッサ C 1 2 5 に供給する。

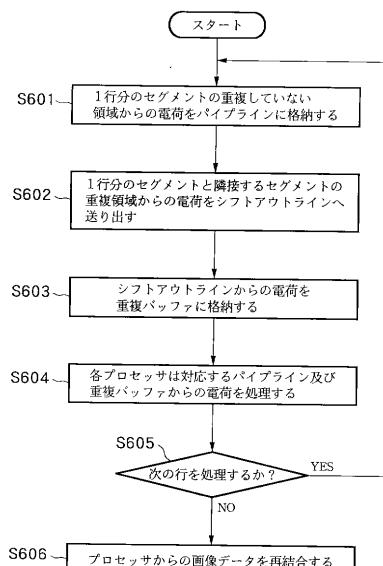

【 0 0 4 7 】

図 6 は、センサアレイ上に形成された画像の電荷から画像データの生成を説明するためのフローチャートである。この場合、画像データは、第 2 の実施形態によるセンサアレイの 2 つの互いに分離したセグメントの境界における重複領域のために複製される。

【 0 0 4 8 】

簡単に言えば、電子イメージングセンサは、複数の分離したセグメントを伴うセンサアレイを有する。複数のセグメントは少なくとも、境界により分離された第 1 のセグメントと、第 2 のセグメントとを含む。第 1 のセグメントの重複していない領域からの電荷又は電圧はパイプラインに格納される。第 1 のセグメントと第 2 のセグメントの重複領域からの電荷又は電圧は、シフトアウトラインへ送られる。シフトアウトラインからの電荷又は電圧は中間バッファに格納される。電荷又は電圧はパイプライン及び中間バッファからプロセッサに供給される。

【 0 0 4 9 】

更に詳細に説明すると、ステップ S 6 0 1 では、ある 1 行のセンサセグメントの重複していない領域からの電荷又は電圧をパイプラインに格納する。即ち、重複していない領域 1 1 5 からの電荷又は電圧はパイプライン A 1 1 6 に格納され、重複していない領域 1 1 9 からの電荷又は電圧はパイプライン B 1 2 0 に格納され、重複していない領域 1 2 3 からの電荷又は電圧はパイプライン C 1 2 4 に格納される。

【 0 0 5 0 】

ステップ S 6 0 2 では、ある 1 行の 1 つのセグメントと、隣接するセグメントの重複領域からの電荷又は電圧をシフトアウトラインへ送り出す。即ち、重複領域 1 3 1 からの電荷又は電圧はシフトアウトライン 1 3 2 へ送り出され、重複領域 1 3 5 からの電荷又は電圧はシフトアウトライン 1 3 6 へ送り出される。

【 0 0 5 1 】

ステップ S 6 0 3 では、シフトアウトラインからの電荷又は電圧を中間バッファに格納する。即ち、中間の A / B バッファ 1 3 3 はシフトアウトライン 1 3 2 からの電荷又は電圧を格納し、中間の B / C バッファ 1 3 7 はシフトアウトライン 1 3 6 からの電荷又は電圧を格納する。

【 0 0 5 2 】

ステップ S 6 0 4 では、パイプライン及び中間バッファからの電荷又は電圧を好ましくは A / D 変換器を介してそれぞれ対応するプロセッサへ送り、処理する。即ち、パイプライン A 1 1 6 及び中間の A / B バッファ 1 3 3 からの電荷又は電圧は A / D 変換器 1 1 8 を介してプロセッサ A 1 1 7 へ送られ、処理されるのが好ましく、パイプライン B 1 2 0 、中間の A / B バッファ 1 3 3 及び中間の B / C バッファ 1 3 7 からの電荷又は電圧は A / D 変換器 1 2 2 を介してプロセッサ B 1 2 1 へ送られ、処理されるのが好ましく、パイプライン C 1 2 4 及び中間の B / C バッファ 1 3 7 からの電荷又は電圧は A / D 変換器 1 2 6 を介してプロセッサ C 1 2 5 へ送られ、処理されるのが好ましい。このように、第 2 の実施形態では、ステップ S 6 0 4 において、重複領域のデータを対応する中間バッファから重複領域に境界を有するセグメントに対応するプロセッサへ送信することにより、データを複製する。

【 0 0 5 3 】

ステップ S 6 0 5 では、画像の処理を完了するために、処理される必要がある行があれば、処理はステップ S 6 0 1 に戻る。そうでなければ、処理はステップ S 6 0 6 へ進み、プロセッサからの画像データを再結合し、センサアレイ 1 0 3 上に集束された画像に相当する全体画像を形成する。

【 0 0 5 4 】

10

20

30

40

50

上述したように、1つのセグメントに対応する各々のプロセッサは、隣接する1つ又は複数のセグメントとの重複領域における画素の画像データを受信する。その結果、各々のセグメントに対応するプロセッサはセグメント間の画像の不連続を補正することができる。

【0055】

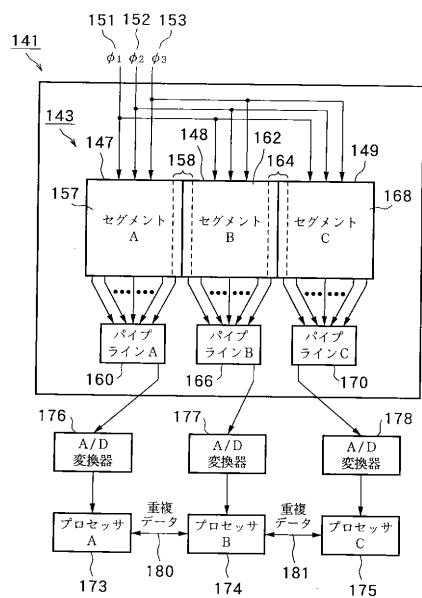

【第3の実施形態】

図7は、本発明に係る第3の実施形態における電子イメージングセンサを示す図である。

【0056】

簡単に言うと、第3の実施形態によれば、電子イメージングセンサは、複数の互いに分離したセグメントに分割されたセンサアレイと、各々がセンサアレイの複数のセグメントの各々に対応する複数の出力パイプラインと、対応する複数のプロセッサとを含む。各プロセッサは、出力パイプラインのうち対応する1つのパイプラインに結合している。重複領域に境界を有するプロセッサ間には通信リンクが設けられ、プロセッサ間で通信リンクを介して複製画素が通信される。

【0057】

更に詳細に説明すると、図7は、センサセグメントA147、センサセグメントB148及びセンサセグメントC149を含むセンサアレイ143を有する電子イメージングセンサチップ141を示す。これらのセンサセグメントの各々は、先に図1を参照して説明したように、位相クロック1(151)、2(152)及び3(153)に従ってセンサセグメント上に集束された画像に対応する複数行分の電荷又は電圧を出力する。

【0058】

本発明の第3の実施形態によれば、重複領域の画像データは、それぞれの画像領域に対応するプロセッサ間で通信リンクを介して画像データを通信することにより複製される。プロセッサと通信回線はチップの外部に設けられるのが好ましい。

【0059】

図7では、セグメントA147の重複していない領域157と、重複領域158の一部とを含む、セグメントA147からの電荷又は電圧はパイプラインA160に格納される。同様に、セグメントB148の重複していない領域162と、重複領域158及び164の一部とを含む、セグメントB148からの電荷又は電圧はパイプラインB166に格納され、セグメントC149の重複していない領域168と、重複領域164の一部とを含む、セグメントC149からの電荷又は電圧はパイプラインC170に格納される。

【0060】

パイプラインの各々は、好ましくはA/D変換器176、177及び178を介して電荷又は電圧を対応するプロセッサA173、B174及びC175に供給する。これらのプロセッサは、対応するセンサセグメントが共有している重複領域の重複画素データを共用するように通信回線180及び181を介して通信する。即ち、好適な実施形態では、プロセッサA173及びB174は重複領域158の画素データを通信回線180を介して通信し、プロセッサB174及びC175は重複領域164の画素データを通信回線181を介して通信する。

【0061】

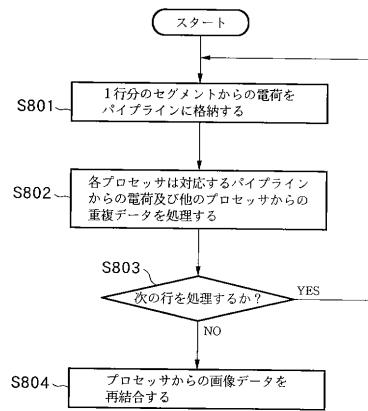

図8は、センサアレイ上に形成された画像の電荷から画像データの生成を説明するためのフローチャートである。この場合、画像データは、第3の実施形態によるセンサアレイの2つの互いに分離したセグメントの境界における重複領域のために複製される。

【0062】

簡単に言えば、電子イメージングセンサは、複数の分離したセグメントを伴うセンサアレイを有する。複数のセグメントは少なくとも、境界により分離された第1のセグメントと、第2のセグメントとを含む。第1のセグメントからの電荷又は電圧はパイプラインに格納される。それらの電荷又は電圧は、パイプラインから第1のセグメントの画素データを処理する第1のプロセッサに供給される。重複領域の画素データは第1のプロセッサと第2のプロセッサとの間で通信され、第2のプロセッサは第2のセグメントの画素データを処理する。

10

20

30

40

50

## 【0063】

更に詳細に説明すると、ステップS801では、1行分のセンサセグメントからの電荷又は電圧をパイプラインに格納する。即ち、センサセグメントA147からの電荷又は電圧はパイプラインA160に格納され、センサセグメントB148からの電荷又は電圧はパイプラインB166に格納され、センサセグメントC149からの電荷又は電圧はパイプラインC170に格納される。

## 【0064】

ステップS802では、パイプラインからの電荷又は電圧を、隣接するセンサセグメントに対応するプロセッサから供給される重複データと共に、プロセッサのうち対応するプロセッサにより処理する。プロセッサA173は、好ましくはA/D変換器176を介して受信されたパイプラインA160からの電荷又は電圧を、セグメントB148の重複領域158の一部に対応するプロセッサB174からの重複データと共に処理する。プロセッサB174は、好ましくはA/D変換器177を介して受信されたパイプラインB166からの電荷又は電圧を、セグメントA147の重複領域158の一部に対応するプロセッサA173からの重複データ及びセグメントC149の重複領域164の一部に対応するプロセッサC175からの重複データと共に処理する。プロセッサC175は、好ましくはA/D変換器178を介して受信されたパイプラインC170からの電荷又は電圧を、セグメントB148の重複領域164の一部に対応するプロセッサB174からの重複データと共に処理する。重複データは通信回線180及び181を介してプロセッサ間で通信される。

10

20

## 【0065】

ステップS803では、画像の処理を完了するために、処理される必要がある行があれば、処理はステップS801に戻る。そうでなければ、処理はステップS804へ進み、プロセッサからの画像データを再結合し、センサアレイ143上に集束された画像に相当する全体画像を形成する。

## 【0066】

上述したように、1つのセグメントに対応する各々のプロセッサは、隣接する1つ又は複数のセグメントとの重複領域における画素の画像データを受信する。その結果、各々のセグメントに対応するプロセッサはセグメント間の画像の不連続を補正することができる。

30

## 【0067】

A/D変換器を介してデータを受信する代わりに、プロセッサは直接電荷又は電圧を処理することもできる。例えば、各プロセッサは電荷又は電圧に関して画像処理を行う埋め込みA/D変換器又は他の回路を含むことができる。その場合、図1、図2、図5及び図7に示すA/D変換器を省略しても良い。

## 【0068】

上述した各実施形態の特徴の何れかを組み合わせることは可能である。更に、電子イメージングセンサチップは、先に説明したセグメント数の3つよりも多い又は少ない数のセグメントを有するセンサアレイを含んでいても良く、それらのセグメントは縦、横、格子状などのどのような配列で配置されていても良い。

40

## 【0069】

尚、本発明は複数の機器（例えば、ホストコンピュータ、インタフェイス機器、リーダ、プリンタなど）から構成されるシステムに適用しても、一つの機器からなる装置（例えば、複写機、ファクシミリ装置など）に適用してもよい。

## 【0070】

また、本発明の目的は前述した実施形態の機能を実現するソフトウェアのプログラムコードを記録した記憶媒体を、システム或いは装置に供給し、そのシステム或いは装置のコンピュータ（CPU若しくはMPU）が記憶媒体に格納されたプログラムコードを読み出し実行することによっても、達成されることは言うまでもない。

## 【0071】

50

この場合、記憶媒体から読出されたプログラムコード自体が前述した実施形態の機能を実現することになり、そのプログラムコードを記憶した記憶媒体は本発明を構成することになる。

【0072】

プログラムコードを供給するための記憶媒体としては、例えばフロッピーディスク、ハードディスク、光ディスク、光磁気ディスク、CD-ROM、CD-R、磁気テープ、不揮発性のメモリカード、ROMなどを用いることができる。

【0073】

また、コンピュータが読出したプログラムコードを実行することにより、前述した実施形態の機能が実現されるだけでなく、そのプログラムコードの指示に基づき、コンピュータ上で稼働しているOS（オペレーティングシステム）などが実際の処理の一部又は全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

【0074】

更に、記憶媒体から読出されたプログラムコードが、コンピュータに挿入された機能拡張ボードやコンピュータに接続された機能拡張ユニットに備わるメモリに書込まれた後、そのプログラムコードの指示に基づき、その機能拡張ボードや機能拡張ユニットに備わるCPUなどが実際の処理の一部又は全部を行い、その処理によって前述した実施形態の機能が実現される場合も含まれることは言うまでもない。

【図面の簡単な説明】

【図1】実施形態における電子イメージングセンサを利用可能な画像記憶装置を示す図である。

【図2】本発明に係る第1の実施形態における電子イメージングセンサを示す図である。

【図3A】センサセグメントの重複領域のための電荷複製回路の概略図である。

【図3B】センサセグメントの重複していない領域のための電荷回路の概略図である。

【図4】本発明の第1の実施形態によるセンサアレイの2つの互いに分離したセグメント間の境界で重複領域のために複製される、センサアレイ上に形成された画像の画像データを生成するフローチャートである。

【図5】重複領域の画像データを中間バッファに格納する、本発明の電子イメージングセンサの第2の実施形態を示す図である。

【図6】本発明の第2の実施形態によるセンサアレイの2つの互いに分離したセグメント間の境界で重複領域のために複製される、センサアレイ上に形成された画像の画像データを生成するフローチャートである。

【図7】重複領域の画素データをプロセッサ間でオフチップ通信する、本発明の電子イメージングセンサの第3の実施形態を示す図である。

【図8】本発明の第3の実施形態によるセンサアレイの2つの互いに分離したセグメント間の境界で重複領域のために複製される、センサアレイ上に形成された画像の画像データを生成するフローチャートである。

【符号の説明】

1 イメージングセンサチップ

2 レンズ系

3 センサアレイ

7 セグメントA

8 セグメントB

9 セグメントC

17 パイプラインA

18 パイプラインB

19 パイプラインC

21 A/D変換器

22 プロセッサA

10

20

30

40

50

- 2 3 A / D 変換器

2 4 プロセッサ B

2 5 A / D 変換器

2 6 プロセッサ C

2 8 再結合プロセッサ

2 9 画像記憶装置

【図 1】

【図 2】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図7】

【図8】

---

フロントページの続き

(51)Int.Cl. F I

H 0 4 N 5/335 (2006.01) H 0 4 N 5/335 Z

(72)発明者 デニー エム.リン

アメリカ合衆国 カリフォルニア州 92612, アーバイン, イノベーション ドライブ

110 キヤノン インフォメーション システムズ, インク. 内

審査官 仲間 晃

(56)参考文献 特開平11-027589 (JP, A)

特開平10-150604 (JP, A)

特開2000-196054 (JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/228

G06T 1/20

G06T 1/60

G06T 3/00

H04N 1/19

H04N 5/335